# OPTIMIZATION AND MINIATURIZATION OF MICROPROCESSOR POWER SUPPLIES

Thesis by Ognjen Djekić

In Partial Fulfillment of the Requirements for the degree of Doctor of Philosophy

California Institute of Technology Pasadena, California

2000 (Submitted November 9, 1999)

# © 2000

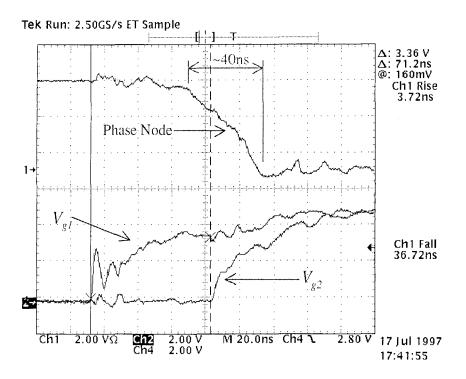

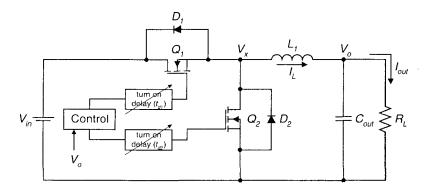

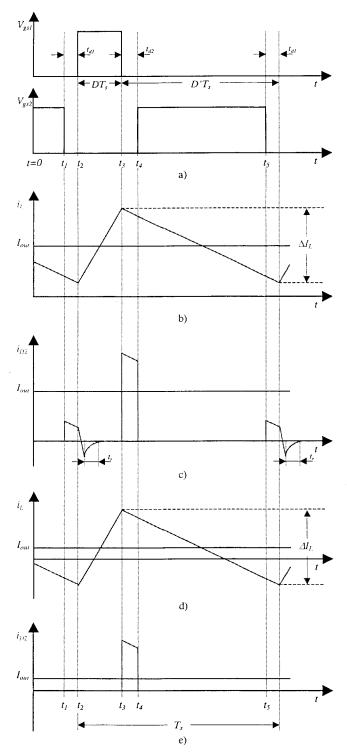

Ognjen Djekić All Rights Reserved To my family

# Acknowledgements

I wish to thank my advisor, Dr. Slobodan Ćuk, for the absolute freedom I have enjoyed in choosing my research topics, for his guidance and support, and most of all, for a wonderful professor-student relationship we shared. I also wish to thank Dr. Miki Brković for the enormous influence he has had on my work, for his guidance and help, and above all for his friendship. I also extend special thanks to Dr. Apurba Roy for offering me a chance to participate in the cutting edge research being performed in his group. I wish to express my gratitude to Dr. Kurt Schenk for his suggestions and many useful discussions we have had over the years. And last, but not least, I wish to acknowledge all the practical help and advice I received from Mr. Ron Law.

I gratefully acknowledge the financial support I received from Caltech, in the form of Graduate Teaching Assistantships, the Powell Fellowship, and the Killgore Fellowship, and the support I received from Lucent Technologies. I would also thank all the companies that supported the Power Electronics Group during my studies at Caltech: Lucent Technologies, Elgar Corporation, General Electric, Ascom Energy Systems AG, and Jet Propulsion Laboratory.

# Abstract

This thesis is motivated by the power demands of the modern Intel microprocessors. These microprocessors require a very stable and tightly controlled core supply voltage in order to reliably operate at their correct clock frequency. The core supply voltage has to remain within the prescribed window during normal operation, as well as during power-up and power-down when the processor current can change from almost zero to 16A or more in 200-300ns. Maintaining tight processor voltage regulation during these current transients can be difficult. In addition to stringent load transient specifications, a microprocessor power supply has to meet efficiency requirements, as well as size and cost requirements. Size requirements become especially important in portable computer systems where space is at a premium.

The work presented in this thesis deals with the optimization of the microprocessor power supply for performance, size and cost, with the emphasis on size. Every aspect of the power supply is carefully analyzed and optimized through the size prism: the topology, the control algorithm, and the components. Design and optimization tools are developed, and the theoretical calculations are verified in hardware. The result of the optimization is a microprocessor power supply that meets Intel Pentium III electrical performance specs in approximately one-fifth of the specified volume, resulting in a power density of roughly 40W/in<sup>3</sup>.

# Contents

| A | ckno  | wledg   | ements                                                                          | iv |

|---|-------|---------|---------------------------------------------------------------------------------|----|

| A | bstra | ıct     |                                                                                 | V  |

| 1 | Inti  | roduct  | ion                                                                             | 1  |

| 2 | Fro   | m the   | Silver Box to the VRM                                                           | 7  |

|   | 2.1   | Conve   | ntional Power Distribution Architecture                                         | 9  |

|   |       | 2.1.1   | Effects of the Parasitic Resistance of the Supply Path on the Processor Voltage | 10 |

|   |       |         | 2.1.1.A Remote Sensing                                                          | 12 |

|   |       | 2.1.2   | Effects of the Parasitic Inductance of the Supply Path on the Processor Voltage | 13 |

|   |       |         | 2.1.2.A Capacitive Bypassing                                                    | 15 |

|   | 2.2   | Distrit | puted Power Architecture                                                        | 16 |

|   |       | 2.2.1   | The VRM                                                                         | 17 |

|   |       |         | 2.2.1.A VRM Candidate Topologies                                                | 18 |

| 3 | Ov  | erview of the Buck Converter Load Transient Response                        | 19 |

|---|-----|-----------------------------------------------------------------------------|----|

|   | 3.1 | Overview of the Buck Converter Load Transient Response                      | 20 |

|   |     | Interval I <sub>1</sub>                                                     | 21 |

|   |     | 3.1.2 Interval I <sub>2</sub>                                               | 23 |

|   |     | 3.1.3 Interval I <sub>3</sub>                                               | 26 |

|   |     | 3.1.4 Interval I <sub>4</sub>                                               | 31 |

|   | 3.2 | Optimizing Voltage Budgeting                                                | 31 |

|   | 3.3 | Approaching the VRM Design Problem                                          | 33 |

|   |     | 3.3.1 Merits of the High Switching Frequency                                | 35 |

|   | 3.4 | VRM Design Philosophy                                                       | 36 |

| 4 |     | erview of Loss Mechanisms in the Buck Topology in natinuous Conduction Mode | 38 |

|   | 4.1 | Overview of Various Loss Mechanisms in the Regular Buck Topology            | 38 |

|   |     | 4.1.1 Losses in the main switch $(S_1)$                                     | 40 |

|   |     | 4.1.2 Loss Mechanisms in the Schottky Diode                                 | 42 |

| 4.2 | Overv | iew of the Losses in the Synchronous Buck Topology | .42  |

|-----|-------|----------------------------------------------------|------|

|     | 4.2.1 | Loss Mechanisms in the Main Switch                 | . 44 |

|     | 4.2.2 | Loss Mechanisms in a Synchronous Switch            | . 44 |

#

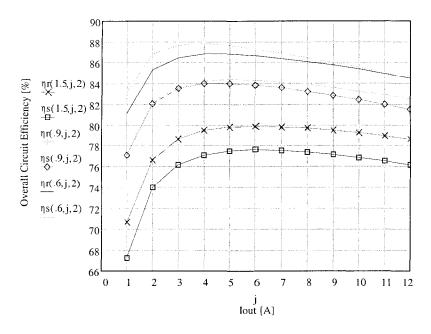

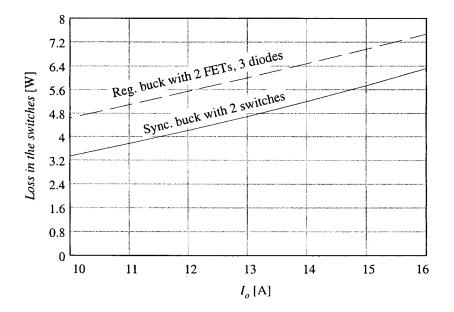

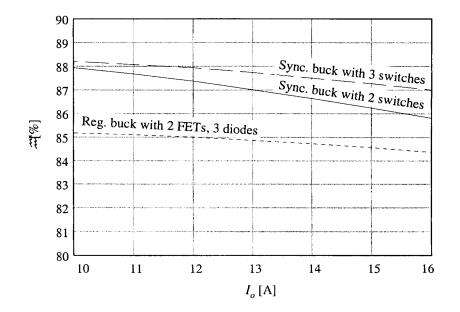

| 5.1 | Efficie | ency Cons  | derations                           | .47  |

|-----|---------|------------|-------------------------------------|------|

|     | 5.1.1   | Overviev   | v of Previously Published Work      | . 50 |

|     | 5.1.2   | Schottky   | Diode Vs. Synchronous Rectifier     | . 51 |

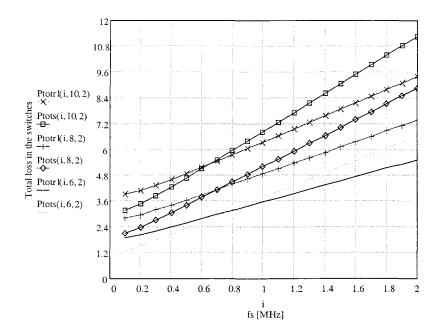

|     |         | 5.1.2.A    | Loss Evaluation in the Switches     | . 52 |

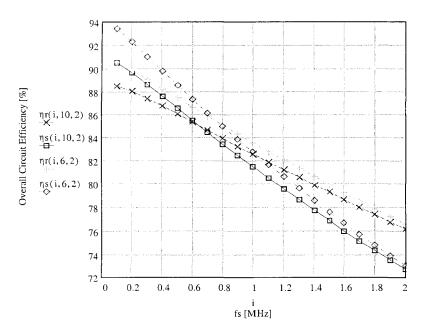

|     |         | 5.1.2.B    | Overall Efficiency Calculation      | . 54 |

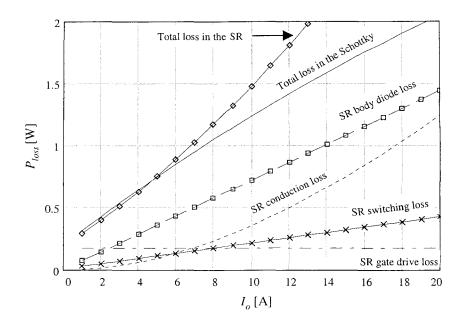

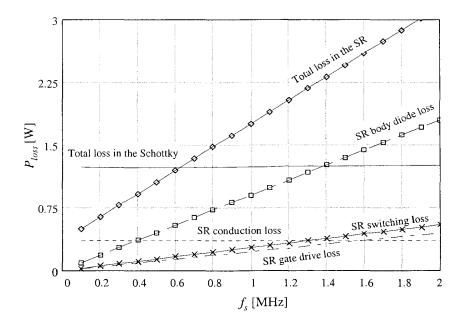

|     |         | 5.1.2.C    | Loss Distribution                   | . 56 |

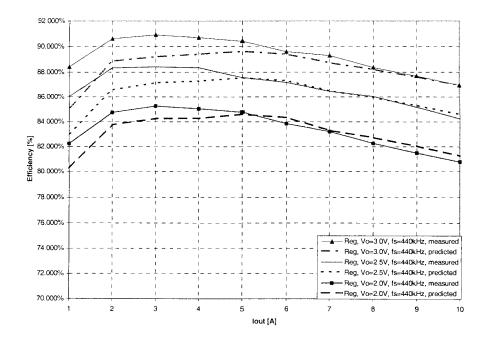

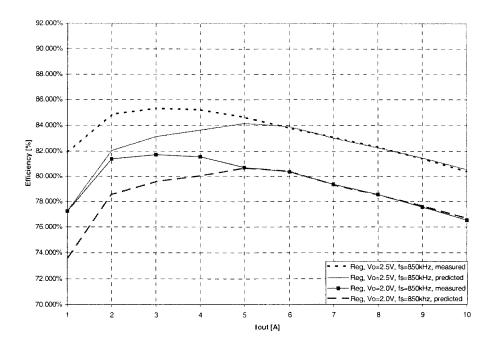

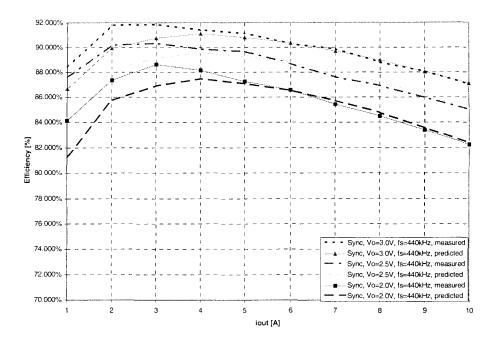

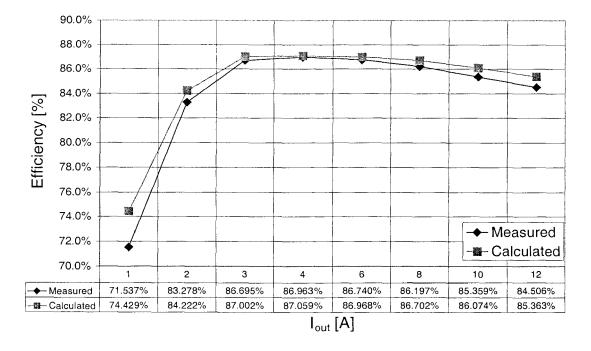

| 5.2 | Experi  | imental Ve | erfification                        | . 59 |

| 5.3 | On the  | e Accuracy | of the Component Level Distribution | .66  |

|   | 5.4  | Concl  | usion                                                                                                            | 67 |

|---|------|--------|------------------------------------------------------------------------------------------------------------------|----|

| 6 | Hig  | h Fre  | quency Synchronous Buck VRM                                                                                      | 70 |

|   | 6.1  | Overv  | view of Previously Published Work                                                                                | 71 |

|   | 6.2  | Overv  | iew of the Proposed Approach                                                                                     | 72 |

|   | 6.3  | Existi | ng Controllers                                                                                                   | 72 |

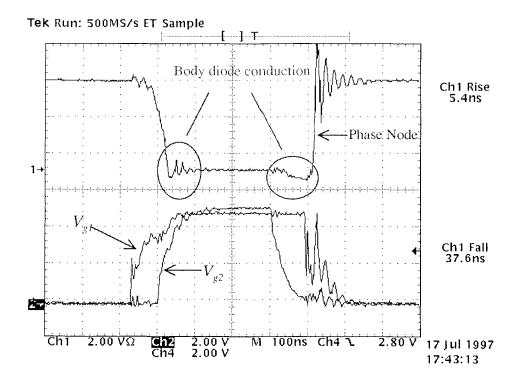

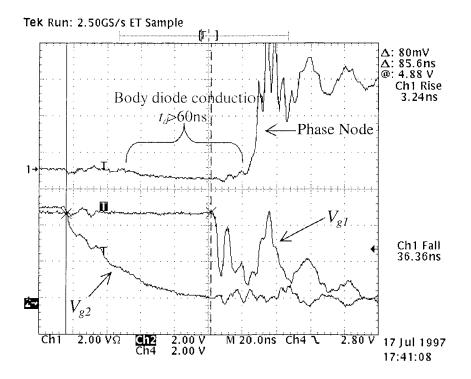

|   | 6.4  | Overv  | iew of the Synchronous Rectifier Loss                                                                            | 79 |

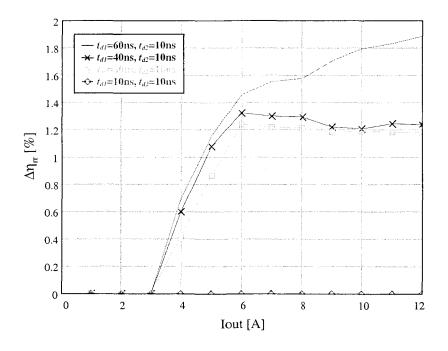

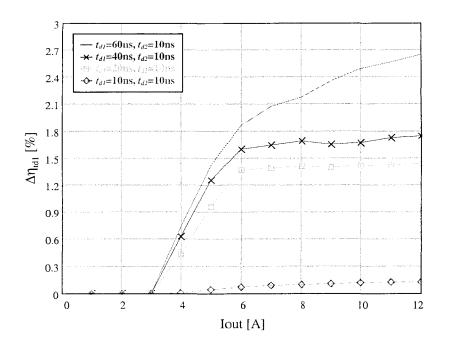

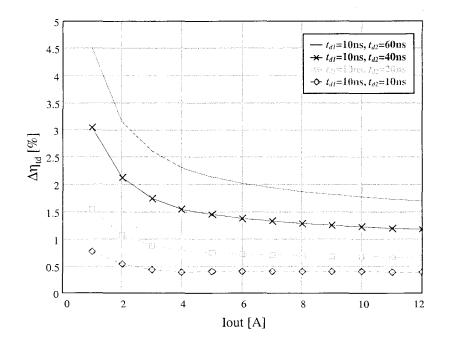

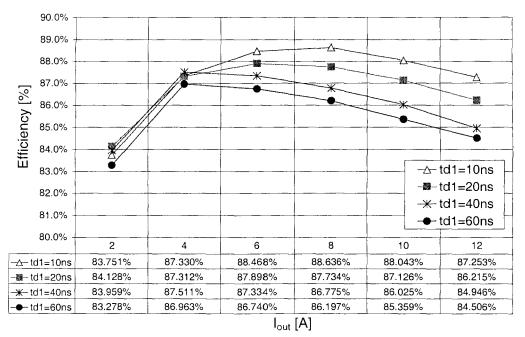

|   | 6.5  | Effect | of $t_{d1}$ on the Synchronous Buck Efficiency in Mode 1                                                         | 81 |

|   |      | 6.5.1  | Overall Efficiency Degradation Due to the Body Diode Conduction During $t_{d1}$ (mode 1)                         |    |

|   |      | 6.5.2  | Overall Efficiency Degradation Due to the Body Diode Reverse Recovery During $t_{d1}$ (mode 1)                   | 83 |

|   |      | 6.5.3  | Overall Efficiency Degradation Due to the Body Diode Conduction<br>and Reverse Recovery During $t_{d1}$ (mode 1) |    |

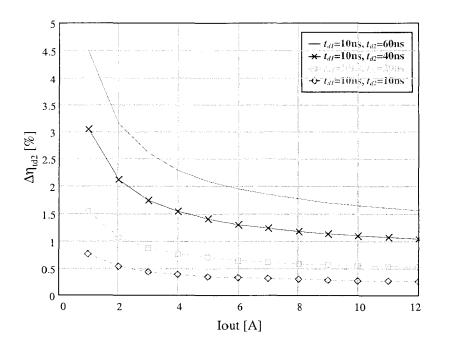

|   | 6.6  | Effect | of $t_{d1}$ on the Synchronous Buck Efficiency in mode 2                                                         | 86 |

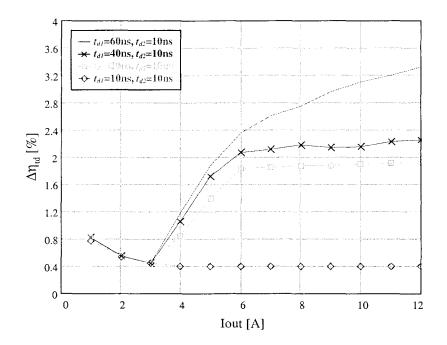

|   | 6.7  | Effect | of $t_{d2}$ on the Synchronous Buck Efficiency                                                                   | 88 |

|   | 6.8  | Effect | of $t_{d1}$ and $t_{d2}$ on the Synchronous Buck Efficiency                                                      | 90 |

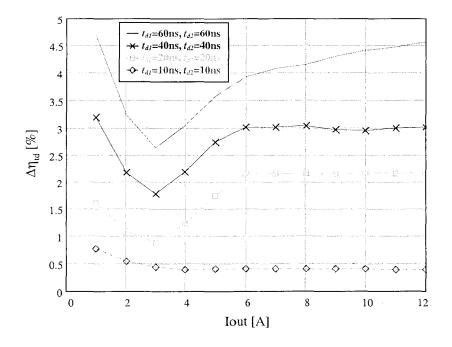

|   | 6.9  | New H  | High Performance Gate Drive Circuit                                                                              | 94 |

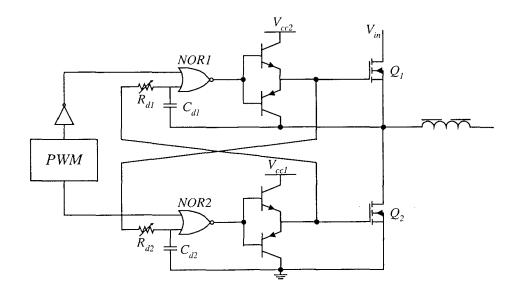

|   | 6.10 | Exper  | imental Verification                                                                                             | 95 |

|   | 6.11 | Concl  | usion                                                                                                            | 97 |

#

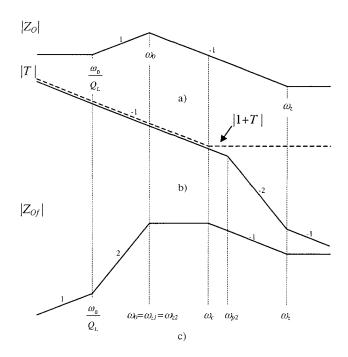

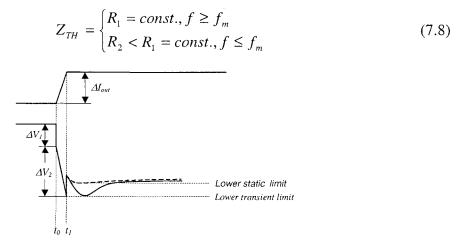

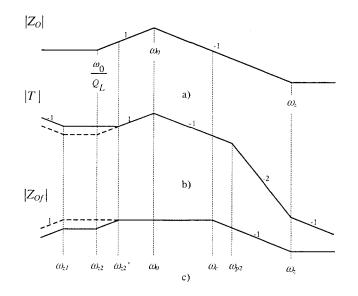

| 7.1 | Introd | uction                                      | 100 |

|-----|--------|---------------------------------------------|-----|

| 7.2 | Buck ( | Converter Load Transient Response Revisited | 103 |

|     | 7.2.1  | Interval I <sub>1</sub>                     | 105 |

|     | 7.2.2  | Interval I <sub>2</sub>                     | 106 |

|     | 7.2.3  | Interval I <sub>3</sub>                     | 107 |

|     | 7.2.4  | Interval I <sub>4</sub>                     | 108 |

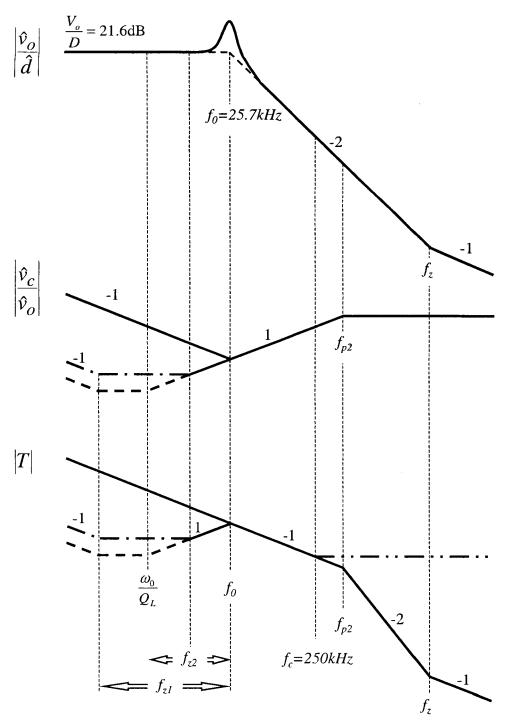

| 7.3 | Conve  | entional Loop Compensation                  | 108 |

| 7.4 | Optim  | um Load Transient Response                  | 111 |

viii

| 7.5 | Achieving Optimum Transient Response With Voltage Mode Control 111 |

|-----|--------------------------------------------------------------------|

| 7.6 | Analysis and Simulation115                                         |

| 7.7 | Calculating the Peak Voltage Deviation117                          |

| 7.8 | Experimental Verification117                                       |

| 7.9 | Conclusion                                                         |

# 8 Practical VRM Design Example ......120

| 8.1 | Board Specifications |                                            |     |

|-----|----------------------|--------------------------------------------|-----|

| 8.2 | Introd               | ductory Remarks                            |     |

| 8.3 | Power                | r Stage Design                             |     |

|     | 8.3.1                | Choosing the Inductor                      |     |

|     | 8.3.2                | Switch Implementation                      |     |

|     |                      | 8.3.2.A Choosing the Switches              |     |

|     |                      | 8.3.2.B Switch Efficiency Comparison       |     |

|     |                      | 8.3.2.C Choosing the Number of Switches    |     |

|     | 8.3.3                | Overall Circuit Efficiency                 |     |

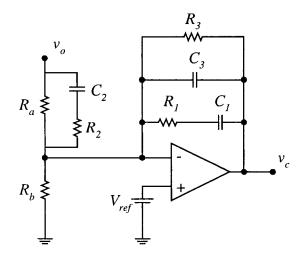

| 8.4 | Contro               | ol Loop Design                             |     |

|     | 8.4.1                | Placing Compensation Poles and Zeros       |     |

|     | 8.4.2                | Circuit Implementation                     |     |

|     | 8.4.3                | Circuit Simulation                         |     |

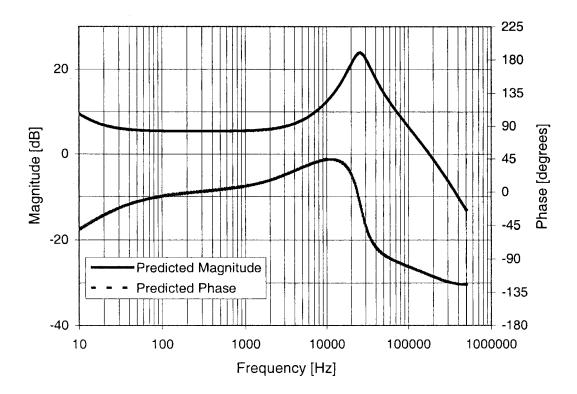

|     |                      | 8.4.3.A Loopgain Calculation               |     |

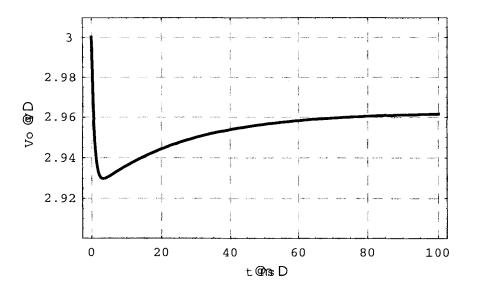

|     |                      | 8.4.3.B Load Transient Response Simulation |     |

| 8.5 | Experi               | rimental Results                           |     |

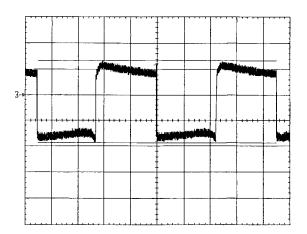

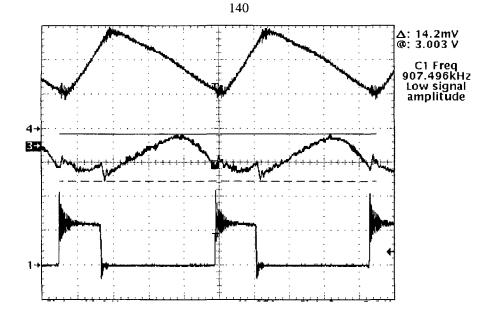

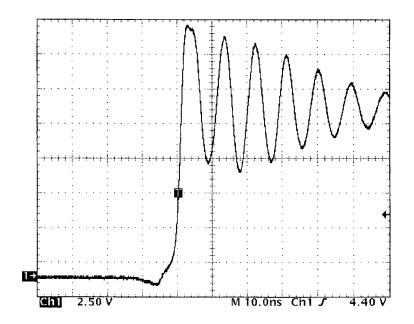

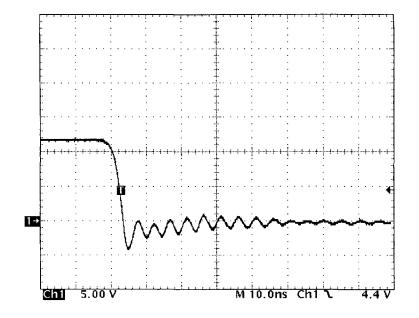

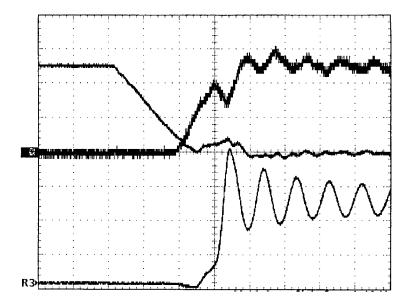

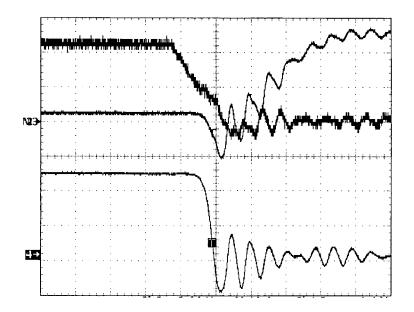

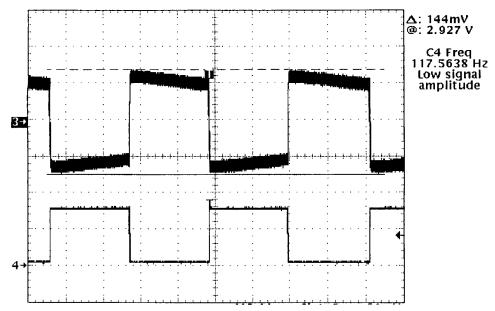

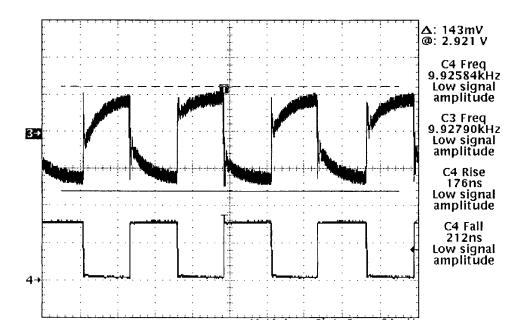

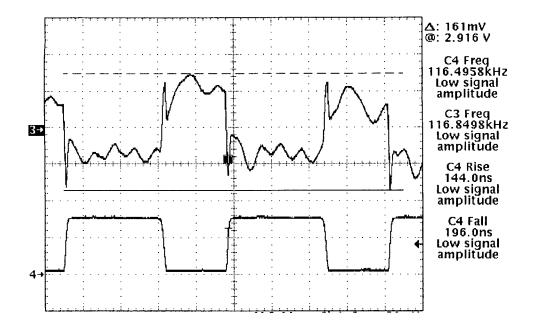

|     | 8.5.1                | Circuit Waveforms                          | 139 |

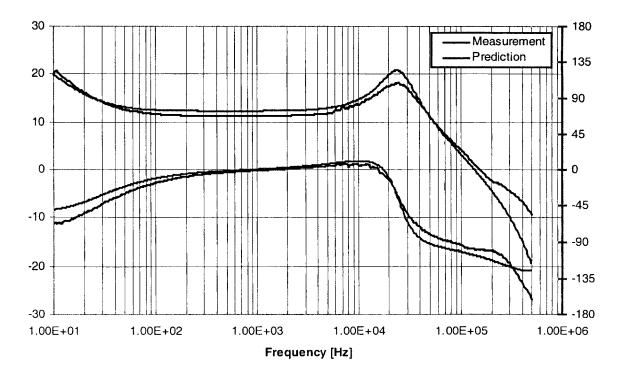

|     | 8.5.2                | Loopgain Measurement                       | 144 |

|     | 8.5.3                | Load Transient Response                    | 145 |

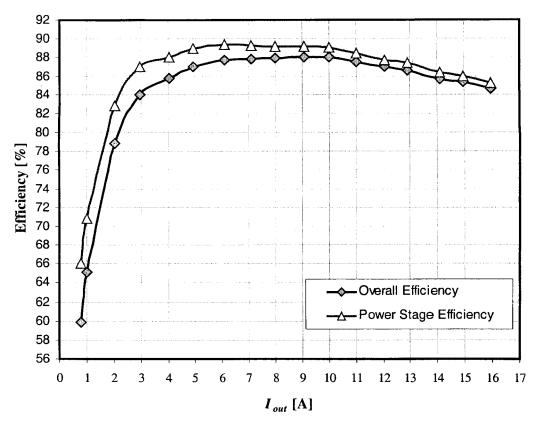

|     | 8.5.4                | Efficiency Measurements                    | 147 |

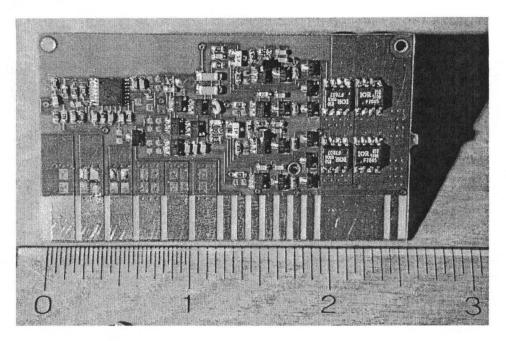

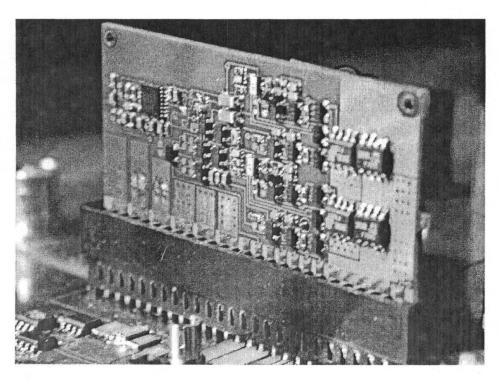

|     | 8.5.5                | Physical Dimensions                        |     |

| 8.6 | Conclu               | luding Remarks                             | 149 |

| 9 | Conclusion152 |

|---|---------------|

|   |               |

|   |               |

## Chapter 1

# Introduction

Today, we live in an increasingly "electronic" world dominated by computers, mobile phones, and pagers. Having instant access to information anywhere and everywhere is becoming essential. And, as the world strives for global connectivity, it leaves it up to the discipline of power electronics to provide the power the world needs to achieve its goal.

Power electronics, in general, deals with the conversion of electric power from one form to another. Since electric power can be either dc-power or ac-power, only four power conversion possibilities exist; namely, dc-to-dc, dc-to-ac, ac-to-dc, and ac-to-ac.

Electronic equipment such as computers and other types of consumer electronic devices operate from dc-power. However, the commonly available power sources are the ac-power from the utility grid and dc-power from batteries. Neither of these power sources can readily power a typical electronic device. Instead, this power has to be conditioned before it can be used. In case of the utility grid, the ac-power needs to be converted to dc-power; in case of a battery source, the dc battery voltage usually needs to be converted to different value of dc voltage.

An example of the utility ac-power being converted to dc-power is a desktop computer. The computer power supply, commonly referred to as the "silver box," takes the ac-power input and converts it to several dc-power outputs required for the proper operation of the computer system. In the past, dc-power provided by the silver box was good enough to guarantee proper operation of the microprocessor and the entire system. However, constant advances in silicon processing enabled the processor manufacturers to increase the number of devices per unit area of a silicon wafer. As the device density per unit area increased, more and more computational power could be packed in the same silicon area. But, as the number of devices increased, so did the power requirements of the processor. Fueling more and more complex processors with higher and higher clock rates became a rather difficult problem for several reasons. First, in an effort to reduce the power dissipated by the processor, CPU manufacturers started lowering the operational voltage of their chips. As a result, maintaining the logic level accuracy became harder simply due to less available voltage headroom. This immediately translated into severe restrictions on the variation of the processor supply voltage, and thus, into very tight power supply output voltage regulation requirements.

Second, the increased number of devices per unit of silicon area of the processor increase the current consumption of the part. The power supply has to be able to deliver the current required by the processor both during normal operation and during "wake up" and "power down" sequences while maintaining a tight output voltage regulation. The "wake up" and "power down" sequences are particularly taxing for the power supply. In these modes of operation the current consumption of the processor can change from maximum to minimum in a matter of nanoseconds. Yet, the power supply has to meet

2

the processor current demands and keep the processor supply voltage variation within the prescribed limits to insure normal, reliable, high-speed operation of the system.

In light of the development trends in the microprocessor industry, it became clear the silver box was no longer able to adequately fuel the modern "megaprocessor". The conventional power distribution scheme in which the silver box supplied power to a connector at one end of the motherboard had to be changed. The long power traces from the motherboard power connector to the processor introduced too much parasitic inductance and resistance into the supply line. These parasitics were the cause of unacceptable processor supply voltage variations under normal operating conditions. The only way to eliminate the effect of the parasitics associated with the power supply traces was to make them as short as possible. Hence, a new power distribution philosophy was born. The dc voltage provided by the silver box had to be stabilized at a location physically close to the load, the microprocessor. The dc-to-dc converter used to achieve this goal became known as the Voltage Regulator Module (VRM) or the Point-of-Load module. The VRM's job was to tightly control the microprocessor supply voltage and provide the required current on demand. Due to the proximity of the VRM to the processor, the parasitics between the processor and the VRM output were minimized and limited to the resistance and inductance of a short supply trace and the processor package leadframe. Now, the processor supply voltage could be tightly controlled providing that the VRM had good load transient response. In addition to good transient response, the VRM had to meet additional requirements. The VRM had to be efficient, small, and low cost. VRM efficiency was important because of the cooling and heat removal issues around the processor that dissipates power by itself. In addition, the efficiency of the VRM is crucial for battery life in laptop computers. Keeping the size of the VRM small was important due to the limited amount of space available on the motherboard. Finally, the low cost requirement was obviously of a purely economic nature and in line with trying the keep the overall cost of the computer system at an absolute minimum. Clearly, the VRM has to satisfy a number of conflicting conditions. The optimization of a VRM is the focus of this thesis.

As it was demonstrated on an example of a desktop computer, ac-power has to first be converted to dc-power, and then processed again by a dc-to-dc converter before it can be used to power a modern microprocessor. On the other hand, when the supply is a dc battery source instead of the utility ac-grid, the ac to dc power conversion is eliminated, but the dc-to-dc conversion still has to take place. Various examples of this type of conversion are found in mobile phones, pagers, and all kinds of other hand-held and portable equipment. While these devices require much less power than a microprocessor of a desktop computer, the VRM and the power supply of a mobile phone share several common characteristics: high efficiency, small size, and low cost. In battery powered applications, the efficiency of the power supply is of utmost importance. Since the power source is limited, the less power is wasted in the power supply, the longer will the device be able to operate before the battery is fully discharged. The size and weight of the power supply are equally important in portable equipment. In order to make a portable device convenient and portable, it has to be small and light. Keeping the size and the weight of the power supply at a minimum contributes to the reduction of the size and the weight of the overall system making it more convenient, portable, and more attractive to

4

the consumer. Finally, the last, but no less important, concern is to maintain the low cost of the power supply in order not to drive up the cost of the portable device.

In light of these developments in the computer and portable electronic device industries, the dc-to-dc converter, and its designer, are facing never before encountered challenges in dc-to-dc power conversion. The only presently known way to reduce the size of a switching dc-to-dc power supply is to increase its switching frequency. Unfortunately, the efficiency of the power supply is heavily dependent on the switching frequency. Therefore, a reduction in size of the power supply is inevitably accompanied by the degradation of its efficiency. Furthermore, maintaining a tightly regulated processor supply voltage under a zero to full load current transient requires, in a conventional design, a significant amount of capacitance at the output of the power supply. Providing an adequate amount of capacitance to meet the transient specifications results in an increase of the size of the power supply and contradicts the goal to keep the power supply small. Ways to reconcile these conflicting requirements and optimize the dc-to-dc power supply for computer and mobile applications are addressed in this thesis.

The analysis presented in this thesis was motivated by VRM specifications. However, developed concepts and optimization tools are general, and can readily be applied in other arenas where high efficiency and small size are of particular interest.

VRMs are designed to use the voltages provided by the silver box (3.3V, 5V, 12V) and convert them into an appropriate processor supply voltage requested by a five bit voltage identification code supplied by the processor to the VRM. The switched mode power supply best suited for VRM applications is a step-down buck converter. There are two possible implementations of a buck converter: regular buck and synchronous buck.

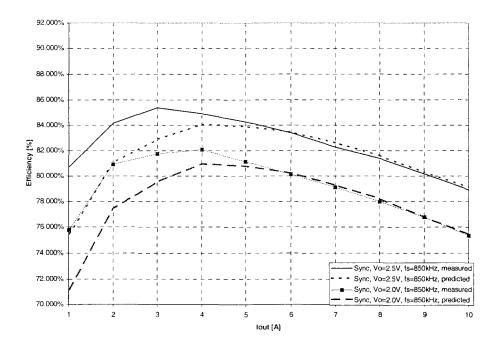

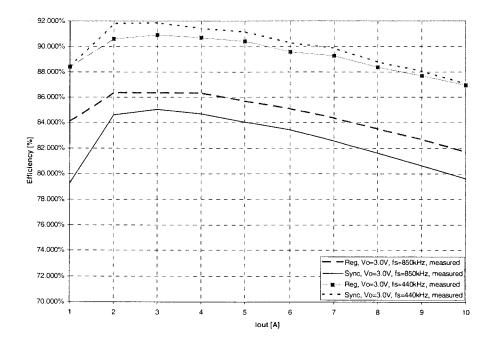

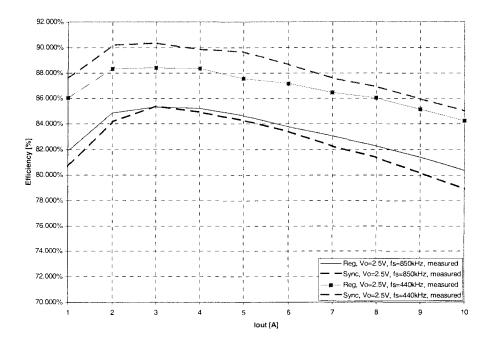

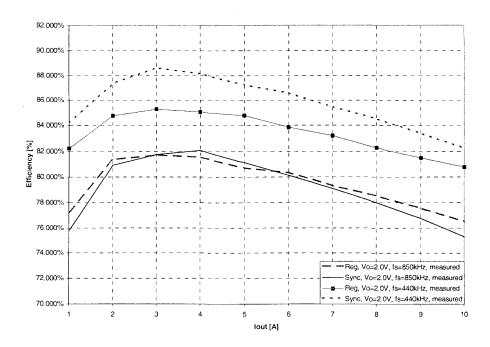

Chapter 5 compares the efficiency of these two implementations of the buck converter. The efficiency is studied as a function of the switching frequency and of the load current. This analysis is aimed at exploring the feasibility of reducing the size of the power supply by increasing the switching frequency while maintaining a high efficiency. The loss distribution is used to identify areas in which improvements can be made.

The advantages and weaknesses of both implementations of a low voltage, buck converter operating at a high switching frequency were clearly exposed in Chapter 5. The examination of the loss distribution in the synchronous buck converter revealed that the switch timing is critical for efficient operation at moderately high switching frequencies. Chapter 6 addresses the switch timing issues in the synchronous buck converter and proposes a switch driver that significantly improves the efficiency of the synchronous buck VRM.

Unlike Chapters 5 and 6 which primarily deal with the efficiency of the VRM, Chapter 7 is devoted to its load transient response. Chapter 7 defines the optimum transient response and discusses the proper ways to close the voltage mode control loop in order to achieve the desired transient response.

6

### Chapter 2

# From the Silver Box to the VRM

The demand for faster, more powerful computers keeps pushing the microprocessor manufacturers to pack more computational power and more features into each new generation of microprocessors. As a result, the power requirements of the microprocessor have steadily been increasing. Under the circumstances, thermal management became a significant concern. Adequate cooling of the processor, and the entire system, became increasingly difficult. To alleviate the problem, CPU designers lowered the supply voltage required by the core logic of the processor. A lower operating voltage of the processor core logic results in lower processor power requirements providing the clock frequency remains unchanged. Or, looking at it in another way, for a given power dissipation, a processor with a lower core logic operating voltage can run at a higher clock frequency. Hence, it is quite clear that as microprocessors become more powerful, they will continue to migrate to lower voltages and higher operating currents making power distribution and delivery an important aspect of the overall system architecture.

In November of 1995, Intel published the power supply guidelines for the Pentium<sup>®</sup> Pro processor [17]. Selected electrical specifications for a 150MHz, 256-Kbyte L2 Cache Pentium Pro<sup>®</sup> are presented in Table 2.1. Most of the specifications contained in Table 2.1 are common in dc-to-dc converter data sheets: input voltage, output voltage, peak load current, and maximum output voltage ripple. The only processor power supply specific requirement is the unusually demanding load transient response spec. According to Table 1.1, the output voltage of the converter has to stay within  $\pm 5\%$  of the nominal voltage under all normal operating conditions, including a sudden  $I_{min}$  to  $I_{peak}$  output current transient.

| Parameter                                 | Value                    |

|-------------------------------------------|--------------------------|

| Output voltage                            | 3.1V                     |

| Output voltage ripple and noise           | ±1%                      |

| Output voltage variation with load        | ±2%                      |

| Transient output voltage tolerance        | ±5%                      |

| I <sub>min</sub>                          | 0.3A                     |

| I <sub>max</sub>                          | 9.9A                     |

| $I_{peak}$ (several $\mu$ s of overshoot) | 11A                      |

| Slew rate ( $I_{min}$ to $I_{peak}$ )     | 30A/µs at converter pins |

| Load toggle rate                          | 100Hz to 100kHz          |

Table 2.1: Pentium Pro power supply specifications

The specified tight output voltage regulation is essential for proper operation of the processor. Overshooting the voltage specification can cause certain signals to violate the

Minimum Valid Delay timing specifications. This timing violation will lead to system instability and failure. Furthermore, excessive and sustained overshooting can cause hot electron related effects that can compromise the reliability and the life of the processor.

Undershooting the voltage specification, on the other hand, degrades the performance of the processor, and can lead to timing related failures. The processor will not function properly at its correct clock frequency. The effects of undershooting are further aggravated by improper cooling mechanisms.

#### 2.1 Conventional Power Distribution Architecture

In the previous section we described some of the mechanisms that cause unreliable system operation and system failure when the processor supply voltage deviates more than  $\pm 5\%$  from nominal. Hence, the processor voltage has to be tightly controlled to ensure proper, reliable high speed operation. The question is, how can this voltage regulation be achieved.

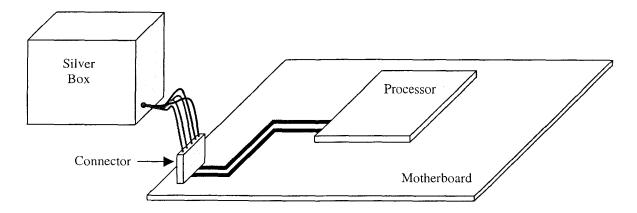

Let's start off with the conventional, centralized power distribution scheme shown in Fig. 2.1. This power distribution architecture is standard in desktop systems. In this

*Figure 2.1: Conventional desktop computer power distribution scheme*

9

approach, an off-board power supply (the silver box) converts the AC voltage from the supply line into several DC voltages needed by the processor and other peripheral devices. The appropriate output of the silver box is connected to a connector located at the edge of the motherboard using a number of wires approximately 6 to 8 inches long. From the motherboard connector, the supply voltage is routed to the processor using heavy copper traces on the motherboard.

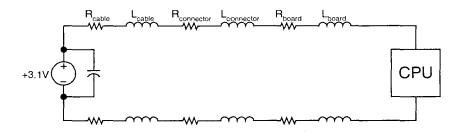

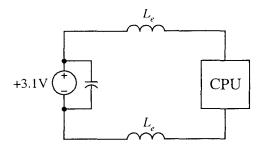

In an effort to evaluate whether this conventional approach is adequate for powering Pentium<sup>®</sup> Pro processors, a lumped circuit model of the conventional power distribution architecture was developed. As Fig. 2.2 shows, the output of the silver box is modeled by an ideal voltage source; the wiring, the motherboard connector, and the PCB traces are modeled by their respective series resistance and inductance; the supply and the return paths are modeled separately. The model of Fig. 2.2 can be used to calculate the voltage at the processor pins during both steady state operation and sudden processor current transients.

Figure 2.2: Model of the conventional power distribution scheme

# 2.1.1 Effects of the Parasitic Resistance of the Supply Path on the Processor Voltage

The effects of the supply path resistance will be studied under the assumption that the processor is constantly drawing its maximum rated current from the power supply.

Under this assumption,  $I_{out}=11$ A=const. Consequently,  $\frac{dI_{out}}{dt}=0$  resulting in a zero voltage drop across all the inductances in Fig. 2.2. Therefore, all the inductances can, for the moment, be neglected. After neglecting all the inductances and collecting all the resistances in the supply path into a single resistor  $R_s$ , and all the resistances in the return

Vau

Vau

Vau

Vau

Vs\*

10mOhm

3.1 V

2.88V

Regulator

10mOhm

Grid

10mOhm

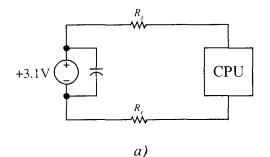

Figure 2.3: a) Simplified model of the conventional power distribution scheme; b) Voltage drops observed in the system

*b*)

path into  $R_r$ , we arrive at a simplified, steady state model of the conventional power distribution scheme. This simplified model is shown in Fig. 2.3a.

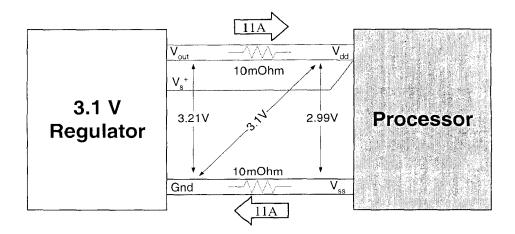

If we assume that the total resistance in the supply path, denoted by  $R_s$  in Fig. 2.3a, is only 10m $\Omega$ , and is equal to the total resistance in the return path,  $R_r$ , we can easily calculate the voltage at the processor pins. The results of the voltage calculations are given in Fig. 2.3b. Fig. 2.3b shows the voltage across the processor pins to be only 2.88V at the rated processor current because of the voltage drop caused by the resistance of the supply and the return path.

According to Table 2.1, the maximum allowed supply voltage variation with load is  $\pm 2\%$  of 3.1V, or  $\pm 62$ mV. Thus, the minimum processor supply voltage is 3.1-0.062=3.038V. Fig. 2.3b shows assuming even a minimal supply trace resistance of 10m $\Omega$ , the conventional power distribution architecture cannot meet the Pentium<sup>®</sup> Pro specs during steady state operation. In fact, just to meet steady state specs, the total resistance of the supply path together with the return path would have to be less than 14m $\Omega$ . Since the 14m $\Omega$  has to include approximately 16 inches of wire, the motherboard connector, and PCB traces, it is clear that this architecture cannot meet the processor's power requirements.

#### 2.1.1.A Remote Sensing

The voltage droop caused by the large processor current across a small parasitic resistance of the supply path,  $R_s$ , can be remedied by the use of a regulator that supports remote sensing. Remote sensing is a technique that uses extra connections to sense and regulate the voltage at the point of use. The voltage sense leads carry almost no current and are, therefore, unaffected by the resistance in their path. Consequently, the voltage is accurately regulated at the sense points. Fig. 2.4 shows a system that offers remote sensing in the supply path. The regulator now regulates the voltage at the processor supply pins with respect to the regulator ground (Gnd). Consequently, as Fig. 2.4 shows, the regulator raises the voltage at its output pins in order to compensate for the voltage drop in the supply line. The regulator does not, however, compensate for the drop in the

Figure 2.4: Conventional desktop computer power distribution scheme with remote sensing in the supply path.

return path. There are two possible solutions to this problem. The first is to minimize the resistance in the return path by using heavy ground planes and multiple processor connections. The other possibility is to use a regulator that offers remote sensing in both the supply and the return paths. However, the addition of the return path sense considerably complicates regulator design, and most off-the-shelf regulators do not offer it.

# 2.1.2 Effects of the Parasitic Inductance of the Supply Path on the Processor Voltage

Due to the high specified processor current slew rate, the parasitic inductance of the power supply lines presents an even greater problem than its parasitic resistance. In order to fully appreciate the magnitude of the problem, consider the following: 1cm of round wire in air exhibits approximately 10nH of inductance. The voltage drop across this piece of wire can be calculated according to

$$\Delta V = L \frac{di(t)}{dt} \tag{2.1}$$

Substituting for  $\frac{di(t)}{dt}$  in (2.1) the specified load current slew rate of  $0.03 \frac{\text{A}}{\text{ns}}$  gives us a voltage drop of 300mV! So, only 1cm of wire between the source and the processor pins is enough to push the voltage at the processor pins out of spec regardless of the behavior of the source. To illustrate this, consider the circuit in Fig. 2.5 obtained from the circuit of Fig. 2.2 by setting all the resistances zero and replacing the CPU with a time varying current source. Even though  $V_I$  is assumed to be an ideal voltage source, the voltage across the current source (CPU) will experience a constant droop equal to

$$\Delta V = 2L \frac{di(t)}{dt} = 600 \text{mV}$$

(2.2)

during the 360ns it takes the processor current to ramp up to its maximum value. In other words, the ability of a power supply to respond to the kind of load current change specified in Table 2.1 is no longer dominated exclusively by the speed of the control loop. Instead, the inductance of the supply determines how quickly can current be delivered to the load. In fact, unless this inductance can be made low enough, even an ideal voltage source cannot meet processor supply voltage tolerances.

*Figure 2.5: Simplified model of the computer power distribution architecture during the load transient*

The previous example shows that as little as 10nH of inductance in the supply path drives the voltage at the processor pins way outside the specifications. In the conventional power distribution architecture, a typical supply path includes, as shown in Fig. 2.1, approximately 16 inches of wire, a motherboard connector, and PCB traces. Thus, the total inductance in the supply path is far greater than 10nH. This parasitic inductance of the supply path makes it impossible for any off-board power supply, with or without a remote sense, to meet the specifications outlined in Table 2.1.

In the preceding discussion, the output of the silver box had been modeled by an ideal voltage source to illustrate the effect of supply line inductance on the voltage at the processor pins. In reality, however, the silver box is a switched mode power supply whose output voltage is regulated by a feedback loop. A typical switching frequency of the converter inside a silver box is around 100kHz. Thus, the duty cycle of this power supply is updated every 10µs. By comparison, the processor current ramps up in only 360ns. Clearly, the power supply cannot respond to this change in its load current until the beginning of the next switching cycle. This inherent inability to react faster causes the output voltage of the power supply to droop. As a result, the initial fast spike at the processor supply pins caused by the voltage drop across the supply line inductance is followed by a slow voltage droop caused by the droop of the supply's output voltage. This droop is the difference between the response of an ideal voltage source and a real life power supply to the load current change specified in Table 2.1.

#### 2.1.2.A Capacitive Bypassing

The only way to quickly deliver current to the load is to place a source physically close to the load. This is accomplished through proper use of bypass capacitors. Bypass

15

capacitors are placed close to the processor in order to minimize the inductance and the resistance of the trace that connects them to the processor supply pins. As a result, the stability of the processor voltage can be improved.

As it was pointed out in the preceding section, a power supply needs time to respond to a sudden change in its load current. Placing bypass capacitors close to the processor allows them to supply the processor current and maintain the voltage at the processor pins within transient limits until the power supply responds. As a result, the number and the quality of the bypass capacitors exclusively determine the initial response to a fast current transient.

Theoretically, the centralized power distribution scheme of Fig. 2.1 could meet the Pentium Pro specifications with the use of remote sensing and enough bypass capacitance. However, due to the inductance of the wiring that connects the output of the silver box to the bypass capacitor bank, the required number of bypass capacitors would be very large. These capacitors would add to the overall cost of the system and occupy valuable motherboard real-estate. Furthermore, with increasing power demands, this system would become increasingly cumbersome, expensive and, therefore, impractical.

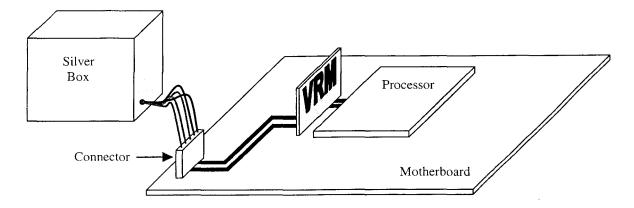

#### 2.2 Distributed Power Architecture

In light of the challenges posed by the parasitic inductance and resistance of the conventional supply path, a logical, new distributed power delivery architecture, shown in Fig. 2.6, was adopted. The idea behind the new architecture was to minimize the physical distance between the output of a fast supply with tight regulation, named Voltage Regulator Module (VRM), and the load (CPU). In this way, the voltage is tightly regulated at the point of use, and supplied to the processor supply pins using only

Figure 2.6: Distributed desktop computer power distribution scheme

a short, low inductance, low resistance PCB trace. So, while the length of the supply path hasn't really changed in comparison with the conventional power distribution architecture, "re-regulation" of the silver box voltage close to the processor eliminates the effects of the parasitic inductance and resistance of the lengthy supply path on the voltage at the processor supply pins. Furthermore, good transient performance of the VRM, and its proximity to the point of use make it possible to significantly reduce the amount of required bypass capacitance in comparison with the conventional centralized power distribution scheme.

#### **2.2.1** The VRM

In addition to good transient performance, the VRM has to satisfy several other conditions. First, the VRM needs to be as efficient as possible to minimize the power it dissipates inside the system. An efficient VRM will keep its contribution to the temperature rise inside the system at a minimum, and thus, facilitate the overall thermal design of the system. Second, the VRM has to be small to allow it to be placed as close to the point of use as possible without taking up more valuable space than it is absolutely

necessary. And finally, the VRM should be inexpensive in order not to increase the price of the entire system.

#### 2.2.1.A VRM Candidate Topologies

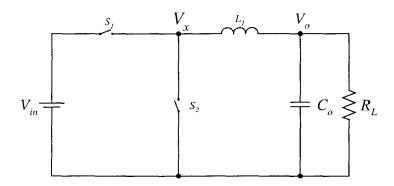

According to the specifications in Table 2.1, the task at hand is to design a DC-DC converter with a 5V input and an output of 3.1V; no isolation is required.

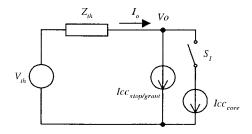

A buck converter shown in Fig. 2.7 is the simplest, and the most cost-effective, way to achieve non-isolated voltage step-down in the specified voltage range. Furthermore, the buck topology has no internal capacitive energy storage-the output is directly connected to the input during the on-time of the main switch ( $S_I$ ). Therefore, a buck converter is well suited to respond to sudden load current changes, an absolute must in VRM applications.

Figure 2.7: Basic buck converter

While the buck topology clearly stood out as the most-likely-to-succeed VRM candidate, it was less than obvious which buck topology implementation, regular or synchronous, would be the best choice. This question will be addressed in detail in Chapter 5.

## **Chapter 3**

# Overview of the Buck Converter Load Transient Response

A Pentium Pro VRM has to meet or exceed a number of electrical and mechanical specifications. Per Table 2.1, the two most challenging electrical specifications are the required tight output voltage regulation of  $\pm 5\%$  during a fast zero to full load output current transient and the required high efficiency at full load. Still, meeting these specifications by themselves would not be particularly hard What makes VRM design rather difficult is meeting these electrical specifications in absolutely the smallest volume possible.

The first thing a VRM has to satisfy are the transient response specifications. If they are not met, the module cannot perform its function, and is useless. Thus, meeting the transient response specs has to be chosen as the starting point in VRM design. The constraints imposed by the transient response largely determine the direction that the design will take.

In Chapter 2, the buck topology has been identified as a topology suitable for VRM applications. Since the load transient response has been identified as a starting point in

VRM design, the load transient response of the chosen topology has to be thoroughly analyzed and well understood in order to insure an optimum overall design.

#### 3.1 Overview of the Buck Converter Load Transient Response

The chosen VRM topology, a buck converter, was given in Fig. 2.7, and is reproduced here, in Fig. 3.1, for convenience. Per Table 2.1 the load current transient occurs in approximately 360ns. By today's standards, a rather high power supply switching frequency might be around 500kHz, resulting in a switching period of  $2\mu$ s. Thus, even if the converter is switching with a rather high switching frequency, the load current transient still occurs in about a sixth of the regulator's switching period.

Figure 3.1: Basic buck converter

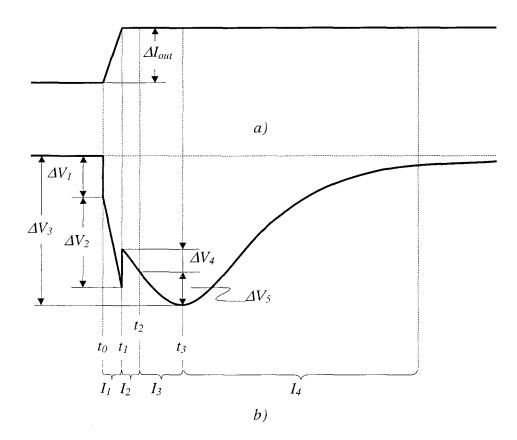

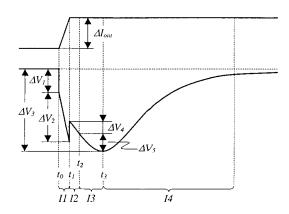

A typical regulator response to an almost zero to full-load load current change occurring within a fraction of the regulator's switching period (see Fig. 3.2a) is sketched in Fig. 3.2b. After a load current transient, the converter will need a number of switching cycles to reach a new steady-state. During the transition to the new steady state, four distinct response intervals,  $I_1$  through  $I_4$ , can be identified as shown in Fig. 3.2b. The first interval,  $I_1$ , coincides with the rise-time of the load current;  $I_2$  represents the response delay inherent to switching converters;  $I_3$  is the time it takes the average inductor current

to become equal to the load current, and  $I_4$  is the interval during which the output voltage recovers to its nominal value after reaching its minimum value at  $t=t_3$ .

Figure 3.2: Typical load transient response of a buck converter: a) load current step, and b) output voltage

#### 3.1.1 Interval I<sub>1</sub>

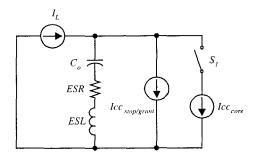

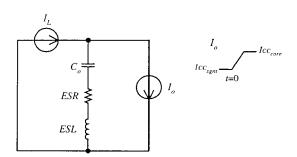

A switching converter is effectively a discrete-time system whose duty cycle gets updated once during each switching period. Every switching converter is in a sense a discrete-time system because the duty cycle is updated only once during each switching period. Since the load current transient occurs in a fraction of the switching period, an inherent delay will exist between the time when the load current transient occurs and the time when the duty cycle gets updated at the beginning of the new switching period. During this interval there is no control action, and the converter is responding essentially in an open loop fashion. Consequently, the output of the converter of Fig. 3.1 can be modeled as shown in Fig. 3.3.

Figure 3.3: Converter output model during the intervals  $I_1$  and  $I_2$

Because the load current transition is much shorter than the switching period of the converter, the output impedance of the converter is simply the impedance of the output capacitors. Therefore, the peak output voltage deviation during  $I_1$  can be expressed as:

$$\Delta V_{o1} = \Delta V_1 + \Delta V_2 = ESL \frac{dI_o}{dt} + ESR \cdot \Delta I_o + \frac{1}{2} \frac{\Delta I_o^2}{C_o \frac{dI_o}{dt}}$$

(3.1)

Hence, the peak output voltage deviation during  $I_1$  depends on the load current slew rate, and the *ESR* and *ESL* of the output capacitors. The magnitude of the spike observed during  $I_1$  is independent of the control loop bandwidth and the chosen switching frequency. Clearly, the only way to reduce the magnitude of this spike is to place a sufficient number of very high quality (low *ESR* and *ESL*) capacitors in parallel at the converter output.

#### 3.1.2 Interval I<sub>2</sub>

Because of the high load current slew rate, the load current will have reached its final value long before the controller can respond to this change in the operating point. Consequently, there will be no control action present during  $I_2$ , and the converter will continue to respond in an open loop fashion to the sudden load current change that had occurred. Thus, the model of Fig. 3.3 remains valid, and can be used to calculate the peak voltage deviation during  $I_2$ .

Since the control loop cannot respond fast enough to the load current change, once the load current reaches its final value at  $t_1$ , it will continue to discharge the output capacitors until the controller turns the main switch  $(S_1)$  on at  $t_2$ . The resulting output voltage drop is:

$$\Delta V_4 = \frac{I_o}{C_o} \cdot D' \cdot T_s = \frac{I_o}{f_s \cdot C_o} \cdot \left(1 - \frac{V_o}{V_{in}}\right)$$

(3.2)

where  $f_s$  is the switching frequency of the converter, and D' is the duty factor of the switch  $S_2$ .

Equation (3.2) shows that the peak voltage drop during  $I_2$  is inversely proportional to the switching frequency and the output capacitance. Thus, keeping  $\Delta V_4$  small requires either a large output capacitor or a high switching frequency.

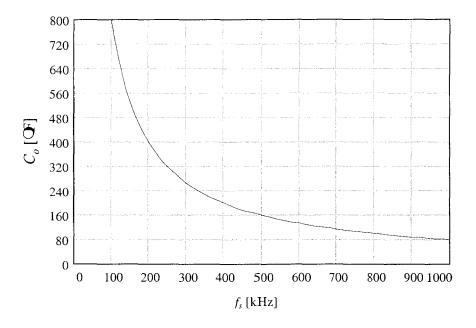

In order to get a quantitative feel for how the size of the output capacitor depends on the chosen switching frequency, (3.2) can be rewritten in the following way:

$$C_o = \frac{I_o}{f_s \cdot \Delta V_4} \cdot \left(1 - \frac{V_o}{V_{in}}\right)$$

(3.3)

From (3.3) we can calculate the amount of output capacitance needed to achieve a particular maximum voltage deviation  $\Delta V_4$ . The value for  $\Delta V_4$  is obtained from

preliminary voltage deviation budgeting. Namely, the peak transient voltage drop specified in Table 2.1 is 150mV. This is the total voltage deviation budget for intervals  $I_2$ and  $I_3$ . As a starting point, let us allot 50mV to  $I_2$  and 100mV to  $I_3$ . Therefore,  $\Delta V_4$ =50mV can be substituted into (3.3) along with  $I_o$ =10A,  $V_{in}$ =5V, and  $V_o$ =3V.

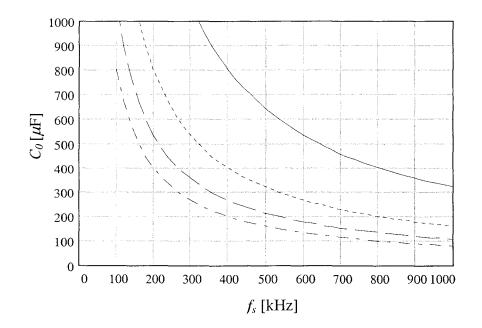

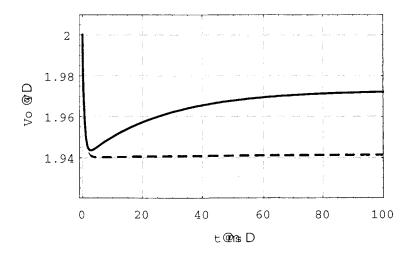

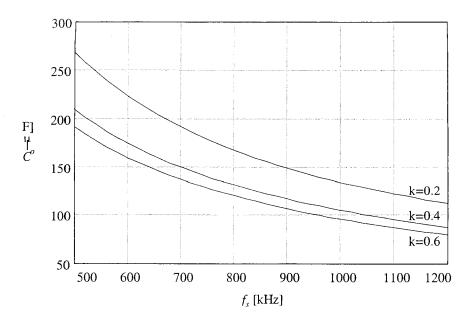

Using (3.3) the amount of output capacitance required to achieve  $\Delta V_4$ =50mV for a load current step of 10A is plotted as a function of the switching frequency in Fig. 3.4. Fig. 3.4 shows that at a switching frequency of 500kHz, more than 160µF of capacitance is needed to achieve a voltage drop of less than 50mV during I<sub>2</sub>.

Figure 3.4: Output capacitance required to achieve a maximum voltage drop of 50mV during the interval  $I_2$  as a function of the switching frequency

The question now becomes how to implement  $160\mu$ F of output capacitance. It would be desirable if only low profile ceramic capacitors in a 1206 package could be used. However, low profile ceramic capacitors in a 1206 package with an X7R dielectric are currently only available with a maximum value of 4.7 $\mu$ F. Placing 35 of these capacitors on the board might not be acceptable from the required board area and the cost standpoints.

Another possibility to implement the 160 $\mu$ F output capacitance would be to sacrifice the low board profile that could be achieved with ceramic chip capacitors and use either expensive tantalum capacitors or less expensive electrolytic capacitors. In order to keep the board cost in check, one might opt to use 100 $\mu$ F OSCON electrolytic capacitors (10SA100M). Two of these capacitors will provide 25% more capacitance than it is needed to make  $\Delta V_4$ =50mV. However, the *ESR* of these capacitors is 30m $\Omega$  and the *ESL* is about 13nH. Substituting these numbers back into (3.1) yields a drop of approximately 378mV during I<sub>1</sub>! Thus, in order to now bring  $\Delta V_{o1}$  within specs, we would need to use five 10SA100M OSCON capacitors in parallel instead of two that would have been more than enough to meet the 50mV maximum deviation during I<sub>2</sub>.

The main disadvantage of using electrolytic capacitors is the significant increase in board height and volume. For example, if only ceramic chip capacitors are used, the component height is only 60 mills. If, on the other hand, electrolytic capacitors are chosen, component height increases significantly. In fact, if 10SA100M OSCON capacitors used in the previous example are chosen, the component height increases to 413 mills. Thus, if the transient response specs can cost effectively be met without electrolytic capacitors at the output, the volume of the module could be reduced 6.8 times! The tremendous height and volume reduction is obviously a huge incentive to avoid placing electrolytic capacitors on the board.

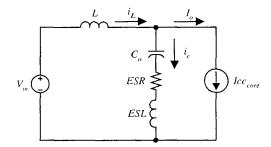

#### 3.1.3 Interval I<sub>3</sub>

At  $t=t_2$ ,  $S_1$  is turned on by the control circuit, and the converter starts to respond to the disturbance. For simplicity, we will assume that once the controller turns  $S_1$  on, it will remain on until the average inductor current becomes equal to the load current. In this case, the circuit of Fig. 3.1 can be modeled as shown in Fig. 3.5. From the model, we can write an expression for the output voltage for  $t>t_2$ :

$$V_o(t) = i_c \cdot ESR + \frac{1}{C_o} \cdot \int_0^t i_c \cdot dt$$

(3.4)

where  $i_c$  is the capacitor current. Applying Kirchoff's current law we get:

$$i_c = i_L - I_o \tag{3.5}$$

Figure 3.5: Simplified model of the converter output during the interval I<sub>3</sub>

From Fig. 3.5, the inductor current can be expressed as:

$$i_L = \frac{V_{in} - V_o}{L} \cdot t = S \cdot t \tag{3.6}$$

where S is the slope of the inductor current. After substituting (3.5) and (3.6) into (3.4) and evaluating the integral we get:

$$V_o = (S \cdot t - I_o) \cdot ESR + \frac{S \cdot t^2}{2 \cdot C_o} - \frac{I_o \cdot t}{C_o}$$

(3.7)

Equation (3.7) can now be used to calculate the peak output voltage deviation during the interval  $I_3$ . The time when the output voltage reaches its minimum value can be calculated by taking the derivative of (3.7) and setting it to zero. Solving for *t* yields:

$$t_m = \frac{I_o}{S} - C_o \cdot ESR \tag{3.8}$$

In some cases,  $t_m$  might turn out to be negative indicating that the voltage drop across the *ESR* is dominant. In such cases a value of zero should be used for t in (3.7). Otherwise (3.8) can be substituted into (3.7) to calculate the peak output voltage deviation during the interval  $I_3$ :

$$\Delta V_5 = \frac{I_o^2}{2 \cdot C_o \cdot S} + \frac{1}{2} \cdot S \cdot C_o \cdot ESR^2 = \Delta V_5 + \Delta V_5^{"}$$

(3.9)

From (3.9),  $\Delta V_5$  can be expressed as:

$$\Delta V_{5} = \left(\frac{I_{o}}{S}\right)^{2} \cdot \frac{S}{2C_{o}}$$

(3.10)

Similarly,  $\Delta V_5^{''}$  can be written as:

$$\Delta V_5^{"} = \left( ESR \cdot C_o \right)^2 \cdot \frac{S}{2C_o}$$

(3.11)

Keeping in mind that (3.9) holds if  $t_m > 0$  from (3.8) we get:

$$\frac{I_o}{S} > ESR \cdot C_o \tag{3.12}$$

From (3.10), (3.11), and (3.12) it is clear that (3.9) holds *iff*:

$$\Delta V_5 > \Delta V_5 \tag{3.13}$$

From (3.9) we can calculate how much output capacitance will be needed to insure that  $\Delta V_5$  does not exceed the chosen maximum value at the selected switching frequency.

Substituting  $S = \frac{V_{in} - V_o}{L}$  into (3.9) yields:

$$\Delta V_{5} = \frac{L \cdot I_{o}^{2}}{2 \cdot C_{o} \cdot (V_{in} - V_{o})} + \frac{1}{2} \cdot \frac{(V_{in} - V_{o})}{L} \cdot C_{o} \cdot ESR^{2} = \Delta V_{5}^{'} + \Delta V_{5}^{''}$$

(3.14)

Equation (3.14) gives the peak voltage deviation during  $I_3$ . This result is a bit counter intuitive. Namely, one would expect  $\Delta V_5$  to be proportional to the size of the inductor and inversely proportional to the size of the output capacitor. This dependence is, indeed, present in the first term in (3.14). However, the second term is actually, unexpectedly, proportional to the size of the output capacitor and inversely proportional to the size of the inductor. This would tend to indicate that at one point the second term in  $\Delta V_5$  could become dominant and  $\Delta V_5$  would start to increase as the value of the output capacitor is increased. However, this cannot happen because of the condition given by (3.13). Thus, despite the second term in (3.14),  $\Delta V_5$  can be minimized by increasing output capacitance or decreasing the size of the inductor.

The size of the inductor is closely related to the switching frequency. Since

$$\Delta I_L = \frac{V_{in} - V_o}{L} \cdot D \cdot T_s \tag{3.15}$$

we get:

$$L = \frac{V_{in} - V_o}{\Delta I_L} \cdot D \cdot T_s \tag{3.16}$$

where  $\Delta I_L$  is the peak to peak inductor current ripple, *D* is the duty cycle of the main switch (*S*<sub>1</sub>), and *T*<sub>s</sub> is the switching period. Substituting (3.16) into (3.14) and rearranging, we get:

$$\Delta V_{5} = \frac{\frac{V_{o}}{V_{in}} \cdot I_{o}^{2}}{2 \cdot C_{o} \cdot \Delta I_{L} \cdot f_{s}} + \frac{1}{2} \cdot \frac{\Delta I_{L}}{\frac{V_{o}}{V_{in}}} \cdot f_{s} \cdot C_{o} \cdot ESR^{2}$$

(3.17)

Assuming further that

$$\Delta I_L = k \cdot I_o \tag{3.18}$$

where k would typically have a value between 0.1 and 0.4 (for an inductor current ripple of 10% to 40% of the maximum load current), (3.17) becomes:

$$\Delta V_{5} = \frac{\frac{V_{o}}{V_{in}} \cdot I_{o}}{2 \cdot C_{o} \cdot k \cdot f_{s}} + \frac{1}{2} \cdot \frac{k \cdot I_{o}}{\frac{V_{o}}{V_{in}}} \cdot f_{s} \cdot C_{o} \cdot ESR^{2}$$

(3.19)

Equation (3.19) gives an expression for  $\Delta V_5$  as a function of the switching frequency and the output capacitance. In order for (3.19) to be valid, inequality (3.12) still has to be satisfied. Given the form of (3.19), it is more convenient to rewrite (3.12) in the following way:

$$f_s \cdot C_o < \frac{1}{ESR \cdot \frac{V_o}{V_{in}} \cdot k}$$

(3.20)

From (3.19) the amount of output capacitance required to achieve a prescribed maximum drop during  $I_3$  can be expressed as a function of the switching frequency with the inductor current ripple as a parameter. So, choosing the maximum allowable deviation for  $\Delta V_5$  and solving for  $C_o$ , we get:

$$C_o = \frac{\Delta V_5 - \sqrt{\Delta V_5^2 - I_o^2 \cdot ESR^2}}{I_o \cdot k \cdot f_s \cdot ESR^2} \cdot \frac{V_{in}}{V_o}$$

(3.21)

Equation (3.21) is, of course, valid if:

$$C_o < \frac{1}{ESR \cdot \frac{V_o}{V_{in}} \cdot k \cdot f_s}$$

(3.22)

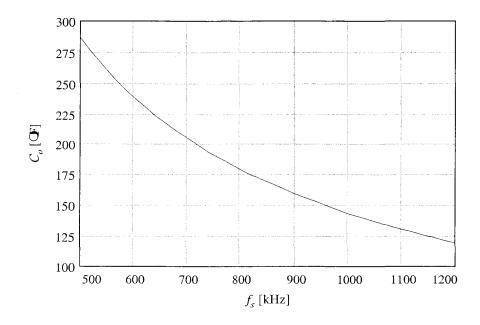

Equation (3.21) was used to create Fig. 3.6 which shows the output capacitance required to achieve  $\Delta V_5$ =100mV as a function of the switching frequency with the inductor current ripple as a parameter.

Fig. 3.6 shows that at 500kHz achieving 100mV of voltage drop during  $I_3$  requires between 150µF and 650µF of output capacitance, depending on the size of the buck inductor. Recalling for the moment that because of intervals  $I_1$  and  $I_2$  we already have 500µF on the board, we could safely choose a k of 0.2 at  $f_s$ =500kHz.

Figure 3.6: Output capacitance required to achieve  $\Delta V_5=100mV$  for four different inductor current ripple magnitudes (k=0.1 to 0.4)

#### 3.1.4 Interval I<sub>4</sub>

During  $I_4$  the duty cycle is no longer saturated, and the converter resumes its normal switching pattern. The integral action of the control loop returns the output voltage to its nominal set-point. Since we are currently interested solely in the peak output voltage deviation during a load current transient, circuit behavior during this interval will be discussed in Chapter 7.

# 3.2 Optimizing Voltage Budgeting

In Section 3.1.2 a preliminary voltage budget was made for the transient response. Under that voltage budget, out of the 150mV of available deviation, 50mV was allotted to the interval  $I_3$ , leaving 100mV for the interval  $I_4$ . However, the real concern is the total voltage deviation after a transient. In other words, how the voltage drop is distributed between the response intervals is not as critical, as long as the specs are met with the least amount of output capacitance.

In order to optimize the voltage budgeting, the voltage drops during  $I_2$  and  $I_3$  need to be taken into account concurrently. Combining (3.2) and (3.19) we get:

$$\frac{I_o}{f_s \cdot C_o} \cdot \left(1 - \frac{V_o}{V_{in}}\right) + \frac{\frac{V_o}{V_{in}} \cdot I_o}{2 \cdot C_o \cdot k \cdot f_s} + \frac{1}{2} \cdot \frac{k \cdot I_o}{\frac{V_o}{V_{in}}} \cdot f_s \cdot C_o \cdot ESR^2 = \Delta V_4 + \Delta V_5$$

(3.23)

Solving for  $C_o$  as a function of the maximum voltage deviation  $\Delta V_4 + \Delta V_5$  and the switching frequency yields:

$$C_{o} = \frac{\Delta V_{4} + \Delta V_{5} - \sqrt{\left(\Delta V_{4} + \Delta V_{5}\right)^{2} - I_{o}^{2} \cdot ESR^{2} \cdot \left(1 + 2 \cdot k\right) + 2 \cdot I_{o} \cdot k \cdot ESR^{2} \cdot \frac{V_{in}}{V_{o}}}{I_{o} \cdot k \cdot f_{s} \cdot ESR^{2}} \cdot \frac{V_{in}}{V_{o}} \cdot \frac{V_{in}}{V_{o}} (3.24)$$

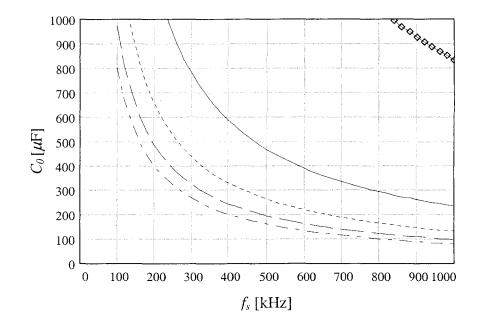

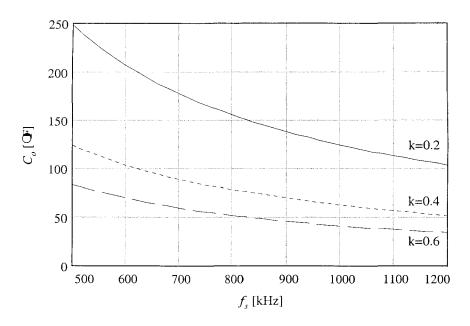

A plot of the output capacitance needed to achieve a combined voltage drop of 150 mV during the intervals I<sub>2</sub> and I<sub>3</sub> is shown in Fig. 3.7 as a function of the switching frequency with the inductor current ripple as a parameter.

Fig. 3.7 shows that with better voltage budgeting during the intervals  $I_2$  and  $I_3$ , the total output capacitance can be significantly reduced. In fact, at  $f_3$ =500kHz, less than 300µF would be enough to keep the output voltage within specs with k=0.2. However,

Figure 3.7: Output capacitance required to achieve  $\Delta V_4 + \Delta V_5 = 150 \text{mV}$  for four different inductor current ripple magnitudes (k=0.1 to 0.4)

the output capacitance cannot be reduced below 500 $\mu$ F because of the *ESR* and the *ESL* of the chosen capacitors. The overkill in capacitance required to make the *ESR* and the *ESL* sufficiently small to meet specs during I<sub>1</sub> can be used to lower the switching frequency and still meet transient specs during I<sub>2</sub> and I<sub>3</sub>. Fig. 3.7 shows that with k=0.2, the switching frequency can be lowered to 300kHz without jeopardizing transient

performance. This reduction in the switching frequency would increase the overall efficiency of the circuit. Hence, the size penalty resulting from the *ESR* and the *ESL* of the chosen capacitors is somewhat compensated by the overall efficiency improvement.

## **3.3** Approaching the VRM Design Problem

Equations (3.1), (3.2), and (3.19) describe the peak output voltage drops during the three intervals of the buck converter transient response. These three equations are reproduced here for convenience.

$$\Delta V_{o1} = \Delta V_1 + \Delta V_2 = ESL \frac{dI_o}{dt} + ESR \cdot \Delta I_o + \frac{1}{2} \frac{\Delta I_o^2}{C_o \frac{dI_o}{dt}}$$

(3.25)

$$\Delta V_4 = \frac{I_o}{C_o} \cdot D' \cdot T_s = \frac{I_o}{f_s \cdot C_o} \cdot \left(1 - \frac{V_o}{V_{in}}\right)$$

(3.26)

$$\Delta V_5 = \frac{\frac{V_o}{V_{in}} \cdot I_o}{2 \cdot C_o \cdot k \cdot f_s} + \frac{1}{2} \cdot \frac{k \cdot I_o}{\frac{V_o}{V_{in}}} \cdot f_s \cdot C_o \cdot ESR^2$$

(3.3)

Obviously, minimizing all three voltage drops yields the best overall transient response. However, the question is how to get the best overall transient response in the smallest volume, with the lowest cost, and with the highest overall efficiency.

From (3.25) it is clear that  $\Delta V_{ol}$  depends only on the *ESR* and the *ESL* of the output capacitors, and is unaffected by any other circuit parameters like the switching frequency or the control loop bandwidth. Thus, the only way to reduce  $\Delta V_{ol}$  is to choose high quality capacitors and place a number of them in parallel. Here again the issue of electrolytic capacitors versus ceramic chip capacitors arises. If ceramic chip capacitors are used,  $\Delta V_{ol}$  will be very small because there will be a large number of low *ESR* and

low *ESL* capacitors at the output. However, meeting transient specs during  $I_1$  may not insure adequate performance during  $I_2$  and  $I_3$  as well. As a result, the number and type of capacitors that will need to be placed at the output will also depend on what happens during the intervals  $I_2$  and  $I_3$ . On the other hand, if electrolytic capacitors are to be used, because of their rather high *ESR* and *ESL* a number of them will have to be placed in parallel in order to maintain  $\Delta V_{ol}$  small. In this case, the *ESR* and the *ESL* determine how many capacitors will have to be used. Typically, however, the amount of output capacitance dictated by  $\Delta V_{ol}$  will far exceed the capacitance requirements imposed by the intervals  $I_2$  and  $I_3$ .

The peak voltage drop during the intervals  $I_2$  and  $I_3$  is given by equations (3.26) and (3.27), respectively. These equations show that good transient response requires either a large output capacitor or a high switching frequency. The optimal solution finds the right balance between VRM size (dictated by the number and the size of the output capacitors) and efficiency (dictated by the switching frequency). For example, from Fig. 3.7 we can see that the total output voltage drop of 150mV during  $I_2$  and  $I_3$  can be achieved with 270µF of output capacitance at a switching frequency of 500kHz. However, meeting the 150mV specification with 270µF of capacitance requires  $k \ge 0.2$  (see Fig. 3.7).

It should by now be clear that there are two design paths that can be taken. One possibility is to keep the switching frequency low and rely on the output capacitors to keep the output voltage within specs. There are several problems with this approach. First, bulky electrolytic capacitors required at the output dramatically increase the volume of the module and prevent its use in laptop applications. For now, however, such solutions are still finding their place in the desktop market (where the space is not as

limited) due their low cost. Second, this approach suffers from the lack of scalability. Namely, the trend in the processor industry has been to demand higher core currents with higher slew rates to be provided by the VRM for every new generation of processors. As a result, relying extensively on the output capacitors to do all the work will quickly become a totally unacceptable solution even in the desktop market because of size issues. Therefore, the low frequency, large output capacitor approach is at best a short-term solution and will not be considered here.

The other VRM design path is based on minimizing the role of the output capacitors in keeping the output voltage within specs. Instead, it is desirable to have a fast, high bandwidth control loop do the bulk of the work in keeping the output voltage within the prescribed limits after a fast load current transient. This is achieved by opting to operate the converter at a higher than usual switching frequency. The high frequency, low output capacitance approach advocated in the rest of this thesis produces a scalable, high power density, low volume solution that will be able to efficiently meet future processor power demands.

# **3.3.1** Merits of the High Switching Frequency

The obvious benefit of a higher switching frequency is the reduction of the physical size of the buck inductor. A smaller inductor helps to reduce the size of the converter. In addition, having a smaller inductor allows the inductor current to be changed faster. This allows the circuit to reach a new steady state sooner. Consequently, transient specs can be met with less output capacitance, which further reduces size of the converter.

Another benefit of high frequency operation is that it shortens the maximum response delay time (interval  $I_2$ ). Consequently, a high switching frequency results in a smaller

peak voltage drop during  $I_2$ . Again, this helps in reducing the size of the output capacitor, and thus, the size of the whole module.

Operating at a high switching frequency makes it possible for the feedback loop to have a high bandwidth. The benefits of a high bandwidth control loop and a small inductor, both results of operating at a high switching frequency, are felt during the interval  $I_3$  where both help to minimize  $\Delta V_5$  (see (3.14) and (3.27)).

In short, a higher switching frequency allows the designer to reduce the size of both the buck inductor and the output capacitors and increase the bandwidth of the control loop. As a result, the overall size of the VRM is significantly reduced. On the down side, however, operating at a high switching frequency will lower the efficiency of the converter and require advanced packaging techniques.

### **3.4 VRM Design Philosophy**

Based on the discussion in this chapter, a new VRM design philosophy will be adopted here. The central idea is to make the module as small and compact as possible. Thus, we want to minimize the board area and achieve a low module profile by eliminating electrolytic capacitors (or any other through-hole parts) from the design. In addition, the goal is to keep the cost of the module as low as possible.

In light of the outlined goals, the switching frequency will be pushed as high as the efficiency specs will allow in order to minimize the size of the module. In order to keep the cost at a minimum, a simple hard-switching buck topology with voltage mode control will be used. Every subsystem will be optimized for maximum performance at high frequency. Alternate topologies and more complicated control schemes will not be used unless the specs absolutely cannot be met with the simplest topology and control method.

Clearly, VRM design philosophy is to push simple topologies and algorithms to their technological limit. Therefore, the chosen buck topology and the chosen voltage mode control algorithm have to be carefully analyzed in order to identify efficiency bottlenecks and find a way to squeeze every bit of efficiency out of the circuit. In order to do this, the losses in the buck topology are carefully analyzed in Chapter 4 as a function of the load current and the switching frequency. Loss equations derived in Chapter 4 are used in Chapter 5 to choose the right topology for VRM boards operating from a 5V input. The conclusions drawn in Chapter 5 are then used in Chapter 6 to optimize the operation and efficiency of a synchronous buck topology designed to operate from a 12V input. The optimization of the transient response of a voltage mode controlled buck converter is undertaken in Chapter 7.

# **Chapter 4**

# **Overview of Loss Mechanisms in the Buck Topology in Continuous Conduction Mode**

In line with the adopted VRM design philosophy, it is important to accurately predict all the losses in the buck topology as a function of the switching frequency and the load current. An accurate loss analysis can be used to optimize the VRM module.

The accuracy of loss calculations will depend on the ability to identify all loss mechanisms in the circuit and model them correctly. Because of high frequency operation, this task needs to be approached with great care so that no high frequency parasitics get overlooked.

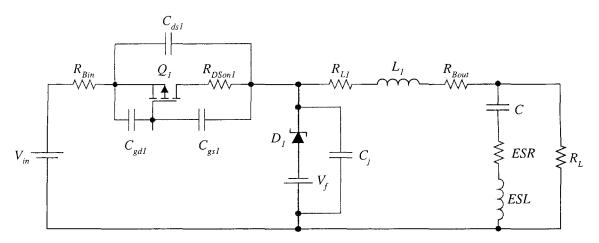

# 4.1 Overview of Various Loss Mechanisms in the Regular Buck Topology

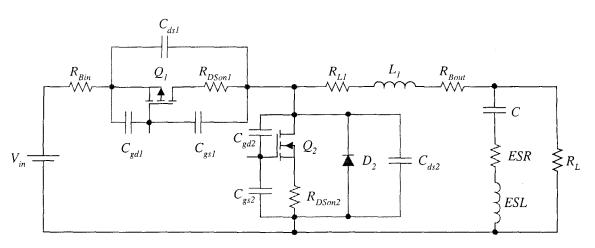

The regular buck topology including loss-causing parasitics is shown in Fig. 4.1. As shown in Fig. 4.1, the following loss mechanisms can be identified in the regular buck topology:

- Main Switch  $(Q_I)$

- Conduction Loss

- Switching Loss

- Drain to Source Capacitance Loss

Figure 4.1: Regular buck converter including parasitics

- Gate Drive Loss

- Schottky Diode  $(D_1)$

- Conduction Loss

- Reverse Bias Leakage Loss

- Junction Capacitance Loss

- Inductor

- Copper Loss

- Core Loss

- Resistive Losses on the Circuit Board

- Input Trace

- Output Trace

- Other Traces

#### **4.1.1** Losses in the main switch $(S_1)$

As it was pointed out, the main switch will suffer from conduction loss, switching loss, drain-to-source capacitance loss, and gate drive loss. Conduction loss in the main switch,  $P_{cl}$ , can be expressed as:

$$P_{c1} = \frac{R_{DSon1}(T)}{N_{m1}} \cdot I_{Lrms}^2 \cdot D$$

$$(4.1)$$

where  $R_{DSon1}$  is the drain to source on resistance of the main switch,  $N_{m1}$  is the number of MOSFETs used in parallel,  $I_{Lrms}$  is the inductor rms current, and D is the duty cycle. The inductor *rms* current can be calculated using the following formula:

$$I_{Lrms} = \sqrt{I_o^2 + \frac{(\Delta I_L)^2}{12}}$$

(4.2)

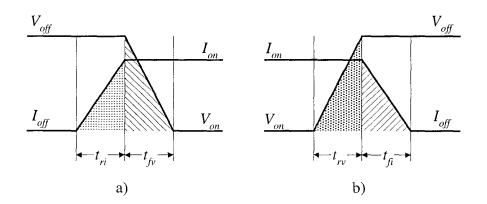

The switching loss, sometimes called the overlap loss, is caused by the nonideality of the MOSFET. If there are no soft-switching techniques being applied, which is the assumption here, the MOSFET will, both turn-on and turn-off, briefly conduct the full on-current while the voltage across the drain and source terminals is still the full offvoltage of the switch (see Fig. 4.2). This produces significant switching (overlap) losses whenever the MOSFET turns on or off, especially at high switching frequencies.

Figure 4.2: Switch voltage and current waveforms at a) turn-on, b) turn-off

From Fig. 4.2 we can derive expressions for the turn-on switching loss,  $P_{son1}$ , and turn-off switching,  $P_{soff1}$ . The turn-on switching loss is given by:

$$P_{son1} = \frac{1}{2} \cdot V_{in} \cdot \left( I_{out} - \frac{\Delta I_{out}}{2} \right) \cdot \left( t_{fv1} + t_{ri1} \right) \cdot f_s$$

(4.3)

while the turn-off switching loss is given by:

$$P_{soff1} = \frac{1}{2} \cdot V_{in} \cdot \left( I_{out} + \frac{\Delta I_{out}}{2} \right) \cdot \left( t_{rv1} + t_{fi1} \right) \cdot f_s$$

(4.4)

where  $f_s$  is the switching frequency,  $\Delta I_{out}$  is the inductor current ripple,  $t_{rvI}$  and  $t_{fvI}$  are the switch voltage rise and fall times, respectively, and  $t_{riI}$  and  $t_{fiI}$  and the switch current rise and fall times, respectively. The total switching loss, Ps1, is then:

$$P_{s1} = P_{soff1} + P_{son1} \tag{4.5}$$

Each time the MOSFET switch is turned on, the voltage across the drain and source terminals drops from  $V_{off}$  to  $V_{on}$  (see Fig. 4.2). Thus, the drain-to-source capacitance of the MOSFET is discharged in a lossy manner through its  $R_{DSon}$ . This lossy discharge of the drain-to-source capacitance has been termed drain-to-source capacitance loss,  $P_{DScl}$ , and can be approximated using the following formula:

$$P_{DSc1} = \frac{1}{2} \cdot C_{DS1} \cdot V_{in}^2 \cdot f_s \cdot N_{m1}$$

(4.6)

where  $C_{DSI}$  is the drain-to-source capacitance of the main switch.

The gate drive loss is caused by the charging and discharging of  $C_{GS1}$  and  $C_{GD1}$  (see Fig. 4.1) each time the MOSFET is turned on or off. While the gate drive loss can be calculated using  $C_{GS1}$  and  $C_{GD1}$ , it is much easier to use the total gate charge needed to turn the FET on provided in the manufacturer's data sheet. In this case the gate drive loss can be expressed as:

$$P_{G1} = V_{GS1} \cdot Q_{G1} \cdot f_s \cdot N_{m1}$$

(4.7)

where  $V_{GSI}$  is the applied gate-to-source voltage, and  $Q_{GI}$  is the total gate charge that needs to be supplied by the gate driver in order to make the gate-to-source voltage equal to  $V_{GSI}$ .

The total loss in the main switch of the regular buck topology can be expressed as:

$$P_{Q1} = P_{c1} + P_{s1} + P_{DSc1} + P_{G1}$$

(4.8)

The expression for each of these loss components is given by (4.1) through (4.7).

#### 4.1.2 Loss Mechanisms in the Schottky Diode

The chief loss mechanisms in the Schottky are the conduction loss, the loss due to the reverse bias leakage current, and the loss due to the charging and discharging of the junction capacitance. The conduction loss is given by:

$$P_{cdr} = V_{fr}(T) \cdot I_{out} \cdot D' \tag{4.9}$$

where  $V_{fr}$  is the forward voltage drop on the Schottky diode. The loss due to the reverse bias leakage current is:

$$P_{ldr} = V_{in} \cdot I_{sr}(T) \cdot D \cdot N_d \tag{4.10}$$

where  $I_{sr}$  is the reverse bias leakage current of the Schottky, and  $N_d$  is the number of diodes used in parallel. The loss due to the junction capacitance can be expressed as:

$$P_{Cj} = \frac{1}{2} \cdot C_j \cdot V_{in}^2 \cdot f_s \tag{4.11}$$

where  $C_j$  is the Schottky diode junction capacitance. The total loss in the Schottky diode is now:

$$P_{Sd} = P_{cdr} + P_{ldr} + P_{Cj}$$

(4.12)

# 4.2 Overview of the Losses in the Synchronous Buck Topology

The synchronous buck topology including loss-causing parasities is shown in Fig. 4.3.

Figure 4.3: Synchronous buck topology including parasitics

As shown in Fig. 4.3, the following loss mechanisms can be identified in the synchronous buck topology:

- Main Switch  $(Q_I)$

- Conduction Loss

- Switching Loss

- Drain to Source Capacitance Loss

- Gate Drive Loss

- Synchronous Rectifier  $(Q_2)$

- Conduction Loss

- Switching Loss

- Body Diode Loss

- Conduction Loss

- Reverse Recovery Loss

- Gate Drive Loss

- Inductor

- Copper Loss

- Core Loss

- Resistive Losses on the Circuit Board

- Input Trace

- Output Trace

- Other Traces

#### 4.2.1 Loss Mechanisms in the Main Switch

The losses in the main switch can, in the first approximation, be assumed to be identical to those in the main switch of the regular buck. Thus, (4.1) through (4.8) can readily be applied, and will not be repeated here. Certain fine points concerning the difference in losses in the main switch of the regular and the synchronous buck will be discussed in more detail in later sections.

#### 4.2.2 Loss Mechanisms in a Synchronous Switch

In order to accurately evaluate the losses in the synchronous rectifier as a function of frequency, we must take into account conduction loss, switching loss, gate drive loss, body diode conduction (dead time) loss, and the body diode reverse recovery loss. Conduction loss is given by:

$$P_{c2} = \frac{R_{DSon2}(T)}{N_{m2}} \cdot I_{Lrms}^2 \cdot D'$$

(4.13)

where  $R_{DSon2}$  is the drain to source on resistance of the synchronous switch, and  $N_{m2}$  is the number of MOSFETs used in parallel. The switching loss consists of the switching loss at  $Q_2$  turn on:

$$P_{son2} = \frac{1}{2} \cdot V_{f} \cdot \left( I_{out} + \frac{\Delta I_{out}}{2} \right) \cdot \left( t_{fv2} + t_{ri2} \right) \cdot f_{s}$$

(4.14)

and at  $Q_2$  turn off:

$$P_{soff 2} = \frac{1}{2} \cdot V_f \cdot \left( I_{out} - \frac{\Delta I_{out}}{2} \right) \cdot \left( t_{rv2} + t_{fi2} \right) \cdot f_s$$

(4.15)

where  $V_f$  is the forward voltage drop of the body diode,  $f_s$  is the switching frequency,  $\Delta I_{out}$  is the inductor current ripple,  $t_{rv2}$  and  $t_{fv2}$  are the switch voltage rise and fall times, respectively, and  $t_{ri2}$  and  $t_{fi2}$  and the switch current rise and fall times, respectively. Hence, the total switching loss is given by:

$$P_{s2} = P_{son2} + P_{soff2} \tag{4.16}$$

The gate drive loss can be estimated from the following equation:

$$P_{G2} = V_{GS2} \cdot Q_{G2} \cdot f_s \cdot N_{m2} \tag{4.17}$$

where  $V_{GS2}$  is the drive voltage, and  $Q_{G2}$  is the total gate charge that needs to be supplied in order to turn the synchronous FET on. Next, we need to consider the losses associated with the body diode. Namely, the body diode will conduct during the dead time between the turn off of one MOSFET and the turn on of the other. The loss before  $Q_1$  turns on is given by:

$$P_{cbd1} = V_f \cdot \left( I_{out} - \frac{\Delta I_{out}}{2} \right) \cdot \frac{t_{d1}}{T_s}$$

(4.18)

while the loss before  $Q_2$  turn on is given by:

$$P_{cbd2} = V_f \cdot \left( I_{out} + \frac{\Delta I_{out}}{2} \right) \cdot \frac{t_{d2}}{T_s}$$

(4.19)

where  $t_{d1}$  and  $t_{d2}$  are the dead time intervals before  $Q_1$  and  $Q_2$  turn on, respectively, and  $T_s$  is the switching period. Finally, the loss due to the reverse recovery of the body diode is:

$$P_{rr} = \frac{1}{2} \cdot I_{rr\max} \cdot t_b \cdot V_{in} \cdot f_s \tag{4.20}$$

where  $I_{rrmax}$  is the peak reverse recovery current, and  $t_b$  is the reverse recovery time. Hence, the total loss in the synchronous rectifier is obtained by summing all the losses characterized above.

$$P_{Q2} = P_{c2} + P_{s2} + P_{G2} + P_{cbd} + P_{rr}$$

(4.21)

# Chapter 5

# Synchronous Rectifiers Vs. Schottky Diodes in a Buck Topology for VRM Applications

## **5.1 Efficiency Considerations**

The reasons for operating a VRM DC-DC converter at a high switching frequency were thoroughly explained in previous sections. However, since most losses in a switching power supply are directly proportional to the switching frequency, increasing the switching frequency results in a lower overall module efficiency. But, by now it is clear that some efficiency will have to be sacrificed in order to meet the transient response requirements in the smallest volume.

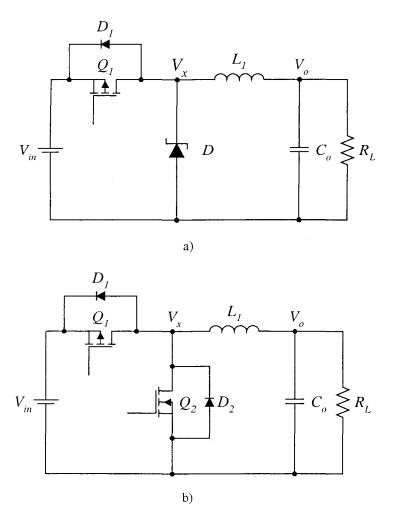

The regular and the synchronous buck topologies, shown in Figs. 5.1(a) and 5.1(b), respectively, are identical in every respect except in the implementation of the slave switch. A low voltage regular buck uses a Schottky diode (D) as a slave switch. In a synchronous buck, the Schottky diode is replaced by an active switch, a low on-resistance ( $R_{Dson}$ ) MOSFET, commonly referred to as a synchronous rectifier (SR).