# FLEXIBLE NEURAL IMPLANTS

Thesis by

Ray Kui-Jui Huang

In Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy

# CALIFORNIA INSTITUTE OF TECHNOLOGY

Pasadena, California

2011

(Defended June 25, 2010)

© 2011

Ray Kui-Jui Huang

All Rights Reserved

To My Family and Friends

#### **ACKNOWLEDGEMENTS**

This dissertation not only reflects the countless hours spinning photoresist, cleaning parylene machines, and mixing epoxy in Caltech Micromachining Laboratory, but it is also a conglomeration of years of wonderful experiences, opportunities, lessons, and valuable encounters during my PhD career. This endeavor would not be possible if it were not for my families, my friends, my mentors, my colleagues, and all those whom I have met over the past years.

Coming to Caltech was one of the best decisions I have made. The lab was not just a research lab to publish papers, it was also a place to nurture students to be ethical, logical engineers; it was a shelter to develop a fearless mind and become a hands-on researcher; and most important of all, it was a sanctuary to foster good thinkers who can solve any problem that they encounter. I have learned so much beyond what was written in books and papers, and I would not have been able to do so if I were not in this lab.

Dr. Tai, you have taught me so much; not just about how to be a good scientist, but you have guided me on acquiring a positive and forward-thinking attitude that has encouraged me and supported me through the toughest time. I want to express my sincerest gratitude and appreciation to you; thank you for the advice, the leadership, the support, and having faith in me. It was my honor to have you as my advisor.

To members of the Caltech Micromachining Laboratory, in particular Dr. Changlin Pang, Dr. Wen Li, Dr. Damien Rodger, Dr. Po-Jui Chen, Dr. Jason Shih, Dr. Siyang Zheng, Dr. Mike Liu, Dr. Nick Lo, and Dr. Quoc Quach; thank you for mentoring and training me the during the earlier years of my career in the lab. To the rest of the members, Dr. John Chen, Luca Giacchino, Jeffrey Chun-Hui Lin, Mandheerej Nandra, Justin Young-Hyun Kim, Bo Lu, Penvipha Satsanarukkit, Wendian Shi, Han-Chieh Chang, Yu Zhao, Charles Deboer, Zhao Liu and Dongyang Kang, thank you for your support, generous assistance and brilliant ideas. The lab would not have been this organized and efficient if it were not for the collaboration and hard work from each and every one of you. Thanks to the very helpful students Adi Gani, Suyao Ji and Siripat Sumanaphan for your hard work.

My thanks also go to Christine Garske, Agnes Tong and Tanya Owen, thank you for your help in purchasing and administrative tasks. You have made the life of all members in the lab so much easier and smoother. Thanks to Mr. Trevor Roper, without whom we would not have any device we have made to date.

I also want to give credit and my appreciation to Dr. James Weiland and Dr. Ellis Meng, and USC students including Artin Petrossians, Alice Cho, Lauren Hickey, Christian Gutierrez, Dr. Brian Li and Dr. Ronalee Lo, who have dedicated their time and effort in advancing the research program in both USC and Caltech and have helped me tremendously in my research endeavor in BMES ERC.

Special thanks go to all the friends that I have made and the old friends that I am so lucky to have kept in contact with during all these years. You have kept me company, brought me laughter, taught me lessons and made my life more exciting and fulfilling than I ever could have imagined. Special note to my Cornell buddies, Caltech ACT members and Sweet Pepper fans, you have been there for me through my highs and lows, thank you.

v

Last but not least, my biggest thanks are to my family; my beloved mother and brother who have always been there for me and have given me unconditional support over the years in every aspect of my life. Words cannot simply describe my sincerest gratitude and appreciation to them. Thank you.

Finally, Dad, this is to you. Thanks.

#### ABSTRACT

Despite recent development in integration technologies for biomedical implantable devices, current state-of-the-art prosthetic platforms still lack a reliable and convenient packaging scheme to integrate high-density signal-driving chips, wireless telemetry circuitries and noise-canceling amplifiers, mainly due to the limitations in fabrication technology, material compatibility and interconnect reliability. In this dissertation, new packaging technologies are developed and presented to enable a new generation of flexible neural implants. These technologies can also house integrated circuit chips and provide high-density electrical connection to it.

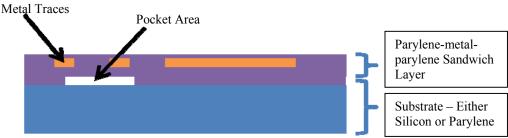

This packaging scheme utilizes the parylene-metal-parylene skin structure and can be totally integrated and be monolithically fabricated with existing functional devices. The size and the electrode patterns can be modified to suit different chips and applications. Integration with flexible cable integrated silicon probes for neural prosthesis, implantable muscle stimulators and implantable RFID tagging technology are all successfully demonstrated in this dissertation. Other discrete components can also be integrated to achieve high level functionality.

In order to ensure the long-term stability of such packaging scheme, accelerated hot saline soaking test is conducted on the overall structure and its components. Detailed adhesion enhancement techniques are also presented to improve its performances. A physical model of the flexible retinal implant is then tested *in vivo* during the course of the experiment. Finally, the high-density squeegee bonding technique is introduced, which allows the integration of a 256-channel chip. Functionality of the chip has been

demonstrated. As a result, this technology has the potential to achieve ultra high lead count connection and can facilitate future research in flexible implantable biodevices.

# TABLE OF CONTENTS

| Acknowledgements                                              | iv        |

|---------------------------------------------------------------|-----------|

| Abstract                                                      | vii       |

| Table of contents                                             | ix        |

| List of figures                                               | xii       |

| List of tables                                                | xxi       |

| Glossary                                                      | xxii      |

| 1 INTRODUCTION                                                | 1         |

| 1.1 PROSTHETIC APPLICATIONS—THE NEED AND DRIVING FORCE        | æ1        |

| 1.1.1 Retinal Prosthesis                                      | 1         |

| 1.1.2 Neural Prosthesis                                       |           |

| 1.2 INTEGRATION TECHNOLOGY                                    |           |

| 1.2.1 Traditional Chip Integration Technology                 |           |

| 1.2.2 State-of-the-Art Chip Integration Technologies with Bio | odevices6 |

| 1.3 PROBLEMS AND CHALLENGES                                   |           |

| 1.4 MEMS TECHNOLOGY                                           |           |

| 1.4.1 Bulk Micromachining                                     |           |

| 1.4.2 Surface Micromachining                                  |           |

| 1.4.3 Introduction to Parylene                                |           |

| 1.4.4 Parylene for MEMS and Biomedical Applications           |           |

| 1.5 PROSTHETIC INTERFACE TECHNOLOGY THRUST                    |           |

| 1.6 LAYOUT OF THE DISSERTATION                                |           |

| 1.7 SUMMARY                                                   |           |

| 2 PARYLENE POCKET TECHNOLOGY                                  |           |

| 2.1 INTRODUCTION                                              |           |

| 2.2 POCKET DESIGN—PARYLENE VS. SILICON SUBSTRATE              |           |

| 2.3 FABRICATION                                               |           |

| 2.3.1 First Generation                                        |           |

| 2.3.2 Second Generation—Silicon Substrate                     |           |

| 2.3.3 Second Generation—Parylene Substrate                    |           |

| 2.3.4 Variety of Pockets                                      |           |

| 2.3.4   | .1 For IC Chips                                    |          |

|---------|----------------------------------------------------|----------|

| 2.3.4   | .2 For Discrete Components                         |          |

| 2.3.4   | .3 For Double Side and Multiple Layer Components   |          |

| 2.4 INT | TEGRATION WITH SILICON PROBES                      |          |

| 2.4.1   | Design                                             | 47       |

| 2.4.2   | Fabrication                                        | 50       |

| 2.4.3   | Testing and Verification                           | 52       |

| 2.5 SU  | MMARY                                              | 55       |

| 3 IMPLA | ANTABLE CHIP INTEGRATION TECHNOLOGY                | 56       |

| 3.1 INT | RODUCTION                                          |          |

| 3.2 RF  | ID CHIP INTEGRATION                                | 57       |

| 3.2.1   | Design and Fabrication                             | 58       |

| 3.2.2   | Integration Demonstration                          | 60       |

| 3.2.3   | Functional System Testing                          | 62       |

| 3.3 BIO | ON CHIP INTEGRATION                                | 64       |

| 3.3.1   | Design and Fabrication                             | 65       |

| 3.3.2   | System Integration Demonstration                   | 66       |

| 3.3.3   | Functional System Testing                          | 68       |

| 3.4 Co  | NCLUSION                                           |          |

| 4 PACK  | AGING, ACCELERATED LIFETIME TESTING AND MOD        | ELING.71 |

| 4.1 INT | RODUCTION                                          | 71       |

| 4.2 PA  | RYLENE TO SILICON INTERFACIAL ADHESION ENHANCEMENT |          |

| 4.2.1   | Sample Preparation                                 |          |

| 4.2.2   | Experiments                                        |          |

| 4.2.2   | .1 Partial Film Peeling Test                       | 76       |

| 4.2.2   | .2 ASTM Standard Tape Peeling Test                 |          |

| 4.2.2   | .3 Accelerated Soaking Tests                       | 80       |

| 4.2.2   | .4 HF Soaking Tests                                |          |

| 4.2.2   | .5 Conclusion                                      |          |

| 4.3 AC  | CELERATED LIFETIME SOAKING TEST OF PROTECTED ICS   | 83       |

| 4.3.1   | Samples Preparation                                | 84       |

| 4.3.2   | Passive Soaking                                    | 85       |

| 4.3.3   | Diffusion of Electrolyte in Silicone               |          |

| 4.3.4   | Active Soaking                          |     |

|---------|-----------------------------------------|-----|

| 4.3.5   | Conductive Epoxy                        |     |

| 4.4 Me  | CHANICAL MODEL FOR IMPLANTATION STUDIES |     |

| 4.4.1   | First Version Mechanical Model          |     |

| 4.4.2   | Second Version Mechanical Model         |     |

| 4.4.3   | Discussion                              | 103 |

| 4.5 Co  | NCLUSION                                | 103 |

| 5 HIGH  | DENSITY CHIP INTEGRATION                |     |

| 5.1 INT | RODUCTION                               |     |

| 5.2 PA  | RYLENE POCKET ON SILICON SUBSTRATE      |     |

| 5.2.1   | Fabrication                             |     |

| 5.2.2   | Fabrication Challenges                  |     |

| 5.2.2   | 1 Lift-off Metal Patterning             |     |

| 5.2.2   | 2 Thick Photoresist for Plasma Etching  |     |

| 5.2.2   | 3 Parylene Cracking                     | 114 |

| 5.2.2   | 4 Metal Line over a Step                | 116 |

| 5.2.2   | 5 Pocket Size                           |     |

| 5.3 PA  | RYLENE POCKET ON PARYLENE SUBSTRATE     |     |

| 5.3.1   | High Density Integration                |     |

| 5.3.1   | 1 Alignment                             |     |

| 5.3.1   | 2 Squeegee Technique                    |     |

| 5.3.2   | Integration Issues                      |     |

| 5.3.2   | 1 Metal Pad on Edge                     |     |

| 5.3.3   | Repairs and Enhancements                |     |

| 5.3.3   | 1 Laser Fix (Short Circuit)             |     |

| 5.3.3   | 2 Conductive Epoxy Failures             |     |

| 5.4 FU  | NCTIONAL TESTING                        |     |

| 5.5 Co  | NCLUSION                                |     |

| 6 CONC  | LUSION                                  |     |

| BIBLIOG | RAPHY                                   |     |

# LIST OF FIGURES

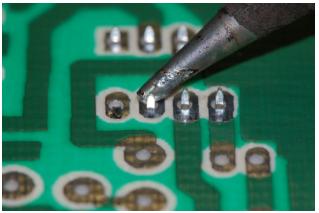

| Figure 1.1. Soldering a component onto the back of a printed circuit board                                                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

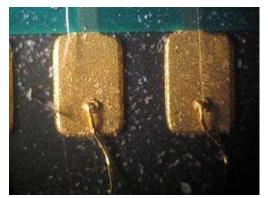

| Figure 1.2. Gold wire bonded onto metal pads to make electrical connections                                                                                      |

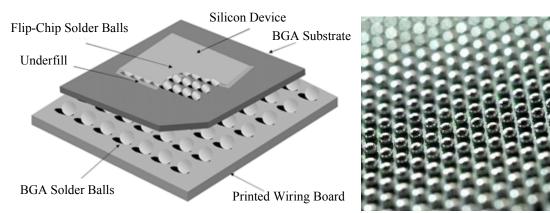

| Figure 1.3. Illustration of the ball grid array; the BGA on an actual IC chip                                                                                    |

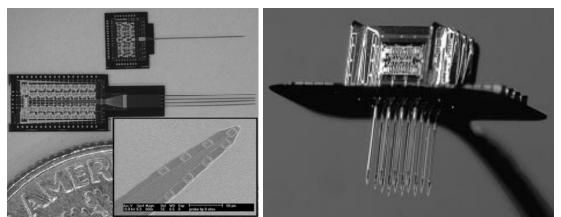

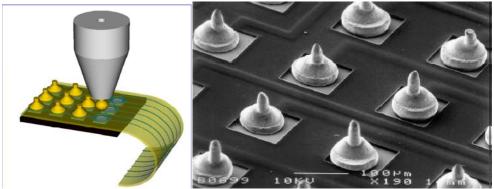

| Figure 1.4. The Michigan three-dimensional neural probe array [40]; SEM picture of the tip of the Michigan probe [33]                                            |

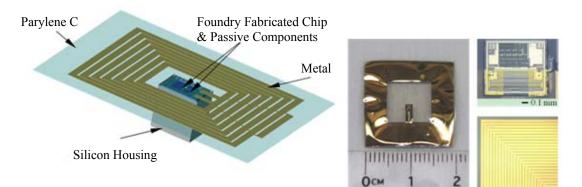

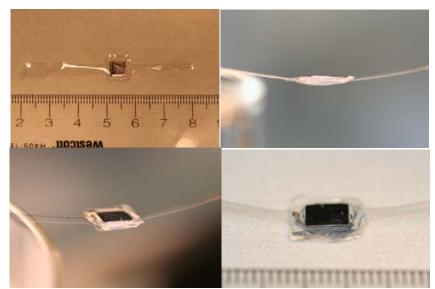

| Figure 1.5. Concept of embedded chip integration; overall view of the device; close-up view of the embedded chip; close-up view of the coil wires                |

| Figure 1.6. Close-up picture of the MicroFlex bonding technique, facilitated by a commercial wire bonding machine setup [70]                                     |

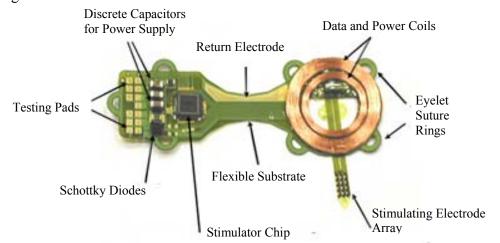

| Figure 1.7. Final implant with parylene C and silicone rubber encapsulation [71] 10                                                                              |

| Figure 1.8. Schematic representation of the retinal implant by Theogarajan et al. [73] 11                                                                        |

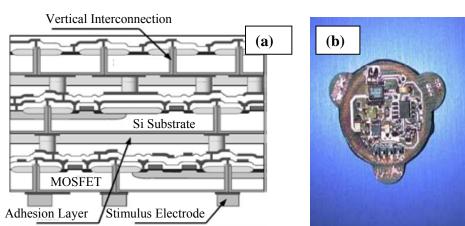

| Figure 1.9. (a) Schematic of the three-dimensional stacked chip [74]; (b) implantable sensor system: A control unit and analogue part with RF coil [75] 12       |

| Figure 1.10. Comparison of positive and negative photoresist                                                                                                     |

| Figure 1.11. Comparison of surface micromachining and bulk micromachining                                                                                        |

| Figure 1.12. Comparison of isotropic and anisotropic wet etching and dry etching 18                                                                              |

| Figure 1.13. Examples of silicon bulk micromachining; the substrate material is etched away to create different features [81]                                    |

| Figure 1.14. An example of surface micromachined gears [82]                                                                                                      |

| Figure 1.15. Chemical structures of parylene N, C, D, and HT, and some of the correlated process parameters used in parylene deposition system PDS 2010 and 2060 |

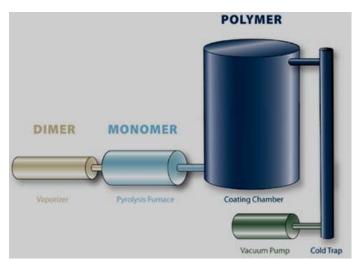

| Figure 1.16. Parylene deposition system and its deposition process                                                                                               |

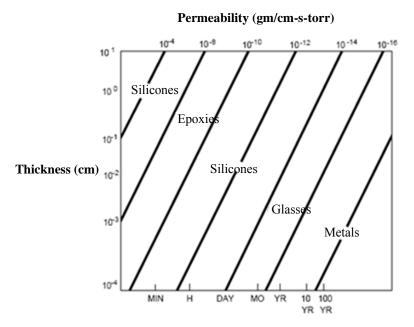

| Figure 1.17. Permeability vs. time of different materials                                                                                                        |

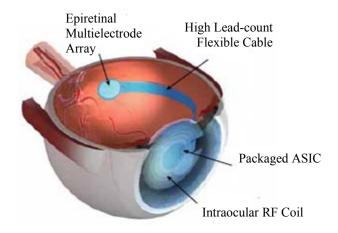

| Figure 1.18. Proposed all-intraocular system for high density epiretinal implant                                                                                 |

| Figure 2.1. Basic structure for parylene pockets                                                                                                                 |

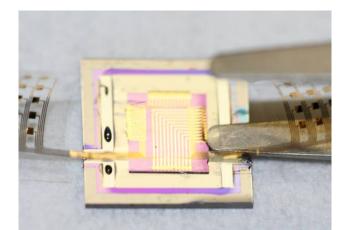

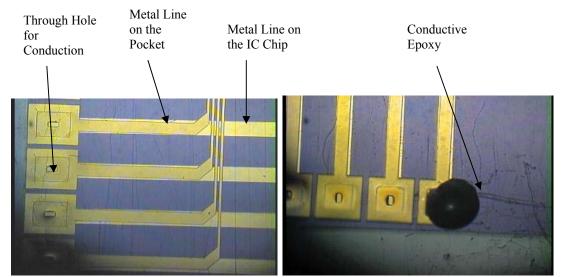

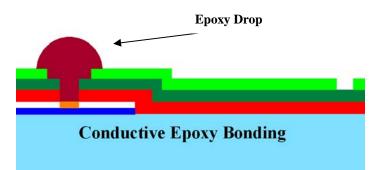

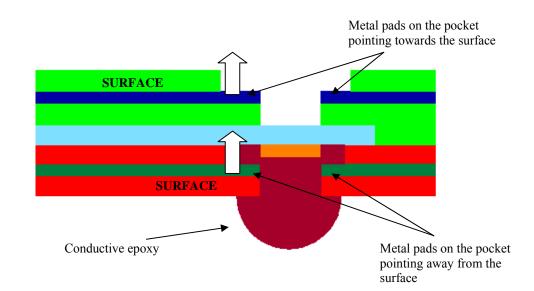

- Figure 2.8. Bonding scheme for the parylene pocket. A drop of conductive epoxy is applied on the bonding hole that exposes the metal pads on the IC chip underneath.36

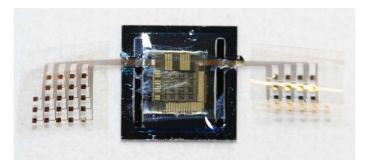

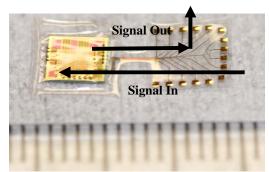

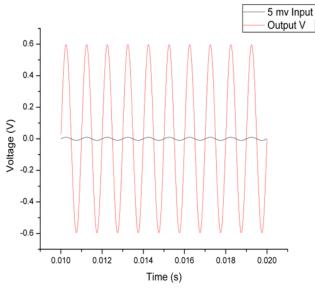

- Figure 2.10. Parylene pocket-only structure. This device is used to test the amplifier chip after bonding. Signal is driven in from the bonding pads on the right-hand side of the figure and is measured from the bonding pads on the left-hand side of the figure.... 39

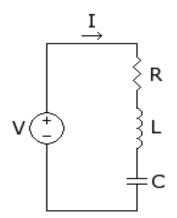

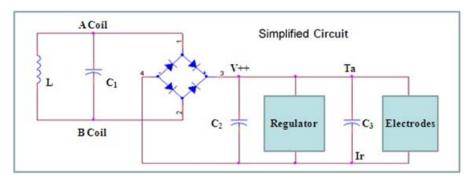

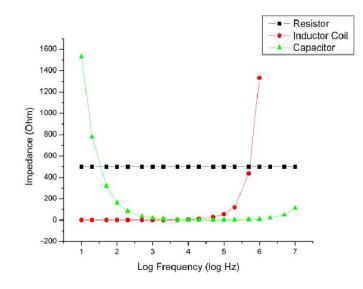

- Figure 2.13. Circuit diagram of the RLC circuit packaged with the parylene pocket. ..... 40

- Figure 2.14. Parylene pocket on parylene substrate for discrete components. An RLC circuit with 0402 sized surface mount components is shown in the figure; backside of the parylene pocket on parylene substrate. The surface mount components are clearly shown inserted in the pocket. 41

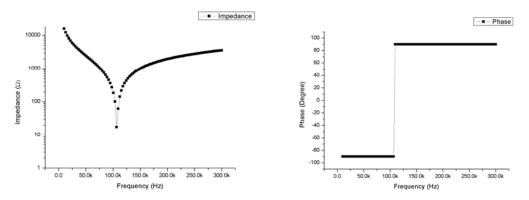

| Figure 2.15. Measured frequency response of the RLC circuit, the resonance frequency can be clearly determined from the plot; measured phase response of the RLC circuit.                                                                                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2.16. Fabrication process for dual layer pocket                                                                                                                                                                                                                             |

| Figure 2.17. (a) Fabricated dual layer parylene pocket device for PCB integration; (b) PCB inserted into the pocket. The insertion process is similar to the process described in previous sections                                                                                |

| Figure 2.18. Close-up view of the PCB inserted into the pocket. One can clearly see the traces on the right-hand side run underneath the PCB whereas the traces on the left hand side run above the PCB; a side-to-side comparison of the front and back of the device.            |

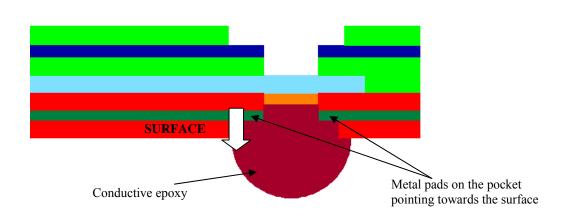

| Figure 2.19. Current metal bonding pad orientation; the metal pads on the bottom layer point away from the bottom surface                                                                                                                                                          |

| Figure 2.20. Ideal metal bonding pad orientation; the metal pads on the bottom layer point toward the bottom surface                                                                                                                                                               |

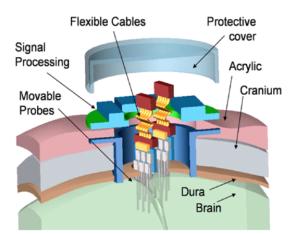

| Figure 2.21. Schematic of cortical implantation using neural probes with parylene cables. 46                                                                                                                                                                                       |

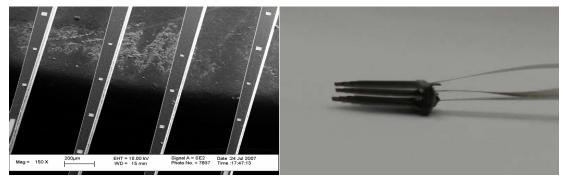

| Figure 2.22. SEM picture of the electrodes on the silicon shanks; probe stacking capability of the silicon probe structure. Figure shows three 32-channel probes stacked together to form a 96-channel three-dimensional structure. The spacing between the probes can be modified |

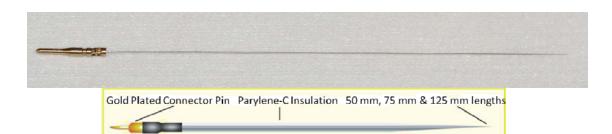

| Figure 2.23. Single microelectrode pin with parylene coating. The only electrode is opened at the tip of the probe                                                                                                                                                                 |

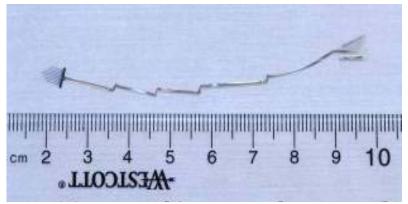

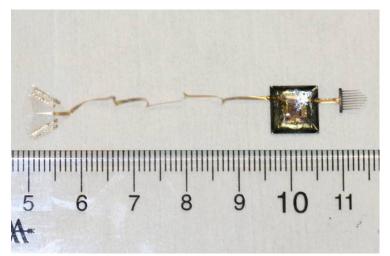

| Figure 2.24. Released silicon probe with parylene flexible cable                                                                                                                                                                                                                   |

| Figure 2.25. Proximal bonding of commercial connector with parylene cable connector pads; before bonding; after bonding with conduction epoxy                                                                                                                                      |

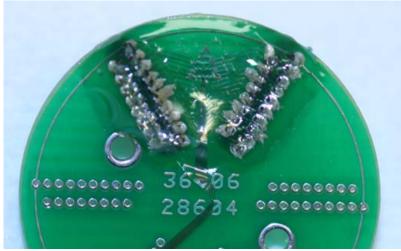

| Figure 2.26. Bonding interface of the connector pads on the silicon probe device and the commercial connector through a custom PC board                                                                                                                                            |

| Figure 2.27. Schematic of the packaged silicon probes. The design shows a 96-channel device consisting of three 32-channel devices. The legs of the titanium pedestal are secured to the skull with bone screws. 49                                                                |

| Figure 2.28. Fabrication process of the parylene-cabled silicon probe with parylene pocket. 50                                                                                                                                                                                     |

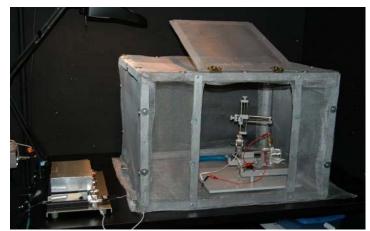

- Figure 2.30. *In vitro* testing setup. The metal box on the left-hand side is a preamplifier. The x-y stage in the Faraday cage maneuvers the probe into the saline solution. ..... 52

- Figure 3.1. CMOS MEMS integrated process [119]. ..... 57

- Figure 3.2. EM4100 RFID chip used to demonstrate the pocket integration technology. 58

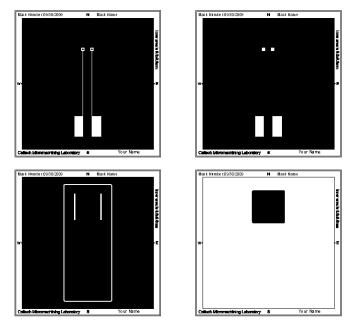

- Figure 3.3. Photolithography masks used for the RFID parylene pocket structure; lift-off lithography mask for the metal; metal exposure mask; through hole and device definition mask; sacrificial layer mask. Positive photoresist is used is this process. 60

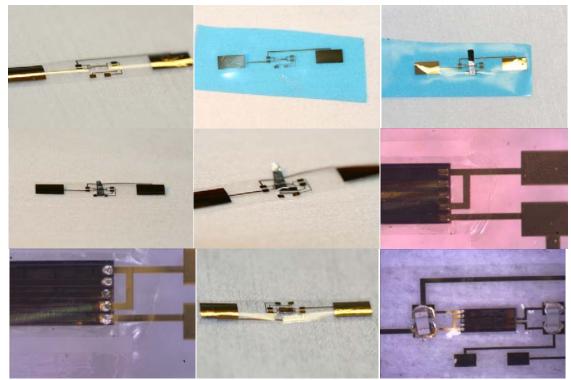

- Figure 3.4. Step-by-step integration process of the RFID chip with the parylene pocket.61

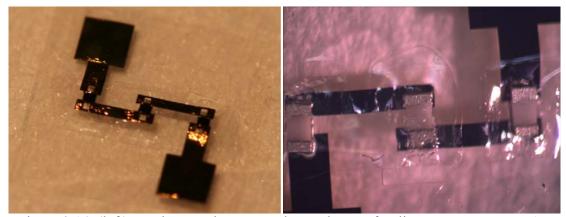

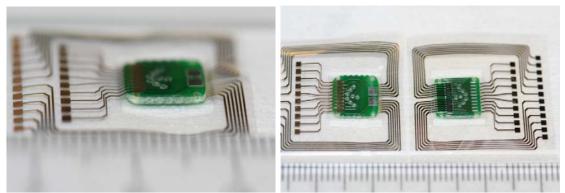

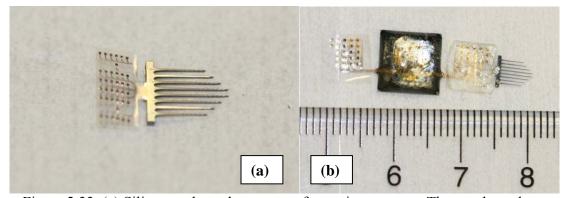

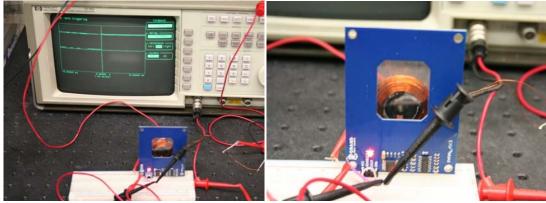

| Figure 3.5. Parylene pocket packaged RFID chip. The structure is coated with 30 μm parylene C and around 1.5–2.0 mm of biocompatible silicone after bonding |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3.6. RFID test setup with the oscilloscope                                                                                                           |

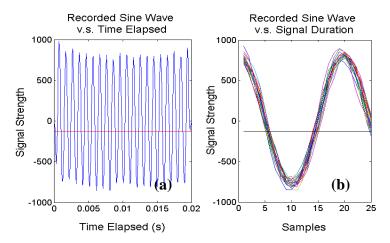

| Figure 3.7. Signal readout from the oscilloscope                                                                                                            |

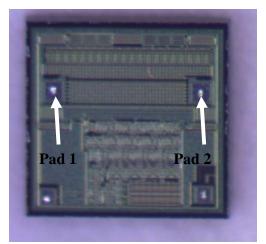

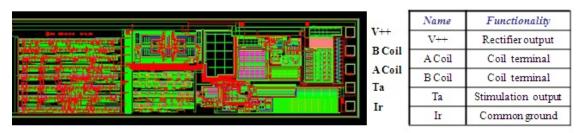

| Figure 3.8. BION chip layout and the pad connection                                                                                                         |

| Figure 3.9. Schematic overview of a BION chip integration system                                                                                            |

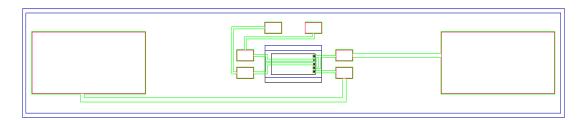

| Figure 3.10. Mask layout for the parylene pocket structure for the BION chip                                                                                |

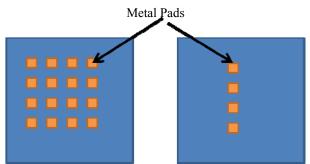

| Figure 3.11. Chip pad arrangement; two-dimensional arrangements; one-dimensional arrangement                                                                |

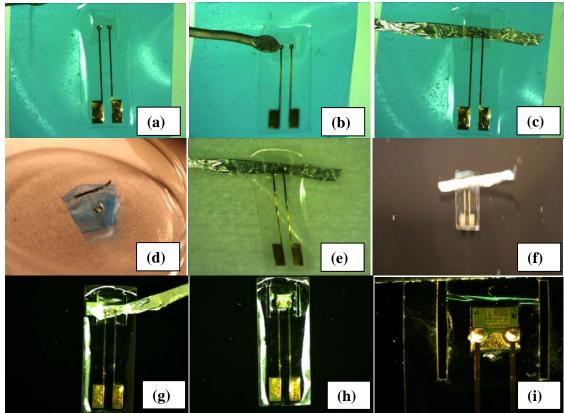

| Figure 3.12. Step-by-step integration process of the BION chip                                                                                              |

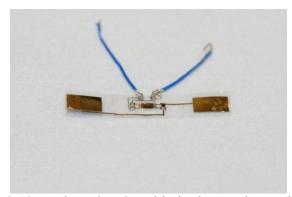

| Figure 3.13. Packaged BION chip in the parylene substrate.                                                                                                                                                                                                                                                                                                                                                 | . 68                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

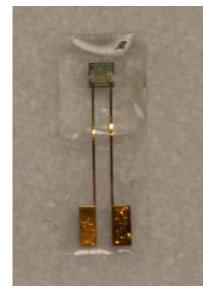

| Figure 3.14. A telemetry setup for functionality test of the assembled BION system; complete set up with the personal trainer and the transmitting coil; the receiving sitting inside the transmitting coil.                                                                                                                                                                                               | coil                  |

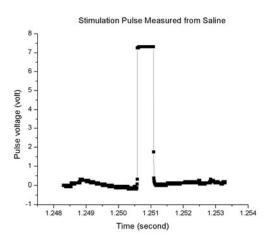

| Figure 3.15. Typical simulation pulse measured from the electrode site.                                                                                                                                                                                                                                                                                                                                    | . 69                  |

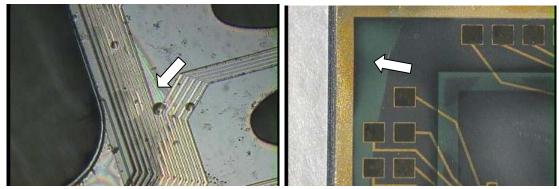

| Figure 4.1. Delamination occurs on an integrated parylene-cabled silicon probe and a<br>eventually separate the parylene and the silicon probe; delamination on the edg<br>an integration chip with parylene layers on top. The performance of the pocke<br>compromised due to the separation of parylene and silicon. The white arrows p<br>out the difference in color, which indicates saline undercut. | e of<br>et is<br>oint |

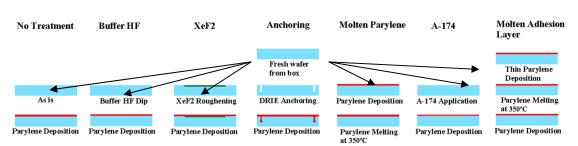

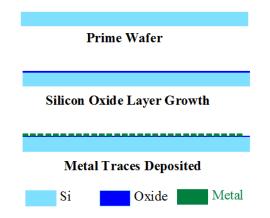

| Figure 4.2. Process steps for different treatment; all of the process steps start wit 500 µm thickness prime silicon wafer that goes through the treatment and then parylene deposited on top of it. The control sample of this experiment has paryl deposited on top of a blank wafer without any type of treatment.                                                                                      | has<br>lene           |

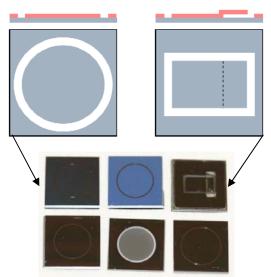

| Figure 4.3. Sample layout for soaking tests. The diameter of the circle is 6.8 mm; san layout for peeling tests (3 mm $\times$ 5.7 mm). For those used for peeling te photoresist is used as sacrificial layer to create the partial film. All trenches 250 $\mu$ m wide; actual samples.                                                                                                                  | ests,<br>are          |

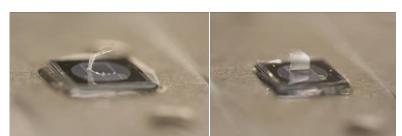

| Figure 4.4. Partial film torn before the film is peeled away from the substrate; partial to completely peeled away.                                                                                                                                                                                                                                                                                        |                       |

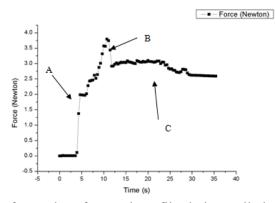

| Figure 4.5. Time vs. force plot of a parylene film being pulled away from the sili substrate. Section A is the elastic part of the pulling process, where section represents rupture and C represents the residual constant force.                                                                                                                                                                         | n B                   |

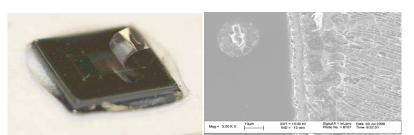

| Figure 4.6. Molten adhesion layer sample (after testing) for pulling test; SEM of peeled interface.                                                                                                                                                                                                                                                                                                        |                       |

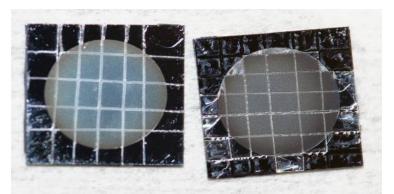

| Figure 4.7. ASTM cross-cut test; XeF <sub>2</sub> treated surface with parylene before 120°C hour soaking; after Scotch tape peeling, parylene on the treated surface is still int The circular shape surfaces in the samples are XeF <sub>2</sub> treated surfaces.                                                                                                                                       | tact.                 |

| Figure 4.8. Annealed sample with molten adhesion layer 90°C soaking result                                                                                                                                                                                                                                                                                                                                 | . 81                  |

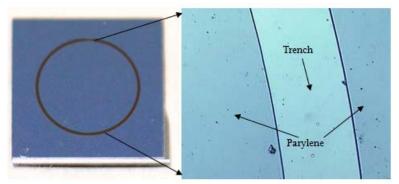

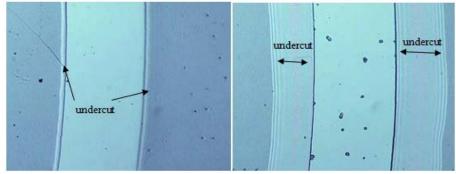

| Figure 4.9. Sample with molten adhesion layer 90°C soaking result; the trench is 200 wide. Nonannealed samples have lower undercut rate than their annea counterparts                                                                                                                                                                                                                                      | aled                  |

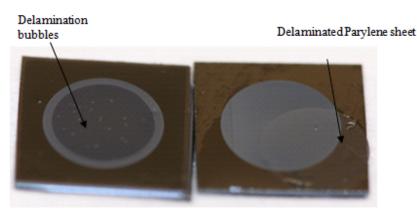

| Figure 4.10. XeF <sub>2</sub> treated samples after 48% HF cleaning for 1 minute; 10 minutes. delamination bubbles in the middle of the island are clearly shown.                                                                                                                                                                                                                                          |                       |

| Figure 4.11. Conduction chip fabrication process.                                                                                                                                                                                                                                                                                                                                                          | . 83                  |

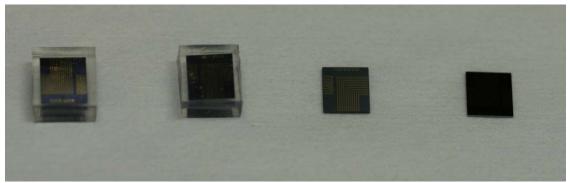

| Figure 4.12. Soaking samples from left to right: bare die coated with both biocompatible silicone and parylene, bare die coated with biocompatible silicone, bare die coated with parylene, bare die                                                                                                                       | d      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

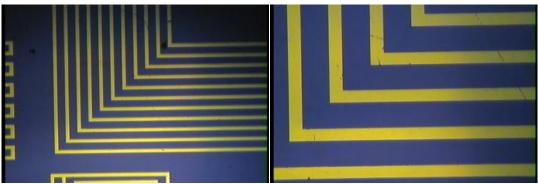

| Figure 4.13. Undamaged metal lines on the bare die before soaking                                                                                                                                                                                                                                                          | 5      |

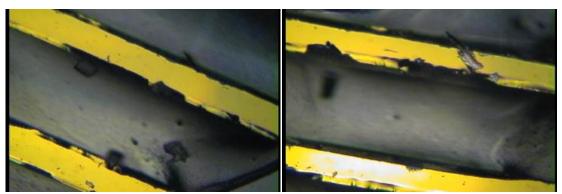

| Figure 4.14. Delaminated metal lines on the bare die after 2 days of soaking at 110°C 87                                                                                                                                                                                                                                   | 7      |

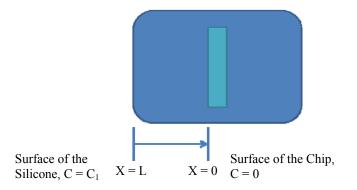

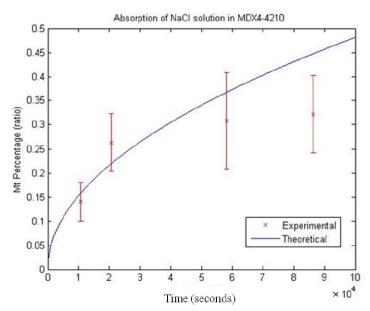

| Figure 4.15. Absorption of NaCl solution in silicone                                                                                                                                                                                                                                                                       | 0      |

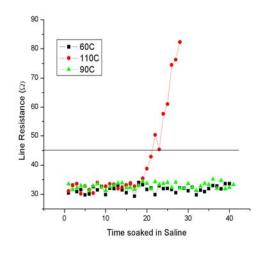

| Figure 4.16. Line resistance vs. time soaked in saline solution                                                                                                                                                                                                                                                            | 2      |

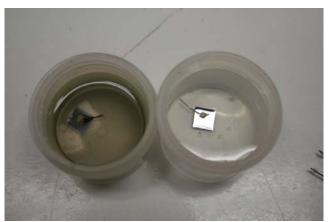

| Figure 4.17. Conductive epoxy filling diffused into surrounding saline solution; the silve residue can be seen coated on the side of the container; this effect is not observed is sample coated with parylene and biocompatible silicone                                                                                  | n      |

| Figure 4.18. Active soaking of parylene pocket that houses an RFID chip                                                                                                                                                                                                                                                    | 4      |

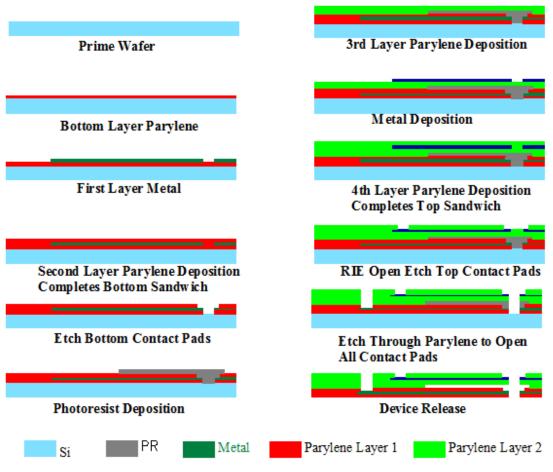

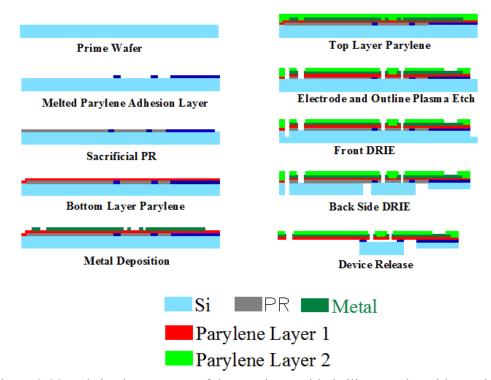

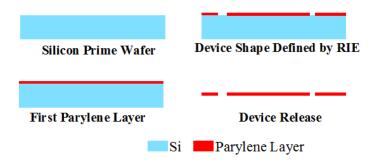

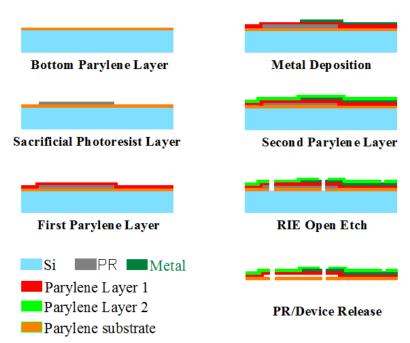

| Figure 4.19. Fabrication step of parylene-only structures for mechanical model                                                                                                                                                                                                                                             | 5      |

| Figure 4.20. Custom heat-forming mold                                                                                                                                                                                                                                                                                      | 5      |

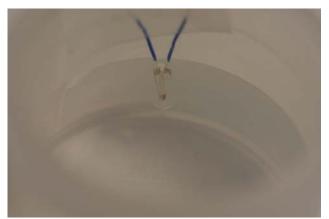

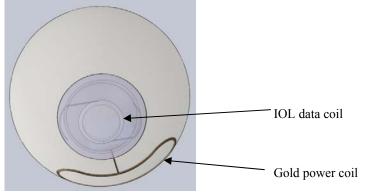

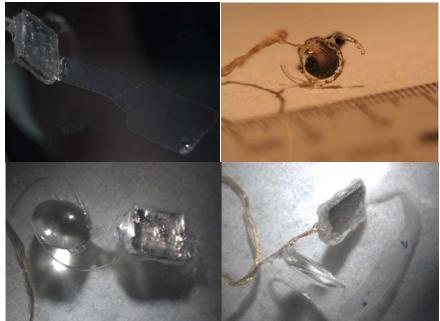

| Figure 4.21. First generation completely intraocular model                                                                                                                                                                                                                                                                 | 7      |

| Figure 4.22. First generation completely intraocular model in porcine eye                                                                                                                                                                                                                                                  | 7      |

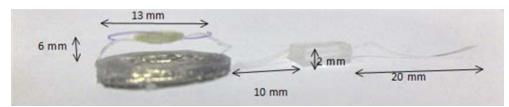

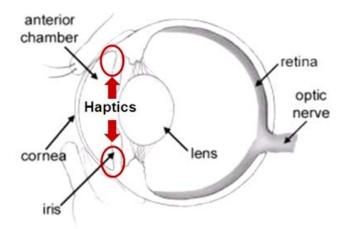

| Figure 4.23. Design of the part intraocular, part extraocular model. The gold wire sit outside the eyeball while the rest of the systems are implanted inside                                                                                                                                                              |        |

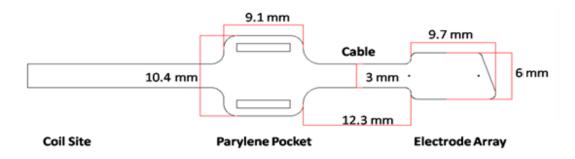

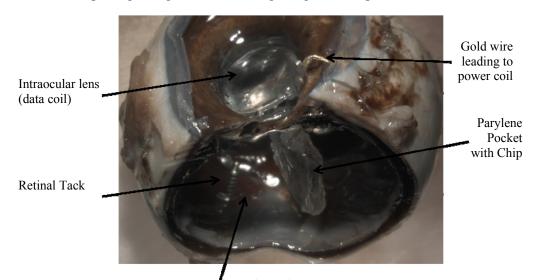

| Figure 4.24. Prototype geometry for a part intraocular, part extraocular parylene-based device with all required component regions for a completely implantable system99                                                                                                                                                   |        |

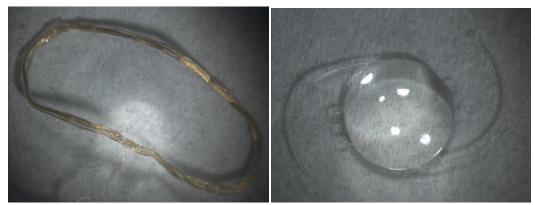

| Figure 4.25. The power coil made from gold wires; the intraocular lens acting as data coil in this mechanical model                                                                                                                                                                                                        |        |

| Figure 4.26. Example of a coil with intraocular coil haptics attached                                                                                                                                                                                                                                                      | 9      |

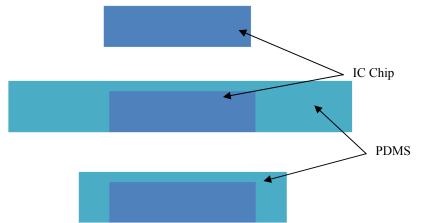

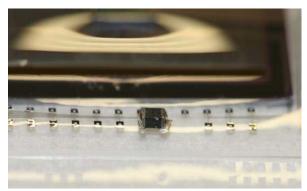

| Figure 4.27. Chip packaging in parylene pocket in mechanical implantation model parylene sheet before assembly with chip inserted; thickness of the chip section i approximately 1.6 mm; parylene pocket after biocompatible silicone coating; th parylene pocket after curing and annealing                               | s<br>e |

| Figure 4.28. Assembled devices; the parylene electrode area; the intraocular lens acting<br>as the data coil; the intraocular lens with the packaged chip structure; the entir<br>device consist of a gold wire power coil, an intraocular lens as data coil, a parylen<br>pocket with chip and a parylene electrode sheet | e<br>e |

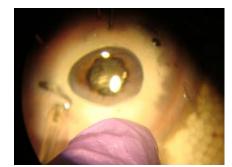

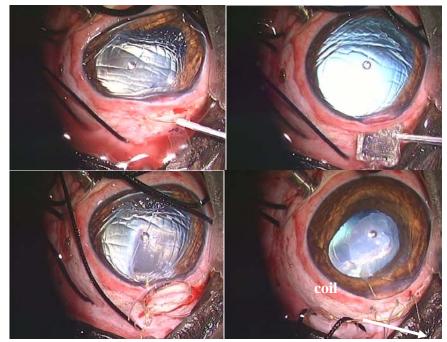

| Figure 4.29. Retinal tack used for attaching the parylene electrode sheet onto the retina surface; view from outside of the eyeball. One can clearly see the tacks coming out; retinal tack.                                                                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 4.30. Intraoperative surgical photographs; the parylene electrode area being inserted into the opening; the parylene pocket with chip being inserted into the opening; the intraocular lens being inserted; the opening being sutured, leaving the gold wire power coil outside. 102 |

| Figure 4.31. Postsurgery dissection of the eyeball                                                                                                                                                                                                                                          |

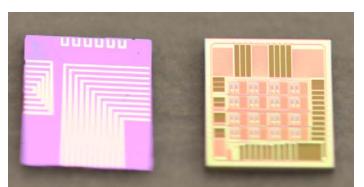

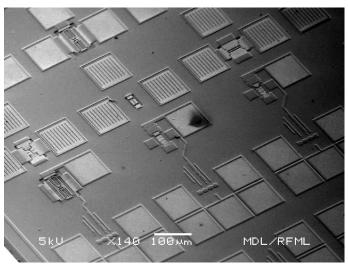

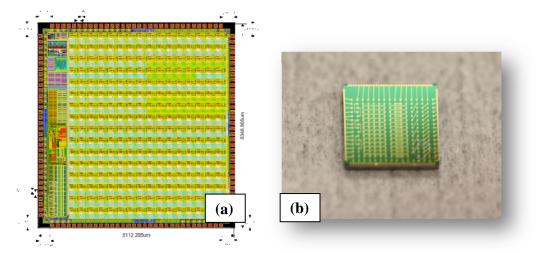

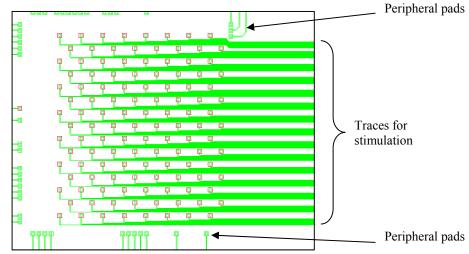

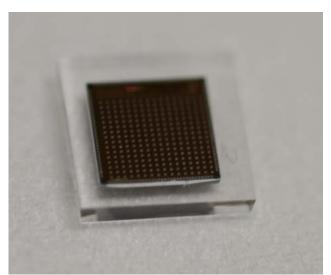

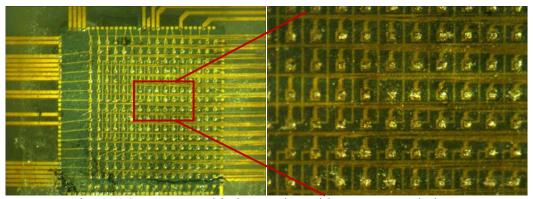

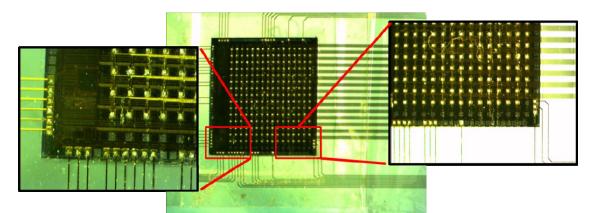

| Figure 5.1. (a) Layout of 256-channel stimulation chip from UC Santa Cruz. The pad size is 100 $\mu$ m × 100 $\mu$ m. There are about 120 functional peripheral pads on the edge of the chip; (b) dummy chip with conductive traces is fabricated to emulate the actual chip. 106           |

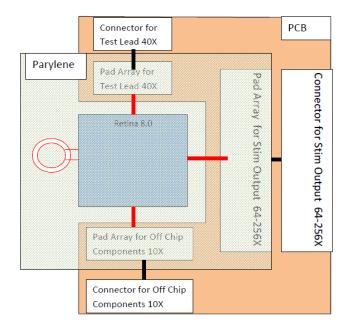

| Figure 5.2. Printed circuit board integration approach with parylene pocket platform for retinal prosthetic prototype testing                                                                                                                                                               |

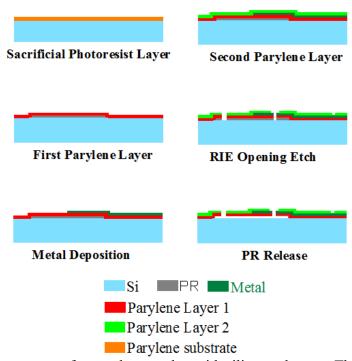

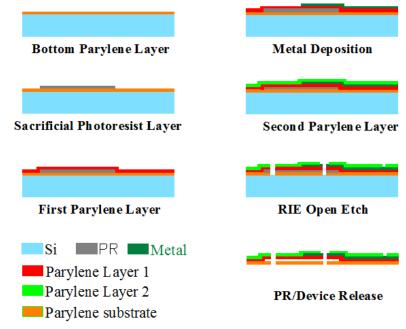

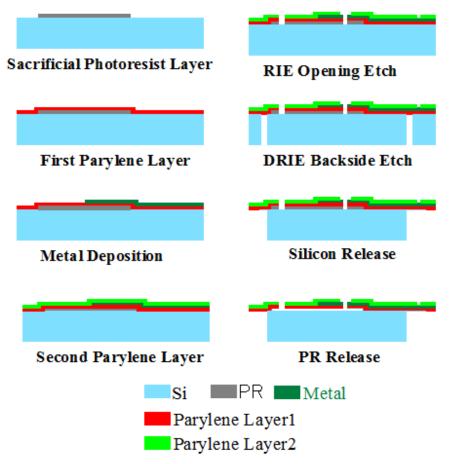

| Figure 5.3. Process step for the parylene pocket platform on silicon substrate 108                                                                                                                                                                                                          |

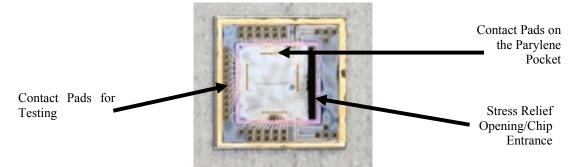

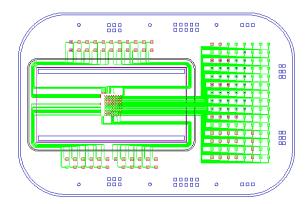

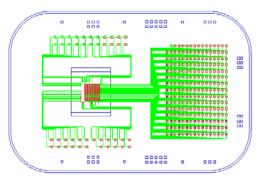

| Figure 5.4. Layout of the parylene pocket on silicon substrate platform 109                                                                                                                                                                                                                 |

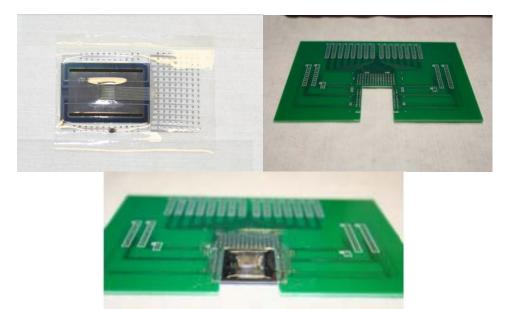

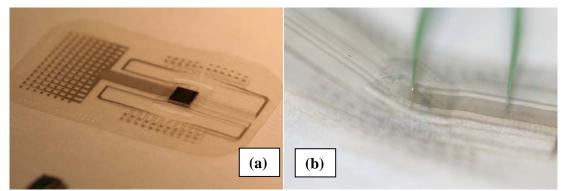

| Figure 5.5. Fabricated parylene pocket platform with silicon substrate with chip integrated; printed circuit board to accommodate the parylene pocket platform; complete integrated and bonded device. 109                                                                                  |

| Figure 5.6. Close-up figure of the layout of the traces near the bonding pads for the chips.<br>Due to the location of the peripheral pads, the traces for stimulation are limited to the middle                                                                                            |

| Figure 5.7. Detached gold lines after the underlying chrome has been etched away due to isotropic undercut etching                                                                                                                                                                          |

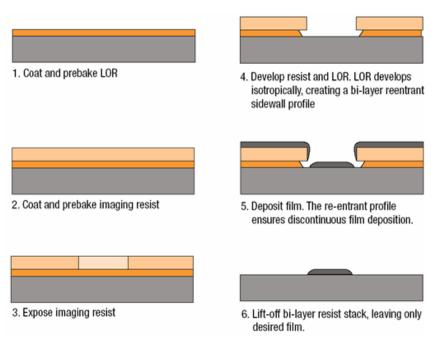

| Figure 5.8. Lift-off lithography steps                                                                                                                                                                                                                                                      |

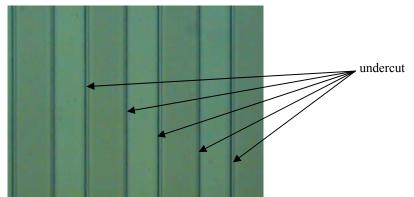

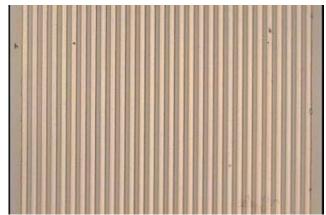

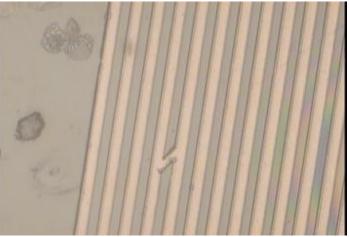

| Figure 5.9. Lift-off photoresist after development; the undercut (white strips) can clearly be seen on the edges of the photoresist lines                                                                                                                                                   |

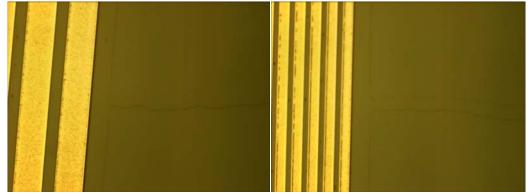

| Figure 5.10. Figure of the trace lines after metal deposition and lift-off resist release 112                                                                                                                                                                                               |

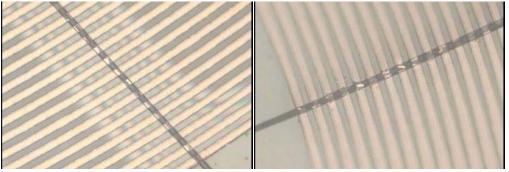

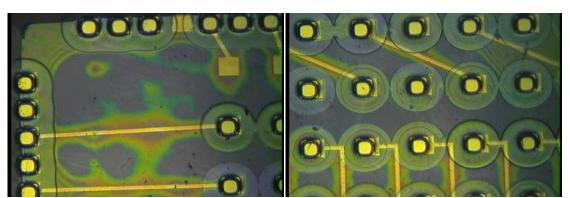

| Figure 5.11. Parylene cracks can be clearly seen on the empty areas on the right hand side of both figures                                                                                                                                                                                  |

| Figure 5.12. Parylene cracks occurs on the edges of the metal lines; resulting in solution attack and causes delamination. 115                                                                                                                                                              |

| Figure 5.13. Figure of metal line going over a step                                                                                                                                                                                                                                         |

# xviii

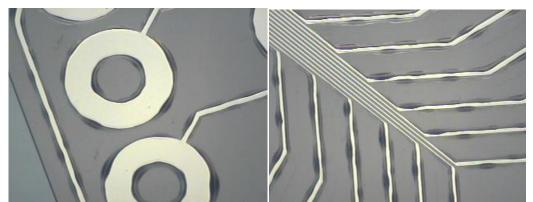

| Figure 5.14. Microscope view of the metal line going over a step 117                                                                                                                                                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 5.15. Process steps for the parylene pocket on parylene substrate                                                                                                                                                                     |

| Figure 5.16. Mask layout for the parylene pocket platform on parylene substrate. Note the area for the pocket is much smaller compared to the pocket platform on silicon substrate                                                           |

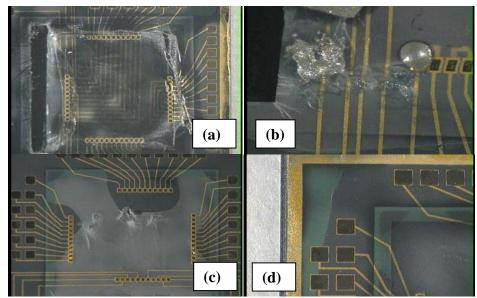

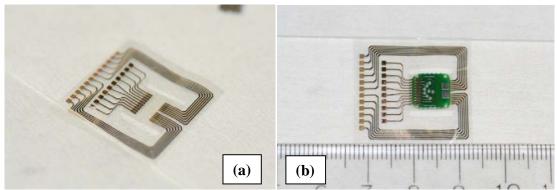

| Figure 5.17. (a) Fabricated parylene pocket platform with IC chip integrated and bonded;<br>(b) the parylene pocket structure                                                                                                                |

| Figure 5.18. Alignment of the pocket bonding pads with the metals pads on the chip.<br>Resolution of 10 µm to 20 µm can be achieved                                                                                                          |

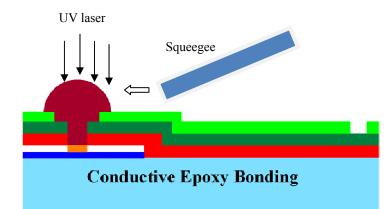

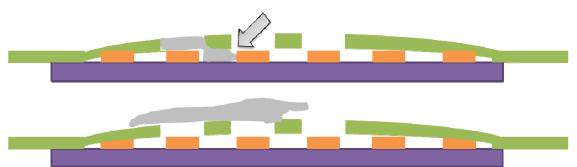

| Figure 5.19. The squeegee is used to push the excess conductive epoxy away from the surface; heat is applied to cure the epoxy that remains in the trench to make the connection between the pads of the parylene and the IC chip            |

| Figure 5.20. The conductive epoxy may short circuit two neighboring metal pads on the chip if the viscosity of the epoxy is too low; the conductive epoxy may not provide electrical connection if the viscosity is too high                 |

| Figure 5.21. The well after the conductive epoxy squeegee process. The well is only 5 microns tall and cannot retain the epoxy, leaving empty spaces in the well. After SU-8 layer application, the wells are completely retained and filled |

| Figure 5.22. The conductive epoxy footprint on a testing substrate after squeegee process.<br>This test is conducted to determine the optimized aspect ratio of the SU-8 well 124                                                            |

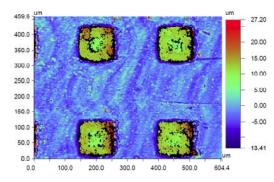

| Figure 5.23. The surface profile of the bonded surface. The maximum height of the conductive epoxy bump is about 25 μm                                                                                                                       |

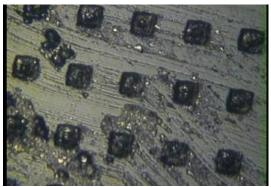

| Figure 5.24. The surface of the bonding pads right after the squeegee. There is a significant amount of residue left                                                                                                                         |

| Figure 5.25. Edge of the chip—where the squeegee process may become a problem 127                                                                                                                                                            |

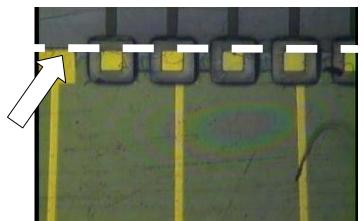

| Figure 5.26. Chip edge protection process: PDMS is poured on top of the IC chip and later trimmed to shape to be inserted into the pocket                                                                                                    |

| Figure 5.27. PDMS mold fitted with a 256-channel stimulation chip 127                                                                                                                                                                        |

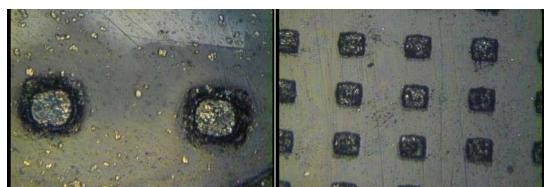

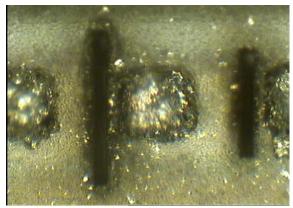

| Figure 5.28. Short circuit defect on dense metal lines                                                                                                                                                                                       |

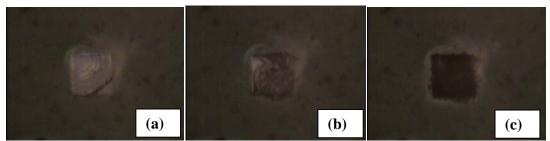

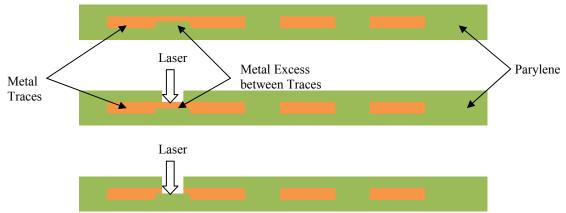

| Figure 5.29. Laser etching of the parylene layer; (a) after 30 pulses; (b) after 60 pulses; (c) after 200 pulses. 130                                                                                                                        |

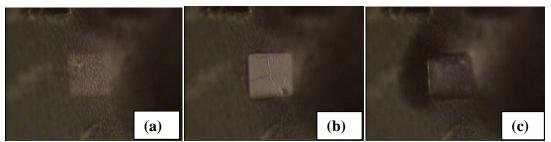

| Figure 5.30. Laser etching of the gold metal layer; (a) before; (b) during; (c) after 130                                                                                                                                                    |

| Figure 5.31. | Short    | circuit   | defect  | repair | process;   | laser   | is used | to  | first  | open | the | pary | lene, |

|--------------|----------|-----------|---------|--------|------------|---------|---------|-----|--------|------|-----|------|-------|

| followed     | l by a s | short etc | h of th | e meta | l excess : | in betv | ween th | e m | etal l | ines |     |      | . 130 |

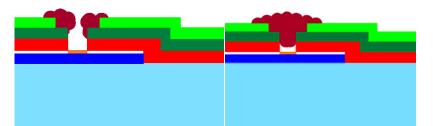

| Figure 5.32. (a) Shortage of neighboring metal pade | s underneath the parylene film due to |

|-----------------------------------------------------|---------------------------------------|

| low viscosity of the conductive epoxy; (b) eve      | n though the surface of the parylene  |

| film is free of conductive materials                |                                       |

- Figure 5.36. Surface mounted resistor bonded on two of the metal pads on the parylene sheet. Note that all discrete components, including MEMS inductive coils, can potentially be integrated with this structure. 133

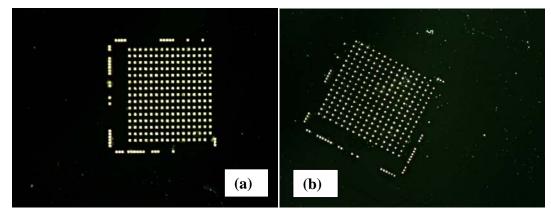

Figure 5.38. 256-channel integration with high density squeegee bonding technique... 134

# LIST OF TABLES

| Table 1.1. Properties of parylene N, C, D, HT, and PDMS.                                                                                                         | 23 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Table 1.2. Parylene coating functions for selected medical applications.                                                                                         | 25 |

| Table 4.1. Force gauge maximum force readings of the peeling test $(n = 4)$ .<br>NA = nonannealed, A = annealed. Molten parylene has the highest adhesion force. | 77 |

| Table 4.2. ASTM D3395B Grading (% film removed).                                                                                                                 | 79 |

| Table 4.3. Result of the ASTM cross-cut test $(n = 2)$                                                                                                           | 79 |

| Table 4.4. Accelerated life time testing to observe the undercut rate of the parylene/silicon interface $(n = 3)$ .                                              | 81 |

| Table 4.5. MTTF of conduction chips in different packaging.                                                                                                      | 87 |

| Table 4.6. MTTF of conduction chips in parylene pocket (estimation assumes an Arrhenius activation energy factor of 2 for every 10°C)                            | 92 |

| Table 4.7. MTTF of conductive epoxy adhesion on different surfaces.                                                                                              | 94 |

| Table 5.1. Step height effect on metal continuity. 1                                                                                                             | 17 |

| Table 5.2. Aspect ratio of conductive epoxy well and its connectivity. 12                                                                                        | 24 |

| Table 5.3. Laser process recipe to etch specific materials on the parylene skin structure.      12                                                               |    |

#### GLOSSARY

- ACIOL anterior chamber intraocular lens

- AMD age-related macular degeneration

- ASCII American Standard Code for Information Interchange

- ASIC Application Specific Integrated Circuit

- ASTM American Society for Testing and Materials

- BGA ball grid array

- CL-I<sup>2</sup> Chip-level Integrated Interconnect

- CMOS complementary metal-oxide-semiconductor

- CT computed tomography

- CVD chemical vapor deposition

- DIP dual in-line package

- DRIE deep reactive ion etching

- EDP ethylene diamine pyrocatechol

- FDA Food and Drug Administration

- HF hydrofluoric acid

- HNA hydrofluoric acid, nitric acid and acetic acid

- IC integrated circuit

- ID identification

- ISO International Organization for Standardization

- KOH potassium hydroxide

LIGA – Lithographie, Galvanoformung, Abformung (Lithography, Electroplating, and Molding)

LOR - lift-off resist

#### xxii

- MEMS micro-electro-mechanical systems

- MFI MicroFlex interconnect

- MRI magnetic resonance imaging

- MTTF mean time to failure

- PCB printed circuit board

- PDMS polydimethylsiloxane

- PR photoresist

- PSG phosphosilicate glass

- RF radio frequency

- RFID radio frequency identification

- RIE reactive ion etching

- RLC resistor-inductor-capacitor

- RP retinitis pigmentosa

- SEM scanning electron microscope

- SNR signal-to-noise ratio

- SOI silicon on insulator

- TMAH tetramethylammonium hydroxide

- TTL transistor-transistor logic

- USP United States Pharmacopeia

- WHO World Health Organization

# **1 INTRODUCTION**

# **1.1** Prosthetic Applications—The Need and Driving Force

# 1.1.1 Retinal Prosthesis

Two of the most common retinal degenerative defects in the world right now are age-related macular degeneration (AMD) and retinitis pigmentosa (RP). RP has already affected several hundreds of thousand people in the United States to date and AMD is estimated to cause more than several million people worldwide to have significant symptoms associated with it in the next ten years [1–3]. Even though gene therapies, drug and nutritional therapies and other types of remedies are developed [4–5] to decrease the rate of such occurrences, the defects still cause the loss of the rod and cone receptors in the eye [4, 6–8], and blindness in the long run becomes inevitable and cannot be treated.

It has been studied, however, that the ganglion cell layer, which consists of the optical nerves, remains functional even after the patient has gone completely blind and can be electrically stimulated to construct localized visual signals in patients [9–12]. Visual prosthesis, a technology that takes advantage of this fact to regains eyesight for AMD, RP and patients with other degenerative eye diseases, quickly becomes the focus for research and development around the world.

There are two main implantation and stimulation schemes in development right now to realize full visual prosthetic applications: subretinal and epiretinal, which differ by the location of the implanted devices and stimulation sites. However, regardless of the location of the implant, the basic system components of this application remain the same. A camera is mounted on an external mount (such as a pair of glasses) and is powered to take videos and pictures to generate the raw signals that are to be sent into the eye. This signal is then passed into a circuitry box where it is analyzed and stimulation signals are generated. The stimulation signal will then be passed to the stimulation electrodes to excite the retinal ganglion cells [13–14].

# **1.1.2** Neural Prosthesis

Diseases, traumatic incidents and natural defects cause the interruption of information flow between the brain, nerves, spinal cords, muscles and sensors in human body. This disconnection have been one of the top priorities for research with goals to develop treatments and rehabilitation methods to either reverse, treat or to alleviate the symptoms and to improve the quality of life of the patients. As early as the 18th century, it was discovered that the use of external electrical stimulation has the potential to overcome paralysis [15]. Since then, a series of technical aids such as neural prosthesis have been developed to bridge the gap between the generation of the biological signals from the brain and the stimulation of the muscles.

Neural probe is one of the most common apparatus to conduct neural prosthetic for either recording or stimulation in the brain. This technology makes it possible to use cellular recording of the activities of individual or groups of neurons in specific areas of the brain to help scientists gain deeper understandings of the brain [16–23]. Regardless of the type of recording or stimulation electrodes that are inserted into the subject's body, the system requires at least (1) a series of electrodes to either sense and/or emit the signal; (2) implant package for all the microelectronics for control and (3) interconnects that connects the different parts of the system. Silicon probe systems developed by University of Michigan [24–46], University of Utah [47–54] and SOI probe [55–58] and polymer probe systems [59–62] all have reported functionality and recording/stimulating capabilities in animal subjects and are expected to make great contributions in neural prosthesis research.

Finally, both neural and retinal prosthetic application are expected and required to be biostable and biocompatible. In-depth research is currently being conducted to realize a fully functional and reliable long-term implantation that is able to both record and stimulate neurons to achieve a total neural prosthetic system.

# **1.2 Integration Technology**

One of the biggest obstacles that the prosthetic systems mentioned in the previous section has to overcome is the integration of circuitries with the biodevices to be implantable in human body. Cochlear implants, which have been commercially available since the 1980s, require only 5 to 6 stimulating electrodes to be able to regain hearing capability of an impaired patient [63]. The integration of circuitry is outside the subject and only the electrodes are implanted inside. Neural and retinal prosthetic applications, however, require hundreds or even thousands of electrodes to be connected and controlled at the same time to achieve minimal working functions [64]. In addition, in order to avoid possible infections and medical complications from percutaneous implantation schemes, the devices have to be completely inside the subject's body. This means the need for integration, connection and packaging of integrated circuit chips in this biodevice system is imminent and cannot be ignored.

Before more advanced techniques such as those discussed in this dissertation were invented, wire wrapping and point-to-point circuit construction was used to realize systems with more than several components [63]. As more complicated and intricate circuits are designed for more advance functionalities, and as more needs for smaller and faster components are demanded, traditional circuit integration methods become obsolete and are unable to be utilized for easy and mass production. The following sections introduce some of the techniques utilized today that were invented for integrating and assembling larger scale, general circuit components. Some specific technologies for bonding IC chips with devices that are used in biomedical fields and more specifically, prosthetic applications are also presented.

# **1.2.1** Traditional Chip Integration Technology

# (a) Soldering

Figure 1.1. Soldering a component onto the back of a printed circuit board. (Courtesy of Wynn Rostek)

Soldering is one of the most widely utilized interconnect technology for printed circuit boards and electronic components. The connection is formed by melting a filler material (solder) (figure 1.1) that would mechanically and electrically connect the target component onto a metal pad. Its biggest advantage is the ease of application for quick and

dirty bonding of discrete components, but the physical weakness of the solder bonding, toxicity of the materials, localized heat during assembly and its inability to connect small and dense array pads makes soldering a less attractive alternative than other more advanced technologies.

# (b) Wire Bonding

Wire bonding is considered one of the most cost effective, flexible and efficient interconnect technology to be used in making connection between a printed circuit board and an integrated circuit chip after soldering technology. In wire bonding, a metal wire (usually gold, aluminum or copper) is fed through the wire bonding machine application tip and is pressed onto the target metal contact pads with electrically generated heat or ultrasonic vibration to form electrical and mechanical contact (figure 1.2). This step is repeated again at the second point of contact to complete a bond. This technology is most useful and most cost efficient in making small number of connection on big substrates and is most commonly used in bonding bare dies in DIP packages.

Figure 1.2. Gold wire bonded onto metal pads to make electrical connections.

# (c) Ball Grid Array

In ball grid array technology, the pins that were traditionally used on printed circuit boards and the metals pads on bare IC chips are replaced by or appended with balls of solder on the bottom of the package. This package is then placed on another printed circuit board or a substrate with metal pads patterns that matches the solder ball patterns (figure 1.3). In order to make mechanical and electrical connection, the entire structure is then heated to melt the solder ball. Surface tension would then align the package with the substrate, thus completing the interconnection. One of the biggest advantages of this approach is the density of leads it is able to achieve. Its need to heat up the substrate, however, posts limitation on the material and the process that is compatible with this technology.

Figure 1.3. (left) Illustration of the ball grid array; (right) the BGA on an actual IC chip. (Image courtesy of ThomasNet and Dominic Plunkett from www.xjtag.com)

### 1.2.2 State-of-the-Art Chip Integration Technologies with Biodevices

## (a) University of Michigan—The Michigan Probes

K. D. Wise at University of Michigan has developed a variety of penetrating electrode in different layouts for neural prosthetics. This endeavor started as early as 1969 in Stanford University [32] and has evolved into complete systems fully integrated with IC circuitries on the same silicon substrate (figure 1.4). The interconnections of these circuitries are made with a  $\sim$ 4–5 µm thick polysilicon cable. Weaknesses of this silicon-film cable are apparent since they are too brittle and are prone to breakage.

The silicon probes developed at the University of Michigan have recently adapted polymer cables [65]. These silicon probes are fully capable of simulating and recording from neural tissues and muscles. Much *in vivo* testing on animal subjects has been successfully conducted. However, the devices are still very difficult to make and require expensive process and equipment to realize; mainly due to the low yield in combining CMOS and MEMS process and the cost of materials.

On the other hand, University of Michigan has recently developed technologies to create electrical connection to a chip that is made separately from the cable and the probe itself [66], signifying a need for improvement for a higher density and easier bonding technique.

Figure 1.4. (left) The Michigan three-dimensional neural probe array [40]; (right) SEM picture of the tip of the Michigan probe [33].

# (b) California Institute of Technology—CL-I<sup>2</sup>

Li et al., with collaboration with the Doheny Eye Institute and University of Southern California Medical Center, has developed an embedded chip technology to integrate commercially available IC chips with polymer substrates and passive components [67]. A placement cavity is etched on the parylene-on-silicon substrate for chip placement. Once the chip is fixed inside the cavity, metal is deposited and a photolithography step is done to make electrical connection between the pads on the chip and outside components. The traces run between two parylene layers and is well protected. The structure is released by back etching of the silicon substrate (figure 1.5).

The parylene substrate to be integrated with the chip is a parylene-metal-parylene sandwich layer that has been well characterized both *in vitro* and *in vivo* and is also approved by the FDA for long-term human implantations. Several chronic and acute devices tested with histology results have also been published to verify the overall biocompatibility and the feasibility of the sandwich layer technology.

However, the alignment problem that arises during the "chip-drop" could severely affect the feasibility of this technology. Not only would the surface flatness inside the cavity limit the metal connectivity over a step, but the low alignment efficiency of the bonding pads on the chip with the metal in the parylene sandwich layer renders the integration inefficient.

Figure 1.5. Concept of embedded chip integration; (left) overall view of the device; (middle) close-up view of the embedded chip; (right) close-up view of the coil wires.

## (c) Microflex Interconnect

Microflex (MFI) is an interconnect technology developed by the Fraunhofer Institute for Biomedical Engineering; Meyer et al. [68] utilizes a polyimide substrate with photolithography patterned metal embedded in it. The pitch and the shape of the metal pads correspond to the bonding pads on the chip. The via-hole on the substrate contact pads is then filled with metal balls or wedges applied by a commercial wire bonder to make the electrical and mechanical contact. This technology, though very similar to wire bonding, is specifically developed to integrate the passive and active electronic components to the electrodes (figure 1.6).

Since this technology is based on polyimide process, it is compatible for biomedical implants. This substrate has passed cytotoxicity testing according to ISO 10993, has been soaked more than 4 years in saline solution and has been implanted for more than 10 months in rats. The MicroFlex technology can also be applied to three-dimensional structures and the density is comparable to that of the flip chip technology. Several ultrasound array sensors, retinal stimulators (EPIRET) and multiplexer modules have been integrated successfully with this technology [68–71].

Their current device, called the EPIRET 3, has transmitting coils on external glasses and an internal receiver coil and chip secured in the eye in place of the lens (figure 1.7). As with all epiretinal prosthesis, the electrode array is tacked onto the back of the retina. In an exploratory human trial in 2009, the device was implanted for four weeks to observe the safety of the device and how well it would work. There was mild inflammatory response in some of the six subjects, but they decided there was no lasting damage from the prosthesis. Four of the six subjects gained light perception, one gained hand movement, and one had no light perception [72].

However, more clinical trials are still needed to demonstrate the long-term performances of implants. The mechanical properties of the bond on the substrate have

9

yet to be tested as well. There are also several other issues including alignment and overall packaging that needs to be considered before this technology can be reliably long-term implanted for chronic use.

Figure 1.6. Close-up picture of the MicroFlex bonding technique, facilitated by a commercial wire bonding machine setup [70].

Figure 1.7. Final implant with parylene C and silicone rubber encapsulation [71].

#### (d) Boston Retinal Implant Project

Dr. Wyatt and Dr. Rizzo from Massachusetts Institute of Technology developed a subretinal implant device that aims to achieve visual prosthesis [73]. The polyimide device substrate hosts all the system components, which are connected via 50  $\mu$ m wide Cu/Ni/Au metallization traces. As shown in figure 1.8, the ASICs on the left-hand side were mounted by stud bumping with 75  $\mu$ m high Au bumps, followed by flip chip die attachment to the host substrate. Stud bumping was also used for the flex-to-flex

connections between the flex circuits and the electrode arrays. Nonconductive epoxy was used to encapsulate the entire device and then coated in PDMS (polydimethylsiloxane).

Although this device has been through several *in vivo* studies, the integration approach proved to be prone to reliability problems. Also, the lifetime of the encapsulation coating (PDMS) has subpar performance relative to other biocompatible coatings.

Figure 1.8. Schematic representation of the retinal implant by Theogarajan et al. [73].

## (e) Other Technologies

Deguchi et al. from Tohuku University in Japan have developed a one-piece, stacked retinal prosthesis chip system to be implanted in human eye [74]. It consists of implantable IC chips responsible for photodetection, image processing, current generation and stimulating arrays (figure 1.9a). While implanting the entire chip into the eye eliminates the need for integration of flexible electrodes with circuitry, the hard substrate that comes along with this stacking technology makes it more damaging to the tissues and less surgically friendly.

A pressure monitoring system integrated in a small package has been developed by Schlierf et al. [75]. The package comprises a sensor ASIC, which includes a capacitive absolute pressure sensor with an inductive telemetry unity and other passive components in different packaging (figure 1.9b). These components are soldered onto the underlying substrate, which is then subsequently encapsulated in a biocompatible silicone and parylene coated. While the system performed satisfactory *in vitro*, the packaging mechanism cannot be scaled to accommodate smaller components and IC chips with higher number of leads.

Other research groups worldwide have also developed different schemes for varieties of biomedical implants and prosthetic devices. The basic idea is to minimize the number of electronic components and the size of the packaging without compromising the functionality of the overall device. While many of these devices have good functionality and short-term stability, clinical trials still needs to be demonstrated for both animal and human models for long-term reliability and performance evaluations.

Figure 1.9. (a) Schematic of the three-dimensional stacked chip [74]; (b) implantable sensor system: A control unit and analogue part with RF coil [75].

# **1.3 Problems and Challenges**

Next generation retinal prosthesis development will require totally implanted devices to minimize inflammations and surgical complexity as well as the physical damages incurred on the receiving subject during surgeries and procedures. This means the telemetry circuit, along with signal processing and the stimulation circuit and a stimulation electrode all would have to eventually be fit inside a human eyeball (<1-2 cm<sup>3</sup>). MEMS technology, which will be discussed in the next section, is not only a great candidate to miniaturize the system, but it has also been utilized to increase the precision and the ease of fabrication of such implantable devices. In fact, MEMS has become one of the most crucial technologies that would foster the success of the development of a reliable implantable system.

However, although numerous implantable devices have been developed with micro-electrical-mechanical system technology to integrate IC with bioimplantable microfabricated devices, there still lacks an enabling packaging technology that is able to meet all of the requirements that are demanded by current state-of-the-art retinal and neural implantable systems. First of all, the analog/digital driving electronics must be in a hermetic package/encapsulant, protected from the saline environment of the body since this package needs to address the long-term biocompatibility and reliability issue in the human body. It is necessary to develop a technique to protect these implanted components from the corrosive substances, like body fluid. As it is discussed later in the chapter, parylene C, a biocompatible polymer, is selected as the main structural and packaging material because of its many favorable properties. By doing so, the package will be mechanically stable within the tissue without causing damage either to the device or to the patient.

Secondly, this hermetic packaging must also have a large number of feed-through connections for the electrical signals and to enable connection to the inductively coupled coils and other passive devices such as chip capacitors. A conservative estimate of pixel density will be  $32 \times 32$  to enable blind individuals to better carry out activities of daily

living [76]. This is a density and number that has yet been fully attempted. It must also connect with an electrode array, either a flexible substrate or a stiff device, and the material used to insulate and stabilize this connection must be biocompatible. Furthermore, current interconnect and packaging technologies are labor-intensive, inefficient, and costly, limiting the achievable device resolution.

In addition, a compatible process must be developed to build implantable devices that can integrate other discrete components (application specific integrated circuits (ASICs), capacitors, etc.) and can withstand adverse human implant environment reliably for many years. The insulating material must not corrode, dissolve, or leak; parylene C, a MEMS compatible material, provides just the right solution to solve this problem.

In conclusion, it is clear that for the state-of-the-art implantable systems on this scale, it has become not only a trend, but a necessity to utilize MEMS technology to fabricate microelectrodes and its packaging schemes. The next section will be devoted to the discussion of this technology with a focus on parylene.

## **1.4 MEMS Technology**

MEMS (Micro-Electrical-Mechanical Systems) encompass miniaturized systems that consist of both electrical parts and mechanical parts. These parts may include elements such as sensors, actuators, fluidic channels and electronics that are fabricated or integrated on a substrate such as silicon by means of microfabrication technology, with typical dimensions ranging from 0.1 to 100 micrometers in size. The history of MEMS started shortly after the realization of transistors in 1947 and has fully taken off since then. Much attention of MEMS was also brought to light after the talk by Richard Feynman's "There's plenty of room at the bottom," which lays out the fundamentals of system miniaturization. The design of MEMS is different from the design of systems of a larger scale. This is due to the fact that the surface area of a miniaturized structure is much greater than its volume and causes the reduction of mass and inertial volume effects but increases the electrostatic and wetting surface effects of the system.

There are countless advantages from using MEMS technology. Not only does it enable the communication between mechanical and electrical elements on the same substrate in a system, it also has lower cost, is smaller in size, mass and power consumption, and has higher functionality, reliability and precision. Because of these advantages, numerous devices such as micromotor [77], accelerometer [78], pressure sensors [79] and RF filters are realized.

Because of its root in the IC industry, many of MEMS basic processing techniques are borrowed or adapted from IC technology, such as photolithography, oxidation, diffusion, ion implantation, chemical vapor deposition (CVD), evaporation, sputtering, wet chemical etching, and dry plasma etching. There are, however, features that one may encounter in MEMS fabrication process that are uncommon in integrated circuit fabrication such as nonplanar substrate (i.e., relatively large three-dimensional features); the use of thick photoresist layers (for structure purposes or for long etching time); relatively high aspect ratio structures; relatively large feature sizes and unusual materials (particularly important in terms of adhesion). Traditional MEMS process, along with several special processes such as deep reactive ion etching (DRIE), LIGA, electroplating, and soft lithography have been developed to support these uncommon features.

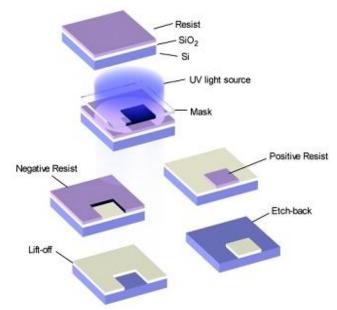

Before any MEMS specific process can be brought to discussion, the most essential step in the process is the photolithography step. This step provides pattern resolutions high enough to achieve miniaturization, which is done with photodefinable compounds called photoresist. Photoresist is a light sensitive material that can be selectively removed by shining light at specific wavelengths on desired areas. Depending on if this material is "positive" or "negative," areas that are shined with light will be removed from or will remain on the substrate, respectively (figure 1.10).

Figure 1.10. Comparison of positive and negative photoresist. (Courtesy of NCSU Soft lithography Wiki)

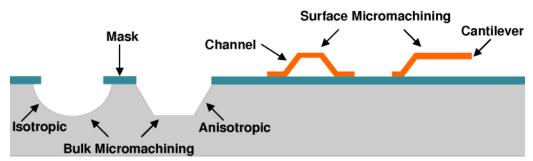

The most noticeable difference of the fabrication process of MEMS from traditional integrated circuit fabrication is the ability to modify the substrate with the two basic techniques: surface micromachining and bulk micromachining (figure 1.11).

Figure 1.11. Comparison of surface micromachining and bulk micromachining.

#### **1.4.1 Bulk Micromachining**

Bulk micromachining takes advantage of all three dimensions of the bulk material and creates features inside the substrate (top-down machining) by etching. Single crystalline silicon is the most common material used in MEMS processing because of its ability to be easily etched. Etching can be separated into two categories: isotropic etching and anisotropic etching; both of these etchings can be achieved in a wet or dry environment (figure 1.12).

In isotropic wet etching, where the etching rates in all directions in the substrate are the same, etchants such as HNA (hydrofluoric acid + nitric acid + acetic acid) are used. In anisotropic etching, where the etching rate differs by the direction of the crystal plane, wet etchant such as solutions of KOH (potassium hydroxide), EDP (ethylene diamine pyrocatechol), TMAH (tetra-methyl-ammonium-hydroxide), and hydrazinewater are used. By combining anisotropic etching with etching stops such as boron implantation (P+ etch-stop) and other electro-chemical etch-stop technique, varied silicon microstructures can be bulk machined.

Figure 1.12. Comparison of isotropic and anisotropic wet etching and dry etching. (Courtesy of An Introduction to MEMs Engineering—Nadim Maluf and Kirt Williams)

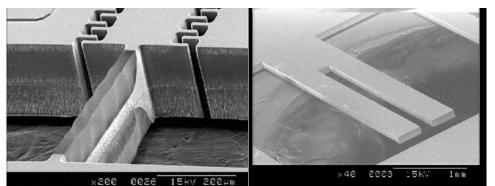

Etching can also be achieved by dry etching, which can be separated into three classes called reactive ion etching, sputter etching and vapor phase etching depending on the different chemical and physical interactions between the ions of the gas and the atoms on the substrate. In reactive ion etching, external energy generated by RF (radio frequency) power induces chemical reaction in low-pressure reaction chambers between the gaseous ions and the atoms on the target substrate. Some physical bombardment of the gaseous ion onto the target substrate also occurs. In this process, gases such as chlorofluorocarbon gases, sulfur hexafluoride, bromine compounds and oxygen are commonly used as reactants. Sputter etching, on the other hand, is very similar to reactive ion etching, except that the process is made up entirely of the physical bombardment of the ions without any chemical interactions. In vapor phase etching, the substrate is placed inside the chamber where the gas is present, and is dissolved at the surface in a chemical reaction with the gas molecules. This process is made possible by using  $XeF_2$  [80] (xenon difluoride) or a mixture of interhalogen gases (such as BrF<sub>3</sub>), which provide very high selectivities for aluminum, silicon dioxide, photoresist and other masking materials used during etching. Examples of bulk micromachining can be seen in figure 1.13.

Figure 1.13. Examples of silicon bulk micromachining; the substrate material is etched away to create different features [81].

# 1.4.2 Surface Micromachining

Surface micromachining, unlike bulk micromachining where features are inside the substrate, is based on the deposition and etching of different structural layers on top of the substrate (bottom-up processing). Because the process does not depend on the etching characteristic of the substrate, different materials such as soda lime, silicon on insulator and metals are sometimes used in this process.

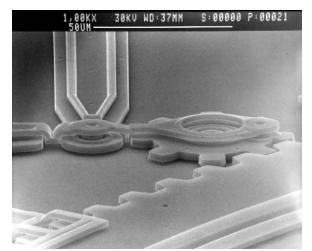

During surface micromachining process, the layers deposited may be metal, oxide, polymer or other process compatible materials. These layers are selectively etched by photolithography with a mask by either a wet etch involving an acid or a dry etch involving an ionized gas or plasma. When a suspended structure is necessary, sacrificial layers are used (figure 1.14). These sacrificial materials must have process-compatible properties such as good adhesion to substrate or low residual stress, to avoid failure during fabrications. Common sacrificial materials are photoresist, polyimide, metals, phosphosilicate glass (PSG) and polysilicon.

Figure 1.14. An example of surface micromachined gears [82].