# Silicon Integrated Optics: Fabrication and Characterization

Thesis by Michael Joseph Shearn II

In Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

California Institute of Technology Pasadena, California 2010

(Defended May 20, 2010)

© 2010 Michael Joseph Shearn II All Rights Reserved

#### Acknowledgements

Thanks to my advisor, Axel Scherer. Your help, support, and understanding throughout my graduate career has been exceeded only by your kindness.

Thanks to all the Scherer group members: Aditya Rajagopal, Andrew Homyk, Chris Walker, David Henry, Imran Malik, Jingqing Huang, Sameer Walavalkar, Uday Khankhoje, Saurabh Vyawahare, Se-Heon Kim, Zhenyu Li, Joyce Wong, and Kate Finigan. You have maybe the task lighter with your knowledge and insight along with your fellowship.

Thanks to all my collaborators and colleagues: Xiankai Sun, Avi Zadok, Ryan Briggs, Ken Diest, Ali Ghaffari, Marina Leite, Chris Michael, Thomas Johnson, Christos Santis, Scott Steger, Oskar Painter, Amnon Yariv, and Harry Atwater. Working with you has been a privilege and a joy.

Thanks to my most frequent coursework companions: Chris Michael, Gerald Miller, Auna Moser, Brian Standley, David Henry, and Sameer Walavalkar. You have taught me so much and spared me many blind alleys.

Thanks all of my teachers and mentors, especially James Walker, Harish Manohara, Rob Phillips, Geoffrey Orsak, Ben Thomas, Kent Hornbostel, Beverly McCarthy, and Ray Gonzales. Learning from you has been a great adventure and continues to be a source of inspiration.

Thanks to all the organizations that have supported my journey in higher education: the National Science Foundation, the Department of Homeland Security, and the President's Scholars Program at SMU.

Thanks to all my friends, especially Anna Beck, Tony Roy, Andy Downard, Matt Eichenfield, Valerie Scott, Will Ford, Lenny Lucas, Eric Brown, Matt Wahlrab, Matthew Longstaff, Aaron Nall, Ryan Jenkins, Roger Kort, and Evan Grim. You have enriched my life and made graduate school fun.

Thank you, Mom, Dad and Paige, for everything.

#### Abstract

For decades, the microelectronics industry has sought integration and miniaturization as canonized in Moore's Law, and has continued doubling transistor density about every two years. However, further miniaturization of circuit elements is creating a bandwidth problem as chip interconnect wires shrink as well. A potential solution is the creation of an on-chip optical network with low delays that would be impossible to achieve using metal buses. However, this technology requires integrating optics with silicon microelectronics. The lack of efficient silicon optical sources has stymied efforts of an all-Si optical platform. Instead, the integration of efficient emitter materials, such as III-V semiconductors, with Si photonic structures is a low-cost, CMOS-compatible alternative platform.

This thesis focuses on making and measuring on-chip photonic structures suitable for on-chip optical networking. The first part of the thesis assesses processing techniques of silicon and other semiconductor materials. Plasmas for etching and surface modification are described and used to make bonded, hybrid Si/III-V structures. Additionally, a novel masking method using gallium implantation into silicon for pattern definition is characterized. The second part of the thesis focuses on demonstrations of fabricated optical structures. A dense array of silicon devices is measured, consisting of fully-etched grating couplers, low-loss waveguides and ring resonators. Finally, recent progress in the Si/III-V hybrid system is discussed. Supermode control of devices is described, which uses changing Si waveguide width to control modal overlap with the gain material. Hybrid Si/III-V, Fabry-Perot evanescent lasers are demonstrated, utilizing a CMOS-compatible process suitable for integration on in electronics platforms. Future prospects and ultimate limits of Si devices and the hybrid Si/III-V system are also considered.

### Contents

| Li | List of Figures |         |                                     |    |  |

|----|-----------------|---------|-------------------------------------|----|--|

| Li | List of Tables  |         |                                     |    |  |

| 1  | Intr            | oduct   | ion                                 | 1  |  |

|    | 1.1             | Scope   | of this thesis                      | 2  |  |

|    | 1.2             | Silicon | n Photonics                         | 3  |  |

|    |                 | 1.2.1   | Simulation of Electromagnetic Modes | 3  |  |

|    |                 | 1.2.2   | Photonic Structure Characteristics  | 5  |  |

| 2  | Plas            | sma E   | tching and Wafer Bonding Techniques | 7  |  |

|    | 2.1             | Introd  | luction                             | 7  |  |

|    | 2.2             | Plasm   | nas in Electronics Processing       | 7  |  |

|    |                 | 2.2.1   | Figures of Merit                    | 8  |  |

|    |                 | 2.2.2   | Plasma Characteristics              | 9  |  |

|    |                 | 2.2.3   | Processing Parameters               | 11 |  |

|    |                 | 2.2.4   | Etch Reaction Dynamics              | 12 |  |

|    |                 | 2.2.5   | Time-Dependent Processes            | 13 |  |

|    |                 | 2.2.6   | Summary                             | 14 |  |

|    | 2.3             | Deep    | Silicon Etching                     | 14 |  |

|    |                 | 2.3.1   | Gas Chemistries                     | 14 |  |

|    |                 | 2.3.2   | Mask Selection                      | 16 |  |

|    |                 | 2.3.3   | ICP Power                           | 17 |  |

|   |                                 | 2.3.4                                                                                                      | CCP Power                                                                                                                                                                                                                                                                                                                     | 18                                                                         |

|---|---------------------------------|------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

|   |                                 | 2.3.5                                                                                                      | Pattern Dependence and Chamber Hysteresis                                                                                                                                                                                                                                                                                     | 19                                                                         |

|   | 2.4                             | Nanos                                                                                                      | cale Silicon Etching                                                                                                                                                                                                                                                                                                          | 19                                                                         |

|   |                                 | 2.4.1                                                                                                      | Gas Chemistries                                                                                                                                                                                                                                                                                                               | 20                                                                         |

|   |                                 | 2.4.2                                                                                                      | Mask Selection                                                                                                                                                                                                                                                                                                                | 20                                                                         |

|   |                                 | 2.4.3                                                                                                      | Etching Conditions and Optimization                                                                                                                                                                                                                                                                                           | 21                                                                         |

|   | 2.5                             | Nanos                                                                                                      | cale Indium Phosphide Etching                                                                                                                                                                                                                                                                                                 | 21                                                                         |

|   |                                 | 2.5.1                                                                                                      | Gas Chemistries                                                                                                                                                                                                                                                                                                               | 22                                                                         |

|   |                                 | 2.5.2                                                                                                      | Mask Selection                                                                                                                                                                                                                                                                                                                | 22                                                                         |

|   |                                 | 2.5.3                                                                                                      | Etching Conditions and Optimization                                                                                                                                                                                                                                                                                           | 24                                                                         |

|   | 2.6                             | Plasm                                                                                                      | a-Assisted Wafer Bonding                                                                                                                                                                                                                                                                                                      | 25                                                                         |

|   |                                 | 2.6.1                                                                                                      | Direct Wafer Bonding                                                                                                                                                                                                                                                                                                          | 25                                                                         |

|   |                                 | 2.6.2                                                                                                      | Bonding Procedure                                                                                                                                                                                                                                                                                                             | 27                                                                         |

|   | 2.7                             | Conclu                                                                                                     | usion                                                                                                                                                                                                                                                                                                                         | 27                                                                         |

|   |                                 |                                                                                                            |                                                                                                                                                                                                                                                                                                                               |                                                                            |

| 3 | Ca                              | Roam                                                                                                       | Lithography for Silicon Nanostructures                                                                                                                                                                                                                                                                                        | 20                                                                         |

| 3 |                                 |                                                                                                            | Lithography for Silicon Nanostructures                                                                                                                                                                                                                                                                                        | 29                                                                         |

| 3 | 3.1                             | Introd                                                                                                     | uction                                                                                                                                                                                                                                                                                                                        | 29                                                                         |

| 3 | 3.1<br>3.2                      | Introd                                                                                                     | vations of Ga masking                                                                                                                                                                                                                                                                                                         | 29<br>30                                                                   |

| 3 | 3.1<br>3.2<br>3.3               | Introd<br>Obser<br>Mask                                                                                    | vations of Ga masking                                                                                                                                                                                                                                                                                                         | 29<br>30<br>31                                                             |

| 3 | 3.1<br>3.2                      | Introd<br>Obser<br>Mask<br>Pseud                                                                           | vations of Ga masking                                                                                                                                                                                                                                                                                                         | 29<br>30<br>31<br>33                                                       |

| 3 | 3.1<br>3.2<br>3.3               | Obser<br>Mask<br>Pseud<br>3.4.1                                                                            | vations of Ga masking                                                                                                                                                                                                                                                                                                         | 29<br>30<br>31<br>33<br>34                                                 |

| 3 | 3.1<br>3.2<br>3.3<br>3.4        | Introd<br>Obser<br>Mask<br>Pseud<br>3.4.1<br>3.4.2                                                         | Patterning Using FIB  obosch Silicon Etching  Determination of Threshold Dose and Selectivity  Determination of Minimum Feature Size                                                                                                                                                                                          | 29<br>30<br>31<br>33<br>34<br>37                                           |

| 3 | 3.1<br>3.2<br>3.3               | Introd<br>Obser<br>Mask<br>Pseud<br>3.4.1<br>3.4.2<br>Cryog                                                | Patterning Using FIB  obosch Silicon Etching  Determination of Threshold Dose and Selectivity  Determination of Minimum Feature Size  enic Silicon Etching                                                                                                                                                                    | 29<br>30<br>31<br>33<br>34<br>37<br>38                                     |

| 3 | 3.1<br>3.2<br>3.3<br>3.4<br>3.5 | Introd<br>Obser<br>Mask<br>Pseud<br>3.4.1<br>3.4.2<br>Cryog<br>3.5.1                                       | Patterning Using FIB  obosch Silicon Etching  Determination of Threshold Dose and Selectivity  Determination of Minimum Feature Size  enic Silicon Etching  Determination of Threshold Dose and Selectivity                                                                                                                   | 29<br>30<br>31<br>33<br>34<br>37<br>38                                     |

| 3 | 3.1<br>3.2<br>3.3<br>3.4        | Introd<br>Obser<br>Mask<br>Pseud<br>3.4.1<br>3.4.2<br>Cryog<br>3.5.1<br>Multil                             | vations of Ga masking                                                                                                                                                                                                                                                                                                         | 29<br>30<br>31<br>33<br>34<br>37<br>38<br>39<br>40                         |

| 3 | 3.1<br>3.2<br>3.3<br>3.4<br>3.5 | Introd<br>Obser<br>Mask<br>Pseud<br>3.4.1<br>3.4.2<br>Cryog<br>3.5.1<br>Multil<br>3.6.1                    | vations of Ga masking  Patterning Using FIB  obosch Silicon Etching  Determination of Threshold Dose and Selectivity  Determination of Minimum Feature Size  enic Silicon Etching  Determination of Threshold Dose and Selectivity  well and Grayscale Etch Masking  Multilevel Masking                                       | 29<br>30<br>31<br>33<br>34<br>37<br>38<br>39<br>40<br>40                   |

| 3 | 3.1<br>3.2<br>3.3<br>3.4<br>3.5 | Introd<br>Obser<br>Mask<br>Pseud<br>3.4.1<br>3.4.2<br>Cryog<br>3.5.1<br>Multil<br>3.6.1<br>3.6.2           | vations of Ga masking  Patterning Using FIB  obosch Silicon Etching  Determination of Threshold Dose and Selectivity  Determination of Minimum Feature Size  enic Silicon Etching  Determination of Threshold Dose and Selectivity  evel and Grayscale Etch Masking  Multilevel Masking  Grayscale Masking  Grayscale Masking | 29<br>30<br>31<br>33<br>34<br>37<br>38<br>39<br>40<br>40<br>42             |

| 3 | 3.1<br>3.2<br>3.3<br>3.4<br>3.5 | Introd<br>Obser<br>Mask<br>Pseud<br>3.4.1<br>3.4.2<br>Cryog<br>3.5.1<br>Multil<br>3.6.1<br>3.6.2<br>Resolu | vations of Ga masking                                                                                                                                                                                                                                                                                                         | 29<br>30<br>31<br>33<br>34<br>37<br>38<br>39<br>40<br>40<br>42<br>43       |

| 3 | 3.1<br>3.2<br>3.3<br>3.4<br>3.5 | Introd<br>Obser<br>Mask<br>Pseud<br>3.4.1<br>3.4.2<br>Cryog<br>3.5.1<br>Multil<br>3.6.1<br>3.6.2           | vations of Ga masking  Patterning Using FIB  obosch Silicon Etching  Determination of Threshold Dose and Selectivity  Determination of Minimum Feature Size  enic Silicon Etching  Determination of Threshold Dose and Selectivity  evel and Grayscale Etch Masking  Multilevel Masking  Grayscale Masking  Grayscale Masking | 29<br>30<br>31<br>33<br>34<br>37<br>38<br>39<br>40<br>40<br>42<br>43<br>43 |

|   |     | 3.7.3   | Possible Origin of the threshold dose                      | 45 |

|---|-----|---------|------------------------------------------------------------|----|

|   | 3.8 | Suitab  | oility of Ga lithography for photonics                     | 46 |

|   | 3.9 | Concl   | usion                                                      | 47 |

| 4 | Cha | ıracter | ization of Silicon Waveguides and Resonators using Grat-   |    |

|   | ing | Coupl   | ers                                                        | 49 |

|   | 4.1 | Introd  | luction                                                    | 49 |

|   | 4.2 | Fabric  | eation                                                     | 49 |

|   | 4.3 | Gratin  | ng Couplers                                                | 53 |

|   |     | 4.3.1   | Grating Transmission                                       | 54 |

|   |     | 4.3.2   | Grating Reflectivity                                       | 57 |

|   |     | 4.3.3   | Grating Summary                                            | 58 |

|   | 4.4 | Ring l  | Resonators                                                 | 58 |

|   |     | 4.4.1   | Determining Q                                              | 59 |

|   | 4.5 | Summ    | nary                                                       | 61 |

| 5 | Hyl | orid Si | licon Devices                                              | 63 |

|   | 5.1 | Introd  | luction                                                    | 63 |

|   | 5.2 | Super   | mode Device Geometry                                       | 63 |

|   | 5.3 | Fabric  | eation                                                     | 64 |

|   |     | 5.3.1   | Pattern Definition                                         | 64 |

|   |     | 5.3.2   | Si Waveguides                                              | 65 |

|   |     | 5.3.3   | Bonding                                                    | 66 |

|   |     | 5.3.4   | InGaAsP Waveguides                                         | 66 |

|   |     | 5.3.5   | Planarization                                              | 67 |

|   |     | 5.3.6   | Contacts and Wet Etching                                   | 69 |

|   | 5.4 | Measu   | rements                                                    | 71 |

|   |     | 5.4.1   | Electrically pumped evanescent hybrid lasers               | 71 |

|   |     | 5.4.2   | Comparison of supermode hybrid lasers to evanescent hybrid |    |

|   |     |         |                                                            |    |

|   |     |         | lasers                                                     | 72 |

| A  | Fab          | ricatio | n Recipes                                                             | <b>7</b> 5 |

|----|--------------|---------|-----------------------------------------------------------------------|------------|

|    | A.1          | Resist  | and Planarization                                                     | 75         |

|    |              | A.1.1   | ZEP-520A Resist Process                                               | 75         |

|    |              | A.1.2   | Shipley 1813 Resist Process                                           | 75         |

|    |              | A.1.3   | AZ 5214 Resist Process                                                | 76         |

|    |              | A.1.4   | nLOF 2070 Resist Process                                              | 76         |

|    |              | A.1.5   | Bilayer PMMA Resist Process                                           | 77         |

|    |              | A.1.6   | PI-2562 Planarization Process                                         | 77         |

|    | A.2          | Plasm   | a Etching                                                             | 77         |

|    |              | A.2.1   | Pulse-mode ${\rm SF_6/C_4F_8}$ etch for silicon (Bosch process)       | 77         |

|    |              | A.2.2   | Mixed-mode ${\rm SF_6/C_4F_8}$ etch for silicon (Pseudobosch)         | 78         |

|    |              | A.2.3   | Cryogenic $SF_6/O_2$ etch for silicon                                 | 78         |

|    |              | A.2.4   | Mixed-mode $\mathrm{CH_4/H_2/Cl_2}$ etch for InP/InGaAsP materials $$ | 79         |

|    |              | A.2.5   | Polyimide Etch                                                        | 80         |

|    |              | A.2.6   | Oxygen Plasma Activation                                              | 80         |

|    |              | A.2.7   | Typical Etch Chemistries                                              | 80         |

|    | A.3          | Wet E   | tching                                                                | 81         |

|    |              | A.3.1   | Piranha clean for surface passivation/bonding                         | 81         |

|    |              | A.3.2   | KOH and HCl etching for Si/Indium                                     | 81         |

| В  | L-E          | dit Co  | de for Layout Generation                                              | 83         |

| Bi | Bibliography |         |                                                                       | 97         |

# List of Figures

| 1.1 | Plot of the electric field intensity profile $ E_x ^2$ of a 220 nm $\times$ 500 nm |    |

|-----|------------------------------------------------------------------------------------|----|

|     | Si waveguide on SiO <sub>2</sub> , showing the fundamental TE mode, calculated     |    |

|     | by FEM simulation in COMSOL                                                        | 5  |

| 2.1 | ICP-RIE chamber geometry                                                           | 10 |

| 2.2 | Ion angular and ion energy distribution functions                                  | 12 |

| 2.3 | Comparison of the Bosch process to cryogenic silicon etching                       | 15 |

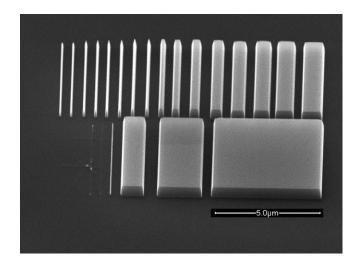

| 2.4 | Pseudobosch etch of a Ga etch mask                                                 | 21 |

| 2.5 | Micromasking during InP etching                                                    | 23 |

| 2.6 | InP Etching with an Au hardmask                                                    | 23 |

| 2.7 | Gallium-implanted etch mask                                                        | 24 |

| 2.8 | InGaAsP film on SOI wafer                                                          | 26 |

| 3.1 | Ga simulated implantation depth                                                    | 32 |

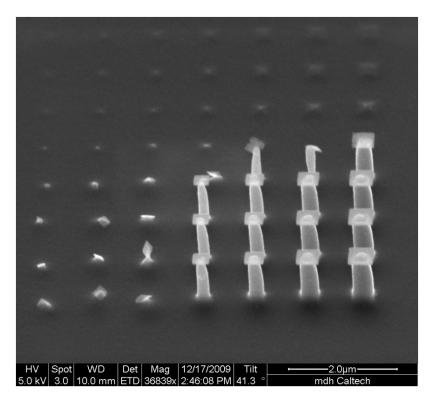

| 3.2 | SEM image of a Ga implanted dose array using ${\rm SF}_6/{\rm C}_4{\rm F}_8$ etch  | 34 |

| 3.3 | Etch depth performance of Ga dose array                                            | 35 |

| 3.4 | SEM image of a silicon nanopillar, 72 nm in diameter and 800 nm tall.              | 36 |

| 3.5 | SEM image of second dose array for nanoscale ${\rm SF_6/C_4F_8}$ etch              | 37 |

| 3.6 | SEM image of third dose array for nanoscale ${\rm SF}_6/{\rm C}_4{\rm F}_8$ etch   | 38 |

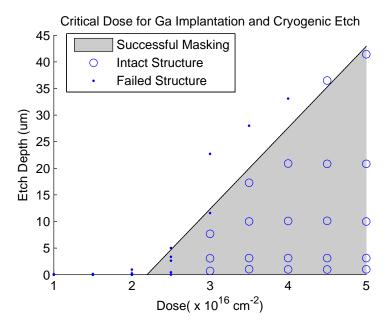

| 3.7 | Critical Ga dose for the Cryogenic etch                                            | 40 |

| 3.8 | SEM image of Ga masked silicon squares with mask undercut associ-                  |    |

|     | ated with cryogenic etching.                                                       | 41 |

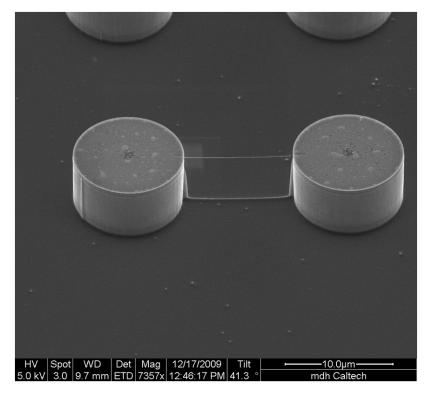

| 3.9  | SEM image of 10 µm diameter silicon with an 80 by 20 nm suspended              |    |

|------|--------------------------------------------------------------------------------|----|

|      | silicon nanowire.                                                              | 42 |

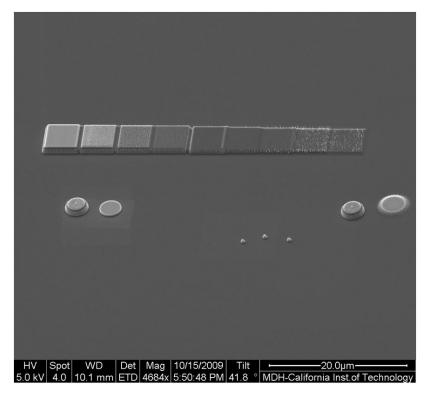

| 3.10 | SEM image of 5 $\mu m$ squares with varied doses                               | 43 |

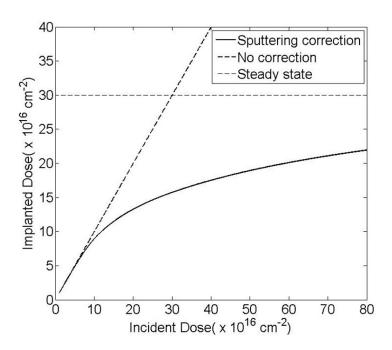

| 3.11 | Plot of implanted dose as a function of incident dose                          | 45 |

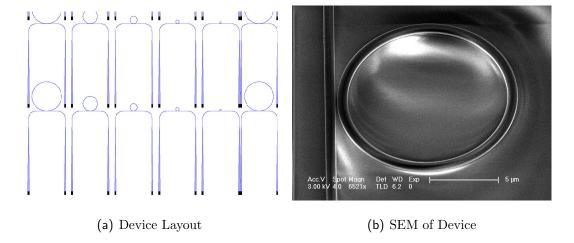

| 4.1  | Typical Si ring-bus geometry. (a) Detail of ring resonator test devices        |    |

|      | consisting of a bus waveguide, ring resonator, and grating couplers.           |    |

|      | Largest ring is 200 $\mu m$ in diameter. (b) Si ring-bus geometry after        |    |

|      | reflow and etching. Despite pattern swelling due to reflow, coupling           |    |

|      | gaps below 100nm are still possible                                            | 50 |

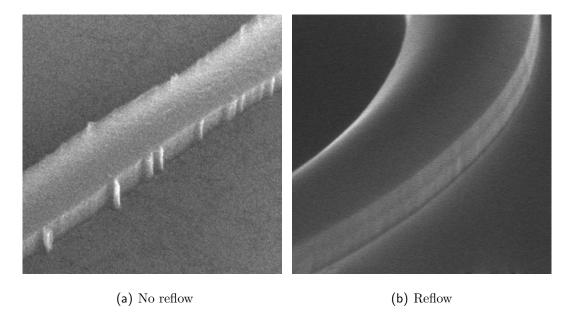

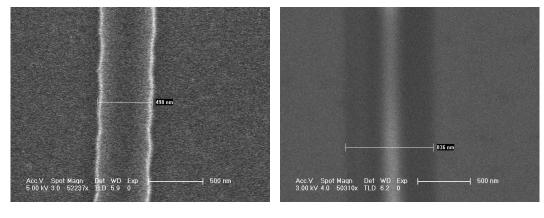

| 4.2  | Reflow smoothing of an Si waveguide                                            | 51 |

| 4.3  | Pattern swelling due to reflow                                                 | 52 |

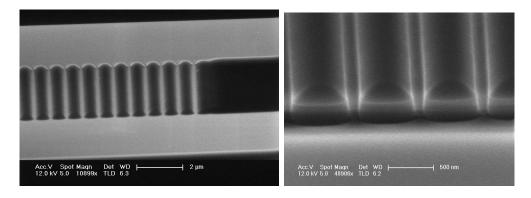

| 4.4  | Reflow smoothing of a grating coupler                                          | 52 |

| 4.5  | Grating Coupler Schematic                                                      | 54 |

| 4.6  | Bus waveguide transmission spectra.                                            | 55 |

| 4.7  | Bus waveguide transmission spectra                                             | 56 |

| 4.8  | Combined Ring-bus waveguide transmission spectra                               | 59 |

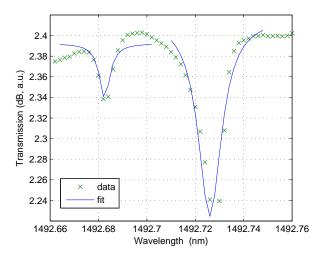

| 4.9  | Example of $Q$ fit to the noisy data                                           | 60 |

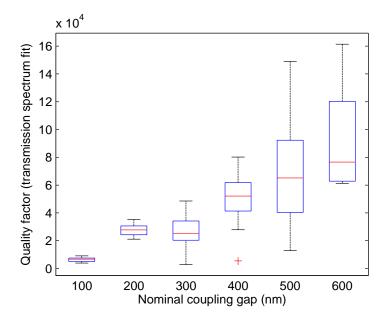

| 4.10 | Ring resonator loaded quality factor for various coupling gaps                 | 60 |

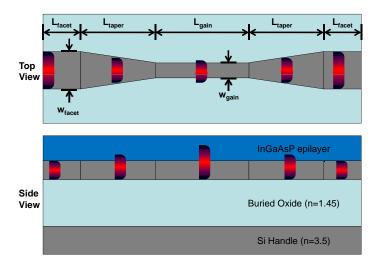

| 5.1  | Schematic of supermode evolution                                               | 64 |

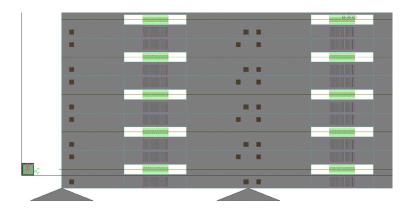

| 5.2  | Portion of a typical a $2 \times 5$ array of devices. Cleave marks (triangles) |    |

|      | on the Si layer separate individual copies of each device, while different     |    |

|      | parameters are changed in the orthogonal direction                             | 65 |

| 5.3  | Isometric view of the cleaved facet of a fully etched Si Waveguide. A          |    |

|      | small foot is visible at the edge of the waveguide due to a slightly slower    |    |

|      | etch rate at that sidewalls.                                                   | 66 |

| 5.4  | View along etched sidewall of III-V waveguide. The spikes in the metal         |    |

|      | mask are caused by partial mask failure during the etch.                       | 67 |

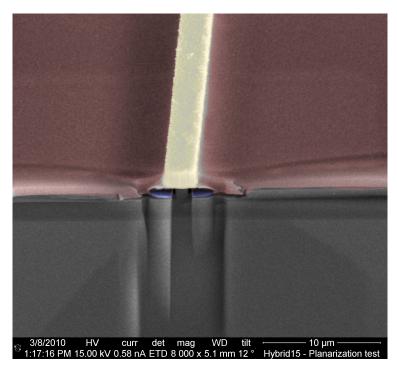

| 5.5 | Cross sectional view of planarization of a hybrid waveguide. The con-   |    |

|-----|-------------------------------------------------------------------------|----|

|     | tact (gold), PI-2562 (red), and failed 110 nm n-InP layer (blue) are    |    |

|     | visible on the SOI substrate (uncolored).                               | 68 |

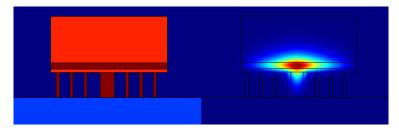

| 5.6 | FEM simulation of a mechanical support structure for the III-V mem-     |    |

|     | brane. The mode is not influenced by the adjacent narrow silicon veins. | 69 |

| 5.7 | InGaAsP film on SOI wafer                                               | 70 |

| 5.8 | L-I-V curve and spectrum of a 960- $\mu$ m-long laser operating in CW   |    |

|     | mode at 15 °C. Courtesy of Xiankai Sun                                  | 71 |

## List of Tables

| 3.1 | Recipes for the two dose array etches. Changed parameters shown in   |    |

|-----|----------------------------------------------------------------------|----|

|     | bold                                                                 | 33 |

| 3.2 | Recipes for the cryogenic dose array etches. Changed parameters      |    |

|     | shown in bold                                                        | 39 |

| 4.1 | Summary of grating coupler performance                               | 58 |

| 5.1 | InGaAsP Wafer Epilayer Structure                                     | 70 |

| 5.2 | Test results of supermode and evanescent lasers. Courtesy of Xiankai |    |

|     | Sun                                                                  | 72 |

#### Chapter 1

#### Introduction

Few materials are as integral to modern society as silicon. It is difficult to imagine microelectronics without the crystalline silicon wafer, or telecommunications without silicon dioxide optical fibers. While silicon is widely used in both industries, the driving forces in each have been very different. The microelectronics industry has sought integration and miniaturization as canonized in Moore's Law [1], and has continued doubling transistor density about every two years. The telecommunications industry has not had the same versatile platform of the silicon chip; instead, it has developed a variety of materials and technologies to achieve long-range, high-bandwidth data transmission. Today, both industries are facing problems to their further development that are a direct product of these development methodologies. In microelectronics, the further miniaturization of circuit elements is creating a bandwidth problem as chip interconnect wires are forced to shrink as well. The problem arises from the increased RC time constant for charging or discharging the line, which is quickly becoming a limiting factor in chip design. For example, at the 1 µm technology node, the switching delay of a MOSFET was 20 times longer than the RC delay of the benchmark 1.0-mm-long Al interconnect (20 ps to 1 ps). However, by the 100 nm technology node, the situation has completely reversed; MOSFETs are 100 times faster than the same generation interconnects (2.5 ps to 250 ps) [3]. This problem will continue to get worse as interconnects are shrunk with each smaller technology node, and may eventually prevent further miniaturization due to excessive power dissipation [4]. In telecommunications, the lack of a unified optical platform has kept

<sup>&</sup>lt;sup>1</sup>The RC time constant scales roughly as  $K^2$ , where K is the scaling factor (linear dimensions shrink by  $\frac{1}{K}$ ). For a full discussion of this scaling, see the chapter by Gaburro[2]

cost per component high and limited growth. These seemingly disparate problems can be addressed by integrating optics with silicon microelectronics. A silicon photonic chip would solve the interconnect bandwidth problem by using optical buses with low delays that would be impossible to achieve using metal buses. Likewise, the same technology used for these buses enables an integrated optical transceiver, extending the same economies of scale to formerly expensive multi-component systems [5].

#### 1.1 Scope of this thesis

Before discussing experimental results in detail, it is important to understand one of the key processing tools used to fabricate these devices: the inductively coupled plasma reactive ion etcher (ICP-RIE). Plasma processing techniques are integral to modern semiconductor fabrication because of their high radical density, high selectivity, and anisotropic etch profiles at low temperatures and mild voltages. This gentle processing environment prevents unwanted diffusion and degradation of materials due to heat and lattice damage from ion bombardment. Plasma treatments have a minimal effect on existing wafer structure, which is a key requirement for large scale integration schemes such as CMOS, such as those discussed in Chapter 5. In this chapter, we will cover the applications of plasmas to etching and bonding materials appropriate for photonic integration, which rely on ICP-RIE capabilities.

Chapter 2 describes plasma applications of etching and surface modification to semiconductor materials, with special attention to processing techniques suitible for low-loss photonic structures and wafer bonding.

Chapter 3 examines a novel masking method using gallium implantation into silicon for pattern definition, characterizing the processing and discussing possible applications of the technique.

Chapter 4 describes compact silicon devices fabricated on 220nm/2um SOI, analyzing a fully-etched grating coupler for interfacing with optical fiber, low-loss waveguides and ring resonators. Characterization of the grating coupler and cavity quality factor (Q) are determined using an automated test system.

Chapter 5 discusses recent progress in the Si/III-V hybrid system, which was performed with members of the Atwater and Yariv groups. Supermode control of devices is described, which uses changing Si waveguide width to control modal overlap with the gain material. Hybrid Si/III-V, Fabry-Perot evanescent lasers are demonstrated, utilizing InGaAsP gain material. Finally, promising results of the supermode lasers over evanscent lasers are presented.

#### 1.2 Silicon Photonics

Before we discuss fabrication techniques for making optical structures, we will introduce the basic concepts and some useful relationships used later in the thesis. More comprehensive treatments are found in several books and theses on the subject [6, 7, 8].

#### 1.2.1 Simulation of Electromagnetic Modes

While many semianalytic methods [9, 10, 11] exist for determining the distribution of electromagnetic energy in dielectric structures, numerical methods for determining the fields are frequently needed to account for the complexity of realistic waveguide designs. To that end, recasting Maxwell's equations in a form amenable to numerical simulation is possible. We start with Maxwell's equations in the absence of free charge or currents:

$$\nabla \cdot \mathbf{D} = 0 \tag{1.1}$$

$$\nabla \cdot \mathbf{B} = 0 \tag{1.2}$$

$$\nabla \times \mathbf{E} = -\frac{\partial \mathbf{B}}{\partial t} \tag{1.3}$$

$$\nabla \times \mathbf{H} = \frac{\partial \mathbf{D}}{\partial t},\tag{1.4}$$

with constitutive relations  $\mathbf{D} = \epsilon \mathbf{E}$  and  $\mathbf{B} = \mu_0 \mathbf{H}$ . Combining the constitutive relations with equations 1.3 and 1.4 yields:

$$\nabla \times \mathbf{E} + \mu \frac{\partial \mathbf{H}}{\partial t} = 0 \tag{1.5}$$

$$\nabla \times \mathbf{H} - \epsilon \frac{\partial \mathbf{E}}{\partial t} = 0. \tag{1.6}$$

Now, if we separate the time and express the fields in the time-harmonic basis

$$\mathbf{E}(\mathbf{r},t) = \mathbf{E}(\mathbf{r})e^{i\omega t} \tag{1.7}$$

$$\mathbf{H}(\mathbf{r},t) = \mathbf{H}(\mathbf{r})e^{i\omega t},\tag{1.8}$$

we can rewrite equations 1.5 and 1.6 as an eigenvalue problem for  $\mathbf{E}(\mathbf{r})$  or  $\mathbf{H}(\mathbf{r})$ :

$$\nabla \times \left(\frac{1}{\mu} \nabla \times \mathbf{E}(\mathbf{r})\right) = \omega^2 \epsilon \mathbf{E}(\mathbf{r}) \tag{1.9}$$

$$\nabla \times \left(\frac{1}{\epsilon} \nabla \times \mathbf{H}(\mathbf{r})\right) = \omega^2 \mu \mathbf{H}(\mathbf{r}). \tag{1.10}$$

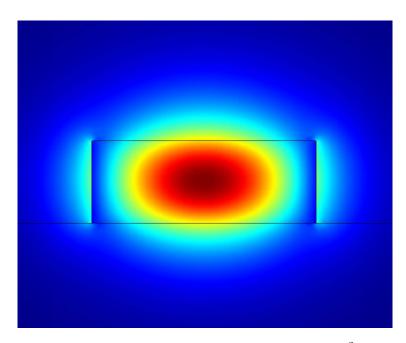

These forms of Maxwell's equations are frequently used in the finite element method (FEM) [12]. An example of an FEM simulation is shown in figure 1.1, which shows the waveguide structure discussed in Chapter 4. Simulation of these structures allows us to quickly determine salient characteristics of the given dielectric structure, and ensures that we do not approximate away any important details of the structure.

Figure 1.1. Plot of the electric field intensity profile  $|E_x|^2$  of a 220 nm  $\times$  500 nm Si waveguide on SiO<sub>2</sub>, showing the fundamental TE mode, calculated by FEM simulation in COMSOL

#### 1.2.2 Photonic Structure Characteristics

A frequently quoted figure of merit is the quality factor, Q, which is defined by [6]:

$$Q \equiv 2\pi \frac{\text{stored energy}}{\text{energy loss per cycle}}$$

$$= 2\pi \left(\frac{\text{cycles}}{\text{second}}\right) \cdot \frac{\text{stored energy}}{\text{energy loss per second}}$$

$$= \omega \frac{U_{stored}}{P_{loss}}$$

$$= \frac{\nu}{\delta \nu}$$

(1.11)

Equation 1.11 is useful when running simulations of electromagnetic modes, where  $U_{stored}$  and  $P_{loss}$  can be calculated directly. In an experimental context, equation 1.12 is more useful since both terms can be determined directly from a transmission measurement. Frequently, measurements are taken with respect to wavelength rather than frequency; using  $c = \nu \lambda$ , we can rewrite  $\Delta \nu$  as

$$\delta\nu = \frac{c}{\lambda_1} - \frac{c}{\lambda_2} \approx \frac{c\delta\lambda}{\lambda^2}, \lambda \equiv \frac{\lambda_1 + \lambda_2}{2}$$

(1.13)

and thus equation 1.12 becomes

$$Q = \frac{\nu}{\delta\nu}$$

$$\approx \frac{c}{\lambda} \cdot \frac{\lambda^2}{c\delta\lambda}$$

$$= \frac{\lambda}{\delta\lambda}.$$

(1.14)

This approximation holds for  $Q\gg 1.$

Finally, in Chapter 5, we will look at maximizing the gain in a hybrid system. In order to do this, it is important to maximize the confinement factor,  $\Gamma$ , in the gain region. This is the fraction of the mode that exists in the gain material, and can be calculated with the FEM using

$$\Gamma = \frac{\int_{dV} n^2(\mathbf{r}) |\mathbf{E}(\mathbf{r})|^2 dV}{\int_V n^2(\mathbf{r}) |\mathbf{E}(\mathbf{r})|^2 dV}$$

(1.15)

where dV is taken over the gain region. This can be used to understand trends in other laser performance characteristics like the threshold voltage and current.

#### Chapter 2

# Plasma Etching and Wafer Bonding Techniques

#### 2.1 Introduction

Before discussing experimental results in detail, it is important to understand one of the key processing tools used to fabricate these devices: the inductively coupled plasma reactive ion etcher (ICP-RIE). Plasma processing techniques are integral to modern semiconductor fabrication because of their high radical density, high selectivity, and anisotropic etch profiles at low temperatures and mild voltages. This gentle processing environment prevents unwanted diffusion and degradation of materials due to heat and lattice damage from ion bombardment. Plasma treatments have a minimal effect on existing wafer structure, which is a key requirement for large scale integration schemes such as CMOS, such as those discussed in Chapter 5. In this chapter, we will cover the applications of plasmas to etching and bonding materials appropriate for photonic integration, which rely on ICP-RIE capabilities. <sup>1</sup>

#### 2.2 Plasmas in Electronics Processing

Plasmas are found in a wide range of industrial applications, including ashing, sputtering, etching, and chemical vapor deposition. However, the types of plasmas used in each process vary greatly. In this section, we will describe the important parame-

<sup>&</sup>lt;sup>1</sup>Portions of this chapter are adapted from a publication with M. David Henry and Xiankai Sun [13].

ters of plasmas for understanding ICP-RIE etching and deposition, and establish how they relate to our desired processing results.

#### 2.2.1 Figures of Merit

Central to semiconductor processing is the high fidelity transfer of a pattern onto a substrate through addition, modification, or removal of material. In order to quantify the ability to accomplish this selective processing, it is useful to have a few figures of merit to describe the process, namely:

- Etch rate controllable and robust to small deviation in processing conditions.

Depending on the application, one may want a higher etch rate for increased throughput or a lower etch rate for precision.

- Uniformity both at each feature and across the wafer

- Selectivity the ability to etch only the desired material, relative to the etching of mask and other substrate materials

- Anisotropy The verticality of the etch profile. Also, the nanostructure of this vertical surface is important in many applications, particularly waveguides.

- Damage Any surface or substrate damage acquired from the processing technique.

In addition, the environment in which the process occurs is important. Some conditions will have a deleterious effect on existing wafer structure. Chief among these is the temperature of processing. Heating (and cooling) can cause many problems, including thin film delamination due to thermal expansion coefficient mismatch, unwanted dopant diffusion, and other negative effects [14]. In the CMOS industry, the wafers tolerance to temperature fluctuations is often captured as a thermal budget [15], which means that minimizing use during one process step can give more latitude in other steps.

#### 2.2.2 Plasma Characteristics

Plasma is a partially ionized gas with a combination of free electrons, ions, radicals, and neutral species. To create and sustain a plasma in the laboratory, it requires some energy input. Different coupling methods generate plasmas of different characteristics. Most useful to RIE are those generated by glow discharge plasmas (GDP), capacitive coupled plasma (CCP), inductively coupled plasma (ICP), or some combination thereof.

In a GDP process, electromagnetic energy is delivered as a voltage applied between two conducting plates, known as the cathode and the anode. The applied voltage is usually DC or in the low frequency regime, such that the characteristic time of field variation is longer than the response time of the system. The voltage generates an electric field across the gases in the chamber. Plasma initiation occurs when a small initial population of charged species is accelerated through the electric field and collides with other molecules, causing them to ionize. A relatively high voltage is required to initiate and sustain the plasma, which is a severe processing drawback. High voltage will cause the resultant energy of incident ions on the cathode to be high, favoring rough, physical processes (sputtering) over smooth, chemical processes (surface reactions). This will lower the selectivity to masking materials and cause sidewall roughening due to mask erosion. For these reasons, GDP sources are often used to sputter materials rather than etch anisotropically [16].

In a CCP process, energy is again supplied as a voltage across an anode and a cathode plate, but in a time-varying fashion. An RF voltage is applied to the plates at a frequency of 13.56 MHz. In this time-varying field, electrons in the plasma tend to oscillate, traveling between the anode and the cathode plates. Collisions of rapidly moving electrons with the slowly moving ions cause further ionizations. However, massive ions are less mobile and cannot track the rapidly oscillating electric field changes. By placing a capacitor between the anode plate and the RF supply, negative charge accumulates on the plate (typically referred to as the table). The resulting potential difference between the plasma and the negatively charged plate is

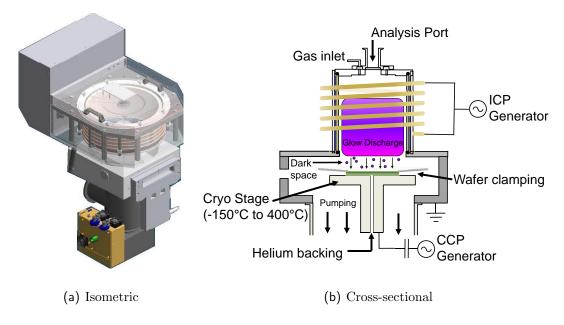

Figure 2.1. Views of an Oxford Instruments ICP-RIE.

called the self-bias  $V_b$ . The electric field due to  $V_b$  drives the positive ions in plasma towards the negatively charged table. This is the basis for traditional reactive ion etching (RIE).

In an ICP process, the excitation is again a time-varying RF source, but is delivered inductively, instead of capacitively, resulting in a changing magnetic field. This changing magnetic field, through the Maxwell-Faraday equation, induces an electric field that tends to circulate the plasma in the plane parallel to the CCP plates. Similarly to a CCP, collisions of the rapidly moving electrons with the slowly moving ions cause further ionizations. Loss of electrons from the plasma through the grounded chamber walls tends to create a static voltage, deemed the plasma voltage  $V_{plasma}$ . This is distinct from the self bias  $V_b$ , as will be examined later. Inductive coupling is generally realized through a large 4 to 5 turn coil encircling the plasma chamber. In the typical geometry, this means that one is able to change ion density and other plasma parameters without significantly perturbing the incident energy of the ions.

The results discussed in this chapter are realized on Oxford Systems Plasma Lab 100 ICP-RIE 380 systems, which utilize a CCP and an ICP power source, as seen in Figure 2.1. This dual plasma powering affords the greatest flexibility in altering plasma characteristics such as ion density and bias voltage independently of each

other. These systems have been extensively studied, particularly for silicon etching [17].

#### 2.2.3 Processing Parameters

There are a few important features of an ICP-RIE plasma that have an effect on etching. Most noticeable during operation is the region of glow discharge, where visible light emission occurs from a cloud of energetic ions and electrons. The emission is caused by inelastic collisions of gas particles, exciting bound electrons into an excited state which results in a photon. The color of the plasma is characteristic of the excited gas species, because the photon energy is a function of the electronic structure of the gas molecules and their interactions with surrounding molecules [18]. This can be a good diagnostic for incorrect plasma striking conditions or other adverse changes in your plasma. For example, in a multiple gas recipe, sometimes the emission looks like only one of your gas species, instead of the average of the colors. This happens when the other species are not being ionized, and thus will cause the process to take on a completely different character from a calibrated recipe.

Beneath the glow discharge region is a dark space, where the depletion of electrons means that atoms are no longer excited into emitting photons. This dark space is also the part of the plasma that most directly affects the paths of incoming ions that will accomplish the etching. Neutral atoms and other ions will tend to scatter the otherwise straight path of the ions from the edge of the glow discharge to the cathode.

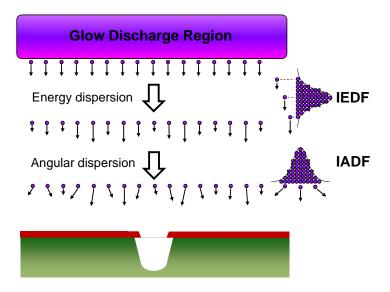

The spread in the ion energy and trajectory is characterized by ion angular distribution function (IADF) and the ion energy distribution function (IEDF) [17]. These distributions, depicted in Figure 2.2, describe the likelihood that an incident ion has a particular energy and trajectory. IADF strongly affects the sidewall profile, as a wider IADF corresponds to a higher flux of ions reaching the sidewall. Similarly, the IEDF controls the types of processes in which the ions can be engaged when they reach the surface; removal of passivating species, overcoming activation energies for reactions to occur, and sputtering yield are all consequences of the IEDF. These are all central to making an etch with desired performance characteristics, so understand-

Figure 2.2. The action of the ion angular and ion energy distribution functions is to spread the kinetic energy and angle of incidence of etch species, resulting in etched profile distortion. Changes of each distribution function shown separately for clarity.

ing these effects and recognizing limitation due to them are paramount to optimizing a recipe. Parameters controlling the IADF and IEDF include the bias voltage  $V_b$ , the ion density, gas composition, and the mean free path (which also depends on the aforementioned parameters).

#### 2.2.4 Etch Reaction Dynamics

In wet chemical processes, etching is accomplished through physical dissolution or reaction specific dissolution [19]. This takes place at any exposed surface and thus results in isotropic etching, although the etch rate can vary along different crystalline orientations due to the bonding state variation of the surfaces. A good example of crystalline anisotropy in Si wet processing is potassium hydroxide (KOH) etching, which is widely used for making MEMS structures that capitalize on the direction-dependent etch rate of KOH [20]. However, in a myriad of planar processes that are utilized in the semiconductor industry, an anisotropic etching profile with sidewalls perpendicular to the wafer surface is frequently required for effective pattern transfer.

In order to prevent the isotropic or crystalline anisotropic behavior of our processing gases, the sidewalls must be protected from further etching. This is accomplished by forming a passivating or inhibiting layer on the sidewall, in one of the following ways:

#### • Surface passivation

- inserting gases in the plasma which react with wafer materials and form involatile compounds [21]

- freezing volatile reaction products at the structures walls using, e.g., cryogenic wafer cooling [22]

#### • Inhibitor deposition

- using polymer precursor gases to form physical barrier layers (e.g., C<sub>4</sub>F<sub>8</sub>) [23]

- eroding and redepositing inert mask materials

All of these processes are important to consider when evaluating an etch, as there may be problems with the etch profile related to the deleterious effect of one of these regimes. We use both surface passivation and inhibitor deposition techniques in the following etch descriptions.

#### 2.2.5 Time-Dependent Processes

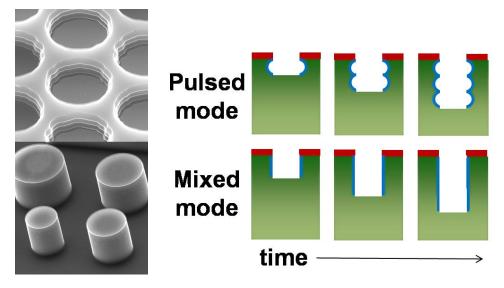

In addition to the previously discussed processing parameters, one additional variable is at our disposal: time. A notable example of using time as an etching parameter is the Bosch silicon etch process, which occurs in a time-multiplexed manner, or pulsed mode, using an etching plasma followed immediately by a deposition plasma. Alternatively, a plasma that contains properly balanced etching and deposition gases can yield the desired etch profile. This is called a mixed mode process. Finally, the process conditions can be changed continuously over time in response to the changing surface condition of our wafer, or to compensate for a negative effect due to the initial conditions of the wafer.

#### **2.2.6** Summary

When making and refining an etching recipe, it is important to have an understanding of all of the aforementioned plasma variables. The diversity of processing conditions accounts for both the sensitivity and flexibility of ICP-RIE plasmas. By having basic knowledge of the underlying physical processes, diagnosing problems in a particular etch recipe becomes more intuitive and makes refinement much easier. In the following sections, we will refer to many of the concepts covered here to explain results and understand the rationale for a given recipe.

#### 2.3 Deep Silicon Etching

Before examining some of the more exotic etching recipes, it is best to examine two of the canonical silicon etching recipes frequently used in industrial settings: the Bosch process [24] and the cryogenic silicon etch [25]. The Bosch process<sup>2</sup> is a pulsed mode etch which uses gas chopping to alternatively etch silicon and deposit inhibitor to protect feature sidewalls. Inherent in the discreteness of the etching is notching on the sidewalls that occurs every step. The duty cycle between steps controls the etch angle and the total length of the combined steps controls the depth of the notching. In contrast, the cryogenic silicon etch<sup>3</sup> is a mixed mode etch that uses a different gas chemistry and chamber conditions to form passivating compounds at the sidewalls at the same time as etching, in effect combining the etch and passivation steps into a single step. By using cryogenic temperatures from  $-80^{\circ}$ C to  $-140^{\circ}$ C, improvements in etch mask selectivity and passivation effects are enabled. These two processes are illustrated diagrammatically in Figure 2.3.

#### 2.3.1 Gas Chemistries

The Bosch process utilizes sulfur hexafluoride (SF<sub>6</sub>) as the etching gas and octafluorocyclobutane ( $C_4F_8$ ) as the passivation gas. When the SF<sub>6</sub> is injected into the

<sup>&</sup>lt;sup>2</sup>Recipe is found in the appendix, A.2.1

<sup>&</sup>lt;sup>3</sup>Recipe is found in the appendix, A.2.3

(a) Example etches (b) Characteristic cross-sections of pulsed and mixed mode etches

Figure 2.3. Comparison of the Bosch process to cryogenic silicon etching.

chamber, the plasma ionizes and radicalizes the gas molecules to create a mixture of  $SF_x$  and  $F_y$  ions and neutrals, where x and y range from 0 to 6 and 1 to 2, respectively [26]. The potential established between the plasma and the substrate, due in part to the ICP and the CCP power, causes the electric field that drives the ions down to the substrate. The unmasked silicon then bonds to the fluorine atoms to create the volatile tetrafluorosilane  $(SiF_4)$  etch product which is then pumped away from the chamber. This is the predominant etching mechanism, and results in an isotropic etch profile. After a few seconds of etch time, the SF<sub>6</sub> flow is rapidly terminated and the C<sub>4</sub>F<sub>8</sub> gas is then injected into the chamber for the passivation step. During this step, the  $C_4F_8$  fragments into smaller  $CF_x$  ions which act as fluorocarbon film precursors [27]. This chemically-resistant film forms on both the vertical and horizontal surfaces of the wafer. The thickness of the protective layer is controlled by the length of the passivation step. Once the deposition is complete the subsequent etch step begins. No silicon etching occurs initially because of the previously deposited layer. However, the fluorocarbon film is milled due to ion bombardment. The bias voltage causes the ions to preferentially remove film from horizontal surfaces (cf. 2.2); once the film is removed, isotropic etching continues on the exposed silicon surface. The discrete nature of these steps results in the scalloping characteristic of the Bosch process.

The cryogenic silicon etch also utilizes the  $SF_6$  chemistry similar to that of the chopping Bosch. However, by lowering the substrate temperature, and by simultaneously injecting  $SF_6$  and oxygen gas,  $O_2$ , a passivation layer is created simultaneously as the silicon is etched. The current understanding of the chemical process is that oxygen ions combine with the fluorine bonded to the silicon surface prior to the silicons removal and forms a  $SiO_xF_y$  layer. The exact composition of this layer is a topic of current research [28]. In a manner similar to the chopping Bosch passivation, the  $SiO_xF_y$  passivation layer protects the exposed vertical silicon while the unmasked horizontal silicon is etched way. To make this passivation process as energetically favorable as the chemical reaction of making  $SiF_4$ , the substrate temperature is required to be cooler than approximately  $-80^{\circ}C$ . When the silicon is warmed back up to room temperature, the  $SiO_xF_y$  becomes volatile and leaves the sample [29].

#### 2.3.2 Mask Selection

The ultimate test of a mask is the fidelity of pattern transfer into the silicon over the entire etching period. Since the mask interacts with the etching process parameters, it is vital to understand which masks to use for different etches. As stated earlier, if the selectivity is too low a thicker mask is required to achieve the desired etch depths. Furthermore, as the edge of the mask erodes it will impart undesired slope or features to the sidewalls of the etched structure, often referred to as mask-induced roughness. For these reasons, deep silicon etching requires higher selectivity masks. Conventional silicon etch masks are metal, oxides, and resist.

Metal masks, such as chrome, offer the advantage of high selectivity as high as thousands to one. This is primarily due to their lack of chemical reactivity with the etch gas molecules and their mechanical strength. However, metal masks typically induce detrimental effects such as notching at the top of the etched structures, due to image charge forces, and unwanted masking due to redeposited metal introduced

by ion sputtering. A particular problem with chrome during the cryogenic etch is that oxygen radicals appear to be locally consumed around the mask reducing the adjacent silicon passivation layer [17]. Silicon dioxide masks typically offer high selectivity (150:1 for Bosch and 200:1 for cryogenic etching) with the added cost of more complicated patterning. The oxide layer must be grown or deposited, followed by pattern transfer from another material or resist into the oxide mask. Increasing the number of processing steps increases the effort needed for accurate pattern transfer as well as the potential for reduction in mask fidelity. Resist masks offer the simplicity of a single processing step along with good selectivity (approximately 75:1 for Bosch and 100:1 for cryogenic etching). These selectivity values highly depend on process conditions and are seen to widely vary.

#### 2.3.3 ICP Power

For both the Bosch process and the cryogenic silicon etch, etch rate is a primary consideration. In order to optimize this, radical density is increased while minimizing decreases in uniformity. The primary method of achieving high radical density is with ICP power; as the ICP power is increased, more energy is available to excite plasma constituents generated, causing the chemical etch rate to increase. However, this can lead to negative consequences of increased milling, reduced selectivity, and reduced passivation due sidewall bombardment. However, the two chemistries display slightly different responses to ICP power increases.

For the Bosch process, the ICP power for the etch and passivations steps is decoupled. By increasing the ICP power for the passivation step, passivation layer thickness can be increased independently of etch rate for a given passivation time, ignoring second order effects such as the C:F ratio in the resultant film due to gas species fractionation [27]. For the etch step, ICP power increases etch rate by increasing the F radical density. Finally, for both steps increasing the ICP power also slightly increases the bias between the plasma and the electrode. For the Bosch etch, this increase is generally negligible (a few volts) since the bias from CCP power is much larger (tens of volts).

For the cryogenic etch, applying more ICP power can significantly increase the amount of milling due to an increased bias voltage, as well increasing the substrate temperature. It is estimated that the exothermic formation of SiF<sub>4</sub> releases 2 W/cm<sup>2</sup> for an 8  $\mu$ m/min etch rate. For an unmasked 6 inch Si wafer, this results in approximately 360 W of exothermic heating. Without proper cooling, the wafer temperature would increase at a rate of  $\geq 10$  °C/second [30, 31].

#### 2.3.4 CCP Power

Increasing the CCP power establishes a larger electric field between the plasma and the table electrode. By imparting more momentum to the ions, the silicon milling rate increases. This typically increases the vertical etch rate (sputtering/milling), reduces the selectivity (faster mask erosion), increases lateral etching slightly (IADF broadening), and raises wafer temperature (higher incident ion energy).

The Bosch process is relatively robust to changes in CCP power; etching proceeds as soon as the passivation is removed, and is predominantly chemical. The Bosch etch is typically insensitive to temperature effects, while the cryogenic etch is extremely responsive to any temperature changes. Since the Bosch etch is performed at 15–20 °C, the polymer passivation layer is far from both the melting and freezing regimes.

The cryogenic etch, however, is very sensitive to CCP power changes. Heating by as little as 5 °C during the cryogenic etch reduces the passivation rate and changes sidewall angle dramatically. Passivation during the cryogenic etch roughly begins to occur around -85 °C. However, if the wafer is too cold,  $SF_x$  etch gases and  $SiF_x$  product gases can freeze on the sample sidewalls, adding to the  $SiO_xF_y$  passivation layer. Variations in table temperature by 5 °C due to oscillations in the table temperature controller have been seen to change the profile of deep etches adding a sinusoidal curvature to the sidewalls. Temperature is typically controlled by cooling the stage with liquid nitrogen or water and thermally connecting the wafer to the table by flowing helium between them.

#### 2.3.5 Pattern Dependence and Chamber Hysteresis

Changing the amount of exposed silicon on a pattern can significantly alter the etch rate by moving the process into a reactant-limited regime. This is further complicated for the cryogenic etch, as a more exposed pattern leads to higher substrate heating and reduced passivation. This can be partially remedied by maintaining a large silicon loading through the use of carrier wafers. By attaching a smaller sample to a large carrier wafer, slight changes in sample mask patterning will be reduced by the relative area. However, this technique is impractical for high throughput applications. A more cost effective solution is calibration to a particular mask set in order to maximize the die area etched per process.

Cleanliness of the chamber can also change the effects of etches. Since the plasma interacts with the sidewalls as well as the substrate, residual molecules from previous etches can be redeposited on the etched surface, causing micromasking, or can chemically react with the etch gas. This is particularly true for the narrow process window of the cryogenic etch, where etch rate can easily be slowed by 50% in a unconditioned chamber.

#### 2.4 Nanoscale Silicon Etching

The Pseudobosch process<sup>4</sup> is a mixed mode etching suitable for photonic and other nanoscale structures. It combines the gas chemistry of the Bosch process with the cryogenic etching strategy of simultaneous passivation and etching. Unlike deep silicon etching, nanoscale etching requires neither extraordinary selectivity nor large etch rates. On the contrary, moderate selectivity of 5:1 is acceptable and slower etch rates are more useful for accuracy of etch depths. Furthermore, Bosch etching and cryogenic etching prove to be unsuitable for very small structures due to the notching and lateral etching of the two chemistries, respectively. In exchange for the lower etch rate, pattern fidelity is improved because of highly controllable sidewalls and low undercutting effects.

<sup>&</sup>lt;sup>4</sup>Recipe is found in the appendix, A.2.2

#### 2.4.1 Gas Chemistries

For Pseudobosch,  $SF_6$  is used as an etch gas while  $C_4F_8$  is used to passivate simultaneously. Plasma parameters are similar to those used in the cryogenic etch, which has a lower ICP power and CCP power. Since incoming ions must constantly mill the continuously deposited fluorocarbon polymer layer, the etch rate is only 200–300 nm/min; this is a significant drop from a comparable Bosch process. The advantage of using  $C_4F_8$  as the passivation gas in mixed mode enables processing at room temperature.

#### 2.4.2 Mask Selection

Typical masks for nanoscale etches are based on the difficult patterning requirements. To define structures down to 20 nm, e-beam resists such as polymethylmethacrylate (PMMA) are employed with film thicknesses ranging from 500 nm down to 30 nm. The advantage of using this as the etch mask is the simplicity in pattern transfer: once the e-beam patterning is complete, the resist can be developed leaving the patterned etch mask. The disadvantage is that typical selectivity values range from 3:1 to 0.5:1. High resolution features require thinner resists; this can often limit the maximum etch depth due to low selectivity. Another polymer-based resist, ZEP-520A, offers the lithographic advantages of PMMA while offering a much higher selectivity ( $\geq 4:1$ ) to F-based etches like the Pseudobosch.<sup>5</sup>.

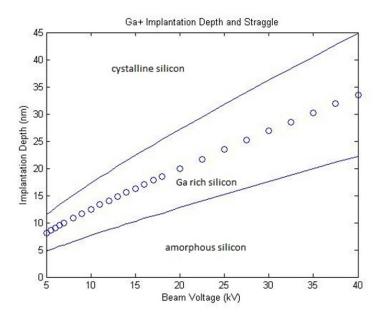

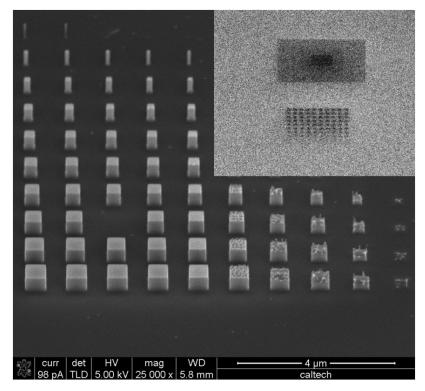

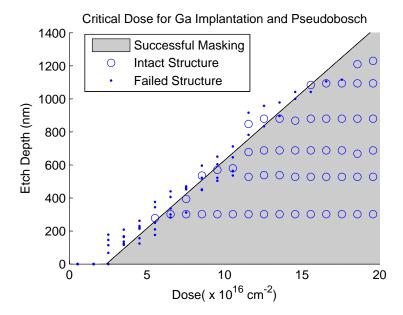

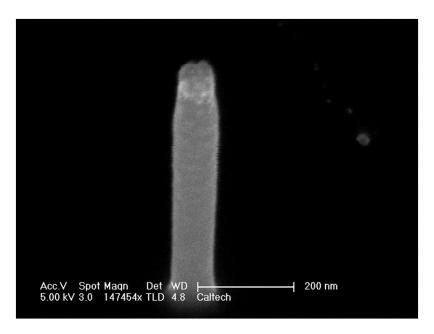

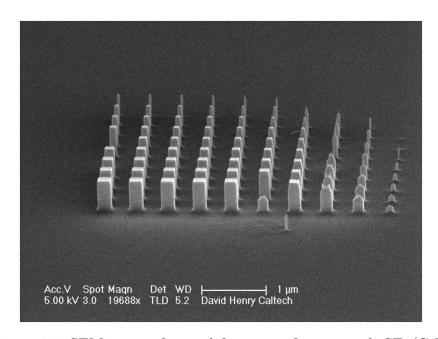

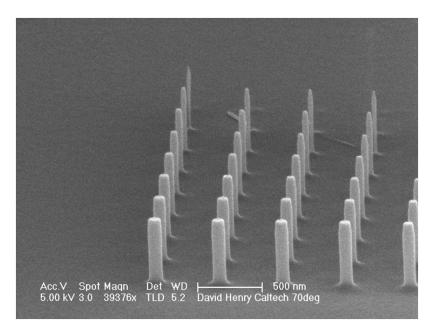

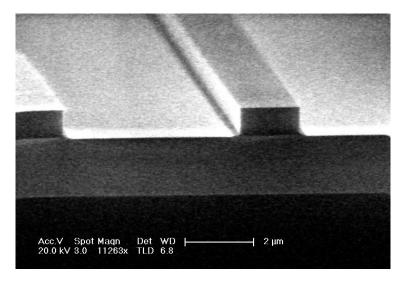

A novel etch mask for silicon nanostructures is implanted gallium [32, 33]. With this method, Ga ions are implanted in the silicon substrate using a focused ion beam. Typical threshold dosages are about  $10^{16}$  ions/cm<sup>2</sup> or 2000  $\mu$ C/cm<sup>2</sup>. For comparison, typical resist sensitivities range from 200–1200  $\mu$ C/cm<sup>2</sup> when exposed on a 100 kV electron beam lithography system. An example of this mask is shown in figure 2.4 This masking technique is explored in further detail in Chapter 3.

$<sup>^5</sup>$ ZEP resist is partly halogenated PMMA, with a chlorine substituting for one of the hydrogens (compare ZEP's monomer formula  $C_5H_7ClO_2$  to PMMA's  $C_5H_8O_2$ )

Figure 2.4. Pseudobosch etch of a Ga etch mask. Etch depth is 700 nm.

#### 2.4.3 Etching Conditions and Optimization

By changing the ratio of the etch gas to passivation gas, SF<sub>6</sub>:C<sub>4</sub>F<sub>8</sub>, the sidewall profile can be controlled. A typical ratio is 1:3 with the absolute gas flow rates dependent upon chamber volume, as sufficient flow is required to establish a chamber pressure of 10 mTorr; a good starting point is roughly 30 and 90 sccm respectively. Increasing the ratio improves the etch rate, reduces the selectivity, and drives the sidewall to be reentrant. Typical ICP power is around 1200 W combined with a slightly higher CCP power than that of the cryogenic etch of around 20 W. Increasing the CCP power again reduces the selectivity with a slight improvement in etching rates. Unlike cryogenic mixed mode, this etch is typically performed at room temperature or 15–20 °C.

## 2.5 Nanoscale Indium Phosphide Etching

In contrast to the previously discussed fluorine-based etch recipes, many III-V materials (GaAs, InP, etc.) require the use of chlorine-based chemistries. This is due to the difference in chemical properties of the etch products. As seen in the previous section, Ga implantation can serve as a mask in fluorine-based plasma. The proposed

mechanism for this masking capability is the formation of involatile  $GaF_x$  compounds that prevent further etching. Thus, for etching of Ga and other similar compounds, we expect that a  $Cl_2$ -based etch will result in faster etching rate and smoother sidewalls from the readily removed etch products. In this section, we will discuss an InP etch<sup>6</sup> that uses a hybrid gas mixture of  $Cl_2$ ,  $CH_4$ , and  $H_2$ , used for etching waveguide structures in Chapter 5.

#### 2.5.1 Gas Chemistries

The gas composition of this etching recipe is a hybrid between two established InP recipes. Specifically, high etch rate recipes with  $Cl_2$ - and  $Cl_2/Ar$ -based plasmas are well known but suffer from sidewall roughness and require high processing temperatures to volatilize  $InCl_x$  species [34], as illustrated in Figure 2.5. Smooth etch recipes with  $CH_4/H_2$  plasmas have also been studied but have prohibitively slow etch rates. In this case, the smoothness is a result of two factors. Firstly, the dominant etching mechanism of InP is the evolution of volatile products PH3 and  $In(CH_3)_3$ , which can be controlled by adjusting the gas flow rates [35]. Secondly, the deposition of CH films from the source gases serves to protect the sidewalls [36]. In our etch, we utilize a precise ratio of source gases that balances all these properties and takes interactions into account, such as removal of H and CI ions by formation of HCI.

#### 2.5.2 Mask Selection

Appropriate masks for the InP etch are metals and dielectrics. This is due to the high rate of mask erosion inherent in the etching conditions. The forward bias and thus bias voltage that drive ions toward the wafer surface are much higher than those found in the SF<sub>6</sub>-based silicon etches in previous sections. This will make the etch more milling, and will help to maintain the same etch characteristics in other stoichiometries of interest, such as InGaAsP compounds. We utilized masks of silicon dioxide spheres and evaporated Au layers in the etching experiments. The selectivity

<sup>&</sup>lt;sup>6</sup>Recipe is found in the appendix, A.2.4

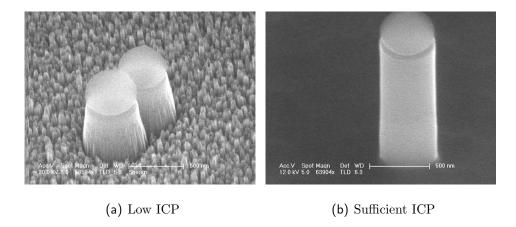

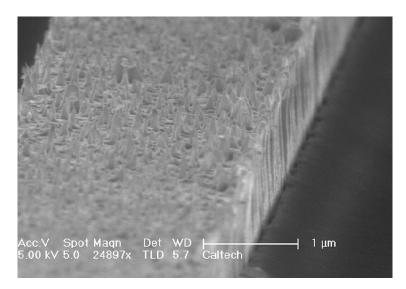

Figure 2.5. InP etching temperature sensitivity. (a) Micromasking due to insufficient heating. (b) By increasing ICP power and thus raising sample temperature, micromasking is removed.

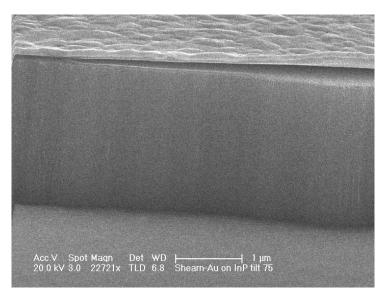

Figure 2.6. Anisotropic InP etch using a metal hardmask. Smoothness is only limited by mask irregularities

of oxide was approximately 10:1; however, faceting occurred before the mask was completely eroded, limiting the useful selectivity to a more modest 4:1. In deeper nanoscale etching applications, a silicon nitride or metal mask is preferred as it has high selectivity and does not suffer from faceting as readily as oxide. As seen in Figure 2.6, the metal hardmask has eliminated most pattern-induced roughness seen in figure 2.5.

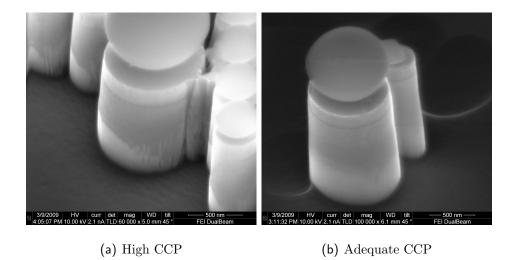

Figure 2.7. CCP power dependence of InGaAsP on InP etching: (a) excessive CCP power and (b) adequate CCP power. The features at the bottom of the pillar are due to faceting and redeposition of mask materials

#### 2.5.3 Etching Conditions and Optimization

Our etch had  $\text{Cl}_2:\text{H}_2:\text{CH}_4$  ratio of 8:7:4 with actual gas flows of 32 sccm  $\text{Cl}_2$ , 28 sccm  $\text{H}_2$ , and 16 sccm  $\text{CH}_4$  and a chamber pressure of 4 mTorr. The table was heated to 60°C to reduce polymer deposition, and no helium backing was applied in order to have the plasma heat the sample. This heating is key to proper etch characteristics, as too little heat will cause micromasking due to involatile gas products such as  $\text{InCl}_x$ . The CCP power was 180 W, found experimentally by varying until an anisotropic profile was achieved without excessive mask erosion. This resulted in a cathode bias of approximately 200 V. ICP power was 2200 W, also found experimentally by monitoring the transition of black InP to smooth InP due to the cessation of micromasking during etching. The etch rate of pure InP was measured to be 1.2  $\mu\text{m}/\text{min}$ .

During some etches with identical conditions, a roughening of the bottom surface was noticed due to chamber cleanliness. The sensitivity of this etch to chamber condition is not as high as the cryogenic Si etch described earlier, but reproducible results require a regular cleaning schedule to return the chamber to a known clean state. This is best implemented by running a short, minute-long  $SF_6$  cleaning plasma just before etching to remove any contaminants that are readily incorporated into the plasma. For long term cleanliness, periodic hour-long  $SF_6/O_2$  plasma is run. The frequency depends on what other etches have been performed previously, but is typically one hour of cleaning per three to four hours of etching. In an industrial setting, this could be done in shorter periods between each wafer to maintain a constant chamber state.

## 2.6 Plasma-Assisted Wafer Bonding

In order to best utilize the capabilities of the patterned Si-based materials and InP-based III-V materials described above, we require a way to combine them onto the same platform. As an alternative to epitaxial growth, direct wafer bonding provides a way to join together two flat and clean semiconductor surfaces at room temperature without the restriction of matching lattice constants. The intermolecular and interatomic forces bring the two wafers together and the bonds form at the interface. By introducing a superlattice defect-blocking layer, dopants and defects are prevented from migrating from the bonding interface to the active region so that the luminescence from the multiple quantum well structure can be preserved [37]. To increase the bond strength, a high-temperature post-bonding annealing step is usually required. However, this high-temperature annealing step induces material degradation and is incompatible with backend Si CMOS processing. For this purpose, many efforts have been put into reducing the annealing temperature while keeping a strong bonding [38, 39, 40]. The technique is integral to the III-V hybrid structures described in Chapter 5.

### 2.6.1 Direct Wafer Bonding

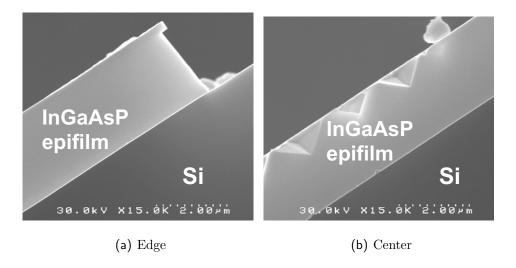

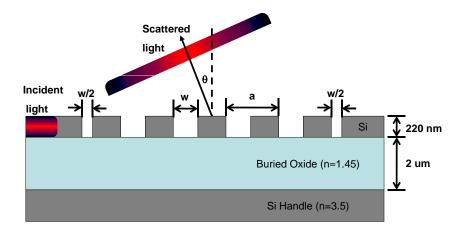

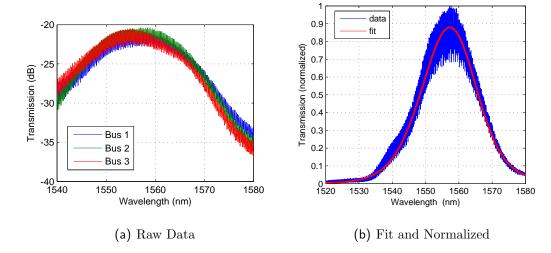

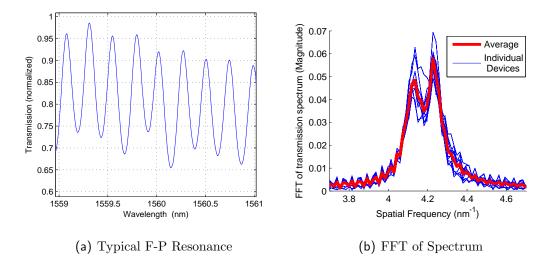

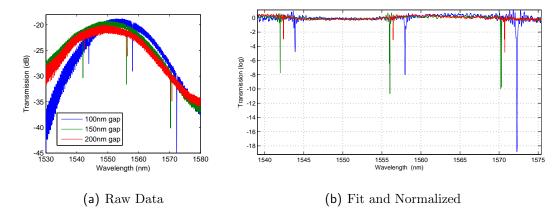

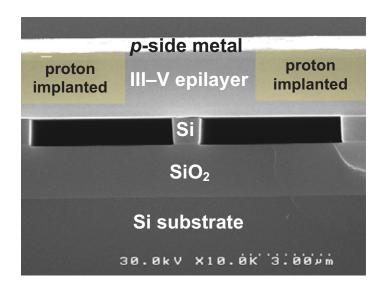

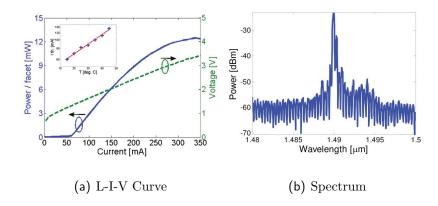

For Si-to-InP wafer bonding, a pre-bonding oxygen plasma treatment for both wafer surfaces has been demonstrated to yield a very spontaneous bonding at room temperature [41]. Similar to previously discussed etching plasmas, the pre-bonding plasma