# A Charge-Controlled Model for MOS Transistors

Thesis by

Mary Ann Maher

In Partial Fulfillment of the Requirements

for the Degree of

Doctor of Philosophy

#### California Institute of Technology

Pasadena, California

1989

(Submitted May 30, 1989)

#### ©1989

Mary Ann Maher

All Rights Reserved

## Acknowledgments

I express my deepest gratitude to Carver Mead for being my advisor. He has provided inspiration, encouragement and emotional support as well as a wonderful environment in which to learn to do research. It has been a privilege and a pleasure to observe and learn from his philosophy of science and his insights into device physics. Among other things he taught me the value of "real data", and to solve the simple problem first. I had a lot of fun; I hope you did too, Carver.

Thanks to the members of our research group, for their friendship, support, and technical interaction: Tobi Delbruck, Steve DeWeerth, Michael Emerling, David Feinstein, Dave Gillespie, John Lazarro, John LeMoncheck, Tzu Mu Lin, Jin Luo, Misha Mahowald, John Platt, Sylvie Rychbusch, Mass Sivilotti, John Tanner, and John Wawryznek. A special thanks to my office mate, Massimo Sivilotti and to Misha Mahowald for many fruitful discussions. I also thank Chuck Seitz and Ralph Cavin for their encouragement over the years. I express my appreciation to Al Barr, Chuck Seitz, Tom McGill, Carver Mead and John Linvill for serving on my committee.

I gratefully acknowledge the assistance of the many people who contributed to my thesis through technical support. The tools I used to design my test structures were written by Mass Sivilotti, Glen Gribble and John Tanner. The figures were drawn using a graphical editor written by Glen Gribble and data plotting software written by Dave Gillespie. I truly appreciate the willingness of Dave and Glen to help with any software problems I had. Jim Campbell helped me to order equipment. Cal Jackson provided support of TEX. Dick Lyon and Lyn Dupre helped me to improve my writing style. Thanks to Carolyn Collins, Helen Derevan, and Diane Dysland for their administrative support and kindness.

This work was supported by the System Development Foundation and the Semiconductor Research Corporation. Experimental devices were kindly donated by Amr Mohsen and Gerry Parker of Intel Corporation. Computer support was provided by an equipment grant from Hewlett Packard. I have been supported by a faculty development fellowship from Hewlett Packard.

Thanks to my parents and my friends, especially Zoya Popovic, for their encouragement and understanding. Special thanks to John LeMoncheck who made the final weeks a real joy. I am deeply indebted to my dear friends Al Barr, Rajiv Gupta and Tim Kay, who were always there and helped me in countless ways.

## Abstract

As MOS (metal-oxide-semiconductor) devices scale to submicron lengths, short-channel effects begin to dominate device behavior, and designers of VLSI (very-large-scale-integrated) circuits see an improved transistor model as a necessary tool. A new physically based, charge-controlled model for the DC current, the intrinsic terminal charges, and the transcapacitances in the MOS transistor under quasistatic conditions has been developed. The model expresses the current in the MOS transistor in terms of the mobile charge per unit area in the channel, and uses a complete set of natural units for velocity, voltage, length, charge, and current. The current-flow equation for the transistor includes both a drift term and a diffusion term, so that the formulation applies equally over the subthreshold, saturation, and "ohmic" regions of transistor operation and includes the effect of velocity saturation. The solution of this dimensionless current-flow equation using these units is a simple, continuous expression, and is suitable for the computer simulation of integrated circuits. The expression allows the regimes of transistor operation and the behavior of long-channel devices versus short-channel devices to be discerned easily. In particular, the expressions for source and drain terminal charges combine the mobile charge in the channel at the source and drain ends in simple polynomials. Analysis of the model shows a fundamental relation between the transistor transcapacitances and transconductances, and

permits the development of efficient simulation models of them.

Our physically based transistor model uses parameters derived from the fabrication process by direct measurement and from the dimensions of the device. The zero-order model agrees closely with measurements on the scaling of current with channel length down to submicron channel lengths. For more detailed analog simulations, the model contains several first-order effects calculated as perturbations on the simple model. Comparisons among calculated and measured curves of conductance, capacitance, and drain currents demonstrate the accuracy of the model both above and below threshold for a number of experimental devices of different channel lengths. Results from the model concur with measurements on short-channel transistors down to 0.6-micron channel length. Several analog circuit simulators now contain the model.

## Contents

|   | Ack  | nowledgments      | iii  |

|---|------|-------------------|------|

|   | Abs  | stract            | v    |

|   | List | of Figures        | х    |

|   | List | of Symbols        | xiii |

| 1 | Intr | oduction          | 1    |

|   | 1.1  | Overview          | 3    |

|   | 1.2  | Chapter 2         | 4    |

|   | 1.3  | Chapter 3         | 5    |

|   | 1.4  | Chapter 4         | 6    |

|   | 1.5  | Chapter 5         | 6    |

| 2 | The  | General MOS Model | 8    |

|   | 2.1  | Electrostatics    | 9    |

|   | 2.2  | Channel Current   | 14   |

|   | 2.3  | Natural Units     | 16   |

|   | 2.4   | Source Boundary Condition                                                                            | 18 |

|---|-------|------------------------------------------------------------------------------------------------------|----|

|   | 2.5   | Saturation $\ldots$ | 20 |

|   | 2.6   | Drain Boundary Condition                                                                             | 21 |

|   | 2.7   | Model Evaluation                                                                                     | 23 |

|   | 2.8   | Experimental Results                                                                                 | 23 |

|   | 2.9   | Summary                                                                                              | 27 |

| 3 | TP:   | st-Order Corrections to the Basic Model                                                              | 28 |

| J | E 113 | st-Order Corrections to the Dasic Model                                                              | 40 |

|   | 3.1   | Mobility Variation                                                                                   | 30 |

|   | 3.2   | Channel-Length Modulation                                                                            | 31 |

|   | 3.3   | Resistance                                                                                           | 36 |

|   | 3.4   | The Upgraded Model                                                                                   | 36 |

|   | 3.5   | Experimental Results                                                                                 | 37 |

|   | 3.6   | Conclusions                                                                                          | 43 |

| 4 | Mo    | del Behavior                                                                                         | 44 |

|   |       |                                                                                                      |    |

|   | 4.1   | The Subthreshold Model                                                                               | 45 |

|   |       | 4.1.1 Current                                                                                        | 45 |

|   |       | 4.1.2 Drain Conductance                                                                              | 48 |

|   |       | 4.1.3 Body Effect                                                                                    | 51 |

|   | 4.2   | The Model Above Threshold                                                                            | 52 |

|   |       | 4.2.1 Long-Channel Limit in Saturation                                                               | 52 |

|   |       | 4.2.2 Short-Channel Transistor in Saturation                                                         | 53 |

|   |       | 4.2.3 Drain Conductance                                                                              | 54 |

|   | 4.3   | Conclusions                                                                                          | 56 |

| 5 | The  | e Charge Model                                       | 57 |

|---|------|------------------------------------------------------|----|

|   | 5.1  | Calculation of Mobile Charge                         | 58 |

|   |      | 5.1.1 Calculation of the Total Mobile Charge         | 61 |

|   | 5.2  | The Terminal Charges                                 | 62 |

|   | 5.3  | Definition of Transcapacitance                       | 64 |

|   | 5.4  | Calculation of Transcapacitance and Transconductance | 64 |

|   | 5.5  | Comparision of Theory and Experiment                 | 66 |

|   |      | 5.5.1 Simulation Results                             | 66 |

|   |      | 5.5.2 Comparison with Ward's Data                    | 66 |

|   |      | 5.5.3 Experimental Data                              | 66 |

|   |      | 5.5.4 Comparison of the Model with Our Data          | 66 |

|   | 5.6  | Conclusions                                          | 69 |

| 6 | Con  | clusions and Future Work                             | 70 |

|   | 6.1  | Summary                                              | 70 |

|   | 6.2  | Circuit Simulation                                   | 72 |

|   | 6.3  | Future Work                                          | 73 |

| A | Tran | uscapacitance and Transconductance Calculations      | 75 |

|   | A.1  | Transcapacitance                                     | 75 |

|   | A.2  | Terminal Derivatives                                 | 76 |

|   | A.3  | Transconductance                                     | 77 |

|   | Refe | rences                                               | 78 |

ix

## List of Figures

| 2.1 | Cross-section of an MOS transistor.                                                           | 9  |

|-----|-----------------------------------------------------------------------------------------------|----|

| 2.2 | Energy diagram of a cross-section through an $n$ -channel MOS transistor                      | 10 |

| 2.3 | Contributions of the surface-potential and of the mobile charge to the gate                   |    |

|     | voltage                                                                                       | 13 |

| 2.4 | Saturation current above threshold versus $1/l$                                               | 20 |

| 2.5 | Determination of substrate doping                                                             | 24 |

| 2.6 | Drain current versus $v_{ds}$ for fixed $v_{gs}$ for a 50-micron channel length transistor.   | 25 |

| 2.7 | Drain current versus $v_{ds}$ for fixed $v_{gs}$ for a 2.8-micron channel length transistor.  | 25 |

| 2.8 | Drain current versus $v_{ds}$ for fixed $v_{gs}$ for a 0.7-micron channel length transistor.  | 26 |

| 2.9 | Drain current versus $v_{ds}$ for fixed $v_{gs}$ for a 0.35-micron channel length transistor. | 26 |

| 3.1 | Conductance and slope of conductance for a 50-micron channel length tran-                     |    |

|     | sistor                                                                                        | 32 |

| 3.2 | Drain current versus $v_{ m ds}$ for $v_{ m gs}=0.5$ volts for a 0.7-micron channel length    |    |

|     | transistor                                                                                    | 32 |

| 3.3 | Drain Current versus $v_{\rm ds}$ for $v_{\rm gs}=3$ volts for a 0.7-micron channel length    |    |

|     | transistor                                                                                    | 34 |

| Conductance and slope of conductance for a 0.7-micron channel length device                   | 35                                                                                                    |

|-----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| Drain current versus $v_{ m ds}$ for $v_{ m gs}=0-3$ volts for a 50-micron channel length     |                                                                                                       |

| transistor                                                                                    | 38                                                                                                    |

| Drain current versus $v_{ m ds}$ for $v_{ m gs}=0-3$ volts for a 2.8-micron channel length    |                                                                                                       |

| transistor                                                                                    | 38                                                                                                    |

| Drain current versus $v_{\rm ds}$ for $v_{\rm gs}=0-3$ volts for a 2-micron channel length    |                                                                                                       |

| transistor                                                                                    | 39                                                                                                    |

| Drain current versus $v_{ m ds}$ for $v_{ m gs}=0-3$ volts for a 0.7-micron channel length    |                                                                                                       |

| transistor                                                                                    | 39                                                                                                    |

| Drain current versus $v_{\rm ds}$ for $v_{\rm gs}=0-3$ volts for a 0.6-micron channel length  |                                                                                                       |

| transistor                                                                                    | 40                                                                                                    |

| Drain current versus $v_{\rm ds}$ for $v_{\rm gs}=0-3$ volts for a 0.35-micron channel length |                                                                                                       |

| transistor                                                                                    | 40                                                                                                    |

| Drain current versus $v_{\rm ds}$ for $v_{\rm gs}=0.5$ volts for a 50-micron channel length   |                                                                                                       |

| transistor                                                                                    | 41                                                                                                    |

| Drain current versus $v_{ds}$ for $v_{gs} = 0.5$ volts for a 2.8-micron channel length        |                                                                                                       |

| transistor                                                                                    | 41                                                                                                    |

| Drain current versus $v_{\rm ds}$ for $v_{\rm gs}=0.5$ volts for a 0.6-micron channel length  |                                                                                                       |

| transistor                                                                                    | 42                                                                                                    |

| Conductance versus $v_{gs}$ for a 2.8-micron channel length transistor                        | 42                                                                                                    |

| Conductance versus $v_{gs}$ for a 0.6-micron channel length transistor                        | 43                                                                                                    |

| Saturation current times channel length versus $v_{ds}$ for transistors in sub-               |                                                                                                       |

|                                                                                               | 49                                                                                                    |

|                                                                                               | Drain current versus $v_{ds}$ for $v_{gs} = 0 - 3$ volts for a 50-micron channel length<br>transistor |

.

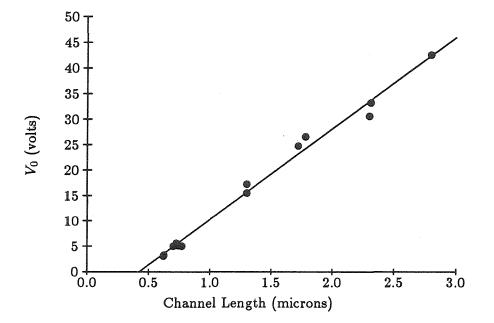

| 4.2 | $V_0$ versus channel length $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 50 |

|-----|--------------------------------------------------------------------------------------------------------------|----|

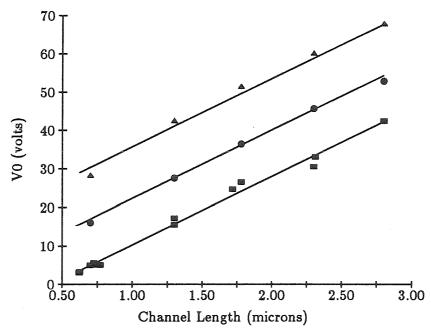

| 4.3 | $V_0$ versus channel length for various $V_g$                                                                | 55 |

| 5.1 | Mobile charge distribution for the subthreshold region                                                       | 59 |

| 5.2 | Mobile charge distribution for an above-threshold, long-channel, transistor.                                 | 59 |

| 5.3 | Mobile charge distribution for a velocity-saturated transistor                                               | 60 |

| 5.4 | Mobile charge distribution for a 3-micron channel length transistor above                                    |    |

|     | threshold                                                                                                    | 60 |

| 5.5 | $\mathcal{Q}_{s}/\mathcal{Q}_{m}$ and $\mathcal{Q}_{d}/\mathcal{Q}_{m}$ versus $v_{ds}$                      | 63 |

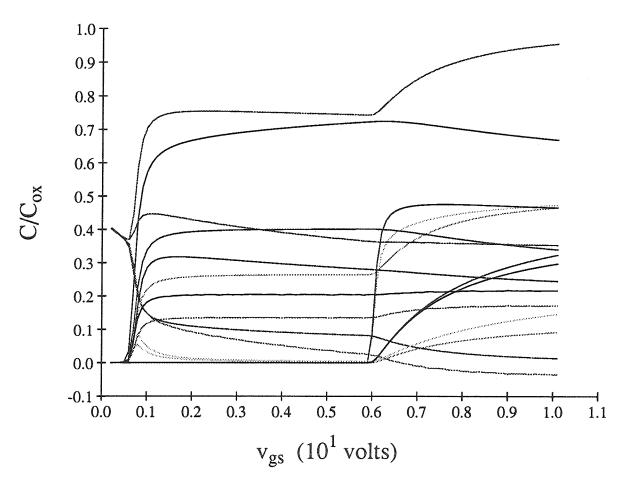

| 5.6 | Model calculation of transcapacitance versus gate voltage                                                    | 67 |

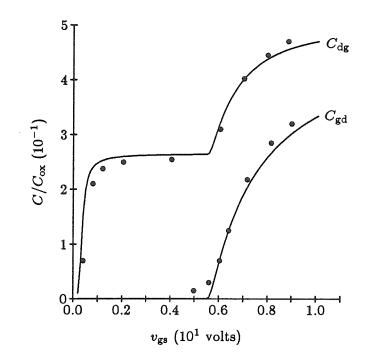

| 5.7 | $C_{ m dg}$ and $C_{ m gd}$ versus gate voltage                                                              | 68 |

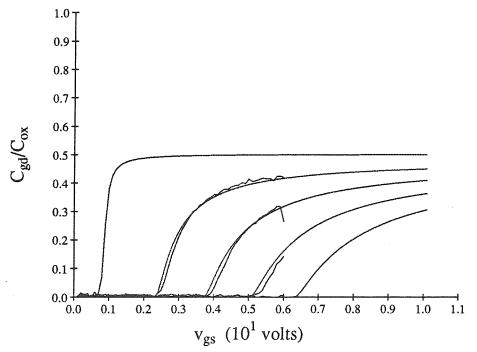

| 5.8 | $C_{\rm gd}$ versus gate voltage for $v_{ m ds}=5$ volts and $v_{ m sb}=0$ volts                             | 68 |

## List of Symbols

C channel capacitance

$C_{\rm b}$  depletion capacitance

$C_{\rm d}$  channel capacitance at the drain end of the channel

$C_{ij}$  transcapacitance between terminals i and j

$C_{\rm ox}$  oxide capacitance

$C_{\rm s}\,$  channel capacitance at the source end of the channel

D diffusion constant

E energy

$E_{\rm c}\,$  energy at the conduction band edge

$E_{\rm f}$  quasi-fermi level

$E_{\rm T}$  thermal energy, natural unit for energy

$\mathcal{E}_{ch}$  electric field along the channel

$\mathcal{E}_{\mathrm{d}}$  electric field along the channel at the drain end

$\mathcal{E}_{f}$  mobility degradation parameter

$\mathcal{E}_g$  vertical electric field

$\mathcal{E}_{\mathrm{gd}}$  vertical electric field at the drain end

$\mathcal{E}_{\rm gs}$  vertical electric field at the source end

g conductance

$g_{\rm d}$  drain conductance

$G_j$  transconductance  $\frac{\partial I}{\partial V_j}$

*i* DC drain-source current

I normalized DC drain-source current

$I_{\rm b}$  normalized bulk current

$I_d$  normalized drain current

$I_{g}$  normalized gate current

$I_{\rm s}$  normalized source current

$I_{tot}$  normalized total current

$I_0$  natural unit for current

k Boltzmann's constant

*l* transistor channel length

L normalized transistor channel length

$L_{\text{eff}}$  effective channel length

$l_0$  natural unit for length

$N_{\rm A}$  density of acceptors in the substrate

$N_{\rm c}$  density of states in the channel at the drain end

$N_{\rm d}$  density of states in the drain

$n_0$  effective density of states in the channel

$P_{\rm c}$  Probability of a state in the channel at the drain end being occupied

$P_{\rm d}$  Probability of a state in the drain being occupied

$P_{\rm cd}$  Probability of transition of a carrier from channel to drain

$P_{dc}$  Probability of transition of a carrier from drain to channel

q charge on the electron

$q_{\rm b}$  depletion charge

$q_{\rm d}$  Mobile charge at the drain end of the channel

$Q_{\rm d}$  normalized mobile charge at the source end of the channel

$q_{\rm m}$  mobile charge per unit area in the channel

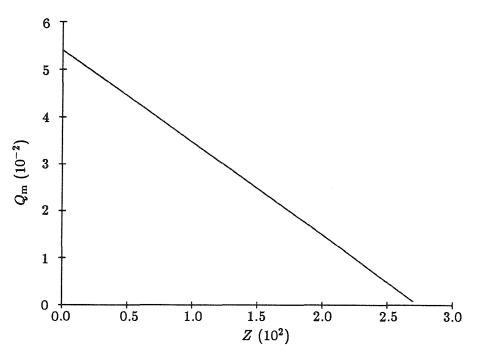

$Q_{\rm m}$  normalized mobile charge per unit area in the channel

$q_s$  Mobile charge at the source end of the channel

$Q_{\rm s}$  normalized mobile charge at the source end of the channel

$Q_{\rm T}$  thermal charge, natural unit for charge

$q_{tot}$  total charge per unit area in the channel

$q_0$  effective charge per unit area in the channel

$Q_0$  normalized effective charge per unit area in the channel

T absolute temperature

$t_{\rm ox}$  oxide thickness

v voltage

V normalized voltage

$V_{\rm b}$  normalized bulk voltage

$v_{\rm b}$  bulk voltage

$v_{\rm d}$  drain voltage

$V_{\rm d}$  normalized drain voltage

$V_{\mathbf{g}}$  normalized gate voltage

$v_{\rm g}$  gate voltage

$V_s$  normalized source voltage

$v_s$  source voltage

$v_{\rm ds}$  drain-source voltage

$V_{\rm ds}$  normalized drain-source voltage

$v_{\rm fb}$  flat band voltage

$v_{gs}$  gate-source voltage

$V_{\rm gs}\,$  normalized gate–source voltage

$V_{\rm T}$  thermal voltage, natural unit for voltage

$V_{\rm th}$  normalized threshold voltage

$v_0$  saturated velocity of mobile carriers in silicon

$V_0$  Early voltage

w transistor width

x distance into the silicon perpendicular to the surface

X normalized distance into the silicon perpendicular to the surface

$x_0$  depletion layer width along the channel

z distance along the channel

Z normalized distance along the channel

$\gamma$  back gate coefficient

$\Delta L_{\rm s}$  width of depletion layer at the source end of the channel

$\Delta L_{\rm d}$  width of depletion layer at the drain end of the channel

$\epsilon_{ox}$  relative permittivity of the oxide

$\epsilon_s$  relative permittivity of the silicon

$\epsilon_0$  permittivity of free space

$\kappa$  derivative of the mobile charge with respect to surface potential

$\mu$  mobility in the channel

$\xi$  quasi-fermi potential

$\Xi$  normalized quasi-fermi potential

$\Xi_d$  normalized quasi-fermi potential at the drain end of the channel referred to the fermi potential

$\rho$  substrate doping density

$\rho_{\text{eff}}$  effective doping density

$\rho_{\rm m}$  effective mobile charge density

$\psi$  surface potential

$\Psi$  normalized surface potential

$\psi_{\rm f}$  fermi potential

$\psi_{

m ms}$  built-in barrier potential

$\Psi_0$  normalized operating point for the surface potential

$\Psi_s$  normalized surface potential at the source end of the channel

$\Psi_d$  normalized surface potential at the drain end of the channel

$\psi_{\rm s}$  surface potential at the source end of the channel

$\psi_{\mathrm{d}}$  surface potential at the drain end of the channel

$\mathcal{Q}_{\mathbf{g}}$  normalized gate terminal charge

$\mathcal{Q}_{\mathtt{s}}$  normalized source terminal charge

$\mathcal{Q}_d$  normalized drain terminal charge

$\mathcal{Q}_{b}$  normalized bulk terminal charge

### Chapter 1

### Introduction

As MOS (metal-oxide-semiconductor) devices scale to submicron lengths, short-channel effects begin to dominate device behavior, and designers of VLSI (very large-scale integrated) circuits see an improved transistor model as an essential tool. Accurate models for MOS transcapacitances and charges are necessary for understanding and simulating the detailed operation of traditional dynamic circuit forms and charge-dependent MOS circuits. Signal margins in dynamic RAMS, error voltages on the floating nodes of analog switches, switched capacitor filters, and the timing and voltage excursion of bootstrapped drivers all need more care in simulation than do signals in strictly digital integrated circuits. Many charge-conserving numerical-integration routines for use in circuit simulation require the model to supply equations for both the transistor charges and the transistor transcapacitances [Yang 82]. If the device model does not provide an analytical method for evaluating the device charge, the simulation algorithm calculates the device charge by integrating the capacitance equations. The path-dependent result of this integration often leads to nonconservation of charge. In addition, since the accuracy of the transistor model directly determines the accuracy of a transient simulation, simulators demand complete and detailed charge models.

The evolution of a wider range of circuit techniques for CMOS (complementary metaloxide-semiconductor) technology compels designers to understand and model accurately the DC as well as the AC transistor characteristics. New circuits working in subthreshold, hybrid analog/digital chips, BICMOS and speed-independent systems present modeling challenges. Large-scale analog systems emulating the behavior of the sensory systems of animals operate over many orders of magnitude in signal level [Mead 89]. The circuits in these systems require transistors operating above and below threshold, in saturation and in the "ohmic" (low drain-source voltage  $v_{ds}$ ) region. Furthermore, these circuits cross the boundaries between these regions during normal operation. Models that describe the different regimes of operation with separate equations lead to discontinuous derivatives in the transition from subthreshold and in the transition into saturation. The device models used in circuit simulation must provide accurate, continuous expressions for charge, transcapacitance and current that are valid over all regimes of transistor operation.

Device models that are developed for circuit simulation must trade off speed for accuracy. This tradeoff is becoming more and more crucial as VLSI circuit designers attempt to simulate the hundreds of thousands of transistors found on a chip. As transistor channel lengths shrink, modeling becomes increasingly difficult as two- and three- dimensional effects become important and add complexity to the modeling process. Finally, if circuit designers are to truly take advantage of the physics of the devices in designing circuits, they must have access to models that are physically based and that will predict circuit properties as the device geometries and the processes vary.

#### 1.1 Overview

In this thesis, we describe a new model for the DC current, transcapacitances, and intrinsic terminal charges of the MOS transistor under quasistatic operation that applies equally in the subthreshold, superthreshold, saturation, and ohmic regions of transistor operation. We use a charge-controlled approach related to the work of Linvill [Linvill 58], and we write the current in the MOS transistor in terms of the mobile charge per unit area in the channel. The model equations are simple and efficient enough to be suitable for computer simulation of integrated circuits, but capture the essential physical behavior needed to describe accurately the transistor operation for analog circuits.

General analyses of the transistor have been published, and there have been many types of models proposed [Pao 66,Brews 78,El-Mansy 77a] [Sheu 84,Baccarani 78,Vogel 85]. However, many of these models are too complicated for circuit simulation. Empirical models, although based on nonphysical assumptions, may still be able to predict I-V curves because they often contain a large number of adjustable parameters. They may not perform well outside the range of the parameter fit, however, and may contain nonphysical, length- and width-dependent parameters. Also, it is difficult to reason about them on the basis of physical knowledge. Table look-up models, while efficient for a well characterized process, are limited in scope as they cannot model a large range of device sizes or process parameters.

Our physically based model uses a small set of parameters that are derived from the fabrication process by direct measurement and from the dimensions of the devices. Extraction of parameters by global curve-fitting and optimization programs can lead to parameters that have misleading and nonphysical values. We develop a model that is physically meaningful and intuitive so that circuit designers can reason about it and can rely on basic physical knowledge to verify model performance. By bridging the gap between the device physics and the circuit designer, the model provides a synthesis tool as well as an analysis tool. The charge-controlled approach allows us to make the model extendable and to develop models at different levels of abstraction. In this dissertation, we also derive a simplified model from our simulation model for circuit reasoning.

#### 1.2 Chapter 2

We give a review of our charge-controlled DC transistor model in Chapter 2. We first develop a zero-order model assuming constant channel length and mobility for a given device. We describe the model in terms of saturation, where charge at the drain moves at saturated velocity. The more involved description of the transistor when it is not in saturation is treated as an extension of the saturation case. The current-flow equation includes both a drift term and a diffusion term, so the formulation applies equally over all regions of transistor operation. This treatment takes into account the finite velocity attained by carriers as they are accelerated in very high electric fields (velocity saturation). We define a complete set of natural units for velocity, voltage, length, charge, and current that relates the physical current-flow mechanisms and provides the key to developing the model equations. The simple, continuous solution of the dimensionless current-flow equation using these units allows us to discern easily the regimes of transistor operation and the behavior of long-channel versus short-channel devices.

Because the model is charge-controlled and continuous, it contains no explicit threshold voltage. However, we show that the common notion of threshold occurs at the point of

4

unit surface charge, where drift and diffusion make equal contributions to the current. The model includes the threshold shift due to the source-substrate bias (body effect) directly, with no new terms or parameters added to the model.

We present results on the zero-order model, comparing theory and experiment on transistors down to 0.35-micron channel length. The theoretical curves use the same set of parameters in all cases. We investigate the scaling of the device characteristics as the transistor dimensions are made smaller and we demonstrate the model's accuracy by presenting plots of saturation current versus channel length.

#### 1.3 Chapter 3

In Chapter 3, for the more detailed analog simulations, we examine several first-order effects as perturbations on the zero-order model. Some of the effects, such as channel-length modulation, increase the current; others, such as mobility variation and internal resistances, decrease the current. All the effects, and the first-order corrections to the model itself, are of roughly the same magnitude. We find a particular regime of operation in which one of the effects is dominant, and we evaluate the effect there. Accurately modeling the channellength modulation by drain voltage is crucial, as devices scale to submicron lengths. We include this effect by calculating an effective channel length as a function of drain and source bias. Observing a subthreshold, short-channel transistor in saturation shows this process nearly independently of other physical effects. We then use transistors above threshold to study the effect of mobile charge on the depletion-layer length. We also include the variation of mobility with gate electric field in the model by looking at the conductance of long-channel transistors. We discuss the consequences of parasitic resistance; an effect that shows up at the higher current levels found in short-channel transistors. In addition, we examine higher-order approximations for the depletion capacitance and the gate electric field as a function of distance along the channel.

Comparisons among calculated and measured curves of conductance, the slope of the conductance, and the drain currents demonstrate the accuracy of the model both above and below threshold for a number of experimental devices of different channel lengths. We present detailed results on 50-micron, 3-micron, 2-micron, 0.7-micron, 0.6-micron, and 0.35-micron channel length devices supplied by Intel Corporation.

#### 1.4 Chapter 4

In Chapter 4, we examine the behavior of the model in different regions of transistor operation. We compare the charge-controlled model expressions with those of typical voltagebased models in both the subthreshold and above-threshold cases. We also derive simplified forms of the transistor model useful to circuit designers in hand calculations. We deduce an expression for the drain conductance of the transistor in saturation in subthreshold, based on the Early voltage model used in bipolar transistors [Early 52]. We extend this model above threshold and include the effects of velocity saturation. Because the simplified models approximate the more complicated simulation model, designers can use their physical intuition about these models to verify and reason about the simulation results.

#### 1.5 Chapter 5

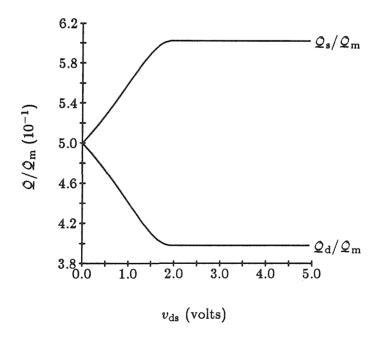

In Chapter 5, we extend the DC model to describe a new model for the intrinsic charges and capacitances in the MOS transistor under quasistatic conditions. The nonlinear equations describing the charge-voltage relations cannot be described by a reciprocal, two-terminal capacitor [Ward 81, Yang 82]. Instead, we define a total intrinsic charge  $\mathcal{Q}$  associated with each terminal and we calculate a set of transcapacitances  $C_{ij} = \frac{\partial \mathcal{Q}_i}{\partial V_j}$  at each terminal from the intrinsic terminal charges. We use the method of Ward [Ward 81] to divide the channel charge into source and drain components.

Our new charge and capacitance expressions are ratios of simple polynomial expressions of quantities needed for calculating the DC model. The calculated charges are continuous, and the results are valid over all regimes of transistor operation. We also develop a fundamental relation between the transistor's transcapacitances and transconductances, and we propose an efficient method for calculating these quantities when they are used in a circuit simulator.

We derive expressions for the mobile charge in the channel as a function of distance along the channel, and we calculate the total mobile charge. The expression for the mobile charge in the channel correctly predicts the behavior of long- and short-channel transistors, and holds above and below threshold. Simulation results displaying the 16 MOS transcapacitances versus gate voltage show the nonreciprocal nature of the transcapacitances. Plots of the total mobile charge splitting into source and drain components reflect the proper behavior under various boundary conditions. We describe how the charges and transcapacitances scale with channel length. We then verify our results by comparison with measured experimental data. Comparison of our complete model with experimental data in our laboratory taken from chips fabricated through MOSIS, the ARPA silicon foundry [Cohen 81], and with published transcapacitance data from Ward [Ward 81], demonstrate the model's applicability.

### Chapter 2

## The General MOS Model

In this chapter, we develop our zero-order model for the DC current in the MOS transistor. We first derive a solution assuming that the channel length and the mobility are constant for a given device. We begin by obtaining the channel current for a transistor in saturation. We examine the electrostatics of the MOS transistor to relate the gate voltage to the mobile charge and the surface potential. We treat the case of a uniformly doped substrate with a threshold-adjustment implant at the surface. We define a fixed relation between the mobile charge and the surface potential, which we call the effective channel capacitance. This definition leads to a complete set of natural dimensionless units for velocity, voltage, length, charge, and current. We obtain the channel current *i* by integrating the current-flow equations from one end of the channel to the other, using the mobile charge per unit area at the source  $q_s$  as a boundary condition. The current-flow equation for the transistor includes both a drift term and a diffusion term, so the formulation applies equally over all regions of transistor operation. This treatment takes into account mobile carrier velocity saturation. The more detailed treatment of the transistor when it is not in saturation is an extension of the saturation case where  $q_d$ , the mobile-charge density at the drain end of the channel, is set not by velocity saturation, but rather by a boundary condition involving the drain voltage. Finally, we relate the mobile charge in the channel to the terminal voltages.

We compare the model with experimental data that were taken on a set of transistors with several channel lengths, down to 0.35 microns. These devices were fabricated with an advanced process (by 1988 standards), and have a gate-oxide thickness of 125 angstroms.

#### **2.1** Electrostatics

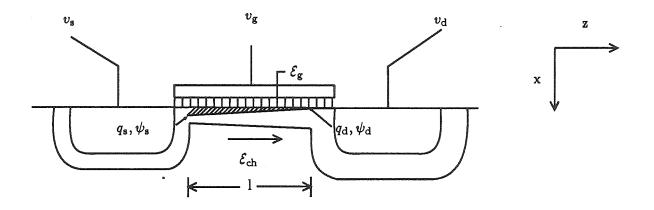

Figure 2.1: Cross-section of an MOS transistor.

Figure 2.1 is a visualization of a cross-section of an MOS transistor; it indicates the overall coordinate system. The energy diagram of a cross-section through the channel region at the barrier maximum of an n-channel MOS transistor is displayed in Figure 2.2. We assume

Figure 2.2: Energy diagram of a cross-section through an n-channel MOS transistor. The cross-section runs normal to the surface through the potential maximum. The zero of surface potential is the conduction band edge deep in the bulk, where the electric field is zero.

that the substrate is uniformly doped with  $N_A$  acceptors per unit volume; hence, under a depletion approximation, the depletion layer contains a constant charge density per unit volume  $\rho = qN_A$ . In our coordinate system, x is measured perpendicular to the surface, with x = 0 at the substrate edge of the depletion layer, and  $x = x_0$  at the surface of the silicon. The mobile charge is quantum-mechanically distributed over some depth [El-Mansy 77a], but we will assume that it is all located at the surface, so that conditions in the bulk are not affected by the presence of mobile charge at the surface. Applying Gauss's law and integrating the electric field in the depletion layer,  $\frac{\rho x}{\epsilon_0}$ , from the bulk to surface yields a relation between the surface potential  $\psi$  and the depletion-layer thickness  $x_0$ , where  $\epsilon_s$  is the permittivity of the silicon:

$$\psi = -\frac{1}{\epsilon_{\rm s}} \frac{\rho x_0^2}{2} \tag{2.1}$$

We will use the conduction band edge deep in the substrate as the reference for the surface potentials. Using this convention, the surface potential is zero at flat-band, when the potential is flat all the way to the interface. Using the depletion-layer thickness, the total charge per unit area  $q_b$  uncovered in the depletion layer is

$$q_{\rm b} = -\rho x_0 = \pm \sqrt{-2\rho\epsilon_{\rm s}\psi} \tag{2.2}$$

This relation allows us to define a depletion-layer capacitance  $C_b$ :

$$C_{\rm b} = -\frac{\partial q_{\rm b}}{\partial \psi} = \sqrt{-\frac{\rho \epsilon_{\rm s}}{2\psi}} = \frac{\epsilon_{\rm s}}{x_0}$$

(2.3)

The applied gate voltage appears partially across the gate oxide and partially across the silicon substrate. The voltage across the gate oxide is the oxide electric field times the oxide thickness  $t_{\text{ox}}$ . The electric field is proportional to the total charge to the left of the oxide  $q_{\text{tot}}$ : the depletion-layer charge  $q_{\text{b}}$ , the mobile charge per unit area  $q_{\text{m}}$ , and the surface fixed

charge  $q_{ss}$  (which includes the interface charge  $q_{it}$  and any threshold-adjustment charge). Consequently, the gate voltage  $v_g$  is

$$v_{\mathbf{g}} = \psi - \frac{t_{\mathrm{ox}}}{\epsilon_{\mathrm{ox}}}(q_{\mathrm{tot}}) + \psi_{\mathrm{ms}}$$

$$= \psi - \frac{1}{C_{\mathrm{ox}}}(q_{\mathrm{b}} + q_{\mathrm{m}} + q_{\mathrm{ss}}) + \psi_{\mathrm{ms}}$$

(2.4)

where  $C_{\text{ox}} = \epsilon_{\text{ox}}/t_{\text{ox}}$  is the oxide capacitance per unit area, and  $\psi_{\text{ms}}$  is the the built-in potential that exists between the gate and silicon surface with zero applied gate voltage [Grove 67]. We take into account the fixed charge  $q_{\text{ss}}$  and the built-in potential by defining the term  $v_{\text{fb}} = \psi_{\text{ms}} - q_{\text{ss}}/C_{\text{ox}}$ . When  $v_{\text{g}} = v_{\text{fb}}$ , the surface potential is equal to zero; hence,  $v_{\text{fb}}$  is called the *flat-band voltage* [Grove 67].

$$v_{\rm g} = \psi + v_{\rm fb} - \frac{1}{C_{\rm ox}}(q_{\rm b} + q_{\rm m})$$

(2.5)

The mobile-charge density  $q_m$  is a smooth function of the position z along the channel. The surface potential  $\psi$  depends on  $q_m$ ; hence, both  $\psi$  and  $q_b$  will be functions of z as well. Solving Equation 2.5 for  $q_m$ , we obtain

$$-q_{\rm m} = C_{\rm ox}(v_{\rm g} - \psi - v_{\rm fb}) + q_{\rm b}$$

(2.6)

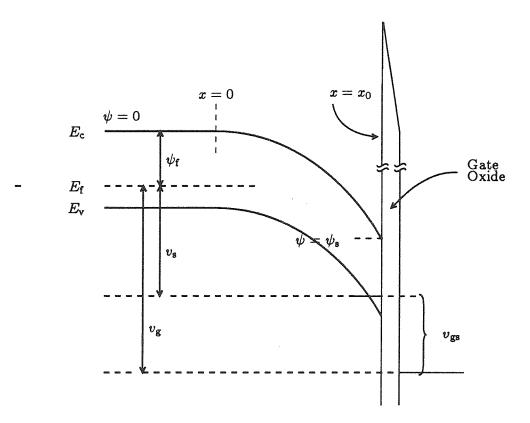

In subthreshold, the gate voltage follows the surface potential, because the mobile charge can be neglected. Above threshold, however, the surface potential changes little, and most of the new electric-field lines from the gate terminate on mobile charges. These relationships are shown in Figure 2.3.

We can extract useful information from Equation 2.5 for small changes in voltage around some operating point. Differentiating this equation with respect to  $\psi$  and applying Equation 2.3, we obtain

$$\frac{\partial v_{g}}{\partial \psi} = 1 + \frac{C_{b}}{C_{ox}} - \frac{1}{C_{ox}} \frac{\partial q_{m}}{\partial \psi}$$

(2.7)

Figure 2.3: Contributions of the terms for the surface potential  $\psi_s$  (solid line) and for the mobile charge  $q_s/C_{ox}$  (dashed line) to the gate voltage, as expressed in Equation 2.5 and evaluated at the source end of the channel. In subthreshold, the gate voltage follows the surface potential, because the mobile charge is negligible. Above threshold, the major contribution to the change in surface potential is the mobile charge, as the surface potential becomes pinned.

For any given operating point, the gate is an equipotential; hence,  $v_g$  does not depend on the coordinate z along the channel, whereas the surface potential  $\psi$  changes considerably. The left-hand side of Equation 2.7 vanishes, and we can relate  $\psi$  to  $q_m$  by defining an effective channel capacitance C per unit area:

$$C = \frac{\partial q_{\rm m}}{\partial \psi} = C_{\rm b} + C_{\rm ox} \tag{2.8}$$

This quantity represents the additional mobile charge that must be injected into the channel per unit increase in surface potential. As the mobile charge flows through the channel, there is a fixed relation between the mobile charge and the surface potential, given by Equation 2.6. Thus, the presence of mobile charge creates an electric field  $\mathcal{E}_{ch}$  along the channel.

#### 2.2 Channel Current

Given the boundary conditions on mobile-charge density and surface potential at the source, we can evaluate the channel current *i* in saturation. Under some circumstances, the current in the channel can be dominated by diffusion; in other regimes of operation, the same transistor may have charge carriers with drift velocities near saturation over the entire length of the channel. We will approximate the current flow by a drift and a diffusion term, and will include the effects of velocity saturation in the drift term:

$$\frac{i}{w} = q_{\rm m} v_{\rm drift} - D q'_{\rm m} \tag{2.9}$$

where w is the width of the channel, D is the diffusion constant,  $v_{drift}$  is the carrier's drift velocity, and  $q'_m$  is the derivative of  $q_m$  with respect to z. Several relations have been proposed for the drift velocity as a function of electric field [Sodini 84,Baum 70,Garverick 87] We adopt a simple relation for the drift velocity that has the proper behavior at both high and low fields [Hoeneisen 72]:

$$v_{\rm drift} = v_0 \left( \frac{\mu \mathcal{E}_{\rm ch}}{v_0 + \mu \mathcal{E}_{\rm ch}} \right)$$

(2.10)

where  $v_0$  is the carrier saturated velocity [Jacoboni 77]. Substituting this relation into Equation 2.9 gives

$$\frac{i}{w} = q_{\rm m} v_0 \left( \frac{\mu \mathcal{E}_{\rm ch}}{v_0 + \mu \mathcal{E}_{\rm ch}} \right) - Dq'_{\rm m}$$

(2.11)

We now introduce an approximation with which we can, for any particular operating point, evaluate Equation 2.9 in closed form. In general, the effective channel capacitance Cdefined in Equation 2.8 between the mobile charge and the bulk and gate (fixed potentials) is a weak function of z, as is the mobility  $\mu$ . The width of the depletion layer in the channel increases with distance toward the drain for nonzero drain voltage. This effect corresponds to a decrease in the channel capacitance. As devices scale to smaller channel lengths and correspondingly thinner oxides, C becomes less dependent on the mobile-charge density  $q_{\rm m}$ . We will first derive the zero-order result, taking C as constant and equal to the value at the potential maximum  $C_{\rm s}$ . In the simple form of our model, we also assume that the gate electric field  $\mathcal{E}_{\rm g}$  (and hence  $\mu$ ) is constant along the channel and is equal to the value at the source  $\mathcal{E}_{\rm gs}$ . However, we still allow the depletion-layer charge  $q_{\rm b}$  used in the calculation of the electrostatics to varys with distance. These restrictions on C and  $\mu$  are relaxed in Chapter 3.

In the following analysis, we compute all currents for a channel of unit width. Because we know that

$$rac{\partial q_{

m m}}{\partial z} = rac{\partial q_{

m m}}{\partial \psi} rac{\partial \psi}{\partial z} pprox C_{

m s} \mathcal{E}_{

m ch} \qquad ext{and} \qquad \mathcal{E}_{

m ch} = -rac{\partial \psi}{\partial z}$$

we can write Equation 2.11 as

$$\frac{i}{w} = q_{\rm m} v_0 \left( \frac{-\mu C_{\rm s} q'_{\rm m}}{v_0 - \mu C_{\rm s} q'_{\rm m}} \right) - D q'_{\rm m} \tag{2.12}$$

#### 2.3 Natural Units

Using the value of the channel capacitance at the source  $C_s$ , we can define a set of natural units for describing the transistor equations:

velocity

$$v_0$$

energy $\mathcal{E}_{\rm T} = kT$ voltage $V_{\rm T} = \frac{kT}{q}$ charge $Q_{\rm T} = \frac{kT}{q}C_{\rm s}$ current $I_0 = v_0Q_{\rm T}$ length $l_0 = \frac{D}{v_0} = \frac{\mu kT}{qv_0}$

The thermal charge  $Q_T = C_s kT/q$  is the mobile charge per unit area at the source required to change the surface potential by exactly kT/q. By expressing all variables in terms of these natural units, we simplify all equations into a dimensionless form that allows us to discern easily the natural relationships and regimes of operation of the transistor.

We use  $Q_m$  for the dimensionless form of the mobile charge density  $q_m$ , and I for the dimensionless form of the current *i*. We write Equation 2.11 in dimensionless form as

$$-I = \frac{Q_{\rm m}Q'_{\rm m}}{Q'_{\rm m}+1} + Q'_{\rm m}$$

(2.13)

$$-I(-Q'_{\rm m}+1) = Q_{\rm m}Q'_{\rm m}+Q'_{\rm m}(Q'_{\rm m}+1)$$

(2.14)

where  $Q'_{\rm m}$  indicates the derivative with respect to Z, the dimensionless distance along the channel.

The first term on the right-hand side of Equation 2.13 is the drift term, and the second is the diffusion term. Using natural units helps to show which terms dominate in a given region of transistor operation. The shortest channel length for which a device can be made to operate is still much longer than is the mean-free path of a carrier, so velocity saturation is not achieved for the diffusion process. We therefore assume that the  $Q'_m$ <sup>2</sup> term is negligible compared with either the  $Q_mQ'_m$  term (when  $Q_m$  is large) or the  $Q'_m$  term (when  $Q_m$  is small). This approximation is excellent as long as  $l_0$  is much less than the device dimensions. For a typical *n*-channel process,  $l_0$  is about 0.007 micron. We thus can write Equation 2.14 as

$$-I(-Q'_{m}+1) \cong Q_{m}Q'_{m}+Q'_{m}=Q'_{m}(Q_{m}+1)$$

or as

$$-I = Q_{\rm m}Q'_{\rm m} + Q'_{\rm m}(1-I) = \frac{\partial}{\partial Z} \left(\frac{Q_{\rm m}^2}{2} + Q_{\rm m}(1-I)\right)$$

(2.15)

We now integrate both sides of Equation 2.15 along the channel from source (Z = 0) to drain (Z = L), where L is the normalized channel length. We note that I is not a function of Z and apply the boundary conditions  $Q_m = Q_s$  at the source and  $Q_m = Q_d$  at the drain:

$$IL = \frac{Q_{\rm s}^2 - Q_{\rm d}^2}{2} + (Q_{\rm s} - Q_{\rm d})(1 - I)$$

(2.16)

Solving Equation 2.16 explicitly for I gives

$$I = \frac{Q_{s} - Q_{d}}{Q_{s} - Q_{d} + L} \left(\frac{Q_{s} + Q_{d}}{2} + 1\right)$$

(2.17)

We can gain important insights into the operation of MOS devices from these equations. For sufficiently large L, the current is small compared with unity, and  $1 - I \approx 1$ . This approximation corresponds to the usual treatment, ignoring velocity-saturation effects. Tracing through the derivation, we see that the quadratic term in Equation 2.16 is a result of the drift term in Equation 2.9, and the linear term is a result of the diffusion term in Equation 2.9 and velocity saturation. The two terms make approximately equal contributions to the saturation current for  $q_s = Q_T$  (in natural units  $Q_s = 1$ ). The gate voltage at which  $Q_s$  is equal to 1 (called  $V_{\rm th}$  in natural units), corresponds to the common notion of threshold and, at threshold, there is no discontinuity. We conclude that below threshold, current flows by diffusion; above threshold, current flows by drift. For larger  $Q_s$ , the surface potential is dominated by mobile charge; for smaller  $Q_s$ , the surface potential is determined by the charge in the depletion layer.

#### 2.4 Source Boundary Condition

We use a charge sheet approximation and assume that the mobile charge is all located at the surface of the channel [Brews 78]. The more general case has been worked out by [Pao 66]. We formulate the boundary condition on  $q_m$  by the integral with respect to the energy E of the carrier density in the source region (a Fermi distribution), times the two-dimensional density of states n(E) (number per unit area, per unit energy) in the channel:

$$q_{\rm m} = q \int_{E_c}^{\infty} \left( n(E) \frac{1}{e^{(E-E_f)/(kT)} + 1} \right) dE \qquad = q \int_{q\psi}^{\infty} \left( n(E) \frac{1}{e^{(E-q\xi)/(kT)} + 1} \right) dE$$

where  $E_c$  is the energy at the conduction band edge  $E_f$  is the quasi-fermi level and  $\xi$  is a quasi-Fermi potential or *imref* [Shockley 60]. For any realizable bias conditions, even for submicron devices, the Fermi level is always many kT below the surface potential. The usual approximation, in which the Fermi function is replaced by a Boltzmann approximation, is thus valid. The resulting expression can be written as

$$q_{\rm m} = q_0 e^{(-q\psi + q\xi)/(kT)} \tag{2.18}$$

where  $q_0 = qn_0$ , is an effective charge density and  $n_0$ , the effective density of states in the channel, is given by

$$n_0 = \int_{q\psi}^{\infty} n(E) e^{-(E-q\xi)/(kT)} dE$$

For a real channel, the form of n(E) is not known; thus, we cannot compute  $n_0$  with confidence. The spacing of the energy levels in the channel is a function of the electric field at the surface; hence, n(E) is proportional to  $1/\sqrt{\psi}$ , a slow dependence that we neglect compared with the exponential due to the Boltzmann function. As long as we have the value of  $n_0$  in the right general order of magnitude, however, the effect of an error in the preexponential factor is easily masked by small changes in surface potential. Solving Equation 2.18 for  $\psi$ , we obtain

$$-\psi = -\xi + \frac{kT}{q} \ln\left(\frac{q_{\rm m}}{q_{\rm 0}}\right) \tag{2.19}$$

At the source, we know that the quasi-Fermi potential is equal to the fermi potential  $\psi_f$  plus the source voltage  $v_s$ . Rewriting Equations 2.18 and 2.19 at the source yields:

$$Q_{s} = Q_{0} e^{(-\Psi_{s} + \Psi_{f} + V_{s})}$$

(2.20)

$$-\Psi_{\rm s} = -\Psi_{\rm f} - V_{\rm s} + \ln\left(\frac{Q_{\rm s}}{Q_0}\right) \tag{2.21}$$

where, in natural units,  $Q_0$  is the effective charge,  $\Psi_s$  is the surface potential at the source end of the channel,  $\Psi_f$  is the fermi potential, and  $V_s$  is the source voltage. We thus can compute the surface potential for any mobile-charge density from Equation 2.21. Given the surface potential, the gate voltage can be determined from Equation 2.5, as described.

## 2.5 Saturation

For channel lengths where the short-channel effects are important but where the limiting behavior has not been reached, we can proceed as follows. For a transistor in saturation, the boundary condition on the charge at the drain is (in natural units)  $Q_d \approx I$ , and Equation 2.16 becomes a simple quadratic form in  $Q_s$ :

$$2I_{\text{sat}}L + 1 = (Q_{\text{s}} + 1 - I_{\text{sat}})^2$$

(2.22)

where  $I_{\text{sat}}$  is the saturation current.

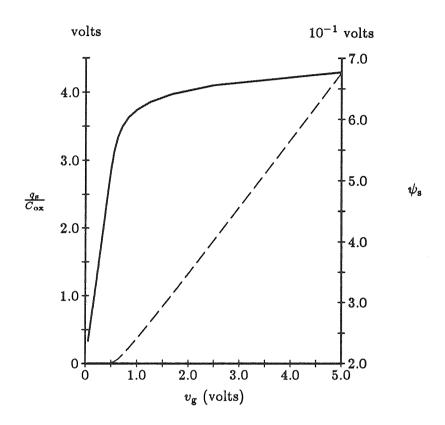

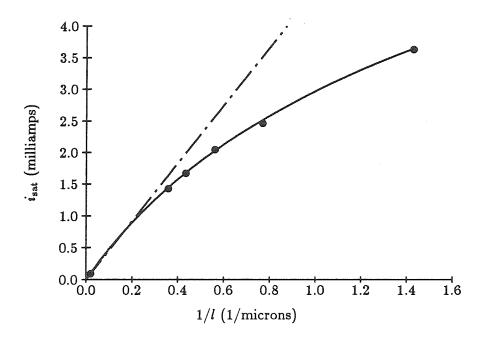

Figure 2.4: Saturation current above threshold versus 1/l. The solid line represents Equation 2.23; dots indicate data from experimental devices. The dashed line shows the long-channel approximation, in which saturation current is inversely proportional to channel length. In a transistor made with current technology (2-micron feature size), the curve deviates substantially from the long-channel behavior.

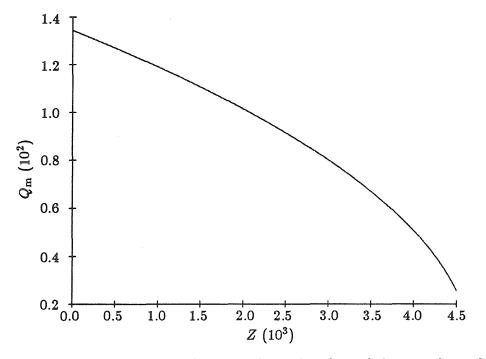

The saturation currents of a number of transistors of different lengths are plotted as a

function of 1/l in Figure 2.4. The dashed line is the long-channel dependence, neglecting velocity saturation. Clearly, devices with channel lengths of the order of 1 micron show large deviations from the long-channel limit. We can solve Equation 2.22 explicitly for  $I_{sat}$ :

$$I_{\text{sat}} = Q_{s} + (L+1) \left( 1 - \sqrt{1 + 2Q_{s} \frac{L}{(L+1)^{2}}} \right)$$

$$\approx Q_{s} + (L+1) \left( 1 - \sqrt{1 + \frac{2Q_{s}}{L}} \right)$$

(2.23)

The solid line in Figure 2.4 represents Equation 2.23, evaluated with the parameters mentioned in the introduction to this chapter.

#### 2.6 Drain Boundary Condition

For sufficiently low drain voltages, the mobile-charge density  $q_d$  at the drain is no longer moving at saturated velocity. We must determine the drain boundary condition for Equation 2.17 to evaluate  $Q_d$  as a function of  $V_d$ . Writing Equation 2.19 for the source and drain in natural units and subtracting the equations yields a relation between the surface potentials at source and drain ( $\Psi_s$  and  $\Psi_d$ ), the mobile-carrier densities at source and drain ( $Q_s$  and  $Q_d$ ), and the imrefs at source and drain ( $\Xi = \Psi_f + V_s$  and  $\Xi = \Psi_f + \Xi_d$ ):

$$\Psi_{\rm d} - \Psi_{\rm s} + V_{\rm s} - \Xi_{\rm d} = -\ln\left(\frac{Q_{\rm d}}{Q_{\rm s}}\right) \tag{2.24}$$

We will derive the drain boundary condition by the following argument. Let the density of states in the drain be  $N_d$  and that at the drain end of the channel be  $N_c$ . The probability  $P_{cd}$  of a carrier in the channel making a transition to a state in the drain is just the probability  $P_c$  of the state in the channel being occupied multiplied by the probability  $1-P_d$ that the corresponding state in the drain is unoccupied. A similar argument produces the probability that a carrier in the drain makes a transition back into the channel.

$$P_{\rm cd} = N_{\rm c}P_{\rm c}N_{\rm d}(1-P_{\rm d})$$

and

$$P_{\rm dc} = N_{\rm d} P_{\rm d} N_{\rm c} (1 - P_{\rm c})$$

with  $N_c$  and  $N_d$  equal to the density of states in the channel and drain. The net drain current is proportional to the difference of these two probabilities:

$$\frac{I}{K} = P_{\rm net} = P_{\rm cd} - P_{\rm dc} = N_{\rm c} N_{\rm d} (P_{\rm c} - P_{\rm d})$$

(2.25)

The actual value of the current is known only to within the constant K.

Writing  $P_c$  and  $P_d$  in terms of the imrefs as given in Equation 2.19, Equation 2.25 becomes (using natural units)

$$I = KQ_{\rm d} \left( 1 - e^{-\Xi_{\rm d} + V_{\rm d}} \right) \tag{2.26}$$

We notice that we can evaluate the constant K by considering operation at large drain voltages ( $V_d$  much greater than  $\Xi_d$ ). This condition corresponds to saturation. Using the saturation boundary condition that  $Q_d \approx I$  in Equation 2.26 yields K = 1. We therefore can write Equation 2.26 as

$$\Xi_{\rm d} = -\ln\left(1 - \frac{I}{Q_{\rm d}}\right) + V_{\rm d} \tag{2.27}$$

Substituting Equation 2.27 into Equation 2.24, we arrive at the final form of the relation among carrier density, current, and drain voltage:

$$V_{\rm d} - V_{\rm s} = \Psi_{\rm d} - \Psi_{\rm s} - \ln \frac{Q_{\rm s}}{Q_{\rm d}} + \ln \left(1 - \frac{I}{Q_{\rm d}}\right) \tag{2.28}$$

The  $\Psi_d - \Psi_s$  term is just the difference in the imrefs at the two ends of the channel. The  $\ln (1 - I/Q_d)$  term is due to the "drain drop"; that is, to the difference between  $\Xi_d$  and  $V_d$ .

Because Equation 2.5 is valid for any surface potential, we can use Equations 2.1, 2.2, and 2.5 to solve for  $\psi_d$ , yielding

$$\psi_{\rm d} = \left(\sqrt{\frac{\epsilon_{\rm s}\rho}{2C_{\rm ox}^2} + v_{\rm g} - \frac{q_{\rm d}}{C_{\rm ox}}} - \sqrt{\frac{\epsilon_{\rm s}\rho}{2C_{\rm ox}^2}}\right)^2 \tag{2.29}$$

# 2.7 Model Evaluation

To generate model curves for comparison with experimental data, we employ the following algorithm. We use voltages  $V_g$  and  $V_s$  with Equations 2.21 and 2.5 to determine the source charge  $Q_s$ . Then, we use the drain voltage  $V_d$  with Equations 2.17 and 2.29 to determine the drain charge and the drain current. Alternatively, we could pick several values of the drain charge varying between  $Q_d = Q_s$  ( $I_{ds} = 0, V_{ds} = 0$ ) and  $Q_d = I_{sat}$  ( $I = I_{sat}$ , large  $V_{ds}$ ), to sweep out the drain characteristic.

#### 2.8 Experimental Results

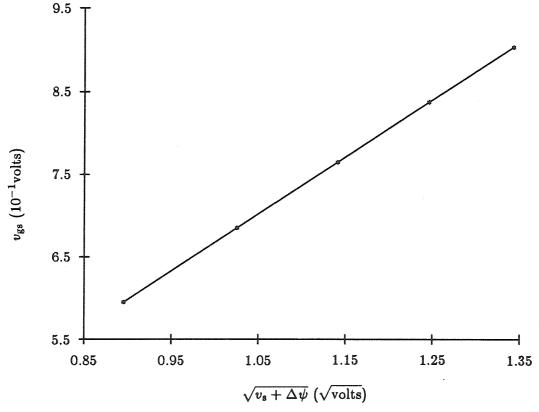

We compared the model predictions against data taken from a number of experimental devices with oxide thickness  $\approx 125$  angstroms provided by Intel Corporation. Detailed comparisons were made for devices from the same wafer, all of width 50 microns and of length ranging from 50 microns to 0.35 micron. Mobility was taken from the channel conductance of the 50-micron channel length device at very low drain-source voltage. Oxide thickness was obtained from the capacitance of a large MOS dot. We found the substrate doping by plotting the threshold voltage versus the square root of the source-substrate reverse bias, as shown in Figure 2.5. The fixed charge at the surface  $q_{ss}$  was computed directly from the threshold voltage once the substrate doping was known. This charge includes any threshold-adjustment implant dose. The saturated velocity of electrons in

silicon was taken from the literature [Jacoboni 77].

Figure 2.5: Determination of substrate doping. Gate-source voltage is plotted versus  $\sqrt{v_s + \Delta \psi}$ , for fixed current level. The slope of the line is proportional to the doping density. Using a value of 125 angstroms for the oxide thickness, we determined the density  $N_A$  to be  $10^{17}/\text{cm}^3$ .

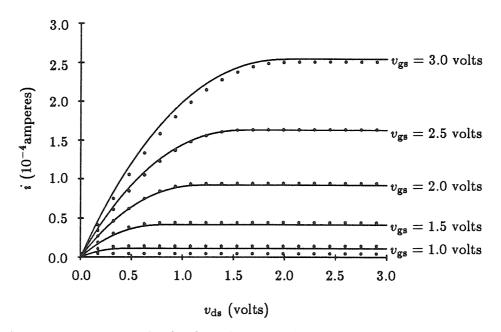

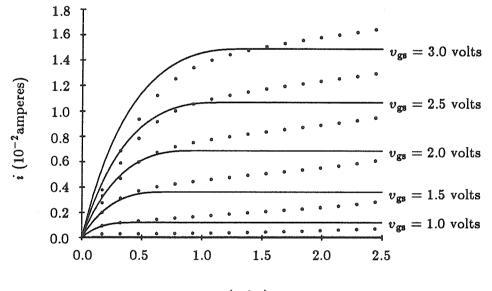

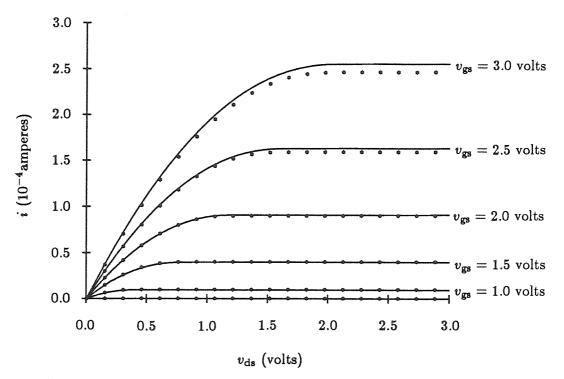

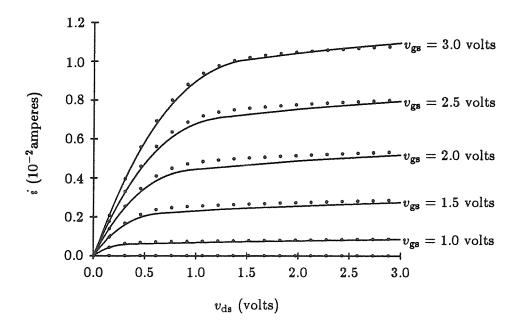

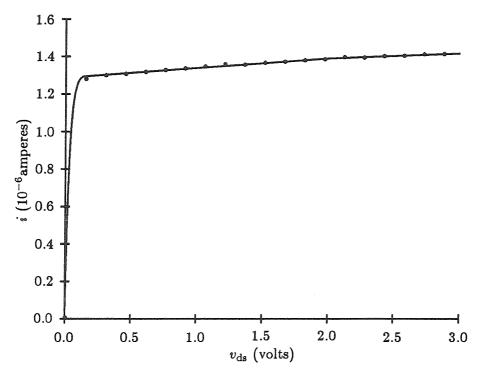

Figure 2.6: Drain current versus  $v_{ds}$  for fixed  $v_{gs}$  for a 50-micron channel length transistor. Solid lines are the values predicted by the model. Dots indicate experimental data.

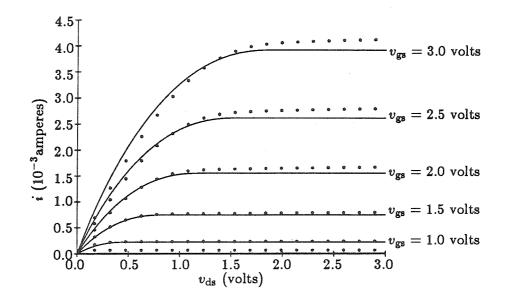

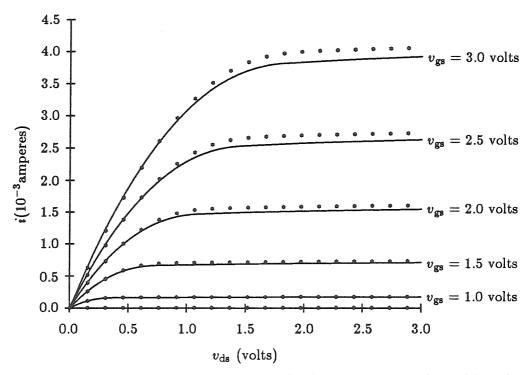

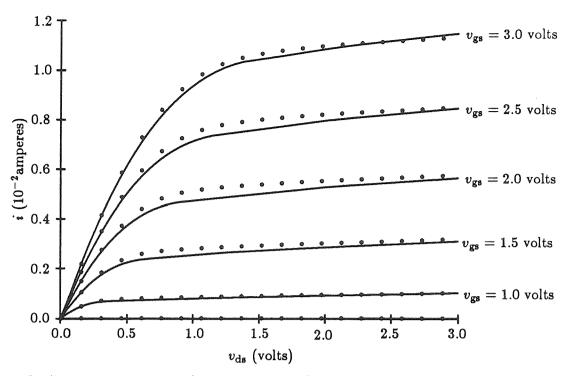

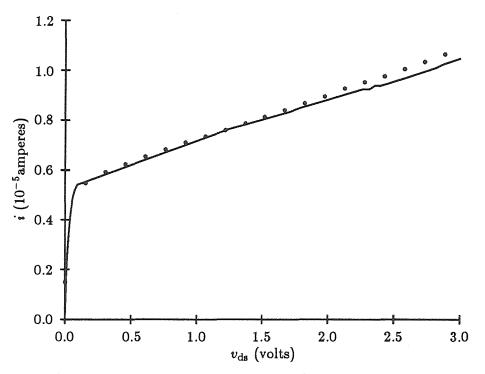

Figure 2.7: Drain current versus  $v_{ds}$  for fixed  $v_{gs}$  for a 2.8-micron channel length transistor. Solid lines are the values predicted by the model. Dots indicate experimental data.

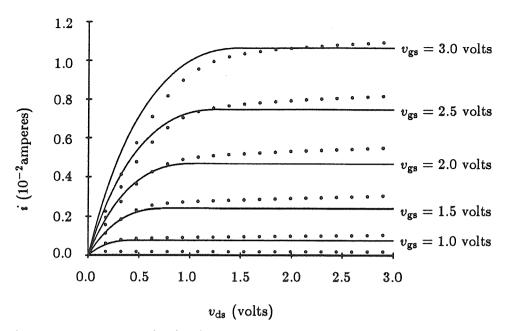

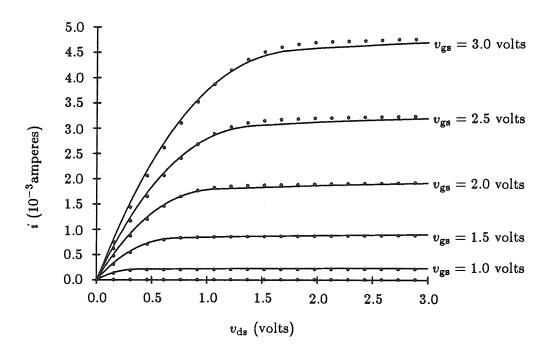

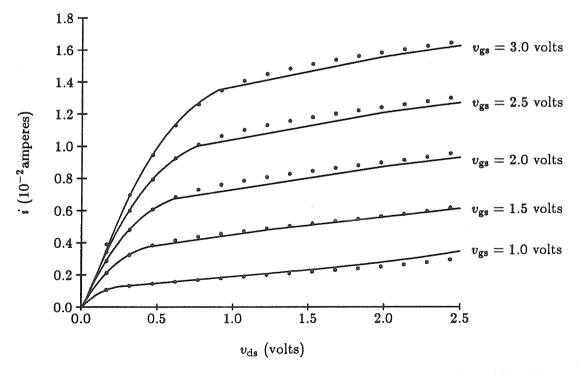

Figure 2.8: Drain current versus  $v_{ds}$  for fixed  $v_{gs}$  for a 0.7-micron channel length transistor. Solid lines are the values predicted by the model. Dots indicate experimental data.

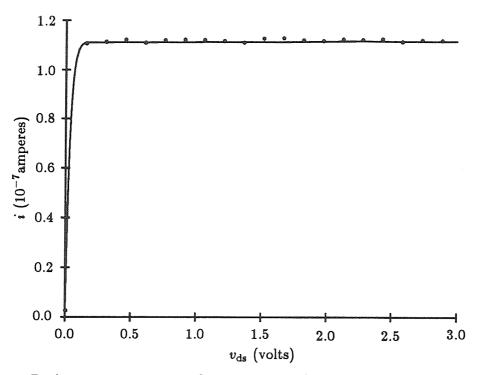

$v_{\rm ds}$  (volts)

Figure 2.9: Drain current versus  $v_{ds}$  for fixed  $v_{gs}$  for a 0.35-micron channel length transistor. Solid lines are the values predicted by the model. Dots indicate experimental data.

Experimental drain families and conductance curves were generated using the Keithley 619 programmable electrometer and Keithley 230 voltage sources under computer control using the Hewlett Packard HP9836 computer. Experiments to determine capacitance used the Boonton capacitance meter. Software for control and graphics was written in Pascal under the UCSD operating system. All parameters were either derived from the process by direct measurement, or were physical dimensions of the layout of a particular device.

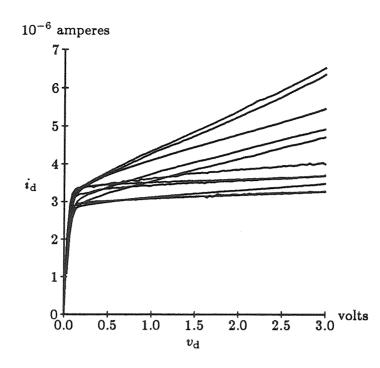

The results of comparing the zero-order model for 50-micron, 2.8-micron, 0.7-micron, and 0.35-micron channel length devices are shown in Figures 2.6, 2.7, 2.8, and 2.9. Drain curves are shown for fixed  $v_{gs}$  ranging from 0 to 3 volts. The theoretical curves use the same set of parameters in all cases.

#### 2.9 Summary

We have formulated a new charge-controlled model for the DC current in the MOS transistor. The model we developed is valid above or below threshold, in saturation or in the ohmic range, and is continuous over all these regions of operation. We have defined a set of natural units for the physical quantities involved in transistor operation. These units have allowed us to express the equations describing transistor operation in dimensionless form, and thus to simplify the analysis. We have seen that the functional form of the equations describing above-threshold operation are far from the long-channel limit, even with 1-micron channel lengths. Subthreshold devices, however, continue to conform to the simple model, even at very small dimensions, as we shall see in Chapter 4. These conclusions have important consequences for the design of digital, as well as of analog, systems.

# Chapter 3

# First-Order Corrections to the Basic Model

There are several first-order effects that need to be added to the model for detailed comparison with submicron devices. The consequences of these first-order effects are visible in Figure 2.9. We have not yet considered the slope of the drain curves in saturation. This dependence of saturation current on drain voltage is due to the change in channel length with drain bias in Equation 2.17. The drain-voltage modulation of channel length is important in today's devices, and becomes crucial as devices scale to submicron lengths. In addition, the conductance of an actual device near the origin is less than that predicted by the simple model, and the discrepancy is larger for larger gate voltages. This behavior is in part due to the dependence of mobility on vertical electric field perpendicular to the direction of current flow, leading to mobility degradation with increasing  $v_{gs}$ . Finally, the experimental saturation currents are less dependent on gate voltage than they should be, even accounting for mobility degradation. This discrepancy is caused by the parasitic resistances of the source and drain. Although resistance is not a device property in the purest sense, it is a necessary and unavoidable byproduct of any real fabrication process. In addition to these phenomena, we will add two other first-order effects to the model. We account for the varying width of the depletion layer in the channel, which corresponds to a decrease in the capacitance  $C = C_b + C_{ox}$ , and for the variation of the vertical electric field  $\mathcal{E}_g$  along the channel.

The several effects mentioned, along with the first-order corrections to the model itself, are of roughly the same magnitude. Some, such as channel-length modulation, increase the current. Others, such as mobility variation and internal resistances, decrease the current. Our *modis operandi* is to find a particular regime of operation in which one of the effects is dominant, and to evaluate the effect there.

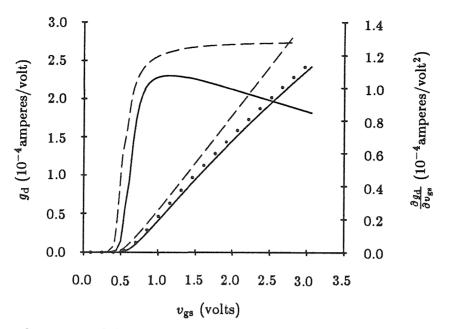

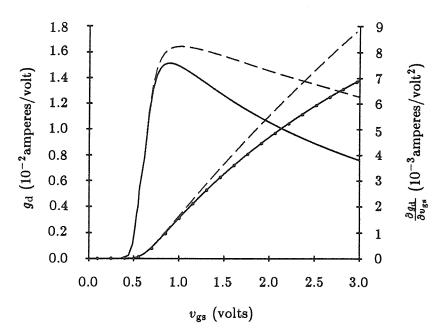

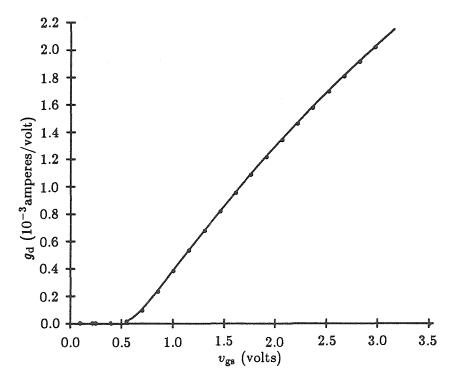

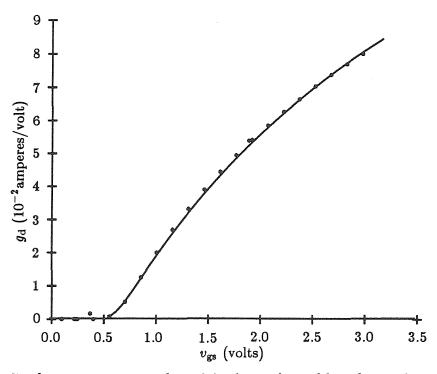

The mobility-degradation effect can be seen quite clearly in a 50-micron channel length transistor in which velocity saturation and series resistance are negligible. If the mobility were constant, the conductance plot shown in Figure 3.1 would be a straight line intersecting at threshold, and the derivative would be constant above threshold. The slope of the derivative curve directly measures the mobility variation with the gate electric field. The conductance of a short-channel transistor shows the effects of the parasitic resistance, which are masked in the smaller currents of a longer channel transistor. Channel-length modulation is best observed in a short-channel device in subthreshold, where there are no mobile-charge carriers to reduce the effect. Current flows by pure diffusion, without velocity saturation to confuse the issue. Electric-field lines from the drain can terminate on mobile electrons as well as on the negative fixed charges in the depletion layer. The density of mobile charge increases at higher gate voltages. We therefore expect a smaller change in channel length at high gate voltages than in subthreshold. To account for this effect, we include the mobile charge in the solution to Poisson's equation for the depletion-layer length.

These effects have been well-studied by other researchers and two and three dimensional analyses have been done, but the results are not computationally efficient to simulate circuits. Because we want a model that is simple enough for circuit simulation, we adopt simple and approximate descriptions of these effects but we stay as close to the physics of the device as possible. The effects mentioned were incorporated into a unified model that was used to generate theoretical curves for measured properties of transistors over a wide range of lengths. We found excellent agreement between theory and experiment. The experimental data we show in this chapter were taken from the devices described in Chapter 2. We present plots of conductance and drain curves both above and below threshold.

## 3.1 Mobility Variation

The vertical electric field acting perpendicular to the channel leads to mobility degradation with increasing  $v_{gs}$  [Garverick 87]. Intuitively, the field from the gate attracts electrons in the channel toward the oxide interface. Conditions at this interface are not as ideal as they are in the silicon crystal, and an electron is more likely to be scattered if it spends more time there. This additional scattering decreases the electron's mean free time, and hence reduces its mobility. This effect can be seen quite clearly in a 50-micron channel length transistor, in which velocity saturation and series resistance are negligible. A plot of the low-field, channel conductance versus gate voltage is shown in Figure 3.1. Also shown in Figure 3.1 is the derivative of the conductance curve  $\frac{\partial g_4}{\partial v_{gs}}$ . If the mobility were constant, the conductance plot would be a straight line with x intercept at threshold, and the derivative would be constant above threshold. The slope of the derivative curve is a direct measurement of the mobility variation with the gate electric field,  $\mathcal{E}_g$ . By adding another term to the scattering model used to derive the velocity saturation, we obtain a form for  $\mu$ :

$$\mu_{\rm eff} = \frac{\mu}{1 + \frac{\mathcal{E}_{\rm g}}{\mathcal{E}_{\rm f}}}$$

We add mobility variation to the model by replacing  $\mu$  in Equation 2.10 with  $\mu_{eff}$ . We calculate the vertical electric field  $\mathcal{E}_g$  from the relation

$$\mathcal{E}_{g} \approx rac{q_{\mathrm{tot}}}{\epsilon_{\mathrm{s}}}$$

where  $q_{tot}$  is the total charge as used in Equation 2.4. For the curve shown in Figure 3.1, the gate electric field was assumed to be constant, and to be equal to the value at the source. Variation of the gate electric field will be discussed in Section 3.4. The parameters  $\mu$  and  $\mathcal{E}_{f}$  can be evaluated directly from the data in Figure 3.1. We found the value of the mobility to be 490 cm<sup>2</sup>/v - s. The results of this refinement to the model and of the uncorrected model are plotted, with the original experimental data, in the figure.

## 3.2 Channel-Length Modulation

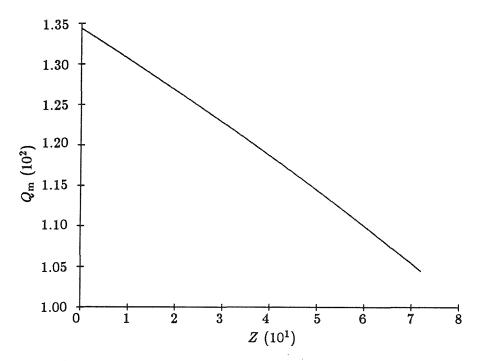

We investigate drain-voltage modulation of channel length by considering a short-channel device in subthreshold, where there are no mobile-charge carriers to reduce the effect. Current flows by pure diffusion, so there is no velocity saturation in the channel proper. We know the surface potential at the source edge of the channel, and know that it is constant to the very edge of the drain depletion region. Hence, a measurement of the slope of saturation current amounts to a direct measurement of the channel in channel length with drain

Figure 3.1: Conductance and slope of conductance for a 50-micron channel length transistor. Dots indicate experimental data; solid lines indicate corrected model curves; dotted lines indicate the model without mobility variation.

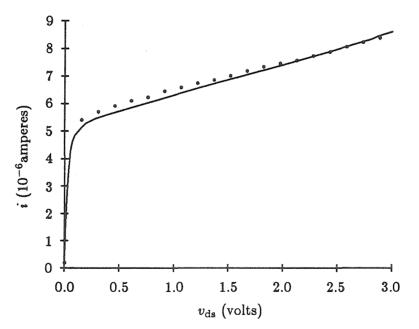

Figure 3.2: Drain current versus  $v_{ds}$  for  $v_{gs} = 0.5$  volts for a 0.7-micron channel length transistor. Dots indicate experimental data; the solid line indicates the corrected model curve.

voltage:

$$\frac{\partial I_{\text{sat}}}{\partial V_{\text{d}}} = \frac{1}{L} \frac{\partial L}{\partial V_{\text{d}}} I_{\text{sat}}$$

(3.1)

where  $I_{sat}$  is the saturation current in the absence of the channel-length-modulation effect. An example of the direct manifestation of the channel-length-modulation effect can be seen in the subthreshold current of a 0.7 micron channel length device in Figure 3.2.

Many models have been proposed for channel length modulation [El-Mansy 77b], [Frohman-Bentchkowsky 69], [Reddi 65], [Popa 72]. To incorporate channel-length modulation into our model, we calculate the effective channel length  $L_{\text{eff}}$  by subtracting the lengths of the depletion layers at source and drain,  $\Delta L_s$  and  $\Delta L_d$ , from the physical channel length:

$$L_{\rm eff} = L - \Delta L_{\rm s} - \Delta L_{\rm d}$$

The actual boundary around the depletion layer near the drain is complicated, involving not only the fixed charges in the depletion layer, but also the mobile charge in the channel in three dimensions [Baum 70,Frohman-Bentchkowsky 69]. Assuming a planar junction at the depletion layer, and using the surface potential at the drain end of the channel, the horizontal electric field at the drain end of the channel  $\mathcal{E}_d$ , and the drain voltage as the boundary conditions in the solution of Gauss's law yields

$$\Delta L_{\rm d} \approx \frac{-\mathcal{E}_{\rm d} + \sqrt{\mathcal{E}_{\rm d}^2 + 8\frac{\rho}{\epsilon_{\rm s}}(v_{\rm d} + \psi_{\rm f} - \psi_{\rm d})}}{2\frac{\rho}{\epsilon_{\rm s}}}$$

(3.2)

A similar equation holds at the source. A simple cylindrical approximation to the twodimensional solution around the drain "corner" in subthreshold gives a value for  $\Delta L_d$  that is  $\sqrt{2}$  times as large as that predicted for a planar junction. We expect a value between 1 and  $\sqrt{2}$  to occur in real devices. The factor derived from Figure 3.2 is 1.4. This value is a parameter of the process and is not a function of the dimensions of a particular device. To add the channel-length-modulation effect to our model, we replaced the value of L in Equation 2.17 by  $L_{\text{eff}}$ . The result of this correction is the model curve shown in Figure 3.2.

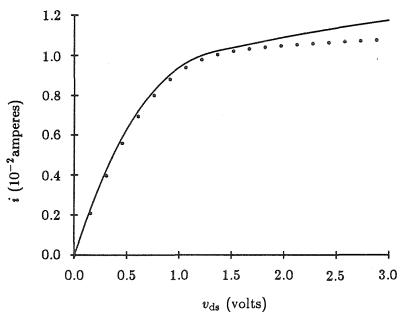

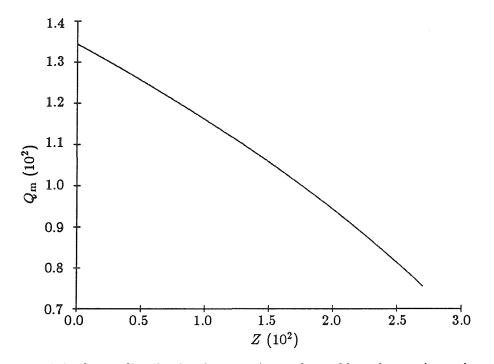

Electric-field lines from the drain can terminate on mobile electrons as well as on the negative fixed charges in the depletion layer [Frohman-Bentchkowsky 69,Popa 72]. The density of mobile charge increases at higher gate voltages. We therefore expect a smaller change in channel length at high gate voltages than in subthreshold. A graphic illustration of the effect of mobile charge on the channel-length modulation can be seen in Figure 3.3, which is a drain curve for higher gate voltage (3.0 volts, well above threshold). The theoretical curve shown is that predicted by the channel-length-modulation effect, ignoring the contribution of mobile charge.

Figure 3.3: Drain current versus  $v_{ds}$  for  $v_{gs} = 3$  volts for a 0.7-micron channel length transistor. Dots indicate experimental data; the solid line is the model curve without the mobile-charge effect.

We define an effective volume charge density  $\rho_m$  at the source and at the drain by normalizing the mobile charge per unit area by the width of the depletion layer normal to

Figure 3.4: Conductance and slope of conductance for a 0.7-micron channel length device. Dots indicate experimental data; solid lines indicate corrected model curves; dashed lines indicate the model without resistance.

the surface, as calculated from Equation 2.1. So  $\rho$  now becomes

$$\rho_{\rm eff} = \rho_{\rm m} + \rho$$

We substitute the value of  $\rho_{\text{eff}}$  in place of  $\rho$  in the calculation of the depletion-layer lengths  $\Delta L_s$  and  $\Delta L_d$ .

Since the mobile charge increases the total charge in the electrostatic equations, it decreases the extent to which the saturation current changes with drain voltage. We call this decrease in the channel-length-modulation effect with mobile charge density the *late effect*. It is clear that the late effect makes the device a better current source and hence, in some sense, more ideal. However, the effect decreases the current-driving capability of the device. The corrected model curve is shown as part of the drain characteristics in Figure 3.8.

#### 3.3 Resistance

Although they are not strictly part of a device model, source and drain resistances must be included as part of the model so that we can compare it with any real measurements. Direct measurements of the sheet resistance of the diffusion layer gave 68 ohms per square. In the test devices, the distance from the metal contact cuts to the edge of the gate was measured to be 5 microns. Since the devices were 50 microns wide, the source and drain resistances were 7 ohms. For a short, wide device 50 microns by 0.7 microns, we measured drain currents up to 10 milliamps. The voltage drop across the 7 ohm source resistance was 70 millivolts, corresponding to an error current of about 15 percent of the spacing between adjacent drain curves. To compute accurate device characteristics, we use a simple model for the parasitic resistance and add lumped source and drain resistors to the model. We simulate this equivalent circuit by iteration, alternately updating  $V_s$  and  $V_d$  and evaluating the model. Figure 3.4 shows the experimental data and the model results with and without resistance. The model uses the same value for the resistivity for all the devices taken from the same wafer.

## 3.4 The Upgraded Model

In addition to the phenomena described above, we added two other first-order effects to the model. The width of the depletion layer in the channel increases with distance towards the drain. This result corresponds to a decrease in the channel capacitance C in Equation 2.8. To add this effect to the model, we interpolate the capacitance linearly between the values at source and drain:

$$C = C_{\rm s} + \beta z$$

where  $\beta = \frac{(C_d - C_s)}{l}$ , and we know the value for  $C_d$  from Equation 2.7. Using this technique is much more accurate than is using a first-order Taylor series. We integrate the equation for current (Equation 2.17) to get a new model equation.

The vertical electric field  $\mathcal{E}_g$  also varies along the channel, reaching a minimum at the drain, affecting the mobility variation in Equation 3.1 at high drain voltages. We use

$$\mathcal{E}_{g} = \mathcal{E}_{gs} + \alpha z$$

where  $\alpha = \frac{(\mathcal{E}_{gd} - \mathcal{E}_{gs})}{l}$ , and  $\mathcal{E}_{gd}$  is calculated from Equation 3.1 evaluated at the drain. We substitute this value for the vertical electric field, and we derive a new current equation.

#### **3.5** Experimental Results