The Tree Machine: A Highly Concurrent

Computing Environment

Thesis by

Sally Anne Browning

In Partial Fulfillment of the Requirements

for the Degree of Doctor of Philosophy

California Institute of Technology

Pasadena, California

1980

(Submitted January 15, 1980)

### Acknowledgements

The Computer Science Department at Caltech provides a marvelous backdrop for learning how to do research. The faculty's unconventional approach to Computer Science is hard to resist.

Two faculty members deserve special thanks. Carver Mead and I have maintained a dialog about Oregon and about software systems since my first week at Caltech. He tree machine proposed the to me as a potentially interesting concurrent programming environment suited to That proposal led to the research described here. Martin Rem not only influenced the development of the tree machine notation, but was instrumental in constraining the scope of the research to a managable set of questions. return to Holland in 1978 provided me with an excuse to see a lot of Europe while consulting him about tree machines.

Three of my fellow students have also contributed to this research. Bart Locanthi provided insights into the maze of numerical analysis algorithms and suggested improvements to the processor instruction set. Jim Rowson and Mike Ullner not only were involved in the design of many of the algorithms included here, but also had the fortitude to read and correct this document. Many thanks.

During my first two years at Caltech, I was supported by a predoctoral fellowship from the International Business Machines Corporation. My research has been partially supported by the Defense Advanced Research Projects Agency under contracts \$N00123-78-C-0806 and \$N00014-79-C-0597.

### Abstract

An architecture for a VLSI multiprocessor machine is proposed. The processors are connected together as a binary tree. A collection of algorithms are mapped onto the tree machine. These include heap sort, transitive closure, the travelling salesman, and matrix inversion, among others. A model of computational complexity for the tree machine is suggested, and the algorithms are analyzed in the context of that model. A notation for expressing the algorithms is described, a processor design is proposed, and a compiler for the notation and processor is presented.

# Table of Contents

| I | ntrod  | uction                                       |

|---|--------|----------------------------------------------|

| 1 | . The  | Tree Machine                                 |

|   | 1.1    | The Tree Machine                             |

|   | 1.2    | A First Step: Simula                         |

|   | 1.3    | A Second Step: CSP18                         |

|   | 1.4    | A Tree Machine Notation                      |

| 2 | . The  | Analysis of Algorithms39                     |

|   | 2.1    | Random Access Machine Model40                |

|   | 2.2    | Reference Machine Model45                    |

|   | 2.3    | Turing Machine Model46                       |

|   | 2.4    | Tree Machine Model49                         |

|   | 2.5    | Sorting                                      |

|   | 2.6    | Transitive Closure                           |

|   | 2.7    | Closing Remarks                              |

| 3 | . NP-( | Complete Problems77                          |

|   | 3.1    | An Introduction to NP-Completeness           |

|   | 3.2    | The Clique Problem                           |

|   | 3.3    | The Color Cost Problem                       |

|   | 3.4    | The Travelling Salesman Problem              |

|   | 3.5    | NP-Complete Problems and the Tree Machine105 |

| 4 | . Matr | rix Manipulation                             |

|   | 4.1    | Matrix Multiplication                        |

|   | 4.2    | Matrix Inversion                             |

|   | 4.3    | Solving Ax=y and AX=B                        |

|   | 4.4    | LU Decomposition128                          |

|   | 4.5    | Matrix Problems on the Tree                  |

| 5. The | Processor Architecture       |

|--------|------------------------------|

| 5.1    | An Overview of the Processor |

| 5.2    | The Size of Each Processor   |

| 5.3    | The Instruction Set          |

| 5.4    | Code Generation              |

| 5.5    | Loading the Tree Machine     |

| 5.6    | Floating Point               |

| 6. "As | Lovely as a Tree"            |

| 6.1    | Concurrency                  |

| 6.2    | Communication                |

| 6.3    | Future Directions            |

| Refere | nces                         |

•

# List of Figures and Tables

| 1.1.1 | Some Potential Wiring Patterns                 |

|-------|------------------------------------------------|

| 1.1.2 | External Connections for the Wiring Patterns8  |

| 1.1.3 | Allocation Technique for Mismatched Fanouts12  |

| 1.1.4 | Tree Characteristics with Mismatched Fanouts12 |

| 1.1.5 | A Planar Layout of a Binary Tree Machine15     |

|       |                                                |

| 2.1.1 | Vector Summing Solution #1 (RAM model)42       |

| 2.1.2 | Vector Summing Solution #2 (RAM model)43       |

| 2.1.3 | Machine Language Translation44                 |

| 2.3.1 | A Turing Machine46                             |

| 2.3.2 | Sample Turing Machine Tape47                   |

| 2.3.3 | Turing Machine Program: Addition49             |

| 2.4.1 | Vector Summing Tree, n=1551                    |

| 2.4.2 | The Vector Summing Tree                        |

| 2.4.3 | The vSumRoot Processor55                       |

| 2.4.4 | The vSum Processor                             |

| 2.4.5 | The vSumLeaf Processor                         |

| 2.5.1 | The Sort Tree                                  |

| 2.5.2 | The sort and sortLeaf Processors64             |

| 2.6.1 | Warshall's Algorithm for Transitive Closure67  |

| 2.6.2 | The Transitive Closure Tree                    |

| 2.6.3 | The closureRoot Processor                      |

| 2.6.4 | The node Processor74                           |

| 2.5.6 | The endNode Processor75                        |

|       |                                                |

| 3.2.1 | Problem Subgraphs in Planarizing Technique80   |

| 3.2.2 | Algorithmic Generation of Potential Cliques81  |

| 3.2.3 | The Connection Plan for the Clique Tree84      |

| 3.2.4 | The cliqueRoot Processor85                     |

| 3.2.5 | The clique Processor87                         |

| 3.2.6 | The cliqueLeaf Processor                       |

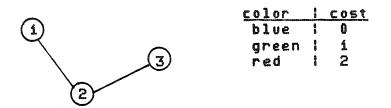

| 3.3.1 | A Sample Graph for the Color-Cost Problem91           |

|-------|-------------------------------------------------------|

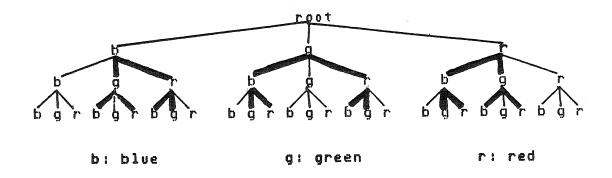

| 3.3.2 | Solution to Sample Coloring Problem93                 |

| 3.3.3 | The Connection Plan for the Color-Cost Tree93         |

| 3.3.4 | The colorRoot Processor94                             |

| 3.3.5 | The coloring Processor96                              |

| 3.3.6 | The colorLeaf Processor                               |

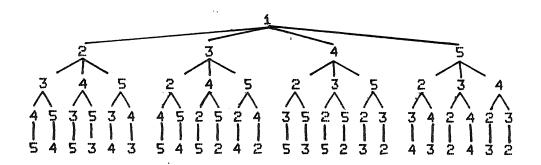

| 3.4.1 | Sample Salesman Tree, n=598                           |

| 3.4.2 | Travelling Salesman Example                           |

| 3.4.3 | Solution Tree for Example Problem                     |

| 3.4.4 | The Travelling Salesman Tree                          |

| 3.4.5 | The salesmanRoot Processor                            |

| 3.4.6 | The salesman Processor                                |

| 3.4.7 | The salesmanLeaf Processor                            |

|       |                                                       |

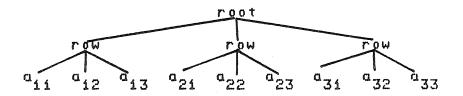

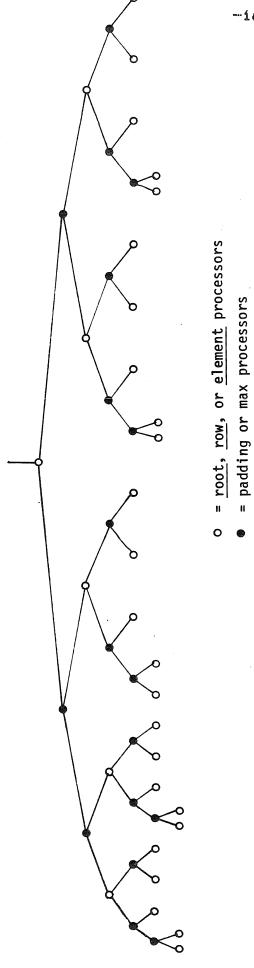

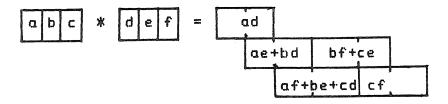

| 4.1.1 | Matrix Multiplication Processor Tree                  |

| 4.1.2 | Sample Loaded Matrix Multiplication Tree              |

| 4.1.3 | The root Processoriii                                 |

| 4.1.4 | The row Processor                                     |

| 4.1.5 | The element Processor                                 |

| 4.2.1 | An Augmented Matrixii5                                |

| 4.2.2 | The Matrix Inversion Processor Tree                   |

| 4.2.3 | Time Complexity for Inverting an nxn Matrix           |

| 4.2.4 | The root Processor                                    |

| 4.2.5 | The row Processor                                     |

| 4.2.6 | The element Processor                                 |

| 4.2.7 | Time Complexity for Column Organization125            |

| 4.3.1 | Time Complexity for Solving AX=B on the Tree128       |

|       |                                                       |

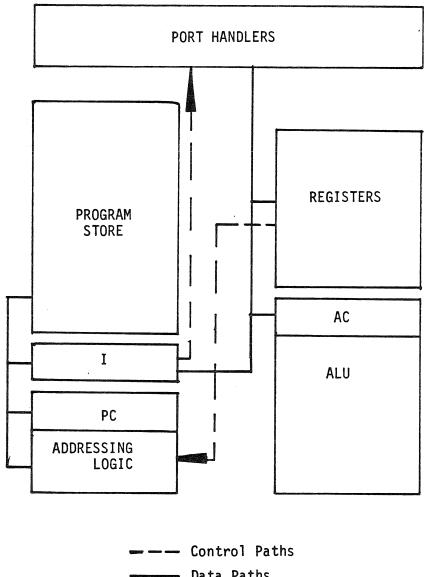

| 5.1.1 | A Block Diagram of the Processor                      |

| 5.2.1 | Space Requirements of the Tree Machine Algorithms.136 |

| 5.3.1 | Control Flow Instructions                             |

| 5.3.2 | Communication Instructions                            |

| 5.3.3 | Data Flow Instructions                                |

| 5.4.1 | The Assignment Statement Syntax                 |

|-------|-------------------------------------------------|

| 5.4.2 | Code Generation for the Assignment Statement145 |

| 5.4.3 | Code Generation for the Message Statement146    |

| 5.4.4 | Conditional and Repetitive Statement Syntax147  |

| 5.4.5 | Conditional and Repetitive Statement            |

|       | Code Generation148                              |

| 5.4.6 | The newColorSorter Processor                    |

| 5.4.7 | The padding and bin Processors                  |

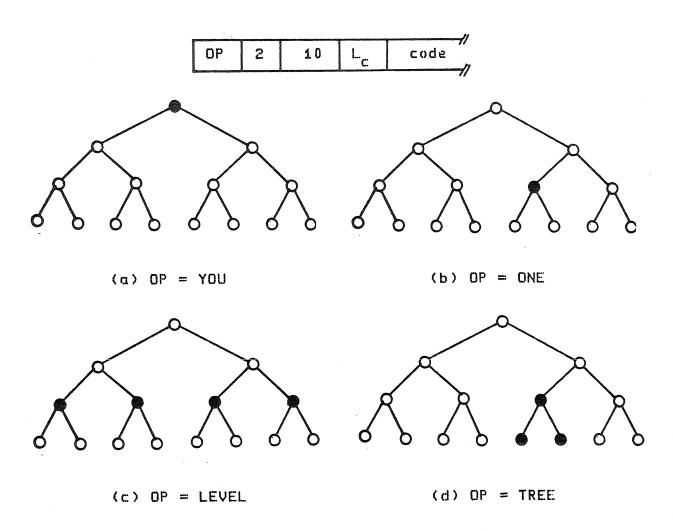

| 5.5.1 | Program Header                                  |

| 5.5.2 | Assigning Unique Addresses to Processors152     |

| 5.5.3 | Path-Oriented Address Assignment                |

| 5.5.4 | Code Stream Opcodes                             |

| 5.5.5 | Loading a Tree Machine                          |

| 5.6.1 | Matrix Multiplication/Inversion Tree for n=5162 |

| 5.6.2 | Multiplication: The Sum of Partial Products164  |

| 5.6.3 | Division: Blazingly Slow                        |

|       |                                                 |

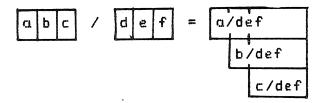

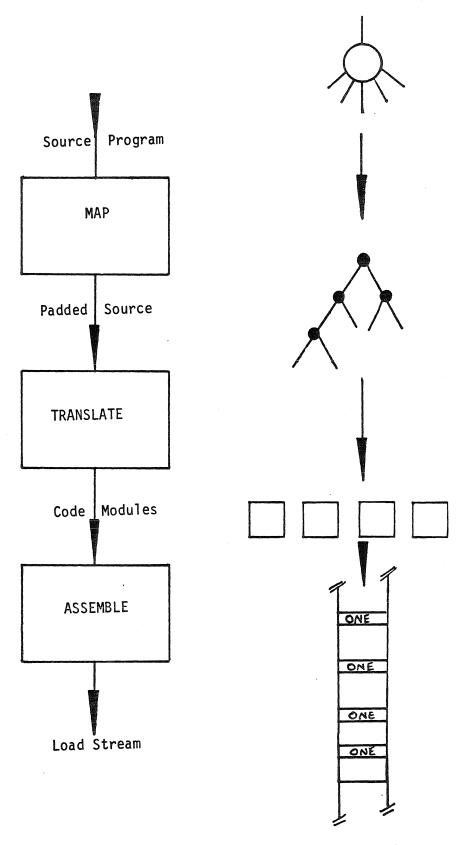

| 6.3.1 | The Compilation Process                         |

## Introduction

As very large scale integration (VLSI) becomes a reality, we have the opportunity to redefine the notion of what a computer is. The traditional view of a single large processing unit physically separated from a large store by a memory bus is certainly realizable in VLSI. But because processing elements and storage elements can both implemented in silicon, we may now consider other architectures.

One new approach to designing computers is to embed an algorithm directly into silicon. There are several examples of special purpose designs in the literature, concentrated in the Proceedings of the Caltech Conference on Very Large Scale Integration held in January of 1979.

My research has centered around the notion of a general purpose computing environment that capitalizes on the properties of VLSI. Ivan Sutherland and Carver discussed the properties of VLSI in "Microelectronics Computer Science", published in Scientific American September of 1977. Among the things they mention are 1) that most of the space on a chip is occupied by the wires that carry control and data information to the function blocks, 2) that regularity of the interconnect means that it will be less expensive in both design time and area, that local communication is less expensive than global communication. In the concluding remarks, they say

"We believe adequate theories that account for the cost of communication will be an important guide for designing the machines that have been made possible by the integrated-circuit revolution."

In the pages that follow, a general purpose machine presented. It is a collection of small processors, each with some local storage, connected together as a binary has a regular interconnection pattern and relies on local communication only. The machine description is accompanied by a notation that requires explicit statement of communication and a model of computational complexity in which the time cost is dominated by the communication cost. The notation and computational model are used to map of algorithms from the sequential view computation to the highly concurrent world of the tree The model of computation, notation, body algorithms, and infant machine design provide a first cut at the "adequate theory" that Sutherland and Mead describe.

The first chapter of this dissertation introduces the tree machine, and discusses the reasons why a tree-structured interconnection pattern was chosen. The notation used to program the tree is also presented, along with some backgound information about how the notation evolved. The second chapter begins with a discussion of traditional complexity theory in order to lay a foundation for the discussion of complexity on the tree machine. The chapter closes with a look at how some familiar algorithms, heap sort and transitive closure, can be mapped onto the tree machine.

The third and fourth chapters present the main body of tree machine algorithms. The third chapter introduces the notion of NP-completeness and presents algorithms for three

NP-complete problems, including the familiar travelling salesman problem. The fourth chapter addresses some matrix manipulation algorithms. In both chapters, the algorithms are analyzed according to the computational model introduced in Chapter 2.

The fifth chapter introduces the beginnings of a system design for the tree machine. It contains a block level design of the individual processors, an instruction set, a strategy for compiling the tree machine notation into the instruction set, and a protocol for loading the tree.

The sixth and final chapter talks about the contributions this work has made in emphasizing that communication is the most significant measure of cost in a highly concurrent programming environment. There is a collection of hard and as yet unsolved problems that I have found during the course of this research. Some of these are mentioned in the last chapter, pointing to future directions the research might take.

### Chapter One

### The Tree Machine

Processors and memory have historically been designed and implemented as distinct modules separated by a bus. This arrangement made sense at one time since the two in completely different media, and the bus made communication between them possible. With the arrival silicon technology, however, both logic and memory can be implemented in the same medium. Why not implement them the same chip? Better yet, why not implement the traditional large processor and large memory as a collection of small modules, each with a small processor and a small memory. Might not the sum of the parts greater than the whole?

The next pages present a proposal for a machine made in just that way: a large number of small, almost inconsequential processors are assembled into a system that can outperform a large single processor system. The machine proposed here is called a tree machine: the many processors are connected as a binary tree.

Chapter One begins with a description of the tree machine, concentrating on the rationale behind the machine design. Following the machine description, a notation for programming it is given. The second chapter begins with an introduction to traditional complexity theory, recalibrates the theory to the highly concurrent world of the tree machine, and looks at some familiar algorithms in the context of the tree machine. The third chapter looks at

some problems that are intractable on single processor machines. The fourth chapter presents some matrix manipulation algorithms. The fifth chapter describes the underlying processor architecture and the system support programs. The final chapter reiterates the high points of the previous seven, and talks about future directions.

#### 1.1 The Tree Machine

The tree machine is composed of many tiny processors, each with a small amount of program store, a few registers for data, and general arithmetic and logic capabilities. The processors are connected together to form a binary tree. That is, each processor has a single parent processor and all but the leaves have two descendents. These connections are the only communication paths in the system.

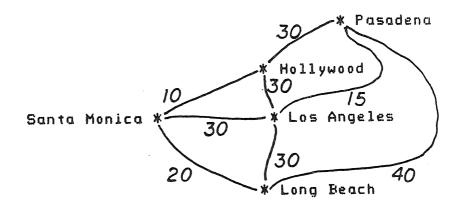

The next paragraphs will attempt to answer a series of questions about the tree machine: Why a tree? Why a binary tree? Is it a special purpose machine? Is it practical to build? If so, how can it be programmed?

### 1.1.1 Why a tree?

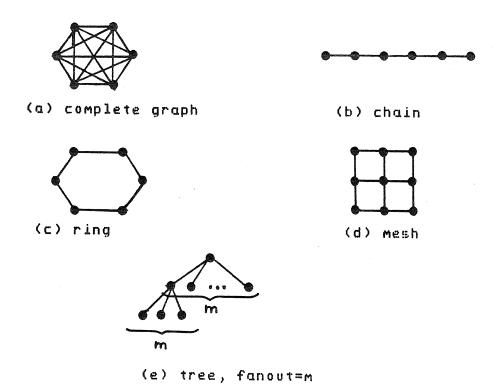

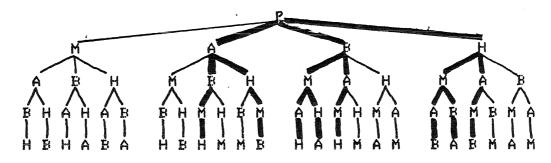

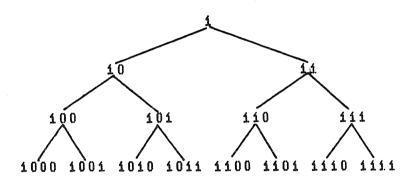

Suppose you have a pile of ten thousand processors, and have been given the task of organizing them as a system. How would you wire them together? The most general way is to connect each processor to every other processor, as shown in figure 1.1.1(a). This might work for tens of processors, but is nearly impossible for thousands of

processors. In this case, each processor must have 9999 connections: you would end up with a hopeless jumble of about 50 million wires!

Suppose you connect the ten thousand processors together in a long chain, a la figure 1.1.1(b). Then there are only ten thousand wires, one per processor. But suppose the first processor wants to communicate with the last one: the message must travel the whole length of the chain, through 9998 intermediate processors. Hooking the ends of the chain together into a loop, as in figure 1.1.1(c), softens the blow a little. The longest distance a message might go is half way: through 4999 processors.

Another option is to make some kind of rectangular mesh out of the processors. Figure 1.1.1(d) shows one such pattern. Here the number of wires is manageable, and the worst case access time is faster than either the chain or the ring. The ten thousand processors can form a 100 by 100 grid; the most distant processors are separated by 197 intermediate processors.

The final wiring pattern shown in figure 1.1.1 is a tree. Here again, the number of wires is proportional to the number of processors, but the access time is considerably better than any of the other schemes. Suppose the tree is a 10-ary tree: each processor has 10 descendents. The distance between the root and the leaves is  $\log_{10}10,000=4$ . The longest distance any message must travel is twice the height of the tree.

The table in figure 1.1.1 summarizes the wire requirements and access time for the five wiring patterns discussed.

| wiring pattern     | # wires       | access time |

|--------------------|---------------|-------------|

| (a) complete graph | n(n-i)/2      | 1           |

| (b) chain          | n-i           | n-1         |

| (c) ring           | n             | n/2         |

| (d) mesh           | 2(n-\sqrt{n}) | 2 (√n-i)    |

| (e) tree, fanout=m | n-i           | 21 o g _ n  |

Figure 1.1.1 Some Potential Wiring Patterns.

The fast access time to any processor in the tree is part of the answer to the question, "Why a tree?".

part of the answer has to do with the number of Another external connections; how many processors reside on the "edaes" of the pattern. If, for example, several processors reside on a chip, how many pins must be made available to wire the chips together? Figure 1.1.2 shows the connection requirements for the five wiring patterns of figure 1.1.1. Notice that the chain, the ring and the tree are the winners: in each case, the number of pins required is independent of the number of processors on a chip. technology improves and more and more devices can be put on a chip, we don't want to have to move to larger and larger packages.

n = number of processors in system

m = number of processors on a chip

| wir. | ing pattern     | e          | xternal connections |

|------|-----------------|------------|---------------------|

| -    | complete graph  | (          | n(n-1) - m(m-1))/2  |

| (b)  | chain           | 2          |                     |

| (c)  | ring            | a          |                     |

| (d)  | mesh            | 4          | M                   |

| (e)  | binary tree (le | af chip) i |                     |

|      | binary tree (no | n-leaf) i  | + (m+1)             |

Figure 1.1.2 External Connections for the Wiring Patterns.

The number of external connections per chip in a tree machine depends on whether the chip contains leaf nodes or not. Chips that provide the leaves of the tree need only a single external connection. Non-leaf chips need not only the external connection for the root, but one for each internal port of the processors in the lowest level on the chip as well. This is shown below for three processors per chip and five chips in the system.

What this means is that the leaf chips are appropriate to VLSI technology: the number of external connections does not depend on the number of processors on the chip. The chips used to build the upper levels of the tree are better suited to medium or large scale integration since the number of connections grows linearly with the number of processors.

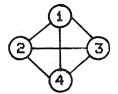

So far we have discussed physical properties of the tree. There are some conceptualization issues that also support the tree interconnection structure. The tree is an acyclic structure: there are no circular paths. This facilitates proof of freedom from deadlock. While deadlock proofs must be constructed for each tree machine program, the hierarchical nature of the tree leads to some general proof techniques.

There are a couple of ways to show that a program is free of deadlock. One, proposed by Martin Rem [Rem79b], is to draw a communication graph for the program. If that (directed) graph, a state machine, has no traps, that is, nodes that can be entered but not left, the program is free of deadlock. Another way of showing freedom from deadlock is to show that the communication can be modelled as a special kind of Petri net called a marked graph. Young-il Choo has investigated this technique for his Masters Thesis

[Choo80]. In both techniques, the hierarchy of tree machine programs makes it possible to characterize the behavior of lower levels of the tree in terms of the behavior of their external ports. As a result, proofs at each level of the hierarchy need only look one level down into the tree (instead of all the way to the bottom), and proofs can be completed with induction.

These, then, are the reasons behind choosing to wire a large number of processors together as a tree. The tree is the only one of the simple, planar wiring schemes that has both fast access time to any processor in the structure a constant external connection function. In addition, the tree is an acyclic structure: it is easy to show that a is free of deadlock. A more complete program including wireability considerations, treatement of analysis of nonplanar structures like the hypercube, has been done by Bart Locanthi [Locanthi79].

## 1.1.2 Why a binary tree?

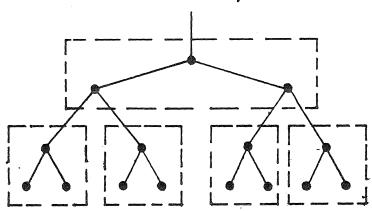

In figure 1.1.1, a tree with arbitrary fanout was shown. Because the tree machine is an architectural proposal, a specific fanout must be chosen. Suppose that a fanout m>1 is chosen. Now, suppose that we have a tree machine program that requires a fanout of f and uses p processors. There are three cases to consider: 1) f=m, 2) f(m), and 3) f(m). What happens to the height and consequently the number of processors in the solution tree?

If f and m are equal, it's easy. The program and the tree match. Exactly p processors are required and the resulting

tree will be log\_p processors high.

If f is less than m, we will allocate only f of the m descendents of each processor. Figure 1.1.3(a) shows the allocation scheme for f=2 and m=3. This results in a tremendous waste as the tree gets deeper: the number of idle processors grows exponentially with the depth of the tree.

If f is greater than m, we must use several processors to simulate the increased fanout. Figure 1.1.3(b) illustrates the method. In particular, f-m processors are used to supply the proper fanout at each logical level of the tree. The padding processors form a piece of the tree that is log<sub>m</sub> f processor high. Thus we consume extra processors at a rate linearly related to p, the number of processors required by the problem.

Figure 1.1.4 gives the precise formulae for the height and number of processors in the solution trees that arise the three cases. Clearly, we want to avoid the exponential waste that arises when the fanout of the physical machine is bigger than that required by the problem. But each program will be different; we can not always guarantee perfect fit. Thus the fanout built into the hardware should be the smallest useful one. The linear waste of simulating larger fanouts is considerably less costly than the exponential waste caused underallocating by processors in the tree. A binary tree has the smallest fanout of all trees, ignoring the degenerate case, the chain.

f=hardware fanout m=program fanout

Figure 1.1.3 Allocation Technique for Mismatched Fanouts.

m = tree machine fanout

f = program fanout

p = required processors

| case  | tree height                                  | extra processors                                        |

|-------|----------------------------------------------|---------------------------------------------------------|

| f < m | log <sub>s</sub> p                           | log <sub>f</sub> p-i<br>m <sup>i</sup> - f <sup>i</sup> |

|       | <b>V</b>                                     | i=0                                                     |

| f = m | log <sub>f</sub> p                           | 0                                                       |

| f > m | (log <sub>f</sub> p)(log <sub>m</sub> f + i) | (f-m)(p-1)/f                                            |

Figure 1.1.4 Tree Characteristics with Mismatched Fanouts.

The table above is just a little simplistic. While there is a linear growth in the number of processors required to establish the program fanout when the physical fanout is too small, the resulting tree is unbalanced whenever the program fanout is not a multiple of the physical fanout. The physical structure is balanced, and must be as deep as the longest path, given as the tree height in figure 1.1.4. The correct number of unused processors must also include the ones that are unneeded but present because of the unbalance. This number is

$$\left(\sum_{i=0}^{h} m^{i}\right) - p \quad \text{where } h = (\log_{f} p)(\log_{m} f + 1)$$

This number grows exponentially with the depth of the tree. If there were some way to keep the tree balanced, the number of extra processors would grow linearly as predicted in the table above. James T. Kajiya of Caltech has proposed a tree-like architecture that can balance itself. It has a few extra communication paths that allow the location of parent and children processors to be less rigid than in a strict binary tree. The proposed structure retains the planar layout feature, and as such, may be practical to build. If the work continues to be as promising as the early reults, his structure may be the way to build a binary tree.

## 1.1.3 Is the Tree Machine a Special Purpose Machine?

In the past decade several machines that intermingle logic and memory have been designed, each with a specific purpose in mind. A survey paper by Thurber [Thurber75] describes many of them. More recent examples are the hexagonal array machine of Kung and Leiserson [Kung79] for matrix multiplication, radar tracking machines [Denny79], and sorting machines [Armstrong77,Bently79]. Is the tree machine yet another special purpose machine?

No. We will show that the tree machine is a general purpose computing machine. In the next few chapters examples of a wide range of algorithms for the tree machine

are presented. In each case, a special purpose machine could be, and often has been, designed to do the task more quickly. But none of those special purpose machines can do the variety of problems that the tree machine can: one operation is made fast at the expense of another. The tree machine presents a system with balanced capabilities; it is general purpose.

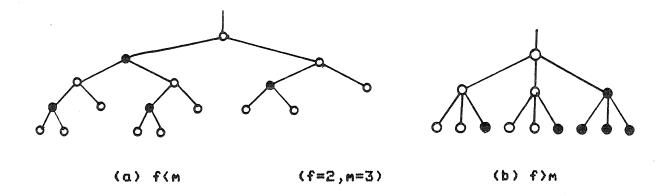

#### 1.1.4 Is it Practical to Build a Tree Machine?

The question of buildability has already been answered, in part. The wiring pattern is planar and the number of wires grows linearly with the number of processors. Figure 1.1.5 shows a possible layout of processors on a chip. Notice that the length of the wires doubles every two levels from the leaves to the root. Notice also that the amount of space available for a processor grows with each level. There is enough room to build the beefier drivers needed to insure constant communication time between levels of the tree. Bart Locanthi has addressed the question of power requirements for the tree machine in [Locanthi79].

A processor architecture is proposed in the fifth chapter. It too is buildable. In fact, if we assume that a logic cell is roughly equivalent in area to four dynamic memory cells, and that the processor is made up of equal number of memory and logic cells, about ten processors can be put on a chip using the same design rules that produce 64K RAMs. Given the very large scale integration of the 1980's we can expect several hundred processors on a chip!

Figure 1.1.5 A Planar Layout of a Binary Tree Machine.

### 1.1.5 How is the Tree Machine Programmed?

Other tree-connected machines have been proposed that identify potential concurrency in an algorithm written in a higher level language. Examples are the applicative language machine of Mago [Mago791 and the various LISP machines [Keller78, Locanthi80].

The philosophy proposed here is different. We assume that the programmer is the ultimate expert on the algorithm. We expect the algorithm to be designed with concurrency in mind from the beginning. To that end, a high level programming notation is introduced in the next section, and used throughout the rest of this paper. Chapter Six describes a compiler that provides the mapping from logical to physical fanout, but the programmer must break the problem into modules that will run on the processors of the tree machine. A tree machine algorithm is successful only if the programmer fully understands the problem at hand.

The remainder of this chapter shows the evolution of the tree machine notation. The original algorithms were programmed in Simula, an object-oriented language described briefly in section 1.2. As this proved unsatisfactory due to inadequate communication primitives, the algorithms were

reprogrammed in CSP, a notation specifically designed interprocess communication facilities. CSP is the subject of section 1.3. unsatisfactory This too was machine architecture is not underlying the because for tree machines reflected in the notation. A notation reflects the architecture has developed, and is described in section 1.5. It is used for the algorithms presented in later chapters.

## 1.2 A First Step: Simula

Simula [Birtwhistle73] is essentially a super-set of Algol-60 with an important addition: the class data type. A class is a collection of data and procedure declarations bound together as a single unit. The data is local to the class object, and the procedures manipulate the data. In fact, if locality of data is emphatically enforced, the only access to the data stored in a class instance is through procedure calls. Then as long as procedure functionality is preserved, the underlying implementation can be modified without affecting existing programs that reference the class.

Each class instance can be thought of as an independent machine, responding to well-defined requests from the world in the form of procedure calls. This outside metaphor is useful for describing concurrent programs. The data attributes correspond to local storage cells, the from by messages actions initiated to procedures neighboring processors.

Another feature of Simula is the ability to factor out things common to a set of related classes. These common attributes are combined into a <u>superclass</u>, that is, a class which is an antecedent of all the others. The <u>subclasses</u>, descendents of the class of common attributes, provide a definition of the variant parts.

This factoring technique leads to hierarchical definitions. tree machine, for example, can be defined hierarchically. CLASS processor might define the hardware capability at each node: number of registers, words of program store, communication protocol. This class is a superclass of the collection of classes representing the code to solve each problem. That is, CLASS sort might supply program text for heap sort while CLASS <u>clique</u> describes the algorithm for finding the largest clique in a Each class is a subclass of CLASS processor. sharing the same hardware definition.

Simula is, however, intended for expressing programs that will run on single processor. There is no facility for sending messages between processors. Procedure calls are an inadequate substitute because the calling processor is blocked until a return from the called processor is executed. There is also no clean way to indicate concurrent execution, although it can be simulated at the expense of many lines of code irrelevant to the problem at hand.

Another problem with Simula is its verbosity. A tree machine algorithm typically involves several different processor definitions, each doing only a small piece of the computation. The collection of processors must be viewed

together in order to understand the algorithm. A language like Simula, with many ways to say the same thing and requiring many symbols to say anything, forces lengthy descriptions at the expense of clarity.

The original tree machine algorithms were programmed in Simula and appear in [Browning79c].

### 1.3 A Second Step: CSP

Hoare's notation for Communicating Sequential Processes (CSP) [Hoare78] certainly doesn't suffer from verbosity. He bases CSP on the concise, restrictive language proposed by Dijkstra [Dijkstra76], adding message-passing facilities and the ability to describe concurrent computation.

I will begin with a description of Dijkstra's language, then describe Hoare's additions, and finally give a critique of my experiences with CSP. The syntax that I use does not exactly match that used by Dijkstra or Hoare, although the semantics are the same.

#### 1.3.1 The Basic Statements

Dijkstra defines a language with five kinds of statements: skip, abort, assignment, a loop, and a conditional statement. There are no procedure calls, no goto's, no choice among ten different ways to write a loop.

There is a unifying notion of a guarded command. The guard is a condition. If the guard is true the command that

follows may be executed. The statement "if c is less than n, interchange the values of c and n" is written as

More than one statement can be included in the command following the guard. Each statement is separated from the next by a semicolon. There is no semicolon following the last statement in the command.

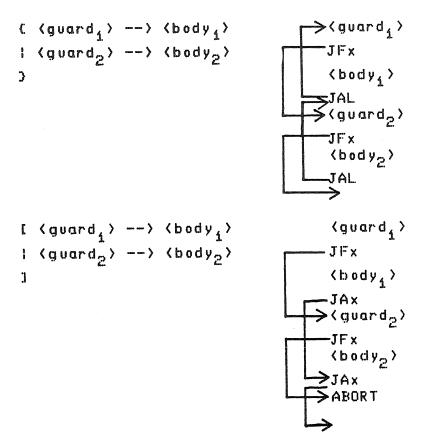

Guarded commands appear in the conditional and loop statements. The conditional statement is analogous to the if-then-else and case statements of Algol-style languages.

It has the form

[ guard --> command ! guard --> command ... ! guard --> command ]

There can be as many guarded commands included in the statement as desired. There is no implied order in the attempt to satisfy a guard, however. That is, unlike Algol, Simula, Pascal, etc, if the second guard is tested and found true, it does not mean that the first guard is not true. There is no catchall <u>else</u> condition that is accepted when all other guards are false. In other words, each guard must be fully specified.

The guarded command given above can be written as a conditional statement:

The second guard,  $c \ge n$ , must be included even though the command that follows,  $\underline{skip}$ , is a no-op. When no guard within a conditional statement is satisfiable, the conditional statement fails and the program will abort.

The other statement that contains guarded commands is the loop construct. It is written

C guard --> command I guard --> command ... I guard --> command )

The statement is executed repeatedly as long as any guard can be satisfied. When none of the guards are true, the loop terminates. The loop construct never aborts. It can, however, never terminate. Semantically, there is no difference between nontermination and abortion [Dijkstra76,p.35].

The sample conditional statement can also be written as a loop:

$$\{c < n \longrightarrow c, n := n, c\}$$

The loop will be executed at most once. If c is at least as large as n, the guard is not satisfiable, and the loop is terminated without the values of c and n being swapped. If c is less than n, the values are interchanged and the guard is reevaluated. This time c is certainly larger than n and the loop is terminated.

The equivalent of Algol's <u>for</u> loop is written with explicit initialization, testing, and incrementing of the control variable. There is no special language construct.

The <u>skip</u> statement, as mentioned above, is a no-op. The <u>abort</u> statement causes an error termination of the program. The assignment statement is much like assignments in Algol-style language, except that a list of variables can appear on the left side, with a corresponding list of values on the right. These are all valid assignment statements:

It must be remembered, however, that all of the expressions on the right hand side of the assignment are evaluated before any assignment is made to variables on the left hand side.

### 1.3.2 Statements to Express Parallelism

The language constructs just described are used to define sequential, though possibly non-deterministic, programs. To these Hoare has added a message sending capability, a class-like structure for defining process units, and statements to specify parallel execution.

### 1.3.2.1 Messages

A message has a name and, optionally, some arguments. Examples are <u>increment</u> or <u>load(a)</u>. In the first case, the message name carries sufficient information. In the

second, additional information is provided by the argument.

Messages are always sent to and received from named processes. The process name is separated from the message name bγ a symbol indicating the direction communication. An exclamation point (!) means send message to the named process. A question mark (?) means receive this kind of message from the named process. message is sent only when both the sender and receiver are willing to process it. Input statements, those with a appear as quards, but output statements cannot. input statement guard is satisfiable if the specified message can be received from the specified process.

### 1.3.2.2 Process Definitions

A process definition specifies local data attributes and some program text that accepts, sends, and responds to messages from other processes. It also supplies a generic name for the kind of process. Processes are replicated in arrays, with a subscript appended to the generic name. For example, to model a bucket brigade, a process <u>fireman</u> might be defined and replicated fifty times:

```

fireman(i:1..50)::

{ fireman(i-1)?bucket --> fireman(i+1)!bucket }

```

Here a subscript, i, indicates one of the fifty firemen. A fireman is prepared to receive a bucket from the left and pass it to the right.

Suppose the empty buckets travel back to the well through the same brigade, but from right to left. The program text

for fireman can accommodate the change:

```

fireman(i:1..50)::

{ fireman(i-1)?bucket --> fireman(i+1)!bucket

! fireman(i+1)?empty --> fireman(i-1)!empty }

```

The endpoints of the brigade are special since there is no fireman to the left of fireman(1) or to the right of fireman(50). There must be special definitions for them. Assume that there are 75 buckets that can be in use at one time. Fireman(1) can fill a bucket only if there is one available.

```

fireman(1)::

integer b;

b := 75;

( b>0 --> b:=b-1; fireman(2)!bucket

! fireman(2)?empty --> b:=b+1 }

fireman(i:2..49)::

( fireman(i-1)?bucket --> fireman(i+1)!bucket

! fireman(i+1)?empty --> fireman(i-1)!empty }

fireman(50)::

( fireman(49)?bucket --> fireman(49)!empty }

```

There is a problem with the program given above. Deadlock can arise if fireman(1) is trying to send a bucket to fireman(2) at the same time that fireman(2) is trying to tell fireman(1) that the brigade is empty. The way to fix this problem is change the first guarded command in the defintion of fireman(1) to read

b)0 and fireman(2)!bucket --> b:=b-1

Regrettably, Hoare does not allow the use of output statements in guards.

## 1.3.2.3 Indicating Parallelism

The third feature that Hoare adds is the ability to indicate parallelism. Each process is a sequential one, but a collection of them can execute in parallel with the messages providing any required synchronization. The symbol !! is used to indicate that the named processes execute concurrently. The bucket brigade is set in motion by the statement

fireman(1) || fireman(2,.49) || fireman(50)

### 1.3.3 A Critique of CSP

CSP does not suffer from the limitations attributed to Simula. A message facility is an integral part of the notation, there are facilities for describing parallel execution among processes, and the language is concise. There is also something like a class construct for defining local data attributes and confining external access to specific entry points.

deficiencies. First, the SOME CSP has However, hierarchical definition capability of Simula is missing. There is no way to define a superclass that contains Instead, the attributes that all the processes share. common part must be repeated in each variation. only way to replicate processes is as arrays. Using subscripting conventions to represent the tree as an array obscures its structure.

Also, CSP has no way of restricting the communication of a process to a select set of other processes. That is, there is no way to enforce a particular interconnect structure. The notation allows a process to communicate with any other process it can name. In a tree, as with any large physical structure, there is a very rigid set of processors that can communicate directly with a given process. The notation should emphasize the physical structure.

By choosing to represent communication as messages sent between named processes, Hoare has made it impossible to assemble a collection of process definitions that can be used as building blocks in many different programs. The processor names are locked into the program text since a process must know the name of its partner in communication. Thus each process definition must be tailor-made for a specific program.

#### 1.4 A Tree Machine Notation

This section proposes a notation that is a blend of Simula and CSP ideas, with some useful additions. While the notation, used throughout the remainder of this paper, is tailored to the tree machine, it can easily be made more general. Extensions are discussed at the end of the chapter.

The syntax of the notation is derived from CSP. The <u>skip</u>, <u>abort</u>, assignment, loop, and conditional statements are identical to those in CSP, and have already been described. The message statements are also similar. Processes correspond directly to the processors of the tree machine.

The processors are defined as self-contained units that communicate through ports to other processors. The processor definitions assume that the ports are capable of processing messages. They assume nothing identity of the processor o n the other end of the port. This is a significant departure from Hoare's style communication, where process definitions name other processes directly.

There are several advantages to naming communication partners indirectly by using ports. A processor can defined without regard to the eventual connection plan of A processor expects to follow the network. a specific when accessing communication protocol a port. Any processor that follows the same protocol can be connected to the other end of the port.

This definitional locality makes possible a parts kit of standard processor definitions. Each part is a processor or tree of processors that can be characterized by the behavior of its ports. As long as the expected messages are sent and received, the part will work anywhere in the system.

In addition to the ability to define processors, the notation provides Q. mechanism for specifying the correspondence between ports and the tree processor interconnections of the complete machine. The mapping of the processor's ports onto the physical communication paths be supplied in order to complete the program description. This mapping is one-to-one and onto: port must be connected to another port, and no two ports can be connected to the same port.

A complete tree machine program has two parts: a set of processor definitions and a connection plan. The syntax of these will be discussed later.

### 1.4.1 Messages

Messages are written just as they are in CSP except that a port is named instead of a process. Another difference is that output statements as well as input statements can appear as guards. An output statement guard is satisfiable if the destination processor is willing to receive the message. Output statement guards are used repeatedly in the algorithms of Chapters 2 and 3. As in CSP, input statement guards can be satisfied if the specified port can receive a message.

The notation also supports broadcast output. A given message can be sent to several ports simultaneously. An output statement can have a list of destination ports each of which will receive the message. If an entire array of ports is to receive the message, the subscript '\*' is used to specify all of the array elements. For example, if L, R, and S(1:5) are ports, these are valid output statements:

L!hi L,R!hi S(3)!hi S(\*)!hi R,S(\*)!hi S(1),S(4)!hi

Broadcast mode output is used frequently in the algorithms of Chapters 2 and 3, usually to send a message to all of the sender's descendents.

Input statements can specify a list of ports as well. In this case, the message can be received from any one of the named ports. Thus if L, R, and S(1:5) are ports, L,R?hi means accept the message 'hi' from either L or R. The message S(\*)?hi means accept the message from any of the S ports. This notation can only be used where it really doesn't matter which port received the message. There is no way to retrieve the identity of the sender unless it is part of the message itself.

## 1,4,2 Processor Definitions

A tree machine program is a collection of modules. Each module is a <u>processor</u>. A processor definition begins with the keyword <u>processor</u>, a name for the processor, and, optionally, an argument. Next come the port and data declarations. The body of statements that form the program text of this module complete the definition. We will look at each of the components of the processor definition in more detail.

The input and output statements name ports to be used in the communication. Each processor can have <u>external ports</u> and <u>internal ports</u>. Every processor is the root of a tree of processors. Communication with this tree is possible only via the external port of the root processor. The internal ports are used for communication between the processor and its subtrees.

A processor must have exactly one external port, but may have any number of internal ports. Leaves have an external

port, but no internal ports. Programs are written for an arbitrary tree of processors, and mechanically translated into programs for a binary tree.

The definition of a processor that sorts marbles by color is given below. The processor, called colorSorter, has one port to the outside world and three ports to subtrees. The processor expects to receive marbles from its external port and will send them to an internal port chosen according to the color of the marble. If the marble is blue, it is routed to the B port, similiarly for green and red marbles. If it is not blue, green, or red, the marble is sent to the reject bin. The color is represented by an integer, with blue=1, green=2, and red=3.

A processor definition can be parameterized to allow one processor definition to fit a variety of situations. The parameter is a constant within the processor definition, and it cannot be modified during the computation. The parameter can be used to specify the number of internal ports a processor has. It can be used as a constant in an expression or in any situation that does not attempt to change its value. It cannot be the target of an assignment, since it is a constant, not a variable.

The processor definition for colorSorter is rewritten to handle n colors instead of three:

In order to complete the example, the definitions of the processors connected to the internal ports of colorSorter must be supplied and the interconnection scheme must be specified. The missing processor definition is given below. The bin processor keeps a count of how many marbles it has received. Bin is a leaf node in the tree so it has no internal ports.

```

processor bin;

external port p;

integer cnt;

cnt:=0;

{ p?marble --> cnt:=cnt+i } .

```

### 1.4.3 The Connection Plan

The processor definitions define the building blocks that the program will use. The connection plan shows how they fit together.

The keyword <u>tree</u> indicates a connection plan. It is followed by a name for the tree and an optional list of parameters. The remaining statements in the plan describe

connections between processors. A <u>connection</u> specifies which kinds of processors will be connected to the internal ports of a given processor. A connection is always between an internal port of one processor and the external port of the other. The external port connections, then, are implicit in a connection statement. I will begin with an explanation of the shorthand form of a connection plan, and gradually move toward the general form.

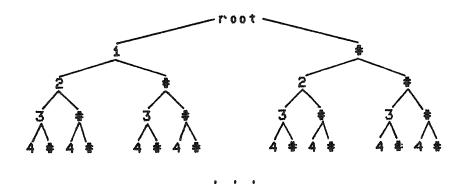

The connection plan for colorSorter and the bins can be expressed very simply as

tree marbleSorter(n): colorSorter(c(1:n),reject) " bin .

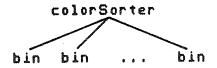

This statement says that the tree is called marbleSorter. It is parameterized by a value, n, that must be provided before the tree can be built. A colorSorter is the root of the tree. It has n+i internal ports, named c(1), c(2), ..., c(n) and reject. These are all connected to bin processors. The symbol '"' is read "is connected to". Implicit in the statement is that there are n+i bins, each with its external port connected to colorSorter. The tree looks like this:

Since the fanout of colorSorter can be determined from the processor definition and all the internal ports are connected to bin processors, the connection plan can be further abbreviated as

tree marbleSorter(n): colorSorter " bin .

The connection plans given so far are shorthand for the more general form. The example gives a tree with two levels, each made of different processors but with all the same kind of processors on a given level. Suppose that this is not the case. If the reject bin in the marble sorting example is a special processor called Rbin that keeps track of the total number of marbles that are successfully sorted as well as the number of bad ones, the tree gets a little more complicated. Here are a modified definition of colorSorter and a definition of Rbin.

The connection plan becomes

Again, there are two kinds of processors on the second layer of the tree: n bins and one Rbin. Here, however, connection statement has two parts, separated by a comma.

The comma signifies that the order of the two parts of the statement does not matter. Each part fully specifies which ports are connected to what type of processor.

Suppose the tree had more than two levels. This might happen if, in addition to differing in color, the marbles could be either square, round, or some other shape. If the marbles are sorted first by shape and then by color, a three level tree could be used:

tree fancyMarbleSorter(n):

shapeSorter(square,round)~colorSorter ,

shapeSorter(reject)~Rbin ;

colorSorter(c(1:n))~bin,

colorSorter(reject)~Rbin .

Notice that the second connection statement describes a defined tree. Since a tree has a single external previously internal port of be connected to an it can port, the same manner a single processor İS processor in connected. Another way of of describing the tree above İS given here:

tree fancyMarbleSorter(n):

shapeSorter(square,round)~marbleSorter ,

shapeSorter(reject)~Rbin .

A three level tree requires two connection statements in the connection plan. In order to avoid writing k statements for a tree that is k+1 levels high, a shorthand is provided for replicating a connection. For example, imagine a tree made up of three kinds of processors: a root, some leaf processors, and in between, mid processors that each have three descendents. If there are M layers of mids, the tree can be described as follows:

The shorthand means "repeat the connection ( mid " mid ) M-1 times". The resulting tree will have M levels of mid processors, and M-1 levels of connections between them.

In order to achieve a pattern of alternating processors by layers, one might write

This will give 2n+1 levels consisting alternatively of a's and b's.

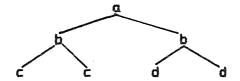

Suppose the tree below is to be built:

It cannot be described with the connection plan presented thus far. The connection plan tree t; a"b; b "c; b "d is ambiguous: which b is connected to the c's and which to the d's? Here, each b must be identified via the path to it from the root of the tree. This tree is described recursively by defining the two subtrees that have root nodes of b processors, and then assembling the complete tree from these.

```

\frac{tree}{tree} \ firstB: \quad b \ \ c \ . \frac{tree}{tree} \ secondB: \quad b \ \ d \ . \frac{tree}{tree} \ t: \quad a(pi) \ \ \ \ firstB \ , \ a(p2) \ \ \ \ secondB \ .

```

The general form of the connection plan provides for layer repetition, a heterogeneous collection of processors on a given layer, and uniquely naming a port in terms of its path from the root. The trees described in Chapters 2 and 3 tend to be simple, requiring only the shorthand notation.

# 1.4.4 Syntax Definition

### 1.4.4.1 Processor Defintion Syntax

```

<quard> ::= <booleanExpr> ! <message>

<assignment> ::= <identifierList> ':=' <exprList>

<identifierList> ::= <ident>

! (ident) ',' (identifierList)

<exprList> ::= <expr> ! <expr> ',' <exprList>

<message> ::= <portList> '?' <contents>

{ <portList > ! ' <contents >

cportList> ::= <port> ! <port> ',' <portList>

<port> ::= <ident> ! <ident> '(' <expr> ')'

{ (ident) '(*)'

<contents> ::= (ident> ! (ident> '(' (exprList> ')')

1.4.4.2 Connection Plan Syntax

<tree> ::= tree <name> ':' <connectBody> '.'

\name> ::= \(ident\) ! \(ident\) '(' \(ident\) ')'

<connectBody> ::= <connectList>

! (connectList) ';' (connectBody)

<connectList> ::= <connection>

{ connection } ',' (connectList)

<connection> ::= (ident> '~' (ident>

! (ident) '(' (pnList) ')' '"' (ident)

! (expr) ( (connectBody) )

<pnList> ::= <pn> ! <pn> ',' <pnList>

<pn> ::= <ident>

! (ident) '(' (expr) '!' (expr) ')'

The usual definitions are assumed for (ident), (expr),

(boolean expr). Comments can appear wherever a blank can,

```

and are enclosed in double quotes: "This is a comment...

### 1.4.5 Future Directions

This notation describes static trees. The tree is assembled before the computation is initiated During the computation, its structure remains unchanged. Static behavior is sufficient for the algorithms presented here. It might be interesting to examine trees with dynamic behavior.

The tree structure is reflected in the notation only because each processor is limited to a single external port. By removing this restriction and requiring that well has internal ports be explicitly declared external as other structures can be the connection statements, retain the important The programs described. the processors are locally sovereign and characteristics: the network is characterized by the traffic through the external ports.

Another extension of the language is to allow substructures other than trees to be defined and included in connection For example, user defined composite processors be nice, especially as a library of processor miaht I have not included them because of definitions develops. arise. that issues disquieting vaauely substructures are no longer characterized solely by the This may affect behavior of the external port. provability of the structure. Second, it becomes harder to Timing assumptions specify the behavior of the ports. about the processors inside a substructure may have to be made. Since a definitional capability for other substructures is a useful one to have, however, it should be investigated. My misgivings may be unfounded.

Messages in this notation are matched on the basis of like names. This is fine for custom processors and small problems, but might be cumbersome as libraries of processor definitions are developed, and complicated problems are tackled. It might be necessary to augment the notation with a way of explicitly specifying the matching of messages between processors.

Finally, there is no capability in the notation for indicating the overall strategy of each algorithm. The individual processors are defined and connected, but it is seldom apparent from these two things what the complete tree is supposed to do. In this thesis, I will present a textual, informal description of the strategy. As it is better understood, a formal specification should be developed.

### Chapter Two

# The Analysis of Algorithms

There are many different ways to solve a given problem. Complexity theory provides a framework for evaluating each solution, or algorithm, so that the best one can be chosen. The usual measures of complexity are the time and space requirements of the algorithm. The relationship of time and space to the size of the problem shows the asymptotic behavior of the algorithm as the problem gets arbitrarily large.

Complexity measures are given as functions of the size of the problem, usually called n. For instance, the space and time requirements of a sorting algorithm depend on the number of items to be sorted. If n elements can be sorted in  $\operatorname{cn}^2$  time for some positive constant c, the algorithm is said to be  $\operatorname{O}(\operatorname{n}^2)$  in time, read "order  $\operatorname{n}^2$ ".

The space requirements of an algorithm are computed by counting the number of storage locations it requires. The time complexity is usually a measure of the number of operations that must be performed on each input, and should properly be called an operation count.

Most measures of complexity are based on a particular model of computation that is chosen to suit the problem domain. For example, analysis of matrix manipulation is done in the framework of a machine with an array of memory, while list processing algorithms are more at home in a computational model with a pointer space. I will describe several different models of computation, ending with a description

of one that can be used to analyze the complexity of tree machine algorithms. The first model, the Random Access Machine (RAM) is discussed in more detail than the other sequential machine models because the individual processors of the tree machine are modelled as RAMs.

Each computation model is accompanied by criteria for calculating time and space costs for algorithms programmed in the context of the model. Most of the traditional models make the assumption that memory cells are equally remote from the processor. Algorithms are not penalized for ignoring locality in accessing memory.

Memory access is a degenerate form of the interprocess communication found in the tree machine. In the tree machine context it becomes apparent that a distance penalty must be assessed for each communication as part of the time cost of an algorithm. Another model that penalizes random Since the access algorithms is the Turing machine model. tape can advance only one cell per step, much as a tree machine message can traverse only one level in the tree at each cycle, examination of adjacent cells is cheap while However, the examination of distant cells is costly. Turing machine program is stored in a lookup table that can be viewed as infinite. There is no distance penalty applied program elements stored in this table. Thus the model is inconsistent in its treatment of communication costs.

#### 2.1 Random Access Machine Model

The most common model for complexity analysis is the random access machine (RAM) [Aho74]. A RAM has a single processor

with one accumulator, an unlimited memory, and some input and output ports. One integer can be read from or written to the ports or the memory at a time. Integers can be of arbitrary size.

The instruction stream does not occupy memory. Thus, it cannot modify itself. The exact instruction set doesn't matter. Arithmetic, logical, input/output, memory addressing, and branching instructions can be assumed, along with anything else that is common to the instruction repertoire of real machines. RAM programs will be stated here in pidgin Algol. Because asymptotic costs are given, the cost difference between Algol and machine language is absorbed in the constant.

The time and space costs of a RAM program can be viewed from two perspectives. The <u>uniform</u> cost criterion assumes that all instructions take the same amount of time and that each datum occupies the same amount of space. The <u>logarithmic</u> cost criterion attempts to recognize that memory is limited. Costs are assigned depending on the number of bits it takes to represent the instruction and the data. Both cost models are illustrated in the following paragraphs.

Consider the following problem. Given a vector a, generate another vector x such that

$$x_i = \sum_{j=1}^{i} a_j$$

where  $i=1,2,...,n$

The two problems that follow are RAM solutions to the vector summing problem described above. The first algorithm mimics the problem definition. The second is optimal for the RAM computational model.

```

integer array a[1:n], x[1:n];

integer i, j;

for i:=i to n do

begin

x[i] := 0;

for j:=i to i do

x[i] := x[i] + a[j];

end;

```

Figure 2.1.1 Vector Summing Solution #1 (RAM model).

The first program, figure 2.1.1, computes the values for the vector x by repetitively summing the values of a. The uniform cost space complexity is found by counting the memory requirements. There are two vectors of n elements each, plus two temporary variables, so the space cost is 2n+2 or O(n). The time complexity is somewhat more complicated. The outer loop is executed n times and the inner loop is executed i times for the i<sup>th</sup> iteration of the outer loop. Thus the time required, given the uniform cost criterion, is

$$n + (1+2+...+n) = n + n(n-1)/2 = (n^2+n)/2 = 0(n^2)$$

The second algorithm, figure 2.1.2, requires only one loop to do the computation because it takes advantage of previous work. The space complexity remains O(n), but the time complexity is improved. The single loop executes n

times and contains two instructions. Thus, it will take 2n or O(n) time.

```

integer array a[1:n], x[1:n];

integer i, sum;

sum := 0;

for i:=1 to n do

begin

sum := sum + a[i];

x[i] := sum;

end;

```

Figure 2.1.2 Vector Summing Solution #2 (RAM model).

So far, costs have been based on the uniform cost criterion. Another way of assigning costs is to relate the cost to the number and size of the operands. This is called <u>logarithmic</u> cost [Aho74], and is based on the assumption that the cost of an instruction is the sum of the lengths of its operands. The length of an operand is the number of bits required for its representation:

$$1(i) = \begin{cases} \log_2 i + i, & i > 0 \\ 0, & i = 0 \end{cases}$$

To compute the logarithmic time cost for the more efficient program, figure 2.1.2, it is useful to look at a machine code translation, given in figure 2.1.3. The time costs for each instruction can be tediously computed using the formula given above and assessing a penalty for the length of the operand and for the length of data fetched in each memory access. The resulting time cost is  $O(nlog_2n + nlog_2s)$ , where  $log_2s$  is the maximum number of bits it takes to represent the sums or vector elements. Logarithmic space complexity is defined as the sum, over all memory and the accumulator, of the length of the largest number stored

in each cell during the computation. Here again, the space complexity is  $O(n\log_2 s)$ .

```

load

=0

; sum := 0

store

SUM

load

=1

; i:=1

store

i

for:

; for i:=1 to n do

load

ΞŊ

sub

done

ineq

load

; fetch a[i]

a

sub

=1

add

i

store

ind

load

*ind

; sum:=sum+a[i]

add

SUM

store

SUM

; x[i]:=sum

load

X

sub

=1

add

i

ind

store

load

SUM

*ind

store

load

i

; i:=i+1

add

= 1

store

i

for

qmui

; 100p

done:

halt

```

Figure 2.1.3 Machine Language Translation

Since logarithmic costs are much more difficult to compute than uniform costs. Thus, uniform costs are usually used with the RAM model of computation. The logarithmic criterion is an attempt to be realistic about memory accesses. There are easier ways of doing that: the tree machine model provides a less cumbersome technique.

#### 2.2 Reference Machine Model

The RAM model assumes the existence of an unstructured store. Many algorithms access memory in a prescribed manner, however, and have no need of the less structured access capability. List processing techniques are an important example of this kind of algorithm. Reference machines [Tarjan77] have been proposed as a computational model that is more appropriate for such problems.

Like a RAM, a reference machine is a processor, a memory, and a collection of registers. The memory is organized as a pool of records, each containing entries that are either data or references to other records. All records are identical in structure.

There are registers that can hold data, and registers that can hold references. All CPU operations apply to these registers. The instruction repertoire includes instructions to transfer data between either kind of register and the memory, to perform the usual arithmetic and logical operations, to create new records, and to conditionally branch.

The main difference between this model and the RAM is that the reference machine severely limits access to the memory. Explicit reference is required. This makes the model appear less powerful than the RAM: some algorithms that rely on address arithmetic cannot be used. However, it can simulate LISP and other list processing languages. Thus, the reference machine is merely different from the RAM, not less powerful.

The reference machine model is interesting because it recognizes that memory access is not free. Rearettably. the model stops short of the point. Though memory are restricted, there is no distance measure applied to make clumped accesses cheaper than widespread ones.

# 2.3 Turing Machine Model

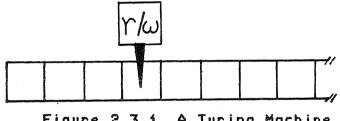

A Turing machine [Turing36] is pictured in figure 2.3.1. It has an infinitely long tape that is divided into cells, each of which can hold one symbol. One cell at a time is scanned by a tape head that can read and write the tape.

Figure 2.3.1 A Turing Machine

The Turing machine is controlled by a primitive program that describes transitions from one state to another based on the cell being scanned by the tape head. The program is represented as a set of quadruples (initial state, input symbol, action, next state). The action taken can be one of three things: move the tape one cell to the left, move the tape one cell to the right, or write a character the cell under the head. No two quadruples in the set can have the same initial state and input symbol.

Turing machine is initialized to a specified state. From there, actions are taken and new states entered by finding a quadruple such that the current state and symbol

under the tape head match the initial state and input symbol in the quadruple.

As an example, we will look at the Turing machine program for adding two integers. First, however, we need to set the stage by defining the Turing machine. A Turing machine is defined by a quintuple  $(Q,I,b,q_0,q_f)$ , where Q is the set of states, I the set of input symbols, b the blank character,  $q_0$  the initial state, and  $q_f$  the final state. The Turing machine for this example, then, is  $((s_0,s_1,s_2,s_f),(i,0),0,s_0,s_f)$ .

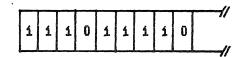

Numbers will be represented in <u>unary</u> form, as a string of ones. Thus the number five is represented as the string '11111'. The first number in the sum starts in the leftmost cell of the tape. The other number is separated from the first one by the blank character '0'. The sum will be written on top of the two numbers. Figure 2.3.2 shows the tape for forming 3+4.

Figure 2.3.2 Sample Turing Machine Tape.

The program proceeds this way: scan the tape, moving right, until the blank character is found. Write a '1' in that cell and continue scanning. When the next blank character is encountered, move left one cell, write a '0' there and halt. Thus the tape of figure 2.3.2 is transformed into '11111111', the unary representation of

seven. Figure 2.3.3 gives the Turing machine program described above.

Figure 2.3.3 Turing Machine Program: Addition.

The Turing machine model of computation is even more primitive than the RAM and reference machine models discussed in the previous sections. Turing invented it before digital computers existed as a framework for comparing abstract computational processes. The model is too primitive to be useful for most complexity analysis. However, it can compute anything a RAM machine can in polynomially related time. That is, if the Turing machine takes  $f_1(n)$  time and the RAM takes  $f_2(n)$  time, then there exist polynomials  $p_1(x)$  and  $p_2(x)$  such that  $f_1(n) \langle p_1(f_2(n))$  and  $f_2(n) \langle p_2(f_1(n))$  for all values of n.

This relationship between the RAM and Turing machine models comes in handy when analyzing programs where the polynomial blowup is lost in the noise. For example, if the time complexity of an algorithm is an exponential function, all polynomially related functions are also exponentials. This fact is used in analyzing the set of NP-complete problems described in the next chapter.

I have described a Turing machine that has a single tape and behaves in a deterministic manner. That is, no two quadruples can have identical initial states and input

Other flavors of the machine have been proposed: multi-tape machines, nondeterministic machines, multi-tape nondeterministic machines. For each flavor there is a set of problems that benefit from being analyzed on that particular computational model. Aho, Hopcroft, and Ullman [Aho74] and Tar.jan [Tarjan78] discuss variations in more detail.

### 2.4 Tree Machine Model

All of the computational models presented above are sequential machines, but the tree machine environment is highly concurrent. A different model of computation is needed to describe the complexity of tree machine algorithms.

Since each processor in the tree machine is a deterministic, sequential processor, the traditional view of complexity can be applied to each individual node of the tree. In the complexity analyses that follow, the RAM model with uniform cost criterion is used to characterize the behavior of the individual processors.

The messages exchanged between processors introduce synchronization and dependencies among the nodes of the tree, and must be figured into the time cost of the tree machine algorithm. The uniform time cost is appropriate here because messages can travel between adjacent levels of the tree in one time step. The farther a message has to go, the greater the cost. Thus, a message travels from the root of a tree of n processors to the leaves in O(log<sub>2</sub>n) time.

Every message does not contribute to the time cost of the algorithm, however. The time cost is really a measure of the <u>sequentiality</u> of the algorithm. Suppose that a message is broadcast from a processor to all its descendents in synchrony. The broadcast communication has the same cost as a communication from the parent to a given descendent because the elapsed time is the same. Similarily, if two communications in different parts of the tree occur in parrallel, the time cost is the cost of one communication. The second one, happening in parallel, is free. Thus, overlapping communications do not individually contribute to the time cost of the algorithm.

Space complexity of tree machines is easy to calculate. Each processor is of constant size, and once the data space in a processor is used, another processor must be allocated. The space cost, then, is the number of processors used to solve a problem.

Let us return to the vector summing problem of the RAM discussion. Given a vector a, calculate x such that

$$x_i = \sum_{j=1}^{i} a_j$$

where  $i=1,2,...,n$

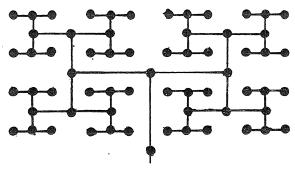

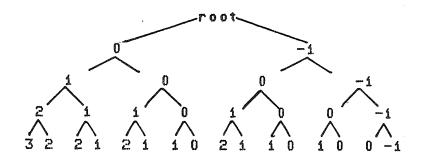

The tree machine algorithm for vector summing is presented in detail in a paper I presented at the Caltech VLSI Conference [Browning79a]. The initial vector a is loaded into the tree in infix order, as shown in figure 2.4.1. The summing begins in the left corner and proceeds up and to the right as the a;'s are replaced with the

corresponding values of x. In the following paragraphs we will examine the algorithm in detail in order to understand how time costs are assigned in tree machine algorithms.

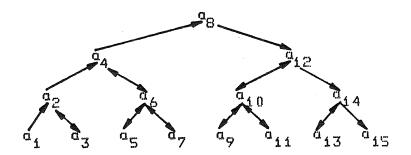

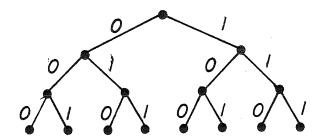

Figure 2.4.1 Vector Summing Tree, n=15.

The arrows in figure 2.4.1 indicate the flow of messages in the tree. The starting place is the leftmost leaf, called:  $a_i$ . The computation ends in the rightmost leaf, labeled  $a_{i5}$ . As the wave front of summing approaches the root, more and more processors are operating in parallel. As the computation crawls back down the right half of the tree fewer and fewer sums are formed in parallel. The net result is that all sums are formed by the time the last one is, and the last one is formed as quickly as a message can travel from the leftmost leaf to the rightmost leaf. That distance is  $2\log_2 n$ . Thus, the time spent computing the vector sum is  $O(\log_2 n)$ .

# 2.4.1 The Vector Summing Tree

Figure 2.4.1 shows a tree machine configuration for n=15. The connection plan we write down must be a general one, parameterized to fit any value of n. Because all the ports of every processor used in the tree must be hooked up to something, we must define the root, leaves, and middle

processors separately. Thus, we define vSumRoot, vSum, and vSumLeaf as the basic building blocks of the vector summing tree.

2.4.2, we see that there is one set In connections between the vSumRoot and vSum processors, vSum and vSumLeaf of connections set between These will remain constant with n. processors. parameterization, then, belongs in the declaration of vSum The connection plan is given to vSum connections. Note the second line: the number of vSum to vSum 2.4.2. connections is  $log_2n - 2$ . When n=15, this is indeed 1. (The logarithm is truncated to an integral value.)

tree vSumTree(n):

vSumRoot ~ vSum

log2n-2 ( vSum ~ vSum ) ;

vSum ~ vSumLeaf .

Figure 2.4.2 The Vector Summing Tree.

### 2.4.2 The vSumRoot Processor

Each of the three kinds of processors have four activities to undertake. Variables must be initialized, the values must be loaded into the proper nodes, the sums must be formed, and the answer must be unloaded from the tree. responsible for beginning the The vSumRoot is loading and It also controls the initialization phase. of the vector values. vector The however, begins in the leaves of the tree.

During the initialization phase of the computation, the vSumRoot sends two different messages to its descendent

subtrees: expect and subscript. The expect message tells the processor how many values must go to the left, how many to the right, and which one will stay here. That is, the processor that represents the fourth element in a vector of length 15 will see seven values during the loading phase: the first three are destined for processors in the left subtree, the fourth value becomes the value stored in this processor, and the remaining three are sent to the right subtree. The subscript message informs each processor which element of the vector it represents. The subscript is used in the summation step to insure that the right things get summed together.

The loading phase, partially described above, is also initiated by the vSumRoot. It reads  $\underline{load}$  messages, n of them, from the system bus. These are distributed to the left and right subtrees, with the middle values remaining in the root, assigned to the variable  $\underline{x}$ .