# The Architecture and Programming of a Fine-Grain Multicomputer

Thesis by

Jakov N. Seizović

In Partial Fulfillment of the Requirements

for the Degree of

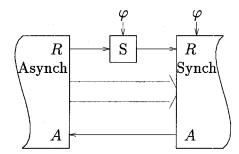

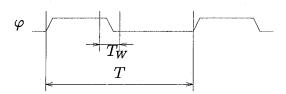

Doctor of Philosophy

California Institute of Technology

Pasadena, California

1994

(Submitted August 20, 1993)

Copyright © 1994 Jakov N. Seizović All Rights Reserved

# Acknowledgments

Many thanks to all the great teachers I've had, in particular: To Chuck Seitz, my research advisor, for knowing when to be a friend and when a tough guy, for his willingness to be both a student and a teacher, for pointing out the obvious and insisting on simplicity. To Jan van de Snepscheut, Mani Chandy, and Eric van de Velde, members of my thesis-defense committee, for teaching me, through their example, that one must never stop learning. To Milenko Cvetinović, for giving me all the right books to get excited about. To Ilija Stojanović, Dejan Živković, and Slobodan Ćuk, for believing in me before I did.

Many more thanks to my fellow students: To Nan Boden, for her dedicated support and critique, depending on what I needed on any particular day. To Wen-King Su, for the long hours we spent working together, and for sharing his insights into the wonderful world of programming. To the late Mike Pertel, for teaching me about stamina in times good and bad. To Bill Athas, Don Speck and Craig Steele, for helping me keep both feet on the ground. To Tony Lee, for being the best office-mate there is.

Thanks also go to my research sponsors: To the Advanced Research Projects Agency, whose program managers repeatedly demonstrated a remarkable ability to balance researchers' vanities against the need for inter-project cooperation. To IBM, for their orientation towards the future, embodied, in part, in numerous student-support programs.

To the entire Caltech Computer Science Department staff, and to Arlene DesJardins in particular, for humming busily in the background of my cocoon.

And to my family and friends who made sure that it wasn't "all work and no play"

$To\ Goga$

## Abstract

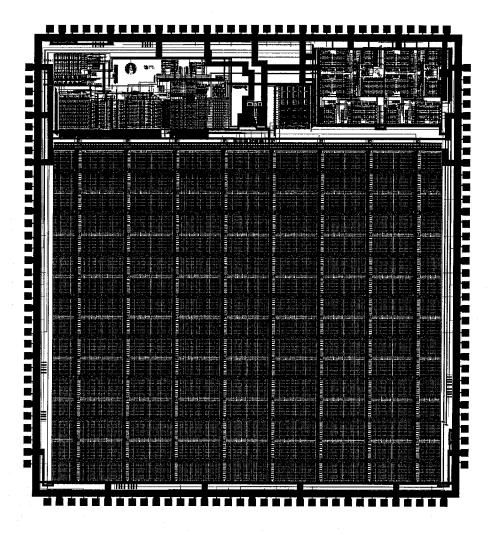

The research presented in this thesis was conducted in the context of the Mosaic C, an experimental, fine-grain multicomputer. The objective of the Mosaic experiment was to develop a concurrent-computing system with maximum performance per unit cost, while still retaining a general-purpose application span. A stipulation of the Mosaic project was that the complexity of a Mosaic node be limited by the silicon complexity available on a single VLSI chip.

The two most important original results reported in the thesis are:

• The design and implementation of C+-, a concurrent, object-oriented programming system.

Syntactically, C+- is an extension of C++. The concurrent semantics of C+- are contained within the *process* concept. A C+- process is analogous to a C++ object, but it is also an autonomous computing agent, and a unit of potential concurrency. Atomic single-process updates that can be individually enabled and disabled are the execution units of the concurrent computation. The limited set of primitives that C+- provides is shown to be sufficient to express a variety of concurrent-programming problems concisely and efficiently.

An important design requirement for C+- was that efficient implementations should exist on a variety of concurrent architectures, and, in particular, on the simple and inexpensive hardware of the Mosaic node. The Mosaic runtime system was written entirely in C+-.

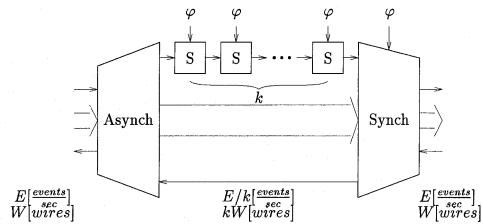

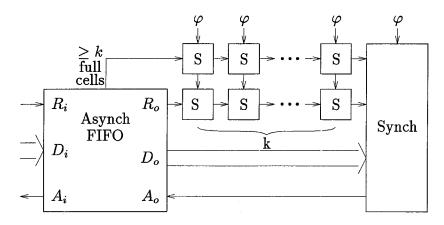

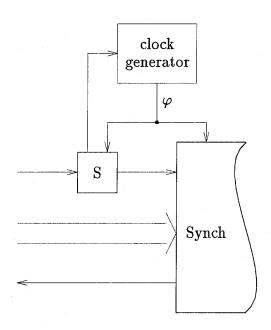

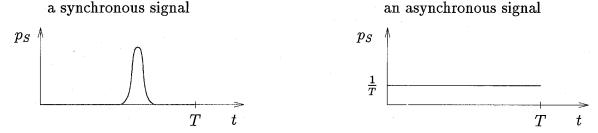

• Pipeline synchronization, a novel, generally-applicable technique for hardware synchronization.

This technique is a simple, low-cost, high-bandwidth, high-reliability solution

to interfaces between synchronous and asynchronous systems, or between synchronous systems operating from different clocks.

The technique can sustain the full communication bandwidth and achieve an arbitrarily low, non-zero probability of synchronization failure,  $P_f$ , with the price in both latency and chip area being  $\mathcal{O}(\log \frac{1}{P_f})$ .

Pipeline synchronization has been successfully applied to the high-performance inter-computer communication in Mosaic node ensembles.

# Contents

| 1 | Int | Introduction     |                                             |    |  |  |

|---|-----|------------------|---------------------------------------------|----|--|--|

|   | 1.1 | urrency and VLSI | 1                                           |    |  |  |

|   | 1.2 | Conci            | urrent Architectures                        | 2  |  |  |

|   | 1.3 | Conc             | urrent Programming                          | 3  |  |  |

|   |     | 1.3.1            | Shared-Memory Programming                   | 4  |  |  |

|   |     | 1.3.2            | Explicit Message Passing                    | 4  |  |  |

|   |     | 1.3.3            | Architecture-Independent Programming        | 5  |  |  |

|   | 1.4 | The F            | Reactive-Process Programming Model          | 8  |  |  |

|   | 1.5 | The N            | Mosaic C Project                            | 9  |  |  |

|   | 1.6 | Overv            | riew of the Thesis                          | 12 |  |  |

| 2 | C+- |                  |                                             | 13 |  |  |

|   | 2.1 | Introd           | luction                                     | 13 |  |  |

|   |     | 2.1.1            | Object-Oriented Programming vs. Concurrency | 13 |  |  |

|   |     | 2.1.2            | Concurrent Object-Oriented Languages        | 14 |  |  |

|   | 2.2 | The P            | rocess Concept                              | 17 |  |  |

|   | 2.3 | Manag            | ging Concurrency                            | 22 |  |  |

|   |     | 2.3.1            | Remote Procedure Call                       | 22 |  |  |

|   |     | 2.3.2            | Call Forwarding                             | 24 |  |  |

|   |     | 2.3.3            | Fork-Join                                   | 25 |  |  |

|   |     | 2.3.4            | Semaphores                                  | 28 |  |  |

|   |     | 2.3.5            | Monitors                                    | 29 |  |  |

|   |     | 2.3.6            | Recursion                                   | 29 |  |  |

|   |     |                  |                                             |    |  |  |

| CONTENTS | viii |

|----------|------|

|----------|------|

|   |     | 2.3.7   | Message Passing                     | 30 |

|---|-----|---------|-------------------------------------|----|

|   |     | 2.3.8   | Single-Assignment Variables         | 32 |

|   |     | 2.3.9   | Process Aggregates                  | 32 |

|   |     | 2.3.10  | Summary                             | 36 |

|   | 2.4 | Manag   | ging Program Complexity             | 36 |

|   |     | 2.4.1   | Class Inheritance                   | 36 |

|   |     | 2.4.2   | Virtual Functions                   | 38 |

|   |     | 2.4.3   | Process Layering                    | 38 |

|   |     | 2.4.4   | Process Libraries                   | 40 |

|   |     | 2.4.5   | Data Exchange                       | 40 |

|   | 2.5 | Puttin  | g It All Together                   | 45 |

| 3 | Imp | olemen  | tation Issues                       | 58 |

|   | 3.1 | The R   | untime-System Framework             | 58 |

|   |     | 3.1.1   | Process Creation                    | 59 |

|   |     | 3.1.2   | Runtime Services                    | 60 |

|   |     | 3.1.3   | Process Dispatch                    | 61 |

|   |     | 3.1.4   | The pointer_t and the entry_t Types | 64 |

|   |     | 3.1.5   | Process State                       | 64 |

|   |     | 3.1.6   | Process Migration                   | 66 |

|   |     | 3.1.7   | Invoking Atomic Actions             | 66 |

|   |     | 3.1.8   | Active/Passive                      | 69 |

|   |     | 3.1.9   | Remote Procedure Call               | 69 |

|   | 3.2 | From (  | C+- to C++                          | 71 |

|   |     | 3.2.1   | Parsing                             | 71 |

|   |     | 3.2.2   | Code Generation                     | 73 |

|   |     | 3.2.3   | Code Splitting                      | 73 |

| 4 | The | Mosai   | c C                                 | 76 |

|   | 4.1 | Multico | omputer Architecture                | 76 |

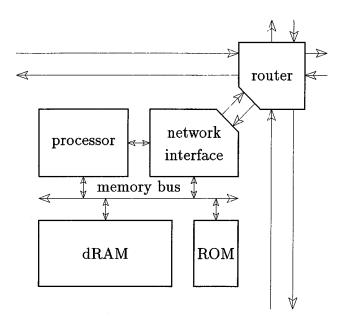

|   | 4.2 | The M   | osaic Node                          | 78 |

| CONTENTS | iv |

|----------|----|

| CONTENTS | ın |

|                  |     | 4.2.1                        | The Mosaic Router                       | . 79  |  |  |  |  |

|------------------|-----|------------------------------|-----------------------------------------|-------|--|--|--|--|

|                  |     | 4.2.2                        | The Dynamic RAM                         | . 81  |  |  |  |  |

|                  |     | 4.2.3                        | The Processor and the Network Interface | . 81  |  |  |  |  |

|                  | 4.3 | Softwa                       | are Overhead of Communications          | . 83  |  |  |  |  |

| 5                | Pip | eline S                      | eline Synchronization                   |       |  |  |  |  |

|                  | 5.1 | Introd                       | luction                                 | . 89  |  |  |  |  |

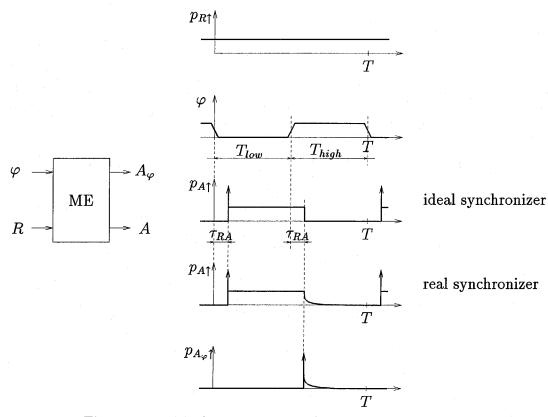

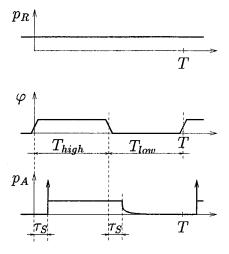

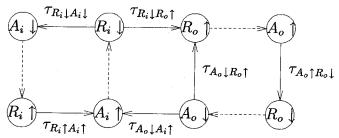

|                  | 5.2 | Problem Specification        |                                         |       |  |  |  |  |

|                  | 5.3 | Existing Solutions           |                                         |       |  |  |  |  |

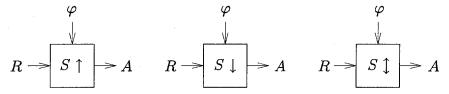

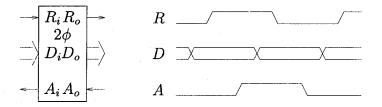

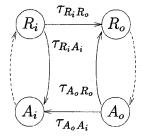

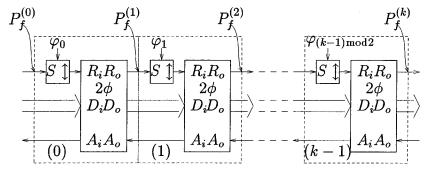

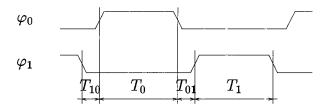

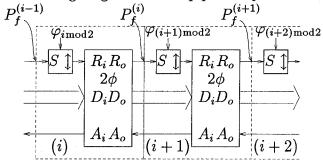

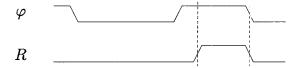

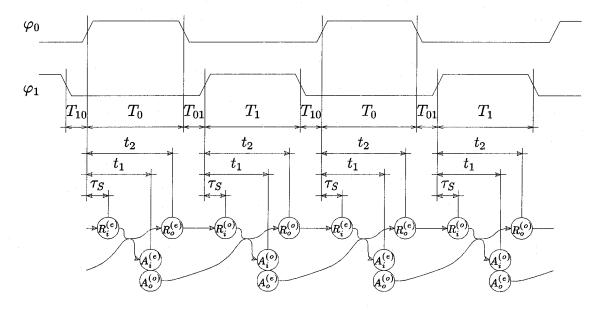

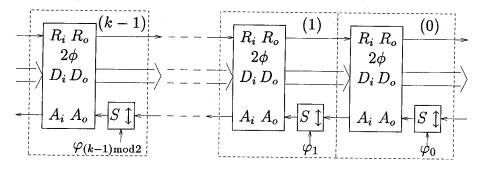

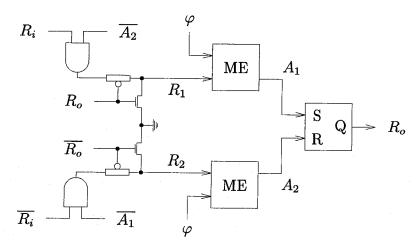

|                  | 5.4 | Pipeli                       | ne Synchronization                      | . 96  |  |  |  |  |

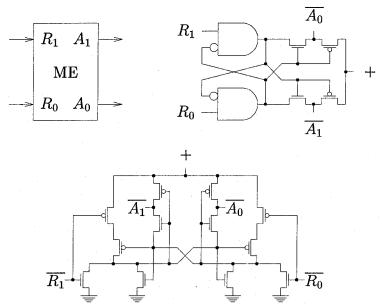

|                  |     | 5.4.1                        | The Mutual-Exclusion Element            | . 98  |  |  |  |  |

|                  |     | 5.4.2                        | Two-Phase-Protocol FIFO                 | . 101 |  |  |  |  |

|                  |     | 5.4.3                        | Pipeline Synchronizer                   | . 104 |  |  |  |  |

|                  |     | 5.4.4                        | Correctness Proof                       | 105   |  |  |  |  |

|                  |     | 5.4.5                        | Variations On the Theme                 | 116   |  |  |  |  |

|                  | 5.5 | A CM                         | OS Implementation                       | 118   |  |  |  |  |

|                  | 5.6 | 6 Conclusions                |                                         |       |  |  |  |  |

| 6                | Con | nclusions                    |                                         |       |  |  |  |  |

|                  | 6.1 | Comparison With Related Work |                                         |       |  |  |  |  |

|                  |     | 6.1.1                        | Medium-Grain Multicomputers             | 121   |  |  |  |  |

|                  |     | 6.1.2                        | Fine-Grain Multicomputers               | 123   |  |  |  |  |

|                  |     | 6.1.3                        | Multiprocessors                         | 125   |  |  |  |  |

|                  | 6.2 | Summ                         | ary                                     | 127   |  |  |  |  |

| $\mathbf{A}$     | Exa | mple I                       | Products of C <sup>+-</sup> Compilation | 130   |  |  |  |  |

| Bibliography 143 |     |                              |                                         |       |  |  |  |  |

# Chapter 1

## Introduction

## 1.1 Concurrency and VLSI

Progress in microelectronics technology during the past four decades has been remarkable by any measure. Three major factors contributed to this progress: (1) a rapid and steady pace of improvements in processing technology to produce ever smaller, faster, and lower-power devices; (2) the development of design methodologies [62] and tools to manage design complexity; and (3) the exploitation of concurrency [75]. The first two factors are readily understood. The importance of concurrency to the performance/cost ratio of VLSI systems can be understood from results of VLSI-complexity theory [97], and has been demonstrated repeatedly in practice.

Special-purpose computing engines were the first to employ concurrent solutions, and continue to do so, highly successfully, to this day [50, 11]. Although various forms of concurrency (bit-level parallelism, pipelining, vectorization) are exploited regularly in general-purpose computing engines [37], applying concurrent solutions to general-purpose computing at the application level has been slower in gaining ground.

A considerable effort has been made to exploit the concurrency that is implicit in sequential programs. This effort has been successful in discovering and utilizing modest degrees of concurrency, but is now regarded almost universally as having approached its limits [49]. Applications with explicitly concurrent formulations are the driving force for a range of concurrent architectures, some of which are discussed in the following section.

#### 1.2 Concurrent Architectures

Most of today's concurrent computers are representatives of one of the following three architectures [33]:

- Computers with a single instruction stream and multiple data streams (SIMD).

- Two variants of computers with multiple instruction streams and multiple data streams (MIMD):

- multiprocessors, which have one global address space, and

- multicomputers, which have multiple local address spaces.

Early concurrent-computer implementations closely followed this classification: SIMD computers employed multiple computing units to which instructions were broadcast [40]; multiprocessors utilized buses and/or switches to connect multiple processors to the global memory [69, 24]; multicomputers featured independent processor-memory pairs interacting through a message-passing network [76].

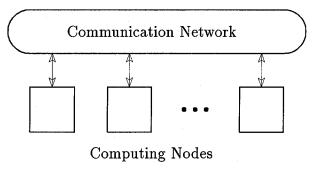

The differences between the more recent representatives of these three architectures [96, 12, 53, 1, 64, 79] are blurred: When observed from a point that is sufficiently close to the hardware, or from a point that is sufficiently far away from the hardware, these three architectures are remarkably similar. Each consists of a communication network connecting a collection of computing nodes. Each node consists of one to several instruction-interpreting processors, a local memory, and a network interface. All three architectures support some concept of processes — computing agents that execute concurrently, and that can communicate data and synchronize activities with each other. What were once architectural distinctions became differences in programming style: data-parallel [70], shared-memory [18], and message-passing (Chapter 2) programming abstractions. Depending on the emphasis on support for one of these

abstractions, additional architectural support is provided for global synchronization [96], for efficient non-local memory access [53, 1], or for low-latency, low-context-switch-overhead message handling [64, 79].

In this thesis, we shall focus principally on the multicomputer variety of MIMD computers, but shall indicate also how our results apply to multiprocessors. Multiprocessors provide hardware support for a global address space, and implement inter-process communication through shared-memory access, whereas multicomputers provide a generic message-exchange mechanism, and implement shared-memory access through inter-process communication.

Given the similarity between these two architectures, one might expect that, given a typical problem-set load of the computer, it would be easy to test and decide which architecture and which machine should be employed. Yet, the reality of concurrent computers and concurrent-programming systems is somber: programs are most often written in notations tailor-made for a particular computer architecture, sometimes even for a particular machine. The cost-effectiveness of program execution on concurrent machines is their main advantage over their sequential counterparts [75]. Striving to maximize this cost-effectiveness, however, emphasizes the concurrent computer's main disadvantage: the complexity of writing programs.

## 1.3 Concurrent Programming

There are two, typically conflicting, driving forces shaping the developments in concurrent programming: increasing efficiency and increasing expressivity.

The efficiency-conscious programming systems are typically the products of design teams also involved with the design of concurrent machines, and often reflect the underlying architecture. Shared-memory programming and explicit-message-passing programming are representatives of this class.

The expressivity-conscious programming systems are often produced by the frustrated users of the products of the former groups, and are typically architecture-independent (Section 1.3.3).

#### 1.3.1 Shared-Memory Programming

The first developments in concurrent programming were motivated by the advent of multiprogramming and multiuser operating systems. It should not, therefore, be surprising that the first concurrent-programming systems supported concurrent processes that communicated and synchronized through the memory of the machine on which they were executing. The development of the Parallel RAM (PRAM) model, a theoretical framework on which much of the work in concurrent algorithms is based, also promoted the popularity of this programming style, which is still the predominant form of concurrent programming.

From the early stages on, shared-memory programming has been plagued by various incarnations of the mutual-exclusion problem. This problem is due primarily to the discrepancy in access granularity between the data structures and the memory units used to represent these data structures. A number of remedies were introduced: atomic test-and-set and/or fetch-and-add instructions [35], and semaphores [28]. One of the most significant efforts was the work of Per Brinch Hansen on Concurrent Pascal, and the development of monitors [36, 41]. Monitors encapsulate data with the (mutually-exclusive) operations defined on the data in programmer-defined, compiler-and-runtime-system-managed units. This work forms a foundation on which many of the recent developments in object-oriented concurrent programming are based, including the programming system described in this thesis.

## 1.3.2 Explicit Message Passing

Communication and synchronization through explicit message passing is a programming paradigm whose roots are as old as computers themselves, stemming from the need for inter-computer information exchange. This programming paradigm was adopted and adapted for programming multicomputers [42, 77]. Starting with the Cosmic Cube [76] and its commercial descendents [78, 54], the mainstream representatives of the multicomputer architecture employ off-the-shelf processor, memory, and compiler technology. Programming systems for these machines are based on a vari-

ety of sequential programming languages for specifying individual process behavior, wherein communication and synchronization between processes is achieved through a set of library routines.

There are two problems that are the curse of this programming style. First, although modular organization of data structures can be achieved within a process, this modularity does not extend readily to collections of processes. Second, the off-the-shelf technology often brought the off-the-shelf notion of process granularity; heavy, UNIX-style processes impose an unacceptably high software overhead to process communication and synchronization.

#### 1.3.3 Architecture-Independent Programming

A number of programming models and notations have been devised to provide a uniform view to the programmer of concurrent computers, and to map computations onto either of the architectures described above. The advantages that these programming systems offer in reducing programming effort are remarkable; preserving the cost-effectiveness of concurrent computers running such programs, however, has yet to be demonstrated. The assembly programming of conventional, sequential computers has been all but eliminated by higher-level notations through large improvements in program-writing efficiency, with small degradations of program-execution efficiency. The same has yet to happen to tailor-made concurrent-programming notations.

#### Functional Programming and Dataflow

In its pure form [6], functional programming provides a method for defining functions in terms of other, more-primitive functions. The value of a function is determined only by the value of its arguments, and is not history-sensitive. Since there are no side effects, functional-programming notations are implicitly concurrent, and sub-expressions, including function arguments, can be evaluated independently of each other.

The introduction of side-effects into functional-programming notations enables them to model history-sensitive behavior, but it also opens them up to the full set of problems associated with imperative-programming notations. Extending pure functional programming with single-assignment variables and streams, as introduced by dataflow researchers, represents an important intermediate point. This extension relaxes the no-side-effects requirement into the *monotonicity* requirement: A variable starts up uninitialized, and an assignment bounds it to a value (multiple assignments are disallowed). A stream consists of a (possibly-infinite) sequence of variables that can only be read and appended. Using single-assignment variables for communication and synchronization is also used extensively in compositional programming [21, 19], and in concurrent logic programming, described next.

#### Concurrent Logic Programming

The programming model typically associated with sequential logic programming is that of proving an existentially quantified statement given a program that consists of a set of axioms [90]. Implementations of this model involve backtracking that could, in principle, be replaced by concurrent examination of all the alternatives. However, for efficiency reasons, and because of the need to better model input/output behavior [93, 83], concurrent logic programming makes a significant departure from this model: There is no backtracking; once a (non-deterministic) choice is made, no alternatives are examined.

A concurrent logic program consists of a set of guarded clauses, and each clause represents a recursive specification of process structures. To program in a concurrent logic programming notation is to specify tasks as unordered, concurrent sets of subtasks. Tasks communicate and synchronize with each other by binding single-assignment variables, and waiting for variables to become bound.

Restrictions on the expressivity of clause guards, to improve efficiency, lead to a family of *flat* concurrent-logic notations [93]. A minimalist approach to concurrent logic programming of Ian Foster and Stephen Taylor resulted in Strand, a streamlined

and efficient concurrent-programming system [34], without giving up much of the expressive power.

#### UNITY

UNITY, developed by K. Mani Chandy and Jayadev Misra [20], is a computation model and a programming notation, with an associated proof methodology. A UNITY program consists of a set of guarded multiple assignments. These assignments are executed in arbitrary order: The focus of programming in UNITY is on what, i.e., on data transformations, as opposed to when. A particular execution order can be enforced only through data dependencies. A computation terminates when it reaches a fixed point, i.e., when no assignment in the program modifies any variables.

An interesting related research has been reported by Craig S. Steele [89]. In this work, a programming model and a corresponding notation are developed, in which program actions are associated with data objects through a programmer-specified triggering mechanism. An efficient multicomputer implementation of this UNITY-like programming system is demonstrated.

#### Actors

The Actors model of computation was first proposed by Carl Hewitt and Henry Baker [38, 39], and was later formalized by William D. Clinger [22] and Gul Agha [3]. In this model, the unit of concurrent computation is an *actor*, an independent computing agent that is activated in response to messages sent to it. Each actor has a unique address, an associated message queue, and a specified behavior. In a response to a message, an actor can: *send* messages, create *new* actors, and *become* a new actor by specifying its replacement behavior.

Because of its simplicity, potential efficiency, and straight-forward implementation on distributed architectures, the Actors model is the basis for numerous concurrent-programming systems. The reactive-process programming model, described next, and its associated notation, described in Chapter 2, are based in part on the Actors model of computation.

## 1.4 The Reactive-Process Programming Model

The reactive-process programming model is a variant of the Actors programming model. Computation in this model is performed by a set of processes, independent computing agents. A process is normally at rest, and starts executing in response to a message (including the initial, creation message). In the course of its execution, a process can send messages, create new processes, and modify its state, including self-termination. Message order is preserved for each pair of processes in direct communication. Each message is marked with a tag that specifies which of the process's compile-time-fixed set of entry points should be invoked. Each entry point runs to completion, and is therefore an atomic update of its process's state. A process can affect the order of execution of its entry points by enabling and disabling them selectively, at run time; all entry points are initially enabled. A message tagged for a disabled entry point is delivered when (and if) that entry point is active again.

This model is extended to include the remote procedure call (RPC). An entry point of a process can be specified to return a value to the message sender. When a message is sent and tagged for such an entry point, the sender is suspended until the message with the returned value arrives.

#### **Background**

The reactive-process programming model is a result of the work in our research group over the last decade. Interestingly, a comparison with the early work of C. R. Lang on a concurrent version of Simula [51] reveals that our group's ideas seem to have come almost full circle. The ideas of C. R. Lang, and the preceding work of Per Brinch Hansen, were far-sighted and out-of-sync with the multicomputer technology of their time. In retrospect, it is as if much of what our research group has been doing was tracking and driving the necessary communication, processor, memory, and compiler technology to approach this target.

Starting with the development of the Cosmic Cube, our group embraced the explicit message-passing programming style. The design of an experimental fine-grain

multicomputer, Mosaic C, and the similarity of our approach to the Actor model of computation, provided additional motivation; this effort culminated with the work of W. J. Dally on Concurrent Smalltalk [26]; of W. C. Athas and N. J. Boden on Cantor, a minimalist Actor-based notation [4, 9]; and of W.-K. Su on Reactive-C and distributed event-driven simulation [91]. The work on the Cosmic Environment [91] and the Reactive Kernel [82] shifted our focus from organizing computations around processes to organizing computations around messages, and the reactivity became an essential part of the programming model.

## 1.5 The Mosaic C Project

The work described in this thesis attempts to make a contribution to the un-stately condition of concurrent programming today. Our work is based on the following principles:

- Concurrency must come cheap: Concurrent machines must be extensible in small and inexpensive chunks.

- Concurrency must come cheap: Only those high-level programming constructs for concurrency that can be implemented efficiently by the (small and inexpensive) hardware can be used.

- Concurrency must come cheap: Expressing concurrency in programs must be simple.

Starting from these simple and restrictive requirements, our research group has been conducting a computer-architecture experiment to design a concurrent-computing system with as high a performance/cost ratio as possible, while still retaining the (not so well-defined) "general-purpose" application span. In the course of this experiment, we have built a testbed consisting of: a fine-grain multicomputer, the Mosaic C; a concurrent-programming notation, C+-; and a distributed runtime system, MADRE.

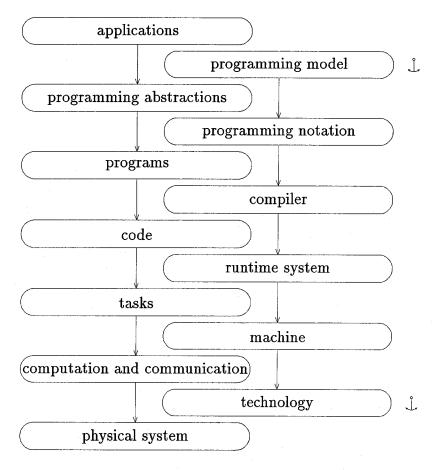

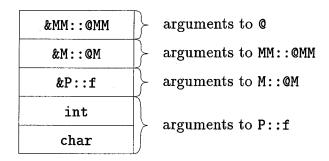

What computer architecture is all about is bridging the gap between a programming model and a technology [37, 77]. Designers of all of today's computers divide this complex spanning task into a set of smaller, more manageable subtasks. A particular choice of subtasks is illustrated in Figure 1.1. Well-defined anchor points

Figure 1.1: Computer architecture

simplify the implementation of the subtasks; however, if those anchor points are too numerous and/or too rigid, the design space may become severely restricted.

For the Mosaic experiment, the fairly rigid anchor points have been:

- the scalable CMOS VLSI technology, because that was the best technology that we both had access to and understood well, and,

- the reactive-process programming model, because we believed we could implement it efficiently.

For each of the remaining intermediate points, we have been able to identify opportunities for what appeared to be significant improvements over existing concurrent-computing systems. In particular:

- The programming notation was to be a derivative of a widely-accepted object-oriented programming notation, trying to leverage off of the advances that object-oriented programming brought to sequential-programming systems.

- The *compiler* technology was mature enough that we believed a compiler could perform much of the checking traditionally done at run time, if at all.

- The runtime system was to be fully distributed, and utilize the distributedqueue algorithm described in [10].

- The *machine* was to benefit from the results in router technology [81], dRAM technology [87], synchronization methods (Chapter 5), packaging technology [79], and self-testing possibilities [79].

Our computer-architecture experiment culminated in designing and building the Mosaic concurrent-computing system. Parts of the Mosaic system are described in [79, 81, 87, 10], and in this thesis.

In as closely-coupled a research team as ours, it is difficult to properly grant every bit of credit, but, to the first order, the following is the list of contributions to the Mosaic project. Most of the work has been done by five people: Nanette J. Boden, Charles L. Seitz, Don Speck, Wen-King Su, and the author of this thesis. Nan has been involved principally with the runtime system, but was also invaluable to the development of the programming model and of the notation, and was the most understanding and thorough tester of the compiler and of the machine. Chuck did most of the overall-machine architecture, the processor architecture, the system integration and packaging, and the router design. Chuck also had important contributions to every other aspect of the project, and the commitment to see it all the way through. Don designed the dRAM and ROM, and taught all of us the value of patience and thoroughness. Wen-King designed most of the processor and router,

the workstation interfaces, and worked on all aspects of verification and packaging. Wen was also a principal contributor to the programming model, wrote a low-level-but-works-reliably-the-very-first-time programming system, and re-targeted the Gnu C and C++ compiler to the Mosaic. The author of the thesis feels he deserves credit only for saying: "Why don't we get this thing finished!", and for then going off to fill in the missing links: routing-network interface, chip-level system integration and verification, the programming notation, and the compiler. Numerous other people have been associated with the Mosaic project, most notably: William C. Athas, who contributed to the programming model and to the processor architecture, and Michael J. Pertel, who contributed to the choice of the routing network and to its performance evaluation.

#### 1.6 Overview of the Thesis

In Chapter 2 we introduce C+-, a concurrent object-oriented notation based on C++. Chapter 3 defines the C+- runtime-system interface, illustrates how C+- can be customized, and explains the C+--compilation process. In Chapter 4, a brief description of the architecture of the Mosaic multicomputer is presented, with emphasis on architectural support for C+-. Chapter 5 presents a novel, generally applicable, synchronization technique, along with a proof of its correctness, and its application to the Mosaic. In Chapter 6, we compare the results of our work with the related research, and suggest possible future research directions.

# Chapter 2

$\mathbf{C}$ +-

#### 2.1 Introduction

### 2.1.1 Object-Oriented Programming vs. Concurrency

Programming notations that support object-oriented programming techniques are the notations of choice for a rapidly growing number of complex applications. Indeed, not since the introduction of structured programming [25] has there been such a degree of unanimity in the programming community. This unanimity is even more remarkable considering that, just as was the case with structured programming [29], the power of object-oriented techniques is difficult to convey to readers through short, example programs in books or articles. When observed in isolation, none of these techniques is new or revolutionary. It is only when one approaches a large-scale programming task armed with the full set of techniques that their power becomes evident.

Structured-programming techniques advocate structuring of program control flow in a top-down, compositional fashion. Object-oriented programming techniques promote data organization in a bottom-up, standard-parts fashion. Both paradigms emphasize modularity, but, whereas the former is focusing principally on modularity of control structures, the latter does a better job of encapsulating data structures with the operations defined on these structures.

Object-oriented programming came about through attempts to make large,

CHAPTER 2. C+- 14

sequential programs more manageable. Techniques such as data encapsulation and access protection, inheritance, and guaranteed initialization, all emerge from the goal of helping programmers help themselves.

By our view, much of what the techniques of object-oriented programming are really helping to manage is *concurrency*. Events are concurrent if they are unordered, *i.e.*, if they can occur in any order, or in parallel. Mutual exclusion is an example of an issue most often associated with concurrent programming, but the problems that result from a disregard for mutual exclusion also occur regularly in large sequential programs. With uncontrolled access to global variables, it is impossible to keep track of all of the places in the code where a certain variable is accessed, and of all the invocations of such code. Non-deterministic execution is another issue most often associated with concurrent programming. For a fixed set of inputs, the execution of a sequential program will always result in the same ordering of state changes, yet, with side effects on global variables, it is often far from obvious what all the inputs to a program are.

Whereas sequential programming brings out the worst in us only in the large, concurrent programming will do that already in the small. It should not be surprising, then, that in the hope of reaping some of the benefits that object-oriented techniques brought to sequential programming, we are witnessing a proliferation of programming systems trying to amend a particular object-oriented notation with concurrent semantics.

## 2.1.2 Concurrent Object-Oriented Languages

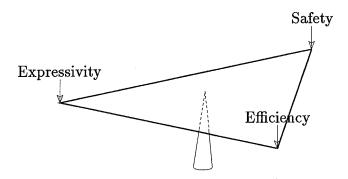

The three-way design tradeoffs illustrated in Figure 2.1 are typical of design of any programming system, not only those attempting to harness concurrency. However, all three requirements are more pronounced, and the balance more difficult to achieve, for a concurrent-programming system:

Figure 2.1: Design tradeoffs for concurrent programming systems

- Efficiency One of the major reasons to employ concurrent solutions in the first place is to get more performance, and programming-system overheads are less likely to be tolerated by users.

- Expressivity Moving from a single to many threads of control, and the requirement that threads can communicate and synchronize their activities, place additional demands on expressivity.

- Safety In addition to mutual exclusion and possible non-determinism mentioned in the previous section, issues such as deadlock and livelock have to be dealt with. Simple semantics that aid correctness proofs are essential.

It is likely that some readers will find what we consider a balanced design to be biased in favor of efficiency, then expressivity, and then safety. Our argument about the increased importance of efficiency in a concurrent-programming environment is sometimes disputed on grounds that, because concurrent systems offer better performance/cost than their sequential counterparts, one can afford more inefficiencies at the operating/runtime system level. The consequence of this view on concurrent architectures is that machines with pathetic process-creation and communication overheads are being designed and built. The major goals of the work described in this thesis are to show that this pitfall can be avoided, and to demonstrate that fine-grain concurrency can be efficiently exploited.

#### Extensions of C++

C++ is an object-oriented notation that is in widespread use due to its efficiency, availability, and upward compatibility with C. C++ is the starting point for numerous programming systems that attempt to amend C++ with concurrent semantics, including the system described in this thesis.

A comparison of our work to related concurrent-programming systems can be found in Section 6.1.

C+-

C+- is the result of an experiment to express reactive-process, concurrent programs (Section 1.4) in an object-oriented programming notation. Although C+- is an extension<sup>1</sup> of C++, the objective of the C+- project has *not* been to be able to execute arbitrary C++ programs efficiently on the Mosaic. The emphasis of C+- is on providing efficient support for the simple abstractions fundamental to the reactive-process computational model: process creation and communication. C+- strives not to impose higher-level policies on synchronization, communication protocols, or process placement.

Although the C+- programming system is portable across a wide range of architectures, the Mosaic has been both the driving force and the reality test behind this effort. Design decisions have consistently been made to avoid compromising the performance of C+- programs on the Mosaic. Higher-level programming systems may be layered on top of C+-, but C+- is intended to serve as the Mosaic's lowest-level, workhorse programming system, suitable both for operating-system and application programming.

The remaining sections of this chapter are devoted to teaching the reader about C+-. Familiarity with the basic concepts of object-oriented programming and of C++ in particular is assumed: classes, inheritance, access rules, operator overloading. Keywords are underlined in programming examples. Although an effort has been

<sup>&</sup>lt;sup>1</sup>C<sup>+-</sup> is not a superset of C<sup>++</sup> because it imposes restrictions on global variables, as discussed in Section 2.3.

CHAPTER 2. C+- 17

made to steer clear of the idiosyncrasies of C++, some of them were essential, and they are explained as they are encountered. The reader is cautioned, however, that C+- is by no measure a minimalist, toy-example-writing notation; some of the more advanced examples are likely to present difficulties to those not familiar with C++. Our hope is that this difficulty is the result of C+-'s completeness, rather than of poor design choices.

## 2.2 The Process Concept

The C++ object concept is carried over intact to C+-: class is a user-defined type; an object created according to a class definition is a collection of data items, a set of operations defined on them, and a set of access rules (Program 1). Class member functions have the usual, sequential semantics.

```

C

class

private:

data;

int

public:

C()

{ data = 0; }

// initialization

write(int i)

{ data = i; }

// update

<u>void</u>

int

read()

{ return(data); }

// retrieve

};

Program 1: A Class Definition

```

The process concept is the only extension that C+- introduces to C++. The processdef keyword parallels the class keyword syntactically (Program 2). Access rules are associated with data members and functions of a process definition, and process definitions can be derived from other process definitions (Section 2.4.1).

However, a process created according to a process definition is more than a collection of data items:

Specification 1 A process is an independent computing agent, and a unit of potential concurrency. Its public interface consists of a set of atomic actions.

```

P

processdef

<u>int</u>

data;

public:

P()

{ data = 0; }

// initialization

atomic

{ data = i; }

atomic

<u>void</u>

write(int i)

// update

read()

{ return(data); }

// retrieve

atomic

int

};

```

Program 2: A Process Definition

At creation time, the process constructor<sup>2</sup> is executed if it is defined. After the constructor completes, the process is at rest. The invocation of an atomic action of a C+- process is decoupled from its execution. Conceptually, there is an infinite queue of incoming requests for each process; the invocation of an atomic action places a request into this queue. Process execution consists of servicing these requests, with each atomic action running to completion.

Creating a process is no different from creating an object (Program 3). In most cases, processes are created dynamically (pp = new P;), and persist until they are explicitly destroyed (delete pp;). One can also create a temporary process as a local variable, just as with any other type (Pp;). This temporary process is destroyed implicitly when execution leaves its scope.

A C+- computation is initiated by a runtime system that, concurrently with initialization of global processes, creates an instance of root (Program 4), the constructor of which is defined by the user.

Specification 2 A process can affect the order of execution of its atomic actions by enabling and disabling them selectively, at run time. All atomic actions are initially enabled; execution of a disabled action is postponed until the action is enabled again.

For example, let us assume that the rules for accessing a process of type P in Program 2 are such that it may be updated only once; every subsequent write request

<sup>&</sup>lt;sup>2</sup>A process constructor is an atomic action with the same name as that of the process definition. The constructor may not return any value.

```

{

// declaring an integer

int i;

// declaring a process pointer

P* pp;

// creating a persistent process

pp = \underline{new} P;

i = pp->read();

// retrieving a value

pp->write(i+1);

// updating

// explicitly destroying the persistent process

delete pp;

{

// declaring a temporary process

Ρ

p;

i = p.read();

// retrieving a value

p.write(i+1);

// updating

}

// implicitly destroying the temporary process

}

```

Program 3: Programming with Processes

should be tagged as an error. Furthermore, all read requests occurring before the first write should be serviced only after the first update occurs. The process definition for this version of P is listed in Program 5.

Processes communicate and synchronize with each other through atomic actions. Thus far, we have discussed only the behavior of processes as servers — how they deal with incoming requests (invocations of their atomic actions). We shall now define the behavior of processes as clients — how they request services from other processes:

Specification 3 When invoking an atomic action that does not return a value (returns a void), or if the returned value is not used, the caller continues execution independently of the callee. The order of invocations is preserved for each pair of processes in direct communication. If the value returned by an atomic action is used, the caller may be suspended until the returned value is available.

```

Р

processdef

private:

initialized;

<u>int</u>

int

data;

public:

P();

atomic

write(int);

<u>atomic</u>

<u>void</u>

<u>atomic</u>

read();

int

};

P::P()

<u>atomic</u>

{

initialized = 0;

passive read;

}

P::write(int i)

atomic void

if ( initialized )

report_error();

}

<u>else</u>

data = i;

initialized = 1;

active read;

}

}

P::read()

atomic int

return(data);

}

```

Program 5: Enabling and Disabling Atomic Actions

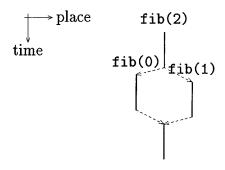

Invoking an atomic action that returns a value does not, in itself, imply that the requesting process will be suspended until the requested value is available. It is only when this value is used that a thread of activity must be suspended. For example, the Program 6 uses a divide-and-conquer approach to compute the  $n^{th}$  Fibonacci number. Both sub-computations are initiated, and the process will suspend only if it attempts to add the two partial results before they are available.

It is sometimes desirable to enforce the sequential order of execution of

```

fib

processdef

public:

atomic

compute (int n)

<u>int</u>

switch (n)

0:

return 0;

case

1:

case

<u>default</u>:

f1, f2;

(f1.compute(n-1) + f2.compute(n-2));

}

}

};

```

Program 6: Divide And Conquer

subcomputations. In such cases, the C+- await construct should be used. For example, <u>return</u> (<u>await(f1.compute(n-1)) + f2.compute(n-2))</u>; ensures that the first subcomputation is complete before the second one is initiated.

Programming systems differ considerably in what constitutes use of unresolved variables, also called *futures*. The most aggressive systems allow futures to be exchanged between processes, and suspend a thread only when a value is needed for a hardware-implemented expression evaluation. Support for futures is the central issue for numerous concurrent-programming systems [44, 86, 99]. C+- is not one of these systems, and is not very aggressive in trying to discover and utilize this type of concurrency. In C+-, assigning an unresolved value to any programmer-defined variable constitutes use of that future, and will cause the thread to be suspended. C+- guarantees only that a thread will not be suspended unnecessarily within an expression evaluation. C+- semantics allow any additional compiler/runtime system optimization, but only within the body of a function or an atomic action. Unresolved variables must be resolved before they can be passed as arguments.

The reason for C+-'s non-aggressive utilization of futures is that we want to encourage a programming style in which the concurrent behavior is generated explicitly, as opposed to trying to utilize the concurrency that is implicit in sequential formulation. Synchronization on an unresolved future is inherently more expensive

than, for example, synchronization using the active/passive semantics, because the process state that must be saved when blocking on a future is much larger. For notations that have stack-based implementations of the regular function-call abstraction, such as C+-, this state includes the stack.

## 2.3 Managing Concurrency

All concurrency-related issues in the C+- programming system are encapsulated into the process concept. The following syntactic restrictions enforce this requirement:

- Only atomic actions can be public members of a process definition.<sup>3</sup>

- Only values, process pointers, and process references<sup>4</sup> can be arguments to atomic actions.

- Processes are the only global<sup>5</sup> variables allowed.

- Process definitions can have no friends.6

As specified in Section 2.2, a process is a unit of potential concurrency. Processes communicate and synchronize with each other through atomic actions. The remainder of this section will be devoted to examples illustrating how some of the well-known concurrent-programming paradigms can be implemented in terms of C+- processes.

#### 2.3.1 Remote Procedure Call

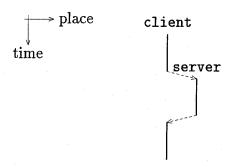

The remote procedure call (RPC) is a common form of interaction between threads of activity. As illustrated in Program 7 and in Figure 2.2, a client requests a service from a server and suspends its execution until the request has been attended to.

<sup>&</sup>lt;sup>3</sup>The C++ static member functions can be public members of a process definition, since their semantics do not allow them to access process members anyway.

<sup>&</sup>lt;sup>4</sup>The difference between pointers and references is a subtle idiosyncrasy of C++, and, for the purposes of this thesis, the two can be considered equivalent.

<sup>&</sup>lt;sup>5</sup>This includes both global and static C++ variables, i.e., all variables with file scope.

<sup>&</sup>lt;sup>6</sup>The friend construct in C++ allows non-member functions to have full access to private class members.

The semantics of the RPC are identical to those of an ordinary procedure call. The implementations of the two types of procedure calls, however, are typically different, because the client and the server may be operating in different address spaces. A better name for the RPC might be "interprocess procedure call."

```

processdef

server

public:

<u>atomic</u>

request (<u>int</u>);

<u>int</u>

};

processdef

client

public:

atomic

client (server* s)

<u>int</u> i = s->request(123);

}

};

Program 7: Remote Procedure Call

```

Figure 2.2: Remote Procedure Call

During a remote procedure call, the calling process is nominally suspended until the returned value is available, so no concurrency is introduced. However, as discussed in Section 2.2, with the use of futures, the semantics of the RPC can be extended so that several requests can be issued concurrently, and the calling process is suspended until all the requests have been serviced (Program 6 and Figure 2.3).

Figure 2.3: Divide And Conquer

## 2.3.2 Call Forwarding

Call forwarding is a paradigm associated with message-based object-oriented programming systems, and is similar to tail recursion. As an example, consider the sequential search of a singly-linked list of dictionary processes in Program 8.

```

processdef

dict

private:

dict*

next;

<u>int</u>

index;

<u>int</u>

data;

public:

atomic

int

find (int i)

if ( i == index )

return

data;

else

return next->find(i);

// can be replaced by:

forward next->find(i);

//

};

```

Program 8: A Sequential Search

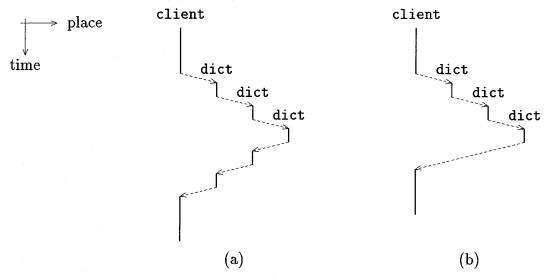

When the value returned from an atomic action is itself obtained by an atomic action invocation, programmer may choose to use the forward statement instead. With the return statement, a request is issued, the process is suspended until the value is available, and then reply is sent to the calling process. The effect of call forwarding is to defer servicing of the request to another process. Two sequential search examples, one using the return, and another the forward statement, are

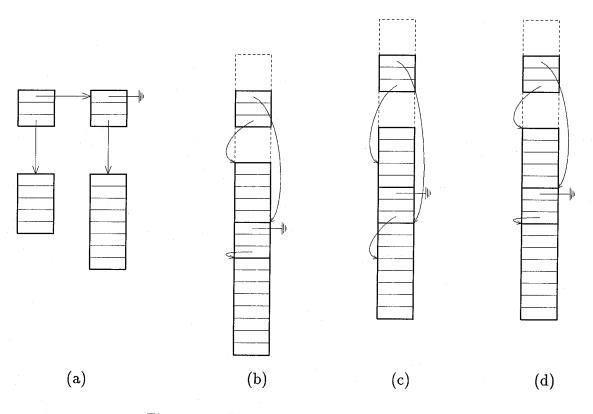

illustrated in Figures 2.4 (a) and (b), respectively. In addition to reducing the number

Figure 2.4: A Sequential Search with RPC (a), and with Call Forwarding (b)

of replies, call forwarding enables the list of processes that form a dictionary to process multiple requests in a pipeline fashion. At any point in time, each search request is being worked on by at most one dictionary process.

#### 2.3.3 Fork-Join

The remote-procedure-call mechanism with limited support for futures, as provided by C+-, offers a convenient and easy-to-understand programming paradigm for an important class of problems. A more flexible, fork-join mechanism for process synchronization in C+- is offered through the combination of non-suspending, atomicaction invocation and active/passive semantics.

There are two paradigms that C+- programmers can use to generate concurrent activities:

• Creating new processes, whether persistent or temporary. The parent process continues execution independently<sup>7</sup> of the child.

<sup>&</sup>lt;sup>7</sup>When a pointer to a newly created process is used in a subsequent computation, this may or may not require suspending the parent, depending on the implementation. However, the parent continues execution concurrently with child's constructor.

• Upon invoking an atomic action that does not return a value, or when the returned value is not used, the caller continues executing without waiting for the callee.

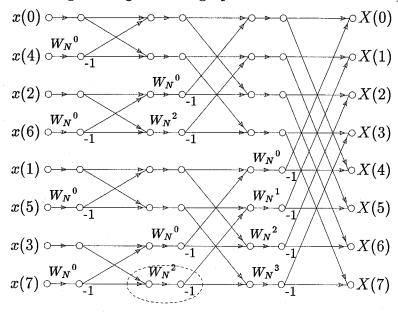

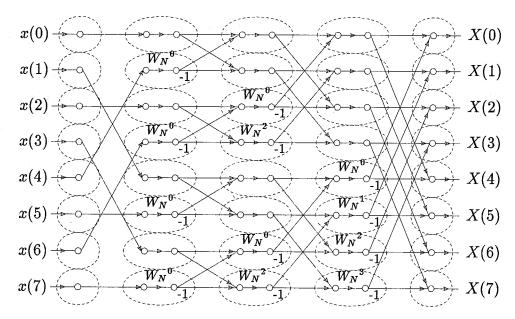

The synchronization barriers can be expressed using active/passive semantics. Suppose that an FFT computation is implemented as illustrated in Figure 2.5 [65]. The expressions along the edges of the graph are coefficients. Multiple inputs to a

Figure 2.5: An 8-Point FFT Computation.  $(W_N = e^{-i\frac{2\pi}{N}}, N = 8)$

node imply addition, and multiple outputs imply replication of the result.

A concurrent program for N-point FFT computation could employ N processes, and compute the result in  $\mathcal{O}(\log N)$  steps. Each step would consist of: getting two requests along the input edges; adding the two input values; multiplying by the coefficient; and producing two output values.

A version of this program could similarly employ  $N \log N$  processes in a pipeline regime, achieving the same  $\mathcal{O}(\log N)$  latency, but a new result would be computed on every step.

In either approach, though, a process (circled in Figure 2.5) must get one data item along each of its input edges to be able to compute and emit one data item along each of its output edges. A process that might be used as part of the FFT-computation pipeline is listed in Program 9.

```

processdef

fft

private:

Complex W, first;

*out_up, *out_dn;

output(Complex in)

<u>void</u>

Complex result = (first + in) * W;

out_up->up(result);

out_dn->dn(-result);

}

public:

fft(fft* u, fft* d, Complex r)

<u>atomic</u>

W = r;

out_up = u;

out_dn = d;

}

atomic void

up(Complex in)

if ( passive(dn) )

// upon receiving both requests

}

// produce the output

active dn;

output(in);

}

// if you only have one request

<u>else</u>

{

// await the second one

passive up;

first = in;

}

dn(Complex in)

atomic void

if ( passive(up) )

// upon receiving both requests

// produce the output

active up;

output(in);

}

<u>else</u>

// if you only have one request

// await the second one

passive dn;

first = in;

}

}

};

```

Program 9: An FFT-Computing Process

## 2.3.4 Semaphores

First introduced by E. W. Dijkstra [28], semaphores are low-level primitives for process synchronization. A semaphore is typically used to control access to a shared data structure, with an N-ary semaphore allowing access to at most N-1 processes at any point in time. Two operations are defined on semaphores: acquire and release. In general, an implementation of an N-ary semaphore must guarantee that the number of acquire operations minus the number of release operations is at most N-1, and at least 0. A C+- implementation of an N-ary semaphore is presented in Program 10.

```

semaphore

processdef

private:

int

count;

// number or processes inside

// the critical section

// the maximum number allowed

int

max;

public:

semaphore(int N)

// initially, there are no

atomic

// processes inside the critical

max = N - 1;

section

count = 0;

passive release;

acquire()

atomic int

{

count++;

// one more inside

active release;

// at least one can release

if ( count == max )

// if the maximum is reached,

passive acquire;

// no one can get in

return 1;

}

atomic int

release()

count--;

// one less inside

active acquire;

// at least one can acquire

<u>if</u> ( count == 0 )

// no one is in, so

passive release;

// no one can exit

return 1;

}

};

```

Program 10: N-ary Semaphore

An often-used special case for N=2, the binary semaphore, is illustrated in Program 11.

```

processdef

semaphore

public:

semaphore()

atomic

passive release;

acquire()

atomic int

{

<u>active</u> release;

passive acquire;

return 1;

}

release()

atomic int

active acquire;

passive release;

return 1;

}

};

```

Program 11: Binary Semaphore

### 2.3.5 Monitors

Of all of the concurrent-programming paradigms, semantics of C+- processes are closest to those of monitors [36]. Just as with monitors, C+- processes encapsulate a set of data items and offer mutually exclusive access to a set of routines operating on this data. C+- processes also share some of the problems associated with monitors, as both are non-reentrant. The invocation of an atomic action of a C+- process is, unlike an invocation of a monitor function, decoupled from its execution: conceptually, there is an infinite buffer of incoming requests for each process. This decoupling enables processes to be active computing agents, able to affect the order of execution of their atomic actions.

#### 2.3.6 Recursion

In the examples shown so far, the requirement that all the public member functions of a process be atomic actions has been helpful in expressing interactions between concurrent threads of activity. From the point of view of C+- programmers, the

most significant repercussion of the atomicity of interprocess activities is that, since at most one execution thread can be associated with a process, atomic actions that return values are not reentrant. For example, in Program 12, the private member function fac has ordinary, sequential, reentrant semantics. However, the public member function FAC must be an atomic action. An invocation of FAC will, therefore, result in deadlock.

```

processdef

bad

private:

fac(int n)

<u>int</u>

<u>if</u> ( n == 0 )

return 1;

else

return n * fac(n-1);

// OK: functions are reentrant

}

public:

FAC(int n)

atomic

<u>int</u>

<u>if</u> ( n == 0 )

return 1;

return n * FAC(n-1);

// ERROR: atomic actions are

// not reentrant

Fac(int n)

atomic int

{

return fac(n);

// OK: atomic-action interface

}

// to a function

};

```

Program 12: Recursive Functions and Non-Recursive Atomic Actions

In the world of non-reentrant atomic actions, processes are the medium used to express recursive behavior (Program 13).

## 2.3.7 Message Passing

Invoking an atomic action of a process is equivalent to wrapping up the argument list and sending it in a message. According to Specification 3, the atomic-action invocation does not imply blocking (waiting for the reply does), so it is equivalent to a non-blocking message send.

```

processdef

fac

private:

output;

<u>int</u>

public:

fac(int input)

<u>atomic</u>

\underline{if} ( input == 0 )

output = 1;

<u>else</u>

}

fac child(input-1);

output = input * child.result();

}

}

atomic int

result()

return output;

};

// or

processdef

fac

private:

int

input;

fac*

parent;

public:

fac(int i, fac* p)

<u>atomic</u>

{

\underline{if} ( i == 0 )

{

p->result(1);

<u>delete</u> this;

}

<u>else</u>

input = i;

parent = p;

new fac(i-1,this);

}

}

atomic void

result(<u>int</u> r)

parent->result(input*r);

<u>delete</u> this;

}

};

```

Program 13: Recursive Processes

Message receiving has two forms:

- explicit, associated with the behavior of processes as clients, which receive a value that is returned from a call to an atomic action; and

- *implicit*, associated with the behavior of processes as servers, which receive an argument list as part of a request to execute an atomic action.

The two forms of receive, explicit and implicit, cover the two extremes of the spectrum of possible mechanisms for message discretion: explicit receive accepts only a particular message from a particular process; implicit receive accepts any message from any process. The active/passive semantics provide a more general selective-receive mechanism: atomic actions of a process represent incoming communication channels, and the process can, at run time, select the communication channels over which it is ready to accept a message.

## 2.3.8 Single-Assignment Variables

Single-assignment variables are a safe form of futures (Section 2.2). Requesting a read access on an uninitialized, single-assignment variable causes the requesting process to be suspended until the variable is assigned to. Since there can be at most one assignment to a single-assignment variable, these variables can be effectively cached. Processes of type P in Program 5 are an example of a possible C+- implementation of single-assignment variables.

## 2.3.9 Process Aggregates

Thus far, we have described processes as independent entities, and have emphasized the code-execution aspects of processes. In this section, we shall show how processes can be treated as instances of a restricted data form, one that can be accessed only through a set of mutually exclusive, atomic actions.

As illustrated in Program 14, C+- programmers can treat processes as variables of any other type. Whether a process is a local variable, member of an object or of

```

processdef

р

// ...

};

<u>class</u>

C

// an object of class C contains:

public:

// a process

p;

P*

// and a process pointer

pp;

};

{

Ρ

// declare two processes

p1, p2;

p1 = p2;

// process assignment

p[10];

// declare a process array

}

Program 14: Treating Processes As Data

```

another process, element of an array, or used in any other way in which a variable can be used in C++, the process semantics are the same. According to the syntactic restrictions described in Section 2.3, the only operations allowed on a process are to take its address and to access its public members (all of which are atomic actions).<sup>8</sup> The various process usages determine only when a process is created and when it is destroyed. For non-process data types, variable usage also implies what the memory layout is. When accessing processes, one cannot assume, for example, that a process declared as a local variable resides on the stack; nor can one assume that a process that is a member of a class is placed in memory next to the other data members. In Section 3.1.1, we shall discuss how programmers can affect process-placement strategy.

The semantics of C+- are defined such that efficient implementations exist for both mainstream variants of MIMD computers: multiprocessors, which have one global address space, and multicomputers, which have multiple local address spaces. In C+-,

<sup>&</sup>lt;sup>8</sup>Process assignment is an atomic action invocation, equivalent to issuing a request to the source process to send a copy of itself to the destination process (Section 3.1.5). Passing processes as arguments is a form of assignment.

regardless of the underlying architecture, a pointer to a process can be dereferenced globally, since it contains sufficient information to uniquely identify the process it points to.

An important advantage that multiprocessors have over multicomputers is that they can employ most of the data-layout strategies developed for sequential computers. There are additional performance considerations guiding the design decisions on the data layout, as discussed in [46]. If, for the time being, we neglect such performance considerations, a vector of C+- processes could, on a multiprocessor, be laid out in memory in the same way as a vector of elements of any simple data type. Elements with successive indices would reside at memory addresses that differ by a stride equal to the size of the process. This approach would allow the programmer to compute the address of any process in the vector given the address of any other process in the same vector, and the two corresponding indices.

On a multicomputer, using the above layout strategy for vectors of processes is unacceptable for two reasons: first, the address space of a multicomputer is contiguous only within each multicomputer node, so the maximum size of a process vector would be limited by the size of node memory; and second, although the computation model allows elements of a process vector to operate concurrently, that concurrency could not be used to a performance advantage, because the elements would all reside on the same node.

This example is but an instance of a more general problem of naming constituent elements of distributed objects [26, 17]. There are two issues that are central to the solution of this problem. The first issue is that there should exist a single name (address) of a distributed object, and a way of addressing constituents given this name. The second issue is that the programmer should be able to compute on references, not just store them at process-creation time and fetch them when they need to be used.

A simple solution that takes only the first issue into the account could employ an address-manager process. The manager's address would represent the address of the distributed process as a whole. All the requests would be directed to this process,

and then forwarded to appropriate constituent processes. This solution obviously introduces an access bottleneck, but may be acceptable for element processes that exhibit a large ratio of computation/communication.

We consider this problem to be too important to be left to *ad hoc* approaches, particularly for such often-used paradigms as arrays of processes. Accordingly, C+- offers a runtime-system-supported mechanism for address management that preserves the C++ address-computation semantics.

The example in Program 15 shows that the creation of a process array consist of

Program 15: Creating A Vector of Processes

two stages. First, a set of unique references is allocated by invoking the unique\_\_CPM function, with arguments specifying how many references are required, and what the stride between the adjacent references should be. This function returns a pointer of the generic process-pointer type, pointer\_t, analogous to void\* in C++. Next, the actual process creation is requested, specifying that each new element process be placed in such a manner that it can be located through the given pointer. A description of various flavors of process creation is presented in Section 3.1.1. A set of algorithms that provide efficient support for process placement and lookup is described in [10].

## 2.3.10 **Summary**

The programming examples in Section 2.3 illustrate that a small set of mechanisms supported by C+- is sufficient to express a variety of concurrent-programming paradigms. This set consists of: process creation, asynchronous request, synchronous request (remote procedure call), and selective servicing of requests (active/passive mechanism). In Chapter 3, we shall present an implementation framework for this set of mechanisms.

# 2.4 Managing Program Complexity

In the introductory section of this chapter, we discussed how object-oriented programming techniques came about through efforts to aid programmers in managing program complexity. All of the object-oriented techniques supported by C++ are extended to managing processes in C+-. The interested reader may consult the wealth of available literature on C++, including, but not limited to [32].

In the remainder of this section, for completeness, we shall mention briefly two of those techniques: inheritance and virtual functions. We shall then discuss the techniques that are specific to C+- and concurrent programming: process layering, process libraries, and customizing of the data exchange.

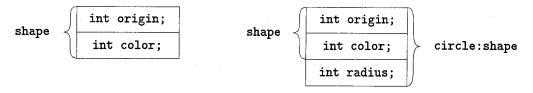

## 2.4.1 Class Inheritance

Class inheritance is the C++ mechanism that enables user-defined types to be derived from more basic types, inheriting data members and functions from the base type, possibly adding new ones and/or overriding old ones. Access rights are associated with each class member. For example, in Program 16, private members of the base class shape can be accessed only by member functions of shape; protected members of shape can, in addition, be accessed by member functions of any class derived from shape (for example, circle); and public members of shape can be accessed by any piece of code anywhere in the program. The class circle is

```

<u>class</u>

shape

private:

origin;

modify_origin();

protected:

color;

<u>void</u>

modify_color();

public:

draw();

<u>void</u>

};

<u>class</u>

circle : shape

private:

radius;

public:

modify_radius();

draw();

<u>void</u>

};

Program 16: Class Inheritance

```

derived from class shape by adding a data member (radius) and a member function (modify\_radius()), and by overriding the member function draw().

A typical memory layout for the two classes is shown in Figure 2.6. The point to

Figure 2.6: Class Inheritance vs. Memory Layout

be remembered is that C++ class inheritance is a compile-time rather than a runtime mechanism.<sup>9</sup> Every instance of class circle contains a part corresponding to an instance of class shape; it is the definition of class shape that is shared, not any particular instance of it.

The C++ class-inheritance mechanism is mimicked by process definitions in

<sup>&</sup>lt;sup>9</sup>Neglecting, for the time being, such C++ features as multiple inheritance and virtual functions.

C+-; they too can be specified through their similarities with and differences from previously-defined process definitions.

#### 2.4.2 Virtual Functions

The virtual-function mechanism supported by C++ is a mechanism that enables programmers to separate the design of member-function interfaces from the design of member functions themselves.

For example, in Program 16, given a shape\* sp, and a circle\* cp, the invocation of sp->draw() and cp->draw() will result in calling shape::draw() and circle::draw(), respectively. The compiler decides which call to generate based on the type of pointer through which the function has been called.

Had the two draw() functions been virtual, the invocation of sp->draw() could have invoked either of the two functions, depending on what the pointer sp pointed to. In this case, the compiler generates an indirect call through the class-specific table.

## 2.4.3 Process Layering

The standard C++ inheritance mechanism allows one to describe process definitions hierarchically. However, once a process is created, it is an independent entity. The hierarchy is reflected in its structure, *not* in its relationship with other processes.

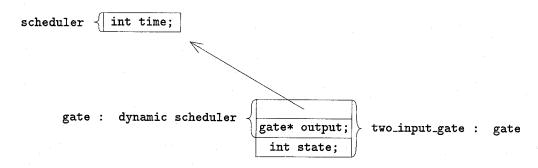

There are important applications where, in addition to hierarchy in structure, it is useful to have runtime-exercised hierarchy in control. For example, in operating or runtime systems [10], user processes are created and managed by system processes. In simulators [91], processes that model the behavior of physical elements are managed by time- or event-driven schedulers.

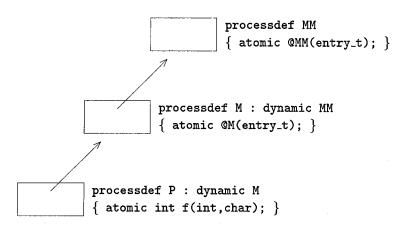

The mechanism that C+- uses to support such applications is process layering, also called dynamic process inheritance. As illustrated in Program 17 and Figure 2.7, every instance of processdef gate is managed by an instance of processdef scheduler. The details of process layering will be discussed in Section 3.1, which

```

processdef

scheduler

private:

<u>int</u>

time;

};

processdef

gate : dynamic scheduler

protected:

gate*

output;

};

processdef

two_input_gate : gate

private:

state;

<u>atomic</u>

<u>void</u>

input1(int);

<u>atomic</u>

input2(int);

<u>void</u>

};

```

Program 17: Process Layering

Figure 2.7: Process Layering vs. Memory Layout

describes the C+- runtime-system interface. The relationship between the manager process and the managed process is established at the creation time of the managed process. The manager provides a set of services to all processes that it manages, with the same access protection that is offered through the class-inheritance mechanism. The manager decides when an atomic action of any of the processes managed by it is executed (as opposed to invoked), while conforming to the definitions of process behavior as specified in Section 2.2.

#### 2.4.4 Process Libraries

Libraries of C+- processes can be organized in the same way as libraries of data structures in C++. In most cases, the remote procedure calls to atomic actions of processes form a suitable interface, and these calls replace the class member-function interfaces. In these cases, it is sufficient that programs include header files that contain interface-process definitions.

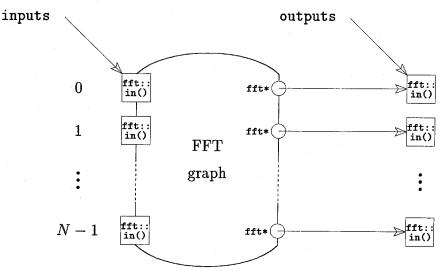

There are cases, however, in which imposing the RPC interface would overly serialize computations that are otherwise concurrent. For example, a process library might initialize a set of processes for FFT computation, as illustrated in Section 2.3.3, employing several input and several output data streams. A stream of input values can be represented by a sequence of non-blocking atomic-action invocations. If a stream of output values were represented as a sequence of replies obtained through the RPC mechanism, just as in the sequential-search example of Section 2.3.2, the computation could not be pipelined. However, unlike in this search example, this problem could not be resolved with call forwarding.

The mechanism typically used for C+- libraries with multiple input and output streams is as follows: an input stream is represented by a sequence of non-blocking atomic-actions invocations of an input-interface process; an output stream is, similarly, a sequence of non-blocking atomic-actions invocations of a process provided by the library user. In this arrangement, the library-user process must be derived from the output-interface process of the library it uses (Section 2.5). When a process uses multiple libraries, multiple inheritance is employed to derive such a process from all of the output-interface processes from which it requires results.

# 2.4.5 Data Exchange

The designers of C++ made a commendable effort to provide an overloading mechanism that enables programmers to pass arguments by value, even when these arguments are arbitrarily-complicated, linked, data structures. This mechanism is not sufficient for concurrent-programming systems, which must take into account some additional

considerations. On multicomputers, object pointers have local meaning. Also, concurrent computers may be heterogeneous ensembles comprised of machines with different data layout, alignment, size, or representation.

C+- addresses all of these potential problems at the inter-process-communication level (invocations of atomic actions) with mechanisms that are described in the remainder of this section. The communication specifications are *declarative*, as opposed to *imperative*: the programmer specifies what special actions should be taken when a data item of certain type is communicated; the compiler guarantees that actions thus specified will be invoked on every occurrence of communication.

## Communicating Arbitrarily-Complex Data Structures by Value

One of the premises of fine-grain concurrent programming is that large data structures are implemented in terms of many small, cooperating processes, so it is tempting to claim that process pointers that can be globally dereferenced are all that programmers might possibly want. However, an important use for pointers in C++ is for data structures that are only partially specified at compile time: linked data structures and arrays of variable size. If proper support and clean semantics for this feature were not offered, users would have resorted to ad hoc solutions.