# SWITCHING CONVERTERS WITH MAGNETIC AMPLIFIERS AS CONTROLLABLE SWITCHES

I: Soft-Switching Converters

II: Input Current Shaping

Thesis by

Milivoje Slobodan Brkovic

In Partial Fulfillment of the Requirements

for the Degree of

Doctor of Philosophy

California Institute of Technology

Pasadena, California

1994 (Submitted January 10, 1994)

© 1994 Milivoje S. Brkovic All Rights Reserved  $to\ my\ parents\ Slobodan\ and\ Dragica$

### Acknowledgements

I wish to thank my advisor, Professor Slobodan Ćuk for accepting me in the Caltech Power Electronics Group and for his guidance, generous support, and encouragement. Also I thank my co-advisor, Professor R. D. Middlebrook for his support and guidance.

I would like to acknowledge the financial support of California Institute of Technology by the way of Graduate Teaching Assistantship and of the following corporations who supported my Graduate Research Assistantships: Apple Computer Inc., Boeing, Day-Ray Products Inc., GEC Ferranti Defense Systems Ltd., General Electric Co., Italtel Inc., Rockwell International Inc., MagneTek Inc., and Southern California Edison.

Credit is due to all present and former members of the Power Electronics Group who have enriched the laboratory with useful computer programs and tools. Special thanks must go to Dr. A. Pietkiewicz, now with the ASCOM Power Systems, Switzerland, for sharing with me the original idea of novel soft-switching converters with magnetic amplifiers.

Thanks also go to all of our predecessors, who have left behind high standards for us to meet, and a large body of knowledge for us to build on.

I thank the support of my former professors and specially my advisor at the University of Belgrade, Yugoslavia, Slavoljub Marjanovic who introduced me to the field of power electronics. Also I thank my colleges at Institute of Physics, Belgrade for their support and the pleasure of friendship.

I must express my deep gratitude to my parents, Slobodan and Dragica Brkovic, for their love, generous support, guidance and encouragement during all these years. Finally, I wish thank my wife Natasha for her love and support.

#### Abstract

#### Part I

Novel soft-switching converters combine the functions of loss-less soft-switching for all switches and secondary side output voltage regulation at constant switching frequency. This was made possible by using magnetic amplifiers in series with the rectifier diodes in the symmetrical topologies. The primary side switches are driven at constant frequency and near 50% duty ratio with small dead-time and the output voltage is regulated by pulse width modulation (PWM) control on the secondary side.

All three soft-switching topologies, half-bridge, full-bridge and push-pull, are analyzed. It was found that the multiple-output extension of these converter do not have some serious adverse effects inherent to their parent PWM converters with magnetic amplifier post-regulators.

Experimental results obtained on two different prototypes confirm the key advantages of the proposed soft-switching converters.

#### Part II

Two classes of automatic current shapers are analyzed, with external and internal capacitive energy storage.

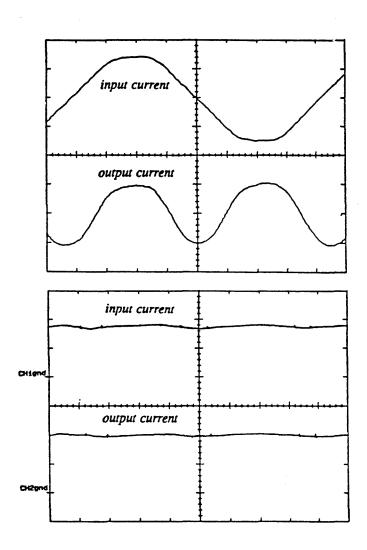

The Ćuk converter with Integrated Magnetics when operated in DICM with external energy storage exhibits advantages over other automatic current shaper topologies. Unity power factor is provided automatically and by using "ripple steering" mechanism essentially zero input and output current ripples are obtained for all operating conditions. Consequently, the size of the magnetics can be significantly reduced even at very modest switching frequencies.

The requirement for fast output regulation implies that low-frequency energy is stored

internally in the input current shaper. A new AC-to-DC converter which combines the functions of automatic current shaping, fast output voltage regulation, and loss-less soft-switching in a single converter is proposed. This was made possible through internal energy storage and discovery of the new modes of operation, which together, effectively decoupled the input boost-like part of the Ćuk converter from its buck-like output. In order to keep the voltage stress on the switches low, the variable frequency control is required in addition to PWM control.

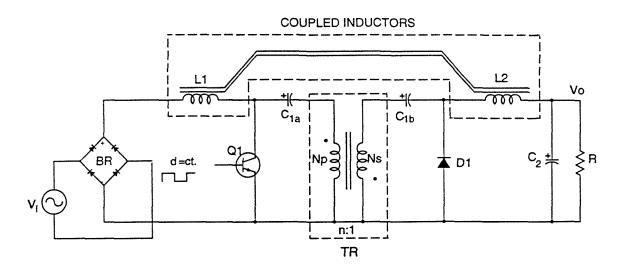

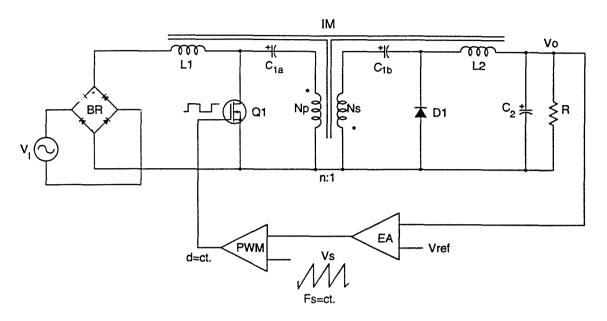

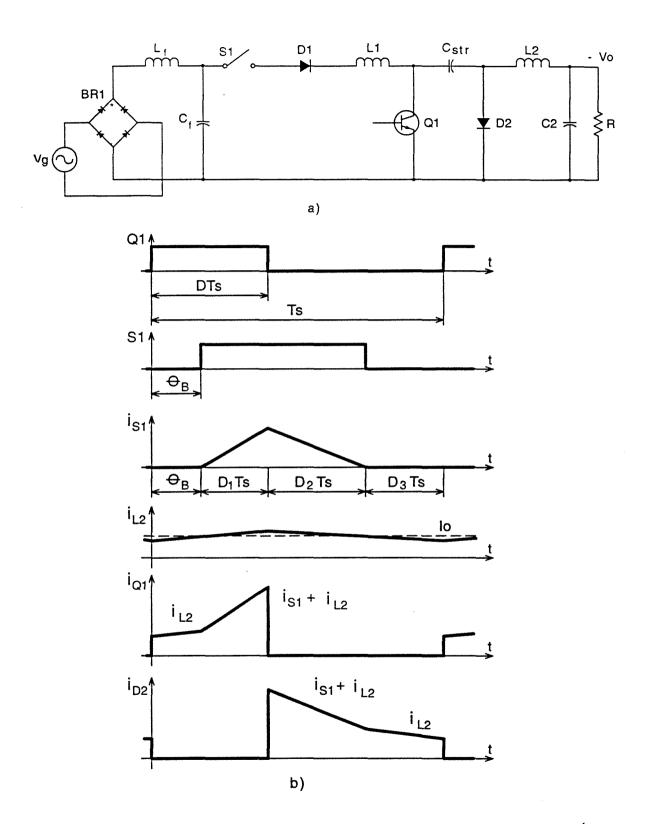

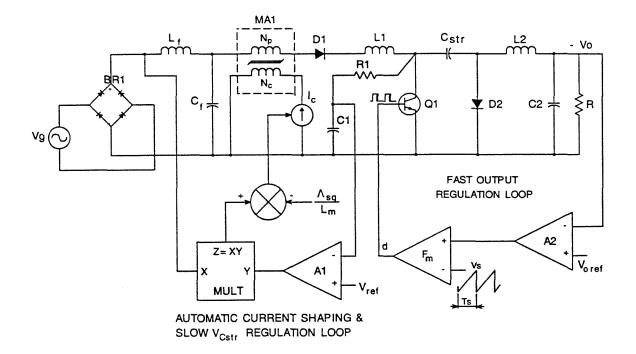

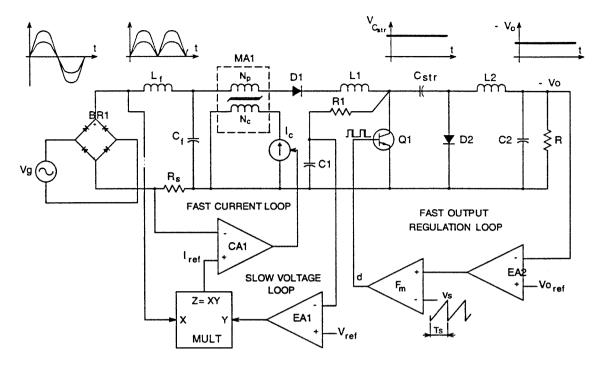

Another novel class of single stage AC-to-DC converters with unity power factor and fast output regulation is also proposed. These converters use a magnetic amplifier for the input current shaping, while the active switch is used for fast output regulation. By using core material for magnetic amplifiers with high saturated permeability, and operating the input stage of the converter in DICM, the linear input inductance can be replaced by the saturated inductance of the magnetic amplifier. Thus, the magnetic amplifier combines the functions of a controllable switch and a linear inductor into a single device.

The proposed method of current shaping with magnetic amplifiers is extended to the full-bridge topologies with their input, boost-like stage operated in continuous conduction mode.

Experimental results obtained on different prototypes confirm advantages of the proposed topologies.

## Contents

| Acknowledgements |       |         |                                                        | iv |

|------------------|-------|---------|--------------------------------------------------------|----|

| ΑÌ               | bstra | ct      |                                                        | v  |

| Ι                | Sof   | t-Swit  | ching Converters                                       | 1  |

| 1                | Intr  | oducti  | ion                                                    | 2  |

| 2                | Rev   | view of | Saturable Inductors and Magnetic Amplifiers            | 5  |

|                  | 2.1   | A Piec  | cewise-Linear Model for Magnetics                      | 5  |

|                  |       | 2.1.1   | Relating Material Properties to Device Characteristics | 6  |

|                  |       | 2.1.2   | The Magnetic Model                                     | 7  |

|                  |       | 2.1.3   | The Electrical Model                                   | 8  |

|                  | 2.2   | Princi  | ple of Operation of Saturable Inductor                 | 9  |

|                  | 2.3   | Magai   | -<br>mp                                                | 13 |

|                  |       | 2.3.1   | A Magamp Control                                       | 14 |

|                  |       | 2.3.2   | Voltage Reset Method                                   | 15 |

|                  |       | 2.3.3   | Current Reset Method                                   | 18 |

|                  | 2.4   | Magai   | mp as a Post-Regulator                                 | 19 |

|                  | 2.5   | Ŭ       | ations of the Magamp as a Switch                       |    |

| 3                | A S   | Survey  | of Soft-Switching Converters                           | 28 |

|                  | 3.1   | Switch  | hing Loss Mechanisms in PWM Converters                 | 28 |

|                  |       | 3.1.1   | Switching Losses Due to Diode's Reverse Recovery Time  | 30 |

|                  |       | 3.1.2   | Switching Loss Mechanism Due to Parasitic Capacitance  | 32 |

|                  |       | 3.1.3   | Switching Loss Mechanism Due to Parasitic Inductance   | 33 |

|   | 3.2   | Differe | nt Approaches to Switching Loss Elimination                     | 34         |

|---|-------|---------|-----------------------------------------------------------------|------------|

|   |       | 3.2.1   | Resonant Converters                                             | 34         |

|   |       | 3.2.2   | Soft-Switching Converters                                       | <b>3</b> 8 |

|   | 3.3   | Differe | ent Approaches to Soft-Switching in PWM Converters              | 39         |

|   |       | 3.3.1   | Basic Principle of Soft-Switching Mechanism                     | 39         |

|   |       | 3.3.2   | Soft-Switching Phase Shifted Full-Bridge Converter              | 43         |

| 4 | A N   | lovel S | oft-Switching Half-Bridge Converter With Magamps                | 51         |

|   | 4.1   | Conve   | ntional Half-Bridge Converter                                   | 51         |

|   | 4.2   | A Nov   | el Soft-Switching Half-Bridge Converter                         | 54         |

|   |       | 4.2.1   | Circuit Description                                             | 54         |

|   |       | 4.2.2   | Soft-Switching Mechanism                                        | 54         |

|   | 4.3   | Comp    | arison of Soft-Switching Mechanisms                             | 58         |

|   | 4.4   | Outpu   | t Voltage Regulation                                            | 59         |

|   | 4.5   | Switch  | Realization                                                     | 62         |

|   | 4.6   | Exten   | ded Range of Soft-Switching                                     | 63         |

|   | 4.7   | Reduc   | tion of Circulating Current                                     | 64         |

|   | 4.8   | Exper   | imental Results                                                 | 67         |

|   |       | 4.8.1   | Circuit Description                                             | 67         |

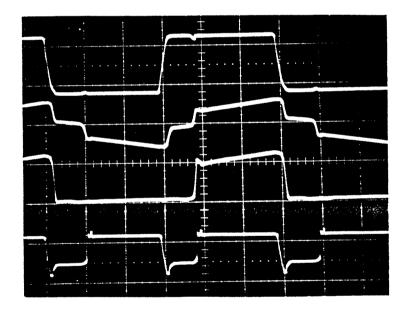

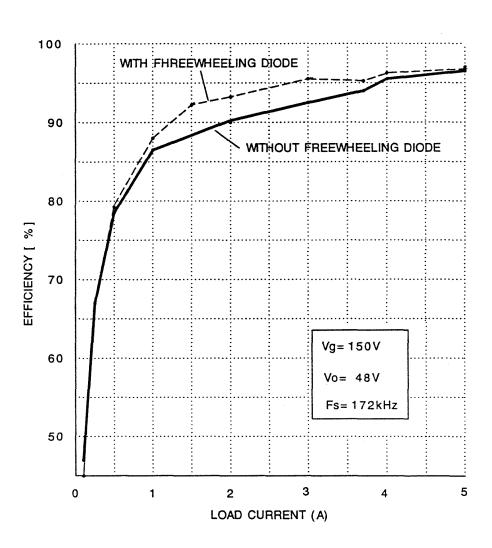

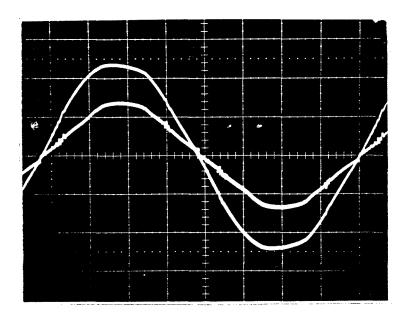

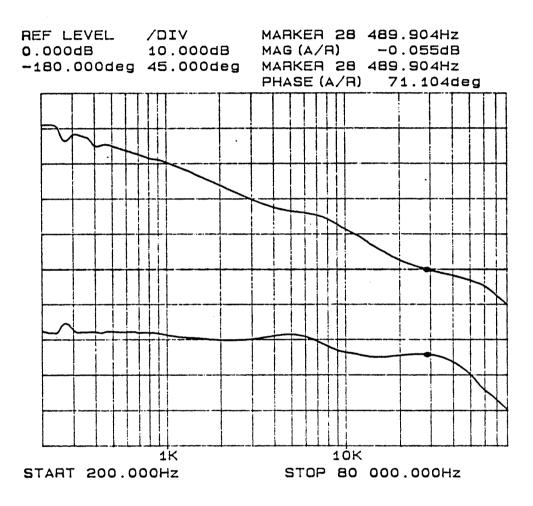

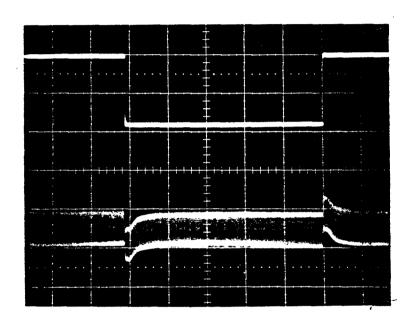

|   |       | 4.8.2   | Experimental Waveforms                                          | 70         |

|   |       | 4.8.3   | Efficiency Measurement                                          | 74         |

| 5 | Ext   | ension  | of Novel Soft-Switching Mechanism to Other Symmetrical          | l          |

| T | opolo | gies    |                                                                 | 77         |

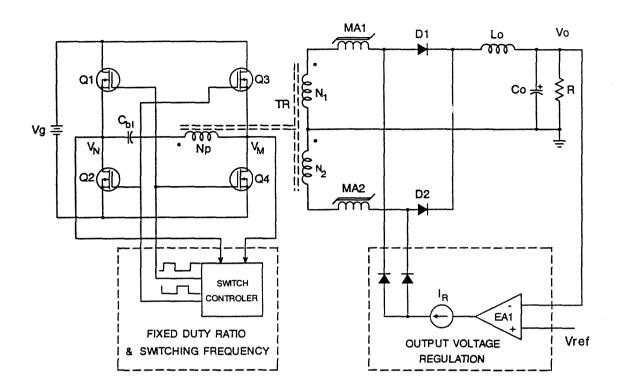

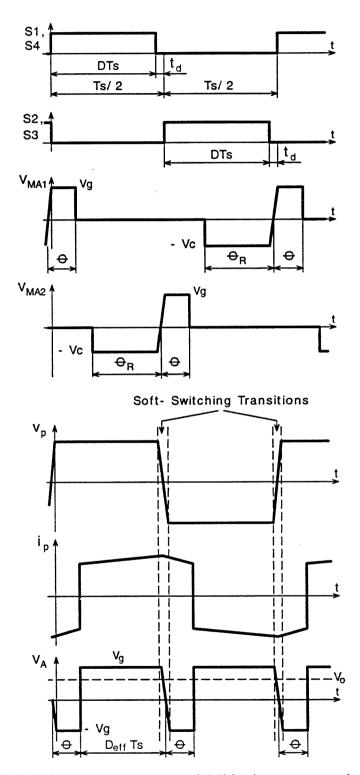

|   | 5.1   | Soft-S  | witching Full-Bridge Converter with Magamps                     | 77         |

|   |       | 5.1.1   | Circuit Description                                             | 77         |

|   |       | 5.1.2   | Comparison Between a Novel Soft-Switching Full-Bridge and Soft- |            |

|   |       |         | Switching Phase-Shifted Full-Bridge Converter                   | 80         |

|   | 5.2   | Soft-S  | witching Push-Pull Converter with Magamps                       | 82         |

|   | 5.3   | Exper   | imental Results                                                 | 83         |

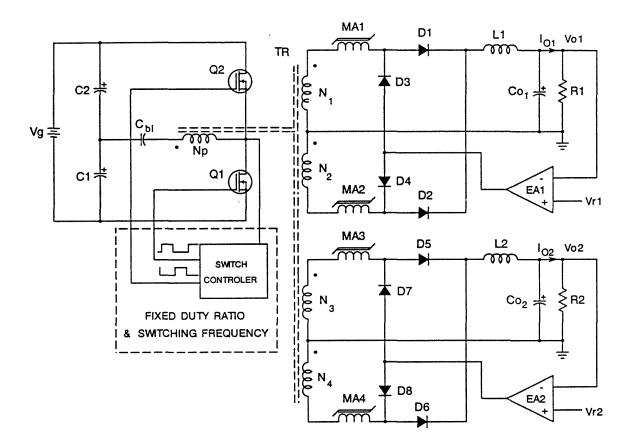

| 6  | Mul  | tiple-Output Extension                                                         | 87          |

|----|------|--------------------------------------------------------------------------------|-------------|

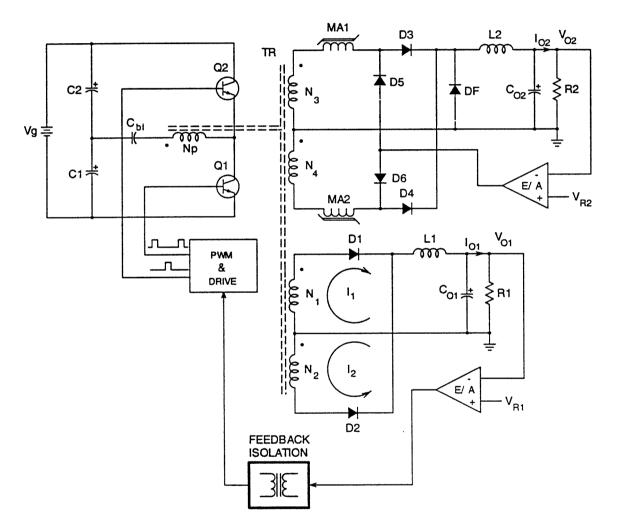

|    | 6.1  | Adverse Effects of Magamp Post-Regulators in Symmetrical Topologies            | 88          |

|    | 6.2  | $Novel\ Multiple-Output\ Soft-Switching\ Converters\ with\ Magamp\ Regulators$ | 92          |

| 7  | Con  | clusion                                                                        | 94          |

| II | Αι   | stomatic Input Current Shaping                                                 | 96          |

| 8  | Intr | oduction                                                                       | 97          |

| 9  | Inp  | ut Current Shaping                                                             | l <b>01</b> |

|    | 9.1  | The Need for Input Current Shaping                                             | 101         |

|    | 9.2  | Power Factor                                                                   | 102         |

|    | 9.3  | Functions and Limitations of the Input Current Shaper                          | 104         |

|    | 9.4  | Minimum Stored Energy                                                          | 105         |

|    | 9.5  | Output Voltage Regulation                                                      | 106         |

| 10 | DC-  | to-DC Converters in Current Shaping Applications 1                             | L <b>08</b> |

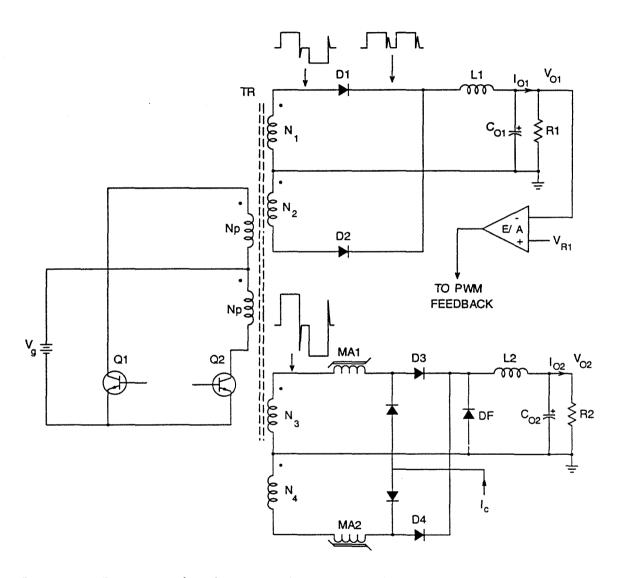

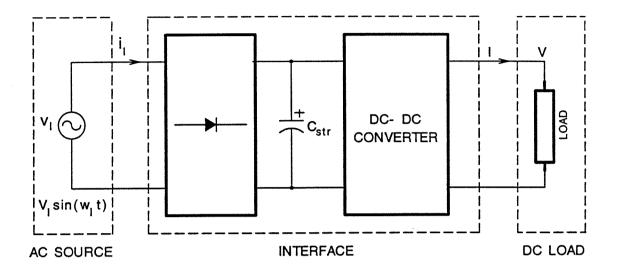

|    | 10.1 | Environment of a Current Shaping Converter                                     | 109         |

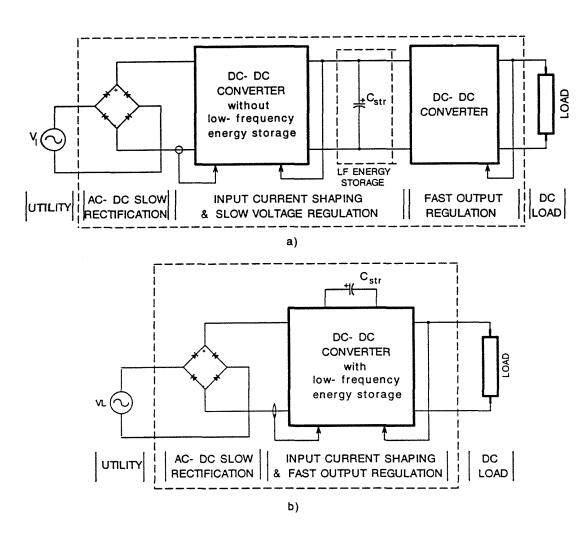

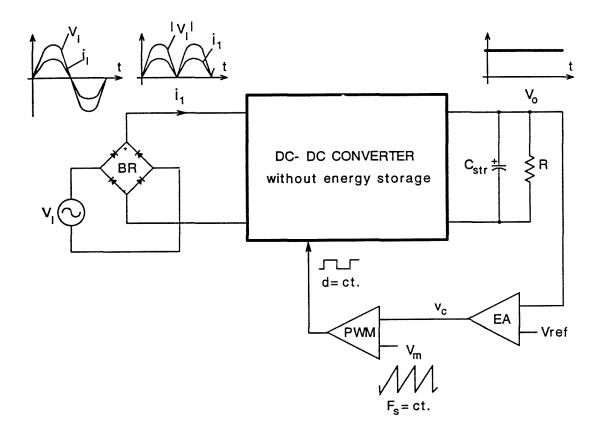

|    | •    | 10.1.1 Current Shapers with External Energy Storage                            | 110         |

|    | 10.2 | Current Shapers with Internal Energy Storage                                   | 112         |

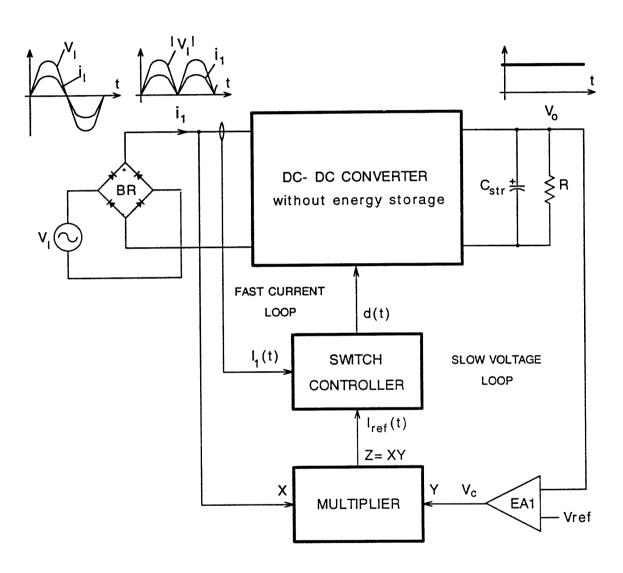

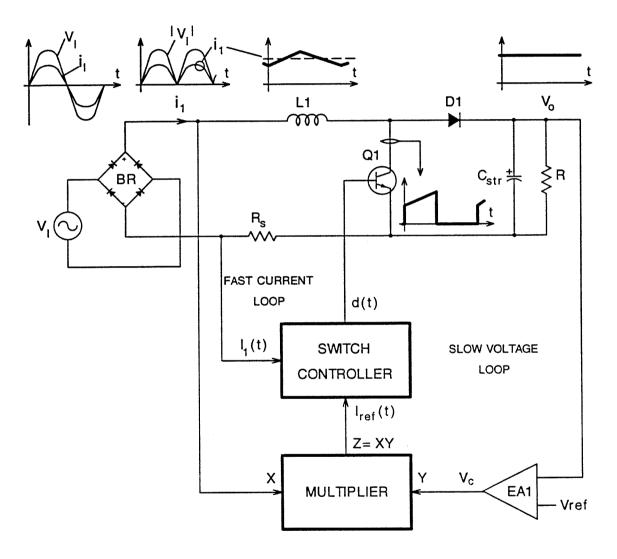

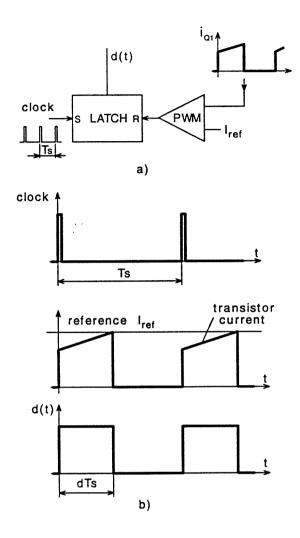

|    | 10.3 | Current Shapers with Current Feedback                                          | 115         |

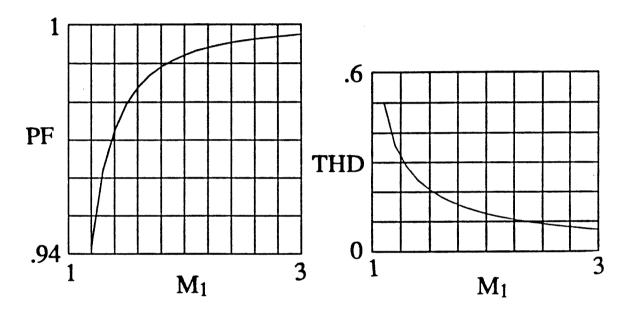

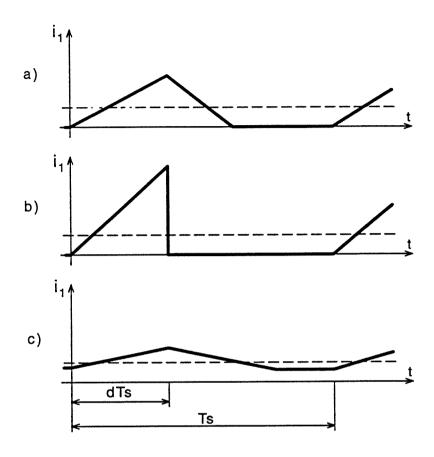

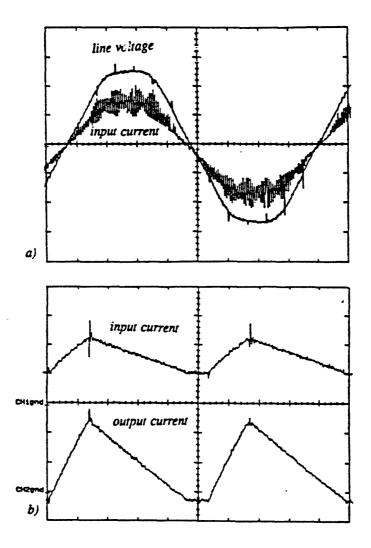

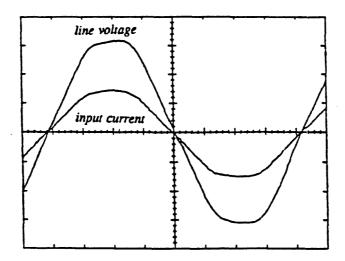

|    | 10.4 | Automatic Current Shaping                                                      | 120         |

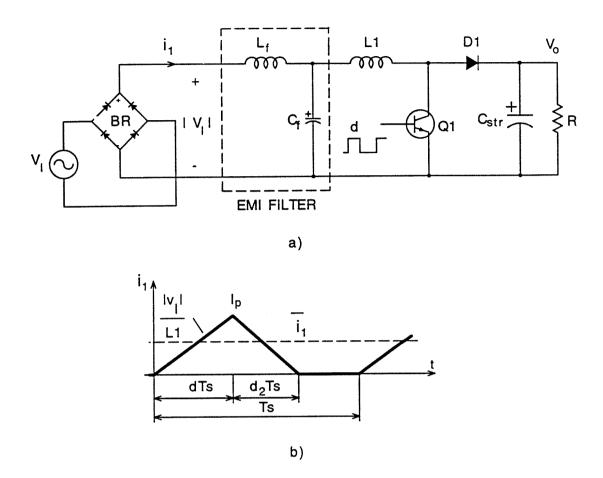

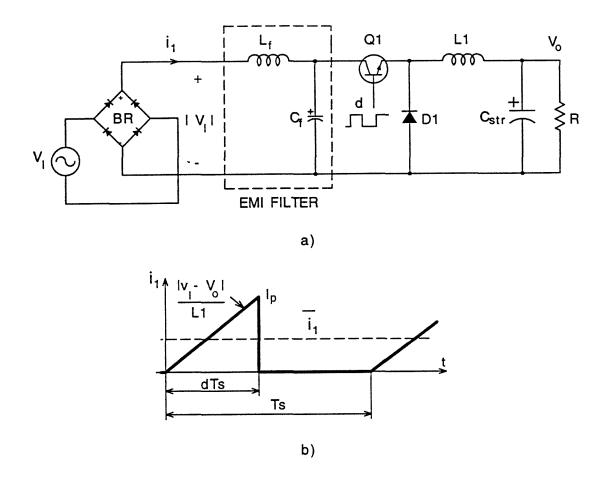

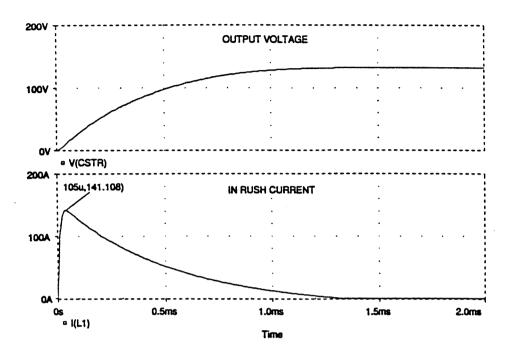

|    |      | 10.4.1 DCM Boost Shaper                                                        | 121         |

|    |      | 10.4.2 DCM Buck Converter                                                      | 124         |

|    |      | 10.4.3 DCM Flyback Shaper                                                      | 124         |

|    | 10.5 | Input Current Waveform Distortion                                              | 126         |

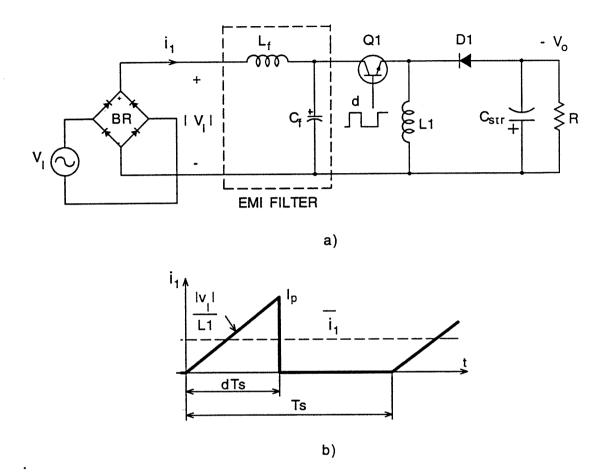

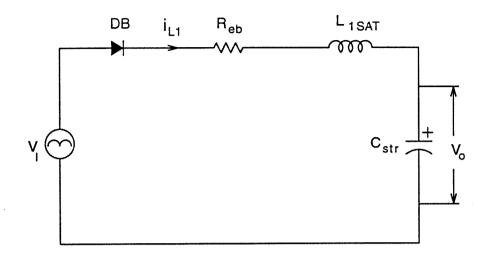

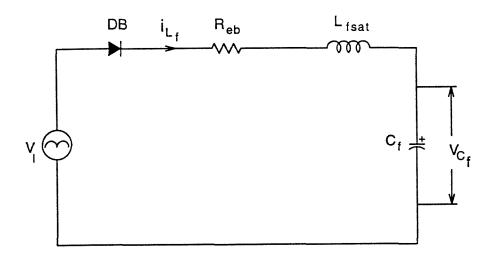

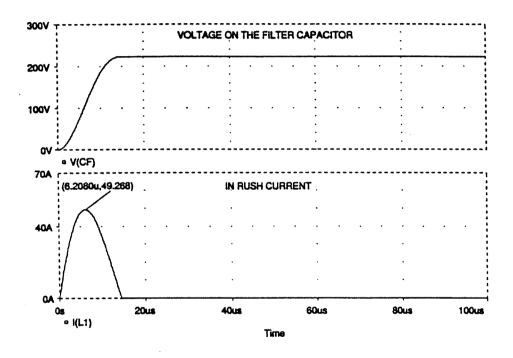

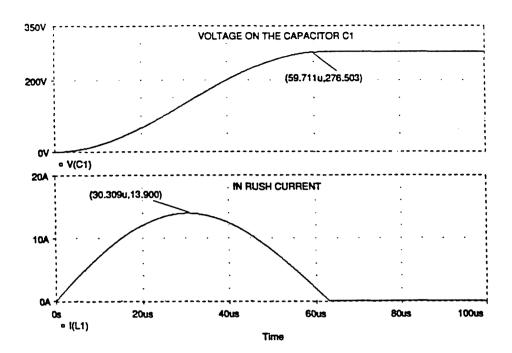

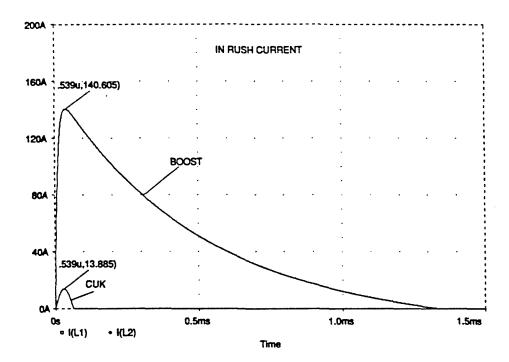

|    | 10.6 | Inrush Current Problem and Short Circuit Protection                            | 128         |

| 11 | Aut  | omatic Current Shaper Using Ćuk Converter 1                                    | 133         |

|    | 11.1 | Input Current Shaper Using Ćuk Converter in DICM                               | 133         |

|    | 11.2 | Current Waveform Distortion Due to Switching Ripple                            | 137         |

|    | 11.3 | Coupled-Inductor Extension                                                     | 139         |

| 11.4    | Integrated Magnetics Topology                                        |

|---------|----------------------------------------------------------------------|

| 11.5    | Inrush Current and Overload Protection                               |

| 11.6    | Experimental Results                                                 |

| 12 Auto | omatic Current Shaper with Fast Output Regulation and Soft-          |

| Switchi | ng 151                                                               |

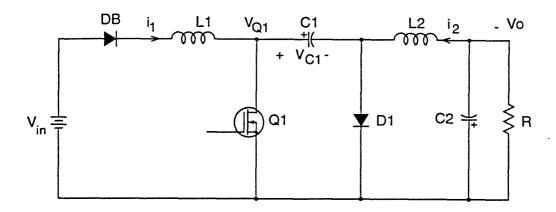

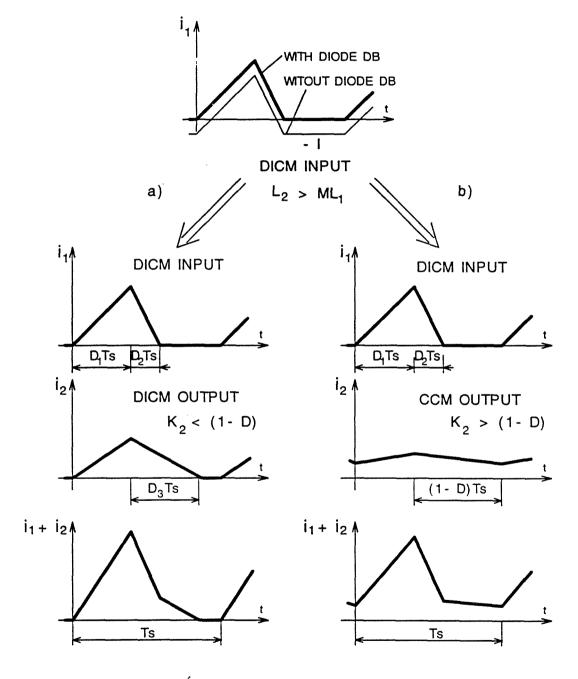

| 12.1    | New DICM Modes in the Ćuk converter                                  |

|         | 12.1.1 Review of the DICM in the Ćuk converter                       |

|         | 12.1.2 Decoupling of DICM in Two New Modes                           |

| 12.2    | DC Analysis                                                          |

|         | 12.2.1 Input Current Waveform                                        |

|         | 12.2.2 Input Inductor in DICM and Output Inductor in CCM $\dots$ 159 |

|         | 12.2.3 Both Inductors in DICM                                        |

| 12.3    | Fast Output Regulation and Automatic Current Shaping 162             |

| 12.4    | Sizing of the Reactances                                             |

| 12.5    | Zero-Voltage Switching                                               |

| 12.6    | Experimental Results                                                 |

|         | 12.6.1 Description of the Circuit                                    |

|         | 12.6.2 Experimental Waveforms                                        |

| 13 Nov  | el Single Stage AC-to-DC Converters Using Magamp for Input           |

| Curren  | t Shaping 177                                                        |

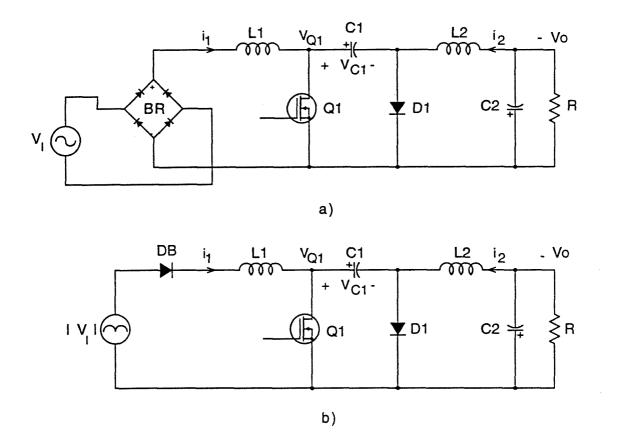

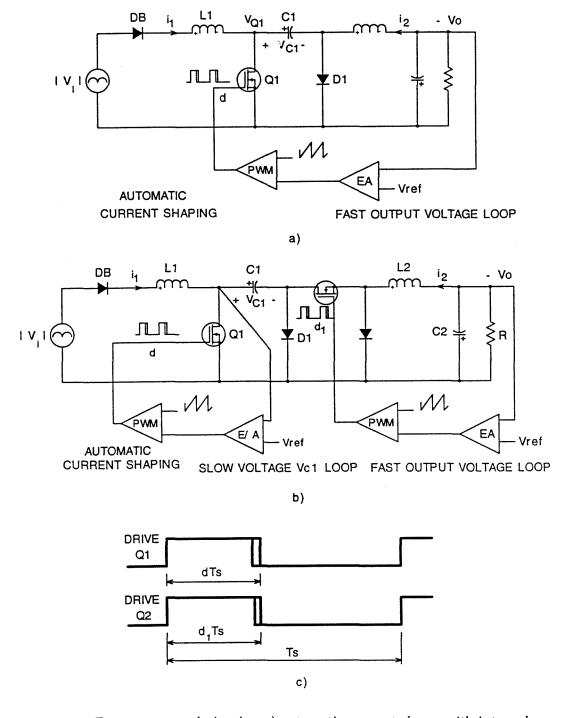

| 13.1    | Problem Statement                                                    |

| 13.2    | Input Current Shaping with Magamp                                    |

| 13.3    | Requirements for Core Material                                       |

| 13.4    | DC Analysis                                                          |

| 13.5    | Control of Magamp Used for Input Current Shaping 189                 |

|         | 13.5.1 Automatic Current Shaping with Magamp 190                     |

|         | 13.5.2 Input Current Shaping with Magamp Using Average Current Mode  |

|         | Control                                                              |

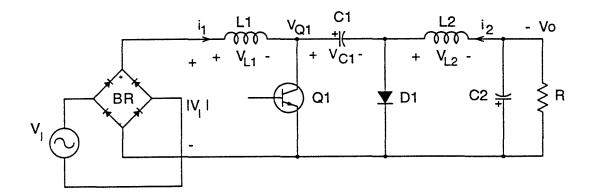

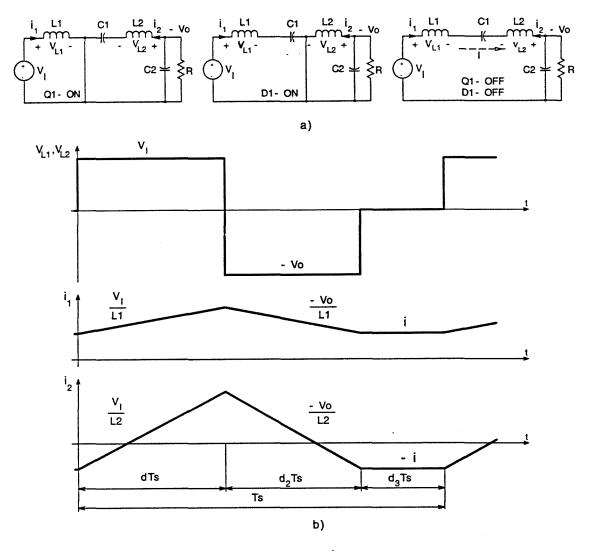

| 13.6    | Shapers with Discontinuous Input Current                             |

| 13.6.1 Shapers Using a Single Transistor Converter | 19  |

|----------------------------------------------------|-----|

| 13.6.2 Bridge Topology Shapers                     | 19  |

| 13.7 Shapers with Continuous Input Current         | 20  |

| 13.8 Experimental Results                          | 210 |

| 13.8.1 DICM Single Transistor Shaper               | 21  |

| 13.8.2 CCM Full-Bridge Shaper                      | 21  |

| 14 Conclusion                                      | 21' |

# Part I

**Soft-Switching Converters**

#### Chapter 1

#### Introduction

With increased demand for faster response and reduced size and weight, the switching frequency of power converters is increasing toward the megahertz range. By increasing switching frequency of the converters, designers face different kinds of problems. The most serious problems related to the high switching frequency are switching losses which drastically degrade overall converter efficiency.

Over several years, the interest in high-frequency power conversion has stimulated the conception of many different converter circuits. Plenty of them are available for every application, and each year several more are going to be introduced. Every one of these topologies offers some particular combination of the following features: low-current stresses, low-voltage stresses, additional control, wide range of conversion ratio, low cost, and simplicity. There is no single topology which is superior in all these areas, so the choice of topology is left to the designer.

While faster power transistors have mitigated overlap loss, the reverse-recovery time of the power diodes as well as voltage spikes and discharging current of the parasitic capacitances start to be a limiting factor in PWM converters. Resonant converters [13, 14, 15] and their derivatives quasi-resonant [17, 18, 19, 20, 21] and multi-resonant converters [22] having continuous waveforms were introduced as a solution for switching loss elimination and higher power density than PWM converters. It turned out that due to increased conduction losses and complex control, resonant converters are only used in very specific applications. Soft-switching converters, recently introduced, combine advantages of both PWM and resonant converters and are becoming a very promising solution for highly efficient and high power density conversion.

Resonant elements in the soft-switching converters are not used for energy transfer but only during switching intervals to provide either zero current (ZCS) or zero voltage (ZVS) switching. During the rest of the switching period, the converter behaves like the PWM converter. Resonant frequency is well above the switching frequency, and the resonant voltage is "clamped" by a rectifier or second switch after the transition is completed. The waveforms between transitions look very much like those in PWM converters. In this thesis soft-switching converters are classified as the converters which use a switching technique that combines PWM control at constant switching frequency, and resonant behavior only during the switching transitions.

Different soft-switching mechanisms have been proposed in the past several years [24, 25, 26, 27, 33, 34, 36]. These solutions have some common disadvantages such as increased current stresses on the switches, increased losses in the magnetics, limited range of soft-switching, and complex control circuitry. In order to achieve zero-voltage switching for all operating conditions, these topologies use an additional active or passive components.

The field of magnetic amplifier regulators is another area in power electronics which has received much attention during the past few years. This becomes more obvious when the operating frequency of the converters increases and switching losses in semiconductor devices start becoming the limiting factor. Due to its non-linear characteristic and very simple control, a magnetic amplifier, or magamp for short, can be used very efficiently as a controllable switch in a large variety of applications.

With the development of new amorphous materials with square-loop characteristics [29, 30, 31] which improve efficiency at higher switching frequency, it seems that magamps are going to play an important role in design of switched-mode power converters. It is gratifying to see that as the operating frequencies of modern power converters increase, the magamp is *not* a critical component. Their capability to work nicely at 1MHz and above has already been proven [6]. The magamp regulators are a dominant force in multiple-output converters [5, 11].

In the thesis magamps are studied as controllable voltage-bidirectional switches which provide two essential functions for any switched-mode regulator: a) soft-switching and b) the output voltage regulation. A novel soft-switching mechanism with magamps [32] is described and applied to all three symmetrical topologies, half-bridge, full-bridge and

push-pull converters.

Chapter 2 gives an overview of saturable inductors and magamps. Different reset methods of the magamp are discussed and the most common application of magamps as post-regulators in the multiple-output converters are reviewed. The limitations of the magamp as a controllable voltage-bidirectional switch are also discussed.

A survey of the soft-switching converters is given in Chapter 3. After the switching loss mechanisms in PWM converters are explained, the existing different solutions to switching loss elimination are briefly reviewed. The basic soft-switching mechanism is explained in the buck converter [25]. Widely used zero-voltage switching phase-shifted full-bridge converter [33, 36] is also discussed.

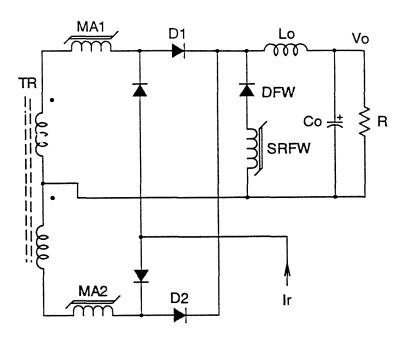

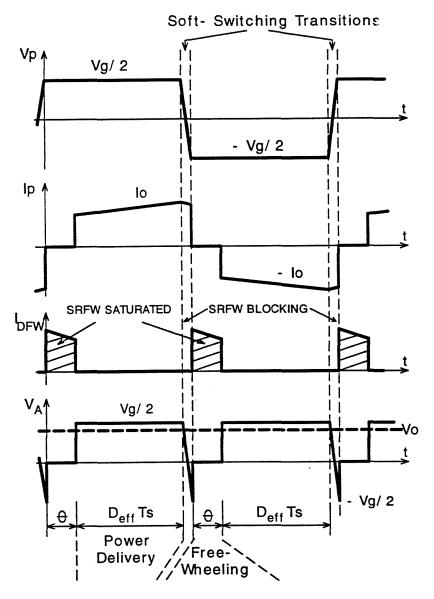

In Chapter 4, a novel soft-switching half-bridge converter with magamps is described. The proposed soft-switching mechanism uses reflected load current for zero-voltage switching of the primary side switches while the soft turn-off of the rectifier diodes is provided by the non-linear characteristic of magamps. Experimental results obtained on the prototype are presented to confirm these features.

The proposed soft-switching mechanism is then extended to the full-bridge and push-pull topologies in Chapter 5. The novel soft-switching full-bridge converter is compared with zero-voltage switching phase-shifted full-bridge converter, and experimental results are presented.

Multiple-output extension of the novel soft-switching converters with magamps is given in Chapter 6. It is shown that these converters do not have adverse effects inherent to their parent PWM converters with magamp post-regulators. The novel soft-switching converters are well suited for independent regulation of the multiple outputs.

Chapter 7 summarizes the advantages of the proposed soft-switching converters.

#### Chapter 2

# Review of Saturable Inductors and Magnetic Amplifiers

Saturable inductors and magamps play an important role in the design of modern switched mode power supplies. This becomes more obvious when the operating frequency of the converters increases, and switching loss in semiconductor devices start to become the limiting factor. Due to its non-linear characteristic and very simple control, the magamp can be used very efficiently as a controllable switch with a wide range of applications.

This chapter gives an overview of saturable inductors and magamps, beginning with a piecewise-linear model for magnetics in Section 2.1. Section 2.2 describes the principle of operation of saturable inductor, while the controllable saturable inductor or magamp is outlined in Section 2.3. In Section 2.4, the multiple output converter which uses magamps for tight regulation of the auxiliary outputs is reviewed. The chapter concludes with a discussion of magamp limitations in Section 2.5.

#### 2.1 A Piecewise-Linear Model for Magnetics

In this section the "integration procedure" (actually a scale factor change) is applied to a collection of magnetic properties that are defined analytically in order to obtain a piecewise-linear model useful for the designer [1].

There are four physical properties of magnetic material which are identifiable components of a magnetization curve, and each of them is modelled in the simplest way. These four components – high permeability, saturation, hysteresis, and dynamic loss – are then collected into a *piecewise-linear model*. The model has two forms, magnetic and electric, which differ in whether the integration procedure has been applied.

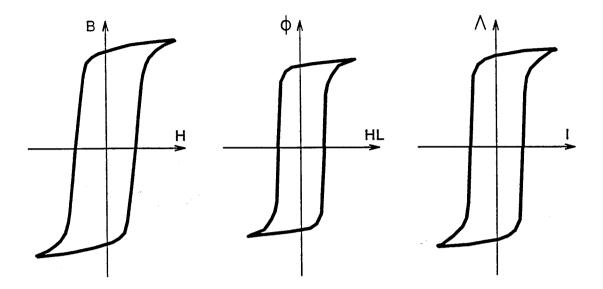

Figure 2.1: An illustration of design mechanics: from material to device properties. Bulk property of material is translated into device property by scaling both axes with geometrical parameters of the particular core.

#### 2.1.1 Relating Material Properties to Device Characteristics

Our goal is to quantitatively translate magnetic material properties of core material (B-H characteristic) to the more useful design volt-ampere characteristic of the device. An illustration of design mechanics is shown in Fig. 2.1. The original curve (B-H) which describes the property of the core material is shown in Fig. 2.1 (a). The slope of the curve,  $\mu$ , is the permeability of the magnetic material, and  $B_s$  is saturation flux density.

In this procedure homogeneous flux distribution and flux path are assumed. By scaling-up (multiplying) the ordinate axis with core cross-sectional area S, and the abscissa with the total magnetic path length l, the new curve with changed scales, F versus  $\Phi$ , is obtained in Fig. 2.1 (b). It describes the property of the magnetic circuit (core) combining the extrinsic design choice of the specific core geometry with the choice of intrinsic material properties specified by the B-H curve. The slope of the  $\Phi-F$  curve has the dimensions of permeance  $P=\mu S/l$ .

The final design step is the specification of the number of turns of wire, N to be

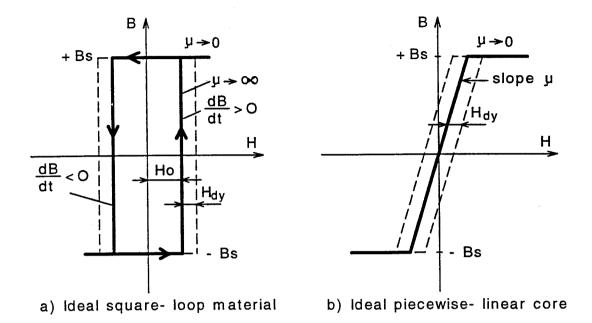

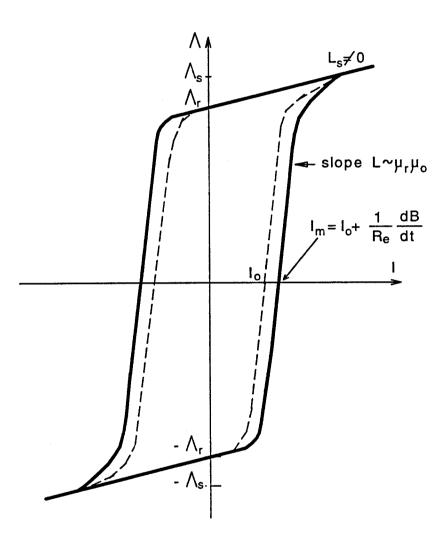

Figure 2.2: A piecewice-linear model for magnetic material combines four essential features of magnetic material: slope  $\mu$ , saturation flux density  $B_s$ , static hysteresis width  $H_o$ , and dynamic hysteresis  $H_{dy}$ .

wound upon the core. By multiplying the ordinate axis and dividing the abscissa axis with N, the final result in Fig. 2.1 (c) is represented in purely electrical units. The slope of the curve in Fig. 2.1 (c) has the dimension of inductance  $L = \int v dt/I = N^2 P$ .

It should be emphasized that all three graphs in Fig. 2.1 have the same shape, but with a different scale.

#### 2.1.2 The Magnetic Model

The first essential feature of magnetic material, high permeability  $\mu$ , is the ability of magnetic material to produce a larger effect ( $B_i$ , hence larger flux) with smaller means (H, hence smaller current). It is translated into the slope of the magnetizing curve in which B is proportional to H as shown in Fig. 2.2 (b).

The second component of the model is the saturation value  $B_s$  which models saturation of intrinsic flux density  $B_i$ . The physical meaning of saturation is that all the elementary magnetic moments that constitute the intrinsic induction of the material are

completely aligned so that any further increase of H does not contribute to change in flux density. The region between saturation levels,  $+B_s$  and  $-B_s$ , is called the *linear region*. Magnetic circuits, such as transformers and linear inductors, are usually designed to operate in linear region of B-H curve and are prevented from running into saturation. On the other hand, saturable inductors are normally designed to have flux density moving between the linear region and saturation.

The B-H curve of magnetic materials possesses a hysteresis property which is manifested as a double-valued curve in the H-direction. The parameter of interest is the "static width" of the hysteresis loop, which is modelled in Fig 2.2 (a) as a square-loop parameter  $H_o$ . The total width of a square-loop material is  $2H_o$ , which in the ideal case is constant and independent of B for any  $|B| < B_s$ .

The fourth component of the piecewise-linear model represents dynamic loss. The area inside a B-H curve is dimensionally equivalent to core loss purely due to hysteresis and associated width  $H_o$ . The excess loss in the core due to eddy current are modelled by the dynamic component of hysteresis loop width  $H_{dy} = g_e dB/dt$  shown by dashed lines in Fig. 2.2.

In the linear region, the magnetic model can be expressed by the following equation in H [1]:

$$H = H_o(sgn\frac{dB}{dt}) + \frac{1}{\mu}B + g_e\frac{dB}{dt}, \ \ for \ |B| < B_s.$$

(2.1)

The first term in Eq. (2.1) describes hysteresis. The second and third terms are the slope and the dynamic width components of H, respectively.

#### 2.1.3 The Electrical Model

With the magnetic model given by Eq. (2.1) the electrical model is obtained by using design mechanics described in Section 2.1.1. The final result is equation in inductor current I [1]:

$$I = I_o(sgnv) + \frac{1}{L} \int v dt + G_e v, \quad for \ |\Phi| < \Phi_S. \tag{2.2}$$

The corresponding piecewise-linear electrical model for a core with N turns is shown in Fig. 2.3. The four circuit elements – inductance L, ideal switch S, reversible current source  $I_o$ , and conductance  $G_e$  – are related to the four intrinsic material properties –

slope  $\mu$ , saturation  $B_S$ , static width  $H_o$ , and dynamic width  $H_{dy}$ . The ideal switch S is a "saturation switch" which is flux controlled. It is open for normal functioning of the other elements, i.e., when  $|\Phi| < \Phi_S$  and closed when core is in saturation, i.e., when  $|\Phi| > \Phi_S$ .

Once the saturation of the core occurs, the switch S is closed and consequently shorts all elements, causing v=0 regardless of the current level. By recalling that v=0 is equivalent to  $\frac{d\Phi}{dt}=0$ , it means that zero voltage is a condition of constant flux in saturation.

The constant current source  $I_o$  represents magnetizing current of the core and is a measure of the static width of a hysteresis loop. The associated ideal diode network, simulating sgnv, provides that the current direction is controlled by the polarity of the input voltage. The reversal network provides a short-circuit across the input terminal if  $|I| < I_o$ . When the input current exceeds  $I_o$ , two diagonal diodes conduct and allow existence of the input voltage which causes excess circuit  $(I - I_o)$  through the inductance L and/or conductance  $G_e$ .

#### 2.2 Principle of Operation of Saturable Inductor

It follows from Faraday's law that total or linkage flux,  $\Lambda = N\Phi$ , is the volt-seconds integral of the voltage across the inductor, i.e.,

$$\Lambda = \int v dt. \tag{2.3}$$

From Eq. (2.3) follows a very important fact that the state of the core is determined by the volt-seconds integral. Consequently we can say that the inductor is "volt-second integral" since it converts voltage applied during a certain interval of time into change of total flux in the core. This fact is used in understanding how a saturable inductor operates and how it can be used as a switch, which is described next.

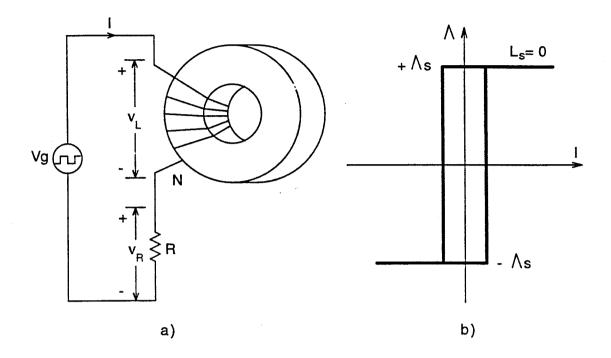

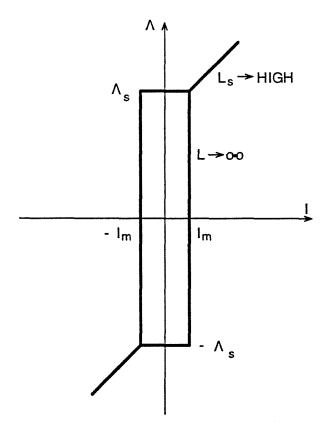

Consider the inductor L in the electrical circuit of Fig. 2.4 (a) with ideal square-loop  $\Lambda - I$  characteristic shown in Fig. 2.4 (b). The inductor is designed to saturate in both positive and negative half-cycle of source voltage.

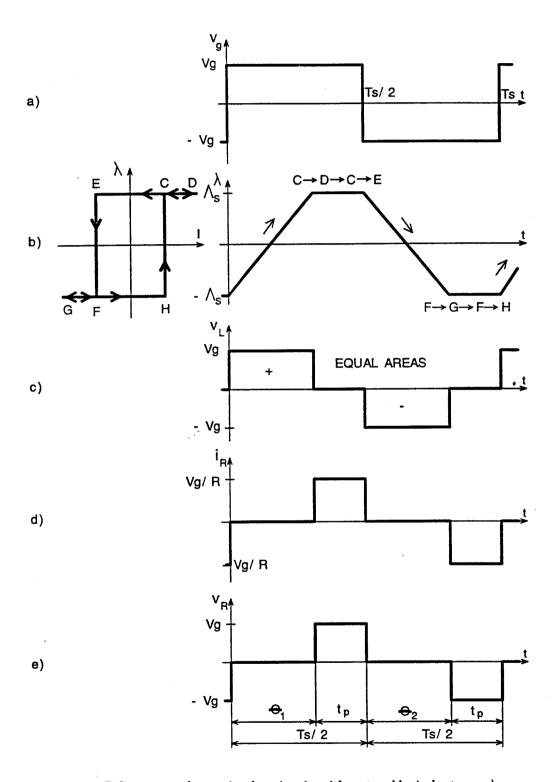

Salient waveforms are shown in Fig. 2.5. At t = 0, the source voltage switches from  $-V_g$  to  $+V_g$ . Since before t = 0, the inductor was in saturation (point G in Fig. 2.5 (b)),

Figure 2.3: Piecewise-linear electrical model of the core of the inductor.

Figure 2.4: Principle of operation of the saturable inductor is explained in the simple circuit using the inductor L with ideal square-loop  $\Lambda-I$  characteristic resistor R.

$v_L=0$  and input voltage  $-V_g$  was applied across resistance R. Inductor current  $I_L$  was negative and limited only by resistance R. Due to the applied positive voltage  $V_g$ , current  $I_L$  drops to zero and reverses direction. The flux in the the inductor moves from point G to point H almost instantaneously (Fig. 2.4 (b)). The inductor runs out of saturation at small current  $i=I_o$  (point H) and blocks source voltage  $V_g$ . The flux linearly increases from  $-\Lambda_s$  until it reaches  $+\Lambda_s$  after time interval  $\theta_1$  (point C) and remains constant until source voltage again switches at  $T_s/2$ . As the core saturates after time  $\theta_1$ , the inductor represents short-circuit ( $v_L=0$ ) and source voltage  $V_g$  appears across the load resistance R (Fig. 2.5 (e)).

The process repeats during negative half-cycle of source voltage when the flux in the core moves from  $+\Lambda_s$  to  $-\Lambda_s$  following path  $D \to C \to E \to F \to G$  on the  $\Lambda - I$  characteristic in Fig. 2.5 (b)). At  $t = T_s/2$ , the source voltage changes polarity from  $+V_g$

Figure 2.5: Salient waveforms in the circuit with saturable inductor: a) source voltage  $v_g$ , b) flux  $\lambda$ , c) inductor voltage  $v_L$ , d) resistor current  $i_R$ , and e) resistor voltage  $v_R$ .

to  $-V_g$  causing the inductor to run out of saturation when  $I_L = -I_o$  (point E). The inductor supports negative voltage  $-V_g$  during the blocking time interval  $\theta_2$  (Fig. 2.5 (c)). At  $t = \theta_2 + T_s/2$  (point F), the inductor runs into negative saturation,  $v_L = 0$ , and consequently source voltage  $-V_g$  appears across load resistance R.

The durations of the blocked parts of incoming positive  $(+V_g)$  and negative  $(-V_g)$  pulses of source voltage,  $\theta_1$  and  $\theta_2$ , respectively, are the same and denoted as  $\theta$ . The blocking interval,  $\theta$ , is the time delay between the voltage pulse applied to the load and source voltage waveform. It is given by

$$\theta = \frac{\Delta\Lambda}{V_a} = \frac{2\Lambda_s}{V_a}.\tag{2.4}$$

The duration of the voltage pulse on the resistance R is given by (Fig. 2.5 (c))

$$t_p = D_{eff}T_s = \frac{T_s}{2} - \theta, \tag{2.5}$$

where,  $D_{eff}$  is effective duty ratio defined as

$$D_{eff} = \frac{t_p}{T_s}. (2.6)$$

The average voltage on the resistor,  $\langle v_R \rangle$ , is given by

$$\langle v_R \rangle = D_{eff} V_g = (1 - \frac{2\theta}{T_s}) V_g.$$

(2.7)

The blocking capability of the saturable inductor,  $2\Lambda_s$ , is the maximum volt-seconds product that the core can withstand. It depends on the number of turns N, core cross-sectional area S and saturation flux density  $B_s$ . The blocking interval given by Eq. (2.4), is the maximum blocking interval for given source voltage and inductor and cannot be continuously controlled in the circuit from Fig. 2.4 (a).

#### 2.3 Magamp

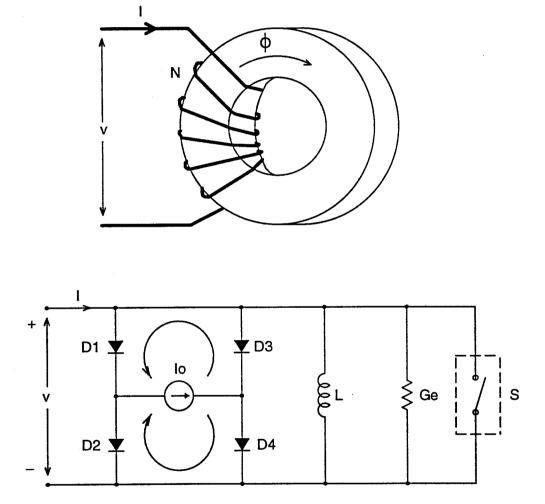

A magamp, also called a transductor, is a controlled magnetic impedance located in series with a unidirectional current switch and load, and connected to an alternating supply voltage. It utilizes the saturable inductor described in Section 2.2 with a controllable blocking time to control the output voltage. Thus, a magamp establishes an OFF-ON type of load control. It is also known as the reactor-rectifier [2].

The increased demand for more compact and reliable switched-mode power supplies has aroused a renewed interest in a well-founded control technique – the magamp. In multiple-output power supplies magamps are adopted as post-regulators required for independent regulation of the output voltages including features such as overcurrent and short circuit protection. In recent years, magamps have received growing interest, and a large number of papers both from the industry and universities have been published [3]-[9].

#### 2.3.1 A Magamp Control

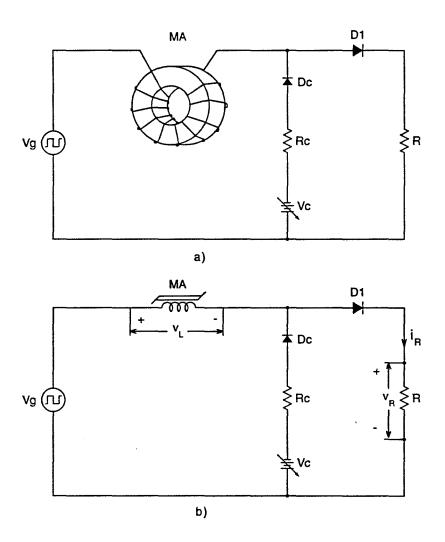

The basic circuit of a magamp is shown in Fig. 2.6 (a). Two main differences between this circuit and the circuit in Fig. 2.4 (a) are:

- a) Diode D1 is added in series with saturable inductor

- b) Voltage source  $V_c$  is used to control the magamp. Resistance  $R_c$  represents control source series resistance, while diode  $D_c$  blocks the positive voltage appearing across the control voltage source  $V_c$ .

Diode D1 is forward biased during the positive half-cycle of source voltage, usually called forward or gate cycle, and reverse biased during negative half-cycle of source voltage, also called reset cycle. During the forward cycle, part of the positive source voltage pulse is blocked for a time determined by the volt-seconds stored in the inductor during the preceeding reset cycle. During the reset cycle the negative voltage applied across the inductor is determined by the control voltage  $V_c$  which opposes the negative source voltage  $V_g$ .

The number of turns N, is chosen so that  $2\Lambda_s$  just exceeds the source voltage maximum half-cycle area  $V_gT_s/2$ . This gives the core the capability of absorbing  $V_g$  over an entire half-cycle, for instance, during overload or short circuit conditions.

Salient waveforms for dc or steady-state operation during a switching period are shown together with the square-loop  $\Lambda - I$  characteristic of the saturable inductor in Fig. 2.7.

There are two methods to control or reset magamp: a) voltage reset, and b) current reset. The basic principle is the same and is based on equality of volt-seconds stored,

during reset, and volt-seconds blocked, during forward cycle. In the voltage reset method  $(R_c = 0)$ , constant reset voltage is applied across the inductor during the reset cycle. On the other hand, in the current reset method  $(R_c \neq 0)$  a constant current is applied to drive the flux away from  $+B_s$ . This method is also known as magneto-motive force control (mmf control).

#### 2.3.2 Voltage Reset Method

During the reset cycle, voltage  $-(V_g - V_c)$  is applied across the inductor (dashed area in Fig. 2.7 (c)) causing flux in the core to move from  $+\Lambda_s$  down to  $-\Lambda_c$  following path  $D \to C \to E \to A$  in the  $\Lambda - I$  characteristic (Fig. 2.7 (b)). Therefore, the control voltage  $V_c$  controls the negative volt-seconds stored during the reset of the core  $(\Delta\Lambda = \Lambda_s - \Lambda_c)$ , and sets up equal positive volt-seconds blocking  $(V_g\theta_c)$  for the following forward cycle. As shown in Fig. 2.7 (b), flux transverses close path  $A \to B \to C \to D \to C \to E \to A$  during one switching period  $T_s$  and core only saturates in the positive direction in contrast to path  $G \to F \to H \to C \to D \to C \to E \to F \to G \to$  in Fig. 2.5 (b).

The flux swing,  $\Delta\Lambda$ , is calculated from volt-second balance on inductor as:

$$\Delta\Lambda = (V_g - V_c)\frac{T_s}{2} = V_g\theta_c. \tag{2.8}$$

The blocking time,  $\theta_c$ , where subscript c denotes blocking time due to the control voltage, can be expressed from Eq.(2.8) as:

$$\theta_c = \left(1 - \frac{V_c}{V_g}\right) \frac{T_s}{2}.\tag{2.9}$$

The duration of the voltage pulse passed to the load,  $t_p$ , is calculated from Fig. 2.7 (b) as

$$t_p = D_{eff} T_s = \frac{V_c}{V_a} \frac{T_s}{2}.$$

(2.10)

The average output voltage,  $\langle v_R \rangle$ , is given by

$$\langle v_R \rangle = D_{eff} V_g = \frac{V_c}{2}.$$

(2.11)

Equation (2.11) suggests perfect line rejection with voltage reset, i.e., that the load or output voltage of the magamp  $v_R$ , is independent of the source voltage  $V_g$ . However

Figure 2.6: The basic circuit of the magamp.

Figure 2.7: Salient waveforms in the circuit with magamp: a) source voltage  $v_g$ , b) flux  $\lambda$ , c) inductor voltage  $v_L$ , d) resistor current  $i_R$ , and e) resistor voltage  $v_R$ .

this is an oversimplification because in Eq. (2.8) the delay between source voltages  $V_g$  on the left and right side of the equation is neglected. The correct result including the time delays was derived in [8] and found to be a function of frequency as follows:

$$\langle v_R \rangle \simeq \pi D_{eff} \frac{f}{f_s} V_g,$$

(2.12)

where, f is the modulating frequency of the control voltage and  $f_s$  is switching frequency.

It can be seen from Eq. (2.9) that when  $V_c = 0$  (no control) the blocking time is equal to  $T_s/2$ , which means it is possible to block source voltage  $V_g$  over an entire half-cycle. This feature allows overload and short circuit protection.

#### 2.3.3 Current Reset Method

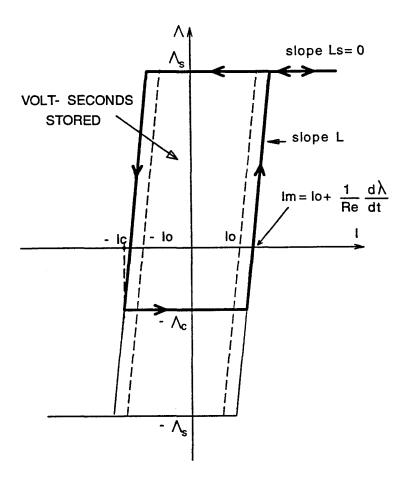

In the current reset method, a constant current is used to control flux reset in the core. Control or reset current  $I_c$  determines magnetic field H (through core geometry and number of turns) which through the permeability  $\mu$  determines flux density B and finally, through cross-sectional area and number of turns, total flux  $\Lambda_c$ . In other words, unsaturated inductance of the magamp, L, converts reset current into the linkage flux, i.e., volt-seconds stored during the reset period.

Total magnetizing current of the inductor is equal to the control current  $I_c$  and consists of three components:

$$I_c = I_o + \frac{1}{R_e} \frac{d\Lambda}{dt} + \frac{\Lambda}{L}.$$

(2.13)

Only the last component in Eq.( 2.13),  $\Lambda/L$  contributes to the dc component of flux reset  $\Lambda_c$ .

A serious disadvantage of the current reset is that the volt-seconds stored, and therefore, the blocking capability are both dependent on the unsaturated inductance of the magamp. It may have wide variations from sample to sample, over temperature, or at different points on the B-H loop. In contrast, the voltage reset does not have that problem because the gain of the reset stage is unity, independent of core characteristics. In addition, the voltage reset provides inherently feed-forward line rejection thus, allowing simple design of the regulator's loop [10].

Figure 2.8: In the current reset method, control current,  $I_c$ , drives core out of saturation and determines value of the reset flux  $\Lambda_c$ .

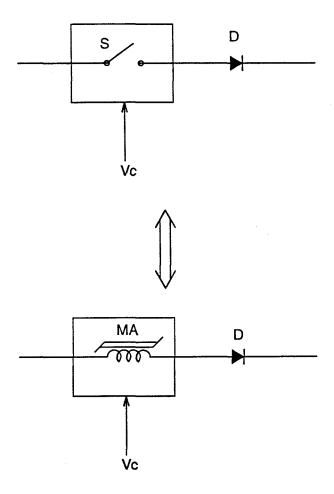

In summary, a magamp can be used as a controllable voltage bi-directional switch consisting of saturation switch S in series with diode D as shown in Fig. 2.9 (d). Controlled variable is volt-seconds stored or flux reset. Saturation switch S is closed when inductor is saturated and open otherwise.

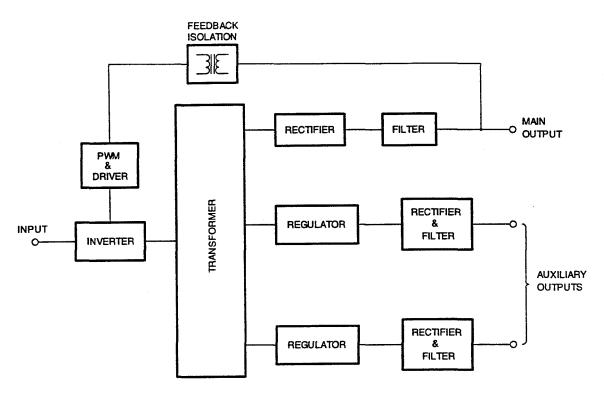

#### 2.4 Magamp as a Post-Regulator

A block diagram of typical multiple-output switched-mode power supply is shown in Fig. 2.10. Since all outputs share the same inverter stage, only one output, called the main output, is fully regulated against load and line voltage variations by pulsewidth

Figure 2.9: Magamp can be used as a voltage bi-directional switch consisting of saturation switch S and diode D.

modulation of the switches in the inverter stage. Additional post-regulators are required for independent regulation of auxiliary outputs against load variations.

The magamp is very attractive as a post-regulator due to its benefits, when compared to other post-regulator techinques [11], such as: lower parts count, more rugged, more efficient, considerable smaller EMI, and lower stress on the main inverter power switches. The recent development of low-cost, high frequency, square-loop amorphous materials has made the magamp regulator a preferred solution to many multiple output applications for operating frequencies over 100kHz [11, 12].

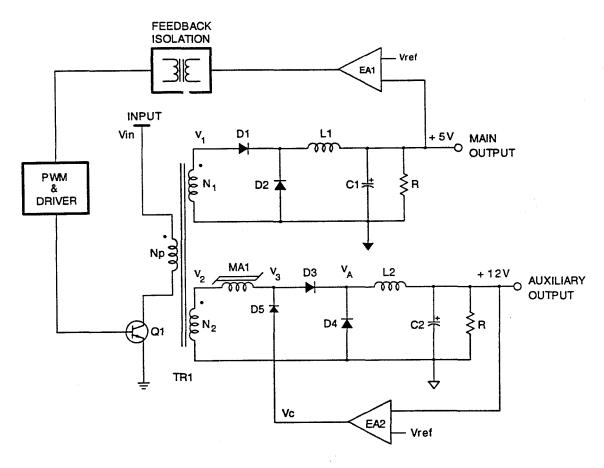

A forward converter using a magamp is shown, as an example, in Fig. 2.11, while the

Figure 2.10: Block diagram of a multiple-output switched-mode power supply. Only one output can be regulated by PWM of the inverter stage while the auxiliary outputs require additional post-regulators.

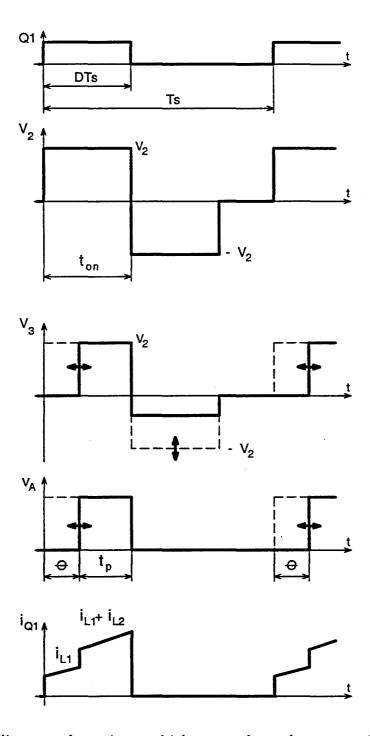

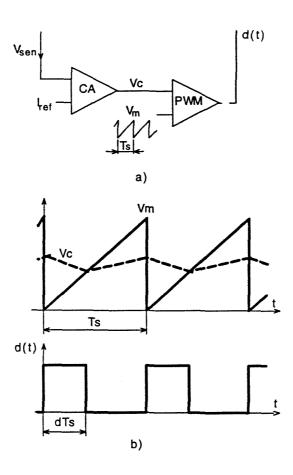

salient waveforms are shown in Fig. 2.12. The technique can also be used in the flyback converter and the symmetrical topologies with full-wave rectification such as push-pull, half-bridge and full-bridge converters. The main switch on the primary side is controlled by a pulsewidth modulator (PWM). Voltage on the main output, usually 5V, is compared with a reference and an amplified error signal is feed into the modulator to adjust the conduction interval  $(t_{on})$  of the main switch. In this way the volt-seconds product, which appears at all secondaries, is adjusted only against input voltage, while the 5V output is in addition, regulated against load variations.

Without magamp MA1, the auxiliary output is "semi-regulated", since the primary control loop provides only regulation against line voltage variation. Thus, an additional post-regulator, realized with a magamp, is used to tightly regulate the auxiliary output.

In order to regulate the auxiliary output voltage at 12V, the average value of the

Figure 2.11: Schematic of a multiple-output forward converter using magamp as post-regulator.

rectified waveform applied to the output filter  $L_2C_2$  ( $V_A$  in Fig. 2.11) must be constant and equal 12V. It means that the volt-seconds product at point A, must be regulated.

Since the magnitude of the secondary voltage  $v_2$  is determined by the input voltage  $(V_{in})$  and the transformer's turns ratio  $(N_2/N_p)$ , only the pulse width of the voltage  $v_A$ ,  $t_p$ , can be controlled. This is provided with magamp which delays the leading edge of the positive pulse by the appropriate time  $\theta$  as shown in Fig. 2.12. The blocking interval  $\theta$  is controlled by the error amplifier EA2 which compares the output voltage to a reference and accordingly adjusts the reseting of the core during the OFF interval of the main switch Q1.

The primary current increases when the core of magamp saturates and begins to

Figure 2.12: Salient waveforms in a multiple output forward converter describing principle of operation of the magamp as a regulator.

deliver current to the auxiliary output. This has an incidental bonus: the primary switching transistor has already turned on and hence, the auxiliary output does not contribute to turn on loss in the transistor.

#### 2.5 Limitations of the Magamp as a Switch

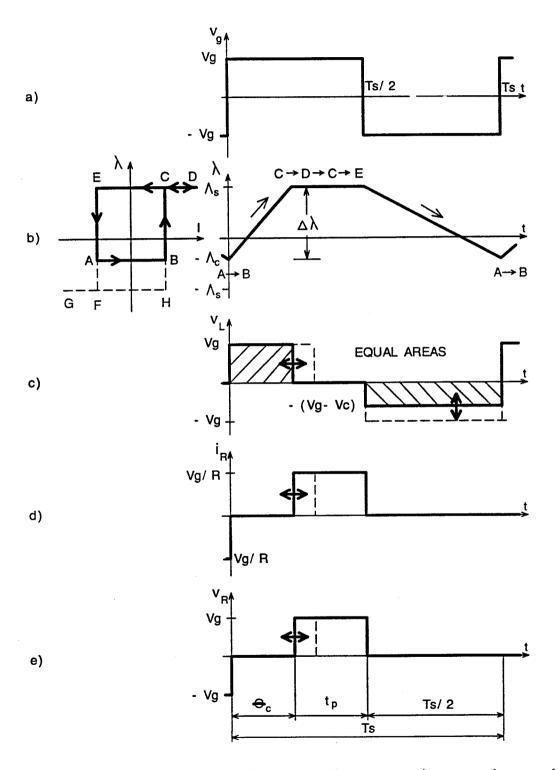

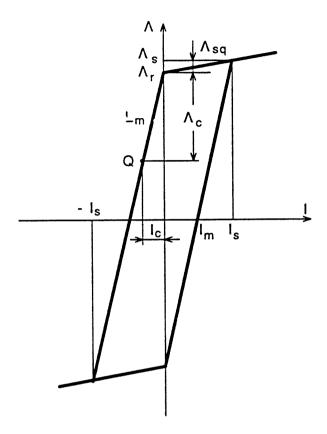

Limitations of the magamp owe to the non-ideal characteristics of the magnetic material. More realistic B-H characteristic for the square-loop magnetic material, widely used for saturable inductors, is translated to the volt-seconds-magnetizing or the  $\Lambda-I$  characteristic in Fig. 2.13. There are five essential non-idealities of the magnetic material which cause three different kind of undesirable effects. They are explained next.

#### FINITE MAGAMP CURRENT IN BLOCKING STATE

The first effect is due to finite unsaturated permeability  $\mu$  which produces finite unsaturated inductance L. The saturable inductor, therefore, does not represent open circuit when it is operated out of saturation because of the non-zero inductor current. In other words, there is a leakage current inversely proportional to the unsaturated inductance L when the switch (saturable inductor) is turned-OFF. Another consequence of the finite slope is increased control current and consequently increased loss in the control circuit. Cores with steeper slopes require lower number of turns and therefore have lower conduction loss.

#### Core Losses

The existence of the hysteresis loop produces core loss. The hysteresis consists of static width, and two dynamic width components due to eddy currents and the re-entry characteristic of the core [7]. Re-entry current occurs as a consequence of increased hysteresis width due to high load current driving the core material far into saturation. It has been shown in [7] that the width of the B-H loop for H>0 is independent of the load current  $B>B_s$  whereas on the left side H<0 (during reset) the width increases with increasing load current. This re-entry current is more noticeable in amorphous materials. In the  $\Lambda-I$  characteristic of Fig. 2.13 the dynamic width due to the re-entrant characteristic is omitted and only components due to static width and eddy currents are shown. The later is the difference between the zero-flux magnetizing current  $I_m$  and the

Figure 2.13: More realistic the  $\Lambda-I$  characteristic of saturable inductor including essential non-linearities of core material.

static value  $I_o$ , and increases in proportion to the winding voltage  $v_L = d\Lambda/dt$ , or

$$I_e = I_m - Io = \frac{1}{R_e} \frac{d\lambda}{dt} \tag{2.14}$$

where,  $R_e = 1/G_e$  is core resistance which describes eddy current loss.

#### MINIMUM BLOCKING CAPABILITY

Core squareness, defined as ratio between residual (zero-excitation) and saturation flux density  $B_r/B_s$  causes a delay as the magamp switches into saturation. This delay (ideally zero) decreases the maximum available volt-seconds which can be applied to the output filter. As a consequence, the minimum input voltage required to maintain output regulation, is increased. This overhead is in addition to the diode voltage drop and voltage drop on the resistances normally included in the design.

Core squareness causes automatic reset of the core with  $\Delta\Lambda = \Lambda_s - \Lambda_r$  when the secondary voltage switches from  $+V_2$  to  $-V_2$ , even though no reset voltage was applied  $(V_c = 0 \text{ in Fig. 2.11.}$  The reason for this is that the current in the saturable inductor,  $I_2$ , quickly falls down to zero when the negative voltage  $-V_2$  is applied. At the same time, freewheeling diode D4 starts to conduct the difference between  $I_2$  and  $I_{L_2}$  and shorts point A to the ground. When the current in the saturable inductor reaches zero, which corresponds to flux  $\Lambda_r$ , forward diode D3 turns-off and the entire negative voltage  $-V_2$  appears across it. Consequently, the voltage on the saturable inductor is zero  $(V_c=0)$  and the flux in the core remains at  $\Lambda_r$  during the entire reset cycle. This  $\Delta\Lambda$  must be traversed during the forward blocking period and corresponds to the minimum volt-seconds blocking of

$$V_g \theta_{sq} = \Lambda_s - \Lambda_r \tag{2.15}$$

which must be accounted for in the average applied voltage.

Saturated inductance also delays the positive voltage pulse at the output filter  $L_2C_2$  (point A in Fig. 2.11), and therefore, reduces the effective duty ratio of the regulator. As the core enters saturation, the current in the saturable inductor  $I_2$  starts to increase from zero toward the output inductor current  $I_{L_2}$ . Voltage  $V_A = 0$  until  $I_2$  reaches  $I_{L_2}$  at which time the freewheeling diode D4 turns-off and the secondary voltage appears at

the output filter. This additional blocking is given by:

$$V_g \theta_{si} = L_s I_{L_2} \tag{2.16}$$

where,  $L_s$  is the saturated inductance given by

$$L_s = \frac{\mu_s S N^2}{l}. (2.17)$$

The saturated permeability,  $\mu_s$ , is not a specified data sheet parameter and is usually determined experimentally by measuring  $L_s$  in the circuit and then calculating it from Eq. (2.17). In [9],  $\mu_s$  is measured for different sizes of square permalloy 80 material and was found in range from  $10\mu_o$  to  $36\mu_o$ . It was suggested to increase these values by 30% to account for the added delay during transition at the B-H loop knee.

In summary, a magamp can be used in a very efficient way as a controllable voltage bidirectional switch. By knowing its limitations, it will be possible to analyze how it affects the operation of the magamp as a controllable switch in any particular circuit. Being a time dependent device, it combines switching and modulator functions into a single power device which can be very easily controlled using analog circuitry in contrast to other semiconductor devices.

# Chapter 3

# A Survey of Soft-Switching Converters

The purpose of this chapter is to review the main problems associated with switching losses and the different solutions proposed for their elimination. In Section 3.1, switching loss mechanisms due to reverse-recovery time of the power diodes and parasitic reactances are described. Different approaches to switching loss elimination are given in Section 3.2, while in Section 3.3 two different soft-switching mechanisms, widely used in practice, are briefly described.

## 3.1 Switching Loss Mechanisms in PWM Converters

The semiconductor device in a switching converter is subjected to simultaneous high voltage and high current during switching instants, turn- on and turn-off, which results in high switching stress. With increased demand for faster response and reduced size and weight, switching frequency is increasing toward the megahertz region where switching losses in conventional PWM converters become intolerably high.

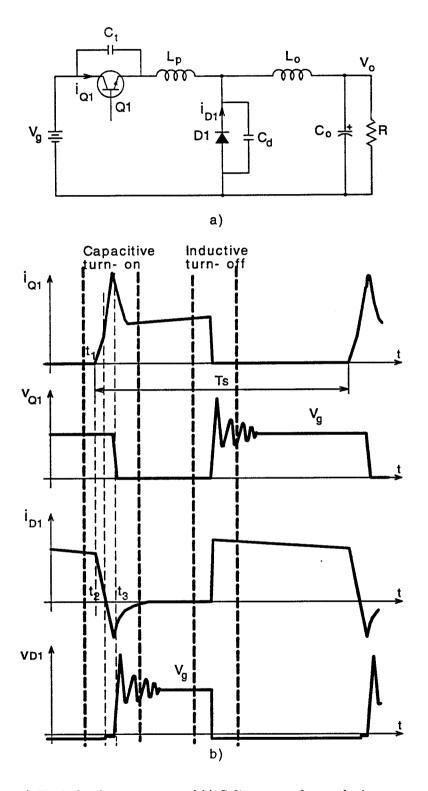

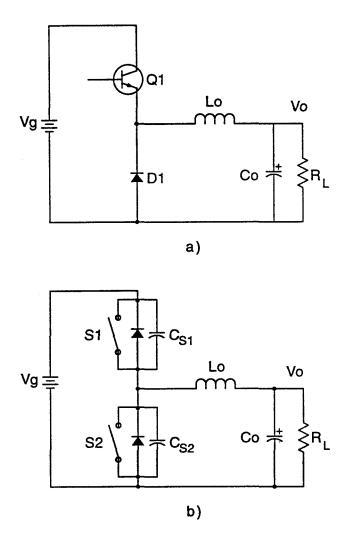

The buck converter is shown in Fig. 3.1 (a) and typical waveforms for a continuous conduction mode of operation (CCM) are shown, as an example, in Fig. 3.1 (b). As in any other PWM converter, semiconductor switching devices exhibit capacitive turnon and inductive turn-off switching. The problems of voltage spikes and discharging parasitic capacitances are both consequences of the discontinuity of the waveforms of PWM converters as shown in Fig. 3.1 (b).

The switching losses depend on different factors and are directly proportional to the switching frequency. It is therefore, necessary to analyze and understand the contribution of each of these factors to the total switching losses and to provide a mechanism for their reduction.

Figure 3.1: a) Basic buck converter and b) Salient waveforms during two switching transitions.

The switching frequency of PWM converters was able to increase along with the speed of available switching devices so long as the loss due to voltage/current overlap was the dominant limit on switching frequency. With very fast transistors, overlap loss is less important than the reverse recovery time of the diode and the problems of voltage spikes and discharging of the parasitic capacitance. These three loss mechanisms are briefly described next.

#### 3.1.1 Switching Losses Due to Diode's Reverse Recovery Time

During the transistor's turn-on transition, shown in Fig. 3.1 (b), the diode D1 is still forward biased causing delay in voltage transition with respect to current transition. Once the diode D1 is turned off, voltage on the transistor Q1 decreases toward zero with a rate determined by the transistor itself.

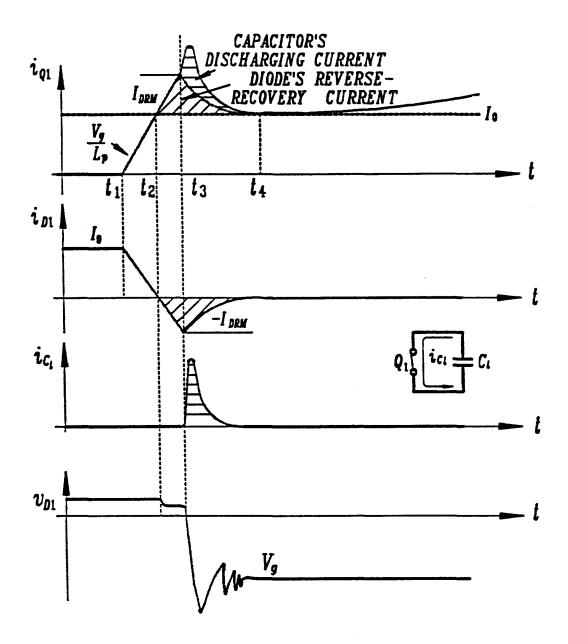

Reverse-recovery current, which exists during the diode's turn-off, becomes a very serious problem at higher power levels and increased switching frequency. Switching waveforms during the transistor's turn-on transition (diode's turn-off) are shown in Fig. 3.2.

At instant  $t = t_1$ , the transistor Q1 is turned-on so the diode's current starts to decrease with slope  $-di_F/dt$  (Fig. 3.2 (b)), limited by the leakage inductance  $L_p$ . The diode's current reaches zero at instant  $t_2$  and continues in the negative direction. During the interval  $t_s = t_3 - t_2$ , called *storage time*, the diode D1 is still forward biased so the losses are low. On the other hand, the negative diode current appears as the transistor's turn-on current in addition to the load current, which as a consequence also increases losses in the transistor.

At the end of the storage time  $(t=t_3)$  the diode's negative current reaches its maximum, the diode becomes reverse biased and the input voltage appears across the diode (Fig 3.2 (d)). During recovery time,  $t_{rec} = t_4 - t_3$ , current through diode decreases exponentially toward zero. Since the diode is subjected to simultaneous high voltage and high current, power loss is relatively high during the recovery time. Switching losses, caused by the diodes reverse-recovery current, can be reduced by using a faster diode, and by limiting both magnitude and slope of the negative diode's current.

Figure 3.2: Switching waveform during the transistor's turn-on transition showing switching loss mechanisms due to reverse recovery of the diode and parasitic capacitance and inductance.

#### 3.1.2 Switching Loss Mechanism Due to Parasitic Capacitance

The presence of the parasitic capacitance causes the power device to operate in capacitive turn-on. The parasitic capacitance which contributes the most to the power dissipation is the device's output junction capacitance. In every switching cycle, charge stored during the turn-off transition in the junction capacitance is dumped into the transistor during the turn-on transition.

Discharging current is only limited by the transistor's switching speed, which results in high di/dt and high current magnitude as shown in Fig. 3.2 (c). Furthermore, turn-on at high voltage levels induces a severe switching noise known as the Miller effect which is coupled into the drive circuit, leading to significant noise and instability. The parasitic capacitance across the switch is, on the other hand, helpful during the turn-off transition because it reduces dv/dt on the switch and consequently reduces voltage/current overlap time.

The junction capacitance is a non-linear function of the applied voltage and can be approximated by

$$C_t \approx C_{to} \sqrt{\frac{V_{off}}{v_t}} \tag{3.1}$$

where,  $C_{to}$  is nominal capacitance,  $V_{off}$  is transistor's off voltage, and  $v_t$  is applied voltage to the transistor. Energy stored in the junction capacitance is given by

$$E_c \approx \int_0^{V_{off}} C_t v_t \, dv_t = \frac{2}{3} C_{to} V_{off}^2 f_s \tag{3.2}$$

while the power lost during the turn-on transition is

$$P_c \approx E_c f_s. \tag{3.3}$$

While not severe at lower switching frequencies, the capacitive turn-on losses become the dominating factor when the switching frequency is raised to the megahertz range. For example, a junction capacitance of 100pF when switched from 300V at 1MHz will induce a turn-on loss of 4.5W.

Therefore, the capacitive turn-on is undesirable because it is dissipative and increases EMI noise.

#### 3.1.3 Switching Loss Mechanism Due to Parasitic Inductance

In general, parasitic inductance can be due to the circuit layout as well as device packaging, the transformer's leakage inductance, and equivalent series inductance (ESL) of capacitors and voltage source. Transistor's turn-on losses can be reduced if the parasitic inductance  $L_p$  is in series with the switches (inductance  $L_p$  in Fig. 3.1 (b)). The inductance  $L_p$  slows down the rate of the rise of the transistor's current, and therefore, reduces turn-on losses caused by the diode's reverse recovery current.

On the other hand, the parasitic inductance produces voltage spikes and oscillation on both switching devices during their turn-off transitions. The abrupt change of the current in the parasitic inductance (the diode's turn-off transition is shown as an example in Figs. 3.2 (b) and (c)), induces voltage spikes with high dv/dt, and magnitude proportional to the rate of the current change (di/dt) and the inductance  $L_p$ . In addition, the parasitic inductance  $L_p$  and the parasitic junction capacitance  $C_t$ , generate high-frequency oscillations and EMI noise. The energy stored in the parasitic inductance  $L_p$  during the conduction interval of the switch is given by

$$E_l = \frac{1}{2} L_p I_p^2 (3.4)$$

where,  $I_p$  is the peak current in the parasitic inductance at the beginning of the turn-off transition. The power dissipated due to the stored energy  $E_l$  is

$$P_l = E_l f_s. (3.5)$$

As can be seen from Eqs. (3.4)-(3.5), power loss due to parasitic inductance becomes very high at higher current levels and high switching frequency. For example, when a current of 4A is switched at 1MHz in a leakage inductance of only  $1\mu H$ , the corresponding power loss will be 8W! Therefore, inductive turn-off is undesirable and should be avoided if the switching frequency is high.

In summary, even though the switching speed of semiconductor devices was drastically increased in the past decade, conventional PWM converters cannot be operated at a high switching frequency without significant degradation in overall efficiency. The main reasons for this are the diode's reverse recovery time and parasitic capacitances and inductances. The problems of voltage spikes and discharging of parasitic capacitance are

both consequences of the discontinuity of the (ideal) waveforms of PWM converters. If the current and voltage are smooth and slowly varying, the parasitic inductance and parasitic capacitance can be charged and discharged gracefully without losses. For the semiconductor devices it is preferable to have inductive turn-on and capacitive turn-off.

# 3.2 Different Approaches to Switching Loss Elimination

Different approaches have been proposed to prevent voltage and current waveforms from being discontinuous, i.e., make the converter insensitive to parasitic components – inductance and capacitance. Some of them are briefly reviewed in the rest of the chapter.

#### 3.2.1 Resonant Converters

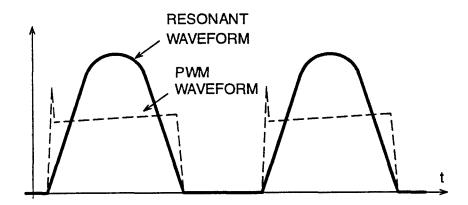

A resonant converter is defined as a power converter in which one or more switching waveforms, either voltage or current, contain pieces of sinusoidal, ringing waveforms [13]. This means that a switching waveform is a continuous, large-ripple voltage or current that starts from and returns to zero (Fig. 3.3). As a result, switching losses caused by voltage/current overlap as well as parasitic reactances can be effectively eliminated thus, allowing the switching frequency to be increased.

Without going into detail on how these waveforms are achieved, it can be stated that, in general, a resonant converter usually contains a resonant circuit in the classical sense: a series or parallel L-C circuit with high Q factor produces quasi-sinusoidal waveforms when driven.

Switching loss due to voltage/current overlap is eliminated by having either the switch voltage or current waveforms continuous. In both cases, one of the switching transitions, the turn-off for zero-current switching (ZCS) or turn-on for zero-voltage switching (ZVS), are uncontrollable and determined by the resonant circuit itself.

Resonant waveforms also eliminate switching losses due to parasitic reactances and overcome problems associated with these parasitics. Having current waveform with sufficiently low di/dt, the voltage spike with magnitude Ldi/dt, generated in parasitic inductance, is no longer dangerous and parasitic oscillations are eliminated. In addition, energy stored in the parasitic inductance can be recovered instead of being dissipated in

Figure 3.3: Typical waveforms in resonant converter.

snubber circuits and switches.

A continuous switch voltage waveform with low dv/dt prevents the loss due to discharging parasitic capacitance through the transistor. The parasitic capacitance is gracefully discharged and its energy is recovered rather then lost. Parasitic reactances can be constructively used in some cases to help in generating the large-ripple resonant waveforms as a part of the resonant circuit. Insensitivity of the resonant converter to parasitic inductance is very helpful in practical design when the transformer must satisfy "creepage" requirement or needs to be wide and flat due to packaging requirements.

Resonant switching waveforms solve the noise problem due to voltage spikes, high frequency parasitic oscillations and "snappy" reverse-recovery of the rectifiers. On the other hand, as a consequence of increased switching frequency, a resonant converter may, in order to meet harmonic limit such as for MIL-STD-461B, require nearly as large a filter as a PWM converter operated at lower frequency.

Resonant converters have some serious drawbacks which limit their wide mass production. These drawbacks are: increased component stresses, large circulating reactive energy, restricted operating region, difficult analysis, variable switching frequency, and complex control.

Resonant waveform in Fig. 3.3 (solid line) has higher peak and r.m.s. values than rectangular waveform of PWM converter (dashed line) for the same average value. Consequently, the resonant converter suffers from higher peak stresses and poorer form factors than its PWM counterpart. The higher stresses imply poorer utilization of the power switches, while the higher r.m.s. current increases the conduction losses in magnetic windings and switch on-resistance. In general, at least one of the switch waveforms, voltage or current, will have higher peak and r.m.s. values than in corresponding PWM converter, and the extra stresses usually propagate to other components in the converter.

In most cases, the variable-frequency control must be used for output voltage/current regulation. The variable-frequency control has several drawbacks: magnetic components have to be designed for full range of the operating frequency, and noise control becomes more complicated. Also there is possibility of entrainment. When the variable-frequency control is used, the noise generated by the converter can move constantly over a wide frequency range so the filter design is made much more difficult. Entrainment is an effect in which the switching frequency of a converter with variable-frequency control locks onto some noise source. Both of these problems are very often dominant arguments for not using resonant converters.

The constant frequency control of resonant converters is possible by using multiple switches [14, 15], electrically variable or saturable magnetic elements [16], and variable capacitances. The latter two methods change the resonant frequency and hence the conversion characteristics of the converter.

The existence of multiple operating modes together with wide variation of the load and switching frequency presents problems for control circuits. A control circuit optimized for a particular mode of operation can be unappropriate or even unacceptable for another mode forced in by change in the load. Therefore, in many cases, converter can be designed for limited range of the load and input voltage variations.

Over several years, the interest in high-frequency power conversion has stimulated the conception of many resonant converter circuits. Plenty of them are available for every application, and each year several more are going to be introduced. Every one of these topologies offers some particular combination of the following features: low-current stresses, low-voltage stresses, additional control, wide range of conversion ratio, low cost, and simplicity. There is no single topology which is superior in all these areas, so the choise of topology is left to the designer.

Quasi-Resonant Converters represent a different approach to resonant power conversion [17]-[19]. They are derived from conventional PWM converters by adding a few components (or utilize equivalent parasitic reactances) to implement resonant switching. These converters share certain features of their PWM parent converters, but they have all the advantages of resonant switching waveforms. Introduction of the resonant switch [17, 18], obtained by adding resonant elements to the ideal switch, has provided derivation of quasi-resonant converters from their PWM parent converters. The new family was given the name "quasi-resonant" to distinguish them from continuously-resonating converters.

The important fact is that all quasi-resonant topologies are insensitive to transformer leakage inductance. In addition, ZCS and ZVS topologies are insensitive to the parasitic capacitance of the main rectifier and transistor, respectively. Quasi-resonant converters provide different kind of zero-switching for the transistor and rectifier. The generalized synthesis procedure of quasi-resonant and multi-resonant converters is given in [20].

The main advantages of quasi-resonant converters are resonant, loss-less switching, low component count and relatively simple analysis and operation. On the other hand, the main drawbacks are very large current stresses and r.m.s. current in ZCS topologies and the voltage stresses in ZVS topologies if the load is allowed to vary widely, variable-frequency control like all single-ended resonant converters. By replacing rectifier diode with controllable switch (MOSFET) [21], the quasi-resonant converter can operate at constant switching frequency.

Quasi-resonant converters, introduced at the beginning, featured different kinds of switching for the transistor and for the main rectifier. Recently, a new class of quasi-resonant converters called *multi-resonant* converters, which features the same kind of switching (ZCS or ZVS) for both the transistor and rectifier, has been introduced. The converter contains, for ZVS case, two resonant capacitances and one resonant inductor

[22, 23]. The resonant frequency varies from one switched network to the next as one capacitor or the other is shorted. A ZVS multi-resonant converter also offers lower voltage stresses and wider load range than a ZVS quasi-resonant converter.

#### 3.2.2 Soft-Switching Converters

Taking into account the pros and cons for both PWM and resonant converter topologies, the "ideal" topology would combine the best features of both families. This includes low switching losses, constant frequency operation, reactive components with moderate stresses and a wide control and load range.

Resonant elements in these converters are not used for energy transfer but they are used only during switching intervals to provide either ZCS or ZVS. During the rest of the switching period the converter behaves like the PWM converter. Resonant frequency is well above the switching frequency, and the resonant voltage is clamped by a rectifier or second switch after transition is completed. The waveforms between transitions look very much those in PWM converters.

There is a large variety of converters which belong to the class of soft-switching converters such as the "pseudo-resonant" full-bridge converter [24], the zero-voltage resonant transition (ZVRT) converters [25], phase-shifted full-bridge converter [33, 34, 36], soft-switching half-bridge converter with asymmetrical drives [26], saturable-reactor assisted soft-switching converters [27] and recently proposed soft-switching converters with magnetic amplifiers [32].

The "pseudo-resonant" full-bridge resonant converter is obtained from the full-bridge PWM converter by adding two "resonant pole" circuits which consist of an LC circuit used for ZVS of each bridge leg [24]. The converter is operated at constant switching frequency and the switch voltage stress is clamped to the input voltage while the current stress of the switches is increased.

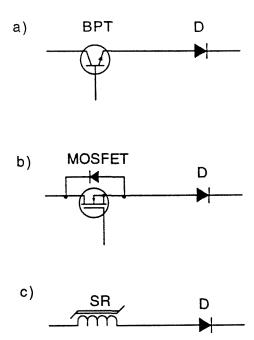

The ZVRT converters differ from some of the ZVS quasi-square-wave converters only in rectifier circuit which employes a synchronous rectifier (realized by MOSFET in practice) as a second, controllable switch [25]. Due to the addition of the second controllable switch, constant-frequency control is allowed and both switches have ZVS.

The soft-switching converters are more promising for high-frequency applications than resonant converters and some of them will be briefly described in the next section.

## 3.3 Different Approaches to Soft-Switching in PWM Converters

#### 3.3.1 Basic Principle of Soft-Switching Mechanism

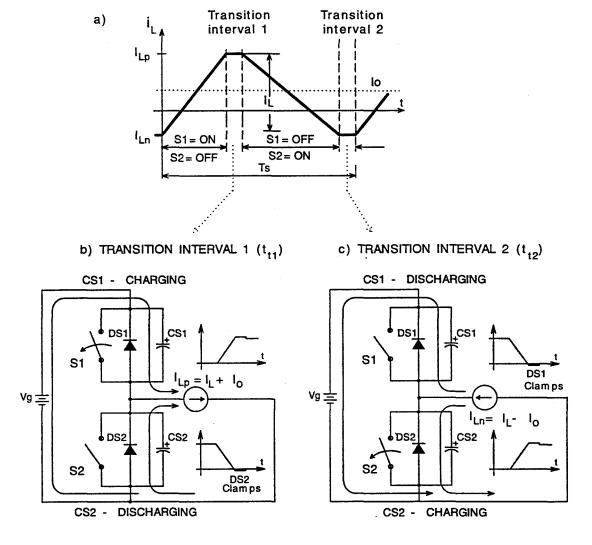

Soft-switching mechanism is explained in the buck converter. In order to obtain zero-voltage switching at constant switching frequency, the active switch Q1 and rectifier diode D1 in the conventional buck converter from Fig. 3.4 (a) are replaced with composite, current bi-directional switches S1 and S2 (realized with MOSFET transistors in practice) as shown in Fig. 3.4 (b). Capacitors across both switches are included in order to model either device parasitic capacitance or the externally added capacitor. Loss-less, soft transition (zero-voltage switching) in switches S1 and S2 occurs during the time intervals when both switches are turned-off, and charge between their capacitors is exchanged in the resonant fashion.

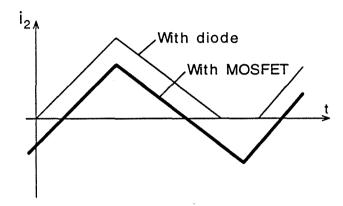

While the soft transition from the top switch S1 to the bottom switch S2 is inherently provided by the positive inductor current, transition from the bottom switch S2 to the top switch S1 requires negative current source to oppose the positive load current flowing through the bottom switch. The simplest solution is to design already existing output inductor L such that its current is bi-directional with peak-to-peak magnitude greater than twice the DC load current, for all operating conditions of interest [25].

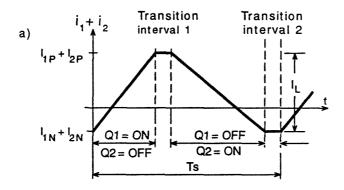

Inductor current waveform during switching period and equivalent circuits of the converter during two different transition intervals are shown in Fig. 3.5. Duration of the transition intervals is assumed to be short compared to the switching period  $T_s$ . The inductor current is constant during these intervals as represented by constant DC current sources in the equivalent circuits in Fig. 3.5 (b)-(c).

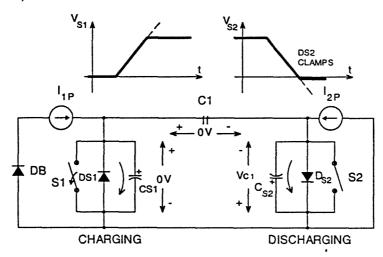

Transition from the top to the bottom switch (interval  $t_{t1}$  in Fig. 3.5 (a)) is initiated by turning-off the top switch. The constant, positive inductor current  $I_{L_p} = I_L - I_o$  (Fig. 3.5 (b)) linearly charges the capacitor across the top switch,  $C_{S1}$ , toward positive voltage and discharges the capacitor across the bottom switch,  $C_{S2}$ , toward negative voltage simultaneously, as shown by the dashed lines in the switch voltage waveforms.

Figure 3.4: : a) Basic buck converter, and b) Soft-switching buck converter obtained by using composite switches S1 and S2.

Figure 3.5: Soft-switching, provided by the bi-directional current source, is explained using equivalent circuits for two transition intervals.

Once the voltage on the bottom switch reaches zero, its diode  $D_{S2}$  becomes forward biased and clamps the bottom switch voltage to zero, and consequently clamps the top switch voltage at bus voltage  $V_g$ . The bottom switch can now be turned-on to zero voltage in a loss-less manner, which completes the first transition interval.

Transition from the bottom to the top switch (interval  $t_{t2}$ ) starts by turning-off the bottom switch S2 carrying negative inductor current  $I_{L_n} = I_L - I_o$  (Fig. 3.5 (a) which provides the opposite charge exchange between the switch capacitors. The bottom switch capacitor  $C_{S2}$  charges toward positive voltage and the top switch capacitor discharges toward negative voltage as shown by the dashed lines in Fig. 3.5 (c). Once the voltage on the top switch reached the bus voltage  $V_g$ , its diode  $D_{S1}$  becomes forward biased and clamps top switch voltage at zero and consequently the bottom switch voltage at  $V_g$ . The top switch (S1) can now be turned-on at zero-voltage in a loss-less manner, which completes the second transition interval  $t_{t2}$ .

Due to different inductor current levels  $I_{L_p}$  and  $I_{L_n}$ , transition from the top to the bottom switch is always shorter than the opposite transition from the bottom to the top switch particularly at high load currents. The amplitude of the inductor current,  $I_L$  has to be at least three to four times greater than the maximum load current in order to achieve soft-switching for all operating conditions, particularly at high switching frequency [25]. It results in increased conduction losses, increased core losses in the inductor, and requirement for additional output voltage filtering. The described soft-switching mechanism is inefficient at high load currents as well as at light loads, even though the loss-less switching can be achieved in a very simple manner and voltage stresses on the switches are the same as in the parent PWM converter.

The proposed soft-switching mechanism can be applied to any basic DC-to DC converter by [25]: a) replacing both transistor and rectifier diode with a composite switch (current-bidirectional switch in parallel with capacitor) realized by MOSFET in practice, b) driving both switches with small and well controlled dead-time, and c) designing the commutating inductor (can be either the output inductor or an additional inductor) such that zero-voltage switching can be achieved for any operating condition.

#### 3.3.2 Soft-Switching Phase Shifted Full-Bridge Converter

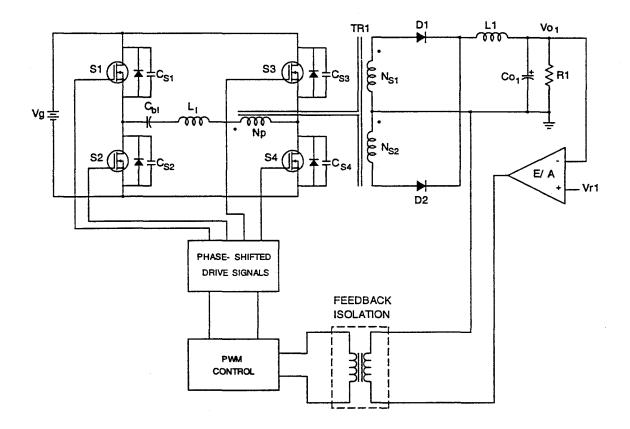

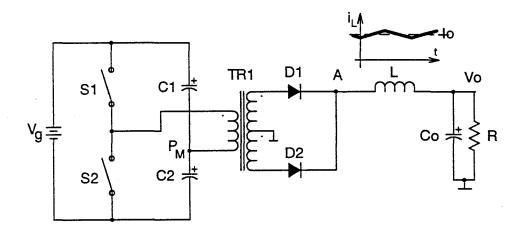

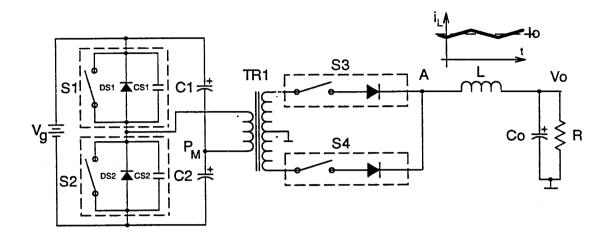

The phase-shifted full-bridge converter is attractive because it utilizes all parasitics and can achieve ZVS of the primary side switches with a constant switching frequency [33]-[37]. The converter is controlled by phase-shifted (four-state) PWM control, as opposed to the parent circuit, the full-bridge converter with traditional (three state) PWM control.

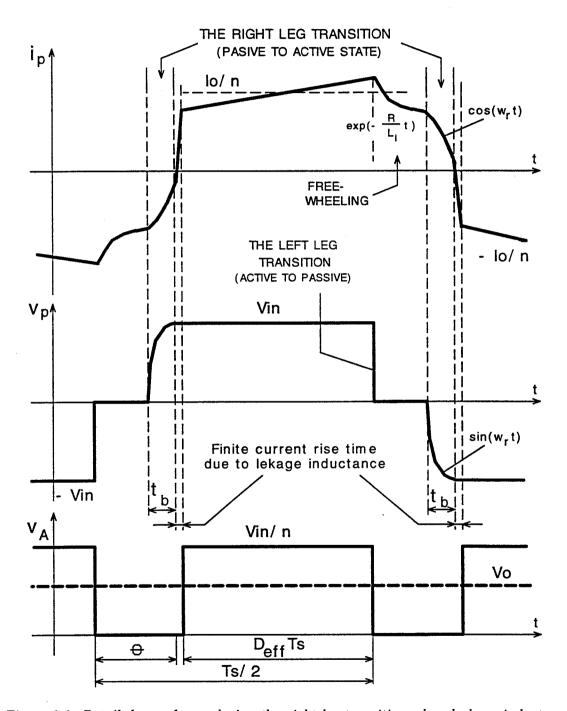

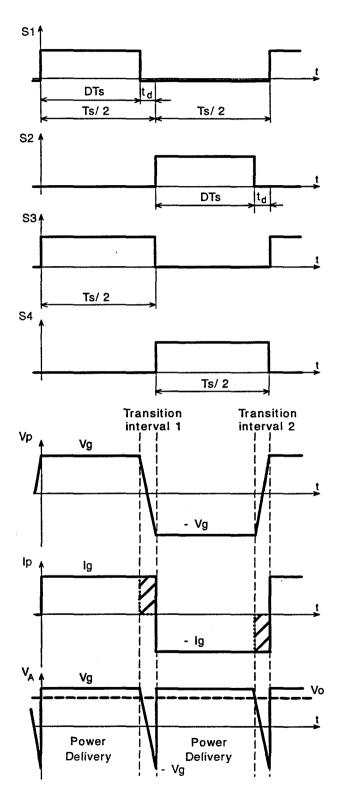

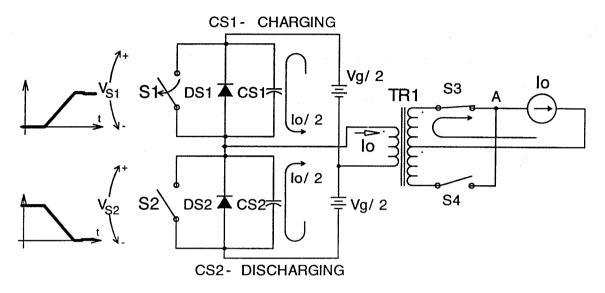

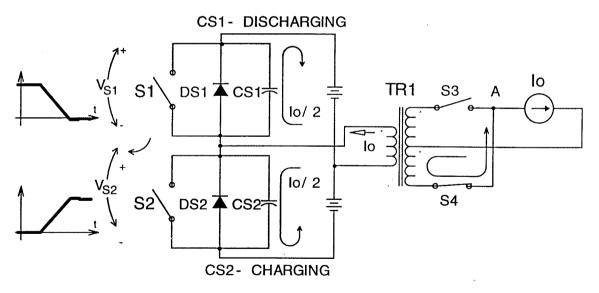

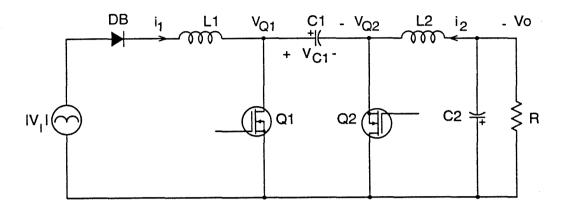

The converter schematic and ideal waveforms are shown in Fig. 3.6 and Fig. 3.7, respectively. Primary side switches, S1-S4, are composite switches realized with MOS-FET transistors in practice. The inductance  $L_l$  represents either leakage inductance of the transformer or externally added inductance required for one transition interval. Capacitances  $C_{S1}-C_{S4}$  represent parasitic capacitances of the composite switches S1-S4, respectively.

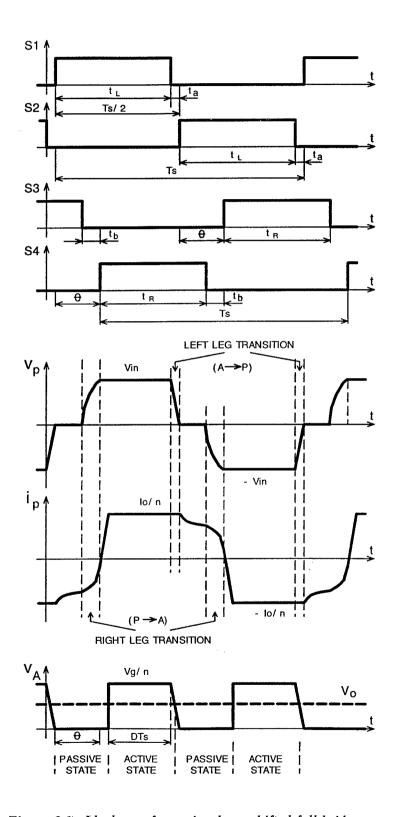

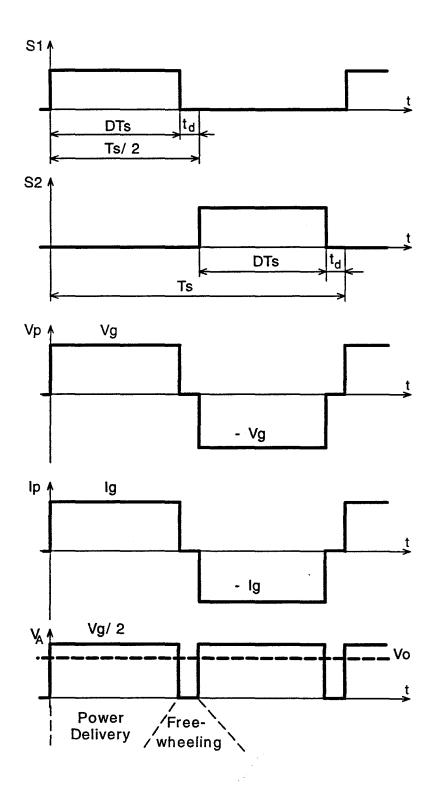

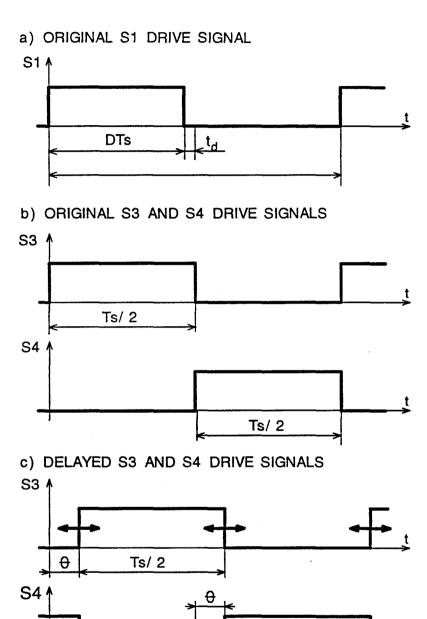

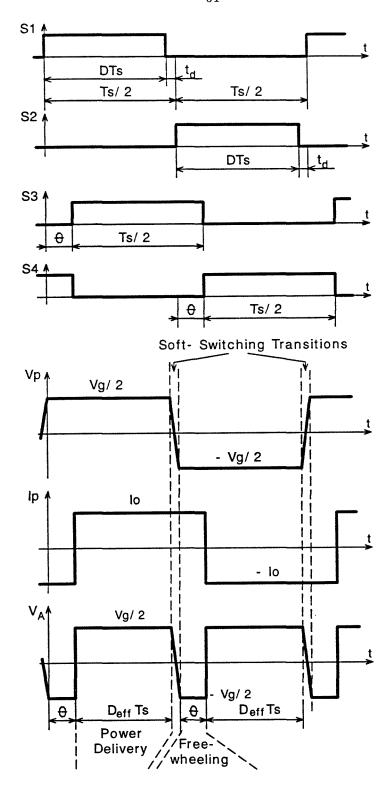

Two switches in the same leg of the bridge, S1 - S2 and S3 - S4, are driven out of phase at 50% duty ratio with small dead-time  $t_a$  and  $t_b$ , respectively (Fig. 3.7). Drive signals for switches S1 and S2 are used as a reference. Their diagonal switches, S4 and S3, are driven with delay or phase shift  $\theta$  as shown in Fig. 3.7 instead of in phase as in a conventional full-bridge converter. Output voltage is regulated by varying phase shift  $\theta$ .

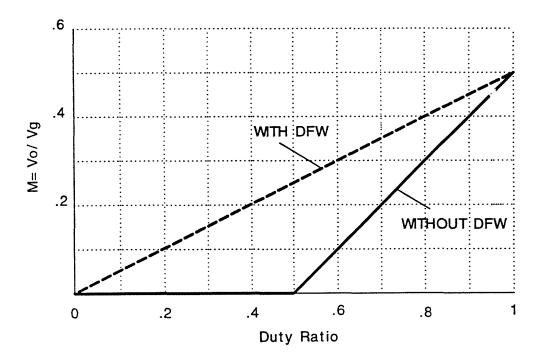

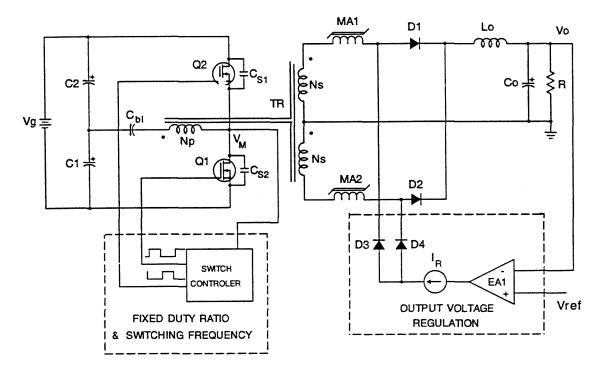

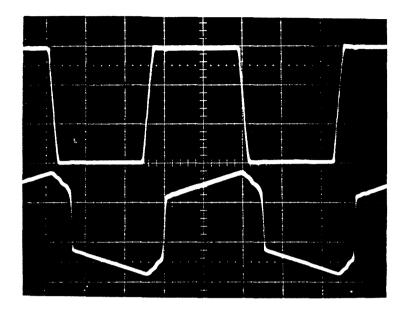

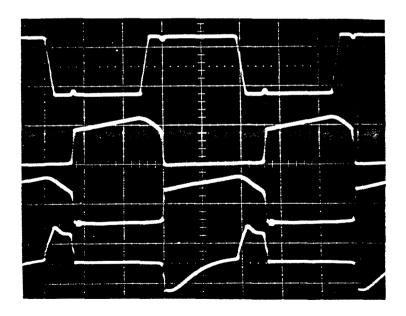

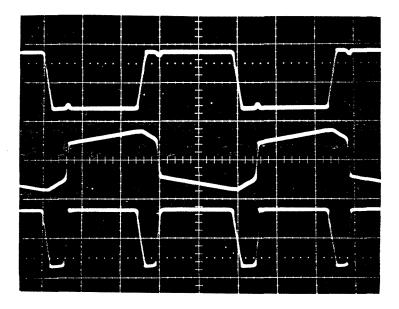

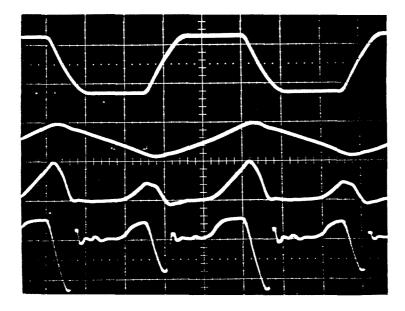

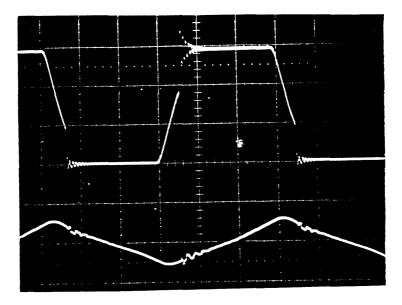

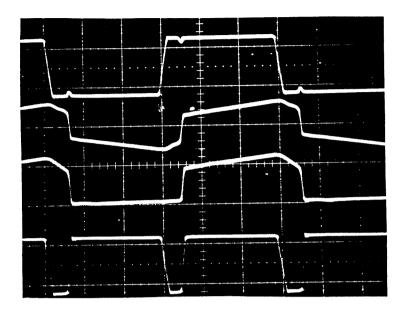

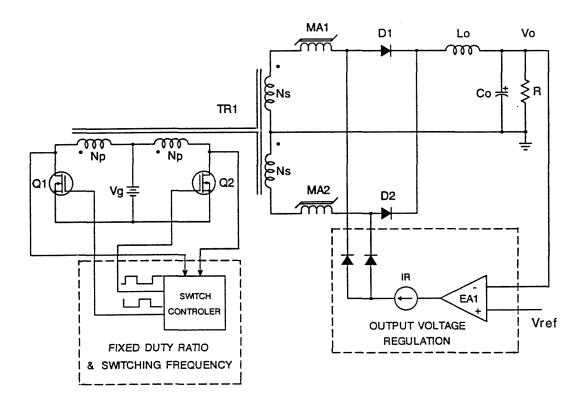

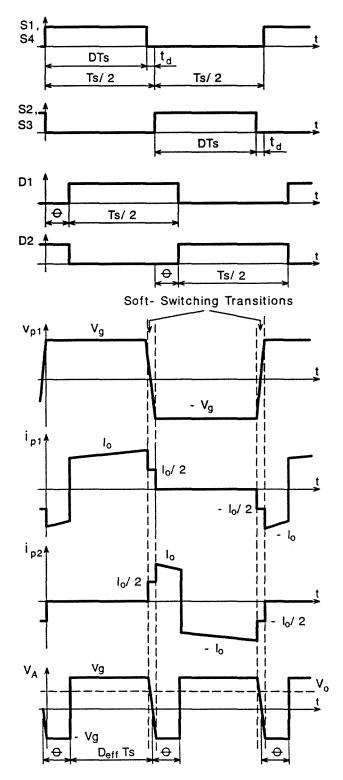

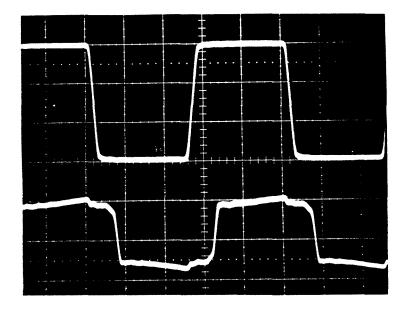

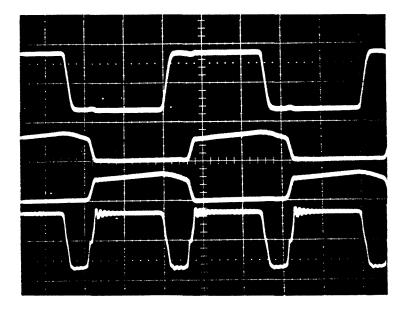

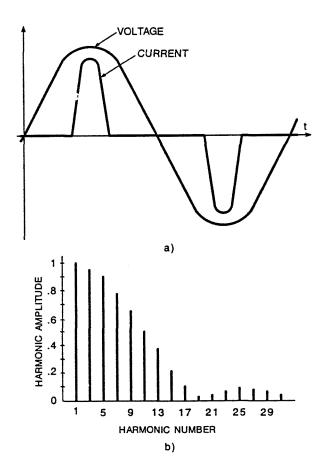

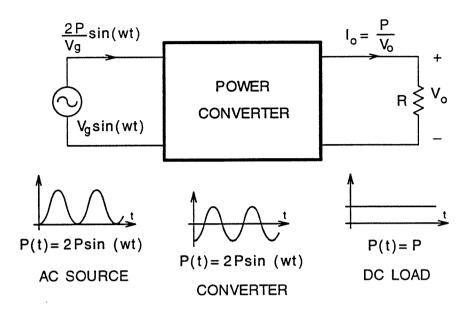

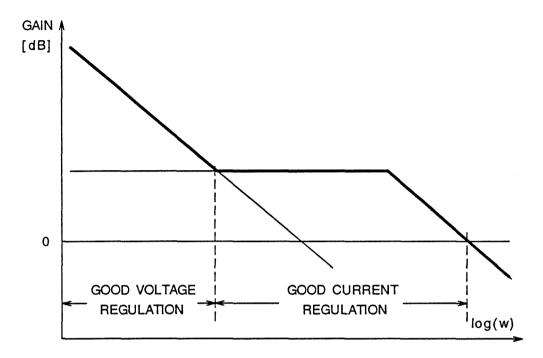

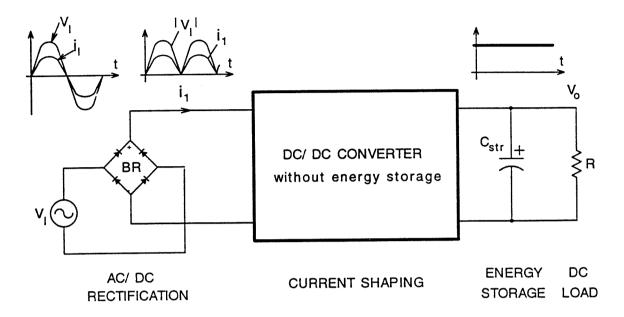

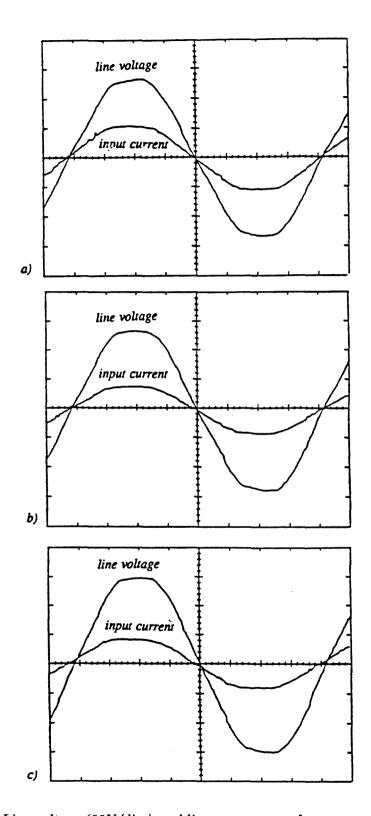

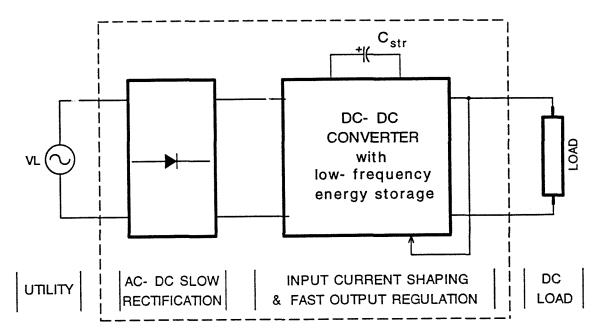

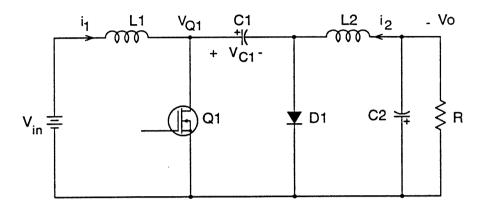

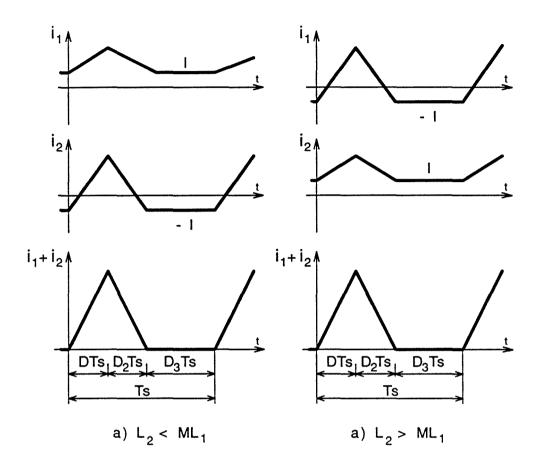

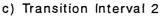

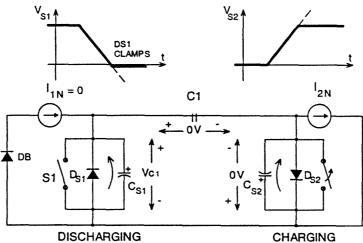

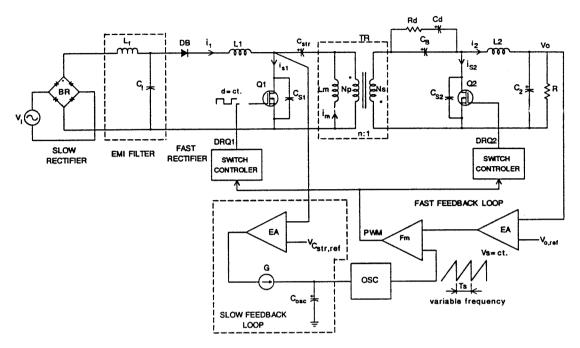

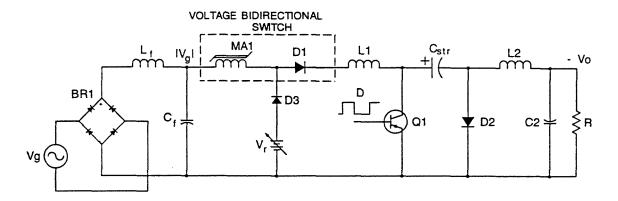

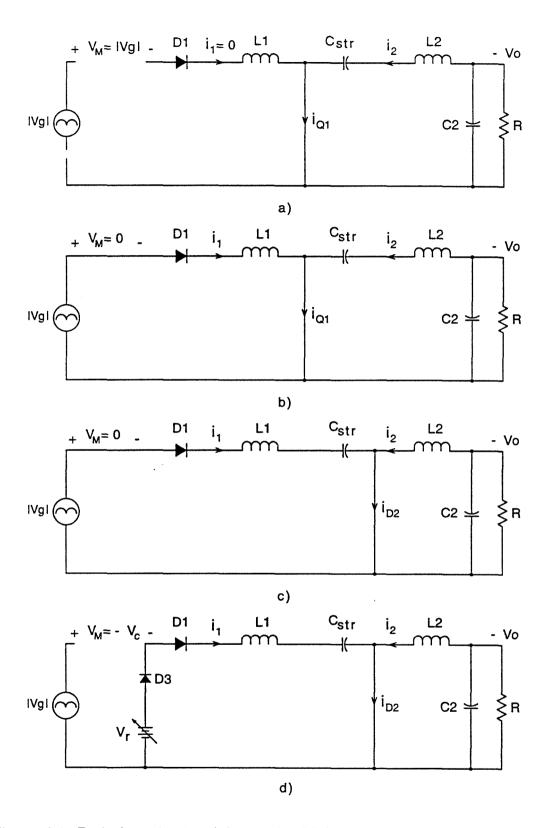

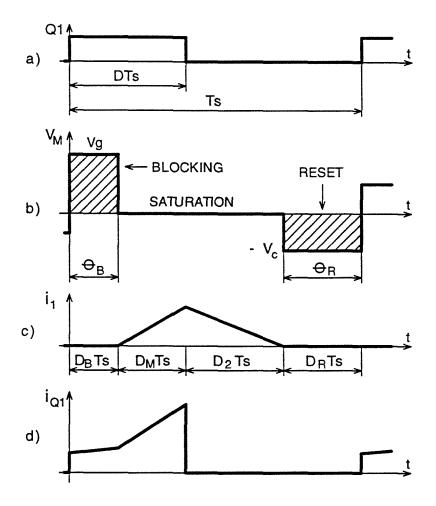

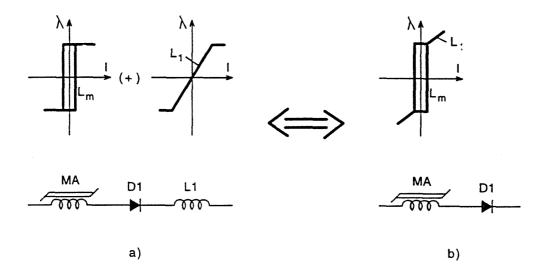

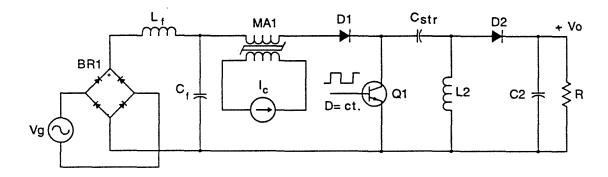

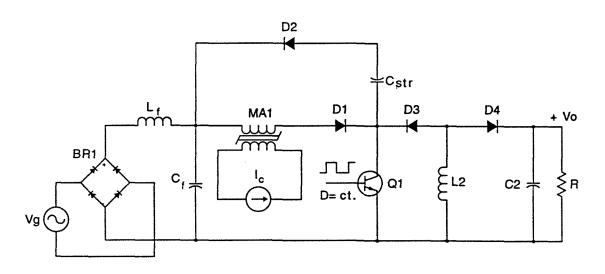

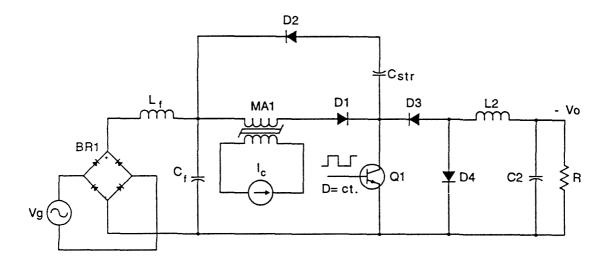

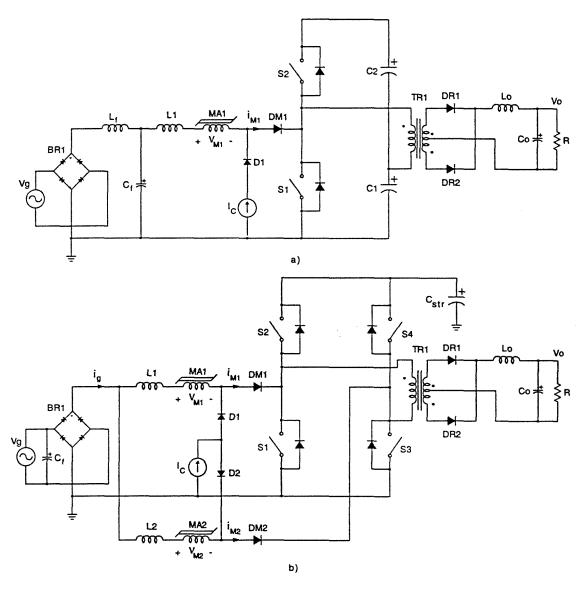

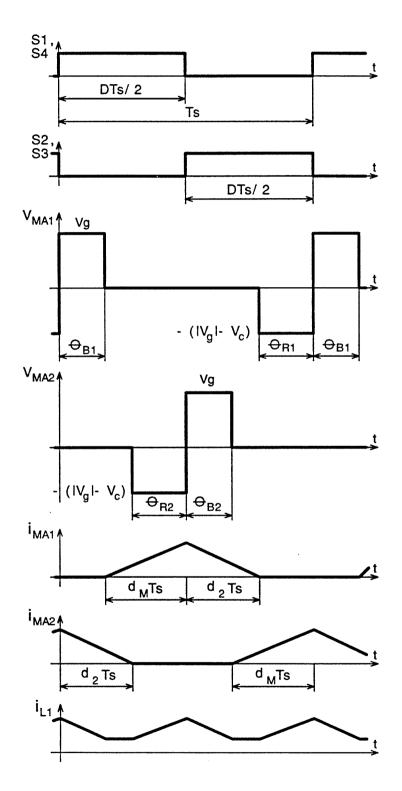

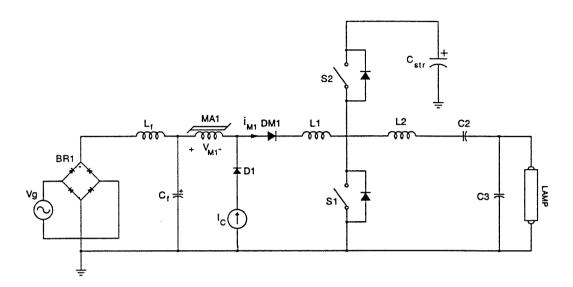

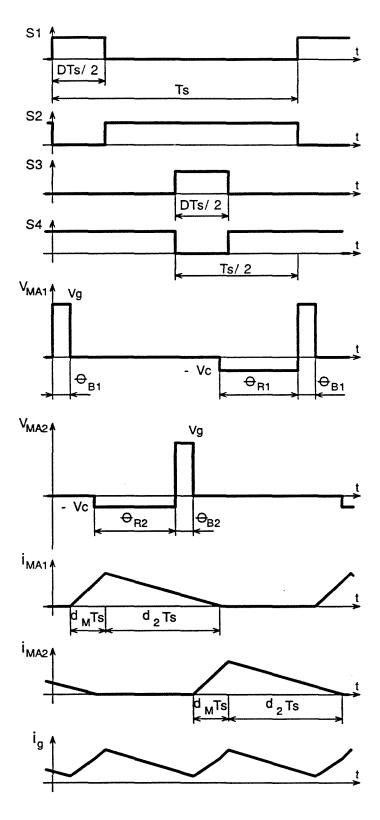

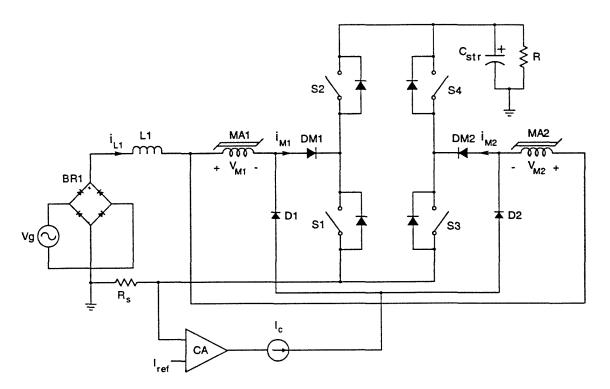

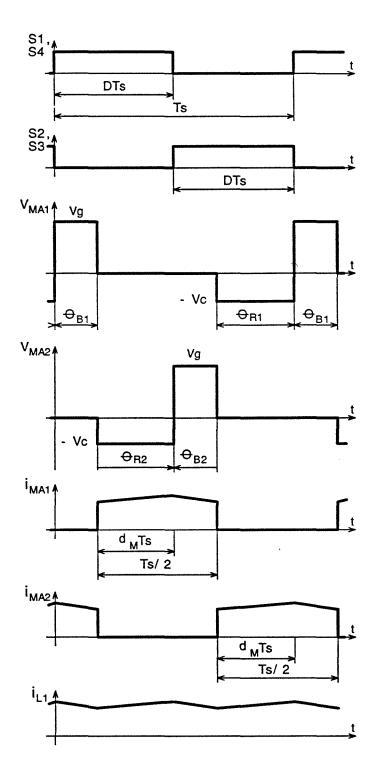

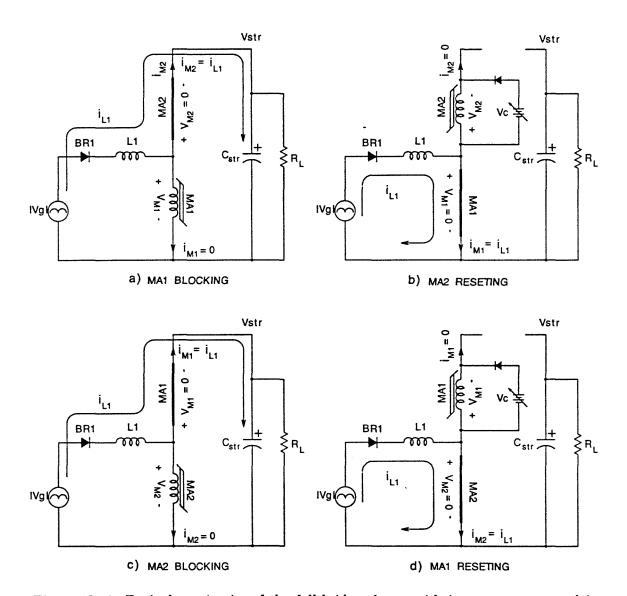

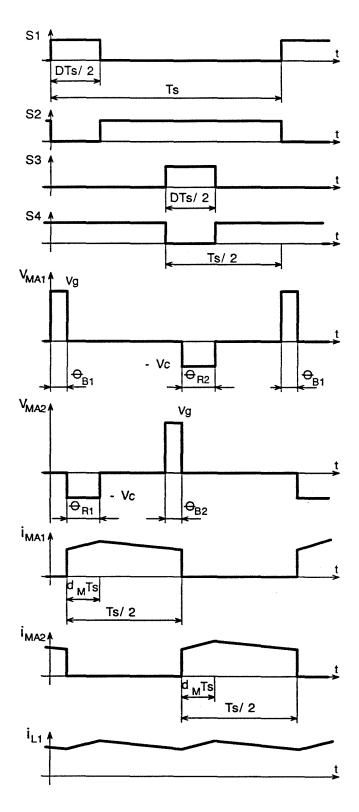

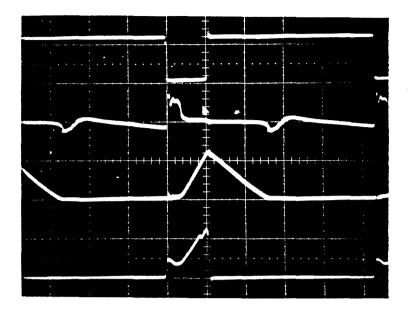

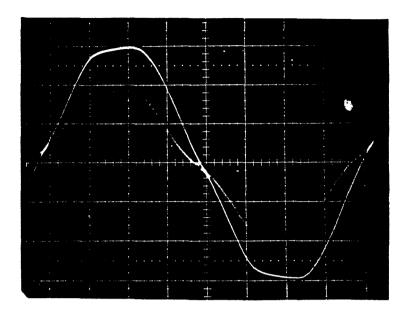

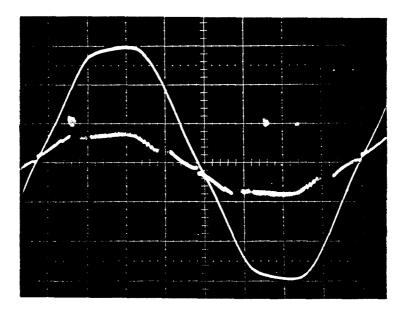

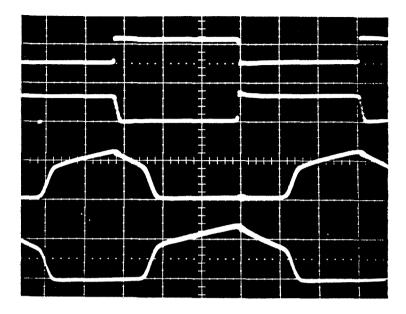

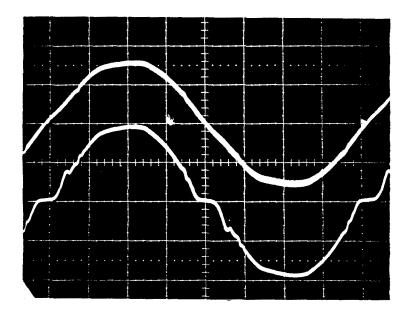

The state in which two diagonal switches are simultaneously conducting is called the *active state*, while the state in which two switches on the same side of the power bus are simultaneously conducting is called the *passive state*. During the passive state both rectifiers, D1 and D2, conduct simultaneously and short the transformer. Power is delivered to the load only during active state. Between active and passive states there are transition intervals,  $t_a$  and  $t_b$ , during which capacitances are charged and discharged simultaneously. In the following analysis transition intervals,  $t_a$  and  $t_b$ , are assumed short compared to switching period  $T_s$ .