# EXPERIMENTAL STUDIES OF HETEROSTRUCTURE DEVICES: RESONANT TUNNELING TRANSISTORS AND GaAs/AlAs/GaAs CAPACITORS

Thesis by

Ted K. Woodward

In Partial Fulfillment of the Requirements

for the Degree of

Doctor of Philosophy

California Institute of Technology

Pasadena, California

1988

(Submitted May 20, 1988)

To my mother and father, for love and courage.

## Acknowledgements

I have developed personally and professionally during my tenure as a graduate student at Caltech. I would like to thank some of the people that have helped me in this ongoing process. I have profited immensely through interaction with my adviser, Professor T. C. McGill. I am indebted to him for his willingness to share his keen intellect and intuition with me. Dr. McGill has provided me a number of excellent research opportunities and the means with which to carry them out. I have learned a lot and had a good time doing it. In addition, Tom has demonstrated a personal concern for me that goes beyond the professional level, for which I am very appreciative.

The standards of professional excellence maintained by the students in Dr. McGill's research group have always been of the highest caliber. The atmosphere among the members of the group is very warm and open. These things have combined to make my graduate experience very enlightening and enjoyable. I would like to express my appreciation to those students who have gone before me. Drs. Reuben Collins, Arati Prabhakar, and Ed Schlesinger were particularly helpful in getting me started in the lab. In addition to useful discussion, Dr. Steve Hetzler's expertise with computer graphics has improved the quality of all theses produced in this group, and mine is no exception. I profited from interaction with Dr. Bob Hauenstein, whose endless curiosity is an example to us all. Dr. Amikam Zur and Dr. George Wu should also be recognized. Dr. Alice Bonnefoi was particularly important to me. We had many interesting discussions, and her work was of great help in my thesis research.

I am indebted to all of the current students in this group, for their willingness to give of their time. Together, we are developing as people and scientists. David Chow has demonstrated a continual willingness to listen to my ramblings, for which I am grateful. I have enjoyed working with Dave immensely. He has

demonstrated an unheard-of patience in his careful reading of the first three chapters of this thesis. I have had many thoughtful discussions with Mike Jackson. He was particularly helpful in trying (without complete success) to straighten out my thinking about the work described in Chapter 5. Richard Miles and Wesley Boudville, my contemporaries in Tom's group, have been helpful as well. I have always appreciated the many ways in which Richard has assisted me during my years in the lab. His sense of humor is remarkable. Thanks, Dick. I have enjoyed various associations with Matthew Johnson, who has convinced me that all Canadians are at least a little bit crazy. He is an an excellent example of the careful researcher. He is also a very tenacious cyclist. More recent members of the group have also been helpful. I am better for having met and spoken with Dr. David Ting, Peter Zampardi, Yasantha Rajakarunanayake, Ed Yu, Ed Croke, and Mark Phillips.

The generous assistance of scientists at Xerox Research Labs in Palo Alto, California, through the provision of samples, made my work possible. I am particularly indebted to Dr. Robert D. Burnham and Harlan Chung. I have enjoyed working with these gentlemen very much. I would like to acknowledge (one last time) the assistance of the whole group at Xerox: F. J. Endicott, D. M. Taylor, T. T. Tjoe, W. J. Mosby, D. W. Treat, S. E. Nelson, R. L. Thornton, J. E. Epler, R. M. Donaldson, T. L. Paoli, and last (but not least) Dr. Robert Bauer.

If Professor McGill is the head of the group, Vere Snell was the heart. I am proud to have known her, for she was one of the nicest people I have ever associated with. I mourn her passing. Marcia Hudson has prevailed, under very difficult circumstances, to become an integral part of the research organization. Her administrative and organizational skills are only surpassed by her friendliness. Carol McCollum has provided exceptional assistance with a myriad of things, which most students never see. Thank you, Carol. Brian Cole played a key part in all of

the MBE research. I would like to acknowledge his assistance.

Dr. David Rutledge and members of his research group have been helpful in explaining the mysteries of microwaves and in the provision of fabrication equipment. I thank Dr. Simon Nieh for TEM measurements on two of my samples. I want to thank Mr. Ogden Marsh for several stimulating discussions. Dr. J. O. McCaldin has also been helpful in this regard.

I am pleased to acknowledge I.B.M. for financial support, with particular thanks to Drs. John Best and Robert Scranton of I.B.M. for their help in securing fellowship support for 1985-86 and 1986-87. I am equally happy to thank T.R.W. for providing fellowship support through the Program in Advanced Technologies for 1987-88.

I would lastly like to thank the friends I have made in my time at Caltech. They are a large part of what make this place special, and bearable. I have never met a more interesting and diverse group of people. To list some would be unfair to the rest. Therefore, thanks to you all. Finally, my special appreciation to Sheryl for her love. For us, this is only the beginning.

## Abstract

This thesis is concerned with the experimental study of two kinds of heterostructure devices. The resonant tunneling transistor (RTT) is the subject of the first part of the thesis. The RTT is a new class of electronic device that has a controllable negative differential resistance (NDR) as its distinguishing characteristic. Since the first realization of a device of this type, in 1985, about 6 types of transistor structures have been reported that exhibit controllable NDR. We report the development of two types of RTTs, which are series integrations of GaAs/Al<sub>x</sub>Ga<sub>1-x</sub>As double-barrier heterostructures with field-effect transistors. Samples were produced by metalorganic chemical vapor deposition (MOCVD). Several fundamental applications of these devices are also presented.

The first device is an integration of a resonant tunneling double-barrier heterostructure with a vertical field-effect transistor. The composite device is referred to as a DB/VFET. The device exhibits NDR in its source-drain I-V curve at 77 K, which is controllable with gate bias. Novel device features include the observation of NDR at large voltages (greater than 10 V) in one bias direction. One device exhibits NDR at room temperature. Typical 77 K peak-to-valley current ratios were about 5. Frequency multiplication and microwave oscillations at 0.8 and 3.3 GHz have been observed in this device. This device is discussed in Chapter 3 and Chapter 5.

The second device is an integration of a double-barrier heterostructure with a planar field-effect transistor, in this case a metal-semiconductor field-effect transistor (MESFET). The composite device is referred to as a DB/MESFET. It also exhibits NDR in its source-drain *I-V* curve, but is qualitatively different from the DB/VFET in its behavior. A variety of output characteristics may be obtained by varying the double-barrier and MESFET parameters. Logic operations are of interest for this device, and a flip-flop circuit is demonstrated with a single

DB/MESFET. This device is described in Chapters 4 and 5.

In Part II of the thesis, studies of a different heterostructure are reported. GaAs/AlAs/GaAs single-barrier capacitor structures, characterized by relatively thick AlAs barriers (1000 - 4000 Å) are the subject of this part of the thesis. Samples were grown by MOCVD. A variety of electrical and optical measurements were performed on these structures. These included capacitance-voltage (C-V), current-voltage (I-V), deep-level transient spectroscopy (DLTS), and photoresponse measurements. This structure, a fundamental part of many heterostructure devices, exhibits novel C-V and I-V behavior that can be attributed to significant densities of electron trap states near one of the GaAs/AlAs interfaces, or in the AlAs. Estimates of the deep-level concentration can be made from both C-Vand I-V measurements, which have been confirmed with DLTS measurements. DLTS confirmed that the trap levels are localized. These studies are described in Chapter 6. Photoresponse measurements of the structures are interesting, and are described in Chapter 7. These studies explain the observation of zero-bias photocurrent consistent with electron transport from the back of the sample to the front.

Parts of this thesis have been or will be published under the following titles:

#### Part I:

Experimental Realization of a Resonant Tunneling Transistor,

T. K. Woodward, T. C. McGill, and R. D. Burnham, Appl. Phys. Lett. 50, 451 (1987).

Integration of a Resonant Tunneling Structure with a Metal Semiconductor Field-Effect Transistor,

T. K. Woodward, T. C. McGill, H. F. Chung, and R. D. Burnham, Appl. Phys. Lett. 51, 1542 (1987).

### Resonant Tunneling Field-Effect Transistors,

T. K. Woodward, T. C. McGill, R. D. Burnham, and H. F. Chung, to be published in Superlattices and Microstructures.

Applications of Resonant Tunneling Field-Effect Transistors,

T. K. Woodward, T. C. McGill, H. F. Chung, and R. D. Burnham, IEEE Electron Dev. Lett. EDL-9, 122 (1988).

#### Part II:

Capacitance-Voltage Characteristics of GaAs-AlAs Heterostructures,

T. K. Woodward, T. E. Schlesinger, T. C. McGill, and R. D. Burnham, Appl. Phys. Lett. 47, 631 (1985).

#### Electrical Behavior of GaAs-AlAs Heterostructures,

T. K. Woodward, T. C. McGill, and R. D. Burnham, J. Vac. Sci. Technol. B 4, 1022 (1986).

Photoresponse of Asymmetrically Doped GaAs-AlAs Heterostructures under External Bias,

T. K. Woodward, T. C. McGill, and R. D. Burnham, J. Appl. Phys. 60, 3755 (1986).

# **Contents**

| A  | cknov | wledge | ments ii                               | ì  |

|----|-------|--------|----------------------------------------|----|

| A. | bstra | ct     | v                                      | 'i |

| Li | st of | Public | cations vii                            | i  |

| 1  | Intr  | oducti | ion and Overview                       | 1  |

|    | 1.1   | Result | s Summary                              | 2  |

|    | 1.2   | Why I  | Heterostructures?                      | 3  |

|    | 1.3   | Reson  | ant Tunneling Transistors              | 5  |

|    |       | 1.3.1  | Double Barriers                        | 5  |

|    |       | 1.3.2  | State of the Art                       | 7  |

|    |       | 1.3.3  | Introduction to Three-Terminal Devices | 9  |

|    |       | 1.3.4  | DB/VFET Devices                        | 0  |

|    |       | 1.3.5  | DB/MESFET Devices                      | 4  |

|    |       | 1.3.6  | Conclusions                            | 7  |

|    | 1.4   | AlAs   | Capacitors                             | 7  |

|    |       | 1.4.1  | Introduction                           | 7  |

|    |       | 1.4.2  | Capacitance Measurements               | 8  |

|    |       | 1.4.3  | DLTS Measurements                      | 2  |

|    |       | 1.4.4  | Current-Voltage Measurements           | 4  |

|   |      | 1.4.5  | Conclusions                                          | 26 |

|---|------|--------|------------------------------------------------------|----|

|   | 1.5  | Photo  | response Measurements                                | 27 |

|   | 1.6  | Guide  | e to Remaining Chapters                              | 30 |

|   |      |        |                                                      |    |

|   | R    | ESOP   | NANT TUNNELING TRANSISTORS                           | 35 |

| 2 | Doi  | ıble B | arriers and Three-Terminal Devices: Background, The- |    |

|   | ory, | and I  | Materials                                            | 36 |

|   | 2.1  | Outlin | ne and Summary of Results                            | 36 |

|   | 2.2  | Theor  | y of the Double Barrier                              | 37 |

|   |      | 2.2.1  | Expression for Current                               | 38 |

|   |      | 2.2.2  | Transmission Resonances                              | 39 |

|   |      | 2.2.3  | Barrier Heights                                      | 42 |

|   |      | 2.2.4  | Peak-to-Valley Ratio                                 | 43 |

|   |      | 2.2.5  | Resonance Width                                      | 43 |

|   |      | 2.2.6  | Inelastic Effects                                    | 43 |

|   |      | 2.2.7  | Speed Considerations                                 | 45 |

|   |      | 2.2.8  | Summary                                              | 46 |

|   | 2.3  | MBE    | Growth of Double Barriers                            | 46 |

|   |      | 2.3.1  | Results                                              | 47 |

|   | 2.4  | MOC    | VD Growth                                            | 53 |

|   |      | 2.4.1  | Comparison to MBE                                    | 54 |

|   | 2.5  | Three  | -Terminal Devices: An Overview                       | 55 |

|   |      | 2.5.1  | Motivation                                           | 55 |

|   |      | 2.5.2  | Working Devices                                      | 57 |

|   |      | 2.5.3  | Quantum-Well RTTs                                    | 59 |

|   | 2.6  | Concl  | usions                                               | 62 |

| 3 | DB/  | VFET           | Devices                           | 67  |

|---|------|----------------|-----------------------------------|-----|

|   | 3.1  | Results        | Summary                           | 67  |

|   | 3.2  | Outline        | e of Chapter                      | 68  |

|   | 3.3  | Device         | Concept                           | 68  |

|   | 3.4  | Actual         | Device Design                     | 70  |

|   | 3.5  | Growtl         | h                                 | 74  |

|   |      | 3.5.1          | Double Barrier                    | 74  |

|   |      | 3.5.2          | FET                               | 75  |

|   | 3.6  | Fabrica        | ation                             | 75  |

|   |      | 3.6.1          | Layout                            | 76  |

|   |      | 3.6.2          | Procedure                         | 78  |

|   |      | 3.6.3          | Refinements                       | 80  |

|   | 3.7  | Experi         | mental                            | 81  |

|   | 3.8  | Basic 1        | Results                           | 82  |

|   |      | 3.8.1          | Sample T245                       | 82  |

|   |      | 3.8.2          | Sample T335                       | 85  |

|   | 3.9  | Discus         | sion and Further Study            | 85  |

|   |      | 3.9.1          | Reverse-Bias Behavior             | 85  |

|   |      | 3.9.2          | Forward-Bias Behavior             | 92  |

|   |      | 3.9.3          | Room-Temperature NDR              | 93  |

|   |      | 3.9.4          | Common Source versus Common Drain | 94  |

|   |      | 3.9.5          | Variable Cross Section            | 96  |

|   | 3.10 | Supple         | ementary Data                     | 98  |

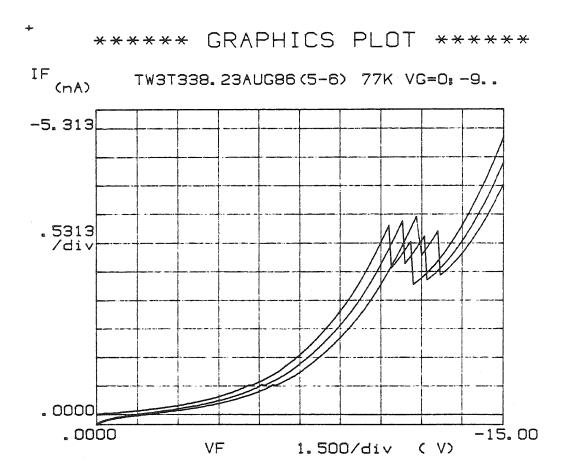

|   |      | 3.10.1         | Sample T338                       | 98  |

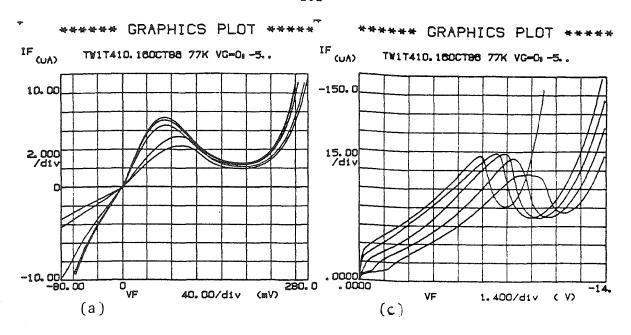

|   |      | 3.10.2         | Sample T410                       | 100 |

|   |      | 3.10. <b>3</b> | Sample T411                       | 100 |

|   | 3.11 | Theore         | etical Considerations             | 103 |

|   | 3.12 | Conclu | isions                                 |

|---|------|--------|----------------------------------------|

| 4 | DB/  | MESI   | FET Devices 111                        |

|   | 4.1  | Introd | uction                                 |

|   |      | 4.1.1  | Summary of Results                     |

|   |      | 4.1.2  | Outline of Chapter                     |

|   | 4.2  | Conce  | pt and Design                          |

|   | 4.3  | Growt  | h                                      |

|   |      | 4.3.1  | Recessed Gate                          |

|   |      | 4.3.2  | Pulsed Doping                          |

|   | 4.4  | Proces | ssing                                  |

|   |      | 4.4.1  | Mask Layouts                           |

|   |      | 4.4.2  | Procedure                              |

|   | 4.5  | Funda  | mental Results and Discussion          |

|   | ,    | 4.5.1  | Overview                               |

|   |      | 4.5.2  | Sample T573                            |

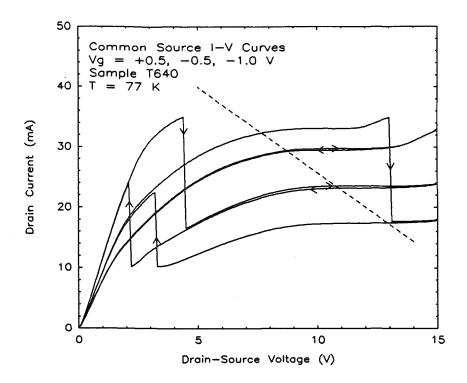

|   |      | 4.5.3  | Sample T640                            |

|   | 4.6  | Simple | e Models                               |

|   | 4.7  | Supple | ementary Results                       |

|   |      | 4.7.1  | Samples T424, T425, T498, and T499 140 |

|   |      | 4.7.2  | Sample T548                            |

|   |      | 4.7.3  | Sample T549                            |

|   |      | 4.7.4  | Sample T550                            |

|   |      | 4.7.5  | Sample T573                            |

|   |      | 4.7.6  | Sample T624                            |

|   |      | 4.7.7  | Sample T625                            |

|   |      | 4.7.8  | Sample T640                            |

|   | 4.8  |        | usions                                 |

|   |      |        |                                        |

| 5  | Dev  | ice Ap  | plications                                     | 1   | 59               |

|----|------|---------|------------------------------------------------|-----|------------------|

|    | 5.1  | Summa   | ary of Results                                 | . 1 | 159              |

|    | 5.2  | Outline | e of Chapter                                   | : 1 | L60 <sub>.</sub> |

|    | 5.3  | Logic I | Elements                                       | . ] | 160              |

|    |      | 5.3.1   | Concept                                        |     | 160              |

|    |      | 5.3.2   | Sample T640 Flip-Flops                         | . : | 161              |

|    |      | 5.3.3   | Sample T573 Flip-Flops                         |     | 163              |

|    |      | 5.3.4   | Other Logic Operations                         |     | 167              |

|    |      | 5.3.5   | Other Devices                                  |     | 167              |

|    |      | 5.3.6   | Extensions                                     |     | 168              |

|    |      | 5.3.7   | Historical: Tunnel Diodes                      |     | 169              |

|    | 5.4  | Freque  | ency Multiplication                            | •   | 170              |

|    |      | 5.4.1   | Concept                                        |     | 170              |

|    |      | 5.4.2   | Results                                        |     | 170              |

|    |      | 5.4.3   | Refinements                                    |     | 173              |

|    | 5.5  | Oscilla | tors                                           | •   | 173              |

|    |      | 5.5.1   | NDR oscillators                                |     | 174              |

|    |      | 5.5.2   | Transit-Time Oscillators                       |     | 177              |

|    |      | 5.5.3   | Results and Discussion                         |     | 178              |

|    |      | 5.5.4   | Refinements                                    |     | 187              |

|    | 5.6  | Conclu  | sions                                          | •   | 188              |

|    |      |         |                                                |     |                  |

| II | G    | aAs/.   | AlAs/GaAs CAPACITORS                           | 1   | 91               |

| 6  | Elec | ctrical | Measurements of GaAs-AlAs-GaAs Heterostructure | s 1 | 92               |

|    | 6.1  | Outlin  | e of Chapter                                   |     | 192              |

|    |      | 6.1.1   | Summary of Results                             |     | 193              |

|    | 6.2  | Introd  | uction and Background                          |     | 194              |

|          | 6.2.1        | General Background                               |  |  |  |  |  |  |  |  |  |

|----------|--------------|--------------------------------------------------|--|--|--|--|--|--|--|--|--|

|          | 6.2.2        | AlAs Barriers                                    |  |  |  |  |  |  |  |  |  |

| 6.3      | Geome        | etry and Growth                                  |  |  |  |  |  |  |  |  |  |

| 6.4      | Experimental |                                                  |  |  |  |  |  |  |  |  |  |

|          | 6.4.1        | Fabrication                                      |  |  |  |  |  |  |  |  |  |

|          | 6.4.2        | C-V and I-V Measurements                         |  |  |  |  |  |  |  |  |  |

|          | 6.4.3        | DLTS 201                                         |  |  |  |  |  |  |  |  |  |

| 6.5      | Capac        | itance Results and Discussion                    |  |  |  |  |  |  |  |  |  |

|          | 6.5.1        | Room-Temperature Observations                    |  |  |  |  |  |  |  |  |  |

|          | 6.5.2        | Pulsed Illumination Studies                      |  |  |  |  |  |  |  |  |  |

|          | 6.5.3        | Variable Frequency Studies                       |  |  |  |  |  |  |  |  |  |

|          | 6.5.4        | Variable-Temperature Studies                     |  |  |  |  |  |  |  |  |  |

|          | 6.5.5        | Capacitance Conclusions                          |  |  |  |  |  |  |  |  |  |

| 6.6      | DLTS         | Results and Discussion                           |  |  |  |  |  |  |  |  |  |

|          | 6.6.1        | Spatial Localization                             |  |  |  |  |  |  |  |  |  |

|          | 6.6.2        | Activation Energies                              |  |  |  |  |  |  |  |  |  |

|          | 6.6.3        | Conclusions                                      |  |  |  |  |  |  |  |  |  |

| 6.7      | Curre        | nt-Voltage Measurements                          |  |  |  |  |  |  |  |  |  |

| 6.8      | Concl        | usions                                           |  |  |  |  |  |  |  |  |  |

| Pho      | toreer       | onse Measurements of GaAs-AlAs-GaAs Heterostruc- |  |  |  |  |  |  |  |  |  |

| tur      | -            | 233                                              |  |  |  |  |  |  |  |  |  |

| 7.1      |              | ne of Chapter                                    |  |  |  |  |  |  |  |  |  |

| 7.2      |              | nary of Results                                  |  |  |  |  |  |  |  |  |  |

| 7.3      |              | imental                                          |  |  |  |  |  |  |  |  |  |

| 7.4      | _            | nated Current-Voltage Measurements               |  |  |  |  |  |  |  |  |  |

| 8 6 T.S. | 7.4.1        | Room-Temperature Measurements                    |  |  |  |  |  |  |  |  |  |

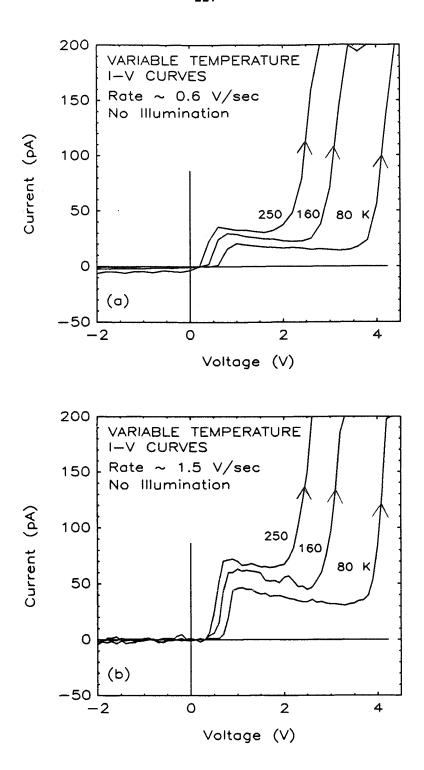

|          |              | Variable-Temperature Measurements                |  |  |  |  |  |  |  |  |  |

|          | v o ≖ o ded  | v waawoo a Campos wu wat ivitono michilo         |  |  |  |  |  |  |  |  |  |

7

## xvi

|   |                        | 7.4.3   | Su   | mn          | ıary |     |     | • • |     | •  | •  | • • | •  | •   | •  | •   |     | • | • | • | • | • | • | • | • | • | • | • | • | • | 240 |

|---|------------------------|---------|------|-------------|------|-----|-----|-----|-----|----|----|-----|----|-----|----|-----|-----|---|---|---|---|---|---|---|---|---|---|---|---|---|-----|

|   | 7.5                    | Photo   | curi | ent         | vei  | rsu | s I | nci | de  | nt | P  | ho  | to | n . | Er | ıeı | gy  |   |   | • |   | • | • |   |   |   |   |   | • |   | 242 |

|   |                        | 7.5.1   | Re   | sul         | ts . |     |     | •   |     | •  | •  | • • |    | ٠   | •  |     | e e | • | • | • |   | • | • |   | • |   | • |   | • |   | 242 |

|   |                        | 7.5.2   | Ar   | ıaly        | sis  |     |     | •   |     | ٠  | •  |     |    | o   | •  | •   | • • |   | • | • | • | ۰ | • | • |   |   | • |   |   |   | 243 |

|   | 7.6                    | Conclu  | usio | ns          |      |     | • • | •   | o e |    | •  |     |    | •   | •  | •   | • • |   | • |   | • | • |   |   |   | • |   |   |   | • | 251 |

|   | 7.7                    | Epilog  | gue: | Lo          | ose  | En  | ıds |     |     |    |    | • • |    | •   |    |     |     |   | • |   |   | • | • | • | • |   |   |   |   |   | 251 |

| A | Pho                    | tolitho | ogr  | aph         | ıy   |     |     |     |     |    |    |     |    |     |    |     |     |   |   |   |   |   |   |   |   |   |   |   |   |   | 255 |

| B | B Photocurrent Details |         |      |             |      |     |     |     |     |    |    | 258 |    |     |    |     |     |   |   |   |   |   |   |   |   |   |   |   |   |   |     |

| C | TEN                    | M Dat   | a    |             |      |     |     |     |     |    |    |     |    |     |    |     |     |   |   |   |   |   |   |   |   |   |   |   |   |   | 263 |

| D | Glos                   | ssary ( | of A | <b>l</b> cr | ony  | m   | ទ ខ | anc | 1 4 | Ab | bı | e'  | vi | at: | io | ns  | 3   |   |   |   |   |   |   |   |   |   |   |   |   |   | 264 |

# List of Figures

| 1.1 | Double-barrier I-V curves and band diagrams                    | 6  |

|-----|----------------------------------------------------------------|----|

| 1.2 | Final DB/VFET device cross section                             | 11 |

| 1.3 | Reverse-bias DB/VFET I-V curve                                 | 13 |

| 1.4 | DB/MESFET cross-sectional schematic                            | 14 |

| 1.5 | Forward-bias DB/MESFET I-V curve                               | 16 |

| 1.6 | Nonilluminated $C-V$ data for sample H399                      | 20 |

| 1.7 | Nonilluminated I-V curve of single barrier                     | 25 |

| 1.8 | Representative I-V curve taken under illumination at room tem- |    |

|     | perature                                                       | 28 |

| 2.1 | Simple band diagram for double barrier                         | 38 |

| 2.2 | I-V curves for an MBE grown double-barrier diode               | 49 |

| 2.3 | I-V curves for an MBE grown double-barrier diode, at 300 K $$  | 50 |

| 2.4 | I-V curves for an MBE grown double-barrier diode               | 51 |

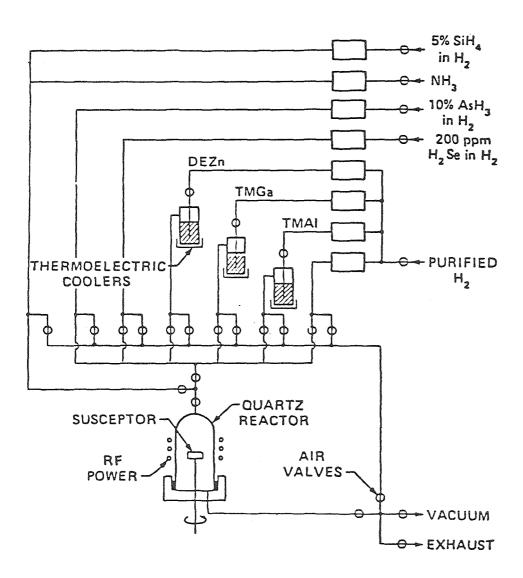

| 2.5 | MOCVD reactor schematic                                        | 56 |

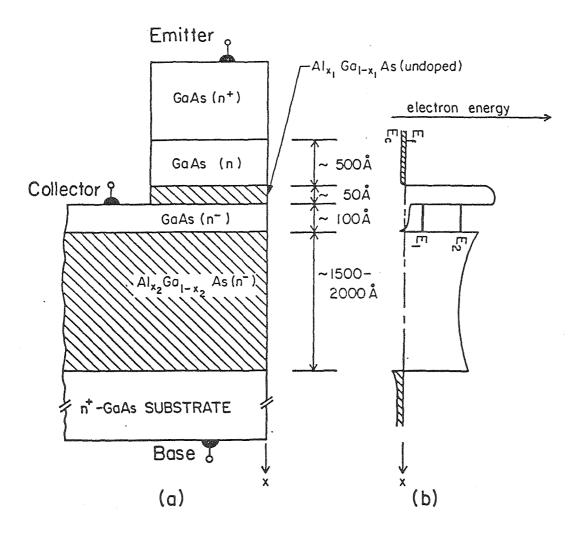

| 2.6 | A proposed resonant tunneling transistor                       | 61 |

| 3.1 | Basic DB/VFET concept                                          | 69 |

| 3.2 | Actual DB/VFET design                                          | 71 |

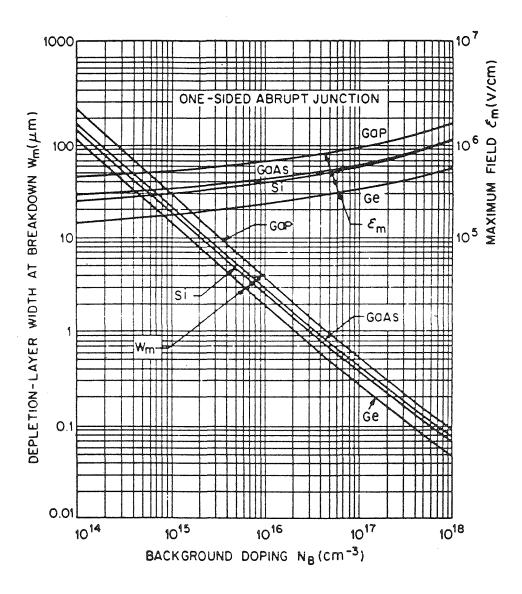

| 3.3 | Maximum depletion length at breakdown in an abrupt junction    | 73 |

| 3.4 | Three-dimensional DB/VFET layout                               | 77 |

## xviii

| 3.5  | Reverse-bias data for sample T245 84                                                                                    |

|------|-------------------------------------------------------------------------------------------------------------------------|

| 3.6  | Forward-bias data for sample T245                                                                                       |

| 3.7  | I-V data for T335 in reverse bias at 300 K                                                                              |

| 3.8  | I-V data for T335 in reverse bias at 77 K                                                                               |

| 3.9  | Additional reverse-bias I-V data for T335 at 300 and 77 K 89                                                            |

| 3.10 | Forward-bias data for T335 at 77 K                                                                                      |

| 3.11 | Diagram of JFET                                                                                                         |

| 3.12 | Common-source I-V data for sample T335 for a variety of mesa                                                            |

|      | cross sections                                                                                                          |

| 3.13 | Reverse-bias common-drain data for sample T338 at 77 K 99                                                               |

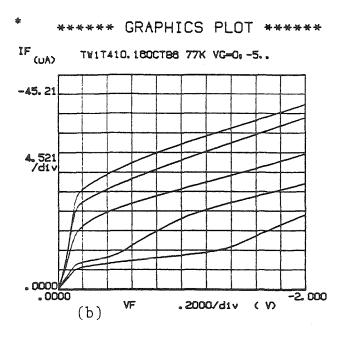

| 3.14 | <i>I-V</i> data for sample T410                                                                                         |

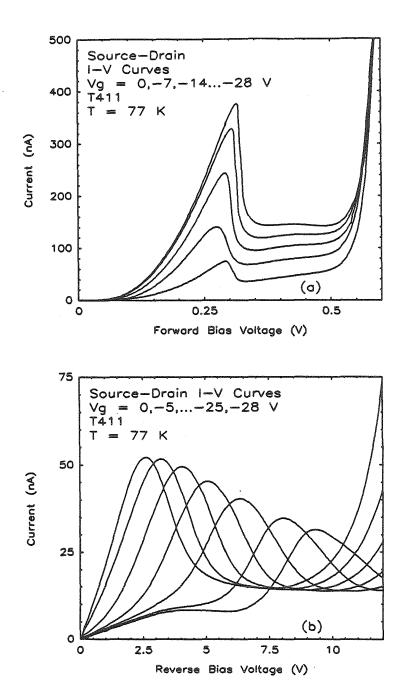

| 3.15 | <i>I-V</i> curves for sample T411                                                                                       |

| •    |                                                                                                                         |

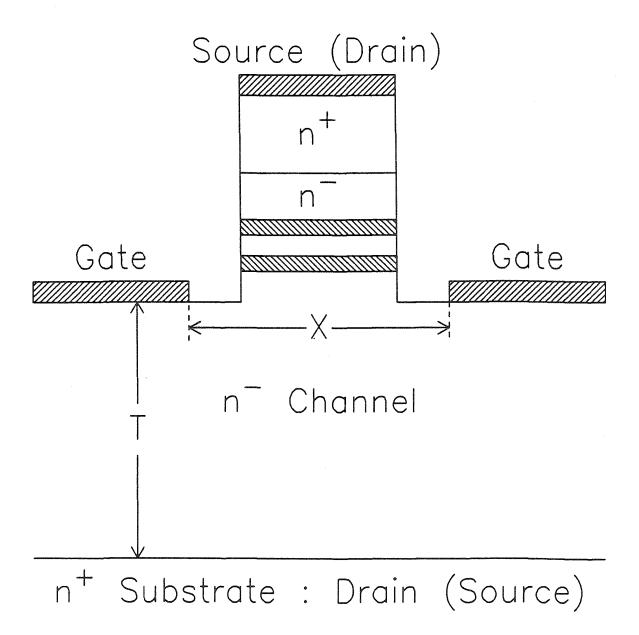

| 4.1  | Cross section of a recessed-gate DB/MESFET                                                                              |

| 4.2  | Data for cycled doped channel layers                                                                                    |

| 4.3  | Three-dimensional view of DB/MESFET layout                                                                              |

| 4.4  | A three-dimensional cutaway view of DB/MESFET 119                                                                       |

| 4.5  | Etch-rate data for 50:3:1 mixture of H <sub>2</sub> O:H <sub>3</sub> PO <sub>4</sub> :H <sub>2</sub> O <sub>2</sub> 121 |

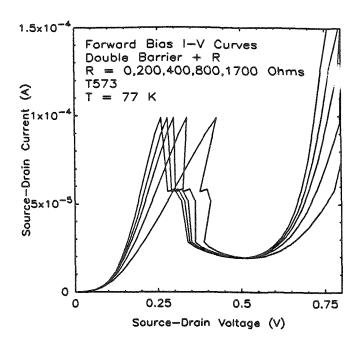

| 4.6  | Two-terminal I-V for sample T573 124                                                                                    |

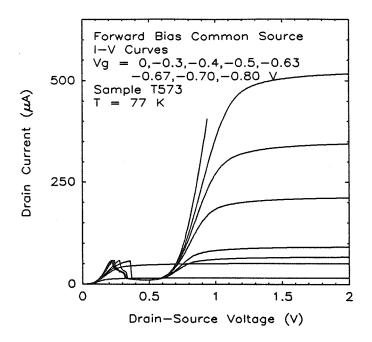

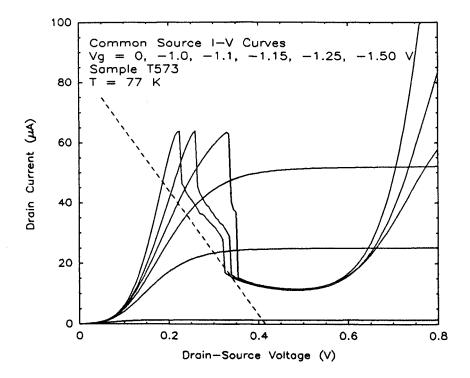

| 4.7  | Forward-bias common-source $I-V$ characteristics for T573 125                                                           |

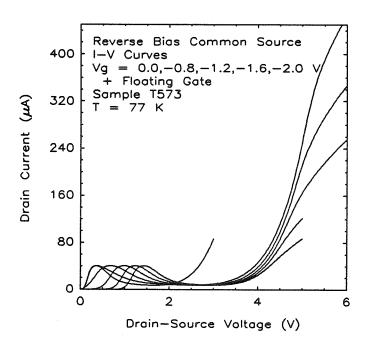

| 4.8  | Reverse-bias common-source I-V characteristics for T573 126                                                             |

| 4.9  | Two-teminal I-V behavior of T640                                                                                        |

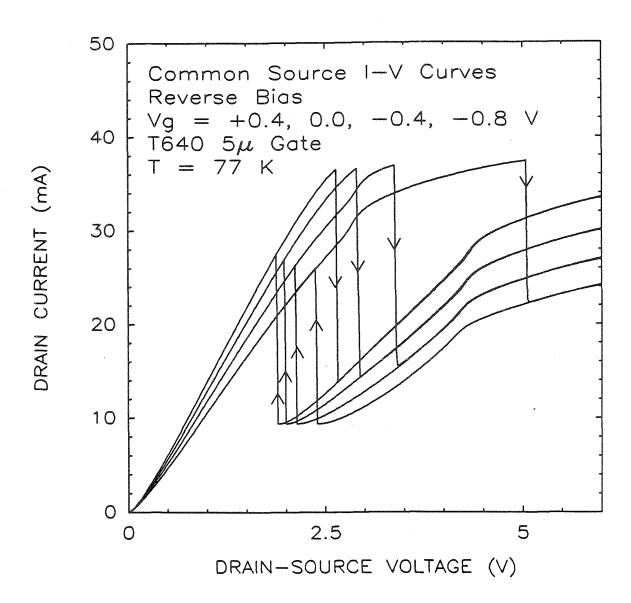

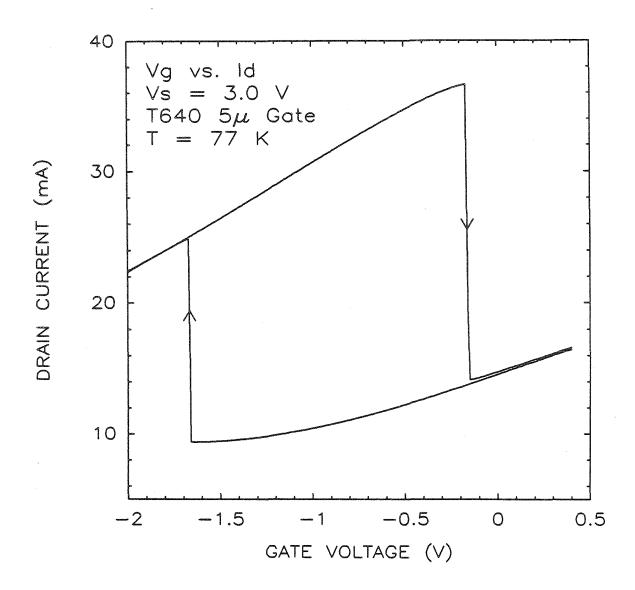

| 4.10 | 2500 Å channel DB/MESFET characteristics for sample T640 130                                                            |

| 4.11 | 2000 Å channel DB/MESFET characteristics for sample T640 131                                                            |

| 4.12 | Drain current vs. gate bias for sample T640                                                                             |

| 4.13 | Linear-resistance addition model of DB/MESFET applied to sample                                                         |

|      | T573                                                                                                                    |

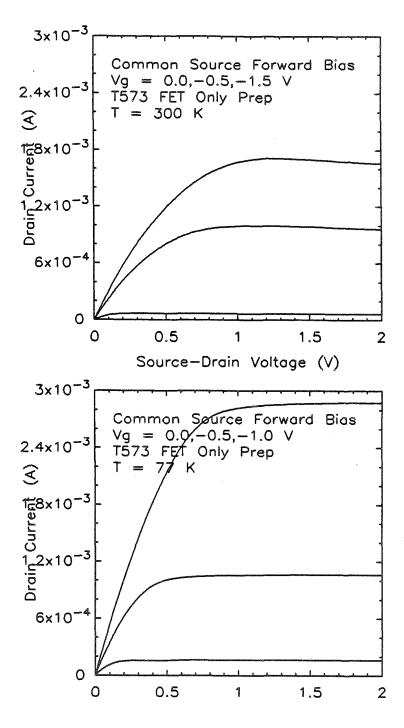

| 4.14 | FET-only preparation I-V characteristics for T573 at 300 and 77 K. 137                                                  |

| 4.15 | Calculated MESFET characteristics for T573                            |

|------|-----------------------------------------------------------------------|

| 4.16 | Series combination of two-terminal NDR characteristic with FET        |

|      | characteristics for T573                                              |

| 4.17 | Linear model calculation for sample T640                              |

| 4.18 | Two-region model calculation for T640                                 |

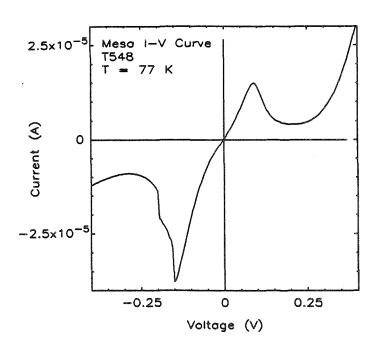

| 4.19 | Two-terminal NDR behavior of sample T548                              |

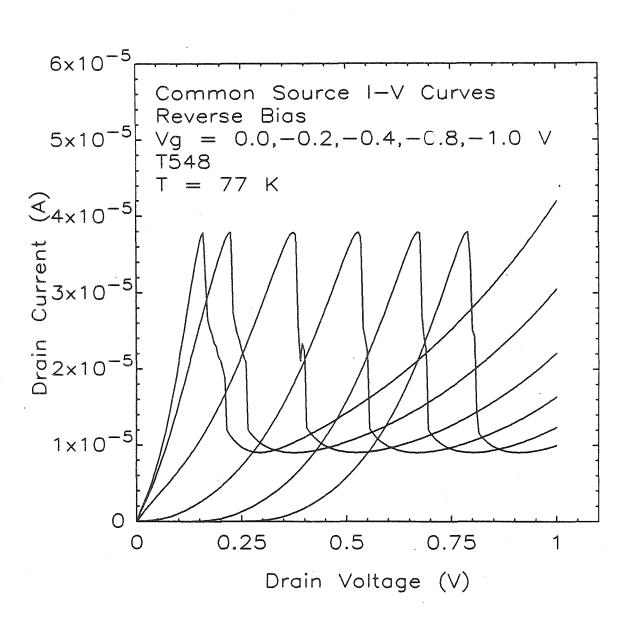

| 4.20 | Reverse-bias common-source behavior of sample T548 143                |

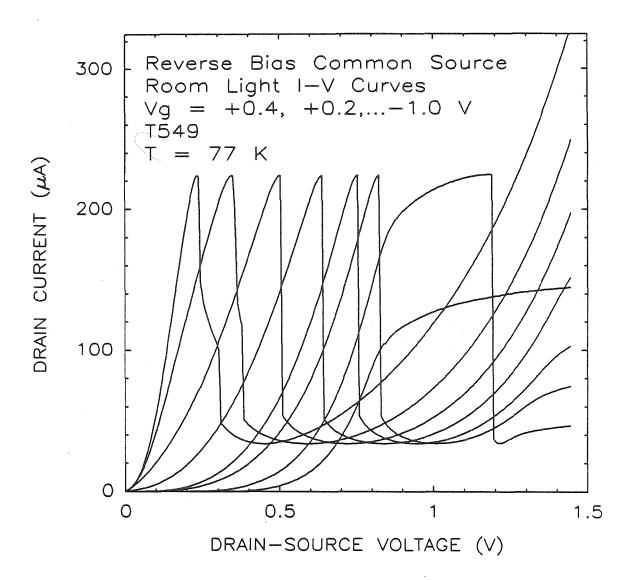

| 4.21 | Reverse-bias common-source data for sample T549 145                   |

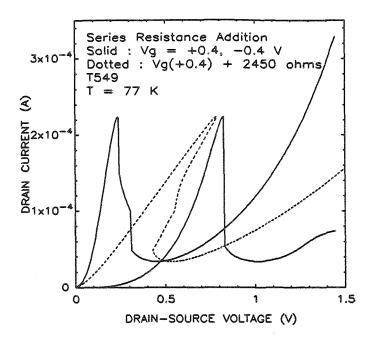

| 4.22 | Series-resistance addition model as applied to sample T549 146        |

| 4.23 | Large-scale forward-bias I-V data for T573                            |

| 4.24 | Large-scale reverse-bias I-V data for T573                            |

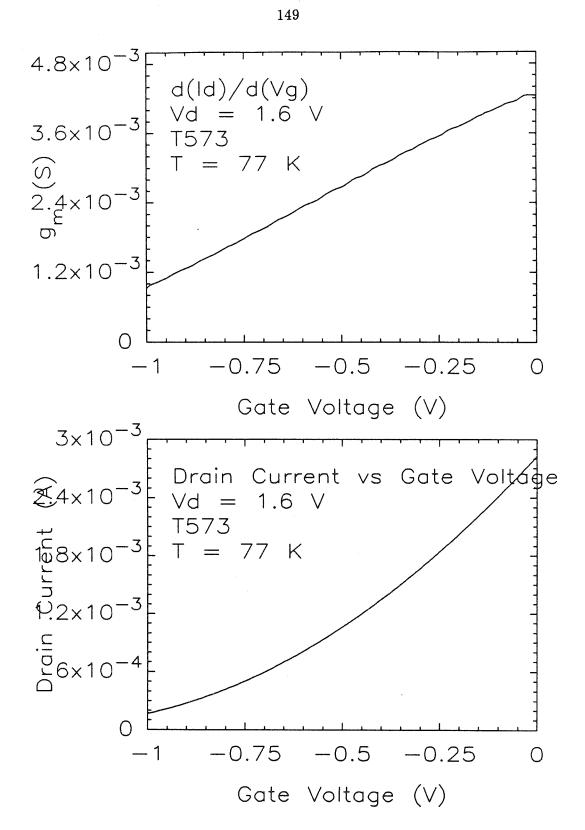

| 4.25 | $dI_d/dV_g$ vs. $V_g$ and $I_d$ vs $V_g$ for T573 at 77 K             |

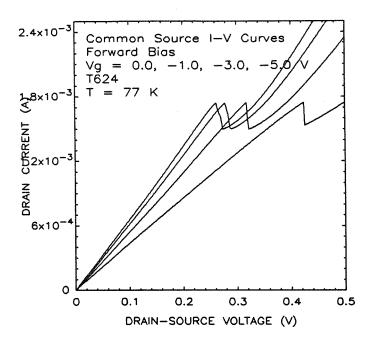

| 4.26 | Forward-bias common-source I-V data for T624                          |

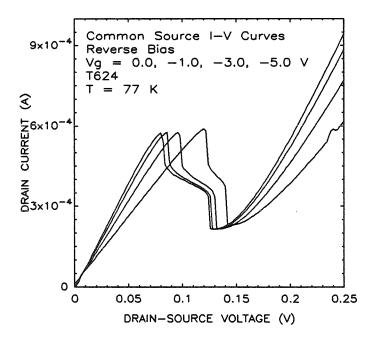

| 4.27 | Reverse-bias common-source I-V data for T624                          |

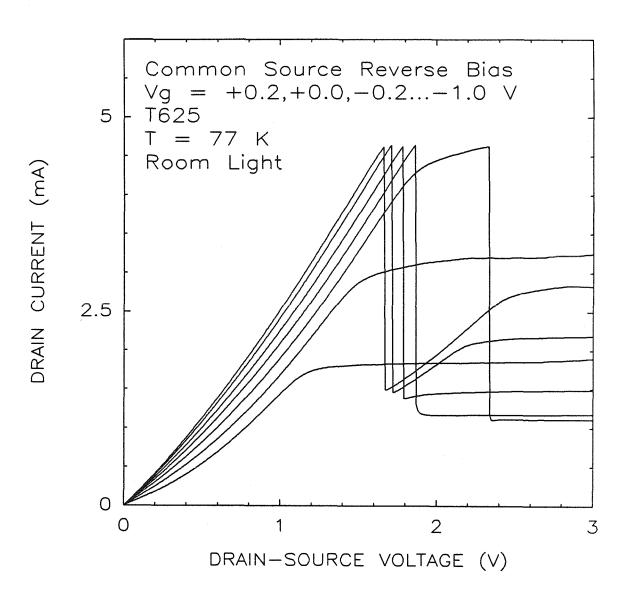

| 4.28 | Reverse-bias common-source operation of T625                          |

| 5.1  | Circuit diagram for flip-flop and frequency multiplier 161            |

| 5.2  | I-V curves for a T640 flip-flop                                       |

| 5.3  | Input-output oscilloscope data for a flip-flop fabricated from sample |

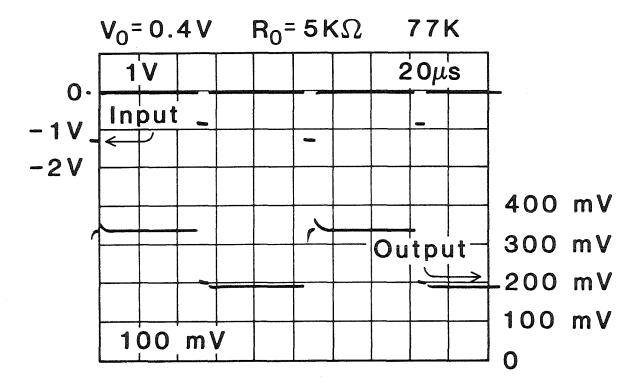

|      | T640                                                                  |

| 5.4  | I-V data for sample T573 appropriate to flip-flop operation 165       |

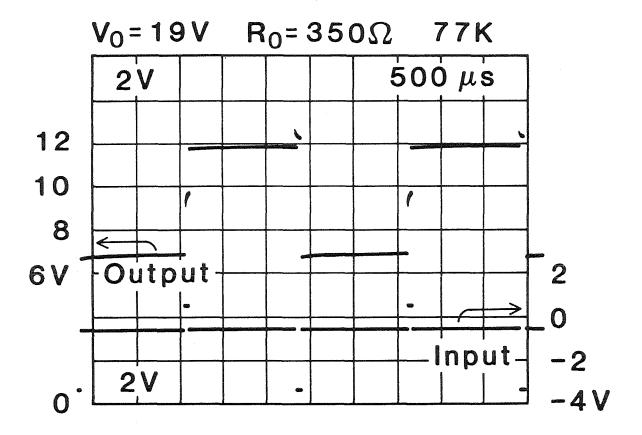

| 5.5  | Input-output oscilloscope data for a flip-flop fabricated from sample |

|      | T573                                                                  |

| 5.6  | T335 I-V curves appropriate to frequency doubling                     |

| 5.7  | DB/VFET frequency multiplier input-output data                        |

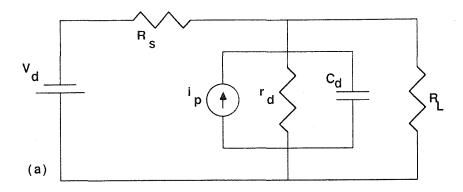

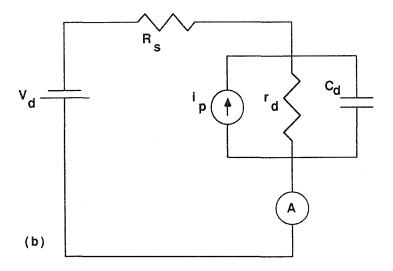

| 5.8  | Equivalent circuit for NDR oscillator                                 |

| 5.9  | 1 GHz microstrip oscillator circuit                                   |

| 5.10 | 800 MHz oscillator characteristics                                    |

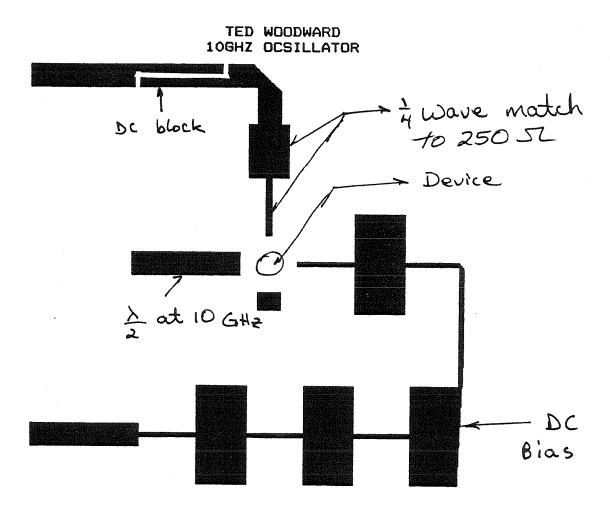

| 5.11        | 10 GHz oscillator circuit layout                                     | 183         |

|-------------|----------------------------------------------------------------------|-------------|

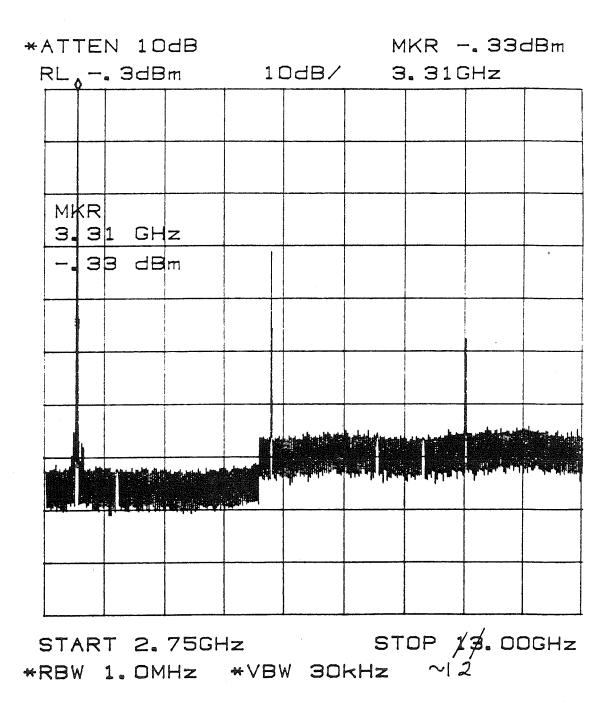

| <b>5.12</b> | Wide-band spectrum analyzer data for a microstrip oscillator made    |             |

|             | with sample T335                                                     | 185         |

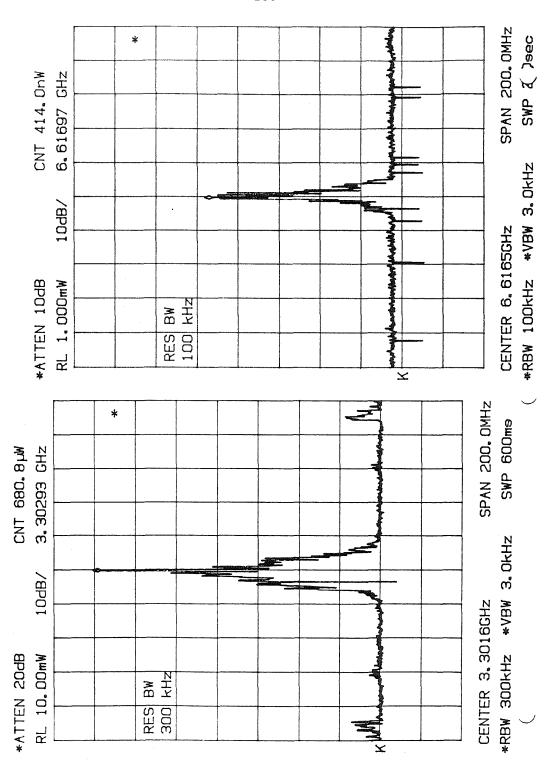

| 5.13        | A closer view of the fundamental oscillation of the 3.3 GHz oscilla- |             |

|             | tion of sample T335                                                  | 186         |

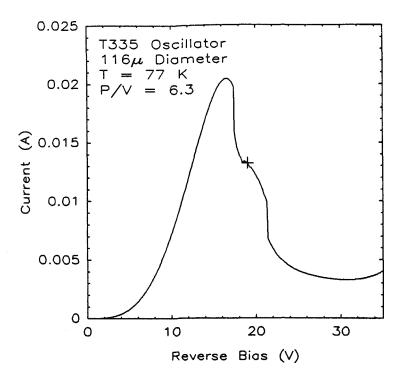

| 5.14        | DC $I-V$ curve for 116 $\mu$ m mesa device for T335                  | 187         |

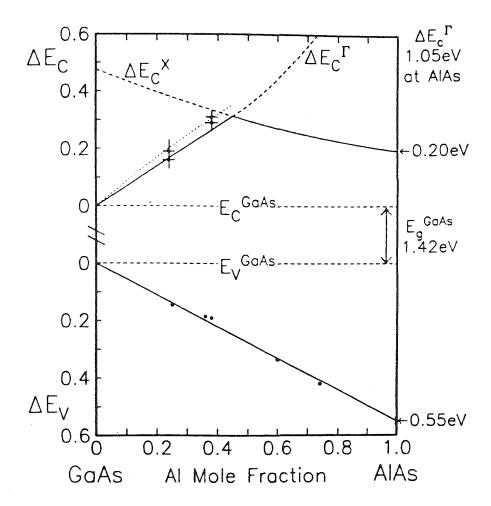

| 6.1         | Band offsets in the GaAs/Al <sub>z</sub> Ga <sub>1-z</sub> As system | 198         |

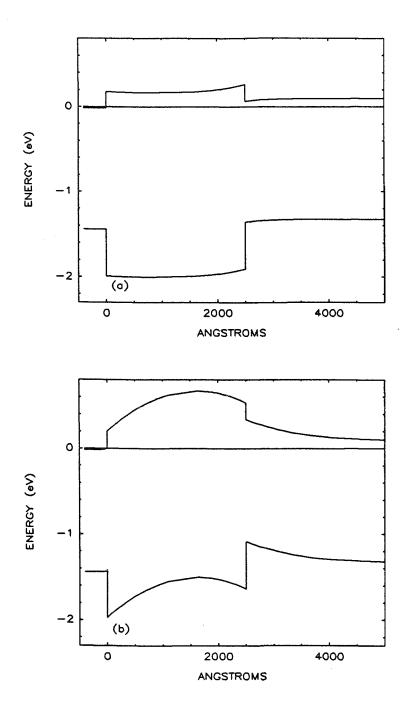

| 6.2         | Band diagrams for GaAs/AlAs/GaAs heterostructures                    | 200         |

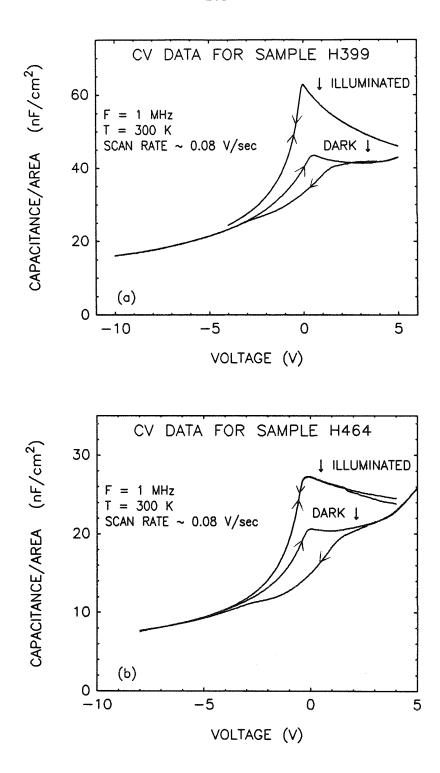

| 6.3         | Representative $C-V$ data for single-barrier samples                 | 203         |

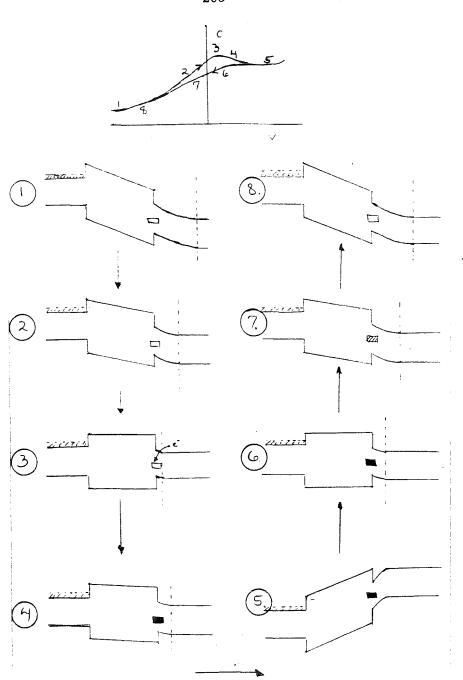

| 6.4         | Schematic explanation of capacitance hysteresis                      | 205         |

| 6.5         | Slowly scanned $C$ - $V$ data for sample H399                        | 207         |

| 6.6         | Pulsed-illumination $C-V$ data for sample H399                       | 210         |

| 6.7         | Elevated-temperature $C-V$ data for sample H399                      | 212         |

| 6.8         | 300 K and 77 K $C-V$ data for two samples                            | 213         |

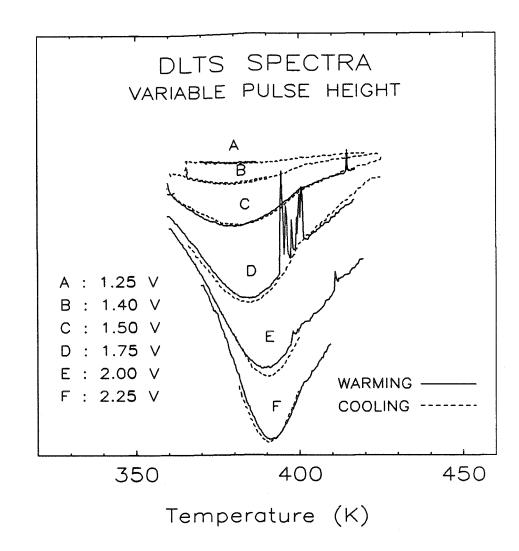

| 6.9         | DLTS trap signatures at a variety of pulse heights                   | 219         |

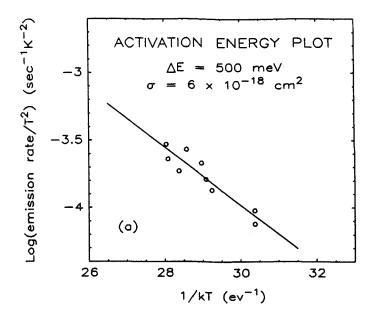

| 6.10        | Activation energy plots for samples H464 and H399                    | 221         |

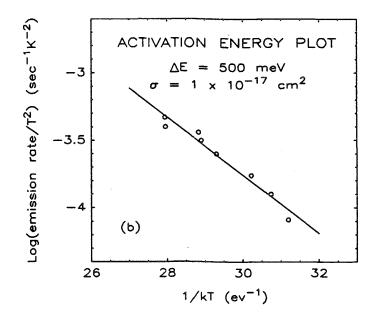

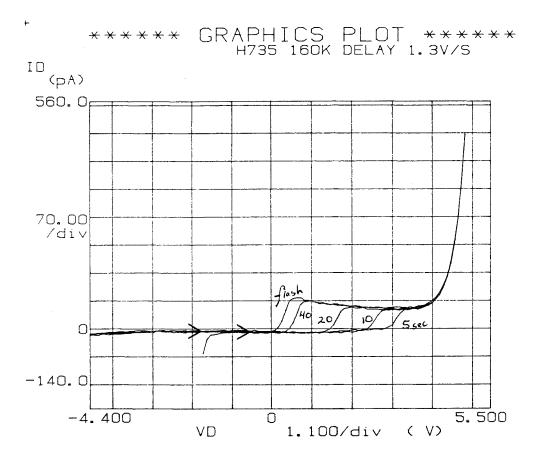

| 6.11        | I-V curve for sample H735 taken in darkness                          | 223         |

| 6.12        | Time-delay measurements of the $I-V$ hysteresis                      | <b>22</b> 5 |

| 6.13        | Temperature- and rate-dependent hysteresis for H735                  | 227         |

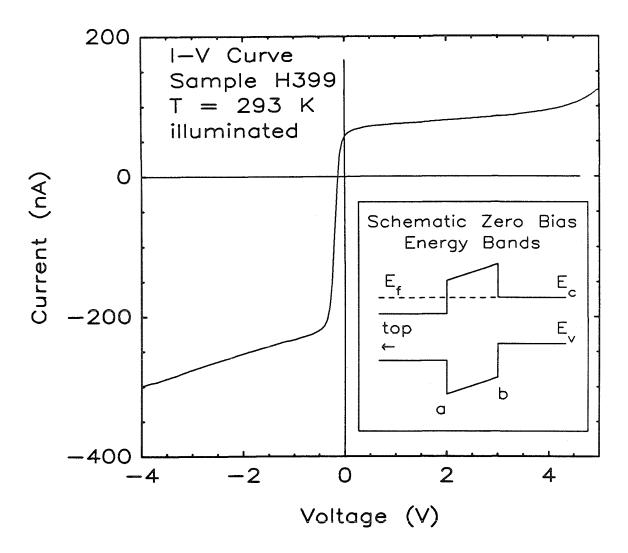

| 7.1         | Illuminated $I-V$ data for sample H399 at room temperature           | <b>23</b> 8 |

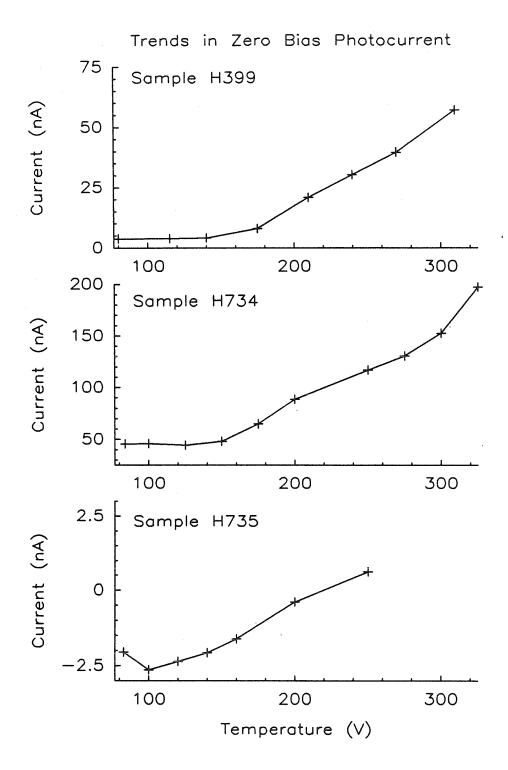

| 7.2         | Trends in zero-bias photocurrent for samples H734, H399, and H735    | 241         |

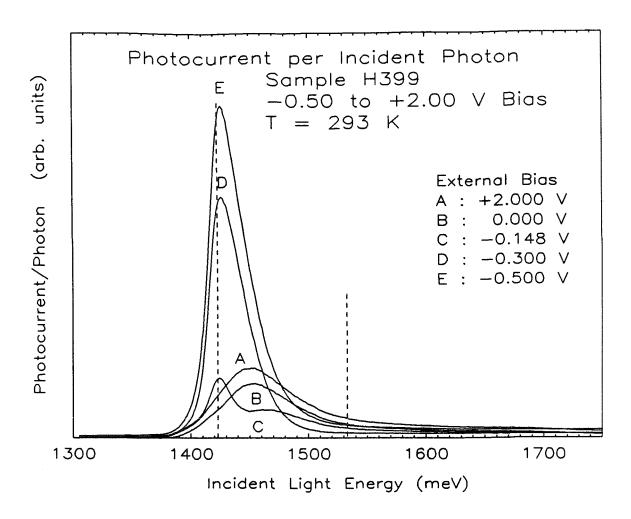

| 7.3         | Photoresponse versus incident photon energy for H399                 | 244         |

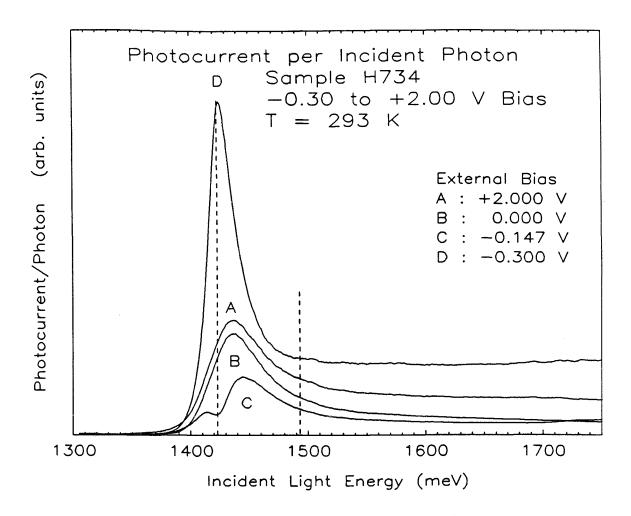

| 7.4         | Photoresponse versus incident photon energy for sample H734          | 245         |

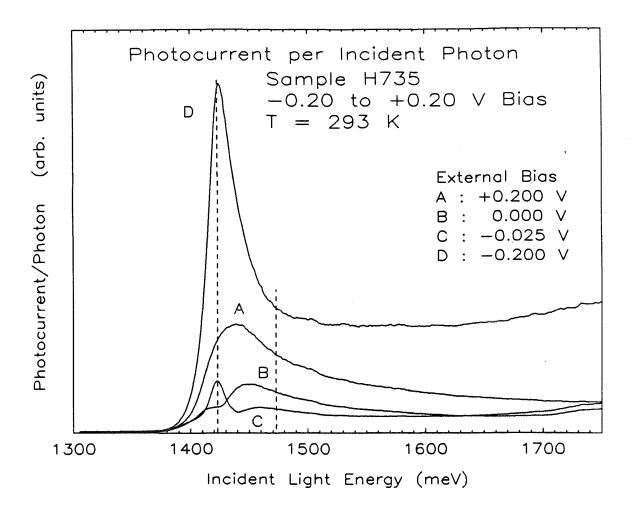

| 7.5         | Photoresponse versus incident photon energy for H399                 | 246         |

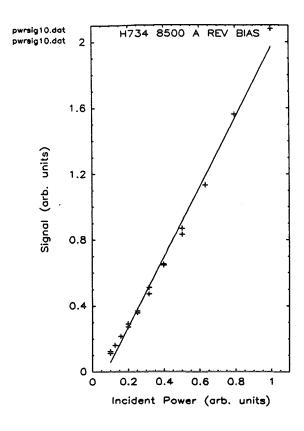

| 7.6         | Signal versus power for one sample at 300 K                          | 247         |

| B.1 | Externally | biased | photov | oltage | and | photocui | rrent m | neasur | ement | cir- |       |

|-----|------------|--------|--------|--------|-----|----------|---------|--------|-------|------|-------|

|     | cuits      |        |        |        |     |          |         |        |       |      | . 259 |

# List of Tables

| 2.1 | Geometry for MBE double-barrier growths                        |

|-----|----------------------------------------------------------------|

| 3.1 | Important parameters for T245 and T335 83                      |

| 3.2 | Table of DB/VFET double-barrier parameters                     |

| 3.3 | Table of DB/VFET channel parameters                            |

| 3.4 | Table of DB/VFET sample operation                              |

| 4.1 | Table of double-barrier growth information for DB/MESFET sam-  |

|     | ples                                                           |

| 4.2 | Table of MESFET growth information for DB/MESFET samples . 155 |

| 4.3 | Table of DB/MESFET operating parameters                        |

| 4.4 | Comments on the performance of DB/MESFET samples 157           |

| 6.1 | Physical parameters for selected single-barrier samples        |

# Chapter 1

# Introduction and Overview

This thesis is concerned with the experimental study of two types of semiconductor devices. One project is concerned with the realization of three-terminal devices utilizing the novel properties of the double-barrier tunnel structure. The second project is an investigation into the basic properties of thick single-barrier GaAs/AlAs/GaAs capacitors. Both the double barrier and the capacitor can be classified as heterostructures, or composite devices consisting of more than one semiconductor material. These materials are usually arranged atop one another in layers that have a definite crystalline registration to one another.\* The experimental results reported here are confined to GaAs/Al<sub>x</sub>Ga<sub>1-x</sub>As heterostructures.

This chapter serves as an overview and summary of the document. It explains some of the reasons for doing the work and describes the major results. In Section 1.1 the major results are briefly summarized. Following this is Section 1.2, a brief explanation of the importance of heterostructure devices to modern microelectronics. Three-terminal device research is covered in Section 1.3, and single-barrier research in Section 1.4.

Referred to as epitazial layers.

## 1.1 Results Summary

Two types of new transistor structures have been successfully demonstrated. Both are integrations of double-barrier tunnel structures with field-effect transistors. One combines a double barrier with a vertical field-effect transistor structure (DB/VFET). The other combines a double barrier with a planar metalsemiconductor field-effect transistor (DB/MESFET). These devices exhibit gatecontrolled negative differential resistance (NDR) in their source-drain characteristics. Results of DC characterization of the devices are described and interpreted in terms of sample geometry in Chapters 3 and 4. In particular, a wide range of characteristics can be obtained, depending upon the relationship between the double barrier and the field-effect parts of the device. Applications of these devices to logic, signal processing, and oscillators are described. Samples were produced by metalorganic chemical vapor deposition (MOCVD). MOCVD growth is rare for resonant tunneling structures, the vast majority of which are produced by molecular beam epitaxy (MBE). We have recently begun efforts to produce double-barrier tunnel structures by MBE. Some success has been achieved, which will be discussed in Chapter 2.

Single-barrier GaAs-AlAs-GaAs structures were also studied. Devices consisted of a  $1000-4000\,\text{Å}$  barrier of AlAs lying between a degenerately doped GaAs top layer and a nondegenerately doped GaAs backside layer. Capacitance-voltage (C-V) curves showed hysteresis and photosensitive behavior attributed to deep levels. Deep-level transient spectroscopy (DLTS) confirmed the presence of these levels and indicated that they are localized in the AlAs or near the interface between the AlAs and the GaAs. Current-voltage (I-V) measurements gave additional evidence for the deep levels in the form of hysteresis at low current levels. Estimates of deep level concentration obtained from all three techniques are in reasonable agreement with one another. These results are described in Chapter 6.

Finally, measurements of the photovoltage induced in the device under front side illumination were made, at a variety of external applied biases. The photovoltage measured with zero applied bias was consistent with electron transport from the back of the device to the front. Further measurements were used to explain this observation as being due to built-in voltages in the device. These experiments are explained in Chapter 7.

# 1.2 Why Heterostructures?

The electrical behavior of semiconductors can be controlled to an exquisite degree. This is why semiconductors form the basis of a technology. Greater control of the behavior of a potential electrical device can be achieved with the use of more than one semiconductor in the same device. Many of these ideas rely on the concept of band offsets. This fundamental issue is a subject of current investigation and so is somewhat controversial. It deals with the question of what happens to the potential experienced by an electron at the interface between two materials. It is commonly assumed that the change in potential occurs abruptly, resulting in potential steps (band offsets) in the valence and conduction bands that add up to the band-gap difference.

The value of heterostructures can be illustrated by considering the bipolar transistor. In an n-p-n transistor, the injection of electrons from the emitter into the base is desirable. The injection of holes from the base into the emitter is undesirable, representing base-emitter leakage current. The ratio of the desired injection to the undesired injection is an important quantity, defined here as  $\Gamma$ . In a conventional homojunction transistor under low injection conditions, ignoring diffusion constants and length factors, it is related to the doping concentration on either side of the junction, and the difference in potential energy across the

junction:

$$\Gamma \sim rac{n_p}{p_n} = rac{n_n e^{q(V-V_{bi}^n)/kT}}{p_p e^{q(V-V_{bi}^n)/kT}},$$

where  $n_n$  is the electron concentration in the n type emitter,  $n_p$  is the electron concentration in the p type base,  $V_{bi}^n$  is the barrier height for electrons between emitter and base, and V is the amount of forward-bias voltage, with similar definitions for holes. In an ordinary bipolar transistor the exponential factors are the same and we are left with  $\Gamma = n_p/p_n = n_n/p_p$ . Large values of  $\Gamma$  therefore impose a number of design constraints on the transistor, particularly on base doping level.

Consider a case in which the n-type emitter is made from a wider band-gap material than the base. Assuming that the smaller energy gap lies within the larger (a type I heterojunction), the potential steps in the conduction and valence bands combine to yield an increased barrier for hole injection. Now the ratio of injected electrons to injected holes is roughly:

$$\Gamma \sim rac{n_p}{p_n} = rac{n_n}{p_p} \left( e^{q \; \Delta E_g/kT}

ight),$$

where  $\Delta E_g$  is the difference in band-gap between the two materials. For semiconductors with large band offsets the improvement in  $\Gamma$  can be quite significant. Such a device is called a Heterojunction<sup>†</sup> Bipolar Transistor (HBT).[1]

This example illustrates what can happen when an additional degree of freedom is introduced; in this case the adjustability of hole and electron barrier heights across a p-n junction. In addition to improving the performance of conventional devices, altogether new devices can be constructed with the new freedoms provided by heterostructures. The geometry of interest here is the resonant tunneling double-barrier structure.

<sup>&</sup>lt;sup>†</sup>A heterojunction is a single interface between two semiconductors. A heterostructure contains an arbitrary number of heterojunctions.

## 1.3 Resonant Tunneling Transistors

## 1.3.1 Double Barriers

A double-barrier heterostructure consists of a thin (about 50 Å) layer of narrow band-gap material separated from electrodes by two equally thin layers of wider band-gap material. GaAs and  $Al_xGa_{1-x}As$  are the two materials commonly used for the narrow and wide band-gap materials, respectively. The thin GaAs region forms a quantum well, the thin nature of which gives rise to quasi-bound states. Because the barrier regions are also thin, there is a significant probability that carriers will tunnel out of the well region. Therefore the states in the well cannot be considered true bound states, but should be viewed as resonant energies for transmission from one electrode region to the other. Transport through the structure in this ideal case is via quantum-mechanical tunneling. The most interesting feature of the device is the existence of a negative differential resistance (NDR) in its I-V characteristic.

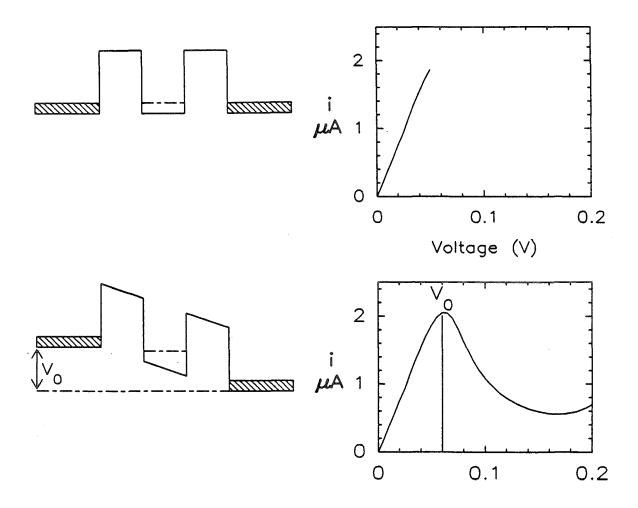

A simple model of the device illustrates the origin of the NDR. For simplicity, consider the problem one-dimensionally, and assume that energy is conserved during carrier transport. For electrons in the left electrode to tunnel through the resonance level into the right electrode (referred to as resonant tunneling), two conditions must be satisfied. First, there must be an occupied electronic state in the left electrode with the same energy as the resonance level (in which there must be an empty state). There must also be an empty state in the right electrode at the same energy as the resonance level. For small amounts of applied bias, both conditions can be satisfied, and resonant tunneling is allowed. At a critical bias the first condition will no longer be satisfied, due to band bending of the resonance level below the conduction band of the left electrode region. The result is an abrupt decrease in the current. This process is schematically illustrated in Fig. 1.1.

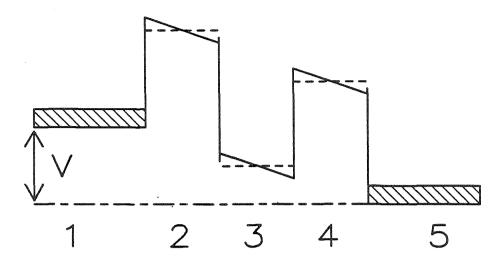

Figure 1.1: I-V curves and conduction-band diagrams for for the double barrier. The top pair of diagrams illustrates the zero-bias band diagram and I-V curve for low bias levels. For low biases, electrons may tunnel through the resonance level. The bottom band diagram and I-V curve illustrate the resonance-voltage band diagram and the entire I-V curve. When the resonance level is brought to the same energy as the conduction-band edge of the left electrode, resonant tunneling is quenched, and negative differential resistance is observed.

In the world of microelectronics, 'small' often translates into 'fast,' and fast is good. By this analysis the double barrier, with critical dimensions of about 100 Å, should be the very good indeed. In fact, the potential for high-speed devices is the driving force behind most of the double-barrier research done today. In practice, things are not so simple. Practical constraints such as capacitive charging effects and unknowns such as tunneling transit times cloud the issue of the ultimate speed of the double barrier. Theoreticians have taken many approaches to the double barrier is contained in Chapter 2.

Experimental results have demonstrated that carrier transport through the double barrier can be very fast. Oscillator structures operating at millimeter wave frequencies (56 GHz, 102 GHz, and 200 GHz) have been demonstrated, with predictions of 600 GHz devices.[2,3] Terahertz (1 THz = 1 × 10<sup>12</sup> Hz) response of the double barrier has been measured.[4] At this point it seems clear that the double barrier is a high-speed device. Exactly how fast is unclear. Oscillators and amplifiers are therefore a clear area of interest for the double barrier. Another potential area of application is in logic and digital systems.

## 1.3.2 State of the Art

Resonant tunneling was first experimentally observed in the derivative of an I-V curve of a double-barrier heterostructure in 1974.[5] Since then, great strides have been made. In 1983 the first observation of room temperature NDR was made.[6] These results were obtained with heterostructures grown by MBE. In 1984 NDR was reported in a structure grown by metalorganic chemical vapor deposition (MOCVD).[7,8,9] The results described in this thesis were obtained with samples grown by MOCVD.

A figure of merit for the double barrier is the peak-to-valley (P/V) current

ratio of the NDR, obtained by dividing the current at the peak of the NDR by the minimum current at voltages greater than the peak voltage. This ratio qualitatively measures the sharpness of the resonance and the amount of current due to mechanisms besides resonant tunneling. A peak-to-valley current ratio of 21.7 has been reported for an MBE grown (Ga,Al)As double barrier at 77 K. This ratio fell to 3.9 at 300 K.[10] For comparison, tunnel diodes—an older kind of NDR device formed from p<sup>+</sup>n<sup>+</sup> diodes—had maximum oscillation frequencies of about 100 GHz, in devices with P/V current ratios of about 7.[11] P/V current ratios exceeding 20 have been reported for GaAs tunnel diodes.[12]

Uniform and abrupt interfaces are critical to the successful growth of a double-barrier structure. [13] Equally important for good operation of the device is the cladding-layer geometry on either side of the barrier. The most successful room-temperature device operation has been achieved with the placement of undoped or lightly-doped spacer layers on either side of the double-barrier heterostructure. [10,14,15] These spacer layers apparently reduce impurity and thermally assisted tunneling, which tend to reduce the NDR P/V current ratio, particularly at room temperature. Spacer layers are discussed further in Chapter 2.

A highly desirable feature in a system for double-barrier growth is a large conduction-band offset. Thus, the GaAs/AlAs materials system may not be the ideal system for double-barrier growth. It has been used extensively because it is technically well understood compared to many other systems. A number of other systems have produced working double barriers. These include HgTe/CdTe[16] and its alloys, InP/GaAs and alloys[17], and In<sub>x</sub>Ga<sub>1-x</sub>As/In<sub>x</sub>Al<sub>1-x</sub>As systems.[14] Of these, the (In,Ga,Al)As system appears very promising. The largest P/V current ratios yet reported have been achieved in an AlAs/In<sub>x</sub>Ga<sub>1-x</sub>As/AlAs double barrier.[18] This ratio was an impressive 14 at 300 K, and increased to 35 at 77 K.

For high-speed applications a very important value is the current density passing through the structure. The current density is usually reported at the peak of the NDR and represents the ability of the device to modulate charge rapidly. Values in the 10<sup>4</sup>A/cm<sup>2</sup> range have been reported.[2,14] This value is adjustable by varying barrier thickness as well as by modifying the thickness and doping of cladding layers surrounding the double-barrier structure.

## 1.3.3 Introduction to Three-Terminal Devices

The ability to isolate input from output, the added flexibility of a third controlling electrode, and the possibility of amplification are all reasons for preferring three-terminal devices to two-terminal ones. It can be argued that the double-barrier structure would benefit from the addition of a third electrode, especially for logic and signal-processing applications. Oscillators might also benefit from the additional electrode. Additionally, virtually all NDR devices are two-terminal in nature; a three-terminal device exhibiting NDR would be unique. These issues notwithstanding, the structures would likely be interesting of themselves.

The goal of a three-terminal negative-resistance device is the modulation of the negative resistance with a third electrode. A variety of ways of doing this have been proposed. [19,20,21,22] All of the ideas that have resulted in functioning devices have combined the double-barrier structure with a more conventional device. Double barriers have been combined with bipolar transistors [20,23], hot-electron transistors [22], and field-effect transistors [21,24,25] to form a new class of device; the resonant tunneling transistor (RTT). Trade-offs between the various devices are discussed in Chapter 2. The two types of devices described below were first proposed by Bonnefoi et al. [19,26,27]

Changing the resistance of one of the electrode regions of the double barrier will

alter the applied voltage at which the resonance condition<sup>‡</sup> is satisfied. Varying amounts of bias will have to be applied to the entire device to satisfy the resonance condition across the double barrier, due to the changing series resistance. The electrode resistance can be varied by placing a field-effect transistor in series with the double barrier. This effect could be achieved with lumped elements and wires. By integrating the two devices into a single semiconductor device, two advantages are accrued. First, parasitic effects are reduced. In fact, as will be seen, the double barrier becomes part of the transistor structure. Second, a more fundamental interaction between the devices becomes possible. An excellent example of this kind of interaction, in this case involving two p-n junctions, is provided by the bipolar transistor.

## 1.3.4 DB/VFET Devices

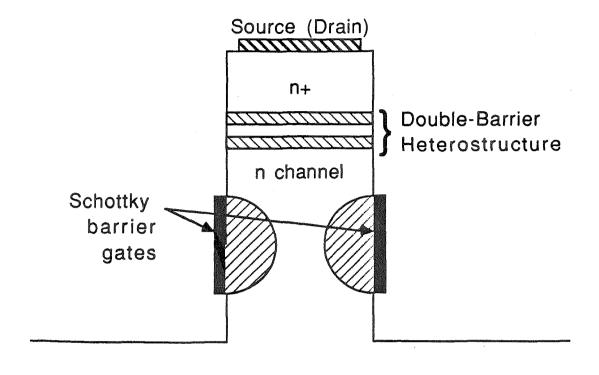

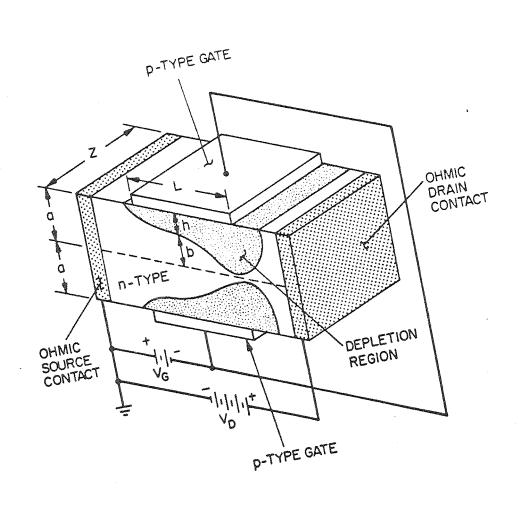

This section presents an overview of the project to integrate a double barrier with a vertical field-effect transistor. The device is simple in concept. A lightly-doped electrode region is pinched off by Schottky barriers placed along its vertical sides in a manner similar to a junction field-effect transistor (JFET).[28]

The ideal DB/VFET device would place electrodes on the sides of a vertical mesa structure; a formidable fabrication challenge. Devices of this type have been made. They are quite intricate, and capable of operation at about 70 GHz.[29,30] In order that our device be fabricated with simple techniques, many design modifications were made. These are described in detail in Chapter 3. The resultant structure makes a number of sacrifices in performance, but is relatively easy to fabricate. Almost any performance improvement will require a more complex fabrication procedure.

<sup>&</sup>lt;sup>‡</sup>The resonance condition is satisfied when the device is biased such that the resonance level lines up with the conduction-band edge of the injecting electrode.

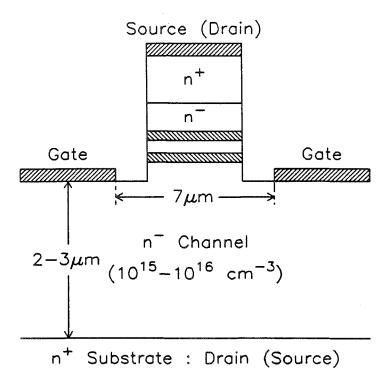

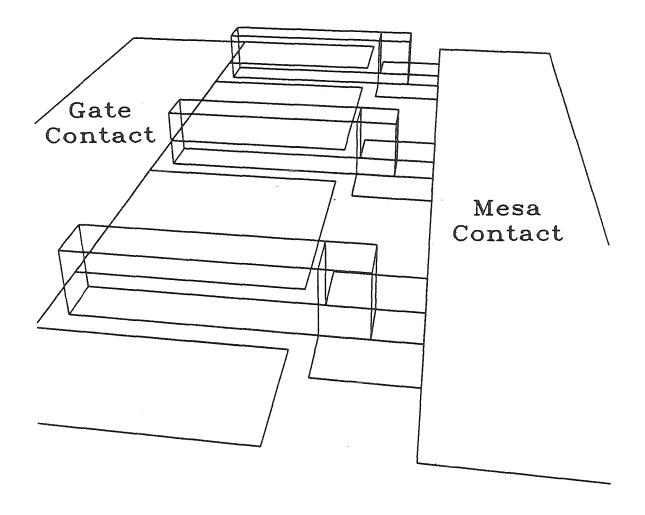

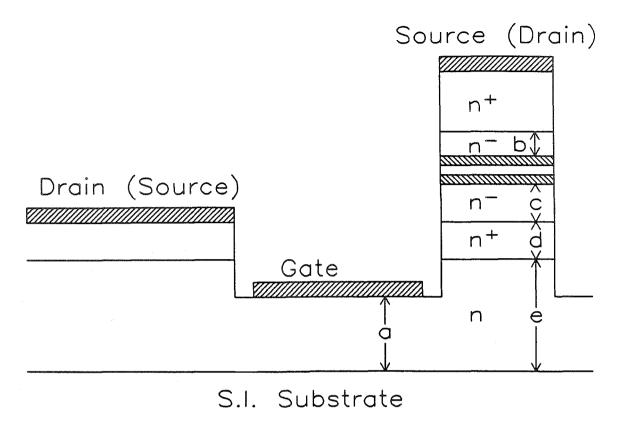

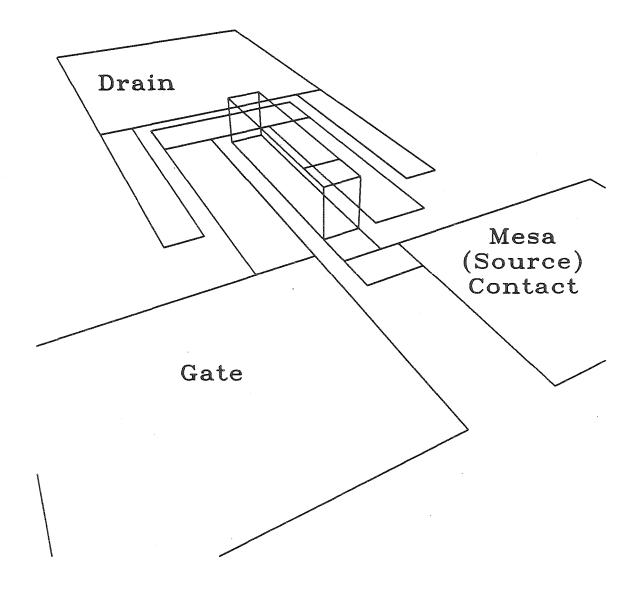

Figure 1.2: Final design of DB/VFET optimized for ease of fabrication. The tolerances for horizontal alignment are 1 micron.

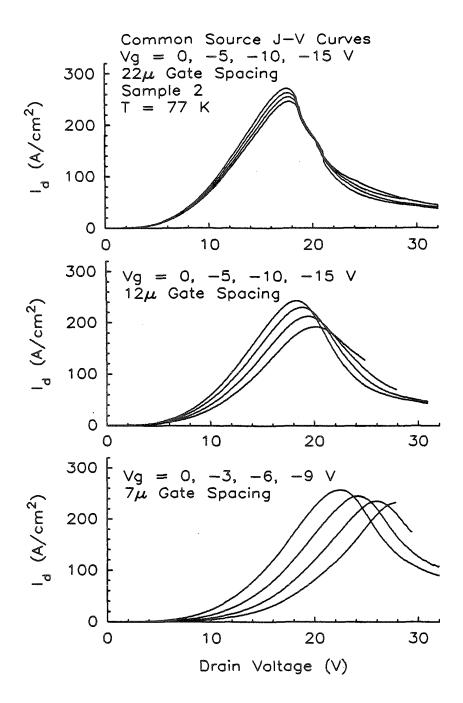

The finished device is schematically illustrated in Fig. 1.2. It places the gate electrodes on a horizontal rather than vertical surface and relies on horizontal spreading of the primarily vertical depletion region under the gate to vary the resistance of the channel region. This design imposes stringent requirements on mesa width, gate spacing, and channel doping. One would like to have a thick, lightly-doped channel, a very narrow offset between the gate and the mesa containing the double barrier, and a very narrow mesa. More details are given in Chapter 3.

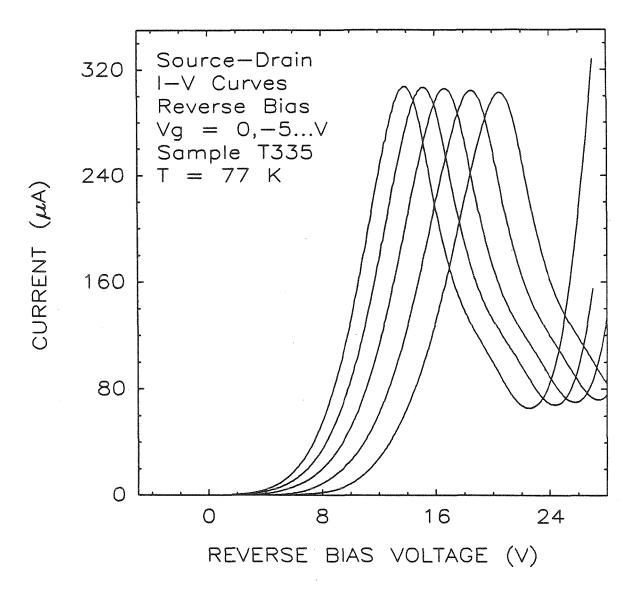

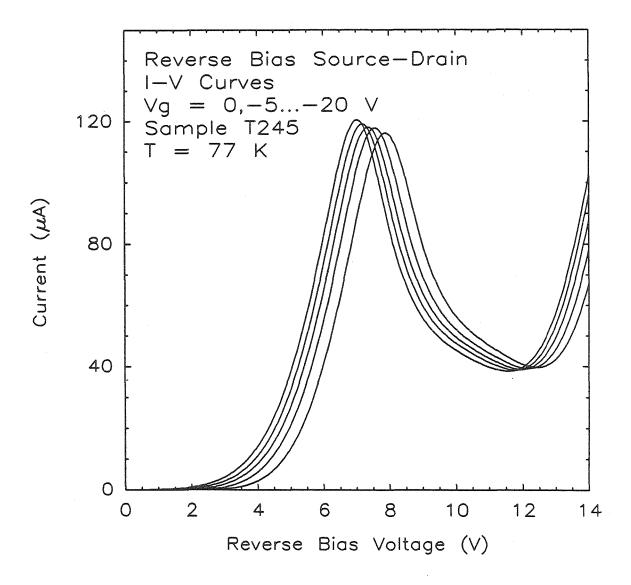

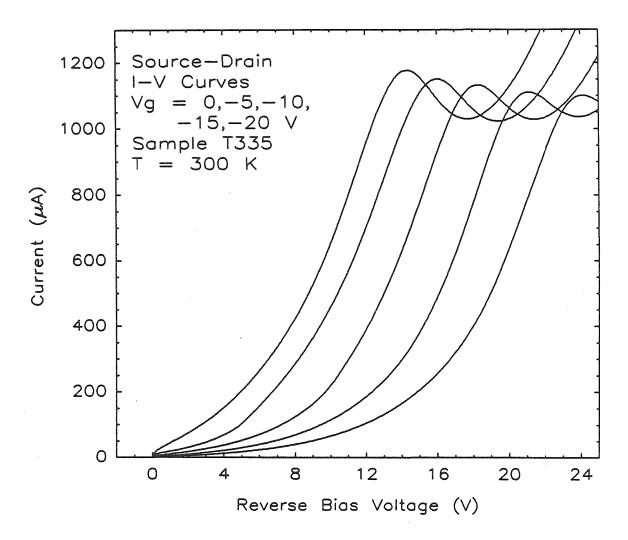

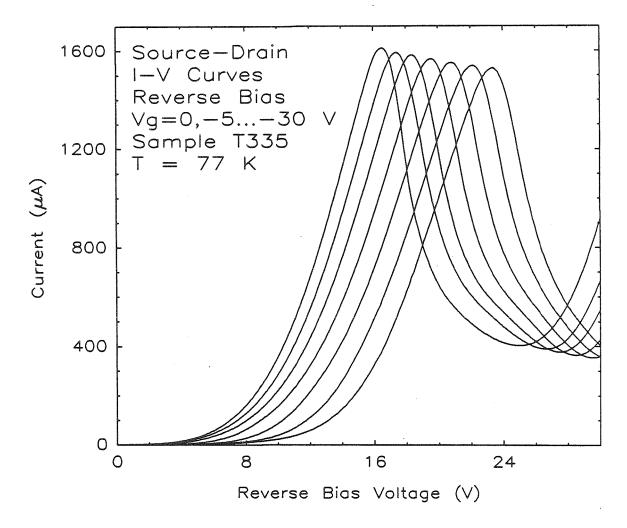

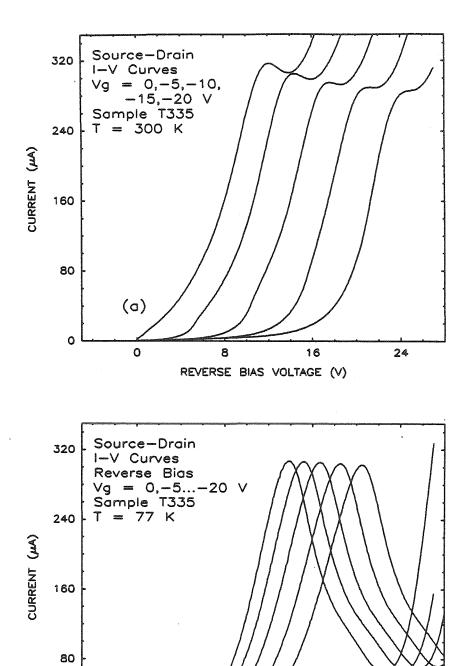

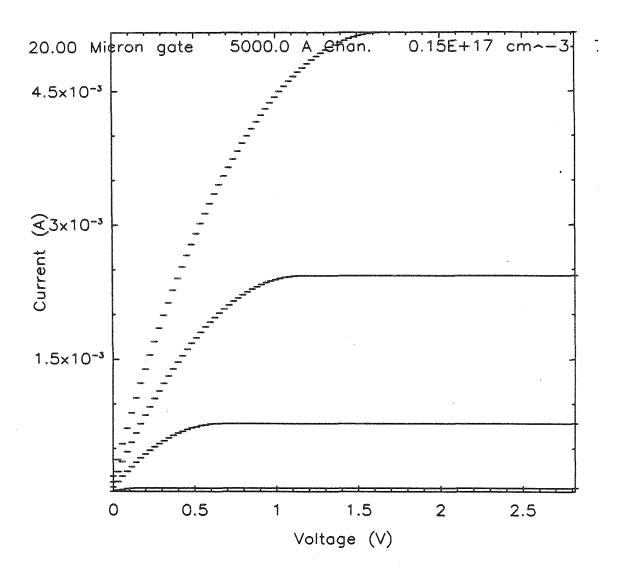

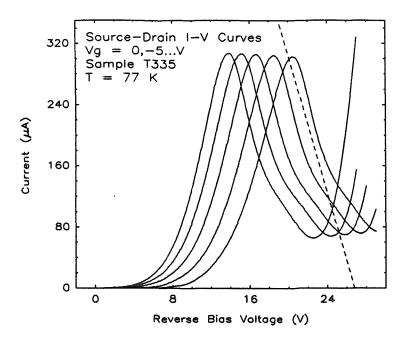

Results for a representative device are presented in Fig. 1.3. An interesting effect of the design is the high voltage at which NDR is observed. This is due to the presence of a large, lightly-doped region on one side of the double barrier. In one bias direction this region is depleted and provides a large region over which to drop bias. To satisfy the resonance condition across the double barrier, a much

larger bias must be applied across the entire device. It should be emphasized that this lightly-doped region does not represent a large series resistance, but rather forms a drift region, whose resistance can be modulated. Results for samples with different channel-doping levels show a consistent trend toward higher NDR voltage with decreasing channel doping, provided that the lightly-doped region is sufficiently thick. Modulation of the position of the NDR is achieved by the lateral extension of the gate field, and its interaction with the channel through which source-drain current flows.

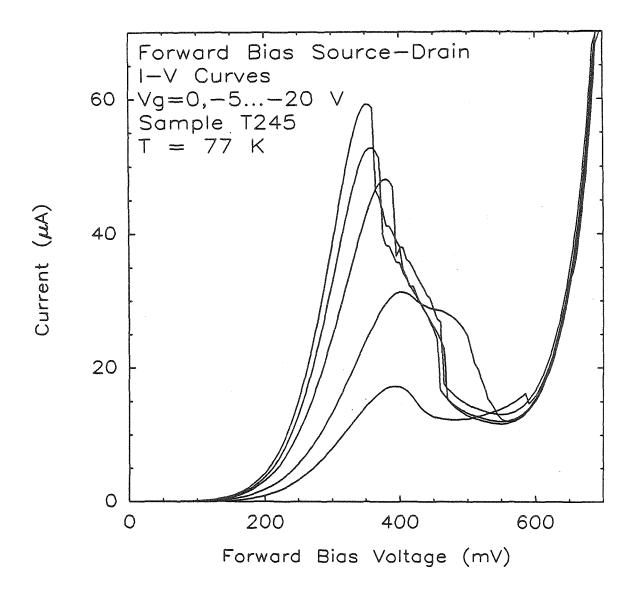

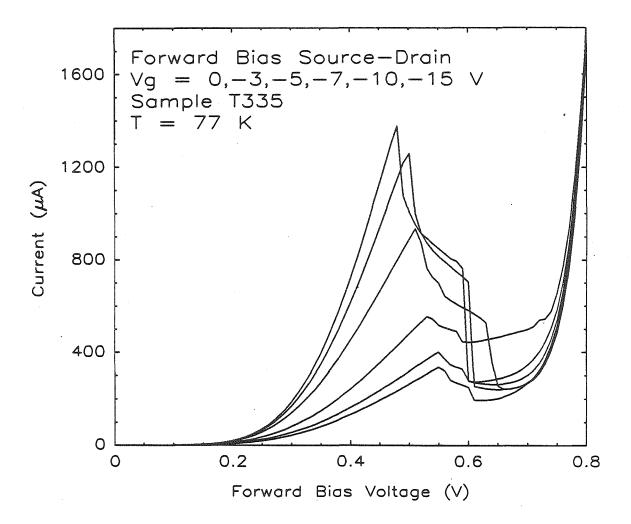

Also of interest is the operation of the device in forward bias. Qualitative differences between forward- and reverse-bias operation were observed and attributed to the differences between the two bias configurations, specifically with respect to the role played by the lightly-doped channel region. These results are discussed in Chapter 3.

Some final comments about the DB/VFET are in order. Quite interesting I-V curves can be obtained. The double barrier and the FET segments of the device interact with one another to yield I-V curves that are not what would be achieved from wiring together lumped elements, as evidenced by the production of NDR at a high voltage. Several working DB/VFETs were eventually produced. While the device is not optimized for high-speed applications, sophisticated processing could be applied to greatly improve performance, as in advanced VFET structures. [29,30]

Some interesting applications of this device have been demonstrated. One is a frequency doubler, which uses the fact that an operating point may be moved completely through the NDR region by application of gate bias. Another application is to oscillator structures; microwave oscillators have been demonstrated at 0.8 and 3.3 GHz, with an output power of about  $700\mu$ W at 3.3 GHz. An interesting potential use of the DB/VFET geometry as a transit-time device has been

Figure 1.3: I-V curves for a DB/VFET device in reverse bias. The leftmost I-V curve was taken with zero gate bias  $(V_g)$ .  $V_g$  is incremented in -5 V steps, resulting in shifts of the NDR region to larger biases.

Figure 1.4: DB/MESFET cross-sectional diagram, showing recessed-gate design.

proposed, by Kesan et al., which would be interesting to explore.[31] It should be possible to fabricate interesting logic elements with these structures as well. These topics are discussed in Chapter 5.

## 1.3.5 DB/MESFET Devices

This section deals with efforts to combine resonant tunneling diodes with planar field-effect devices, in particular a metal-semiconductor field-effect transistor (MESFET). The composite device is referred to as a DB/MESFET. This device is a logical companion to the DB/VFET.

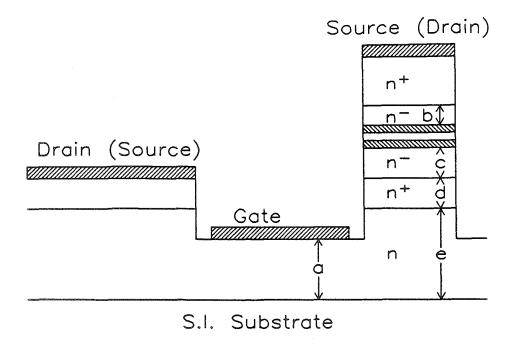

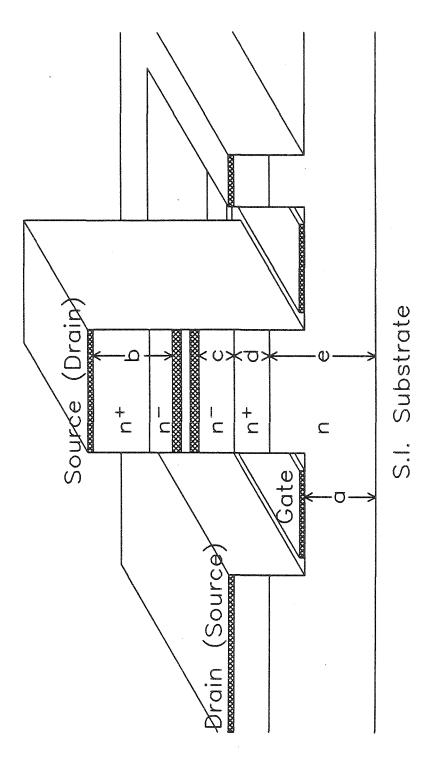

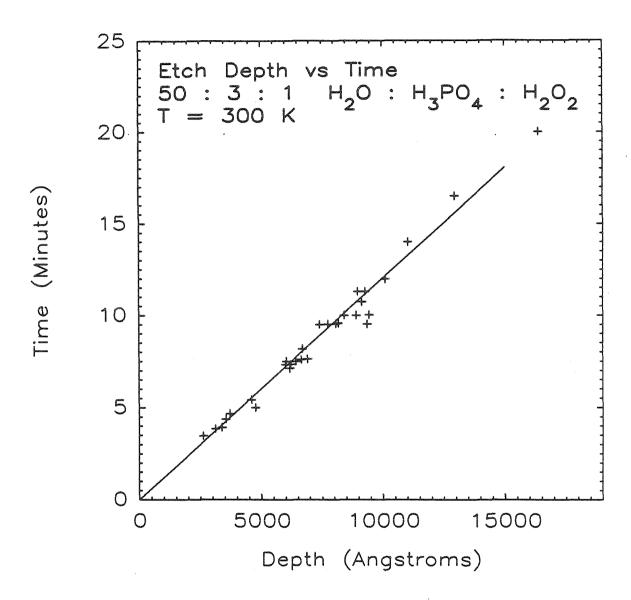

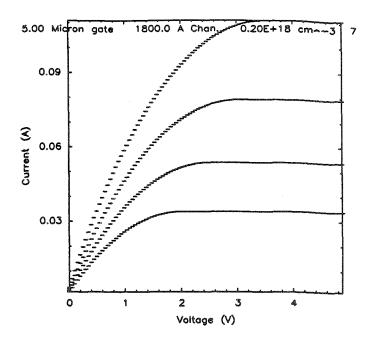

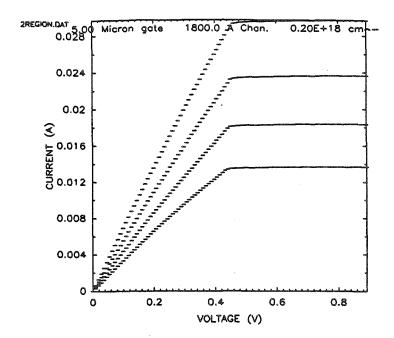

The DB/MESFET avoids the conceptual problems associated with the DB/VFET by using a planar layout. The final device is a series combination of a double barrier and a MESFET. A finished device is schematically illustrated in Fig. 1.4. Fabrication procedures for the DB/MESFET were more complex than for the DB/VFET,

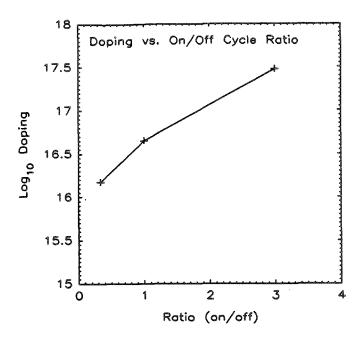

requiring 3 masks, 2 alignments, 2 etches, and 3 evaporations. The recessed-gate design was used to allow a wider latitude for channel dopings, and to ensure good ohmic contacts. Devices with channel dopings from  $1 \times 10^{16}$  cm<sup>-3</sup> to  $3 \times 10^{17}$  cm<sup>-3</sup> were made.

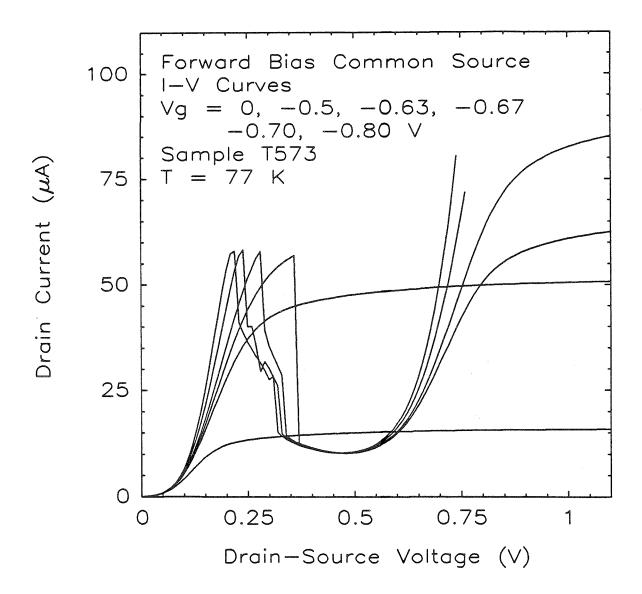

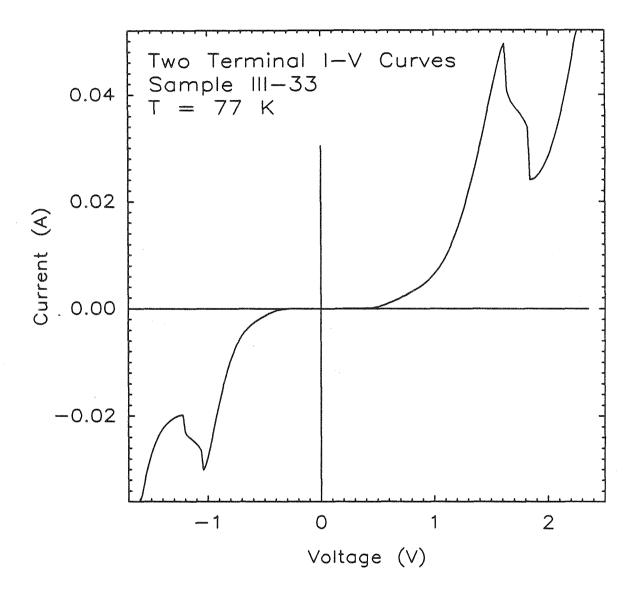

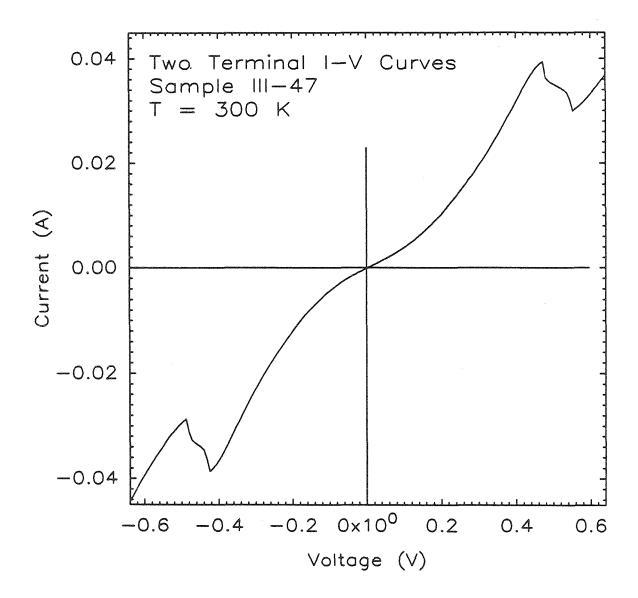

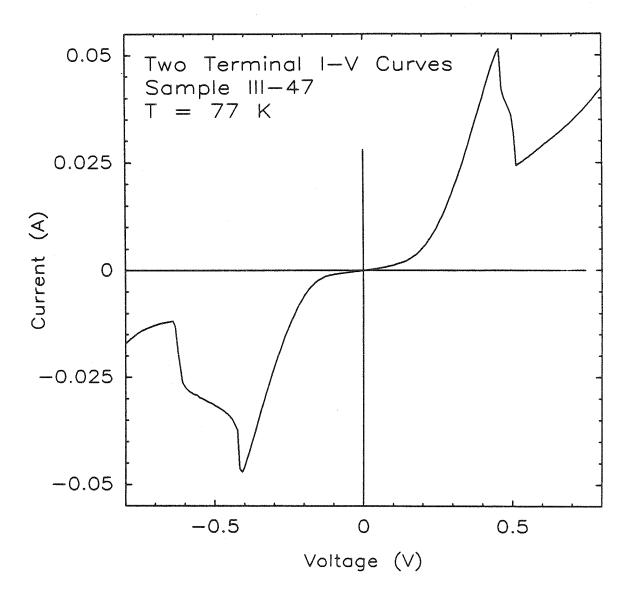

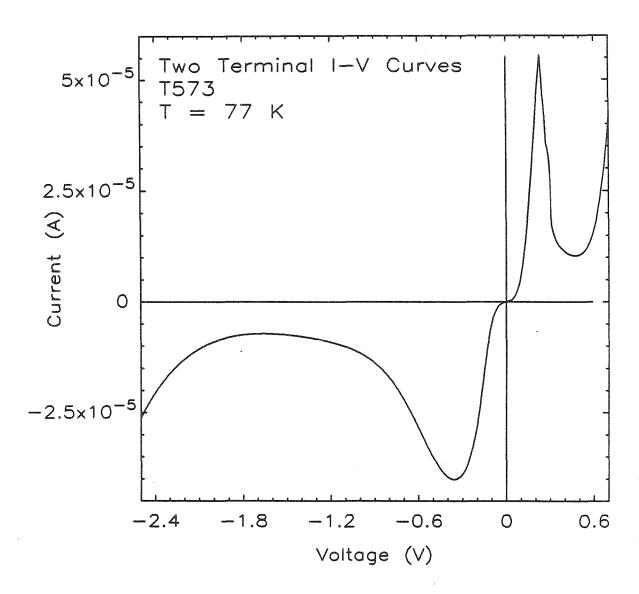

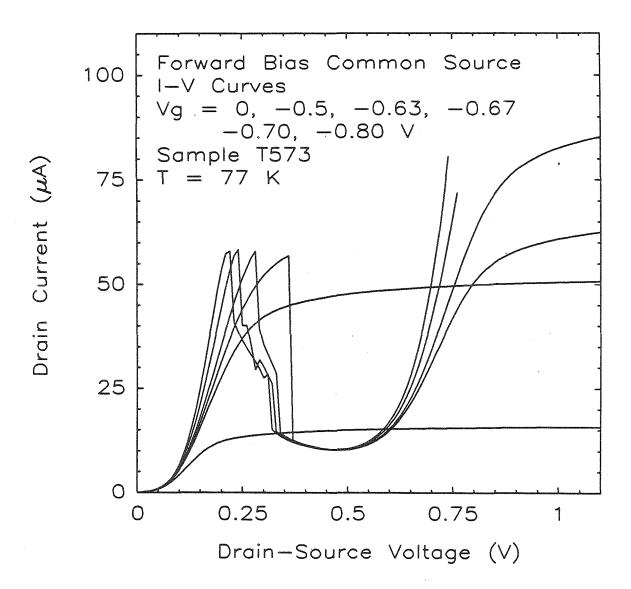

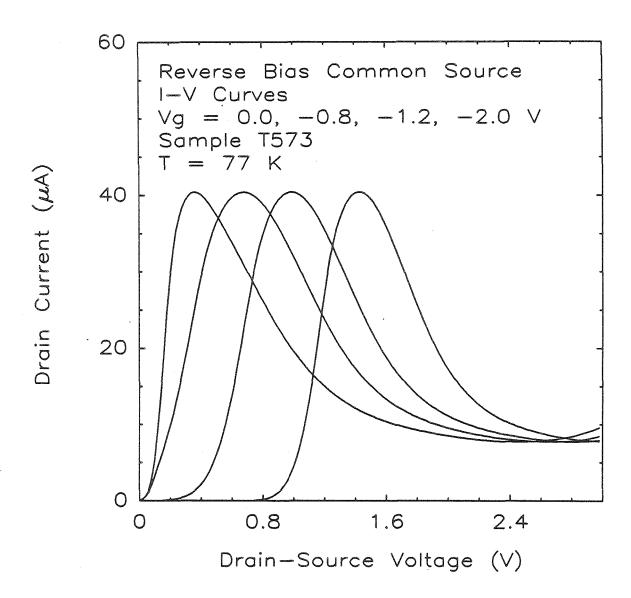

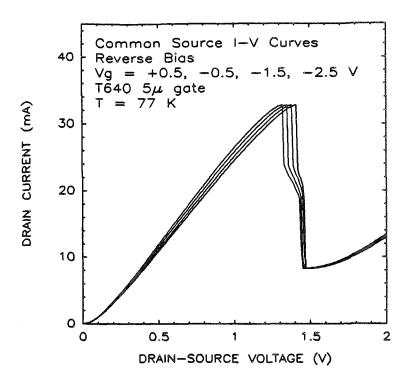

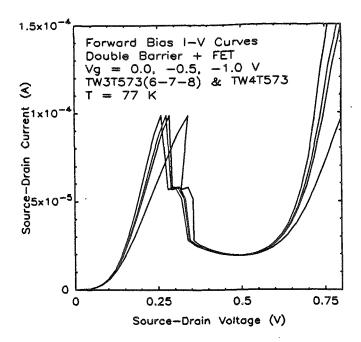

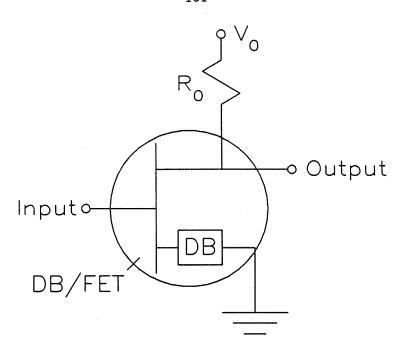

Results for a particularly instructive device are presented in Fig. 1.5. The NDR characteristic of a resonant tunneling structure is evident near zero bias, and the saturation characteristics of a MESFET are apparent at larger voltages. For zero gate bias  $(V_g)$ , the resistance of the double barrier is dominant at low drain biases  $(V_d)$ . As  $V_g$  is made more negative, the resistance of the FET portion of the device becomes comparable to the double barrier. The increased channel resistance results in a shift of the NDR to larger biases, followed by its eventual elimination, when the FET portion of the device becomes the dominant resistance. Note that shifts in the NDR begin to become significant at  $V_g = -0.5$  V; NDR is eliminated by the time  $V_g = -0.7$  V, illustrating the relative efficiency of the gate voltage in this device, as compared to the DB/VFET. The small amount of bias required to turn off the NDR may be relevant for switching applications.

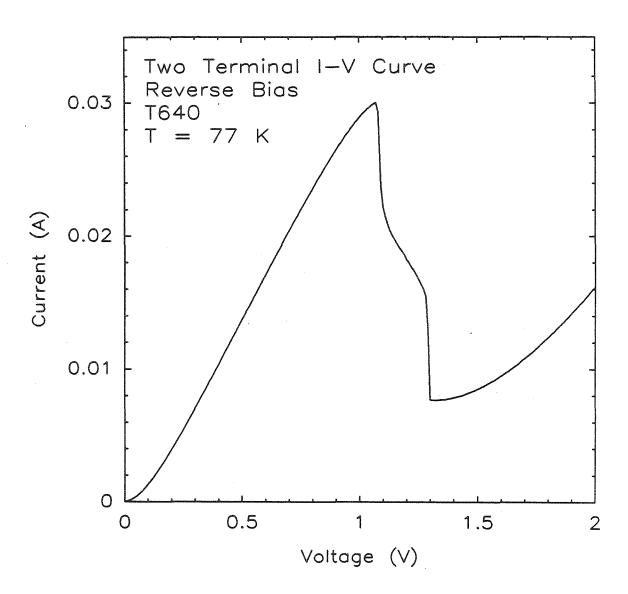

This device presents a case in which the NDR lies near zero bias, in the linear region of the MESFET. It is possible to obtain a variety of other types of I-V curves. By decreasing the well width in the double barrier, the NDR shifts to larger biases. The addition of a relatively resistive channel will shift the NDR out of the linear region of the FET, resulting in bistable hysteresis regions in the I-V characteristic. By increasing the thickness of layer 'c' in Fig. 1.4, one can obtain characteristics similar to DB/VFETs. These results are discussed in more detail in Chapter 4.

Provided that successful growth of the double barrier can be obtained, the DB/MESFET is readily amenable to existing integrated-circuit fabrication techniques, because the fabrication procedures for this device can be made virtually

Figure 1.5: Forward-bias common-source I-V curve for a DB/MESFET device. Both resonant tunneling and MESFET behavior can be seen. The NDR peak of the  $V_g = 0$  V characteristic lies closest to zero bias. As  $V_g$  is made more negative, the peak of the NDR shifts to higher biases, and is eventually eliminated, at  $V_g = -0.7$  V. The 'step' in the NDR region of the curves is due to oscillation, see also Chapter 5.

identical to MESFET fabrication techniques.

Applications for the DB/MESFET lie primarily in logic and signal processing. The same features that allow frequency multiplication in the DB/VFET should work with the DB/MESFET, too. To explore one area of interest, flip-flop circuits were demonstrated using single DB/MESFET devices. The two stable states of the flip-flop are obtained from the bistable intersection of a load-line with the negative resistance characteristic. The states are controlled with gate bias. Two DB/MESFET samples have demonstrated this operation. Additionally, many interesting applications were developed for tunnel diodes, but fell from favor due the difficulty of integrating these devices with others.[32] Some of these applications may prove feasible with DB/MESFET devices. These topics are the subject of Chapter 5.

#### 1.3.6 Conclusions

Two types of three-terminal NDR devices have been made. Both combine resonant tunneling heterostructures with field-effect devices. The two devices operate in different ways and exhibit characteristics qualitatively different from each other and from two-terminal double-barrier diodes. The devices presented here are pioneering efforts. Perhaps because of this, neither the double barrier nor the FET sections of the device is particularly remarkable or state of the art. It is their combination that is unique.

# 1.4 AlAs Capacitors

## 1.4.1 Introduction

This section presents an overview of the topics to be discussed in greater depth in Part II of this thesis. Here, we are concerned with the study of single-barrier heterostructures. The particular geometry studied here consists of a layer of AlAs several thousand angstroms in thickness, separating two GaAs regions from each other. One of these GaAs regions is degenerately doped; the other is nondegenerately doped. All doping is n type. The AlAs layer is intended to form a barrier to electron transport. This topic was studied with samples produced by MOCVD. The source of the material was Xerox Research Labs in Palo Alto, California.

There are several reasons to be interested in epitaxial barrier materials. The epitaxial nature of the barrier material allows the subsequent deposition of further crystalline structures. Crystalline regrowth is much more difficult on top of amorphous layers. Resistance to electrical conduction perpendicular to the layer, and the ability to modulation-dope the barrier create some useful device possibilities.

One of these interesting devices is the GaAs-gate field-effect transistor.[33] It depends upon the ability to accumulate electrons against an  $Al_xGa_{1-x}As$  barrier. This device has been demonstrated and has the potential to operate at very high speeds. This device is similar in concept to a silicon MOSFET. If the GaAs-gate FET could operate in inversion, a low-power consumption, high-speed logic system could be devised in GaAs, similar to the CMOS system in silicon. The  $Al_xGa_{1-x}As$  (or  $In_xAl_{1-x}As$ ) single barrier is important to several other devices, most notably the modulation-doped field-effect transistor (MODFET).[34] This device is currently one of the fastest transistor structures known.

# 1.4.2 Capacitance Measurements

In concept the  $n^+$ -GaAs/i-AlAs/n-GaAs heterostructure can be viewed as an MOS (or MIS) capacitor. The  $n^+$ -GaAs top layer behaves like a metal; the n-GaAs backside layer is semiconducting with a moderate to low carrier density. The AlAs should be a barrier; therefore, it may be either undoped, p-type, or very lightly n-type. Since this geometry would not be expected to draw a lot of current,

capacitance measurements might be informative. The theory of the MOS device is well developed. [35,36] In particular, the capacitance-voltage (C-V) behavior is well understood. Should the single barriers studied here exhibit similar C-V behavior, a GaAs-AlAs-GaAs MOSFET-like device might be possible.

All samples exhibited similar C-V behavior. Light sensitive C-V behavior was seen, with a photosensitive peak in the illuminated data being the dominant feature. The light sensitivity of the samples led to extensive nonilluminated characterization of the samples, the results of which will now be summarized.

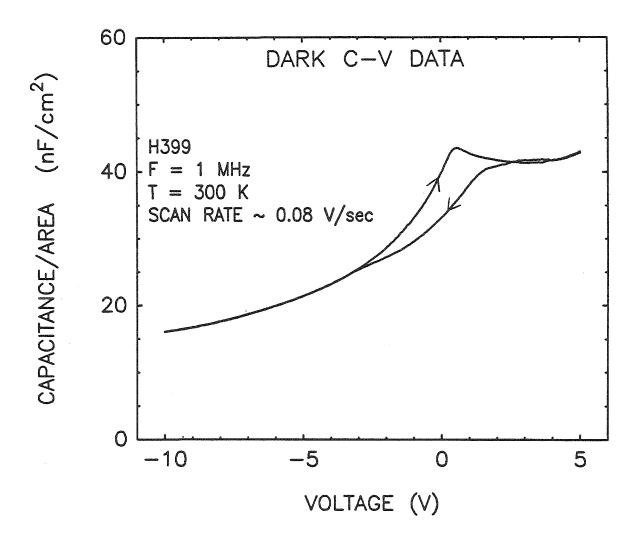

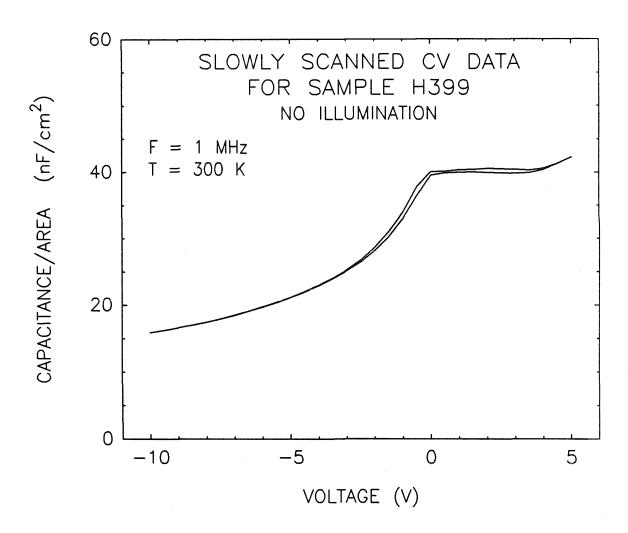

Fig. 1.6 presents data for sample H399, taken in darkness. Arrows indicate the direction of bias sweep, and the rate of data acquisition is indicated. A dramatic drop in the size of the illuminated capacitance peak was observed in nonilluminated C-V data. A region of relatively constant capacitance is observed in forward bias. A thickness estimate can be obtained from the equation

$$C = \frac{\epsilon}{d} \,, \tag{1.1}$$

where C is the capacitance per unit area,  $\epsilon$  is the dielectric constant of the material multiplied by the permittivity of free space,  $\epsilon_0$ , and d is the barrier thickness. The thickness predicted is 2250 Å, in fairly good agreement with scanning electron microscope (SEM) measurements of 2500 Å for the AlAs thickness and suggests that the region of constant capacitance arises due to carrier accumulation against the AlAs.

A dominant feature of the dark C-V data is the observation of hysteresis. The hysteresis is rate dependent, with slowly scanned C-V data showing very little hysteresis, and no discernible peaks in the capacitance. To understand the hysteresis, bias polarities need to be thoroughly understood. Positive voltages in Fig. 1.6 refer to positive voltage on the top  $n^+$  layer. Such a configuration is referred to as forward bias. Conversely, reverse bias occurs when negative voltage is applied to the top electrode. The nondegenerate n-type layer beneath the double

Figure 1.6: C-V data for sample H399, taken in darkness. Forward bias denotes positive bias application to the top layer of  $n^+$ GaAs. Direction of bias sweep is indicated by arrows.

barrier is depleted of carriers in reverse bias.

In the dark, for sweep rates like those illustrated in Fig. 1.6, the capacitance is higher when voltage is swept from reverse to forward bias than when swept the other way. This nonequilibrium situation is highly suggestive of the presence of a long-lived state, or deep level. Since this hysteresis does not persist for the entire C-V curve, it is reasonable to suspect that the deep levels are spatially localized.

The hysteresis can be explained by considering the effect of a large number of electron traps spatially localized near the GaAs/AlAs interface (between the lightly-doped GaAs and the AlAs). These levels would be empty in reverse bias, because there would be no electrons around to populate them. An empty electron trap carries a positive charge and will drop a certain amount of bias. When most of the traps are empty, they can make a significant contribution to the charge in the depletion layer, thus allowing a smaller amount of bulk depletion, and a higher capacitance than if they were not present. When the bias on the structure becomes zero or slightly positive, electrons accumulate near the AlAs barrier, filling the levels. When bias is then swept from forward to reverse biases, the trap levels begin to empty when the depletion edge sweeps over them, but this emptying may be a slow thermal process taking many seconds. To drop a given voltage, additional depletion of the nondegenerate material will be required as compared to the forward-going sweep. Consequently, the capacitance will be lower than the forward-going case. Eventually, the trap population reaches equilibrium, and the two curves coincide with each other.

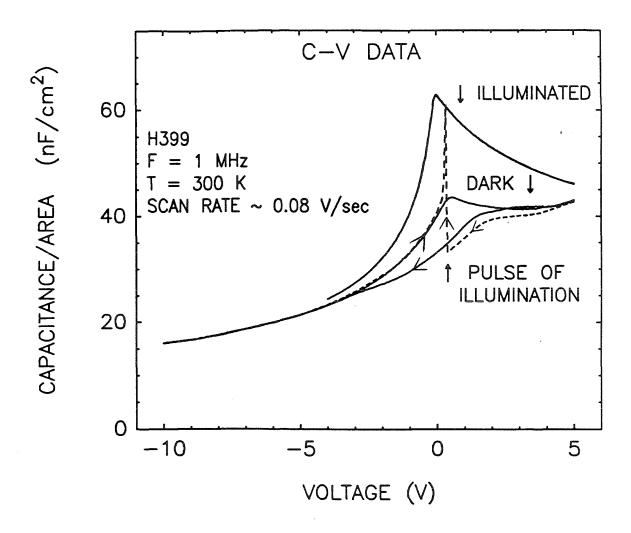

This hypothesis has been tested with the selective application of light pulses during the hysteresis. It was possible to cause the capacitance to move from

<sup>§</sup> A deep level, or trap, can be viewed as a spatially localized energy level lying in the forbidden gap of the semiconductor, typically far from the band edges. This level may have several charge states and is characterized by an activation energy and a capture cross section. See Ref. 37 for more information.

the branch of the hysteresis associated with filled trap states to that associated with empty trap states by application of a light pulse. See Chapter 6 for more information.

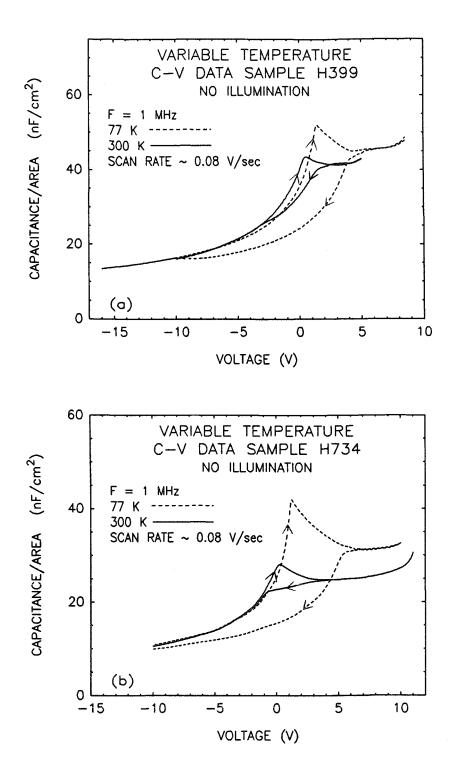

A concentration estimate for the deep levels may be made by considering the area enclosed by the hysteresis. This area can be converted to a charge, and thence to a concentration, under the assumption that all the levels fill and are emptied during the hysteresis, and that they are located at the edge of the depletion region. Values obtained at low temperature (77 K), when the hysteresis is larger, yield estimates of  $1 \times 10^{11} \, \text{cm}^{-2}$ .

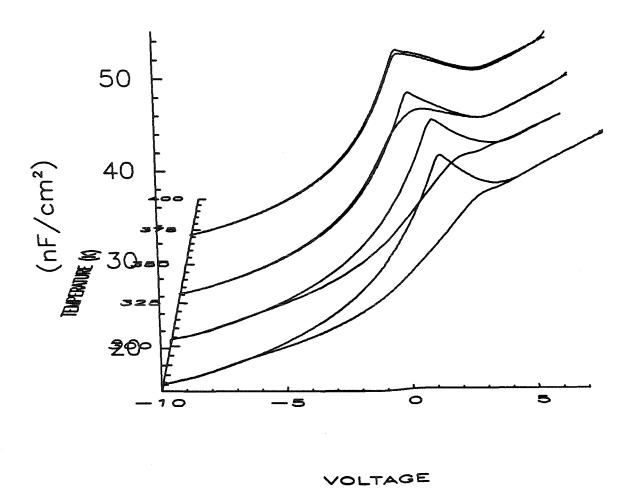

No evidence of inversion was observed in our C-V studies. Normally, a high frequency MOS C-V curve exhibits a region of constant capacitance in reverse bias corresponding to voltages at which large numbers of minority carriers are generated near the insulator interface. Since inversion is not observed, the operation of inversion-mode devices would not be possible with these structures. Many other capacitance studies were performed, including variation of temperature, sweep rate, and measurement frequency. These measurements were performed on several samples. Detailed results of these studies are presented in Chapter 6. In summary, the major results of capacitance studies are the lack of inversion, and evidence for localized deep levels.

#### 1.4.3 DLTS Measurements

Deep-level transient spectroscopy (DLTS) allows a more detailed examination of the capacitive transient behavior seen in the previous section. DLTS is done by suddenly filling or emptying the levels and then measuring the time required for the level populations to return to equilibrium, by examining the transient capacitance of the structure. DLTS is best applied to structures whose impedance is mainly capacitive, *i.e.*, devices that draw little current. An explanation of the DLTS

technique may be found elsewhere, [8,37,38,39] and in Chapter 6.

DLTS was applied to several samples, two of which were studied in detail. Results corroborate and expand the C-V data presented previously. No trap signatures were observed until the bias on the sample during the pulse neared zero. This observation showed that the deep levels were localized at or near the interface between the AlAs and the low doped GaAs, with possible extension into the AlAs evidenced by increase in trap signature for forward-bias pulses. Some evidence for an interface character to the levels was seen.

Activation energies were measured for both samples. Both samples showed activation energies of about 500 meV. Capture cross sections consistent with a very long trap emission time (many seconds) were obtained, in agreement with C-V data. It is interesting that both samples exhibited nearly identical trap signature, suggesting that the same trap is seen in *all* the samples. The attributes of the level indicate that it might be a 'DX' center. [40]

Concentration estimates can be performed using a standard method. [39,41,40] This method underestimates the true trap concentration, particularly when the deep-level concentration approaches that of the shallow level. Thus, the estimate of  $1 \times 10^{15}$  cm<sup>-3</sup> obtained in this manner is probably too low. A sheet concentration of  $1 \times 10^{10}$  cm<sup>-2</sup> is obtained if these levels are assumed to be distributed over 1000 Å, which is lower than that obtained by C-V estimates.

DLTS studies yield several supporting pieces of information. Deep levels were identified and localized to an area near the GaAs/AlAs interface. Since evidence of the traps continued to be seen when the devices were pulsed into forward bias, they may also be distributed in the AlAs. The extent to which the AlAs was probed is not known, because the amount of AlAs being scanned by the trap-filling pulses is uncertain. Very similar results were obtained for two samples, suggesting that the

Forward-bias DLTS behavior showed some evidence of conduction.

same level is present in all samples.

# 1.4.4 Current-Voltage Measurements

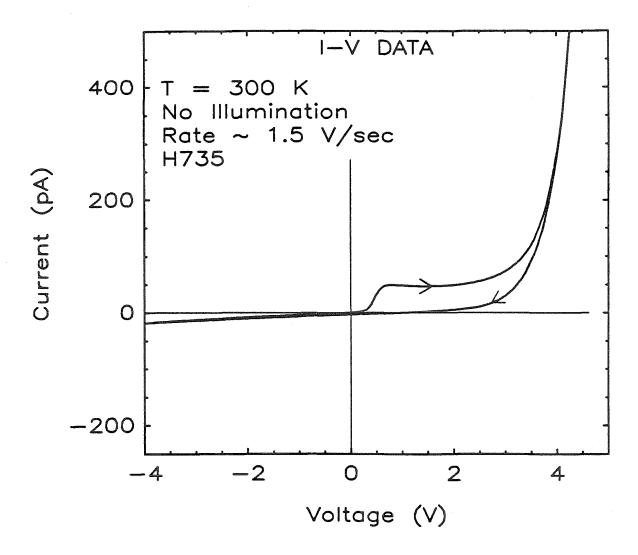

I-V measurements were made on all samples. Measurements were made both with and without illumination. The samples draw very little current when not illuminated. Illuminated I-V curves are the subject of the following section. When examining the I-V curves of nonilluminated samples, hysteresis could be observed. This hysteresis was investigated as a function of rate, temperature, and illumination.

In Fig. 1.7, I-V data for a representative sample are presented. No light falls on the sample over the voltage range depicted. The direction of bias sweep is indicated. When bias is swept from negative to positive, a sudden jump in current is observed, which persists until large-scale conduction is observed at the far right of the figure. This current step is not seen when bias is swept the other way.

The hysteresis seen in Fig. 1.7 can be explained by the same deep levels evidenced in C-V and DLTS measurements. Consider the case in which bias is swept from reverse to forward values. At large reverse biases, the trap levels should be depopulated of electrons. The sample can be briefly exposed to light in reverse bias, to ensure the depopulation of the levels. As voltage becomes positive, electrons are brought near the trap levels, and they begin to fill. The trap filling represents a removal of carriers from the circuit. This time rate of change of carriers is the current enhancement observed.

When bias is swept from forward to reverse values, the trap levels are filled at the start of the sweep. As the depletion layer envelops the deep levels, they begin to empty thermally. This process does not suddenly change the number of carriers in the circuit, so no current jump is seen.

Trap-level concentration estimates may be made by considering the area under

Figure 1.7: I-V curves for sample H735 at room temperature. Direction of sweep is indicated by arrows. In the forward-going sweep, trap levels were emptied at about -5V by brief exposure to light. The hysteresis is due to trap-filling effects.

the current step. This area may be converted to a charge, and then to a sheet concentration. One obtains a value of  $3 \times 10^{11} \,\mathrm{cm^{-2}}$ , which is in good agreement with estimates made from C-V data. The current jump was investigated as a function of temperature and sweep rate. More details of this work are contained in Chapter 6.

#### 1.4.5 Conclusions

This section has described electrical measurements on AlAs capacitor structures that were grown by MOCVD. An analogy to MOS or MIS devices was put forward and seen to be inadequate to explain the C-V behavior of the device. A lack of inversion was seen under all conditions. Light sensitive C-V and I-V behavior was observed. Hysteresis in the C-V and I-V data was observed. These effects were attributed to deep levels in the sample, which were observed more directly with DLTS techniques. Trap-level concentration estimates were obtained from all three techniques and were in rough agreement with one another.

The results of this study have implications for devices. The lack of inversion observed make the devices unsuitable for use as inversion-mode FETs. GaAsgate FETs operating in accumulation mode may be possible, since the devices can sustain several volts before forward conduction begins. The deep levels evidenced in C-V, I-V, and DLTS studies would degrade the operation of such a device, because they would decrease the number of carriers in the accumulation layer. More work on the production of high-quality MOCVD AlAs films is needed before these materials will be useful in devices.

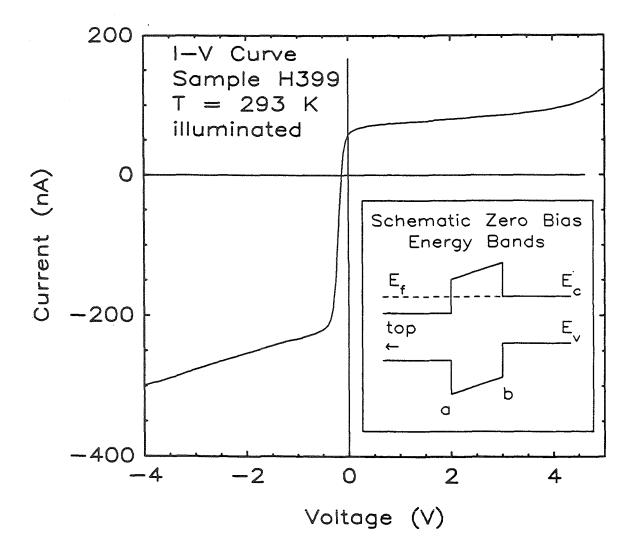

# 1.5 Photoresponse Measurements

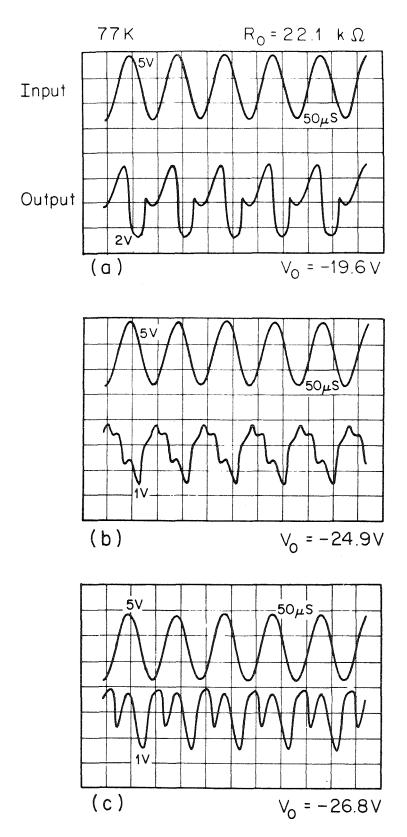

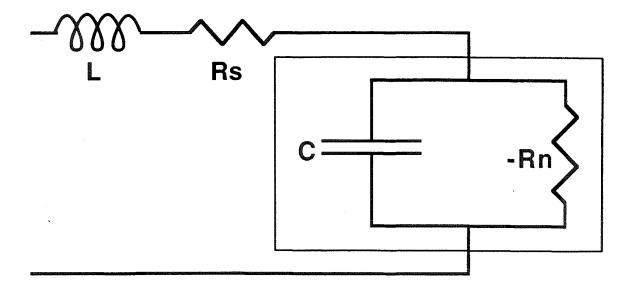

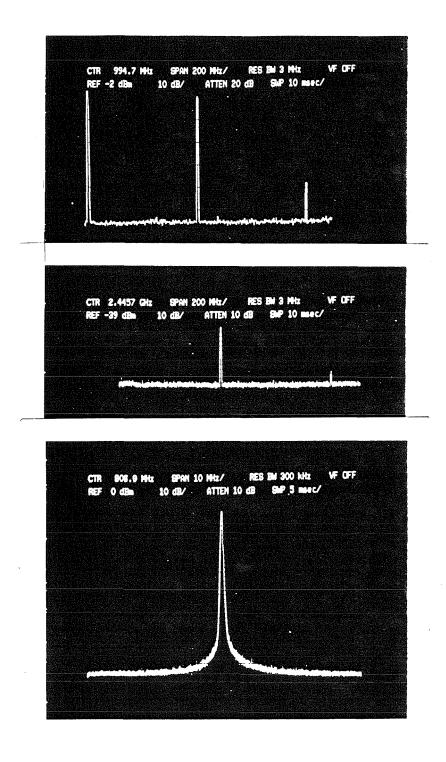

This section reports some new experimental results in the photoresponse behavior of single-barrier heterostructures. Photoresponse measurements record the electrical response of a device as a function of the light energy falling on it and can provide information about the device. The behavior of our AlAs single-barrier heterostructures differs from that of symmetric thin-barrier samples, whose photoresponse has been reported by Schlesinger et al.[42,43]