## Parallel Machines for Computer Graphics

Thesis by

Michael K. Ullner

In Partial Fulfillment of the Requirements

for the Degree of

Doctor of Philosophy

California Institute of Technology

Pasadena, California

1983

(Submitted January 7, 1983)

### PARALLEL MACHINES FOR COMPUTER GRAPHICS

Copyright © 1983 by Michael K. Ullner. All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of the author.

## Acknowledgments

y stay at Caltech was guided by a succession of advisors: Fred Thompson started me going, back in the old days; Ivan Sutherland pulled when I got stuck; Jim Kajiya pushed, and he carried a shovel for when things got messy. I appreciate their care and patience.

I would also like to thank Zipporah Sabsay for carefully scouring this monstrous document in search of errors in grammar and lapses in style. She did so not once, but twice!

I am especially grateful to Calvin Jackson, who was always willing to share his TEXnical expertise and to offer advice and encouragement. Cal's enthusiasm for the craft of bookmaking is infectious, and much of his taste has filtered into the appearance of this document.

### Abstract

omputer graphics provides some ideal applications for the kind of highly parallel implementations made possible by advances in integrated circuit technology. Specifically, hidden line and hidden surface algorithms, while easily defined and simple in concept, entail a substantial amount of computation. This requirement fits the characteristics of integrated circuit technology, where modular designs involving regular communication between many concurrent operations are rewarded with high performance at an acceptable cost.

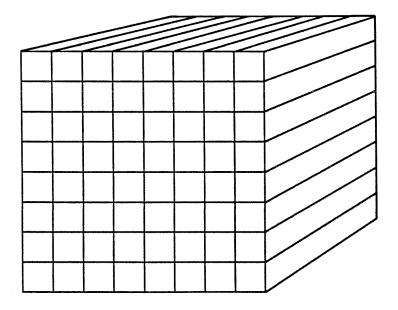

Ray tracing is a very flexible technique that can be used to produce some of the most realistic of all computer generated images by simulating the interactions of light rays with surfaces in a modeled scene. Because light rays are mutually independent, many may be processed simultaneously, and the potential for concurrency is great. One architecture for expediting a ray tracing algorithm consists of a conventional computer equipped with a special purpose peripheral device for locating the intersections of rays and surfaces. This intersection computation is the most time consuming aspect of a ray tracing algorithm. Although the attached processor configuration can produce images more quickly than an unaided computer, its performance is limited. Alternatively, a pipeline of surface processors can replace the peripheral device. Each processor computes the intersections of its stored surface with rays that flow through the pipe. Such a machine machine can be quite fast, and its performance can be increased by lengthening the pipeline, but the component processors are not very effectively utilized. A third approach combines the advantages of the prior two machines by using an array of processors, each simulating a distinct subvolume of the modeled world by treating light rays traveling through space as messages flowing between processors. Local communication is sufficient because light rays travel continuously through space.

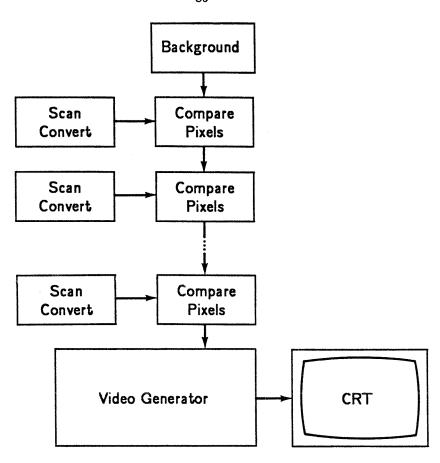

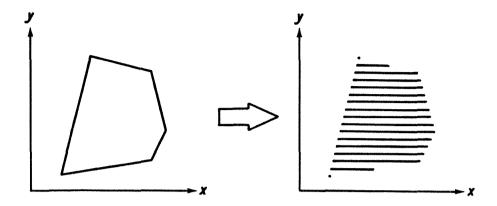

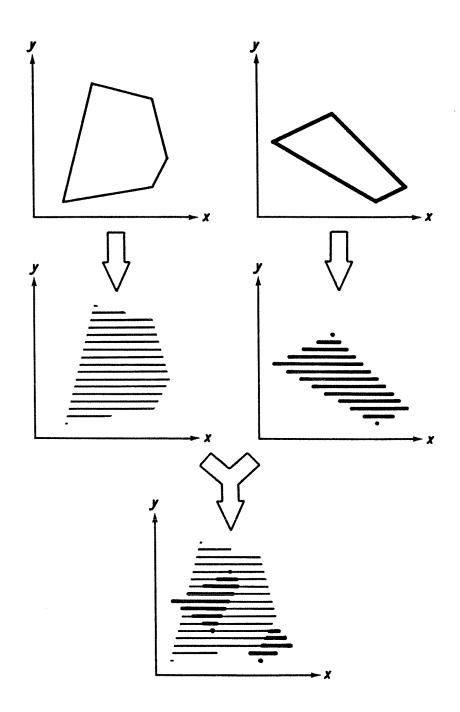

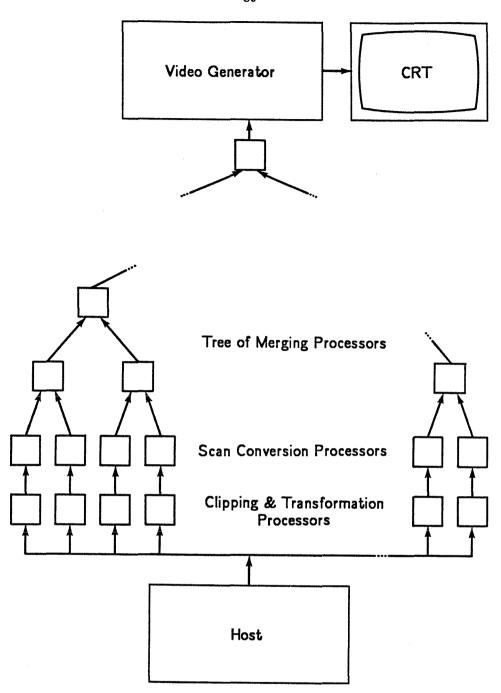

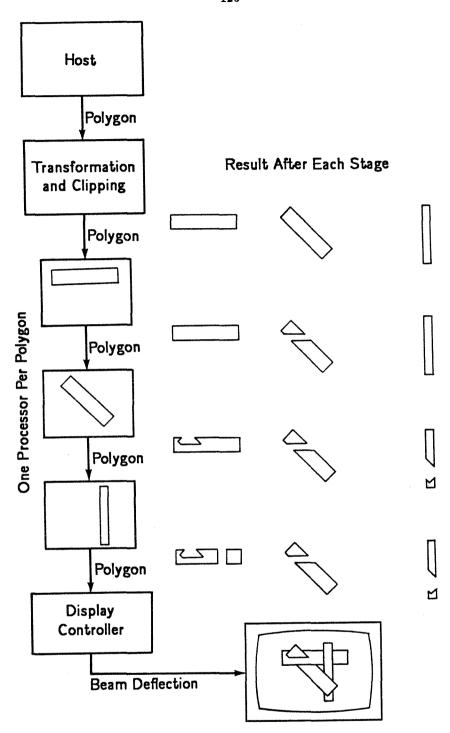

In real time computer graphics, successive images must be produced in times that are imperceptible to a viewer. Although the ray tracing machines fall short of this performance, it is possible to compromise image quality in order to produce a highly parallel machine capable of real time operation. The processors in such a machine are organized to form a binary tree. Leaf processors scan-convert surfaces, producing a sequence of segments, where a segment is the portion of a surface that appears on a single scan line of the display. Processors towards the root of the tree accept two such segment sequences and produce a third in which all segment overlap has been resolved. The final image is available at the root of the tree. The communication bottleneck that would otherwise occur at the root can be eliminated by breaking out

parallel roots, and the resulting tree may be extended to scenes of almost arbitrary complexity merely by increasing the supply of available processors.

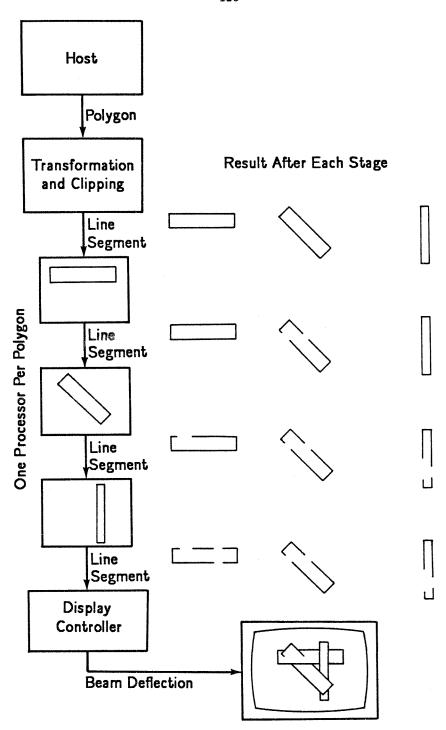

Massive parallelism can also be applied to the problem of removing hidden edges from line drawings. A suitable architecture takes the form of a pipeline in which each processor is dedicated to the handling of a single polygon edge. These processors successively clip line segments passing through the pipeline to eliminate portions hidden behind surfaces. Each edge processor can be constructed out of little more than three serial multipliers.

The machines described here are varied in organization, and each functions differently, but their treatment of sorting is one ingredient common to all. Sorting is a key component of hidden surface algorithms running on conventional computers, but its extensive communication requirements make it costly for use in a highly integrated design. Consequently, the highly parallel machines described here operate largely without sorting. Instead, they maintain information in sorted order or make use of already sorted information to limit communication requirements.

## Table of Contents

| Ac | kno          | wledgn                       | nents                  |           |       |     | •   |     |    | • | • | • |  |  | • |   | iii |

|----|--------------|------------------------------|------------------------|-----------|-------|-----|-----|-----|----|---|---|---|--|--|---|---|-----|

| Ał | str          | act                          |                        |           | • • • |     |     | •   |    | • | • |   |  |  | • | • | iv  |

| 1. | Introduction |                              |                        |           |       |     |     |     |    |   |   |   |  |  |   |   | 1   |

|    | 1.1          | Integrat                     | ed Circuit Tec         | hnology   |       |     |     |     |    |   |   |   |  |  |   |   | 2   |

|    | 1.2          |                              | er Graphics            |           |       |     |     |     |    |   |   |   |  |  |   |   |     |

|    | 1.3          | -                            | w                      |           |       |     |     |     |    |   |   |   |  |  |   |   |     |

| 2. | Ra           | y Tracii                     | ng Machines            | 3         |       |     |     |     |    |   |   |   |  |  |   |   | 7   |

|    | 2.1          |                              | y Tracing Algo         |           |       |     |     |     |    |   |   |   |  |  |   |   |     |

|    | 2.2          |                              | ations for Ray         |           |       |     |     |     |    |   |   |   |  |  |   |   |     |

|    | 2.3          |                              | Tracing Periph         |           |       |     |     |     |    |   |   |   |  |  |   |   |     |

|    |              | -                            | ost-Peripheral         |           |       |     |     |     |    |   |   |   |  |  |   |   |     |

|    |              |                              | peration of th         |           |       |     |     |     |    |   |   |   |  |  |   |   |     |

|    |              |                              | nplementation          |           |       |     |     |     |    |   |   |   |  |  |   |   |     |

|    |              | 2.3.4 A                      | nalysis                |           |       |     |     |     |    |   |   |   |  |  |   |   | 35  |

|    | 2.4          |                              | <b>Fracing</b> Pipelii |           |       |     |     |     |    |   |   |   |  |  |   |   |     |

|    |              |                              | peration of th         |           |       |     |     |     |    |   |   |   |  |  |   |   |     |

|    |              |                              | ${	t nple mentation}$  |           |       |     |     |     |    |   |   |   |  |  |   |   |     |

|    |              |                              | ommunication           |           |       |     |     |     |    |   |   |   |  |  |   |   |     |

|    |              |                              | nalysis                |           |       |     |     |     |    |   |   |   |  |  |   |   |     |

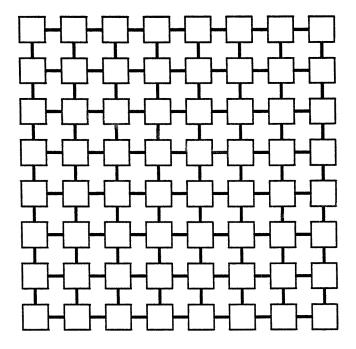

|    | 2.5          |                              | Iracing Array          |           |       |     |     |     |    |   |   |   |  |  |   |   |     |

|    |              |                              | peration of th         |           |       |     |     |     |    |   |   |   |  |  |   |   |     |

|    |              |                              | rocessor Orga          |           |       |     |     |     |    |   |   |   |  |  |   |   |     |

|    | 2.6          |                              | nalysis ons            |           |       |     |     |     |    |   |   |   |  |  |   |   |     |

|    |              |                              |                        |           |       |     |     |     |    |   |   |   |  |  |   |   |     |

| 3. |              |                              | Machines               |           |       |     |     |     |    |   |   |   |  |  |   |   |     |

|    | 3.1          | Model I                      | Preparation .          |           |       |     |     |     |    |   |   |   |  |  |   |   | 74  |

|    | 3.2          | Previous Parallel Algorithms |                        |           |       |     |     |     |    |   |   |   |  |  |   |   | 78  |

|    | 3.3          | A Scan                       | Line Tree .            |           |       |     |     |     |    |   |   |   |  |  |   |   | 85  |

|    |              | 3.3.1 T                      | ransformation          | and Clip  | pping | Pro | oce | sso | rs |   |   |   |  |  |   |   | 90  |

|    |              | 3.3.2 S                      | can Conversio          | n Process | sors  |     |     |     |    |   |   |   |  |  |   |   | 99  |

|    |              |                              | lerging Proces         |           |       |     |     |     |    |   |   |   |  |  |   |   |     |

|    |              | 3.3.4 T                      | he Pixel Conv          | ersion Pr | ocess | or  |     |     |    |   |   |   |  |  |   |   | 112 |

|        |                                  | 113 |

|--------|----------------------------------|-----|

|        |                                  | 122 |

| 3.4    | Hidden Line Elimination          | 124 |

| 4. Obs | servations and Conclusions       | 141 |

| Appen  | dix A. Implementing Arithmetic   | 145 |

| A.1    | Using Commercial Components      | 145 |

| A.2    | Using Custom Components          | 149 |

| Appen  | dix B. Moving Between Subvolumes | 155 |

| Appen  | dix C. Programming in Silicon    | 159 |

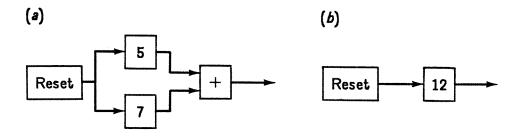

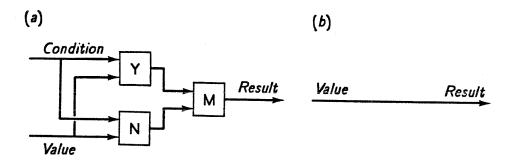

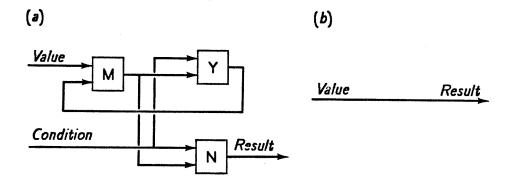

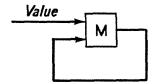

| C.1    | Silicon Programming              | 160 |

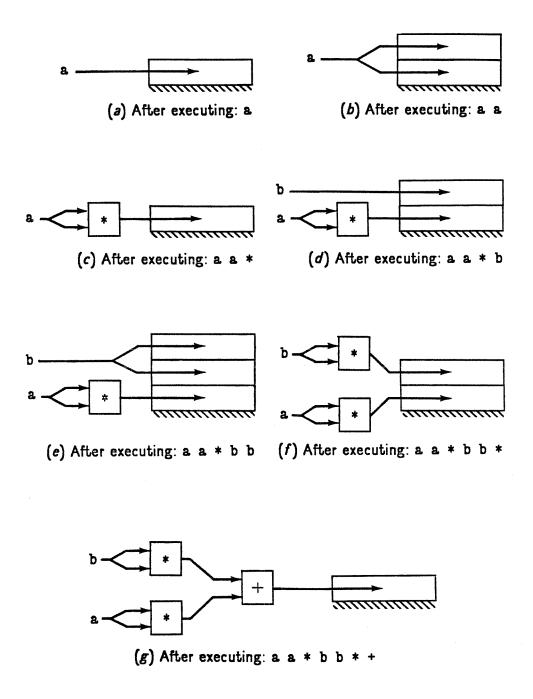

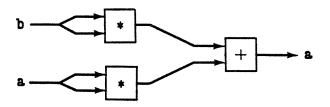

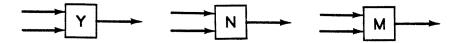

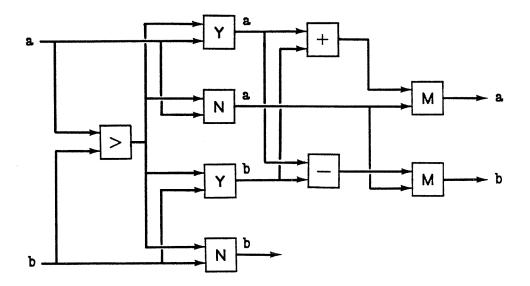

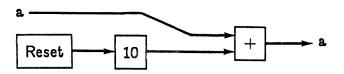

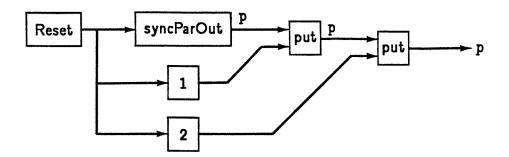

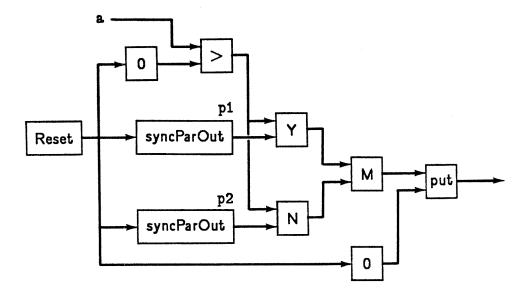

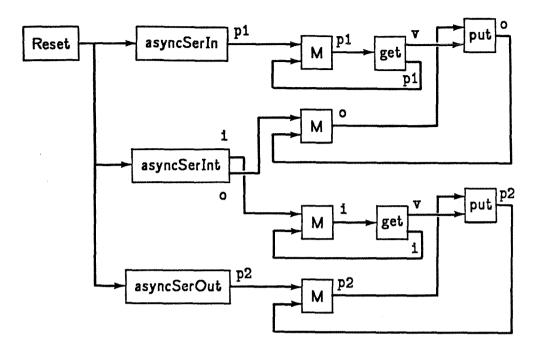

| C.2    | Example: Inner Product           | 162 |

|        |                                  | 164 |

| C.4    | Example: Convolution             | 172 |

| C.5    |                                  | 175 |

| C.6    |                                  | 178 |

| C.7    |                                  | 183 |

| C.8    |                                  | 185 |

| C.9    |                                  | 187 |

| C.10   |                                  | 200 |

| C.11   |                                  | 205 |

| C.12   |                                  | 206 |

| C.13   | Bit Serial Implementation        | 207 |

|        |                                  | 219 |

|        |                                  | 221 |

| Refere | ences                            | 993 |

# 1

### Introduction

omputer graphics is the art and science of making pictures by means of computation. Beginning with little more than an idea for a scene to be depicted, the artist/programmer must first transcribe that idea into a geometric model. Next, some form of computing engine processes the model into the electrical signals that control the electron beam in a cathode ray tube. The modulated beam of electrons strikes the inside surface of the tube, exciting a phosphor coating to produce the pattern of light that we perceive as the final image.

Since its inception, progress in computer graphics has been tied to the availability of suitable computing and display hardware. Some of the earlier displays could show only patterns of dots, and the images that could be produced were correspondingly limited. Subsequent displays could draw lines in addition to dots, thereby extending the range of possible images. The frame buffer, a device for storing a digitized, continuous tone image and displaying it on a television monitor, represents a further advance in display hardware. Early frame buffers used magnetic disks for the storage medium, but as memory technology improved, frame buffers began to use large, random access memories. The new devices were not only cheaper and more readily available, but also their very existence suggested new applications and algorithms for computer graphics.

The progress of computing technology, as well as display technology, has influenced the progress of computer graphics. The algorithms used to make pictures tend to be computationally intensive. In fact, it has been estimated that even a Cray-1, which

is generally acknowledged to be among the fastest computers in the world, can produce only about four minutes of high quality motion pictures per month [WHIT82]. This figure takes into account the draft work that must precede the finished product. Most computer graphics, however, is done on minicomputers rather than supercomputers, forcing compromises in image realism. Another branch of computer graphics makes use of special purpose processors in order to produce successive images in times that are imperceptible to the viewer. Because it is so difficult to generate images at this rate, the pictures produced by these machines tend to be less complex than the pictures that can be made without timing restrictions. Such machines are typically used in visual environment simulators, and because the moving images are under direct control of the viewer, many of the image quality compromises that were made in exchange for performance can be overlooked.

One of the more recent technological developments that can be applied to computer graphics is the practice of fabricating large scale integrated circuits. Using this technology, it is possible to fit an entire electronic subsystem onto a single, fingernail-sized chip of silicon. The cost per computing device is correspondingly diminished, making it feasible to apply more computing power to a task with the hope of improving performance. Like all technologies, however, integrated circuits have their own peculiar set of properties that must be considered if the final product is to be a practical one. For integrated circuit technology, it is cheap to replicate components, but communicating between the various parts of a system is very expensive. These characteristics suggest that highly parallel algorithms are suitable, so long as the communication between the various operations taking place concurrently is not excessive.

The following pages explore some computer graphics algorithms that can utilize the technology for fabricating very large scale integrated circuits. The algorithms are designed to make effective use of concurrency while keeping communications requirements down to an acceptable level. The primary emphasis will be on algorithms for detecting and removing those parts of a simulated scene that should be hidden from the viewer. One type of algorithm will concentrate on rapidly producing images of very high quality, while another will accept poorer image quality in order to achieve high performance. Before proposing the algorithms and their associated machine architectures, however, a brief overview of the technology characteristics and the problems involved at the graphics end may be helpful.

#### 1.1 Integrated Circuit Technology

Using large scale integrated circuit technology, it is possible to fabricate a single chip of silicon containing an amount of logic that formerly required an entire printed circuit board. It would be a mistake, however, solely to regard integrated circuits as miniaturized printed circuit boards, because they have a different set of strengths and weaknesses. The major differences have to do with communications. Within

an integrated circuit, the cost of transmitting a signal across the chip is substantially greater than the cost of communicating it locally. Not only does a longer transmission path consume more area, it is also slower because it has a larger capacitance and stores a correspondingly greater charge that must be overcome in order to accomplish the transmission. Compared with these communication paths, the actual active computing elements consume relatively little power, time, or area. This situation led Sutherland and Mead to observe that integrated circuits make "switching elements essentially free ... leaving wires as the only expensive component" [SUTH77].

Just as the communications within a single chip limit performance, the amount of communication between chips is restricted. A single printed circuit board might have hundreds of connections to its environment. In contrast, an unusually large and complex integrated circuit might have eighty pins connecting it with the outside, while typical chips have fewer than fifty. These pins supply power to the chip as well as serving as portals for data transfer. In addition to being limited by the number of pins on a chip, communication between two chips is generally slower than communication between points within a single chip.

Testing is another area in which integrated circuitry requires some extra attention. On a printed circuit board, most of the signals are accessible to an oscilloscope probe. This is not so with an integrated circuit, where the only access to the internals of a chip is through the limited number of signal pins. The problem of testing is still largely unresolved, but one technique that has been used successfully involves chaining a portion of a chip's internal state into a long serial register, which may then be shifted out of the chip through a small number of pins for examination and possible modification [EICH77].

In many ways, the process of fabricating integrated circuits is similar to the techniques of book printing. In both cases, the setup costs are high, but the incremental cost of producing each unit is comparatively low. After printing the pages of the book or fabricating the chip, a culling phase is required to eliminate defective units before packaging the final product. Because highly replicated chips are individually less expensive, an engineer contemplating the use of custom integrated circuits is encouraged to come up with designs that can make use of many copies of a single chip type.

The characteristics of integrated circuit technology tend to push one in the direction of highly parallel designs with regular, if somewhat constricted, communications paths. The goal is to achieve high performance by applying a large number of concurrently operating processing elements to a particular problem. Since it is easy and inexpensive to duplicate chips, it is also desirable to apply a myriad of identical processors. The fact that all processors are the same tends to encourage the use of regular interconnection structures. Notice that this approach is almost completely opposite from the one that is useful in printed circuit technology, where overall performance is achieved by relying on the individual component speeds rather than on their combined speeds.

Many types of processor interconnection structures have been proposed or actually implemented [ANDE75]. The most common of these is the conventional pipeline

consisting of a linear array of processors, each connected to its two neighbors. Work flows into one end of the pipe and passes from processor to processor, rather like the material in an assembly line. Each processor performs a single stage of the computation before it passes a partial result to the next processor. The final result appears at the end of the pipeline. More elaborate pipelines have also been proposed [KUNG80]. These organizations have more than one input and output stream, and the internal communication schemes are more complicated, but they still pass partial results in one direction from processor to processor in a very regular and rigid manner.

Other types of interconnection strategies suggest communication schemes that are different from the approach used in linear pipelines. In tree structures and arrays, for example, each processor is connected to a few nearby processors. In trees, each component processor has connections for a superior processor and for two or more subordinate processors. Component processors in a rectangular array are each connected to four others, although different kinds of arrays may have richer interconnection patterns. For these and other types of structures, asynchronous message passing is often a more useful communication strategy than the rigid, unidirectional flow found in conventional pipelines. Using this technique, the communication occurs only when and where there is information to be transmitted. The disadvantage, of course, is that message passing requires a great deal more logic devoted to its control.

#### 1.2 Computer Graphics

As mentioned earlier, the first step in making a picture is to transcribe an idea into a geometric model suitable for manipulation by computer. This usually means that the surfaces in the scene must be split up into a collection of planar polygons defined in three dimensions, although some techniques for dealing directly with curved surfaces have been developed. One way to prepare the scene model is to use a large digitizing tablet to derive three-dimensional coordinates by tracing blueprints of the objects. After the geometric properties of the surfaces have been described, it is still necessary to provide color and texture information for them. Also, the light sources that illuminate the scene must be identified and described. The result is a complete, three-dimensional model of the scene to be depicted.

Because television and movie screens are flat, the scene model must be projected onto two dimensions before it can be displayed. The projection operation simulates the action of a camera, given its position and the direction in which its lens is pointed. After projection, surfaces that would obscure one another in a natural scene overlap each other in the synthetic one. These obscured surfaces must be detected and deleted if the final image is to appear at all realistic. The process for doing so is called hidden surface elimination, and the corresponding techniques are called visible surface algorithms.

A great variety of visible surface algorithms have been developed over the years,

but they generally share a common feature. The algorithms all perform some form of sorting operation to reduce the amount of computation necessary for locating overlapping surfaces [SUTH74b]. The sorting is used, in some sense, to bring surfaces that appear near to each other on the screen into similar proximity within the machine implementing the algorithm. The goal is to reduce the number of surfaces that must be compared, since this comparison is usually very time consuming. The visible surface algorithm is often considered to be the heart of a computer graphics system. Various algorithms will be considered in greater depth in the chapters that follow.

After the visible surface algorithm has terminated, it is still necessary to determine the colors of the remaining surfaces. Once again, researchers have devised many techniques for modeling the interactions between light and surfaces [BLIN77]. The apparent color of a point on a surface is some function of the color and other properties of the surface, the colors of the light sources, and the relative positions and orientations of the simulated camera, surface, and light sources.

The completed image can be displayed on some type of frame buffer, as mentioned earlier. This device consists of a fairly large memory, where each word in the memory stores the color of a single position on the screen. These individually accessible screen positions are called picture elements, or pixels. The fact that a screen can display only a finite number of pixels poses one final obstacle in the image generation process: aliasing [CROW77]. The number of pixels on the screen is limited, and the values of individual pixels are determined by discretely sampling the continuous simulated scene. If the spatial frequency of the scene is too high relative to the sampling resolution, aliasing will result. It generally shows up as jagged edges, or as small features that disappear and reappear in successive frames of a movie. Although its causes are well understood, there are no really good methods for eliminating aliasing. One commonly used technique can, however, reduce the visible effects. This method involves computing the image at a resolution greater than the screen resolution and then filtering the higher resolution image to obtain the lower resolution one.

There are two reasons that computer graphics provides an ideal application area for parallel implementations. First of all, the algorithms are sufficiently involved and time consuming that a parallel solution can provide genuine performance benefits. Second, the problems can often be cleaved into a collection of smaller problems with manageable intercommunication requirements. These two properties mesh well with the characteristics of integrated circuit technology.

#### 1.3 Overview

Computer graphics systems may be classified into one of four broad categories on the basis of their performance: real time, movie time, still time, and too slow. Of course, the classification of a particular implementation depends not only on the algorithm being used, but also on the hardware support that is available and on the

complexity of the image being produced. Real time systems are the fastest, generating successive images quickly enough for a viewer to interact with them. That is, a viewer can make small changes in the scene and immediately see the visible effects of the changes. Real time performance is generally considered to mean that the system must be able to produce thirty completely new images every second, although for some applications this requirement may be relaxed a bit. Movie time performance is achieved if the system is fast enough to compute the successive frames of a motion picture in a reasonable amount of time, but not fast enough to produce them in real time. Presumably, the goal is to provide better image quality, or lower cost, in a movie time system than in a real time one. The next category is still time performance, where the time required to compute a single image is so long that computing an entire movie would be infeasible. Graphics programs running on minicomputers often fall into this category. Finally, implementations where the mean time between failures of the hardware exceeds the time required to make a picture are simply too slow.

Ray tracing is a very flexible approach to making pictures. With it, one can generate very realistic images that show reflection, refraction, and shadows. The difficulty is that although it is simple in concept, ray tracing requires a great deal of computation. Its performance ranges from still time to too slow, although some very short and limited movies have been made. Fortunately, as discussed in Chapter 2, special purpose hardware can boost the performance of a ray tracing algorithm solidly into the movie time category, making ray tracing a practical alternative to approaches that may be faster, but are more complicated and less functional.

The timing constraints imposed on a real time system are severe, since there is quite a bit to be done in the thirtieth of a second that is available for each frame. Existing real time systems have achieved high performance largely by relying on the speed of their individual components. When using integrated circuit technology, however, the speed of a single chip is not always very great, and performance must be achieved by amassing many chips. The challenge of integrated circuits, therefore, is to devise highly parallel algorithms that have manageable communications requirements, as well. Chapter 3 discusses some approaches to this problem.

# 2

## Ray Tracing Machines

Ray tracing is a technique that is capable of producing some of the most realistic of all computer generated images. It is primarily a method for performing hidden surface elimination, but the primitive operation of tracing a ray can also be used to model shadows, reflective surfaces, and transparent surfaces with refraction. In fact, essentially all of the effects available in shaded computer graphics can be achieved by a ray tracing algorithm. Beyond pure image generation, ray tracing can be used, for example, to estimate the volumes of modeled objects, as well as to simplify the construction of these models.

As might be expected, the drawbacks of ray tracing are almost as pronounced as its benefits. First of all, it is among the slowest of the algorithms for hidden surface elimination that run on commercially available computers. It is so tedious that it is never considered for most applications. Another difficulty is that a ray tracing algorithm produces an image by sampling the object space, rather than by any kind of direct or exact computation. This makes it inherently susceptible to the various aliasing problems that can be caused by sampling too infrequently.

Ray tracing is, however, interesting in the context of parallel computation. It suggests a natural way of separating the problem of hidden surface elimination into a vast number of simpler computations that are largely independent of one another. Therefore, it seems especially suitable for implementation on a machine consisting of a number of relatively unsophisticated processors operating in parallel.

This chapter proposes three different organizations for machines designed to

implement a ray tracing algorithm. Each of the organizations was designed to exploit a different aspect of the concurrency that is potentially available in the algorithm. In the first approach, the primitive ray tracing computation itself provides the concurrency. In the second approach, all of the polygons in the scene are processed at the same time. Finally, in the third approach, polygons are separated into disjoint regions of volume, and these regions are processed simultaneously. Before delving into the details of these three machines, however, it may be helpful to understand the general behavior of a ray tracing algorithm.

#### 2.1 The Ray Tracing Algorithm

Ray tracing algorithms were pioneered by Appel back in the late 1960's. The Mathematical Applications Group, Inc. (MAGI) has been using ray tracing for quite some time in their production of television commercials and video logos, among other things. Other than this, however, the techniques lay dormant for over a decade until fairly recently when they were revived and extended by Whitted. Ray tracing seems to be getting more attention lately as people come to appreciate its simplicity and generality. The remainder of this section describes ray tracing algorithms, and it may be skipped by readers who are already familiar with them.

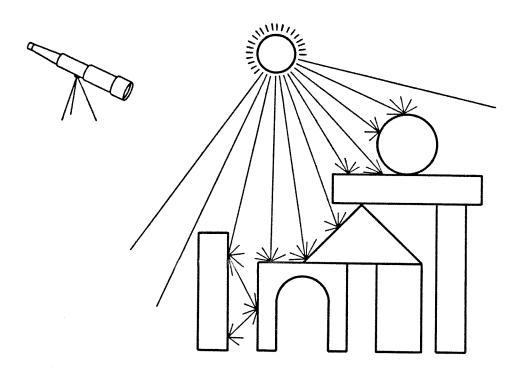

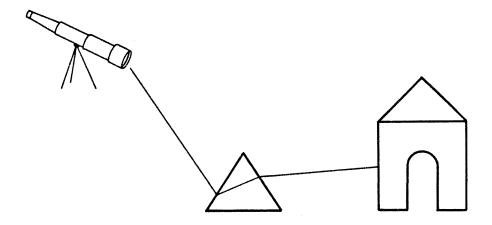

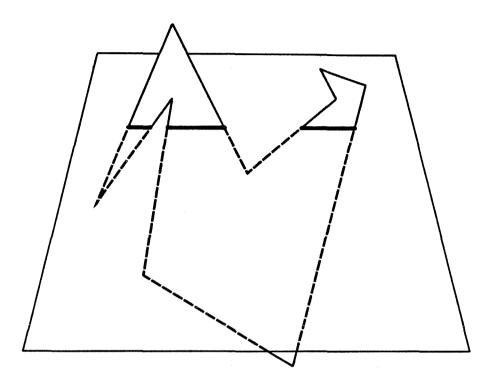

To understand how a ray tracing algorithm works, imagine a scene consisting of a number of objects illuminated by a single light source, as sketched in Figure 2-1. Light rays emitted from the light source may strike the surfaces of objects in the scene, and secondary light rays will be emitted from the points of intersection in ways that depend upon the surface characteristics of the objects. For example, the color of a secondary ray is partially determined by the color of the surface. In addition, the distribution of secondary rays depends on how glossy the surface is. Secondary light rays may strike other objects in the scene to create many levels of interaction.

Eventually, some of the light rays will reach the eye of a nearby observer, who will perceive them as an image. Suppose that there is a transparent sheet of glass in a wall between the observer and the scene, so that light rays must pass through the glass before the observer can see them. One ideal in computer graphics is to be able to replace this sheet of glass with the screen of a television monitor in such a way that the observer cannot distinguish between the genuine image and a synthetic one. Of course, this ideal cannot be realized in practice, partly because of the two-dimensional nature and limited resolution of the display screen. Assume, therefore, that the observer sits very still, wears a patch over one eye, and is accustomed to viewing the world through a window screen.

The direct approach to determining the synthetic image is to simulate the behavior of light rays using models of the scene, the light source, and the surface interactions. Rays can be simulated by tracing them from the light source to determine whether they will strike an object. If this happens, the surface interactions must be

Figure 2-1. Light rays illuminating a scene.

simulated to create new secondary rays, which should then be traced in a similar manner. If, by chance, a ray passes through the simulated sheet of glass on a path leading to the observer, it is captured and displayed on the television screen. Of course, since the number of rays leaving the light source is essentially infinite, as is the number of rays emitted from each surface intersection, the rays must be simulated by using some sort of sampling technique. Unfortunately, only a very small proportion of the rays leaving the light source will ever contribute to the final image, so that any effort spent simulating the others will have been wasted.

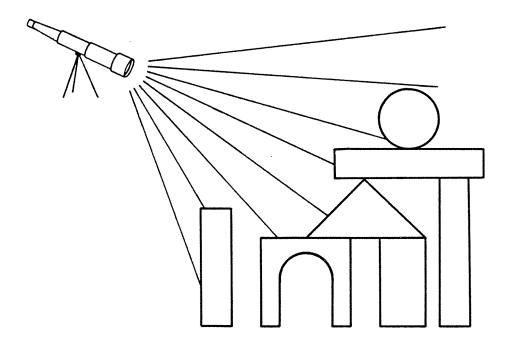

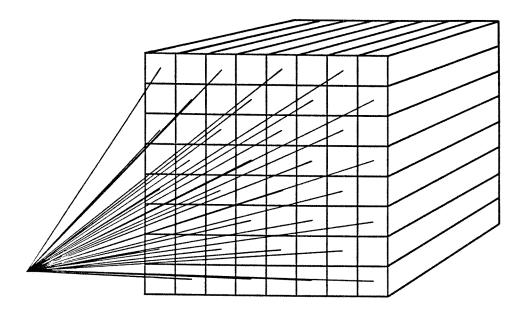

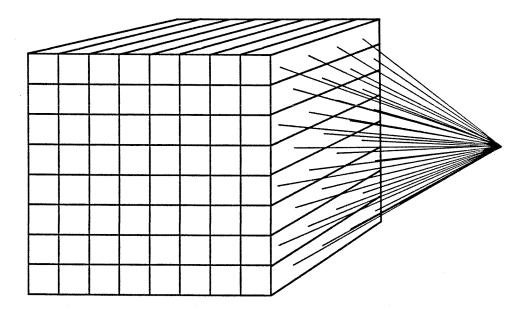

Notice that the only rays that are really of any interest are those that arrive at the viewer's eye by passing through the simulated sheet of glass. Furthermore, since the final image will be displayed on a television monitor as a raster of pixels, rays passing through the pixels of this raster are more pertinent than those passing between them. It seems prudent, therefore, to restrict the algorithm to this subset of the rays. A way to do this is to trace rays backwards from the viewing position, through the pixels on the sheet of glass, and out into the scene, as shown in Figure 2–2. These backwards light rays may be thought of as vision rays.

Tracing vision rays reduces the number of first-level rays that must be simulated, but the number of secondary rays remains large. Just as a light ray striking a surface generates secondary rays in all directions, one particular secondary ray could have been generated by a ray coming from any direction. This means that in order to simulate vision rays properly, it would be necessary to trace an infinite number of

Figure 2-2. Tracing vision rays to sample a scene.

secondary vision rays emitted in all directions from each intersection point. Of course, not all directions are equally likely, and this fact can be used to reduce the number of rays under consideration. These types of approximations are successful to varying degrees.

Consider, for the moment, the simplest possible version of a ray tracing algorithm. For each pixel in the raster, the algorithm traces the corresponding vision ray to the first object that it encounters in the scene. The color of the surface at the point of intersection completely determines the color of the pixel in the final display; that is, secondary rays are just ignored. The resulting image will not show any hidden surfaces, but no shadows or other interesting lighting effects will be apparent either. It will be cartoon-like, resembling an image produced by one of the early algorithms for hidden surface elimination, like Warnock's algorithm [WARN69].

It is not difficult to see why ray tracing algorithms are generally considered to be slow. They make absolutely no use of any kind of coherence. That is, the process of tracing one particular ray does not provide any information that may be used to simplify tracing the next. It is exactly this mutual independence of rays, however, that makes ray tracing compatible with a parallel implementation. Since rays do not affect one another, it is possible to trace several rays concurrently. This aspect of ray tracing will be explored more fully in later sections.

The minimal ray tracing algorithm given above may be extended in a rather natural way to synthesize shadows. As before, the algorithm begins by tracing a vision

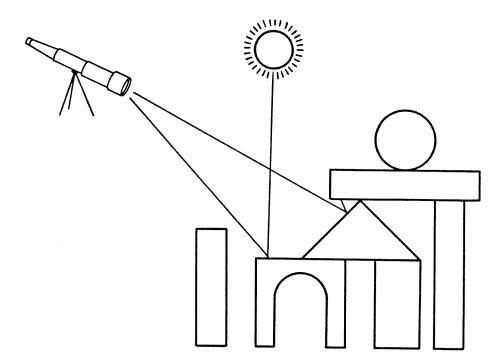

Figure 2-8. Tracing rays to a light source to determine whether intersection points are in shadow.

ray to determine which object is visible through a particular pixel. But this time, the algorithm traces a new ray emitted in the direction of the light source from the point of intersection on the visible surface. See Figure 2-3. If this new ray extends all the way to the light source without striking any other surface, then the intersection point is directly illuminated by the light source; otherwise, the point is in shadow. In a scene illuminated by more than one light source, separate rays must be traced in the direction of each light source. Appel used an algorithm much like this one in the late 1960's to produce pictures on, of all things, a digital pen plotter [APPE68]. This was in the days before there were devices capable of displaying true shaded images.

Reflection is another phenomenon that a ray tracing algorithm can model. As in the case of shadows, the extension to handle reflection is a rather natural one. The algorithm traces a vision ray to determine which point in the scene is visible from a particular pixel. Then, in addition to shadow rays aimed at the light sources, it generates a new ray in the direction of reflection, as in Figure 2-4. This reflection ray may, in turn, strike another surface and generate still more rays. The surface properties and shadowing information at all of the intersection points combine to determine the color of the original pixel.

Refraction can be produced in much the same way as reflection. Instead of generating a new ray in the direction of reflection, however, the algorithm must generate it in the direction of refraction, according to Snell's Law and the index of refraction of the material. Refraction rays are illustrated in Figure 2-5. Actually,

Figure 2-4. Tracing rays from an intersection point in the direction of reflection.

Figure 2-5. Tracing rays from an intersection point in the direction of refraction.

it is perfectly permissible to generate both a reflection ray and a refraction ray. For instance, both kinds of rays would be needed to make a picture of a magnifying glass with reflections visible on its surface.

Sampling too infrequently can be a problem with all ray traced images, but the techniques used for modeling reflection and refraction can further aggravate the situation. For example, rays reflected from a convex surface will be more "spread out" than the incident rays, so that the reflected image is not sampled as frequently as the rest of the image. Whitted has used ray tracing techniques like those described above to make images showing reflection and refraction [WHIT80]. He also suggested a fairly simple way of dealing with the problem of aliasing.

Whitted's technique for anti-aliasing begins by examining the colors of adjacent pixels in the displayed image. If the colors are sufficiently different, the algorithm assumes that the pixels lie on opposite sides of an edge. In this case, it traces another ray between the pixels so as to determine the color at that intermediate point. This process is applied recursively either until the colors are sufficiently similar or until some fixed depth limit is reached. Finally, the algorithm averages, or otherwise filters, the colors at the intermediate points to determine the colors of the original pixels. This procedure may still, however, overlook small objects that fall between adjacent pixels in the raster. Whitted solved the problem by forcing a subdivision in this case, even when the nearby pixels are colored similarly. A pleasant aspect of this anti-aliasing technique is that the effort tends to be concentrated along edges, where it is most needed. Moreover, it meshes well with the rest of the ray tracing algorithm by making use of the same basic computation.

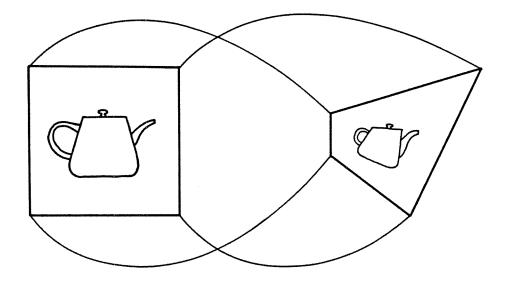

Ray tracing can also be used with the various surface mapping techniques that have been developed. These work by setting up a mapping between a unit square and a surface in the scene, as shown in Figure 2-6, so that values of an arbitrary function can be associated with points on the surface. Values mapped in this way can then take part in the computation of the intensities to be displayed in the final image. Catmull first used the technique to map photographs and images of textures onto surfaces [CATM74]. In his pictures, the function values derived by sampling stored images were used to determine the colors at points on surfaces. Objects in the resulting images appeared to have photographs glued to their surfaces. Blinn was able to produce convincing pictures of wrinkled and bumpy surfaces by mapping perturbations of surface normal vectors [BLIN78].

Still other types of mappings are available in a ray tracing algorithm because of its greater generality. For example, mapping a surface's index of refraction might be an effective way to model a simple lens. Transparency mapping is another technique that can be used when intricate two-dimensional objects are to be displayed. Conventionally, this kind of object would be modeled by a myriad of polygons. Using transparency mapping, however, the usual surface model gives the general spatial location of the object, while the transparency map determines where on this surface the object actually exists. Notice that the number of surfaces has been substantially

Figure 2-6. Mapping a unit square in the uv-plane to a surface in the scene.

reduced, thereby easing the burden on the hidden surface processor as well as the modeler.

Although ray tracing is probably the most flexible hidden surface and shading algorithm available, there are still many effects that are difficult or impossible for it to achieve. One source of difficulty stems from the fact that ray tracing does not make use of phase information. Thus, it cannot simulate diffraction, but this is probably not a very serious shortcoming for most applications. A more important problem occurs in situations that involve diffuse illumination, reflection, or transmission. In a diffusely illuminated scene, the light does not come from a point source, and therefore shadows do not have sharp edges. Diffuse reflection occurs, for instance, when an object takes on some of the color of another object nearby. Illumination that is reflected by a mirror is a related problem. A view through a translucent screen is an example of diffuse transmission. In each of these cases, the assumptions used to reduce the number of secondary rays are no longer valid. Of course, it is still possible to approximate these effects by tracing a random sample of rays, but it would be very costly to do so.

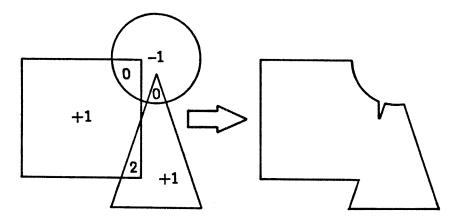

It was mentioned earlier that the use of a ray tracing algorithm for rendering an image of a scene could, in some cases, ease the task of producing the scene model. The basic idea here is that surfaces may be thought of as enclosing either positive or negative volume and, furthermore, that these volumes can be combined algebraically. For example, to model a hole in an object, a negative object correspond-

Figure 2-7. Using negative volumes to model a holes in an object. The square and triangle have positive volume, while the circle has negative volume. The numbers correspond to the net volume of each region.

ing to the hole can be superimposed on the positive object, partitioning space into regions of positive, negative, and zero net volume. Such a case is diagrammed in Figure 2-7. The surface of the complete object is the boundary between the positive and zero volumes. To make an image of this object using a ray tracing algorithm, it is necessary to find the intersections of a ray with each of the modeled surfaces. From these intersections, along with the surface descriptions, the algorithm can determine when the ray is passing through the positive volume, negative volume, or zero volume. Finally, the visible point is where the ray first passes into the positive volume. The Mathematical Applications Group, Inc. (MAGI) has been using techniques like this for quite some time to produce television commercials and the like [GOLD71]. More recently, the techniques have been applied to the design of automotive parts [ROTH80].

In the automotive application, ray tracing can produce not only a realistic image of the part, but also an estimate of the volume of an object, so that its weight can be computed. The volume of an object can be determined to any desired precision by passing a raster of parallel rays through it. For each ray, the algorithm accumulates the length of the ray passing through the object's positive volume. When the accumulations from all of the rays are added together and the sum is multiplied by the cross-sectional area of the original raster, the result is an estimate of the object's volume. The precision of this estimate can easily be increased by tracing more rays.

#### 2.2 Computations for Ray Tracing

This section describes some of the computations needed to implement a ray tracing algorithm as outlined in the previous section. The discussion will be limited to planar surfaces, primarily because this simplification makes hardware implementations more feasible. Furthermore, only convex quadrilaterals will be considered. These may, of course, be pieced together in order to form arbitrarily complicated polygons or other surfaces. For the rest of this discussion, the term "polygon" should be understood to mean "convex quadrilateral."

The main computation involved in ray tracing determines whether a given ray intersects a given polygon and, if it does, determines where on the ray and where on the polygon the intersection occurs. The position on the ray is described by the distance between the origin of the ray and the point of intersection. The ray tracing algorithm will use this distance to isolate the first polygon struck by the ray. The position on the polygon is specified by a point within a two-dimensional unit square. If the polygon is considered to be a mapping from the square onto a surface in three dimensions, then the point on the polygon where the ray and polygon intersect corresponds to a point in this unit square. The polygon position will be used in the shading computations and, optionally, for the various effects like texture mapping. Using quadrilaterals makes it possible to have a fairly direct mapping from the unit square to the polygon.

A ray can be specified by two points:  $\mathbf{r}_0$  is the origin of the ray, and  $\mathbf{r}_1$  is another point on the ray. The ray itself is represented parametrically, so that an arbitrary point along the ray is given by

$$\mathbf{r}(t) = (1-t)\mathbf{r}_0 + t\mathbf{r}_1 = (\mathbf{r}_1 - \mathbf{r}_0)t + \mathbf{r}_0.$$

Notice that if the origin of the ray corresponds to the viewing position, negative values of the parameter t represent points behind the viewer. Also, since the parameter value is a measure of the distance between the origin of the ray and a point along its length, it may be used to determine which of two points on the ray is visible. The unit of measure is the distance between  $\mathbf{r}_0$  and  $\mathbf{r}_1$ .

The representation of polygons is somewhat more involved. At some point in the modeling process, polygons are represented as a sequence of vertices, but this format is not especially convenient for all of the computations needed in a ray tracing algorithm. Indeed, the polygon will appear in several guises at various stages in the algorithm.

Recall that the primary computation finds the intersection of a ray and a polygon. This task will be broken down into two steps. The first step finds the intersection of the ray with the plane containing the polygon. The second step determines whether the intersection point actually lies within the polygon and, if so, computes the point on the unit square corresponding to the intersection point in the polygon.

Polygons may be thought of as having a parametric representation. p(u, v) is a point within the polygon, where u and v each range between zero and one. The vertices of the polygon correspond to the vertices of the unit square in the uv-plane:

$$\mathbf{p}_{01} = \mathbf{p}(0,1), \quad \mathbf{p}_{11} = \mathbf{p}(1,1), \\ \mathbf{p}_{00} = \mathbf{p}(0,0), \quad \mathbf{p}_{10} = \mathbf{p}(1,0).$$

An arbitrary point within the polygon is given by a bilinear interpolation of the vertices according to the values of u and v. Thus,

$$\mathbf{p}(u,v) = (1-u)(1-v)\mathbf{p}_{00} + (1-u)(v)\mathbf{p}_{01} + (u)(1-v)\mathbf{p}_{10} + (u)(v)\mathbf{p}_{11}$$

$$= (\mathbf{p}_{00} - \mathbf{p}_{01} + \mathbf{p}_{11} - \mathbf{p}_{10})uv + (\mathbf{p}_{10} - \mathbf{p}_{00})u + (\mathbf{p}_{01} - \mathbf{p}_{00})v + \mathbf{p}_{00}$$

$$= \mathbf{p}_{a}uv + \mathbf{p}_{b}u + \mathbf{p}_{c}v + \mathbf{p}_{d},$$

where

$$\mathbf{p}_a = \mathbf{p}_{00} - \mathbf{p}_{01} + \mathbf{p}_{11} - \mathbf{p}_{10}$$

$\mathbf{p}_b = \mathbf{p}_{10} - \mathbf{p}_{00}$

$\mathbf{p}_c = \mathbf{p}_{01} - \mathbf{p}_{00}$

$\mathbf{p}_d = \mathbf{p}_{00}$ .

The first stage of the ray tracing algorithm, which finds the intersection of the ray with the plane of the polygon, is most easily done if the plane surface is represented algebraically:

$s_p(\mathbf{q}) = \mathbf{n}_p \cdot \mathbf{q} + d_p.$

$s_p(\mathbf{q})$  is the distance from the plane of the polygon to an arbitrary point  $\mathbf{q}$ ;  $\mathbf{n}_p$  is the normal vector of the plane; and  $d_p$  is the distance from the plane to the origin. Thus, the intersection of the plane and the ray can be determined from the solution of

$$s_p(\mathbf{r}(t))=0.$$

Substituting and solving for t, we find that

$$t = \frac{\mathbf{n}_p \cdot \mathbf{r}_0 + d_p}{\mathbf{n}_p \cdot (\mathbf{r}_0 - \mathbf{r}_1)}.$$

If  $\mathbf{n}_p \cdot (\mathbf{r}_0 - \mathbf{r}_1) = 0$ , then the ray is parallel to the plane and therefore does not intersect it. Otherwise, t exists and can be used to find the point of intersection  $\mathbf{p}_r$ .

Having found the position along the ray, the next stage of the ray tracing computation determines the position on the polygon of the point where the ray and polygon intersect. That is, it finds u and v such that  $\mathbf{p}(u,v) = \mathbf{p}_r$ . It turns out that u and v can be determined independently of one another. To see how this may be done, first consider the family of lines derived by mapping constant u lines from the uv-plane to the plane of the polygon. Corresponding to each member of this family, there is a plane that both contains the line through the polygon and is perpendicular to the polygon itself. The equation describing this family of planes is

$$s_u(\mathbf{q}) = \mathbf{n}_u(u) \cdot \mathbf{q} + d_u(u).$$

Again,  $\mathbf{n}_u(u)$  is the vector normal to a plane, and  $d_u(u)$  is the perpendicular distance from the plane to the origin. The value of u at the intersection point  $\mathbf{p}_r$  may be determined by solving  $s_u(\mathbf{p}_r) = 0$ . It remains to find expressions for  $\mathbf{n}_u(u)$  and  $d_u(u)$ .

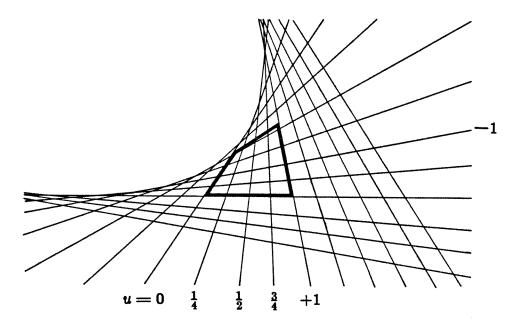

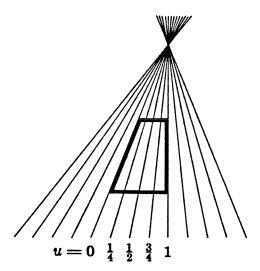

Figure 2-8. Some lines of constant u shown in the plane of a polygon that has no parallel edges. Some points on the plane do not lie along any of the lines; others are on two lines. For example, the  $u = \frac{1}{2}$  and u = -1 lines intersect inside the polygon.

Before deriving these equations, it may be helpful to examine more closely the situation leading to them. First of all, consider the case, shown in Figure 2-8, where no two edges of the polygon are parallel. In this configuration, some points in the plane of the polygon lie along more than one of the constant u lines. The interior of the polygon is part of the area that is covered more than once. Also, there are other portions of the plane that do not lie along any of the constant u lines. This situation suggests that the expression for the constant u planes will be quadratic in u, so that solving this expression for u at the point of intersection  $p_r$  will yield two solutions. The solutions will be real if  $p_r$  lies in a portion of the plane that is covered by the lines of constant u; otherwise, they will be imaginary. Only one of the real roots, however, will lie between zero and one, representing an intersection on the interior of the polygon.

A distinctly different expression for the constant u planes arises if the v=0 and v=1 edges of the polygon are parallel, as in Figure 2-9. In this case, the lines of constant u cover most of the polygon plane exactly once, but there is a single point through which every line passes. This means that for most values of  $\mathbf{p}_r$ , it is possible to compute a unique value for u, but if  $\mathbf{p}_r$  happens to be the point common to all of the constant u lines, no solution for u will exist. This behavior suggests that the expression for u as a function of  $\mathbf{p}_r$  will take the form of a ratio.

It may now be appropriate to mention the reason for excluding concave polygons

Figure 2-9. Some lines of constant u shown in the plane of a polygon whose v = 0 and v = 1 edges are parallel. Every point on the plane is on exactly one constant u line except for the single point through which all such lines pass.

from consideration. The problem is that the interpolation scheme used to find points on the interior of a polygon, given its vertices and a uv-coordinate pair, simply doesn't work if the polygon is concave. The difficulty is illustrated in Figure 2-10. First, some of the points on the interior of the polygon can be obtained from either of two valid uv-coordinate pairs. This fact alone would make it impossible to implement texture mapping or any of the related techniques. It also means that the computations for u and v would be mutually dependent. Second, the fatal flaw is that there are valid combinations of u and v that actually give rise to points outside of the polygon. Thus, concave polygons clearly fail to function within the framework that has been set up here.

The normal vector  $\mathbf{n}_{u}(u)$  in the equation of the constant u plane may be derived from the parametric representation for the family of constant u lines in the polygon:

$$\mathbf{p}_{u}(v) = \mathbf{p}(u, v).$$

Note that this line is parametric in v for any fixed value of u. A vector in the same direction as this line of constant u can be formed by taking the difference of two points along the line, say  $\mathbf{p}_{u}(0)$  and  $\mathbf{p}_{u}(1)$ . A vector that is normal to the constant u plane must be perpendicular both to this direction vector and to the normal vector of the polygon plane. A suitable vector may be conveniently constructed with a cross product:

Figure 2-10. A concave polygon shown with some lines of constant u. Notice that each of these lines corresponds to a value of u between zero and one, and also that the lines are restricted to the segment where  $0 \le v \le 1$ . Because there are valid combinations of u and v that specify points outside the polygon, concave polygons must be disallowed.

$$\mathbf{n}_{u}(u) = (\mathbf{p}_{u}(1) - \mathbf{p}_{u}(0)) \times \mathbf{n}_{p}$$

$$= ((\mathbf{p}_{a}u + \mathbf{p}_{b}u + \mathbf{p}_{c} + \mathbf{p}_{d}) - (\mathbf{p}_{b}u + \mathbf{p}_{d})) \times \mathbf{n}_{p}$$

$$= (\mathbf{p}_{a} \times \mathbf{n}_{p})u + (\mathbf{p}_{c} \times \mathbf{n}_{p})$$

$$= \mathbf{n}_{a}u + \mathbf{n}_{c}.$$

Of course, the magnitude of this vector need not be one, so it is not necessarily a unit normal vector, but at least its direction is correct.

An expression for  $d_u(u)$  can be formed by substituting into the plane equation a point known to be on the constant u plane, setting the result to zero, and then solving for  $d_u(u)$ . Using the point  $\mathbf{p}_u(0)$  and solving  $s_u(\mathbf{p}_u(0)) = 0$  yields

$$d_{\mathbf{u}}(u) = -\mathbf{n}_{\mathbf{u}}(u) \cdot \mathbf{p}_{\mathbf{u}}(0)$$

$$= -(\mathbf{n}_{a}u + \mathbf{n}_{c}) \cdot (\mathbf{p}_{b}u + \mathbf{p}_{d})$$

$$= -(\mathbf{n}_{a} \cdot \mathbf{p}_{b})u^{2} - (\mathbf{n}_{a} \cdot \mathbf{p}_{d} + \mathbf{n}_{c} \cdot \mathbf{p}_{b})u - (\mathbf{n}_{c} \cdot \mathbf{p}_{d})$$

$$= d_{\mathbf{u}2}u^{2} + d_{\mathbf{u}1}u + d_{\mathbf{u}0}.$$

With this expression, along with the one for  $n_u(u)$ , the equation of the plane of constant u becomes

$$s_u(\mathbf{q}) = d_{uz}u^2 + (\mathbf{n}_a \cdot \mathbf{q} + d_{uz})u + (\mathbf{n}_c \cdot \mathbf{q} + d_{uc}).$$

The value of u at the point of intersection  $\mathbf{p}_r$  is the solution of  $s_u(\mathbf{p}_r) = 0$ :

$$d_{u_2}u^2 + (\mathbf{n}_a \cdot \mathbf{p}_r + d_{u_1})u + (\mathbf{n}_c \cdot \mathbf{p}_r + d_{u_2}) = 0.$$

In the case where the v=0 and v=1 edges of the polygon are not parallel,  $d_{uz}$  will not be zero, and this expression may be solved by substituting into the quadratic formula:

$$u = \frac{-(\mathbf{n}_a \cdot \mathbf{p}_r + d_{u1}) \pm \sqrt{(\mathbf{n}_a \cdot \mathbf{p}_r + d_{u1})^2 - 4(d_{u2})(\mathbf{n}_c \cdot \mathbf{p}_r + d_{u0})}}{2(d_{u2})},$$

or

$$\begin{split} u &= -\left[\left(\frac{\mathbf{n}_a}{2d_{uz}}\right) \cdot \mathbf{p_r} + \left(\frac{d_{u1}}{2d_{uz}}\right)\right] \\ &\pm \sqrt{\left[\left(\frac{\mathbf{n}_a}{2d_{uz}}\right) \cdot \mathbf{p_r} + \left(\frac{d_{u1}}{2d_{uz}}\right)\right]^2 - \left[\left(\frac{\mathbf{n}_c}{d_{uz}}\right) \cdot \mathbf{p_r} + \left(\frac{d_{u0}}{d_{uz}}\right)\right]}. \end{split}$$

This expression, of course, yields two solutions for u, but the only useful value is real and lies between zero and one. If both solutions are outside of this range, then either the ray and the polygon plane do not intersect, or the point of intersection is not inside the polygon. Otherwise, the value where  $0 \le u \le 1$  locates the intersection point, and the other one is spurious.

If the two planes of constant v are parallel, then  $d_{uz}$  will be zero, and the equation  $s_u(\mathbf{p}_r) = 0$  becomes

$$(\mathbf{n}_a \cdot \mathbf{p}_r + d_{u1})u + (\mathbf{n}_c \cdot \mathbf{p}_r + d_{u0}) = 0,$$

which has the solution

$$u = -\frac{\mathbf{n}_c \cdot \mathbf{p}_r + d_{uo}}{\mathbf{n}_a \cdot \mathbf{p}_r + d_{uo}}$$

Again, the value of u must exist and lie between zero and one for  $p_r$  to be inside of the polygon.

The technique just described is equally suitable for finding the value of v at the point where the ray strikes the polygon. As in the prior case, the family of planes corresponding to constant values of v is represented algebraically:

$$s_v(\mathbf{q}) = \mathbf{n}_v(v) \cdot \mathbf{q} + d_v(v).$$

Points along the constant v line are  $p_n(u)$ , so that the normal vector is

$$\mathbf{n}_{v}(v) = (\mathbf{p}_{v}(1) - \mathbf{p}_{v}(0)) \times \mathbf{n}_{p}$$

$$= (\mathbf{p}_{a} \times \mathbf{n}_{p})v + (\mathbf{p}_{b} \times \mathbf{n}_{p})$$

$$= \mathbf{n}_{a}v + \mathbf{n}_{b}.$$

Substituting this expression into  $s_v(\mathbf{q})$  and solving  $s_v(\mathbf{p}_v(0)) = 0$  for  $d_v(v)$  gives

$$d_v(v) = -(\mathbf{n}_a \cdot \mathbf{p}_c)v^2 - (\mathbf{n}_a \cdot \mathbf{p}_d + \mathbf{n}_b \cdot \mathbf{p}_c)v - (\mathbf{n}_b \cdot \mathbf{p}_d)$$

=  $d_{vx}v^2 + d_{vx}v + d_{vx}$ .

and so the complete plane equation is

$$s_{v}(\mathbf{q}) = d_{v2}v^{2} + (\mathbf{n}_{a} \cdot \mathbf{q} + d_{v1})v + (\mathbf{n}_{b} \cdot \mathbf{q} + d_{v0}).$$

In the non-parallel case, where  $d_{vz} \neq 0$ , solving  $s_v(\mathbf{p}_r) = 0$  produces two values for v:

$$\begin{split} v &= - \left[ \left( \frac{\mathbf{n}_a}{2 d_{vz}} \right) \cdot \mathbf{p_r} + \left( \frac{d_{v_1}}{2 d_{vz}} \right) \right] \\ &\pm \sqrt{ \left[ \left( \frac{\mathbf{n}_a}{2 d_{vz}} \right) \cdot \mathbf{p_r} + \left( \frac{d_{v_1}}{2 d_{vz}} \right) \right]^2 - \left[ \left( \frac{\mathbf{n}_b}{d_{vz}} \right) \cdot \mathbf{p_r} + \left( \frac{d_{v_0}}{d_{vz}} \right) \right]}. \end{split}$$

As before, the only one of these values that is meaningful is real and lies in the range  $0 \le v \le 1$ . If both values are out of range, then the ray misses the interior of the polygon. In the parallel case, where  $d_{v2} = 0$ , v is given by

$$v = -\frac{\mathbf{n}_b \cdot \mathbf{q} + d_{vo}}{\mathbf{n}_a \cdot \mathbf{q} + d_{vo}}.$$

Again, this solution is valid only if it exists and if  $0 \le v \le 1$ .

After the algorithm has examined enough polygons to locate the first point at which the ray strikes a surface, it must apply a lighting model to determine the apparent color of that point. This color will contribute to the color of a pixel in the final image. One such lighting model was devised by Bui-Tuong Phong [PHON75]. It works well in a variety of situations, yet it doesn't require extensive computation. Basically, Phong's model separates the light illuminating a point into ambient, diffuse, and specular components. An additional component for transmitted light may be used to model transparent or translucent surfaces. The overall intensity is the sum of these four components:

$$I = RI_a + \sum RI_p \cos i + \sum W(i)I_p(\cos s)^n + TI_t,$$

where

I =Final intensity value.

R = Proportion of light reflected by the surface.

$I_a =$ Intensity of the ambient illumination.

$I_p$  = Intensity of the point light source.

i = Angle between the light source and the surface normal vector.

W(i) =Specular reflection coefficient.

n =Shininess exponent.

s = Angle between the reflected light ray and the viewing ray.

T =Proportion of light transmitted by the surface.

$I_t =$ Intensity of light passing through the surface.

Notice that if there were more than one light source, the diffuse and specular components of each would simply be added together. Also, if the point on the surface is

shadowed from any of the light sources, the corresponding specular contributions are omitted from the computation. Finally, although the above description was couched in terms of a monochrome image, full color is equally possible by using three equations for the three components of the color vector.

The two cosine terms of the illumination equation may be evaluated by taking dot products of appropriate vectors. The value of  $\cos i$  may be computed from a unit vector in the direction of the light source 1 and the unit surface normal vector  $\mathbf{n}$ :

$$\cos i = \mathbf{n} \cdot \mathbf{l}$$

.

Determining the value of cos s requires a vector in the direction of reflected light in addition to the normalized vector to the viewing position:

$$\cos s = (-\mathbf{l} + 2\mathbf{n}\cos i) \cdot \left(\frac{\mathbf{r}_0 - \mathbf{r}_1}{\|\mathbf{r}_0 - \mathbf{r}_1\|}\right).$$

The value of W(i) can most easily be found by look up into a table indexed by  $\cos i$ . One more thing to notice is that R and T, the reflection and transmission parameters of the surface, need not be constant over the entire surface. It is sometimes useful to define them as functions of u and v so as to map a texture onto the surface. The values contained in these maps can be computed either directly as mathematical functions of u and v, or by using u and v as array indices. The index of refraction can be mapped in a similar manner.

A problem with the shading scheme presented above is that complicated surfaces made up of many polygons will appear faceted. Gouraud recognized this and suggested an approximation that smoothly shades such surfaces [GOUR71]. Subsequently, Phong devised an improved method that synthesizes a surface normal vector based on considerations more global than the properties of a single polygon. With the improved method, four normal vectors,  $\mathbf{n}_{00}$ ,  $\mathbf{n}_{01}$ ,  $\mathbf{n}_{11}$ , and  $\mathbf{n}_{10}$ , are associated with the four corners of a polygon. These vectors are chosen so as to somehow represent the overall surface in which the polygon is embedded. Normal vectors at points within the polygon are computed by interpolating the four corner vectors:

$$\mathbf{n_r}(u,v) = (1-u)(1-v)\mathbf{n_{00}} + (1-u)(v)\mathbf{n_{01}} + (u)(v)\mathbf{n_{11}} + (u)(1-v)\mathbf{n_{10}}$$

$$= (\mathbf{n_{00}} - \mathbf{n_{01}} + \mathbf{n_{11}} - \mathbf{n_{10}})uv + (\mathbf{n_{10}} - \mathbf{n_{00}})u + (\mathbf{n_{01}} - \mathbf{n_{00}})v + \mathbf{n_{00}}$$

$$= \mathbf{n_0}uv + \mathbf{n_0}u + \mathbf{n_0}v + \mathbf{n_0}d.$$

At this stage, the interpolated vector could be perturbed by some function of u and v in order to perform bump mapping. Finally, although the direction of this interpolated vector is correct, it must be normalized before it can be used in the shading computations as described above.

#### 2.3 A Ray Tracing Peripheral

As mentioned earlier, a ray tracing algorithm is not a particularly speedy way to make a picture. In fact, Whitted and Rubin have quoted CPU times in excess of an hour just to generate a single frame [WHIT80, RUBI80]. Whitted also reported that between 75% and 95% of this time was spent finding the intersections of rays and surfaces. These findings suggest that some hardware support for the intersection computations could dramatically improve the running time of a ray tracing algorithm.

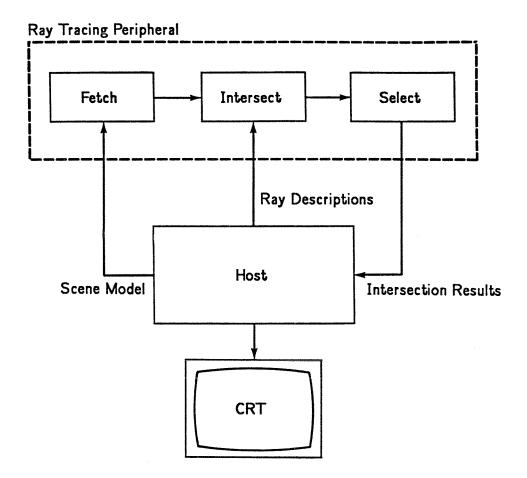

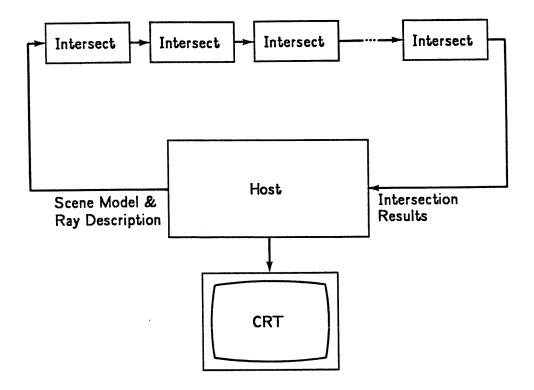

The ray tracing processor proposed in this section acts as one of the peripheral devices of a medium-sized host computer. Its primary task is to find intersections between the rays and polygons supplied by the host machine. The ray tracing peripheral has its own copy of the scene model, not only to reduce the load on the host's memory, but also to permit the model to be organized in a way that is suitable for the intersection computations; the host, however, retains control of the ray tracing algorithm. After the scene model has been loaded into the peripheral processor, communications between the host and the peripheral consist of rays to be traced and the results of those requests. This division of labor is convenient for two reasons. First, since the peripheral processor is not burdened with the control of the ray tracing algorithm, its data paths may be more easily optimized for computing intersections. Second, the algorithm can be very flexible because it is implemented as a program in the host machine, yet its performance is acceptable because the expensive computations are implemented in hardware.

#### 2.3.1 Host-Peripheral Interaction

To understand how the host computer and ray tracing peripheral cooperate to make pictures, it is helpful to examine the individual steps required in the process of image generation. First of all, the host must prepare the scene model in a suitable form and transfer it to the peripheral device. Ray tracing is an object space algorithm, which means that it operates on a model expressed in a full, three-dimensional coordinate system. In particular, the model representation is independent of viewpoint, so the host can generate several views of the same scene without reloading the model. When the model does have to be modified, only those surfaces that actually change need be sent to the peripheral. This property is useful for making movies depicting motion through a relatively fixed scene.

After loading the surface model, the host computer can begin to generate the image. For each pixel on the screen, it selects the corresponding vision ray emanating from the viewing position. It then sends a specification of this ray to the ray tracing peripheral. At some later time, the peripheral responds by reporting whether this ray intersects any polygon in the scene model. If an intersection has occurred, the peripheral also reports the identity of the intersecting polygon that is closest to the

viewing position. Notice that this polygon is the one that would be visible along the original ray. Additionally, the peripheral computes the three-dimensional spatial coordinates and two-dimensional uv-coordinates of the intersection point, and the distance from the viewing position to the point of intersection.

After having retrieved the result of the ray tracing operation, the host machine computes the color of the pixel. This computation may in turn require more rays to be traced. For example, if the original ray struck a reflective or refractive surface, the host uses the polygon identity, the point of intersection, and the normal vector at the intersection point to generate a new ray. It then passes this new ray to the ray tracing peripheral for processing. If shadowing is being modeled, the point of intersection and the direction to the light source combine to form still another new ray. In this case, however, the ray is marked as a shadow ray before it is transferred to the peripheral, since the exact identity of the polygon occluding the light source is unimportant and the peripheral can save some time by not attempting to find the closest such polygon. The host computer determines pixel colors on the basis of the results of the ray tracing operations together with additional information about the scene model, possibly including surface coloration and texture information that was never passed to the peripheral device. Once computed, the pixel color may be written to a file on disk, or stored directly in a frame buffer for immediate display.

One way to view the interaction between the host machine and the ray tracing peripheral is to regard the peripheral as a hardware subroutine of a program running in the host. Thus, whenever the ray tracing algorithm would otherwise invoke a subroutine to do an intersection computation, it now invokes a computation in another processor. This view of the situation is, however, somewhat inadequate, because it suggests that the host machine must wait while the peripheral completes its task, thereby missing an opportunity for exploiting parallel operation. A better way to utilize the hardware is to maintain queues between the host and the peripheral. The first queue contains rays to be traced. These are supplied by the host and removed by the peripheral as it becomes idle. The second queue buffers results transmitted in the opposite direction. In order to make use of these queues, the host machine would be multiplexed between two tasks. The first task generates vision rays that correspond to pixels in the final image, and it runs whenever the host would otherwise be idle. The second task processes the results of the ray tracing requests, possibly generating new requests itself. It is this second task that computes actual pixel colors.

The interesting feature of the two-task ray tracing algorithm just described is that it is completely asynchronous. There is no way to predict the exact order in which pixel colors will be computed. This works because the rays are mutually independent; therefore, the order in which they are processed does not affect the outcome of the computation. In this case, only two processors, the host machine and the ray tracing peripheral, are working at the same time, but the fact that rays can be traced independently and in any order offers a foothold for even greater concurrency. Machines capitalizing on this extra concurrency are the subjects of later sections. For

now, let us consider only the parallelism that can be introduced within the ray tracing peripheral itself.

#### 2.3.2 Operation of the Peripheral

The main task of the ray tracing peripheral, as mentioned earlier, is to find intersections of rays and polygons. It must also determine which of the polygons intersecting a given ray is closest to the viewing position. There are many ways of organizing the peripheral to solve this problem, and the approach taken here is one of the most straightforward. Upon receiving a ray from the host, the peripheral attempts to intersect the ray with every polygon in the scene. After doing so, it examines all of the intersections that it found and selects the one closest to the source of the ray. This means, of course, that every ray needed to make the picture must potentially be intersected with every surface in the scene model. Thus, the intersection processor must be very fast indeed if it is to perform this rather substantial task at an acceptable rate.

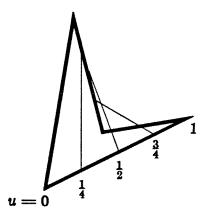

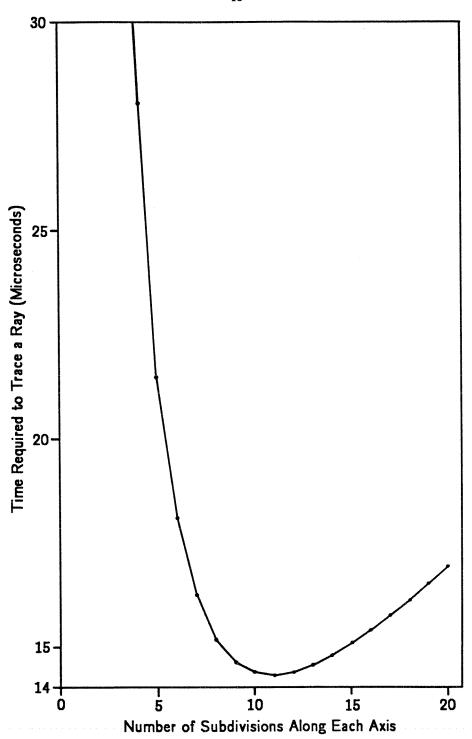

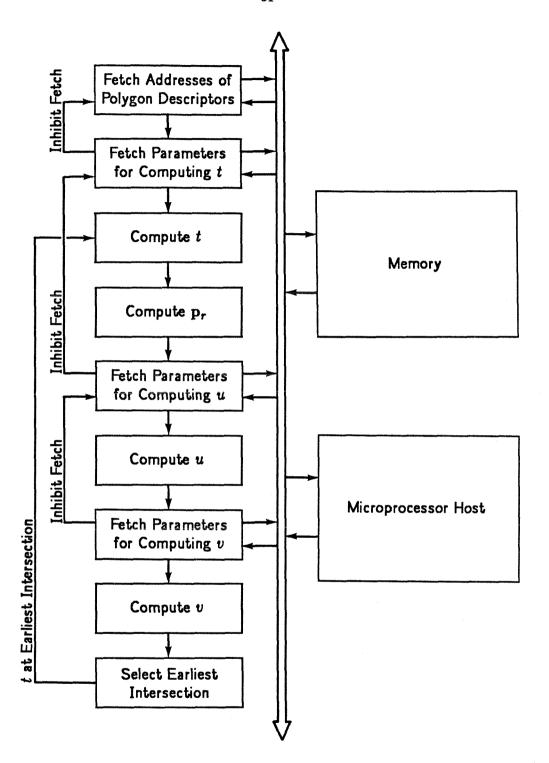

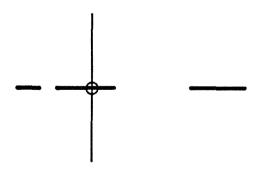

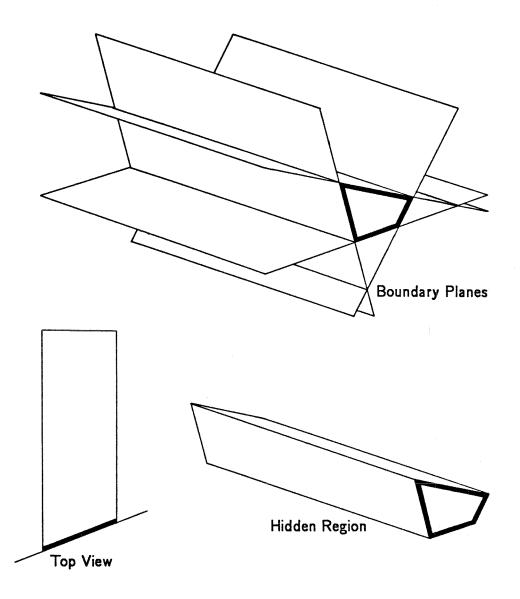

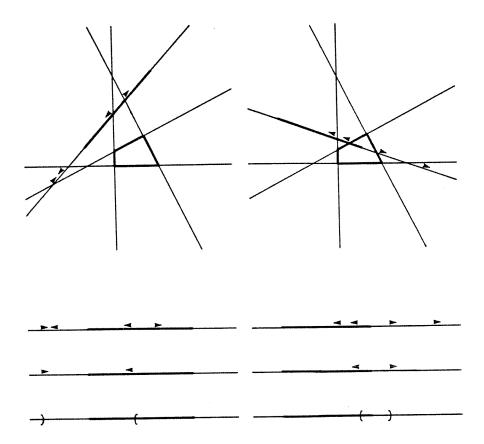

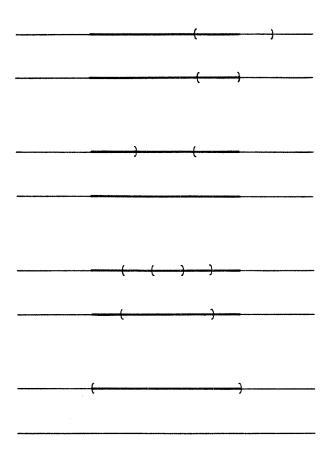

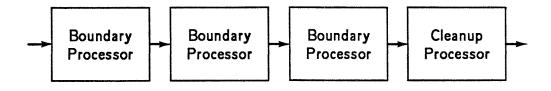

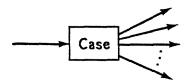

Fortunately, the operation of intersecting rays and polygons is sufficiently simple and regular that it may be pipelined in order to raise the throughput. The pipe can be thought of as having three stages, each of which may be pipelined internally; refer to Figure 2-11. The first stage fetches successive polygons from a scene model memory and passes their representations to the second stage, which performs the actual intersection computation. The third stage examines each new intersection and discards all but the one that is closest to the origin of the ray. After every polygon in the scene has passed through the pipeline, the final stage of the pipeline contains the result that should be returned to the host machine.

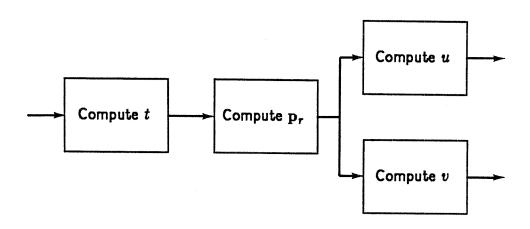

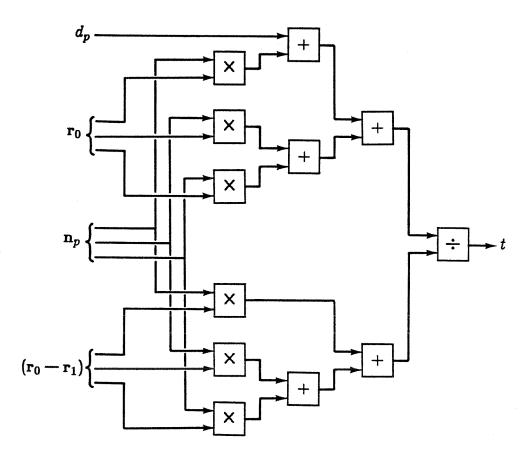

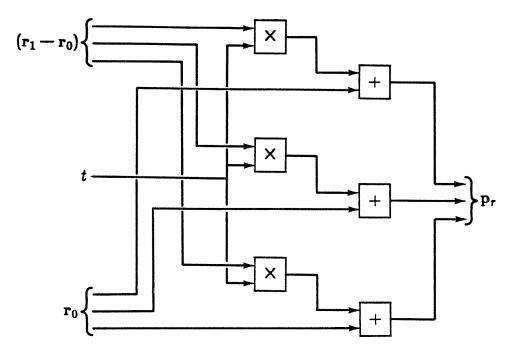

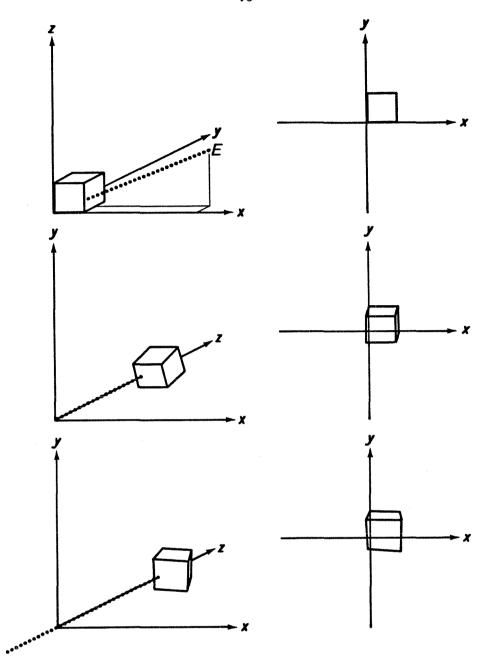

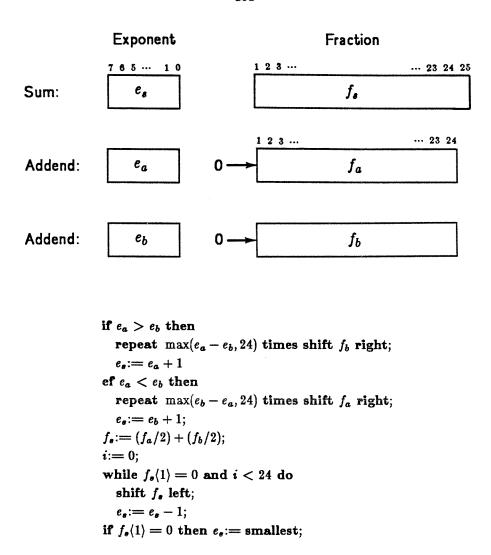

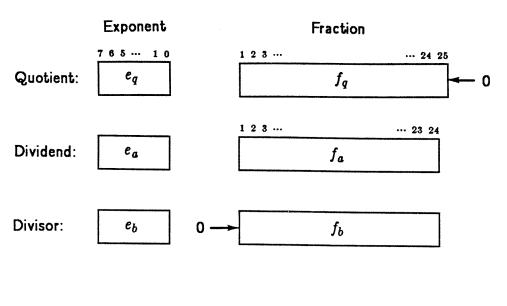

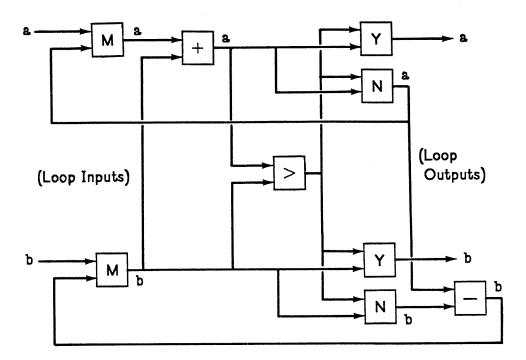

Clearly, most of the work required of the ray tracing peripheral is concentrated in the intersection stage of the pipeline. This stage may conveniently be pipelined internally so as to increase its performance. The three stages of the expanded intersection pipeline correspond to the three steps of the intersection computation that was described in the previous section and is summarized in Figure 2-12. The resulting pipeline is diagrammed in Figure 2-13. In the first stage, the processor determines the value of the ray parameter t at the point where the ray and polygon plane intersect. In the second stage, it computes the three-dimensional coordinates of the intersection point  $\mathbf{p_r}$ . Finally, in the third stage, it finds the parameter values u and v, which describe the position of the intersection point with respect to the polygon.

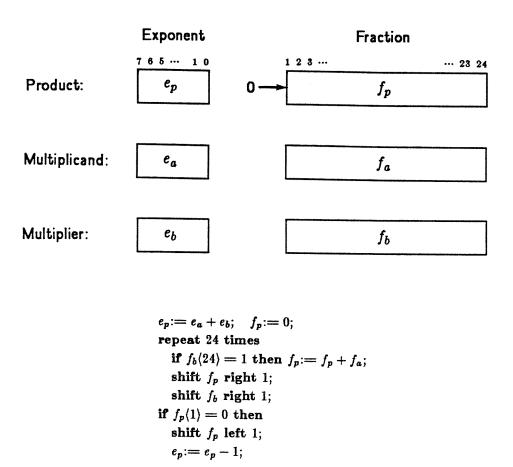

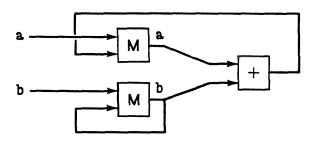

Within each stage of this expanded pipeline, still more concurrency can be exploited. Consider first the expression for t, which consists of the ratio of two inner products. The numerator and denominator of this ratio may be computed at the same time. Further concurrency is available within each inner product operation, since the three required multiplications may occur simultaneously, and the additions may be pipelined. Thus, the computation of t can be expanded into a four-stage pipeline:

Figure 2-11. The three major pipeline stages in the ray tracing peripheral.

Stage 1:

$$q_1 \leftarrow n_{px}r_{0x}$$

,  $q_2 \leftarrow n_{py}r_{0y}$ ,  $q_3 \leftarrow n_{px}r_{0z}$ ,  $q_4 \leftarrow (r_{0x} - r_{1x})n_{px}$ ,  $q_5 \leftarrow (r_{0y} - r_{1y})n_{py}$ ,  $q_6 \leftarrow (r_{0x} - r_{1z})n_{px}$ . Stage 2:  $q_7 \leftarrow q_1 + q_2$ ,  $q_8 \leftarrow q_3 + d_p$ ,  $q_9 \leftarrow q_4 + q_5$ . Stage 3:  $q_{10} \leftarrow q_7 + q_8$ ,  $q_{11} \leftarrow q_9 + q_6$ . Stage 4:  $t \leftarrow q_{10}/q_{11}$ .

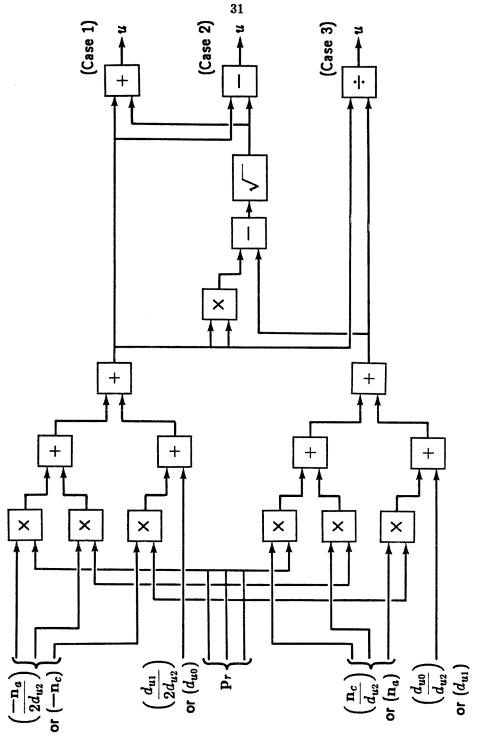

The required devices are shown in Figure 2-14. Next, the value of t is used to find the point  $\mathbf{p}_r$ . Note that each of its three components is independent of the others, so that all may be computed at the same time. Furthermore, pipelining may be employed within each of the individual component computations, as diagrammed in Figure 2-15. Finally, the expressions for u and v also involve dot products, and Figure 2-16 shows that concurrency is possible here as well.

$$t = \frac{\mathbf{n_p} \cdot \mathbf{r_0} + d_p}{\mathbf{n_p} \cdot (\mathbf{r_0} - \mathbf{r_1})}$$

$$\mathbf{p_r} = (\mathbf{r_1} - \mathbf{r_0})t + \mathbf{r_0}$$

$$t = \begin{cases} -\left[\left(\frac{\mathbf{n_a}}{2d_{u_3}}\right) \cdot \mathbf{p_r} + \left(\frac{d_{u_1}}{2d_{u_2}}\right)\right] \\ \pm \sqrt{\left[\left(\frac{\mathbf{n_a}}{2d_{u_2}}\right) \cdot \mathbf{p_r} + \left(\frac{d_{u_1}}{2d_{u_2}}\right)\right]^2 - \left[\left(\frac{\mathbf{n_c}}{d_{u_2}}\right) \cdot \mathbf{p_r} + \left(\frac{d_{u_0}}{d_{u_2}}\right)\right]} & \text{if } d_{u_2} \neq 0 \\ -\frac{\mathbf{n_c} \cdot \mathbf{p_r} + d_{u_0}}{\mathbf{n_a} \cdot \mathbf{p_r} + d_{u_1}} & \text{if } d_{u_2} = 0 \end{cases}$$

$$v = \begin{cases} -\left[\left(\frac{\mathbf{n_a}}{2d_{v_2}}\right) \cdot \mathbf{p_r} + \left(\frac{d_{v_1}}{2d_{v_2}}\right)\right] \\ \pm \sqrt{\left[\left(\frac{\mathbf{n_a}}{2d_{v_2}}\right) \cdot \mathbf{p_r} + \left(\frac{d_{v_1}}{2d_{v_2}}\right)\right]^2 - \left[\left(\frac{\mathbf{n_b}}{d_{v_2}}\right) \cdot \mathbf{p_r} + \left(\frac{d_{v_0}}{d_{v_2}}\right)\right]} & \text{if } d_{v_2} \neq 0 \\ -\frac{\mathbf{n_b} \cdot \mathbf{p_r} + d_{v_0}}{\mathbf{n_a} \cdot \mathbf{p_r} + d_{v_1}} & \text{if } d_{v_2} = 0 \end{cases}$$

Figure 2-12. Summary of the intersection computation.

Figure 2-13. A three stage pipeline to perform the intersection computation.

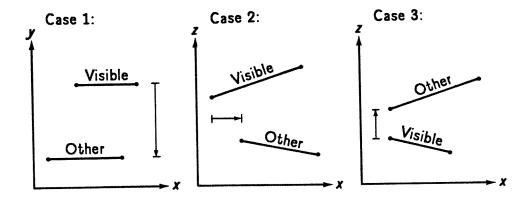

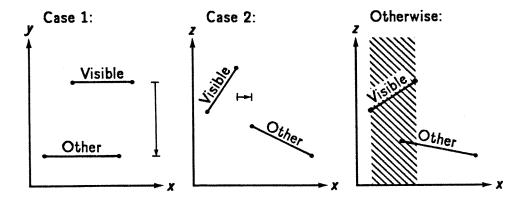

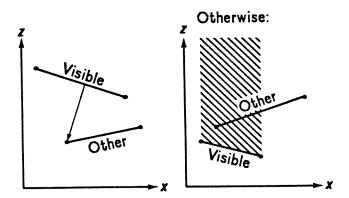

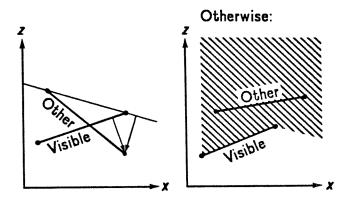

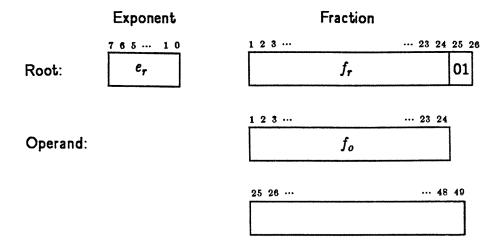

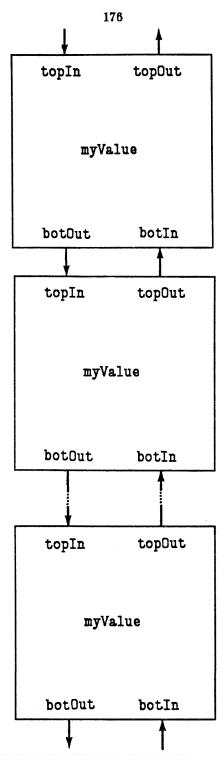

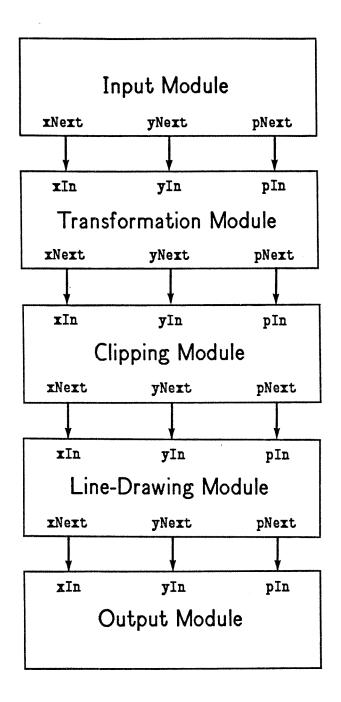

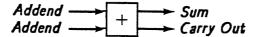

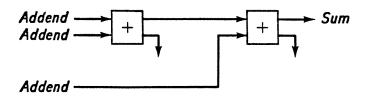

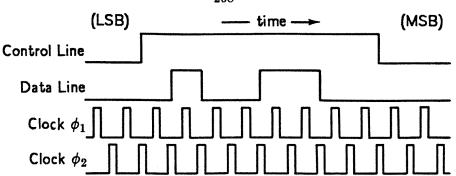

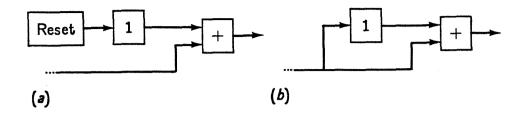

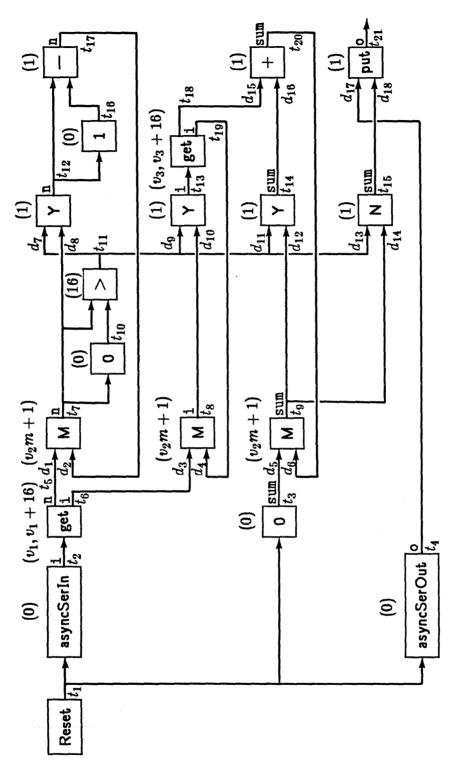

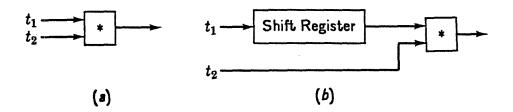

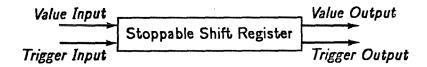

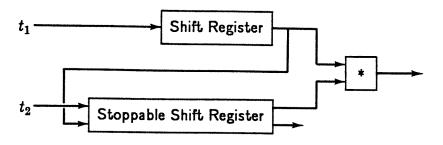

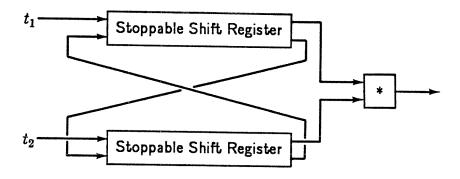

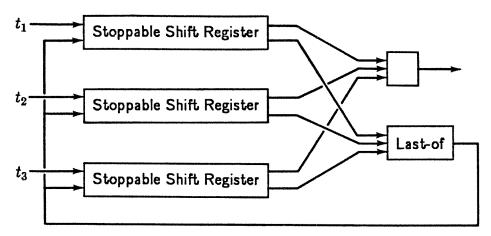

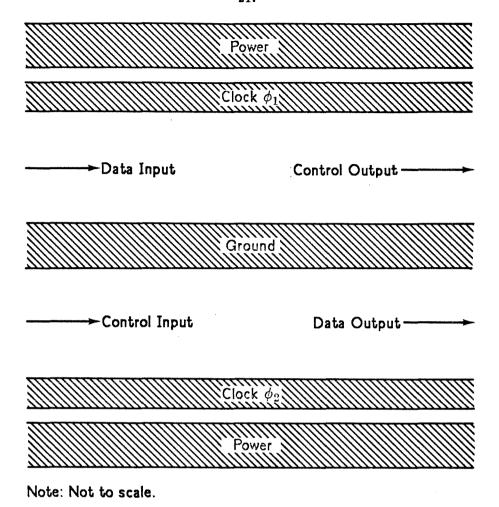

Figure 2-14. A four stage expanded pipeline to compute t. Note that the delays required in an actual implementation are not shown.