# An Energy-Complexity Model for VLSI Computations

Thesis by José Andrés Tierno

In Partial Fulfillment of the Requirements

for the Degree of

Doctor of Philosophy

California Institute of Technology

Pasadena, California

1995

(Submitted January 11)

© 1995 José Andrés Tierno All Rights Reserved Mamá, Papá, Rosana y Jorge.

# Acknowledgements

After six years of toil, the journey is over. Caltech was for me an incredible experience, for its people, its traditions, and its enormous accumulated wealth of scientific knowledge. I must thank all of the Caltech community, for all that I learned from them, either directly or indirectly.

From none did I learn more, however, than from Alain Martin. For six years he patiently guided my research, and taught me most of what I know about concurrency and asynchronous design.

A lot of other people has to be especially mentioned, because things would have been different without them. I want to thank Chuck Seitz, for having introduced me to the black magic of VLSI. I want to thank Drazen Borkovic, for having patiently listened to my ramblings for so many years. I want to thank Marcel van der Goot, for his programs, his IATEX macros, and many very stimulating conversations around a dictionary. I want to thank Tony Lee, for his wonderful CAD tools, and his incredible energy to fix what didn't work right or do enough. I want to thank Peter Hofstee, for all the lunch-time discussions. I want to thank Jessie Xu, for teaching me some Chinese characters and a little patience. I want to thank Wen-King Su for the Friday-night movies. I want to thank all of the CS185 students, for all of what they taught me.

Finally, a very special thanks to Mr. Oshima, for teaching me that of a one thousand mile journey, nine hundred and ninety nine is only half.

#### Abstract

An energy complexity model for CSP programs to be implemented in CMOS VLSI is developed. This model predicts with some accuracy the energy dissipation of the "standard" asynchronous VLSI implementation of a CSP program, associated to a given trace of that program. This energy complexity is used in the analysis of CSP programs, in order to optimize this high level representation of asynchronous circuits for energy efficiency. A lower bound to the energy complexity of a CSP program is derived, based on the information theoretical entropy per symbol of the input/output behavior of the CSP program. This lower bound abstracts the specification of the circuit (that is, its input/output behavior), from the implementation of the specification (that is, the text of the program), and therefore applies to any program that meets the specification. A number of techniques are presented to write programs of low energy complexity, and are applied to several examples.

To link the high level representation of circuits to the CMOS representation, several circuits are analyzed to provide standard translations for basic CSP operators into CMOS. In particular, a method for pipelining bus transfers using the sense-amplifier of the bus as a register is proposed.

# **Table of Contents**

| 1 | Intr | oducti | ion                                     | 1  |

|---|------|--------|-----------------------------------------|----|

|   | 1.1  | Why I  | Energy Efficiency?                      | 2  |

|   | 1.2  | Archit | tectural Energy Optimization            | 3  |

|   | 1.3  | Low-E  | Energy vs. Low-Power                    | 4  |

|   | 1.4  | Energy | y Model for High-Level Programs         | 5  |

|   | 1.5  | Low-E  | Energy Programming Techniques           | 5  |

|   | 1.6  | Shorte | er Delays for the Same Energy           | 6  |

|   | 1.7  | Energy | y and Entropy                           | 6  |

|   | 1.8  | Transi | stor Level Techniques                   | 7  |

|   | 1.9  | Contri | butions                                 | 8  |

|   | 1.10 | Conter | nts                                     | 8  |

| 2 | Ema  | N.I.   | adal for CSD Dragnama in CMOS           | 10 |

| 4 |      | 00     | odel for CSP Programs in CMOS           |    |

|   | 2.1  | 0.0    | y Index                                 | 11 |

|   |      | 2.1.1  | Sources of Energy Dissipation           | 11 |

|   |      | 2.1.2  | Linear Energy Model                     | 13 |

|   | 2.2  |        | y Model for CSP Programs                | 13 |

|   |      | 2.2.1  | Synchronization                         | 15 |

|   |      | 2.2.2  | Assignments and Communication           | 20 |

|   |      | 2.2.3  | Function Evaluation                     | 25 |

|   | 2.3  | Examp  | ole: Counter                            | 27 |

|   |      | 2.3.1  | Handshaking Expansion, Production Rules | 28 |

|   |      | 2.3.2  | Average Energy and Latency              | 28 |

|   | 2.4  | Examp  | ole: Memory Array                       | 30 |

|   |      | 2.4.1  | Energy Model and Optimization           | 32 |

|   |      | 2.4.2  | Multi-bank Memory Array                 | 34 |

|   | 2.5  | Summa  | ary & Conclusion                        | 36 |

| 3 | Ent | ropy and Energy of Reactive Computations        | 38  |

|---|-----|-------------------------------------------------|-----|

|   | 3.1 | Flat CSP                                        | 39  |

|   |     | 3.1.1 Flattening a CSP Process                  | 40  |

|   |     | 3.1.2 Flat Process Decomposition                | 41  |

|   | 3.2 | Energy and Entropy                              | 42  |

|   | 3.3 | Process Decomposition                           | 49  |

|   |     | 3.3.1 Program Approximation                     | 49  |

|   |     | 3.3.2 Breaking-Up the Input                     | 53  |

|   |     | 3.3.3 Control/Data Separation                   | 54  |

|   |     | 3.3.4 Pipelining/Parallelism                    | 56  |

|   | 3.4 | Summary & Conclusion                            | 59  |

| 4 | Lov | v-Energy Programs                               | 60  |

|   | 4.1 | Reactive Programs                               | 60  |

|   | 4.2 | Lazy Programs                                   | 62  |

|   |     | 4.2.1 Non-Causal Probe                          | 66  |

|   | 4.3 | Worst-Case Delay/Average Energy                 | 68  |

|   | 4.4 | Concurrency                                     | 71  |

|   | 4.5 | Summary & Conclusion                            | 77  |

| 5 | Ene | ergy/Delay Sizing                               | 78  |

|   | 5.1 | Delay vs. Energy Optimization                   | 79  |

|   | 5.2 | Gate Modeling                                   | 82  |

|   |     | 5.2.1 Transistor Modeling                       | 85  |

|   |     | 5.2.2 Macro Modeling                            | 87  |

|   |     | 5.2.3 Gate Model for Optimum-Energy Sizing      | 87  |

|   |     | 5.2.4 Parameter Reduction                       | 90  |

|   |     | 5.2.5 Posynomial Interpolation                  | 92  |

|   |     | 5.2.6 Sizing with a Pre-Computed Table          | 95  |

|   |     | 5.2.7 Sizing with a Post-Computed Approximation | 97  |

|   | 5.3 | Summary & Conclusion                            | 97  |

| 6 | Dat | apath Techniques                                | 99  |

|   | 6.1 | Register-to-Register Transfers                  | 99  |

|   |     | 6.1.1 Dual-Rail/One-Hot Encoding                | 100 |

|   |     | 6.1.2 Bundled-Data                              | 108 |

|   | 6.2  | Buses   |                                  | 110        |

|---|------|---------|----------------------------------|------------|

|   |      | 6.2.1   | Multiple-Sender Channel          | 111        |

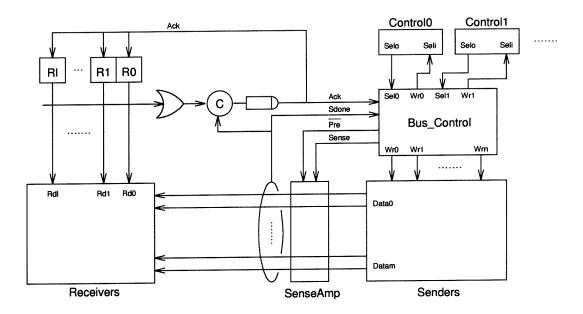

|   |      | 6.2.2   | Bus with Sense-Amplifier         | 111        |

|   |      | 6.2.3   | Pipelined Bus Transfer           | 115        |

|   |      | 6.2.4   | Multiple-Receiver Channel        | 116        |

|   |      | 6.2.5   | Safe Completion                  | 116        |

|   |      | 6.2.6   | Unsafe Completion                | 118        |

|   | 6.3  | Summ    | nary & Conclusion                | 119        |

| 7 | Self | -Limit  | ing Circuits                     | <b>120</b> |

|   | 7.1  | Heat 1  | Equation                         | 121        |

|   | 7.2  | Tempe   | erature Feed-Back                | 122        |

|   |      | 7.2.1   | Linear Feedback                  | 122        |

|   |      | 7.2.2   | Non-Linear Feedback              | 123        |

|   |      | 7.2.3   | Exponential Control              | 124        |

|   |      | 7.2.4   | On/Off Control                   | 125        |

|   | 7.3  | Currer  | nt Feedback                      | 125        |

|   |      | 7.3.1   | Sub-Optimal Voltage              | 126        |

|   |      | 7.3.2   | Current and Temperature Feedback | 127        |

|   | 7.4  | Summ    | ary & Conclusion                 | 127        |

| 8 | Exa  | mple:   | Processor Design                 | 128        |

|   | 8.1  | Specifi | ication                          | 128        |

|   | 8.2  | Instru  | ction Set                        | 130        |

|   |      | 8.2.1   | Control-Transfer                 | 130        |

|   |      | 8.2.2   | Arithmetic/Logic Operations      | 134        |

|   |      | 8.2.3   | Memory Addressing                | 134        |

|   | 8.3  | Proces  | s Refinement                     | 135        |

|   |      | 8.3.1   | Instruction Fetch                | 137        |

|   |      | 8.3.2   | Instruction Decoding             | 138        |

|   |      | 8.3.3   | Offset Register                  | 141        |

|   |      | 8.3.4   | Register-File Extraction         | 142        |

|   |      | 8.3.5   | Pipelining and Concurrency       | 143        |

|   | 8.4  | Proces  | s Decomposition of <i>PCunit</i> | 146        |

|   | 8.5  | Summa   | ary & Conclusion                 | 147        |

| 9  | Con   | clusion | ı & Fut | tu | re | 9 | W | <b>7</b> 0 | rk | ζ. |  |   |   |   |   |  |   |  |   |   |  | 149 |

|----|-------|---------|---------|----|----|---|---|------------|----|----|--|---|---|---|---|--|---|--|---|---|--|-----|

|    | 9.1   | Conclu  | sion    |    |    |   |   |            |    |    |  |   |   |   |   |  |   |  |   |   |  | 149 |

|    |       | 9.1.1   | How?.   |    |    |   |   |            |    |    |  |   |   |   | ٠ |  |   |  |   |   |  | 149 |

|    |       | 9.1.2   | Where?  | ?  |    |   |   |            |    |    |  |   |   |   |   |  |   |  |   |   |  | 150 |

|    |       | 9.1.3   | Why?    |    |    |   |   |            |    |    |  |   |   |   |   |  |   |  |   |   |  | 152 |

|    | 9.2   | Future  | Work .  |    |    |   |   |            | •  |    |  | • | • | • |   |  | • |  | • | • |  | 153 |

| Bi | bliog | raphy   |         |    |    |   |   |            |    |    |  |   |   |   |   |  |   |  |   |   |  | 155 |

# List of Figures

| 2.1 | Graph of $E_T/V_{DD}^2$ against $V_{DD}$ for a 4-bit counter (SPICE sim-    |    |

|-----|-----------------------------------------------------------------------------|----|

|     | ulation), and for the $3x+1$ engine, and the $1.6\mu m$ and $2.0\mu m$      |    |

|     | processors                                                                  | 14 |

| 2.2 | Extra circuits required to implement sequencing between two                 |    |

|     | blocks of concurrent processes. The fork and join trees can be              |    |

|     | configured in several ways                                                  | 16 |

| 2.3 | Energy cost of an assignment. $I_w^A$ and $I_r^A$ are the fan-in and        |    |

|     | fan-out of channel A; $I_w^y$ and $I_r^y$ are the fan-in and fan-out of     |    |

|     | register $y$                                                                | 21 |

| 2.4 | Process decomposition of $MEM$ as a two-dimensional array.                  |    |

|     | Only the channels corresponding to a read operation are shown.              | 32 |

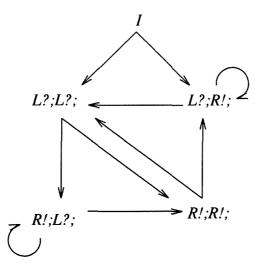

| 3.1 | Transition diagram for $P_f    P_g$ . A path on this diagram corre-         |    |

|     | sponds to an allowed sequence of input/output symbols                       | 58 |

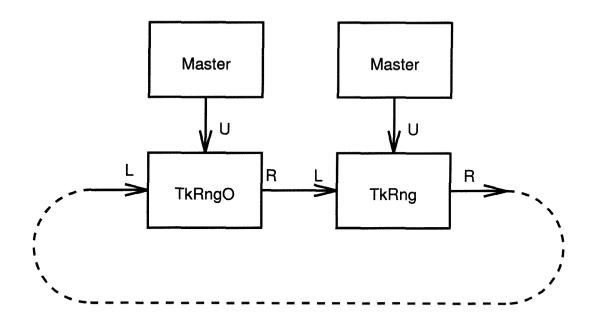

| 4.1 | Channel connections for a mutual exclusion token ring                       | 61 |

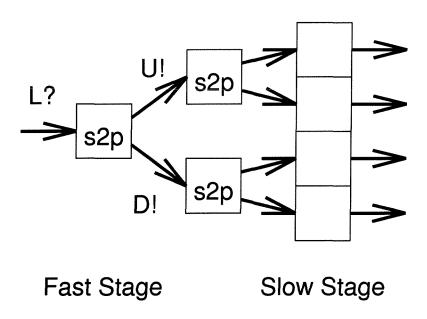

| 4.2 | Channel interconnection for a serial-to-parallel converter                  | 72 |

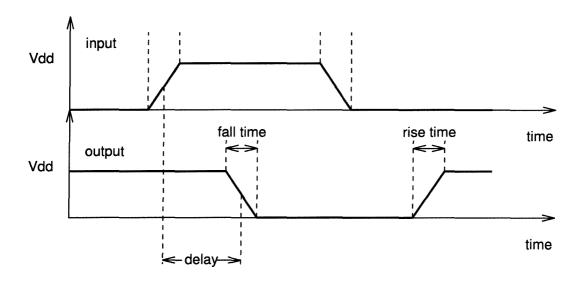

| 5.1 | Input/output voltage relationships                                          | 83 |

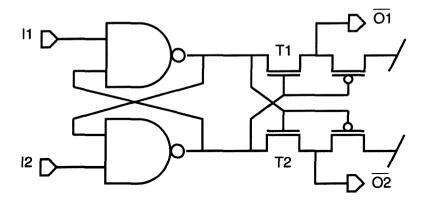

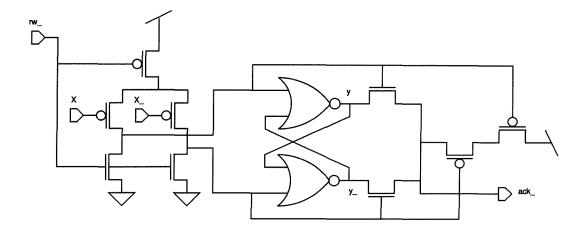

| 5.2 | Arbiter Implementation for QDI circuits                                     | 84 |

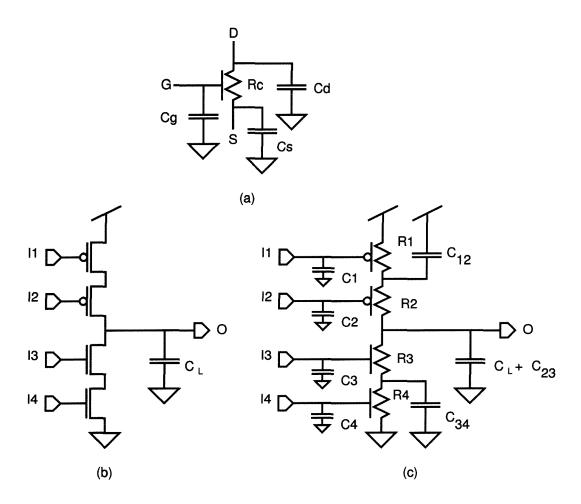

| 5.3 | RC-model for CMOS gates. (a) transistor model, (b) CMOS                     |    |

|     | gate, and (c) equivalent $RC$ -network model for that gate                  | 86 |

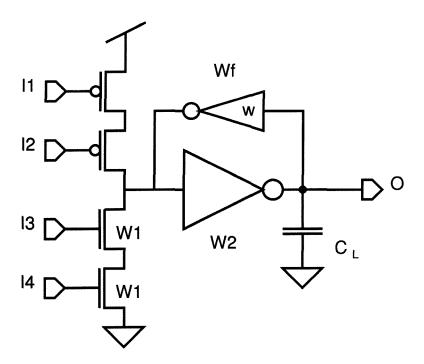

| 5.4 | Two-level circuit for a generalized C-element with weak inverter            |    |

|     | feedback                                                                    | 90 |

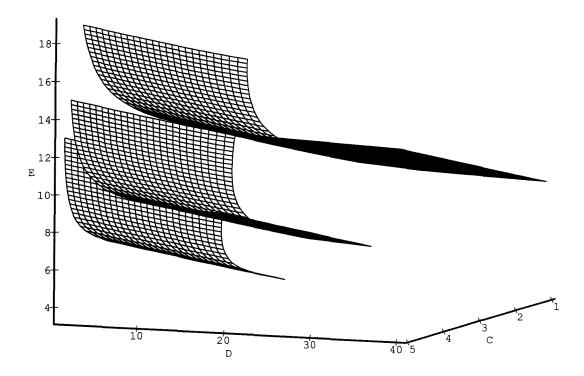

| 5.5 | $E	ext{-}D	ext{-}C$ surface for a two-stage generalized C-element, for sev- |    |

|     | eral values of $C_L$                                                        | 93 |

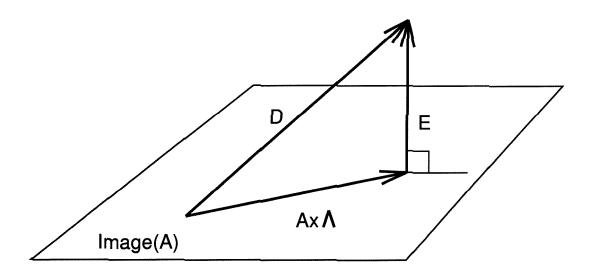

| 5.6 | Graphical representation of the error vector. The norm of the               |    |

|     | error vector is minimized when ${f A}\Lambda$ is the orthogonal projection  |    |

|     | of ${f D}$ on Image( ${f A}$ )                                              | 94 |

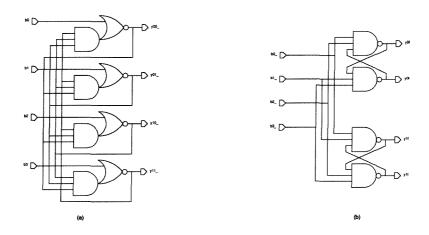

| 6.1  | Transistor circuit for a dual-rail, four-phase channel           | 101 |

|------|------------------------------------------------------------------|-----|

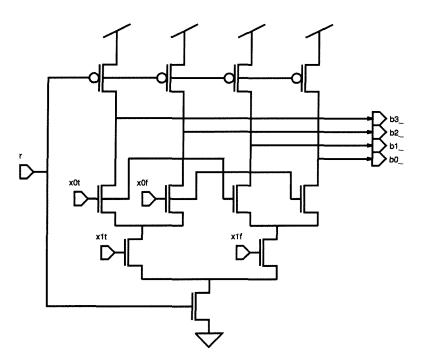

| 6.2  | Best transistor circuit for one-of-four sender, one stage        | 103 |

| 6.3  | Best transistor circuit for one-of-four sender, two stages       | 104 |

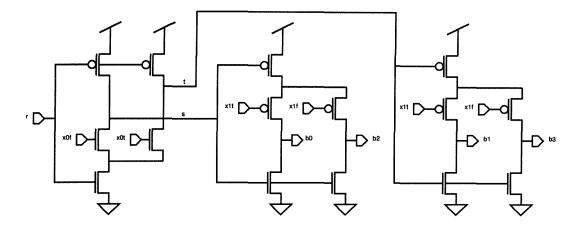

| 6.4  | (a) Quad-flop with one write port, positive inputs; and (b)      |     |

|      | double flip-flop, one write port, negative inputs. Completion    |     |

|      | circuit not shown.                                               | 105 |

| 6.5  | Three possible transistor circuits for the non-safe acknowledge  |     |

|      | of a quad-flop.                                                  | 107 |

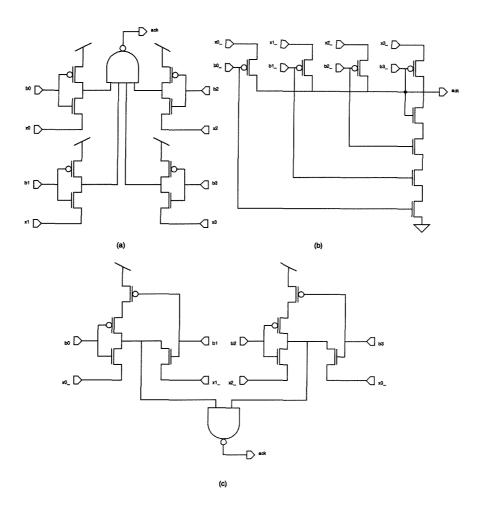

| 6.6  | Bundled data, register transfer circuit, non precharged. (a)     |     |

|      | Direct copy; (b) indirect copy                                   | 109 |

| 6.7  | Bundled data register-to-register transfer circuit, precharged.  | 110 |

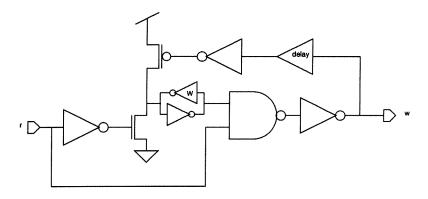

| 6.8  | Write pulse generation from the read pulse for a precharged      |     |

|      | register-to-register transfer                                    | 111 |

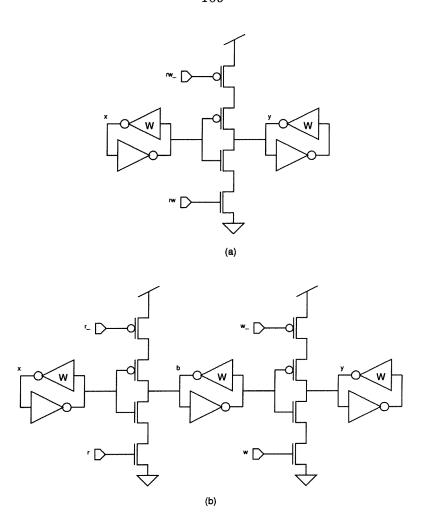

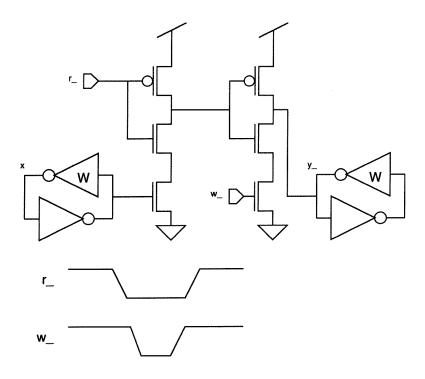

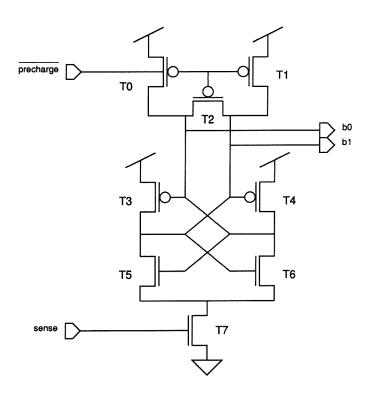

| 6.9  | Sense-amplifier circuit for asynchronous buses                   | 112 |

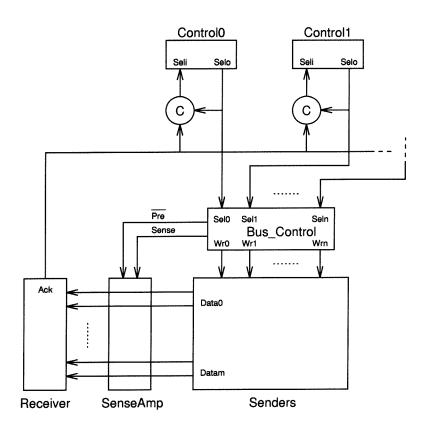

| 6.10 | Signal interconnection for a non-pipelined asynchronous bus      |     |

|      | with sense-amplifier                                             | 113 |

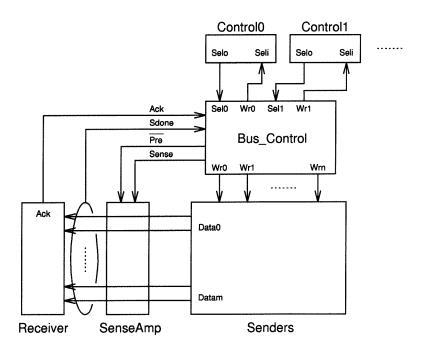

| 6.11 | Signal interconnection for a pipelined asynchronous bus with     |     |

|      | sense-amplifier                                                  | 114 |

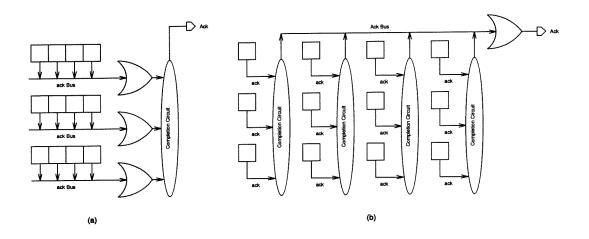

| 6.12 | Safe completion schemes for multiple receiver channels. (a)      |     |

|      | shared completion tree, and (b) local completion tree            | 116 |

| 6.13 | Unsafe completion scheme for multiple sender, multiple receiver  |     |

|      | channels. The bus transfer is pipelined to reduce the cycle time |     |

|      | and decouple senders from receivers                              | 118 |

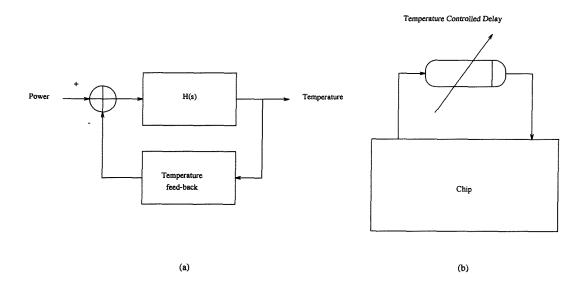

| 7.1  | Negative temperature feedback. H(s) is the transfer from power   |     |

|      | to temperature for the system composed of the chip, package,     |     |

|      | and cooling fluid. Temperature feedback can be implemented       |     |

|      | as a temperature-controlled delay inserted in a critical loop.   | 123 |

|      |                                                                  |     |

# List of Tables

| 2.1 | Measured (SPICE) and predicted (Model) energy index for sev-              |     |

|-----|---------------------------------------------------------------------------|-----|

|     | eral register/bus configurations (results in fF). The worst-case          |     |

|     | relative error is less than 2%                                            | 23  |

| 2.2 | Cost of the communications involved in accessing an $n \times b$ mem-     |     |

|     | ory array                                                                 | 31  |

| 2.3 | Cost of the communications involved in accessing an $l \times w \times b$ |     |

|     | memory array.                                                             | 33  |

| 8.1 | Instruction types according to their effect on the pc register            | 138 |

# Chapter 1

# Introduction

In this chapter we justify the need for a methodology to design energy-efficient digital circuits. Three main reasons are given: it is hard to supply integrated circuits with substantial amounts of power, it is hard to extract from an integrated circuit a substantial amount of heat, and, if the integrated circuit is to operate from batteries, the total amount of energy available is limited. We then explain what type of approach we have taken towards energy-efficient design, and then describe the contents of this thesis.

There are several aspects to be considered when designing an energy-efficient circuit. We can put our effort on the circuits we use to implement logic gates, we can put our effort on the technology we use to fabricate those circuits, or we can put our effort on the algorithm that the circuit uses to perform the computation. In this thesis, the main focus will be directed to improving the algorithms used in the computation, analyzing their performance based on their "energy complexity." This energy complexity is based on the high level algorithmic description of the computation performed by a circuit, and is an abstraction of the actual energy required by the circuit to operate.

In the end, the actual energy dissipation of the circuit is going to be a product, the average energy dissipation per transition, times the number of transitions. Energy complexity addresses the number of transitions required to perform a computation; circuit optimization and technology optimization address the average energy per transition. Both terms of the product can be optimized separately for better energy performance.

## 1.1 Why Energy Efficiency?

Electric energy, once spent, is transformed into heat that has to be taken from the chip surface. Heat dissipation is a relatively efficient process. DEC's alpha microprocessor, for example, dissipates 36 W and can be cooled with a heat sink and forced air circulation. For larger power requirements, Cray Computer's freon-cooling technology can eliminate the 150 kW that a Cray-2 requires for operation. However, the more sophisticated liquid-cooling technologies are expensive, and, as much as possible, we want to be able to use exclusively air cooling.

Air cooling cooling is efficient primarily because of conduction from the chip surface to the heat sink of the package, and convection from the heat sink into the cooling fluid. Radiation plays only a small role, since surface temperature is low — about 70°C — and radiated heat warms up the chassis around the heat sink. This heat also has to be removed by the cooling fluid.

The situation in a satellite is quite different. Because the available mass is finite, any heat put out by the devices on board heats the satellite. The only way of removing this heat is to radiate it into space. Radiation is inefficient at low temperature. Heat pumps can be used, but they require energy to operate and add to the weight of the satellite.

Another problem related to power is getting the energy to the chip's surface. For example, a chip that requires 22 W at 2.2 V uses 10 A of current. This large amount of current will force a high number of the pins in the package to be dedicated to power connections, reducing the number of pins available for signals. In some cases, this problem can be a more serious limit than the amount of heat that can be eliminated from the package.

Both problems are related to packaging technology. In the present state of the art, we can cool any circuit that we can build. However, sophisticated packaging has an elevated cost, and it pays off to design circuits that — for a given function and level of performance — use the minimum possible amount of energy.

If the circuit has to work out of batteries, as in portable computers, satellites, or pacemakers, every bit of power saved translates directly into extended battery life. Portable applications are becoming more important, especially in the area of portable computing and wireless networking. Current portable computers have a limited battery life, about one hour of operation per pound of battery. A practical amount of energy is between 5 to 8 hours of continuous operation: 5 hours for a transcontinental flight, 8 hours for a full day's work away from the office. Extra requirements on portable computers, like network connections, cellular phone connections, and more powerful processors and larger memories, will increase, in the future, the amount of energy required for operation, unless these portable computers are designed in a very different way than they have been designed so far.

### 1.2 Architectural Energy Optimization

Power optimization at the gate level is important, but if a circuit is inherently wasteful in energy, this optimization will only mitigate a bad problem. The situation is similar to the huge performance improvement of microprocessors over the last 20 years. An Intel 8080 from 1974, operating at 2.5 MHz, will execute about 0.5 MIPS, while an Intel 80486 from 1989, operating at 25 MHz will execute about 15 MIPS. There is a factor of three in circuit performance improvement, which is due only to better system level design. In the same way, low-power has to be designed-in at the system level.

Asynchronous circuits such as the Caltech Asynchronous Microprocessor [21,22] were designed with high performance in mind. It was not until the design was fabricated and tested that an interesting side effect of asynchronous design was noticed: the power delay figures for this processor were very good, executing 200 MIPS per watt at 5 V power supply, 600 MIPS per watt at 2 V power supply. In an asynchronous circuit, in principle, every transition contributes to the computation, and there are no hazards or spurious transitions. Inactive circuits only consume static power, which, in CMOS technology, is a small fraction of the total. On the other hand, it is not unusual for a clocked circuit to spend about a third of the total power just driving the clock lines (this has to be done irrespective of the level of activity of the circuit). On the down side, asynchronous operation may require extra transitions for synchronization, which do not directly contribute to the computation, as well as dual-rail implementation of many logic blocks.

This architectural efficiency is not exclusive of asynchronous design. They can be, and have been, used in the design of low-power synchronous systems.

However, in asynchronous designs the implementation comes for "free": no extra circuitry is needed to shut down the idle parts of the system.

This thesis has, as a central idea, the concept that the sources of energy dissipation can be pinpointed in the high level description of the circuit; this description can then be optimized to eliminate those sources whenever possible. Not all high level descriptions or design methodologies are suitable for such a manipulation. There has to be some correspondence between the operators described in the high level specification language, and the circuits actually generated. There has to be a match as well between the operations described in the specification language, and the activity in the different parts of the circuit.

#### 1.3 Low-Energy vs. Low-Power

Electrical power dissipation has been used as a figure of merit for energy efficient applications. Power is a convenient measure for synchronous circuits with no power management, where power dissipation is very much independent of the level of activity of the circuit. In this context, reducing power will reduce energy consumption. Asynchronous operation is better described in terms of reactive programs: energy is dissipated only when the circuit is active. For asynchronous systems, a proper measure of performance is the "energy per operation." This metric measures the energy required to execute an instruction, fetch a piece of data from memory, service an interrupt, etc. To maximize the battery life, we can minimize the average energy per operation, that is, we maximize the number of instructions that we can execute with one battery charge.

Energy per operation is an additive quantity. Given a computation described in terms of some more elementary operations, we can calculate the energy required to execute that computation by adding the energies required by the elementary operations. In this way, we can compare different algorithms to execute the same computation in terms of energy efficiency, independent of timing considerations. A comparison based on power requires precise knowledge of timing and the way in which the computation is going to be implemented.

## 1.4 Energy Model for High-Level Programs

The first step towards tying the high level description of a system to the energy performance of the circuit itself, is having an energy model, not of the circuit, but of the high level constructs — a model that can predict accurately enough what is going to happen in the circuit before the circuit is even designed. Accuracy is necessary in relative terms; at this level, we want to compare high-level designs, or, given a design, see how we can improve on that design. This model must somehow express the trade-offs that are possible at the circuit-level design stage. For example, for each delay we can design the most efficient circuit in terms of energy per operation; this delay-to-energy function becomes part of the model. We build the model for more complex operators using the models for the parts of those operators.

This energy model is expressed as the energy complexity of the CSP program that we use as the specification for the circuit. This energy complexity counts the number of transitions executed by the program to compute a given trace, or set of traces, taking into account the fan-in and fan-out of these transitions to give them weights.

### 1.5 Low-Energy Programming Techniques

Given the ideas presented in the previous sections, asynchronous circuits designed using Martin synthesis [18,19,20], appear to be an ideal target for the techniques to be presented in this thesis. In the Martin synthesis method, the circuit to be designed is specified as a CSP program [14]. This CSP program is then successively refined by semantics-preserving program transformations, expanded into handshaking variables, and finally translated into a network of boolean operators. Each CSP operator (send, receive, add, etc.) corresponds to some specific circuitry; every time that a CSP statement is executed, the corresponding circuitry is activated.

The techniques to be presented here are of general use; they can be applied to other design methodologies, even to synchronous circuits. There is, however, an underlying assumption that the target technology is CMOS, or any other technology where the static power dissipation (that is, the power that is independent of the level of activity of the circuit) is only a small part

of the total power dissipation. The energy complexity techniques assume that energy has to be spent only to change the state of the circuit, and no energy is required to maintain the state of the circuit.

Low-energy programs are reactive: work is done only when requested by the environment. In a CSP program, this characteristic applies to individual processes and excludes busy-waiting or input-polling strategies.

Low-energy programs are "lazy": work is postponed as much as possible, reducing preparatory work to a minimum and hoping to avoid unnecessary computation. Lazy programs exhibit a very good average-delay average-power product, at the cost of an increased worst-case delay. The trade-off between energy per computation and worst-case delay is the most important consequence of lazy programming.

### 1.6 Shorter Delays for the Same Energy

Low-energy circuits will almost always have worse delays than circuits built for speed. It is important to see how to make these delays shorter, without paying too much of a price in energy.

Techniques such as pipelining, caching, or concurrency, have been well exploited to increase the throughput of digital systems. We look at these techniques from the low-energy point of view, to see what their cost or benefit is, which ones are preferable, or when to use each of them.

In asynchronous systems, communication reshuffling can increase throughput, by making signal dependencies closer to what data dependencies are for the registers in the circuits. This communication reshuffling is an important optimization because it almost never has an energy overhead.

#### 1.7 Energy and Entropy

The energy complexity of a CSP program is used as an indication of how efficient this program is, and can be used to compare two solutions to the same problem. There is, however, the following question: given a specification, what is the lowest energy complexity of any program that satisfies that specification? If we can compute this lower bound, we can compare our solutions not only to each other, but to the best possible solution.

Such a lower bound can be computed from the input/output behavior of the specification. If the sequence of input/output symbols is completely predictable, then there is no need to compute it (we already know the result), and the minimum energy complexity is zero. If the sequence of input/output symbols is completely random, then there are no "easy" ways of computing that sequence, and the minimum energy complexity is high. Based on these intuitive considerations, we look at the information-theoretic entropy of the sequences of input/output actions that the specification requires. Entropy can be used as a measure of the "randomness" of these sequences. As it turns out, this entropy can be used as a lower bound for the energy complexity of a CSP program; in some cases, this lower bound is tight.

There are other consequences of this lower bound. Because of the way it is constructed, we can apply information-theory results to the construction of CSP programs, using the statistics of the input/output sequences. Process decomposition, concurrency, pipelining, and control/data decomposition can be directed using entropy arguments. Also, entropy can be used to refine and simplify the specification of the problem.

#### 1.8 Transistor Level Techniques

The models used for evaluating the performance of CSP programs make some assumptions about how the corresponding circuit looks. For some types of operations, like register arrays, buses, completion trees, and control-signal buffering, the interaction between the parts is so important that they have to be treated as a unit.

These operations have to be designed with a great level of detail, going all the way to the transistor description. Even layout issues are of importance, and they will influence the parameters of the model. High-level optimization is very powerful, but the final product still will be a transistor circuit, and the characteristics of transistors have to be taken into consideration.

A good collection of datapath operators is also important, since it can be used to verify some of the assumptions made by the energy complexity model, and to compute parameter values in the model. We look, in particular, at efficient implementations for bus transfers, which are an expensive on-chip data movement operation.

#### 1.9 Contributions

This thesis makes the following contributions:

- It shows how to generate an energy model from the high-level description of a circuit. Because this model separates the high-level description of a circuit from the details of the implementation, it makes it possible to compare programs, or choose architectural parameters.

- It demonstrates a number of high level programming techniques to obtain low-energy circuits, or to improve on existing circuits.

- It demonstrates a number of high level programming techniques to improve the throughput of a program with a small cost in energy.

- It introduces a lower bound to the attainable energy complexity of a CSP program that has to satisfy a given specification. It also demonstrates how to use this lower bound to direct the process decomposition so that the energy complexity of the final program is as close as possible to the lower bound.

- It demonstrates a number of specialized datapath circuits for low-energy asynchronous design, in particular a pipelined bus transfer, using the sense amplifiers on the bus as an extra register.

- These techniques are applied to the design of a microprocessor, to show with an example the impact they can have.

#### 1.10 Contents

Chapter 1 is a brief introduction to the contents of this thesis.

Chapter 2 explains the causes of power dissipation in CMOS and proposes an energy model for CSP programs that takes into account trade-offs between energy, delay, and power supply voltage. A performance index is proposed that captures the essence of those trade-offs, enabling the designer to better compare alternative circuits for the same computation.

Chapter 3 analyzes the energy complexity of CSP programs, based on the input/output behavior of the specification of the program. As a result, we

derive a lower bound to the attainable energy complexity of any solution to a given specification. This lower bound is based on the information-theoretic entropy of the sequences of input/output symbols.

Chapter 4 takes a detailed look at low-energy programming. Reactive programming, lazy programming, energy/worst-case-delay trade-off, caching, pipelining, concurrency, and non-causal probes, are analyzed to evaluate their relative merits.

Chapter 5 shows that the minimum-delay transistor-sizing problem is equivalent to the minimum-energy transistor-sizing problem. We propose a gate energy/delay model for accurate minimum-energy sizing based on least-squares posynomial approximation of the gate equations.

Chapter 6 goes back to the transistor level issues of low-energy design. Some specialized circuits are proposed to deal with buses, register arrays, completion trees, and other datapath structures.

Chapter 7 discusses self-limitation as a way to prevent high-power asynchronous circuits from exceeding the maximum allowable chip temperature. We also show how we can select the supply voltage so that the circuit works at the highest possible speed.

Chapter 8 Shows how to apply some of the techniques described in this thesis to the design of an asynchronous microprocessor based on the architecture of the Caltech Asynchronous Microprocessor.

Chapter 9 makes some concluding remarks about this work.

# Chapter 2

# Energy Model for CSP Programs in CMOS

In this chapter we present an energy model for asynchronous circuits derived from the CSP specification of the circuit. The model is based on the energy dissipated per operation (i.e. executing one instruction of a processor, accessing one element of a memory array, etc.).

The CSP description abstracts the notion of timing by providing the partial ordering of actions that the circuit has to perform. Likewise, to calculate the energy per operation we do not need timing information; we only have to add the energy required by each of the sub-parts of that operation.

The energy dissipation of a CMOS circuit is dependent on the power supply: the speed of operation and the energy required to charge capacitors increases at higher voltages. In this chapter we derive an energy-based index of performance that is independent of the power-supply voltage and we use it to justify an energy model for asynchronous circuits based on the energy cost of communication actions. This model is based on counting transitions, in the sense that we tally all the actions in the trace of an execution of the CSP program. Just counting transitions is, however, not enough, since not all transitions are equivalent. Variables that are accessed from several places in the circuit are more expensive in energy than localized, non-shared variables. The extra read and write circuits and wires used to distribute the value of the variable increase the cost of switching that variable to a new value. It is possible to reduce the energy cost of a program and at the same time increase the number of transitions, either by making each of those transitions cheaper,

or by simplifying the average-case performance at the expense of the worst-case performance. Therefore, we take into account the fan-in and fan-out of all variables in the energy model.

As an example of the use of the energy model, we analyze the design of asynchronous memories. Memory subsystems are usually designed for speed and density, with secondary consideration given to energy. Memory is slow compared to processors; high throughput in memory is achieved through parallelism (wide data-words) and prediction (memory caching). These same design techniques can be used to improve energy performance.

First, we show how to partition a memory array to minimize access energy under the assumption that all addresses are equally probable. Second, we show how to use the statistics of long sequences of addresses to further reduce the average energy per access. These techniques result in a trade-off between area and energy per access. This analysis shows that conventional commercial architectures are not optimal from the point of view of energy efficiency.

### 2.1 Energy Index

The energy dissipation of a CMOS circuit is dependent on the supply voltage: the speed of operation and the energy required to charge capacitors increases at higher voltages. In order to evaluate the energy efficiency of a high level circuit description, we need a measure of energy dissipation that is independent of the supply voltage. In this section, we derive such an index of performance and use it in the following section to justify an energy model for asynchronous circuits based on the energy cost of communication actions and synchronization primitives.

#### 2.1.1 Sources of Energy Dissipation

CMOS circuits have three main sources of energy dissipation: leakage currents, short-circuit currents, and dynamic currents. The total energy dissipated during the execution of one operation,  $E_T$ , can be calculated as:

$$E_T = E_s + E_d + E_{sc} \tag{2.1}$$

where  $E_s$  is the energy dissipated by the sub-threshold leakage currents,  $E_d$  is the energy used for charging and discharging capacitors, and  $E_{sc}$  is the energy dissipated by the short-circuit currents.

Leakage currents come from the sub-threshold behavior of MOSFET's. For  $V_{GS} < V_{th}$ , the channel conductance,  $g_c$ , can be modeled by [33]:

$$g_c = I_c \frac{q}{kT} \exp\left(\frac{q(V_{GS} - V_{th})}{kT}\right)$$

(2.2)

All these currents add up and are responsible for an energy dissipation of the form:

$$E_s = \int V_{DD}^2 I_c \frac{q}{kT} \exp\left(-\frac{qV_{th}}{kT}\right) dt \tag{2.3}$$

where  $V_{GS} = 0$  is assumed. At the present state of the technology, energy dissipation due to leakage currents represents only a small fraction of the total power of a CMOS circuit.

Short-circuit currents originate in the short transients, as in the case of a CMOS inverter, when both pull-up and pull-down transistors conduct while the input signal switches between  $V_{thn}$  and  $V_{DD} - V_{thp}$ . This energy dissipation has the form [34]:

$$E_{sc} = \sum s_i \left( V_{DD} - 2V_{th} \right)^3 \tag{2.4}$$

where the  $s_i$ 's are proportionality constants, and the sum is made over all transitions executed in one operation. Short-circuit currents also play a significant role in storing a value into a flip-flop built from cross-coupled inverters.

Dynamic energy dissipation,  $E_d$ , comes from the energy used to charge the capacitors in the circuit. The capacitors are then discharged to ground, and the energy is not recuperated.  $E_d$  can be computed as:

$$E_d = \sum_{C_i} n_i C_i V_{DD}^2 \tag{2.5}$$

where the  $C_i$ 's are all the capacitors in the circuit, and  $n_i$  is the number of times the capacitor is switched in the execution of one operation. We rewrite Eq. 2.5 as:

$$E_d = K_L V_{DD}^2 (2.6)$$

#### 2.1.2 Linear Energy Model

Using Eqs. 2.4 and 2.6, and neglecting the effect of sub-threshold currents, we rewrite the energy equation as:

$$E_T = \left(K_L + K_S \frac{(V_{DD} - 2V_{th})^3}{V_{DD}^2}\right) V_{DD}^2 \tag{2.7}$$

Outside the sub-threshold region,  $(V_{DD} \gg V_{th})$ , Eq. 2.7 simplifies to:

$$E_T = (K_L + K_S V_{DD}) V_{DD}^2 (2.8)$$

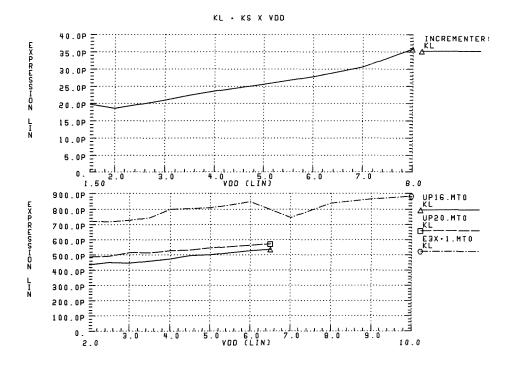

Fig. 2.1 shows  $E_T/V_{DD}^2$  as a function of  $V_{DD}$  for a 4-bit counter (SPICE simulation), and for the Caltech Asynchronous Microprocessor [21,22] and for a 3x + 1 engine [17] (measurement). This figure shows that the linear approximation of Eq. 2.7 is indeed accurate.

Based on these results, we propose, as an index of performance for an asynchronous CMOS circuit, the corresponding constants  $K_L$  and  $K_s$ . These indices are independent of the power-supply voltage and the speed of operation; furthermore,  $K_L$  and  $K_s$  are additive: we can calculate the index corresponding to an operation by adding the indices of all of its sub-operations.

As a first-order approximation, we assume  $K_s = 0$ , and use  $K_L$  as the energy performance index.

### 2.2 Energy Model for CSP Programs

The CSP specification of an asynchronous circuit corresponds very closely to its implementation. For each assignment, communication and function evaluation executed by the CSP program there will be a corresponding assignment, communication, function evaluation computed by the CMOS implementation. In fact, it is possible to do a purely syntactic translation from CSP into CMOS [3]. The CMOS implementation will dissipate energy only during the execution of the assignment, etc. This energy can be assimilated to the energy required to execute the corresponding CSP statement. To calculate the energy required to execute a CSP program, we add the energy required to execute each statement in a "canonical" trace of that program; we can also use the relative

Figure 2.1: Graph of  $E_T/V_{DD}^2$  against  $V_{DD}$  for a 4-bit counter (SPICE simulation), and for the 3x+1 engine, and the  $1.6\mu m$  and  $2.0\mu m$  processors.

frequencies of occurrence of each statement in the program on a reasonably large set of typical traces.

We would like to be able to map each statement into an energy performance index, independently of the other statements in the program. In general, it is not possible to do so; layout constraints result in the length — and therefore capacitance — of wires being affected by the connectivity of the whole circuit, not just the local connections. A detailed energy model would have to take into consideration the program as a whole, instead of individual statements.

The purpose of the model is, however, to study architectural trade-offs (e.g., compare bit-serial and parallel implementation of a function) or determine architectural parameters (e.g., determine the optimal width of a cache memory). A very detailed model with a large number of parameters can be

intractable and not that much more accurate if those parameters are layoutdependent (and, therefore, not well known before the layout is finished). At the architectural design stage a simpler model is desirable; we will base this model on the cost of communication, assignment, and selection.

The model proposed is based on the energy performance index. To each type of statement, we assign a capacitance that is representative of the energy that we expect that operation to cost in a typical implementation.

As much as possible, we want to remove syntactic dependencies from the energy model; similar programs that result in identical implementations should have the same energy performance. To this effect, we define an energy index for just a few constructs that can be used to implement any CSP program.

#### 2.2.1 Synchronization

The synchronization primitives of CSP are parallel composition ('||'), sequential composition (';'), guarded choice ('||'), repetition, and bullet synchronization between communication actions ('•'). Some of these primitives have zero energy cost, such as parallel composition. Some of these primitives require extra hardware to be implemented, such as guarded choice. We make an estimate of the extra hardware to assign a cost to each primitive.

#### Concurrency:

A basic postulate of this model is that parallel composition is free: no extra circuits are required in the implementation. If there is no synchronization between the  $P_i$ 's, we can write:

$$C(\langle ||i:1..n:P_i\rangle) = \sum_{i=1}^n C(P_i)$$

(2.9)

where C() is the cost function that assigns an energy index to a program.

#### Sequencing:

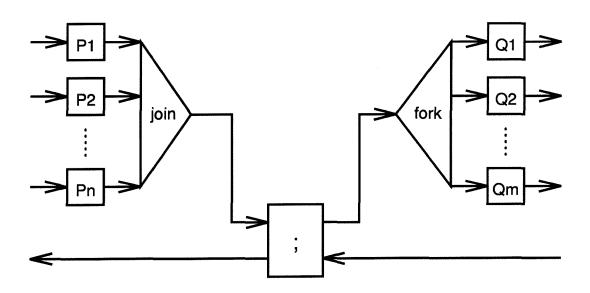

Sequencing synchronizes the end of an action with the beginning of the next action. If the previous action is the parallel composition of several actions, the end of those actions has to be synchronized with a tree, which has a linear energy cost. If the next action is the parallel composition of several actions, the start signal has to be distributed to them (maybe with a tree), which also

has a linear cost (see Fig. 2.2). We can express these costs with the following equation:

$$C(\langle ||i:1..n:P_{i}\rangle; \langle ||j:1..m:Q_{j}\rangle) =$$

$$C(\text{join}(n)) + C(\text{fork}(m)) + C(;) + C(\langle ||i:1..n:P_{i}\rangle) + C(\langle ||j:1..m:Q_{j}\rangle)$$

$$= K_{j}(n-1) + K_{f}(m-1) + K_{sc} + \sum_{i=1}^{n} C(P_{i}) + \sum_{j=1}^{m} C(Q_{j})$$

(2.10)

where  $K_j$ ,  $K_f$ , and  $K_{sc}$  are technology dependent constants. If n = 1 and m = 1, then the fork and join circuits are not needed, and the cost of sequencing is just the constant overhead  $K_{sc}$ .

**Figure 2.2**: Extra circuits required to implement sequencing between two blocks of concurrent processes. The *fork* and *join* trees can be configured in several ways.

Consider, for example, the following programs:

$$P_1 \equiv (A_1; ..; A_n) || (B_1; ..; B_n)$$

$$P_2 \equiv (A_1 || B_1); ..; (A_n || B_n)$$

Using Eqs. 2.9 and 2.10 we can compute the cost of  $P_1$  and  $P_2$  as:

$$C(P_1) = 2K_{sc}(n-1) + \sum_{i=1}^{n} (C(A_i) + C(B_i))$$

(2.11)

$$C(P_2) = (K_{sc} + K_f + K_j)(n-1) + \sum_{i=1}^{n} (C(A_i) + C(B_i))$$

(2.12)

$$C(P_1) - C(P_2) = (K_{sc} - (K_f + K_j))(n-1)$$

(2.13)

The relative efficiency of these two programs depends on the value of  $K_{sc}$  –  $(K_f + K_j)$ . Program  $P_2$  reduces the number of sequencing operators at the expense of reduced concurrency and extra join and merge circuits.

#### Choice:

Guarded choice can be implemented in a number of ways. We consider the cost of selection as the difference in cost between the following two programs:

$$PAR \equiv \langle \parallel i : 1..n : *[[G_i \longrightarrow A_i]] \rangle$$

and,

$$CHOOSE \equiv * \llbracket \llbracket \langle \llbracket i : 1..n : G_i \longrightarrow A_i \rangle \rrbracket \rrbracket$$

Program CHOOSE can be transformed into program PAR using the P and V operations on a semaphore:

$$CHOOSE \equiv \langle \parallel i: 1..n: *[[ G_i \longrightarrow P; [G_i \longrightarrow A_i \llbracket \neg G_i \longrightarrow \mathbf{skip}]; V ]] \rangle$$

If the guards  $G_i$  are stable, we can simplify the implementation to:

$$CHOOSE \equiv \langle \parallel i: 1..n: *[[G_i \longrightarrow P; A_i; V]] \rangle$$

The cost of choice is, therefore, the cost of implementing that semaphore. A number of implementations are possible and practical; a state variable per choice and an extra process can be used to that effect:

$$CHOOSE \equiv \langle \parallel i:1..n: *[[ \neg u \land G_i \longrightarrow u_i \uparrow; [u]; A_i; u_i \downarrow ]] \rangle$$

$$\parallel * \texttt{[[(\lor i:1..N:u_i];u\uparrow;[(\land i:1..N:\neg u_i];u\downarrow]]}$$

The cost of selection can be reduced to the cost of an Or-gate with fan-out proportional to the number of choices. If statement i is chosen, we can express the energy required to execute the selection plus statement i as:

$$C([\langle [ : i : 1..n : G_i \to A_i \rangle], i) = K_o \log_2 n + K_f n + C([\neg u \land G_i]; u_i \uparrow; [u]; A_i; u_i \downarrow)$$

(2.14)

where  $K_o$  and  $K_f$  are technology constants, corresponding to the energy cost of computing an n-input 'or' and forking the result to n receivers.

We can get rid of the indexation of the cost function by using the frequencies with which each statement is taken. We can write:

$$C([\langle [ : i : 1..n : G_i \to A_i \rangle]) = K_o \log_2 n + K_f n + \sum_{i=1}^n p_i C([\neg u \land G_i]; u_i \uparrow; [u]; A_i; u_i \downarrow)$$

(2.15)

where  $p_i$  is the conditional frequency of selection of statement i in the traces of the program, given the history of the computation.

Alternatively, if the guards are stable, the semaphore may be implemented with a selection tree:

$$\begin{split} CHOOSE \equiv & \; \langle \; || \; i:1..N: \; \; * \llbracket \llbracket \; G_i \longrightarrow U_i; A_i; \, U_i \; \rrbracket \rrbracket \rangle \\ & \; || \; * \llbracket \llbracket [\langle \; \rrbracket \; i:1..N/2: \; \overline{U}_i \longrightarrow L; \, U_i; \, U_i; \, L \; \rangle \rrbracket \rrbracket \\ & \; || \; * \llbracket \llbracket [\langle \; \rrbracket \; i:N/2+1..N: \; \overline{U}_i \longrightarrow H; \, U_i; \, U_i; \, H \; \rangle \rrbracket \rrbracket \\ & \; || \; * \llbracket \llbracket \; \overline{L} \longrightarrow L; L \; \rrbracket \; \overline{H} \longrightarrow H; \, H \; \rrbracket \rrbracket \end{split}$$

We apply this transformation recursively, and we get a cost of selection that is logarithmic on the number of choices and can be expressed as:

$$C([\langle [:i:1..n:G_i \to A_i \rangle]) = K_c \log_2 n + \sum_{i=1}^n p_i C([G_i]; U_i; A_i; U_i)$$

(2.16)

Either Eq. 2.15 or 2.16 can be used to compute the cost of guarded selection, depending on the expected implementation of the command. The linear cost

implementation is more efficient for low values of n, while the logarithmic cost implementation has more concurrency in the guard evaluation, and scales better for large values of n.

We can use the frequencies of the guarded commands to improve the average cost by using the Huffman tree for the  $p_i$ 's instead of a symmetric tree. We will see more about this on Chapter 3.

The remaining question is whether a better implementation (i.e., with a worst-case better that  $\log_2 n$ ) of the choice statement exists. We will prove that this is not true under some fairly general assumptions that are justified in terms of the CMOS energy model.

We implement the mutual exclusion between the branches of the selection statement with shared variables. Let n be the number of branches in the selection statement,  $s_i$  be the number of variables that have to be set in branch i to enter the critical region, and  $q_i$  the number of variables that have to be consulted in branch i to enter the critical region; each of these variables is written by  $w_{ij}$  and read by  $r_{ij}$  different branches respectively, with  $w_{ij} \geq 2$  and  $r_{ij} \geq 2$  for all i, j.

Now, the  $s_i$  written variables have to cover all branches to ensure mutual exclusion; therefore, for all i,  $\sum_{j=1}^{s_i} w_{ij} \geq n$ ; the same is true for the  $q_i$  read variables, and therefore  $\sum_{j=1}^{q_i} r_{ij} \geq n$ .

Writing into a variable with m write ports can be accomplished with  $K_w \log_2 m$  energy cost, using a tree multiplexer to write into the variable; reading from a variable with m read ports can be accomplished with  $K_r \log_2 m$  energy cost, using a tree demultiplexer. The average cost per branch of mutual exclusion can be expressed as:

$$C(n) = \frac{1}{n} \sum_{i=1}^{n} \left( K_w \sum_{j=1}^{s_i} \log_2 w_{ij} + K_r \sum_{j=1}^{q_i} \log_2 r_{ij} \right)$$

(2.17)

If  $a_i \geq 2$  for all i, then  $\sum_i \log a_i \geq \log \sum_i a_i$ , and we can write the following inequality:

$$C(n) \geq \frac{1}{n} \sum_{i=1}^{n} \left( K_w \log_2 \sum_{j=1}^{s_i} w_{ij} + K_r \log_2 \sum_{j=1}^{q_i} r_{ij} \right)$$

$$\geq \frac{1}{n} \sum_{i=1}^{n} \left( K_w \log_2 n + K_r \log_2 n \right)$$

$$= (K_w + K_r)\log_2 n \tag{2.18}$$

Equality is achieved for a single variable shared by all branches.

In conclusion, assuming that we cannot implement access to a shared variable with less than logarithmic cost, the worst-case cost per branch of a selection statement is always at least logarithmic in the number of branches. Exact logarithmic cost is achieved if we implement mutual exclusion with a single variable.

#### 2.2.2 Assignments and Communication

The datapath of a circuit very often consumes the bulk of the energy required for operation. This is especially true for wide datapaths, where the overhead of control is relatively small. In the energy cost of the datapath, we will also include the cost of the control lines that drive it.

There are three main datapath operations: assignments, communications, and guard and function evaluation. Guard and function evaluation is treated later, assignment and communication is analyzed in this section.

A CSP assignment can be implemented with data communications. In fact, the usual implementation of an assignment is as follows:

$$\ldots; x := y; \ldots \rhd \ldots; (A!x \parallel A?y); \ldots$$

where channel A is a new channel.

A CSP data communication involves two actions: first, copying the data into the wires that implement the communication channel, and second, copying the data from the communication channel into a register; the second part may not be present if the data is to be tested on the channel wires.

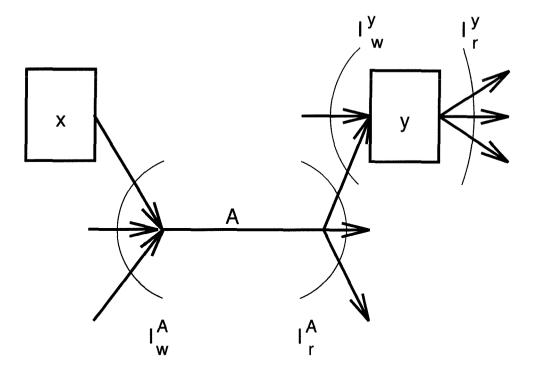

We assign an energy cost to the two parts of the communication, send and receive. In this case, copying data into the channel wires has a cost which is proportional to the number of bits of data. Copying data into the channel wires has an extra cost related to the capacitance on those wires. If the channel is shared by several registers, the capacitance of the channel wires will have contributions from the write ports to the channel, from the read ports to the channel, and from the wire itself. As a simplifying assumption, we will consider that the length of the wire scales with the number of writers, plus the number

**Figure 2.3**: Energy cost of an assignment.  $I_w^A$  and  $I_r^A$  are the fan-in and fan-out of channel A;  $I_w^y$  and  $I_r^y$  are the fan-in and fan-out of register y.

of receivers. Under these conditions, we can write:

$$C(A!x) = (K_r I_r^A + K_w I_w^A + K_s) \log_2 N$$

(2.19)

where  $I_r^A$  and  $I_w^A$  are the number of read and write ports, respectively, on channel A;  $K_r$ ,  $K_w$ , and  $K_s$  are technology constants; and N is the number of different values that the variable x can take (see Fig. 2.3).  $K_r$  corresponds to the contribution of each read port to the capacitance of the channel,  $K_w$  corresponds to the contribution from each write port to the capacitance of the channel, and  $K_s$  corresponds to the contribution from the pre-charge circuit and other fixed costs (sense-amplifier if present, for example) to the capacitance of the channel.

Likewise, The cost of assigning to a register increases with the complexity of that register. More read and write ports represent added capacitance to the storage nodes of the register; we can write:

$$C(A?y) = (K_r'I_r^y + K_w'I_w^y + K_s')\log_2 N$$

(2.20)

where  $I_r^y$  and  $I_w^y$  are the number of read and write ports respectively on variable y;  $K'_r$ ,  $K'_w$ , and  $K'_s$  are technology constants; and N is the number of different values that the variable y can take (see Fig. 2.3).

The technology parameters  $K_r$ ,  $K_w$ ,  $K_s$ ,  $K_r'$ ,  $K_w'$ , and  $K_s'$  can be measured, for example, from a SPICE simulation of a test circuit. To this effect we designed a standard register with multiple read and write ports and measured the energy index of several transfers between registers, separating the energy required to assign to the bus from that required to assign to the register. The register energy is the energy required to change the value of the register (if the register doesn't change value, the energy is zero). The measurement was made at several different voltages, and the parameters were computed using a least-squares approximation. The values of the parameters in fF for the  $1.2\mu m$  HP process are:

$$C(A?y) = (22.3I_r^y + 22.4I_w^y + 66.8)\log_2 N$$

(2.21)

$$C(A!x) = (15.6I_r^A + 9.6I_w^A + 10.7)\log_2 N$$

(2.22)

The raw data is shown on Table 2.1.

|       |         | I    | Bus     |      | $R\epsilon$ | egister |         |       |

|-------|---------|------|---------|------|-------------|---------|---------|-------|

|       |         |      | $I_w^A$ |      |             |         | $I_r^y$ |       |

|       | $I_r^A$ | 1    | 2       | 3    | $I_w^y$     | 1       | 2       | 3     |

| SPICE | 1       | 35.5 | 45.7    | 55.6 | 1           | 112.8   | 131.3   | 157.5 |

| Model |         | 36.0 | 45.6    | 55.2 |             | 111.6   | 133.9   | 156.2 |

| SPICE | 2       | 51.8 | 61.7    | 70.2 | 2           | 135.4   | 153.6   | 179.9 |

| Model |         | 51.6 | 61.2    | 70.9 |             | 134.0   | 156.3   | 178.6 |

Table 2.1: Measured (SPICE) and predicted (Model) energy index for several register/bus configurations (results in fF). The worst-case relative error is less than 2%.

The numbers  $I_r^A$ ,  $I_w^A$ ,  $I_v^y$ ,  $I_w^y$  can be derived syntactically from the text of the program by counting in how many places a variable is used, how many different variables can be sent over a channel, number of assignments, guard evaluations, etc. There is, however, the possibility of optimizing the channel assignment by adding extra intermediate registers and other high level optimization steps that cannot be derived from the program text, but are dependent on the optimization algorithm used. Since this type of optimization can be expressed in CSP, we only consider explicit channels and assignments.

We will show next how to assign channels to optimize the cost of data communications. Consider, for example, a single-bit register with multiple read and write ports, where the mutual exclusion between the reads and writes is guaranteed by the environment:

```

REG \equiv \quad \langle \parallel \ i:1..r: \ \ast \llbracket \llbracket \ \overline{R}_i \longrightarrow R_i!x \ \rrbracket \rrbracket \ \rangle

\parallel \ \langle \parallel \ i:1..w: \ \ast \llbracket \llbracket \ \overline{W}_i \longrightarrow W_i?x \ \rrbracket \rrbracket \ \rangle

```

and the environment can be modeled by:

$$ENV \equiv *[[\langle \ \ ] \ i:1..r: \ \ \mathbf{true} \longrightarrow R_i?y_i \ \rangle$$

$\langle \ \ [] \ i:1..w: \ \ \mathbf{true} \longrightarrow W_i!z_i \ \rangle$

From the traces of the program we compute the frequencies of each communication action; these frequencies are  $p_i^r$  for the read ports, and  $p_i^w$  for the write ports, with  $\sum_i p_i^r = p_r$ ,  $\sum_j p_j^w = p_w$ , and  $p_r + p_w = 1$ . The average cost per communication can be computed as:

$$p_{r}C(R) = p_{r}(K_{r} + K_{w} + K_{s}) + \sum_{i} p_{i}^{r}(K_{r}'I_{r}^{y_{i}} + K_{w}'I_{w}^{y_{i}} + K_{s}')$$

$$p_{w}C(W) = p_{w}(K_{r}'r + K_{w}'w + K_{s}') + p_{w}(K_{r} + K_{w} + K_{s})$$

$$C(RW) = p_{r}C(R) + p_{w}C(W)$$

$$= (K_{r} + K_{w} + K_{s}) + p_{w}(K_{r}'r + K_{w}'w + K_{s}') + \sum_{i} p_{i}^{r}(K_{r}'I_{r}^{y_{i}} + K_{w}'I_{w}^{y_{i}} + K_{s}')$$

$$(2.23)$$

To improve on this energy cost, we reduce the number of channels to variable x by merging the channels  $W_1$  and  $W_2$ :

$$REG \equiv \langle \parallel i:1..r: *[[\overline{R}_i \longrightarrow R_i!x]] \rangle$$

$$\parallel *[[\overline{W}_{12} \longrightarrow W_{12}?x]]$$

$$\parallel \langle \parallel i:3..w: *[[\overline{W}_i \longrightarrow W_i?x]] \rangle$$

$$ENV \equiv *[[ true \longrightarrow W_{12}!z_1$$

$$\parallel true \longrightarrow W_{12}!z_2$$

$$\langle \parallel i:1..r: true \longrightarrow R_i?y_i \rangle$$

$$\langle \parallel i:3..w: true \longrightarrow W_i!z_i \rangle$$

$$\parallel \exists$$

The new energy cost per communication action from register x,  $\mathcal{C}'(RW)$ , can be computed as:

$$p_{r}C'(R) = p_{r}(K_{r} + K_{w} + K_{s}) + \sum_{i} p_{i}^{r}(K_{r}'I_{r}^{y_{i}} + K_{w}'I_{w}^{y_{i}} + K_{s}')$$

$$= p_{r}C(R)$$

$$p_{w}C'(W) = p_{w}(K_{r}'r + K_{w}'(w - 1) + K_{s}') + (p_{w} - p_{1}^{w} - p_{2}^{w})(K_{r} + K_{w} + K_{s}) + (p_{1}^{w} + p_{2}^{w})(K_{r} + 2K_{w} + K_{s})$$

$$= p_{w}C(W) - p_{w}K_{w}' + (p_{1}^{w} + p_{2}^{w})K_{w}$$

$$C'(RW) = p_{r}C'(R) + p_{w}C'(W)$$

$$= C(RW) - p_{w}\left(K_{w}' - \frac{p_{1}^{w} + p_{2}^{w}}{p_{w}}K_{w}\right)$$

(2.24)

To maximize the energy savings, we merge the two channels with the lowest frequencies  $(p_1^w + p_2^w < p_w 2/w)$ , and the energy savings are:

$$C(RW) - C'(RW) = p_w \left( K'_w - \frac{p_1^w + p_2^w}{p_w} K_w \right) \ge p_w \left( K'_w - \frac{2}{w} K_w \right)$$

(2.25)

Eq. 2.25 represents the trade-off between more complex registers and more complex buses. From a previous measurement we know that  $K'_w \approx K_w$ , and therefore this transformation improves the energy cost as long as w > 2. The same transformation can be used iteratively as long as the energy improvement is positive.

If all ports have the same frequency, we can build those ports as a tree of multiplexors and de-multiplexors. This results in an average and a worst-case energy cost logarithmic in the number of read ports for the read actions, and logarithmic in the number of write ports for the write actions.

The global optimization problem of channel assignment is more complex. Local optimization per variable does not give a global optimum, and other considerations, such as the complexity of the resulting wiring problem or the introduction of extra intermediate variables, may have a strong impact on energy cost. Global optimization is beyond the scope of this section.

#### 2.2.3 Function Evaluation

Function evaluation can hide part of the computation executed by the program. To incorporate that cost into the energy model, we have to make the evaluation of that function explicit in the CSP specification, or otherwise use a worst-case cost for the evaluation of an arbitrary boolean function.

Given the program:

$$\ldots; F!f(x); \ldots$$

we want to express the cost of the evaluation of f(x). To estimate the worst-case cost we give a specific implementation for f and calculate the cost of that implementation based on the energy model described so far. This way we know that the cost of evaluating a function is consistent with the rest of the model.

If the range of x is  $\{x_1, \ldots, x_n\}$ , and  $f(x_i) = f_i$ , we can express the function evaluation as:

$$\ldots$$

;  $[\langle i:1..n: x=x_i \longrightarrow F!f_i\rangle];\ldots$

The cost of this program scales with n, which can be a large number. To obtain a more efficient implementation, we encode x as an array of  $N = \lceil \log_2 n \rceil$  bits, and eliminate one bit from the function evaluation by currying:

$$\begin{aligned} & \dots; \\ & [ & x[\theta] \longrightarrow X_t! x[1..N-1]; & F!(F_t?) \\ & \exists \neg x[\theta] \longrightarrow X_f! x[1..N-1]; & F!(F_f?) \\ & \exists; \dots \end{aligned}$$

$$\begin{aligned} & \| *[X_t?y; & F_t! f_t(y)] \\ & \| *[X_f?y; & F_f! f_f(y)] \end{aligned}$$

From the previous decomposition we see that the cost of evaluating a function of N bits,  $C_f(N)$ , is, at worst, the cost of communicating N-1 bits  $(X_{tf}$  channel),  $K_c(N-1)$  plus the cost of evaluating an N-1 bit function,  $C_f(N-1)$  plus the cost of merging the  $F_t$  and  $F_f$  channels,  $K_M$ :

$$C_f(N) = K_c(N-1) + C_f(N-1) + K_M$$

(2.26)

Solving for  $C_f(N)$ ,

$$C_f(N) = K_c \frac{N(N-1)}{2} + C_f(0) + NK_M$$

(2.27)

This equation can be further refined. If the range of the function f has m different values that can be expressed as an array of  $M = \lceil \log_2 m \rceil$  bits, the cost of merging  $F_t$  and  $F_f$  can be expressed as  $K_M = MK_m$ , and we have:

$$C_f(N) = K_c \frac{N(N-1)}{2} + C_f(0) + NMK_m$$

(2.28)

In general, the cost of evaluating a function of N inputs and M outputs,  $C_f(N, M)$  can be expressed as:

$$C_f(N,M) \approx K_1 N^2 + K_2 NM \tag{2.29}$$

## 2.3 Example: Counter

In this section we develop an example — a self incrementing register — and show how to predict the energy consumption of the incrementer using the above energy model.

The following CSP process will serve as the specification for the counter:

In most applications, the environment would be responsible for ensuring the mutual exclusion between the I, R, L, and S channels. We can rewrite PC as:

$$PC \equiv ( *[[\overline{I} \longrightarrow x := x + 1; I]]$$

$$\parallel *[[\overline{R} \longrightarrow x := \theta; R]]$$

$$\parallel *[[\overline{L} \longrightarrow L?x]]$$

$$\parallel *[[\overline{S} \longrightarrow S!x]]$$

$$)$$

To improve the performance of the incrementer, we separate the I communication in two parts:

$$INC \equiv *[[\overline{Iu} \longrightarrow y := x+1, Iu; [\overline{Id}]; x := y; Id]]$$

The value of x is stable until Id is started, and stable again after Id is completed. Iu can execute concurrently with S.

Notice that when x is even, it is trivial to calculate x + 1. We separate process INC into two parts, one that takes care of the least significant bit of x, and one that takes care of the rest:

INC0 is a one-bit incrementer, and INCR is an n-1 bit incrementer. We apply to INCR the same transformation, until we end up with one-bit counters only.

#### 2.3.1 Handshaking Expansion, Production Rules

The following is a handshaking expansion for the program INC0. We rename the channel Iu, Id as I, and the channel I1u, I1d as O.

$$INC \equiv * \begin{bmatrix} Ii & \wedge & \neg x & \longrightarrow & Io\uparrow; & [\neg Ii]; & x\uparrow; & Io\downarrow \\ & & Ii & \wedge & x & \longrightarrow & Oo\uparrow, & Io\uparrow; & [\neg Ii]; & x\downarrow; & [Oi]; \\ & & & & Oo\downarrow; & [\neg Oi]; & Io\downarrow \end{bmatrix}$$

To generate the production rules, we change the comma into a semicolon, and add the state variable s:

$$INC \equiv * \begin{bmatrix} Ii & \wedge & \neg x & \longrightarrow & s \uparrow; & Io \uparrow; & [\neg Ii]; & x \uparrow; & s \downarrow; & Io \downarrow \\ & Ii & \wedge & x & \longrightarrow & Oo \uparrow; & Io \uparrow; & [\neg Ii]; & x \downarrow; & [Oi]; \\ & & & & Oo \downarrow; & [\neg Oi]; & Io \downarrow \end{bmatrix}$$

]]

We derive the production rules for this handshaking expansion:

If x is implemented as cross-coupled inverters, the previous production rules are directly implementable.

#### 2.3.2 Average Energy and Latency

We will derive the average energy cost per increment of the counter, under the assumption that all register values are equally probable. Therefore, half of the time the register contains an even number, and only the first bit of the counter is utilized:

$$E_n = E_1 + \frac{1}{2}E_{n-1} \tag{2.30}$$

where  $E_j$  is the average energy dissipated by a j-bit counter.

From the characteristic equation,  $E_n$  has the form  $A2^{-n} + B$ . Substituting in the above expression, we derive A and B:

$$E_n = (2 - \frac{1}{2^{n-1}})E_1 < 2E_1 \tag{2.31}$$

The average energy dissipation can be bounded by a constant, irrespective of the word size.

A similar computation can be done for the average latency of this circuit. Again, assuming that x is even half of the time, we get the following equation:

$$L_n = L_1 + \frac{1}{2}L_{n-1} \tag{2.32}$$

This is the same equation as Eq. 2.30. The average latency is therefore bounded by two times the latency of one stage, no matter what the word size is.

Worst-case delay and energy are linear in the word size, of course, but this is not worse than a simple incrementer design with no carry-tree.

To finish this computation, we calculate the value of  $E_1$  based on the previously defined energy model, and then compare it with a SPICE simulation of the circuit.

We can compute  $E_1$  as the energy cost of the I communication. The I channel is one-to-one, and the target, register x, has 3 write ports (I, R,and L) and two read ports (S,and guard evaluation). The value of the register is changed in all I communications. We can approximate  $E_1$  by:

$$E_1 = (K_r + K_w + K_s) + (2K_r' + 3K_w' + K_s') + K_c$$

(2.33)

In this case selection is implemented with a shared variable with two read and two write ports, and we can write  $K_c = 2K'_r + 2K'_w + K'_s$ . Using the constants previously computed, we get  $E_1 \approx 36 + 179 + 156 = 371$  fF. This number can be measured directly on a SPICE simulation of an implementation of the incrementer based on the same register circuits, and we get  $E_1 = 350$ fF. The difference is due to an optimization in the implementation of the shared variable where only one of the branches of the choice statement needs to read the variable (see in the handshaking expansion, variable s). In this case,  $E_1 \approx 36 + 179 + 134 = 349$ .

This example shows that the energy cost for CSP programs can be predicted with a good measure of accuracy, based on some fairly general assumptions about the implementation methodology.

# 2.4 Example: Memory Array

In this section we examine the design of a memory array from the energy-efficiency point of view. The energy model previously developed is used to express the architectural trade-offs in the partitioning of such an array [32].

In CSP, a memory is an array, and reading from memory is one of the two operations: x := M[a] or X!M[a]; writing to memory is one of the two operations M[a] := y or Y?M[a], where M[a] is an array of n words of b bits. A program that describes a memory array with one read and one write port is:

The indexing M[a] is removed by breaking up the memory array into a decoder and an array of registers:

$$DECODER \equiv \langle \parallel i:0..n-1: \\ * \begin{bmatrix} \overline{R} \land \left( \overline{A?} = i \right) \longrightarrow & A?; R_i! \\ \overline{W} \land \left( \overline{A?} = i \right) \longrightarrow & A?; W_i! \\ \end{bmatrix}$$

$$\rangle$$

$$ARRAY \equiv \langle \parallel i:0..n-1: \\ * \begin{bmatrix} \overline{R_i} \longrightarrow R! x_i \bullet R_i \end{bmatrix} \end{bmatrix}$$

$$\parallel * \begin{bmatrix} \overline{W_i} \longrightarrow W? x_i \bullet W_i \end{bmatrix} \end{bmatrix}$$

To read one word from the array, we have to execute an A communication (one sender, n receivers,  $\log_2 n$  bits wide), an  $R_i$  communication (one sender, one receiver, data-less), and an R communication (n senders, one receiver, b bits wide). The costs of these operations are summarized in table 2.2. The energy cost of reading one word is the sum of the energy costs of executing each of these communications, that is:

$$E_{1D,R}(n,b) = K_A n \log_2 n + K_{R_i} + K_R nb$$

(2.34)

where  $K_A$ ,  $K_{R_j}$ , and  $K_R$  are geometry dependent proportionality constants.

| Channel | Type           | Width      | Cost             |

|---------|----------------|------------|------------------|

| A       | 1-to- <i>n</i> | $\log_2 n$ | $K_A n \log_2 n$ |

| R       | n-to-1         | b          | $K_R nb$         |

| W       | 1-to- <i>n</i> | b          | $K_W nb$         |

Table 2.2: Cost of the communications involved in accessing an  $n \times b$  memory array.

A one dimensional array is a viable solution only for small arrays; for large n, the energy cost scales like  $n \log_2 n$ . One way of improving on this cost is by mapping the one-dimensional array into a two-dimensional array. We represent the double indexing by splitting the address in two:

$$MEM \equiv *[[\overline{R} \longrightarrow A?(a_w, a_l); R!M[a_l][a_h]]$$

$$[\overline{W} \longrightarrow A?(a_w, a_l); W?M[a_l][a_h]$$

The first indexing is removed by extracting a row decoder:

$$DEC \equiv \langle \parallel i:0..l-1: \\ * \texttt{[[} \left( \overline{Al?} = i \right) \longrightarrow Al? \parallel S_i! \texttt{]]}$$

The second indexing is removed by extracting a column decoder:

$$\begin{aligned} MUX &\equiv \langle \parallel j: 0..w-1: \\ &* \texttt{[[} \overline{R} \land \left(\overline{Aw?} = j\right) \longrightarrow Aw? \parallel R!(R_j?) \\ &\mathbb{\overline{W}} \land \left(\overline{Aw?} = j\right) \longrightarrow Aw? \parallel W_j!(W?) \\ &\texttt{]]} \end{aligned}$$

where l and w are such that  $l \times w = n$ . Finally, the register processes:

$$\begin{array}{c} ARRAY \equiv \langle \parallel \ i: 0..l-1: j: 0..w-1: \\ \qquad * \llbracket \llbracket \ \overline{S_i} \wedge \overline{R_j} \longrightarrow R_j! x_{ij} \bullet S_i \ \rrbracket \rrbracket \\ \qquad \parallel * \llbracket \llbracket \ \overline{S_i} \wedge \overline{W_j} \longrightarrow W_j? x_{ij} \bullet S_i \ \rrbracket \rrbracket \\ \rangle \end{array}$$

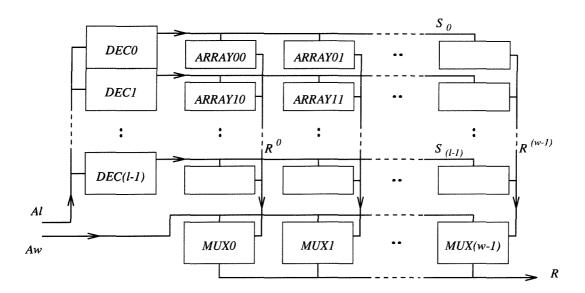

**Figure 2.4**: Process decomposition of MEM as a two-dimensional array. Only the channels corresponding to a read operation are shown.

The process decomposition and channel interconnection are shown in Fig. 2.4. In the following section, we show how to choose l and w from a simple energy model.

#### 2.4.1 Energy Model and Optimization

The energy cost of accessing one element of the array is calculated as the sum of the costs of the communications executed by the DEC, MUX, and ARRAY processes. A read from memory requires executing communication R (w senders, one receiver, b bits wide), communication Al (one sender, l receivers,  $log_2 l$  bits wide), communication Aw (one sender, w receivers,  $log_2 w$  bits wide), communication  $S_i$  (one sender, w receivers), and communication  $R_j$  (l senders, one receiver, b bits wide). Table 2.3 summarizes the energy costs for all of the communication actions in MEM.

The total energy cost  $E_r$  of reading a memory location is:

$$E_{2D,R}(n,b) = K_{Al} \log_2 l + K_{Aw} w \log_2 w + K_{Sw} + K_{R_j} lb + K_{Rw} b \qquad (2.35)$$

| Channel | Type           | Width      | Cost              |

|---------|----------------|------------|-------------------|

| Al      | 1-to- <i>l</i> | $\log_2 l$ | $K_{Al}l\log_2 l$ |

| Aw      | 1-to-w         | $\log_2 w$ | $K_{Aw}w\log_2 w$ |

| $S_i$   | 1-to-w         | dataless   | $K_S w$           |

| $R_j$   | <i>l</i> -to-1 | b          | $K_{R_j}lb$       |

| R       | w-to-1         | b          | $K_Rwb$           |

| $W_j$   | 1-to- <i>l</i> | b          | $K_{W_j}lb$       |

| W       | 1-to-w         | b          | $K_W wb$          |

Table 2.3: Cost of the communications involved in accessing an  $l \times w \times b$ memory array.

We simplify (2.35) by assuming all constant equal to one. This approximation is acceptable for most technologies; if a more accurate model is needed, the parameters can be calculated from the layout, and the optimization is done with those values of the parameters.

$$E_{2D,R}(n,b) = l \log_2 l + w \log_2 w + (w+l)b + w$$

(2.36)

We minimize  $E_{2D,R}$  with respect to l and w under the constraint  $l \times w = n$ , using Lagrange multipliers:

$$U = l \log_2 l + w \log_2 w + (w+l)b + w + \lambda(n-lw)$$

(2.37)

We take derivatives with respect to l, w, and  $\lambda$ :

$$\frac{\partial U}{\partial l} = \log_2 l + \log_2 e + b - \lambda w \tag{2.38}$$

$$\frac{\partial U}{\partial w} = \log_2 w + \log_2 e + b + 1 - \lambda l \tag{2.39}$$

$$\frac{\partial U}{\partial l} = \log_2 l + \log_2 e + b - \lambda w \tag{2.38}$$

$$\frac{\partial U}{\partial w} = \log_2 w + \log_2 e + b + 1 - \lambda l \tag{2.39}$$

$$\frac{\partial U}{\partial \lambda} = n - l w \tag{2.40}$$

Assuming that  $\frac{1}{2}\log_2 n + b + \log_2 e \gg 1$ , we solve for l, w, and  $\lambda$ , and  $l_{opt} =$

$w_{opt} = \sqrt{n}$ . The optimum energy per access,  $E_{2D,R}(n,b)$  is:

$$E_{2D,R}(n,b) = \sqrt{n} (\log_2 n + 2b + 1)$$

(2.41)

Memory designed for speed usually has  $l = b \times w$  [7]. A completely square bit-array optimizes the access time per bit, but does not take into account the energy savings derived from selecting only the bits that are part of the desired word. This extra selection step takes time and area, and saves energy.

If we compare the optimal energy for a two-dimensional array with the energy used by a one-dimensional array (assuming that all constants are equal to one), we get:

$$\frac{E_{1D}}{E_{2D}} = \frac{n(\log_2 n + b + 1)}{\sqrt{n}(\log_2 n + 2b + 1)} \approx \sqrt{n}$$

(2.42)