### SPACE-CHARGE-LIMITED CURRENT IN GERMANIUM

Thesis by

Alex Shumka

In Partial Fulfillment of the Requirements

For the Degree of

Doctor of Philosophy

California Institute of Technology

Pasadena, California

1964

(Submitted March 2, 1964)

#### ACKNOWLEDGMENTS

The author is greatly indebted to Dr. M-A Nicolet under whose direction and constant encouragement this work was carried out. Thanks are due to Dr. K. Das Kuptas for verifying the crystallographic alignment of the wafers by X-rays and to the members of the Solid-State Laboratory for the Hall effect measurements. Hughes Semiconductor Division generously donated the germanium crystal. This work was initiated and supported in part by the funds made available by the California Institute of Technology Jet Propulsion Laboratory and completed under the support of the Naval Ordnance Test Station.

#### ABSTRACT

An experimental verification of the theory of space-charge-limited hole current in germanium is presented. Alloyed p-n-p solid-state diodes of various base widths W are fabricated. The V-I characteristic of each diode is measured at an ambient temperature of  $78^{\circ}$  K. These results are compared with theory. Dacey (4) predicts:  $J = 1.43\varepsilon\varepsilon_0 \; \mu_0 \quad E_c^{1/2} v \quad 3^{1/2} v^{-5/2} \; \text{where} \; \mu_0 \; \text{is the low field} \; \text{mobility of the holes and} \; E_c \; \text{is the critical electric field.}$  This expression assumes a field dependence of hole mobility of  $\mu = \mu_0 (E_c/E)^{1/2}$ .

The three halves power relationship between current and voltage is observed over nearly two current decades. In that same current range, a direct proportionality of V with  $W^5/3$  at a constant current density is also observed to within the accuracy of base width and area measurements which are better than 5%. The value of the critical electric field obtained agrees with that estimated by Shockley's model (11).

Measurements are also made at higher ambient temperatures. The current decreases as expected from hot carrier considerations.

These results represent the first detailed verification of the validity of the theory of pure space-chargelimited current of hot carriers in solids. The measured peak current density of 180 a/cm<sup>2</sup> is greater than any value reported on space-charge-limited current in solids by an order of magnitude.

Photographic materials on pp. 39, 40, 68, 89 and 91 are essential and will not reproduce clearly on Xerox copies. Photographic copies should be ordered.

### TABLE OF CONTENTS

| INTRODUC             | CTION                           |                                                                                                                                  | 1                                      |

|----------------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

|                      |                                 | CHAPTER I                                                                                                                        |                                        |

| SPACE-CH<br>AND EXPE |                                 | -LIMITED CURRENT IN GERMANIUM: THEORY                                                                                            |                                        |

| Introduc             | etion                           |                                                                                                                                  | 4                                      |

| Section              | 1.1                             | Theory of Space-Charge-Limited Current in an Idealized Solid One-Dimensional Model Properties of the Idealized Solid-State Diode | 5<br>5<br>7<br>7                       |

| Section              | 2.1                             | Discussion on Space-Charge-Limited Current in Practical Solids Insulators Semiconductors                                         | 10<br>10<br>12<br>14                   |

| Section              | 3.1<br>3.2<br>3.3<br>3.4<br>3.5 | 3.2a Punching-Through Range                                                                                                      | 17<br>19<br>21<br>22<br>24<br>27<br>29 |

|                      | 4.1<br>4.2<br>4.3<br>4.4<br>4.5 | State Diode                                                                                                                      | 36<br>36<br>45<br>50                   |

| CONCLUS              | IONS                            |                                                                                                                                  | 55                                     |

## CHAPTER II

| FABRICAT | CION,                                  | EVALUATION AND MEASUREMENT                                                                                   |                                        |

|----------|----------------------------------------|--------------------------------------------------------------------------------------------------------------|----------------------------------------|

| Introduc | tion                                   |                                                                                                              | 57                                     |

| Section  | 1.1                                    | Measurement of Material Properties . Resistivity Measurements Hall Effect Measurements Lifetime Measurements | 59<br>59<br>63<br>64                   |

| Section  | 2.1                                    | Crystal Alignment                                                                                            | 65<br>65<br>69<br>70                   |

| Section  | _                                      | Fabrication of P-N Junctions and P-N-P Structures                                                            | 76<br>76<br>78<br>79<br>81<br>84<br>84 |

| Section  | 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6 | Measurement of P-N Junction and P-N-P Structure Properties                                                   | 87<br>87<br>92<br>96<br>101<br>104     |

| APPENDI  | X A                                    | Impedance of Space-Charge-Limited Currents with Field Dependent Mobility                                     | 113                                    |

| APPENDI  | ХВ                                     | Resistance-Base Width Relationship: Theory                                                                   | 122                                    |

| APPENDI  | хс                                     | Electrical Measuring Apparatus                                                                               | 126                                    |

| REFEREN  | CES                                    |                                                                                                              | 131                                    |

#### INTRODUCTION

The effect of space charge in limiting the flow of electrons through vacuum in thermionic vacuum tube diodes and related devices is well known. Similar conditions can exist in solids such as insulators and semiconductors into which holes or electrons are injected. The objective of constructing solid-state devices which are analogs of the vacuum tube devices is a tantalizing one and its inevitable success will be an important contribution to the field of electronics. The best survey on the expanding interest in this field is given by Wright (1). The reader is referred to this recent article which also includes an extensive bibliography.

There exist several important theoretical studies on space-charge-limited (abbreviated scl) current in solids. Mott and Gurney (2) have considered a solid-state diode in which holes or electrons flow through a perfect crystal of infinite bulk resistivity from an ideal emitter to an ideal collector. For this idealized solid-state diode, the scl current is directly proportional to the square of the applied voltage. Shockley and Prim (3) modified this idealized model to include fixed ions in the solid. This analysis is applicable to scl current in semiconductors. Dacey (4) extended this result to include the effect of field dependent mobility. Rose (5) considered the influence

of traps, which are normally present in insulators. These theoretical contributions are representative of the important advancements toward understanding scl current in practical solids.

A limited amount of experimental work has been done on scl current in practical solids. Dacey (4) has made measurements on a germanium solid-state diode. In a semi-quantitative manner his results indicate scl current flow. Rose and Smith (6) and Wright (7), among others, have performed experiments on cadmium sulfide to which they succeeded in making injecting and collecting contacts. They observed non-ohmic current which can be interpreted as scl current in the presence of traps. This result has a firm semi-quantitative basis, but the theory of scl current has not been completely verified so far.

The subject matter to be presented here is an experimental verification of the theory of scl current in solids. Germanium is chosen as a suitable practical solid in which the theory can be tested. The following description is one that can be divided into three principal parts.

Part one outlines some theoretical aspects of scl current in solids (chapter I, sections 1, 2 and 3, and Appendix A). The primary objective is to consider the effect of different properties of the solid on scl current. This is accomplished by modifying the idealized case to include the properties of practical solids. A detailed

theory of scl current in germanium is given.

Detailed experimental results for scl current in germanium are presented and compared with theory in the second part (chapter I, section 4).

Part three describes the material used in the fabrication of the germanium p-n-p solid-state diodes. The techniques of fabrication, evaluation and measurement are outlined (chapter II, and appendices B and C).

#### CHAPTER I

# SPACE-CHARGE-LIMITED CURRENT IN GERMANIUM: THEORY AND EXPERIMENT

#### Introduction

This chapter is divided into two parts. The first part outlines the theory of scl current in solids. The second part compares this theory with experimental results obtained in germanium.

The theory of scl current in solids is given in the first three sections. In section 1, an idealized solidstate diode similar to that assumed by Mott and Gurney is described. The current-voltage relationship is derived for a one-dimensional current flow. In section 2, the advantages and disadvantages of different types of solids as practical representatives of the idealized solid are discussed. Germanium is selected as the most suitable practical solid in which to verify the validity of the theory. In section 3 an alloyed p-n-p germanium structure, as a practical analog of an idealized solid-state diode, is considered. A theoretical treatment of scl current in such a solid-state diode, which is essentially that presented by Dacey, is outlined. Experimental results obtained from current-voltage measurements on fabricated germanium p-n-p solid-state diodes of different n-region (base) width are presented in section 4. From these results the

interrelationship between current, voltage, ambient temperature, and base width, are determined and compared with theory.

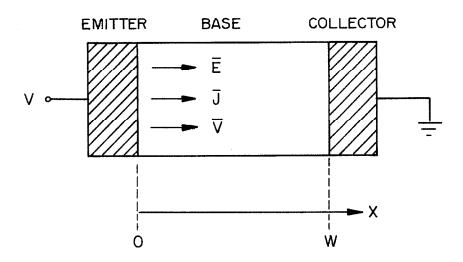

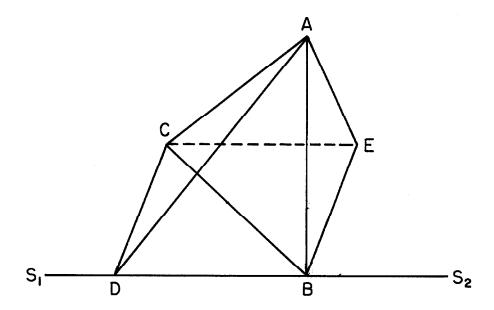

# 1 Theory of Space-Charge-Limited Current in an Idealized Solid

bounded by two parallel and planar electrical contacts is considered. One of the electrical contacts is assumed to inject charge carriers into the solid while the other contact acts as a collector. The injecting contact is called the emitter, the collecting contact the collector, and the region in between the base. A one-dimensional model for such a geometric arrangement is represented in figure 1.1. The x-axis has the emitter-solid boundary as the origin and is directed towards the collector. The electric field intensity vector  $\overline{\mathbf{E}}$ , the current density vector  $\overline{\mathbf{J}}$ , and the charge transport velocity vector  $\overline{\mathbf{v}}$  are considered as being directed in the positive x-axis direction. The potential of the emitter is measured with respect to the collector which is at zero potential.

The emitter is considered to inject holes only when it is at a positive potential. When it is at a negative potential no charge carriers are injected into the solid. This physical model is very similar to that of a thermionic vacuum tube diode where the cathode which injects electrons

Figure 1.1. A one-dimensional model for a solid-state diode.

into the vacuum corresponds to the emitter, and the anode to the collector.

The model described here is called a solid-state diode. It will be used to study scl current in solids.

- 1.2 Properties of the Idealized Solid-State Diode.

To obtain a simple theory for space-charge-limited current in solids, it is necessary to consider an idealized solid-state diode. Its properties are as follows:

- 1. The emitter is an infinite source of holes and the collector an ideal sink.

- 2. The resistivity of the solid is infinite.

- 3. There are no traps, no recombination centers, no defects of any kind in the solid.

- 4. The injected charge carriers are transported through the solid by drift only.

- 5. The drift velocity is directly proportional to the electric field.

- 1.3 Voltage-Current Relationship. When a voltage V is applied at the emitter an electric field will be established in the solid. If this voltage is positive then the holes injected into the base will be transported by the electric field to the collector. The transport velocity v of the holes is directly proportional to the electric field E and the proportionality constant is µ which is called

the hole mobility in the solid, as indicated in equation 1.1.

$$v = \mu E \tag{1.1}$$

For charges transported in vacuum, the charge carriers act as free particles. In this case, it is the acceleration v of the particle which is directly proportional to the electric field E, as indicated in equation 1.2.

$$\dot{\mathbf{v}} = (\mathbf{q/m})\mathbf{E} \tag{1.2}$$

From these equations, it is apparent that the analogy between the solid and the vacuum conduction medium is not a direct one.

When injected holes are transported from the emitter to the collector, there is a net current flow. This current is directly proportional to the injected hole charge density  $\rho(x)$  within the base and to the transport velocity v(x) of the injected holes, as is expressed in equation 1.3

$$J = \mu(x) v(x)$$

(1.3)

where J is the current density. At steady state, this current density is independent of x and t. The hole transport velocity v(x) is expressed in equation 1.1 as a function of the electric field E(x). Since the holes are injected into an originally charge neutral base, they will establish a space charge within the base by virtue of their charge. The electric field E(x) which is established in the base by the injected charge density

$\rho(x)$  is given by Poisson's equation

$$\frac{dE(x)}{dx} = \frac{\rho(x)}{\epsilon \epsilon_0} \tag{1.4}$$

or

$$\frac{d^2 \psi(x)}{dx^2} = \frac{\rho(x)}{\varepsilon \varepsilon_0} \tag{1.5}$$

where  $\psi(x)$  is the potential with respect to the collector, and  $\varepsilon$  the relative dielectric constant. Since an ideal emitter is considered, the electric field is zero at x=0. The appropriate boundary conditions for determining the current-voltage relationship for the solid-state diode thus are:

$$\mathbb{E}(0) = 0$$

, and  $\psi(0) = V$ . (1.6)

By manipulating equations 1.1, 1.3, 1.4 and 1.5 in a straight forward manner and by applying the given boundary conditions, the current-voltage relationship can be determined and is expressed as follows:

$$J = \frac{9}{8} \frac{\epsilon \epsilon_0 \mu}{w3} V^2 \tag{1.7}$$

This result was first derived by Mott and Gurney (2). In equation 1.7 the current density J is directly proportional to the square of the applied voltage V and to the hole mobility  $\mu$ , and inversely proportional to the cube of the base width W.

The corresponding current-voltage relationship for

the vacuum tube diode is expressed in equation 1.8 in which the current density J is directly proportional to the three-halves power of the applied voltage V and inversely proportional to the square of the width of the vacuum conduction medium W. This equation is known as Child's three-halves power law. The difference between the two current-voltage relationships stems from the difference in the transport velocity-electric field relationship expressed in equations 1.1 and 1.2.

$$J = \frac{4}{9} \left(\frac{2q}{m}\right)^{1/2} \frac{\epsilon_0}{w^2} V^{3/2}$$

(1.8)

1.4 Impedance. The small signal impedance of the idealized solid-state diode has been calculated by Shao and Wright (8). Their results, along with those for the vacuum tube diode, will be presented in section 3.4 of this chapter where they will be compared with the results to be derived for the germanium solid-state diode.

# 2. <u>Discussion on Space-Charge-Limited Current in Practical</u> <u>Solids</u>

2.1 Insulators. It is of interest to modify the model of the idealized solid-state diode to include the electrical properties of practical solids. One of the stated conditions is that the resistivity of the solid be

infinite. This would restrict the consideration to insulators that have a wide band gap. Good insulators have resistivities of the order of  $10^{12}~\Omega$  -cm. Another stated condition is that there be no traps, no recombination centers, no defects of any kind in the solid. However, it is a well known fact that wide band gap materials usually have large densities of traps. Finally, it is necessary to make injecting and collecting contacts to the solid. This presents a rather severe restriction on the electron affinity of the insulator and the work function of the metal contact. Often surface states prevent a large scale injection of charge carriers into the insulator. From these considerations it is evident that the theoretical treatment of practical scl current is more complex than already presented.

Experiments have been performed by Rose and Smith (6) and Wright (7) on CdS to which they succeeded in making injecting and collecting contacts. They were able to show, after taking into account the trapping mechanisms within CdS, that there is a square law dependence between the injected current and the applied voltage. This is an important result in that it indicates that space-charge-limited current can indeed flow through insulators.

To show that there is a direct correlation between theory and experiment, it is necessary to know how the injecting contact functions, what the effective width of the base is, and what the bulk electrical properties of the

solid are to at least a reasonable degree of accuracy. CdS at the present state of the technological art satisfies only the first condition and yet it is the only insulator in which scl current has been extensively studied. For these stated conditions to be satisfied, narrower band gap elemental materials such as germanium and silicon appear much more desirable.

2.2 Semiconductors (Germanium and Silicon). It would seem that the selection of semiconductors as practical solids in which scl current could be studied would be a serious violation of the restriction that the resistivity of the material be very large. However, this is not as severe a violation as one may believe. It will be shown in section 3 of this chapter that the important parameter is not the conductivity due to the majority mobile charge carrier density, but the conductivity due to the minority mobile charge carrier density. Since the density of the minority mobile charge carriers is exponentially temperature dependent, it is possible to reduce greatly their density by lowering the ambient temperature. In this way the bulk resistivity that is related to the minority mobile charge carrier density could be made very large.

From a large class of semiconductors only germanium and silicon appear to be the most suitable practical solids for consideration for the following reasons: there is a

large inventory of available information about the electrical properties of these two semiconductors that can be put to good use; the technological art of growing pure germanium and silicon crystals is highly developed in comparison with that of other materials; finally, the technology of fabricating p-n junctions is also more advanced.

The appropriate semiconductor structure in which scl current can be studied is an alloyed p-n-p structure in which the conductivity of the p-regions is much higher than that of the n-region. This makes it possible to consider one of the alloyed p-n junctions as an emitter and the other as a collector. The width of the solid conduction medium is the separation distance between the two alloyed p-n junctions. This p-n-p structure is the solid-state diode to be considered. Since the technology of germanium differs from that of silicon and since the solid-state diode had to be fabricated in the laboratory (see chapter II), only germanium has been considered.

In the practical solid-state diode to be studied, there are two important features that differentiate it from the ideal solid-state diode. First, the impurity doping in the n-type germanium must be accounted for as will be shown in section 3. Second, the mobility of the mobile charge carriers in the base is not independent of the electric field, as will be shown in the following section.

2.3 Field Dependent Mobility in Germanium. In the theory of scl current in an idealized solid, it is assumed that the mobility of holes or electrons is constant, that is, the drift velocity of mobile charge carriers is directly proportional to the electric field. This consideration is valid in practical solids such as insulators up to very high fields, since the mobility in these solids is low when compared with that of germanium. For materials in which the mobility is high, it takes but a relatively small electric field to give sufficient energy to the mobile charge carriers such that these carriers are out of thermal equilibrium with the surrounding solid. These carriers are called "hot" carriers, and their mobility is field dependent.

Ryder (9) has measured the mobility of holes and electrons in germanium and silicon as a function of the electric field, and found that the drift velocity of the mobile charge carriers is directly proportional to the electric field up to what he calls the critical electric field  $E_c$ . In this range the mobile charge carriers are in thermal equilibrium with the solid. For electric fields higher than the critical electric field, the drift velocity is directly proportional to the square root of the electric field. In this range, the mobile charge carriers are not in thermal equilibrium with the solid. Finally, for very high electric fields, the drift velocity ceases to increase further with the electric field and saturates at

the "limiting drift velocity". These results are graphically shown in figure 1.2.

The drift velocity v as a function of the electric field E for low and intermediate electric fields is expressed in equations 1.9 and 1.10, respectively.

$$v = \mu_0 E$$

for  $E < E_c$  (1.9)

$$v = \mu_0 \left(\frac{E_c}{E}\right)^{1/2} E \qquad \text{for } E_c < E < E_c' \qquad (1.10)$$

where  $\mu_{0}$  is the low field mobility, and  $E_{c}^{\tau}$  is the electric field at which the drift velocity saturates. The limiting drift velocity is

$$v = \mu_0 (E_c E_c^i)^{1/2}$$

From equations 1.1 and 1.2 we found that the relationship between the transport velocity and the electric field resulted in a different current-voltage dependence for the scl current in solid and vacuum. If the problem of scl current in germanium is to be solved, it is necessary to include the effect of the field dependent mobility. Before presenting the solution to the problem outlined, we will first describe the salient operating features of the germanium solid-state diode.

Figure 1.2. A graphical representation of the drift velocity v of a charge carrier in germanium and silicon as a function of the electric field E.

### 3. Theory of Space-Charge-Limited Current in Germanium

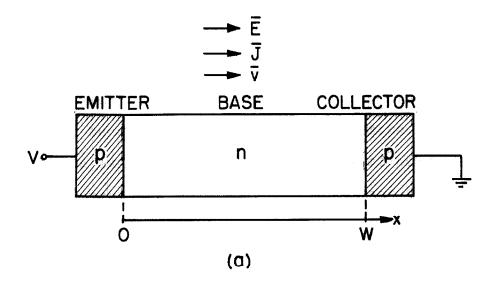

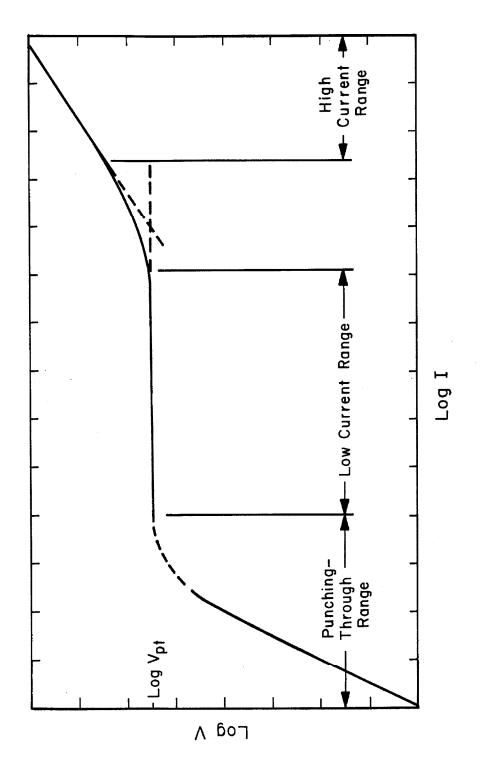

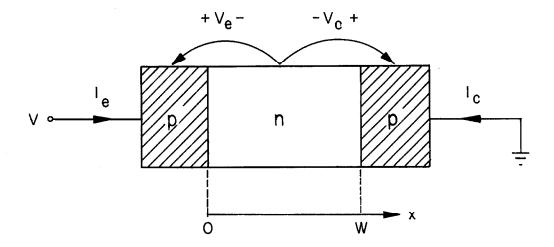

3.1 Germanium P-N-P Structure as a Solid-state

Diode. The germanium solid-state diode considered is an alloyed p-n-p planar structure in which the n-region is of much lower conductivity than the alloyed p-regions. The one-dimensional model for the structure is shown in figure 1.3a, which is the same representation as that used for the ideal solid-state diode.

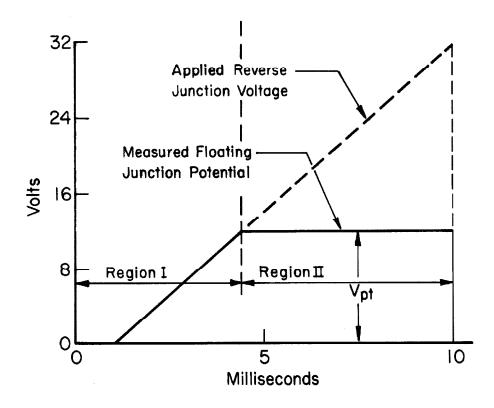

When a positive voltage is applied, the emitter junction becomes forward biased whereas the collector junction becomes reverse biased. The mode of operation is essentially that of a junction transistor with floating Nearly all of the applied voltage appears across the reverse-biased collector and generates a depletion region in the base. The current is proportional to the saturation current of this junction. Upon further increase of the applied voltage the depletion region will eventually extend throughout the base. This "punching-through" will occur at a particular applied voltage  $\mathbf{V}_{\text{pt}}$  which is called the "punchthrough" voltage. A base region in the sense of the simple transistor model no longer exists. For applied voltages slightly larger than the punch-through voltage, the current increases rapidly because the additional electric field can be sustained only by mobile charge carriers (holes) injected into the base from the emitter. As long as their density

Figure 1.3. An alloyed p-n-p germanium solid-state diode: (a) a one-dimensional model, and a sketch of the potential distribution for (b) V=0, (c)  $V\ll V_{pt}$ , (d)  $V=V_{pt}$ , and (e)  $V\gg V_{pt}$ .

is small compared with that of the fixed ionized donors in the base, this additional electric field is negligible compared with that due to the donor ions.

The fast increase in current ends when the additional electric field becomes dominant. The holes injected into the base finally outnumber the donor ions. It is then that the current becomes fully space-charge-limited.

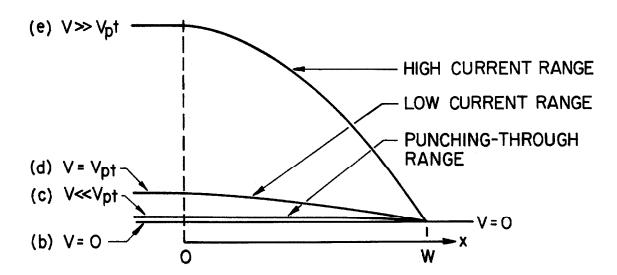

There exist three distinct ranges of operation. In the first range, the applied voltage is less than the punch-through voltage and is referred to as the <u>punching-through range</u>. In the second range, the applied voltage is slightly larger than the punch-through voltage. The current increases rapidly, but the injected hole density is less than the donor ion density. This range is referred to as the <u>low current range</u>. In the third range the injected hole density is so large that the donor ion density can be neglected. This is referred to as the <u>high current range</u>. These three ranges are sketched in figures 1.3 and 1.4. A more detailed analysis follows.

- 3.2 Three Ranges of Operation. In this section the current-voltage relationships will be derived for the three ranges of operation. The following assumptions are made in addition to that of planar geometry:

- 1. The width  $W_t$  of the transition region at thermal equilibrium is negligible compared with the base width W.

A sketch of the V-I characteristic of a germanium solid-state diode showing the three ranges of operation. Figure 1.4.

2. The built-in voltage  $V_j$  of the p-n junction at thermal equilibrium is negligible compared with the punch-through voltage  $V_{\rm pt}$ .

In the low and high current ranges, it is also assumed that:

- 3. The electric field at the emitter is zero (ideal emitter).

- 4. Current flow is by drift only.

- 5. The effect of traps, recombination centers or defects of any kind is negligible.

- 3.2a Punching-Through Range. According to the theory of a reverse-biased abrupt (alloyed) p-n junction, the depletion layer in the lightly doped n-type base for an applied voltage V has a width Y where

$$V + V_j = \frac{qN_D}{2 ee_0} Y^2$$

(1.11)

$V_j$  is the built-in potential of the junction and  $N_D$  the donor ion density. For a p-n-p structure of metallurgical base width  $W_j$ , punch-through is reached when  $Y=W-W_t$ . Hence

$$v_{pt} + v_{j} = \frac{qN_{D}}{2 ee_{o}} (W - W_{t})^{2}$$

(1.12)

For the model of figure 1.3 this equation reduces to

$$v_{pt} = \frac{qN_D}{2 e \epsilon_0} w^2 \qquad (1.13)$$

since  $V_{j}$  and  $W_{t}$  are neglected. If it is assumed that charge

carrier generation in the depletion region is the dominant factor in the saturation current, then it is expected to be proportional to  $Y \sim V^{1/2}$  (10) for  $V < V_{pt}/10$ . The analysis of the current dependence in the vicinity of punch-through is complex and has, to our knowledge, never been attempted. For a clear observation of the following range, however, the essential condition is that this saturation current does not appreciably increase until immediately prior to punch-through.

3.2b The High Current Range. This range of operation is identical to that of the idealized solid-state diode except that the hole mobility is field dependent. It is assumed that the current flow is by drift only. For this case the hole transport velocity v(x) is expressed as a function of the electric field E(x) (see section 2.3) as follows:

$$v(x) = \mu_0 E(x) \tag{1.14}$$

for  $x < x_0$ , where  $E(x_0) = E_c$ , and

$$v(x) = \mu_0 \left(\frac{E_c}{E(x)}\right)^{1/2} E(x)$$

(1.15)

for  $x \gg x_0$ , where  $E(W) < E_C^{\dagger}$ . The current-voltage relationship that results from the consideration of the field dependent mobility is

$$J = \frac{9}{8} \frac{\epsilon \epsilon_0 \mu_0}{x_0^3} \left( V - \psi(x_0) \right)^2$$

(1.16)

for  $x < x_0$ , and

$$J = \frac{2}{3} \left( \frac{3}{3} \right)^{3/2} \frac{\epsilon \epsilon_{\text{o}} \mu_{\text{o}} E_{\text{c}}^{1/2}}{\sqrt{5/2}} \sqrt{3/2} \left( 1 + \frac{1}{3} \frac{E_{\text{c}}^2}{E_{\text{c}}^2} \right)^{5/3} - \frac{1}{6} \left( \frac{4}{3} \frac{E_{\text{c}}^2}{E_{\text{c}}^2} \right)^{5/3} \right)^{-3/2}$$

(1.17)

for  $x > x_0$ , where

$$E_{1} = \left(\frac{2JW}{\epsilon \epsilon_{0} \mu_{0}}\right)^{1/2} \tag{1.18}$$

Equation 1.16 represents the current-voltage relationship in the region where the hole mobility is not field dependent. In this region a square dependence between the voltage and current exists as in the case of the idealized solid-state diode. A deviation from the idealized solid-state diode resulting from the field dependent mobility is apparent in equation 1.17. Here  $E_1$  is the electric field that would have been present at the collector had the mobility not been field dependent.

The electric field at the collector is always directly proportional to the net charge per unit crosssectional area in the base. When holes are injected, then the net charge in the base is always greater than that due to fixed donor ions which is  $qN_DW$ . Thus, in the presence of scl current  $E_1$  is always larger than  $E_2$ , where

$$E_2 = \frac{qN_D}{\epsilon\epsilon_O} W \tag{1.19}$$

Even for the most stringent case to be considered ( $N_D$  =  $10^{13}$  donor ions cm<sup>-3</sup>, W =  $8.3\,\mu$ , T =  $78^{\circ}$  K)  $E_2$  = 947 V/cm and  $E_c$  = 21 V/cm. This indicates that the terms  $(E_c/E_1)^2$  in equation 1.17 are much less than unity and can be neglected. Thus for practical considerations this equation, which was first derived by Dacey (4), can be expressed as

$$J = \frac{2}{3} \left( \frac{5}{3} \right)^{3/2} \frac{\epsilon \epsilon_0 \mu_0 E_c^{1/2}}{w^{5/2}} v^{3/2}$$

(1.20)

An identical result could have been obtained directly if the field dependent mobility had been assumed to hold everywhere in the base.

When the mobility becomes field dependent then the current-voltage relationship derived by Mott and Gurney (2) is no longer valid. According to equation 1.20 the current is directly proportional to the three-halves power of the applied voltage and inversely proportional to the five-halves power of the base width.

3.2c Low Current Range. In this range, the voltage is nearly constant and essentially equal to the punchthrough voltage  $V_{\rm pt}$ . The current, however, changes rapidly from values of the order of the saturation current in the punching-through range to values of the order of the scl

current in the high current range.

In the transition from the low to the high current range, the space charge of both the fixed ions and the injected charge carriers has to be considered. With the assumption that the field dependence of the mobility  $\mu = \mu_0 \left( E_C / E \right)^{\frac{1}{2}} \text{ holds throughout the base, Dacey (4) has arrived at the following parametric representation for the V-I characteristic$

$$V = V_{pt} \left( \frac{3e^{2u} - 16e^{3u/2} + 36e^{u} - 48e^{u/2} + 6u + 25}{3(e^{u} - 4e^{u/2} + u + 3)^{2}} \right)$$

(1.21)

$$J = 1.98 J_{pt} (e^{u} - 4e^{u/2} + u + 3)^{-1/2}$$

(1.22)

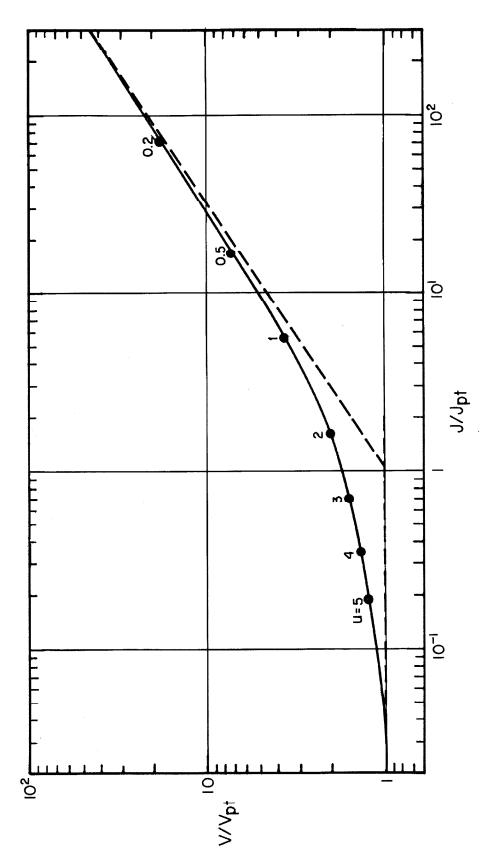

where u takes on positive values from zero to infinity, and  $J_{pt}$  is the current density for the applied voltage  $V_{pt}$  if there are no donor ions present in the base. The result of a numerical evaluation of this dependence is shown in figure 1.5 where the voltage is normalized with respect to the punch-through voltage  $V_{pt}$  and the current with respect to  $J_{pt}$ . When u tends toward infinity, the voltage approaches  $V_{pt}$  asymptotically while the current exponentially decreases with u. When u tends toward zero, the V-I characteristic approaches that of the fully scl current.

The parameter u can be expressed as u =  $qN_D\mu_0T/\varepsilon\varepsilon_0$  where T is the time that charge carriers of constant mobility  $\mu_0$  would take to traverse the base in the presence

A theoretical normalized V-I characteristic for scl current in a germanium p-n-p solid-state diode. Figure 1.5.

of the actual field. The condition u << 1 for the presence of pure scl current therefore requires that

$$\frac{qN_DW}{\varepsilon\varepsilon_0} << \frac{W}{T\mu_0}$$

This expression shows that the average value of the electric field in the base must be much less than the electric field at the collector at punch-through. This inequality will be satisfied provided the injected charge carriers dominate over the fixed ions as indicated in section 3.2b.

3.3 Temperature Dependence. In the high current range the current density is proportional to the mobility of the hot holes. This mobility  $\mu(T)$  is a function of the ambient temperature\* T as expressed in the following equation.

$$\mu(T) = \mu_0(T) \quad \left(\frac{E_c(T)}{E}\right)^{-1/2} \tag{1.23}$$

The low-field mobility  $\,\mu_{O}(T)$  as a function of the ambient temperature  $\,T\,$  is

$$\mu_0(T) = AT^{-3/2}$$

(1.24)

<sup>\*</sup>The ambient temperature is that of the crystal and not of the hot holes.

where A is a constant. This equation is valid when the holes are predominantly scattered by the lattice. The mobility of the hot charge carriers for the same scattering mechanism has been studied by Shockley (11). He considers two limiting energy distributions of the hot charge carriers. For the Boltzmann energy distribution he obtains

$$E_c(T) = 1.84 - \frac{c}{\mu_0(T)}$$

(1.25)

For the discrete energy distribution he obtains

$$E_c(T) = 1.03 - \frac{c}{\mu_0(T)}$$

(1.26)

In both equations, c is the group velocity of the longitudinal acoustical waves in the lattice. He also considers an intermediate case for which he obtains

$$E_c(T) = 1.51 - \frac{c}{\mu_0(T)}$$

(1.27)

By combining equations 1.23, 1.24 and 1.27 the mobility of hot holes as a function of the ambient temperature is obtained. From this result the current-voltage relationship can be derived as a function of the ambient temperature and is expressed as follows:

$$J = \frac{2}{3} \left(\frac{5}{3}\right)^{3/2} \frac{\varepsilon \varepsilon_0 (1.51 cA)^{1/2} T^{-3/4}}{\sqrt{5/2}} \sqrt{3/2}$$

(1.28)

In this equation the current density is inversely proportional to the three-fourths power of the ambient temperature.

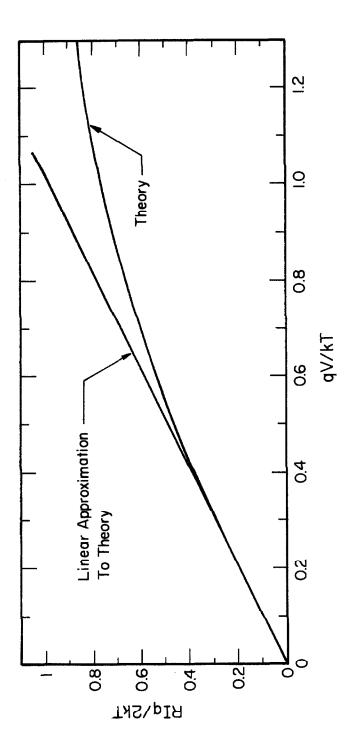

3.4 Impedance. The small signal impedance of the solid-state diode with field independent mobility has been derived by Shao and Wright (8). In appendix A this impedance is determined for a field dependent mobility of the form  $v = \mu E_C(E/E_C)^{1/n}$ . The result is given in table 1.1. The impedances of the idealized solid-state diode (n = 1), of the germanium solid-state diode in the full scl current range (n = 2), and of the vacuum tube diode are included for comparison.

It is seen that the values of the equivalent parallel capacitance  $C_1$  for the cases of n=1 and n=2 differ by a ratio of 3/4:5/7=1.05. The corresponding ratio for the equivalent ac resistance  $R_1$  is  $1/3:2/5\simeq0.83$ . For values of n larger than 2 these ratios do not change significantly, since for  $n\to\infty$ , the corresponding ratios are 9/8 and 2/3. It is thus found that the value of the equivalent parallel capacitance of the small-signal impedance of space-charge-limited currents is only slightly affected by the mobility variations considered. The same

TABLE 1.1

| ν Tω                                           | Vacuum<br>(reference 26)                                              | (reference 8)                                                                     | Sc                                                          | Solid                                                                         |

|------------------------------------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------------------------|

| Field-Velocity<br>relationship                 | 子 <u>2</u> = \$                                                       | 표) = A                                                                            | $v = \mu(E_c E)^{1/2}$                                      | $v = \mu E_c(E/E_c)^{-1/n}$                                                   |

| dc transit time<br>T                           | $\left(\frac{6d\mathfrak{e}_{o}^{m}}{q\mathfrak{j}_{o}}\right)^{1/3}$ | $\left(\frac{2\mathrm{d}\varepsilon_{\mathbf{c}}}{\mu_{\mathbf{j}}}\right)^{1/2}$ | $\left(\frac{9d^2\varepsilon_0}{4\mu^2E_cj_0}\right)^{1/3}$ | $\left( \frac{n+1}{n} \right)^{n} \frac{ee_{o}}{\mu^{n}E_{c}} \sqrt{1/(n+1)}$ |

| dc resistance<br>R                             | $\frac{3}{4} \cdot \frac{\Gamma_o}{C_o}$                              | $\frac{2}{3}$ . $\frac{T_0}{C_0}$                                                 | $\frac{3}{5} \cdot \frac{T_o}{C_o} \cdot .$                 | $\frac{n+1}{2n+1} \cdot \frac{T_o}{C_o}$                                      |

| ac resistance $ m R_{ m l}$                    | $\frac{1}{2} \cdot \frac{T_o}{C_o}$                                   | 1 . T o                                                                           | 2 . T <sub>o</sub> 5 . C <sub>o</sub>                       | $\frac{n}{2n+1}$ $\frac{T_o}{C_o}$                                            |

| Equivalent parallel ac capacitance ${\sf C}_1$ | 3<br>5 ° C <sub>o</sub>                                               | ы 141<br>°<br>С                                                                   | 7 · Co                                                      | $\frac{2n+1}{3n+1} \cdot C_{o}$                                               |

conclusion holds for the ac resistance  $R_1$  of the small-signal impedance (as well as for the dc resistance R) as long as changes in the dc transit time  $T_0$  are accounted for explicitly.

These conclusions must be applied with caution. In practical cases, the mobility does not obey laws of the form  $v = \mu \ E_C(E/E_C)^{1/n}$ . For the range  $0 < E < E_C$ , a linear relation holds. In view of the present results, it seems likely that this more complex case will not exhibit properties which deviate significantly from those of the simple case with constant mobility. However, a more detailed analysis than the present one is needed to fully support this statement.

3.5 Discussion on Validity of Assumptions. The punch-through voltage  $V_{pt}$  is directly proportional to  $W^2$  provided W is much larger than the width  $W_t$  of the transition region of the junction at thermal equilibrium. It is difficult to accurately evaluate  $W_t$  in near-intrinsic materials, but an estimate indicates that at liquid nitrogen temperature,  $W_t$  must be of the order of a few microns in germanium (12). The dependence of  $V_{pt}$  on  $W^2$  is thus expected to break down at base widths of the order of 10  $\mu$ . An adequate theory for the current in the punching-through range as the applied voltage approaches  $V_{pt}$  is not available. However, even the simple model of a transistor in floating

base operation is sufficient to indicate that the current in the punching-through range will increase very rapidly with increasing temperature. Ultimately, there may be no distinction between this range and the low current range.

The effect of diffusion on the V-I characteristic for a solid-state diode in which the mobility is field independent has been considered by Lindmayer et al. (13). They find that for injection densities at the emitter larger than  $p_e = 10^8 \text{ W}^2/\text{cm}^3$ , where W is in cm., the V-I characteristic can be derived directly by assuming that the charge transport through the solid is by drift only. If it is assumed that this condition also holds for field dependent mobility, then for our thickest sample with W = 0.0107 cm  $p_e$  is approximately  $10^4$  holes/cm<sup>3</sup>. But in the high current range, the injected hole density at the emitter is always greater than the  $10^{13}$  donor ions/cm<sup>3</sup> in the base. The factor of  $10^9$  clearly indicates that the effect of diffusion on the V-I characteristic is negligible.

Since it is assumed that the electric field at x = 0 is zero in the low and high current range, the potential maximum must occur at x = 0. However, in the actual case the potential distribution in the base will exhibit a maximum in the vicinity of, but not at, x = 0. Hence the effective width of the conduction medium, which is the distance from this potential maximum ("virtual emitter") to

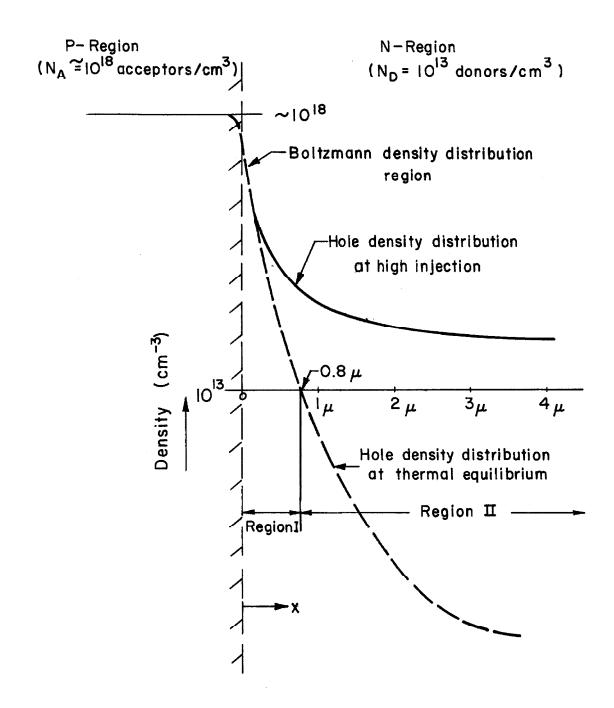

the collector, is less than the base width W. To determine the exact location of this virtual emitter is dif-Therefore the following qualitative analysis is used. The current flow in the vicinity of the virtual emitter is essentially by diffusion. The hole density gradient at the potential maximum will be  $(1/qD_{\rm p}){\rm J}$  which is of the order of 1.3 x  $10^{17}$  J cm<sup>-4</sup>, where J is the current density in  $a/cm^2$  and  $D_{p}$  the diffusion constant for the injected holes in  $cm^2/s$ . From this result it is evident that in the high current range  $(J > 10 \text{ a/cm}^2)$  the density gradient must be higher than  $10^{18}/\text{cm}^{4}$ . In figure 1.6 the hole density distribution at thermal equilibrium and at high injection in the vicinity of the alloyed p-n emitter junction of the solid-state diode is sketched. The doping density in the p-region and the n-region is  $10^{18}$  acceptors/  $cm^3$  and  $10^{13}$  donors/ $cm^3$ , respectively. From the sketch it is evident that hole density gradients of the order of  $10^{18}$  holes/cm<sup>4</sup> at high injection appear within region I of figure 1.6. This is less than  $0.8 \,\mu$  at  $78^{\circ}$  K from the metallurgical junction as shown in figure 1.6 where the value of 0.8  $\mu$  corresponds approximately to 2(  $\epsilon \epsilon_0 \, kT/2qN_D$ )  $^{1/2}$ . Thus in the high current range the effective width of the solid conduction medium can be approximated by the base width W provided W  $\gg$  0.8  $\mu$ . In the low current range the potential maximum will be near the edge of the transition region of the

Figure 1.6. A sketch of the hole density distribution in the vicinity of the alloyed p-n emitter of the germanium solid-state diode.

emitter at thermal equilibrium, which is a distance  $W_{\rm t}$  from the metallurgical Junction. Thus in the low current range the effective width can be approximated by the base width W provided W >>  $W_{\rm t}$ .

A one-dimensional model is assumed for a planar germanium solid-state diode. This assumption is valid provided the ratio of the lateral dimensions to the base width of the solid-state diode is much greater than unity. For the actual solid-state diodes fabricated this ratio is larger than 7.

It has been assumed that the effects of traps, recombination centers, or defects of any kind in the low and high current range are negligible. This assumption appears to be valid for high quality near intrinsic n-type germanium with a doping density as low as  $10^{12}$  donors/cm<sup>3</sup> (4). Our measurements on germanium with a doping density of  $10^{13}$  donors/cm<sup>3</sup> do not indicate the effects of this nature either.

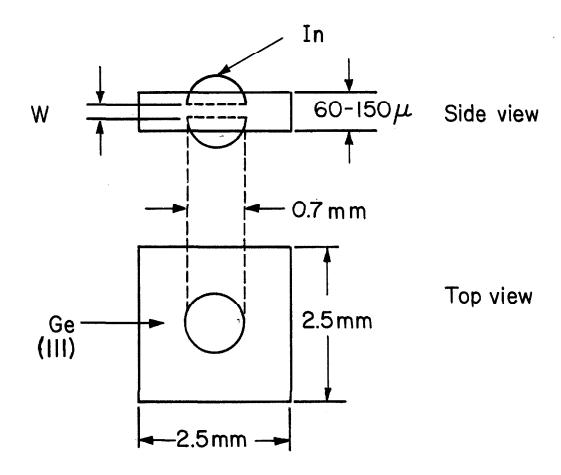

# 4. Experimental Results

- 4.1 Fabricated Germanium P-N-P Solid-State Diode. The fabricated germanium solid-state diode (see chapter II, section 3) consists of a near intrinsic n-type wafer on which two parallel and planar p-type regions are alloyed as shown in figure 1.7. These alloyed p-n junctions form abrupt metallurgical contacts with the parent material (see chapter II, section 4). The separation distance between these two contacts represents the base width (see chapter II, section 4.6). The n-region which contains  $10^{13}$  donors/cm<sup>3</sup> (see chapter II, section 1.1) is of a much lower conductivity than the alloyed p-regions which contain approximately 10<sup>18</sup> acceptors/cm<sup>3</sup> (14). This high density of acceptors makes it possible to consider the p-n injecting junction as an ideal emitter and the p-n collecting junction as a metallic contact. The lateral dimensions of the p-n junctions are made large compared to the base width. From these considerations it is evident that the one-dimensional model discussed in section 3 of this chapter is a good representation of the fabricated germanium solid-state diode.

- 4.2 Voltage-Current Relationship. The V-I characterization of the fabricated germanium solid-state diode is described in chapter II, section 4.7. The V-I characteristics for two different samples as obtained on an

Figure 1.7. A schematic diagram of an alloyed p-n-p germanium structure (not drawn to scale).

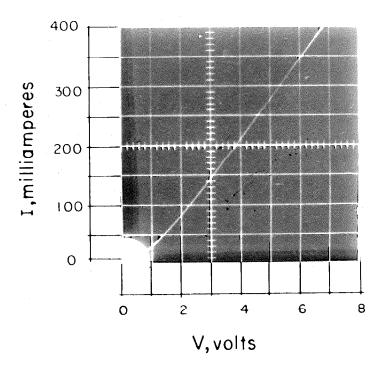

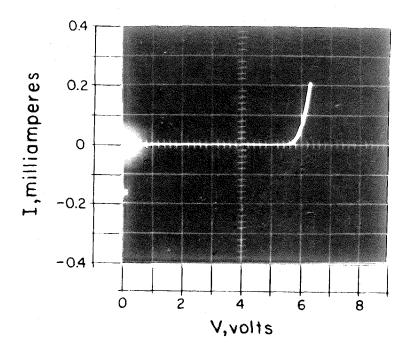

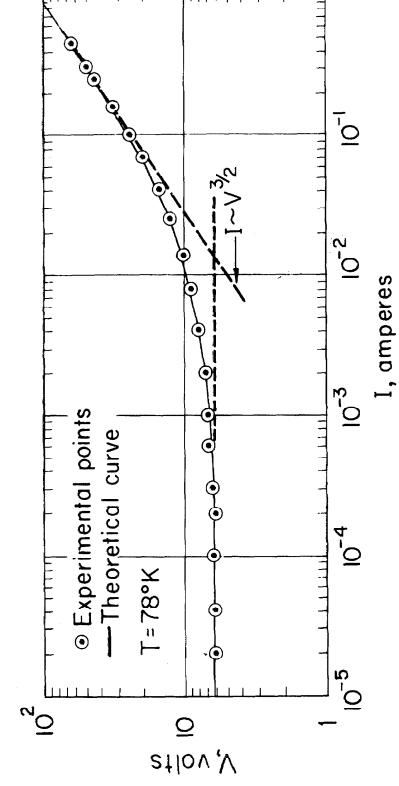

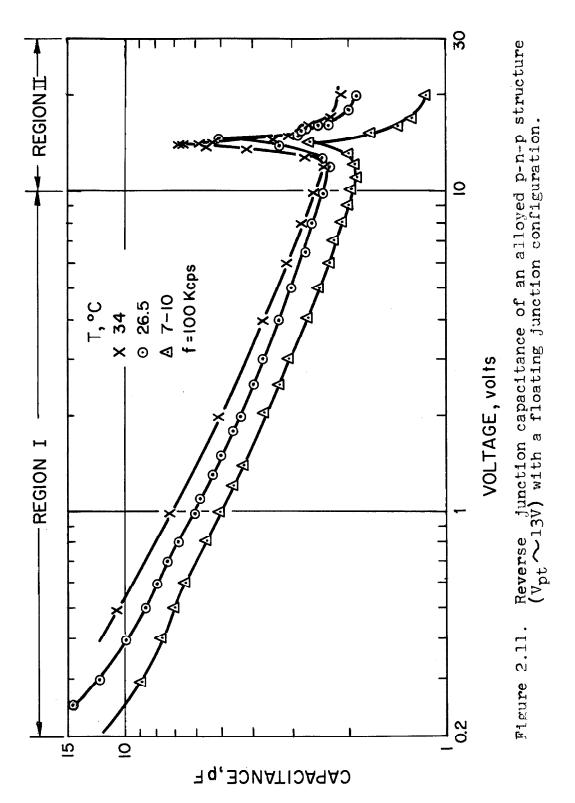

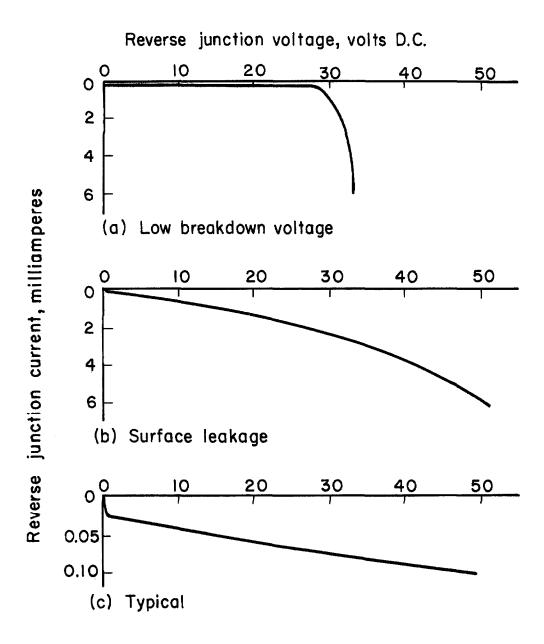

oscilloscope display are shown in figures 1.8a and 1.8b. The V-I characteristic in figure 1.8a is of the sample with the narrowest base width (8.3 \mu), and it clearly exhibits the operation of the solid-state diode in the high current range. For currents larger than 10 ma, the three-halves power relationship is obeyed as shown in figure 1.10. The maximum current passed through the sample is about 800 ma which is equivalent to 180 a/cm². In figure 1.8b the V-I characteristic exhibits very clearly the operation of the solid-state diode in the punching-through range. For voltages less than the punch-through voltage the saturation current is of the order of 1 \mu a. This sample which has a 34.7 base-width also exhibits a three-halves power relationship as shown in figure 1.9, but this is at much higher currents than shown in figure 1.8b.

In figure 1.9 the experimental result for a fabricated  $34.7~\mu$  base width solid-state diode at an ambient temperature of  $78^{\circ}$  K is compared with theory. For this sample it is clearly evident that two straight lines can be drawn through the experimental points in figure 1.9: the V = 6.2 volt line (low current asymptote) and the  $I \sim V^{3/2}$  line (high current asymptote). Furthermore, if the normalized theoretical curve shown in figure 1.5 is fixed between these two lines an excellent fit between the theoretical curve and the experimental points.

Figure 1.8a An oscilloscope trace of a V-I characteristic of the narrowest base width sample.  $(\text{W=}\,8.3\,\mu\;,\,\text{V}_{\text{pt}}\simeq\text{0.13V, and T=}\,78^{\circ}\text{K})$

Figure 1.8 b An oscilloscope trace of a V-I characteristic of a  $34.7\mu$  base width sample.  $(V_{pt}=6.2 \text{ V and T}=78^{\circ}\text{K})$

A comparison between theory and experiment for scl current 1n a n-n-p germanlum structure at T =  $78^{\circ}$  K. (W = 34.7  $\mu$ , A = 4.24  $10^{-3}$  cm<sup>2</sup>. N<sub>D</sub> =  $10^{13}$  cm<sup>-3</sup>, and V<sub>pt</sub> = 6.24V). Figure 1.9.

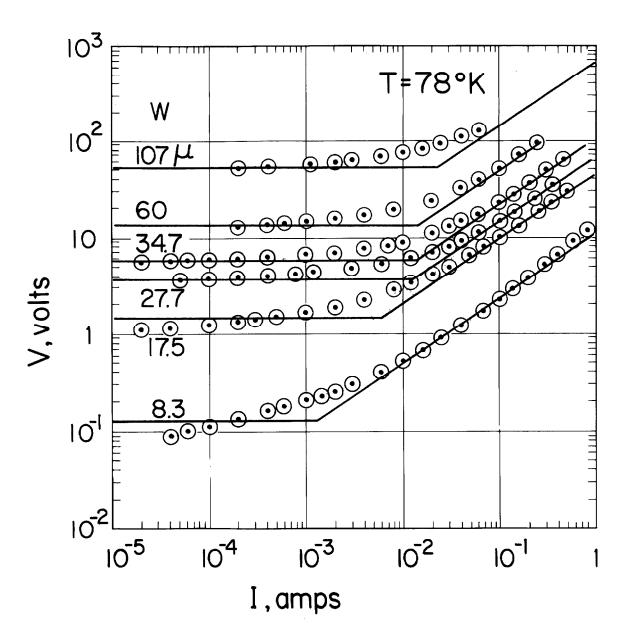

In figure 1.10 the experimental results for the solid-state diodes of various base widths at an ambient temperature of  $78^{\circ}$  K are given. The low and high current ranges can be represented by two straight lines as indicated in figure 1.9 except for the 8.3 µand the 17.5 µsamples. For these samples the low current lines are determined by finding the best fit between the theoretical curve and the experimental points. The base width in each sample is indicated in the figure. The junction area and the base width of each sample are given in table 1.2.

TABLE 1.2

| Base width<br>10 <sup>-4</sup> cm | Junction area |

|-----------------------------------|---------------|

| 8.3                               | 4.52          |

| 17.5                              | 4.24          |

| 27.7                              | 4.31          |

| 34.7                              | 4.24          |

| 60                                | 4.24          |

| 107                               | 4.18          |

Figure 1.10. V-I characteristics of p-n-p germanium structures of different base widths at  $T = 78^{\circ}$  K.

The base width ranges from 8.3  $\mu$  to 107  $\mu$  and the punch-through voltage ranges from 0.13 V to 55 V. The base width range of more than one order of magnitude and the corresponding punch-through voltage range of more than two orders of magnitude cover a wide range of operation in which the current-voltage characteristics of the fabricated samples are studied.

There are two anomalies observed in the 8.3 µ base width sample. First, in the high current range of this sample, the current-voltage characteristic deviates from the three-halves power relationship in the region in which the electric field at the collector is greater than 104 V/ It was mentioned in section 2.3 of this chapter that at very high electric fields the drift velocity becomes saturated. When this is the case, the current is directly proportional to the voltage. The tendency of the deviation observed is in the direction expected for saturating drift velocity. The value of 104 V/cm for the electric field is that expected from theory (11). Second, for this sample, as well as for the 17.5  $\mu$  base width sample, a deviation is also observed at very low currents. The theoretical analysis presented in section 3 of this chapter is based on the assumption that the punch-through voltage is determined by the base width W. This assumption is true as expressed in equation 1.13 provided the width of the transition region of the emitter and collector junction for zero current is much less than the base width. However, for these samples, particularly for the  $8.3\,\mu$  sample, this assumption is not valid. In this case a deviation is observed as expected.

The agreement between theory and experiment is excellent and where deviations do occur (for the narrow base width samples), there is valid reason for expecting these deviations. In fact, they tend to demonstrate the necessity of the assumptions made in the theory. The experimental results indicate that for each sample considered there is space-charge-limited current. Furthermore, they conclusively exhibit the two ranges of operation (the low and the high current range).

The only other published measurement of space-charge-limited current in germanium is that of Dacey (4). In his paper he presents the results for only one sample with a base width of 280  $\mu$  and a punch-through voltage of 40 V. The maximum current density of 10 a/cm<sup>2</sup> reported was not sufficient to exceed the intermediate current range.

4.3 Base Width Dependence. Another important feature in the theory of scl current is the base width dependence. A convenient way to express this dependence is to rearrange equation 1.20 into the following form

$$V = \left(\frac{(2/3)(5/3)^{3/2} e e_0 \mu_0 E_c^{1/2}}{J}\right)^{-2/3}$$

(1.29)

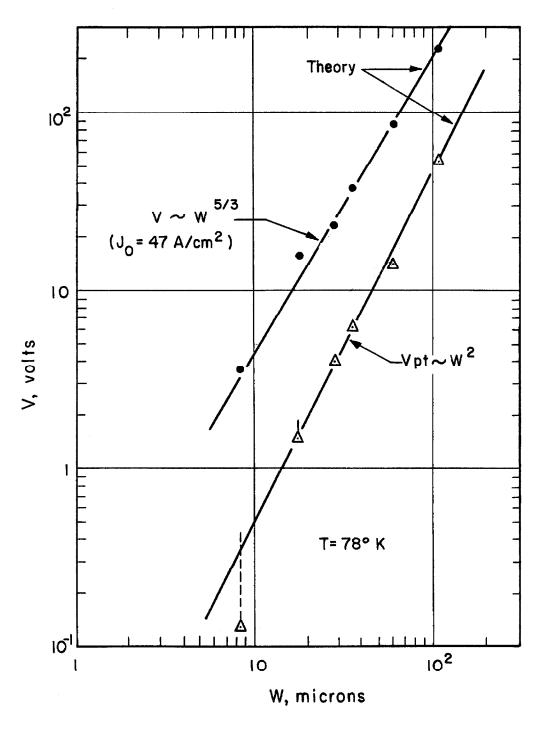

From this equation it is seen that if the current density J and the ambient temperature are kept constant, while the base width is allowed to vary, the applied voltage V is directly proportional to the five-thirds power of the base width.

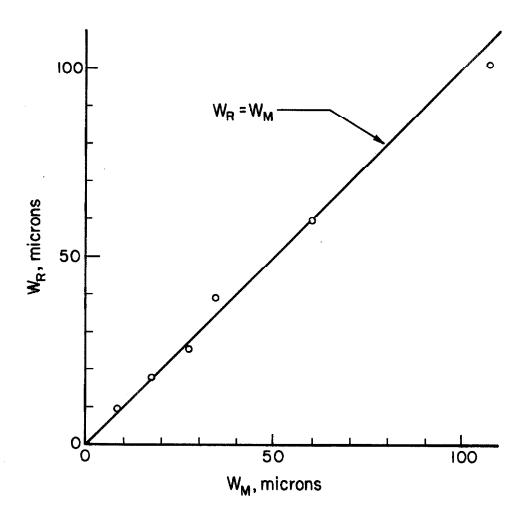

A verification of this dependence is possible. Since there are samples of different base width, all that is necessary is to keep the ambient temperature and the current density constant for all samples and to measure the resulting applied voltages. These voltages can be obtained directly from figure 1.10. The constant current density chosen is 47 a/cm<sup>2</sup>. This value is within the three-halves power range for all samples. In figure 1.11a this result is compared with theory.

The agreement between theory and experiment is excellent. Any deviation observed is within the expected experimental error of about 5%. From this result it is concluded that there is indeed the base width dependence as predicted by theory.

There is also a base width dependence at punchthrough. In accordance with equation 1.13 the punch-through voltage is directly proportional to the base width squared.

Figure 1.11. A comparison between theory and experiment for (a) scl current ( $v\sim w^{5/3}$ ) (b) punch-through voltage ( $v_{\rm pt}\sim w^2$ )

This relationship can be checked experimentally by referring to the very low current range in figure 1.10 where the punch-through voltage of each sample is measured. The experimental result obtained in this manner is plotted and compared with theory in figure 1.11b.

The agreement between theory and experiment is excellent for the samples of larger base width. A marked deviation from theory is observed for the  $8.3~\mu$  sample. The width of the emitter transition region for zero current is not negligible when compared with base widths of  $8.3~\mu$  and  $17.5~\mu$  as explained in section 4.2~of this chapter. For this case, and particularly for the  $8.3~\mu$  sample, the second power relationship does not hold as expected. For these two samples equation 1.12~cannot be reduced to equation 1.13. Furthermore the transition from the punching-through range to the high current range through the low current range is more rapid for the narrower base width samples. As a result the low current range for the very narrow base width samples may not be clearly defined.

From the experimental result for the punch-through voltage, the donor doping density  $N_D$  can be obtained. The value of  $N_D$  determined from figure 1.11b is  $9.2 \times 10^{12}$  donors/cm<sup>3</sup>. This value agrees within the expected experimental error of approximately 10 percent with that deduced from resistivity measurements.

4.4 Critical Electric Field. The coefficient in the base width - voltage relationship expressed in equation 1.29 can be determined directly from the experimental result in figure 1.11a. Because the low field hole mobility  $\mu_0$  can be expressed as  $\mu_0$  = 1900 (300/T)<sup>1.7</sup> cm<sup>2</sup>/Vs, where T is the ambient temperature (see section 1.1 of chapter II), the critical electric field  $E_c$  can be determined from the experimental value of this coefficient. The value so obtained for  $78^\circ$  K is 21 V/cm. Similarly, the critical electric field can be determined from the current-voltage measurements made on a few samples for other ambient temperatures (see following section). These values as well as corresponding theoretical values are given in table 1.3.

The experimental values of the critical electric field in table 1.3 for  $195^{\circ}$  K and  $273^{\circ}$  K are the average of three and two samples, respectively. Although the variation in the value of  $E_{c}$  from sample to sample in this temperature range is appreciable, the average value compares favorably with the intermediate theoretical value. At  $78^{\circ}$  K the value of  $E_{c}$  is based on a much larger number of samples and as a consequence it is more reliable. This value is comparable to the theoretical value for the discrete energy distribution. In all cases, the experimental values of  $E_{c}$  fall within the range of the theoretical values. Ryder's

TABLE 1.3

| Ambient     | Critical Electric Field V/cm |                 |                 |                |  |

|-------------|------------------------------|-----------------|-----------------|----------------|--|

| Temperature | Theory*                      |                 |                 | Experiment     |  |

| т°к         | E <sub>c1</sub>              | E <sub>c2</sub> | E <sub>c3</sub> | E <sub>c</sub> |  |

| 78          | 29                           | 43              | 52              | 21             |  |

| 195         | 140                          | 210             | 250             | 220(1 ± 0.4)   |  |

| 273         | 250                          | 360             | 440             | 330(1 ± 0.3)   |  |

results (9), which are based on conductivity measurements, are more than a factor three higher. Compared to this, the present results are in good agreement with theory.

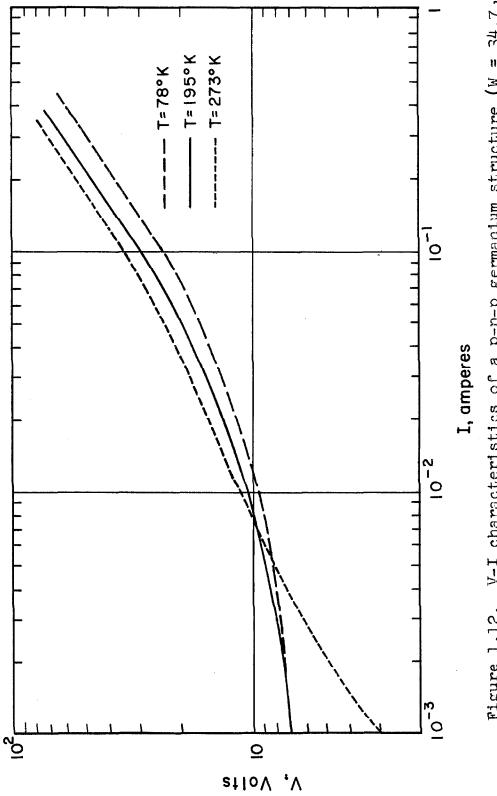

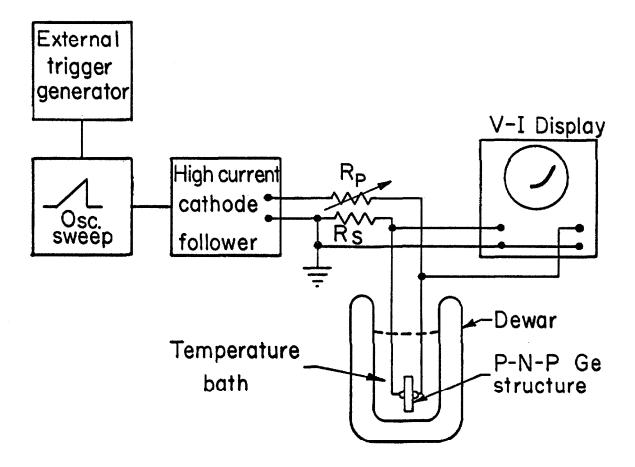

4.5 Temperature Dependence. In figure 1.12 the voltage-current characteristic of the 34.7 μ sample is plotted for different ambient temperatures to show its effect on scl current. The measurements are described in chapter II, section 4.7.

The important experimental results are: Scl current increases as the ambient temperature decreases for a constant applied voltage. This is the current-temperature

<sup>\*</sup>The theoretical values  $E_{cl}$ ,  $E_{c2}$ , and  $E_{c3}$  are for the Boltzmann, the discrete, and the intermediate hot hole distributions respectively (see chapter I, section 3.3).

V-I characteristics of a p-n-p germanium structure (W =  $34.7~\mu$ ) at different ambient temperatures. Figure 1.12.

tendency expected as expressed in section 3.3 of this chapter. The two ranges of operation described in section 3.2 of this chapter are observed for the three different ambient temperatures (273° K, 195° K and 78° K) considered. This is evident from the fact that the curve for 195° K is a translation of the curve for 78° K along the current axis. Except for very low currents, this also holds for the 273° K curve. The deviation observed is in the direction expected for large saturation currents. This is very probable since this deviation occurs at higher temperatures where larger saturation currents are present. No quantitative analysis of this deviation is given.

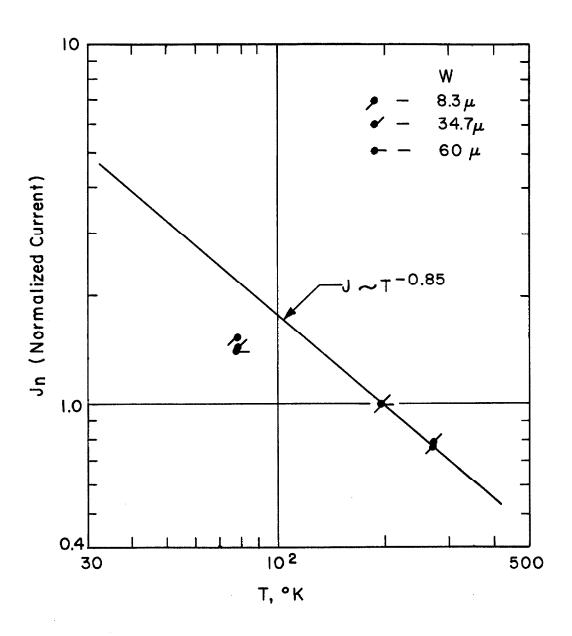

If we consider the solid-state diode in the high current range of operation in which the applied voltage is kept constant while the ambient temperature is varied, then a quantitative relationship between the current and the ambient temperature can be obtained. Furthermore, if we normalize the measured current to unity at one particular ambient temperature, it is then possible to represent the current-ambient temperature relationship for different samples on one graph. The results so obtained are shown in figure 1.13 where the temperature of normalization is 195° K.

A theoretical curve is also shown in this figure. Its slope of -0.85 is a modified value of -0.75 given in equation 1.28. This modification has been introduced to

Figure 1.13. A comparison between theory and experiment for scl current as a function of the ambient temperature.

account for the temperature dependence of the low field mobility as measured (see chapter II, section 1.1), which is A  $T^{-1.7}$  instead of A  $T^{-1.5}$  as assumed in the theory.

In figure 1.13 a good agreement between theory and experiment exists for the high temperature range, but for 78° K there is a deviation of about 50 percent. However, the small number of measurements do not justify a quantitative comparison with theory. Furthermore, it is evident in section 3.3 of this chapter that the theory is itself semi-quantitative in that two different energy distributions are considered for the hot holes. Also, in section 4.4, the experimental results for the critical electric field tend to indicate a transition of the energy distribution of the hot holes from the Boltzmann distribution towards the discrete distribution as the temperature is lowered. If this were indeed the case, then from table 1.3 a deviation of about 50 percent would be expected in figure 1.13 at 78° K, as observed.

In summary, the agreement between theory and experiment is sufficient to indicate that a current-temperature dependence exists and that this dependence is of the magnitude expected.

## CONCLUSIONS

The theory of scl current in a germanium p-n-p solid state diode predicts three regions of operation: the punching-through region, the low current range in which the effect of the donor ions is significant, and the high current range in which the effect of the donor ions is negligible. The presence of the low and the high current range is experimentally confirmed.

At punch-through the relationship between punch-through voltage and base width W has been experimentally determined. These observations agree with the theory and show a  $\mathbb{W}^2$  dependence as expected.

In the high current range the current is directly proportional to  $V^{3/2}$ . This is the dependence expected for pure scl current for the field dependent mobility. The relationship between voltage V and base width has also been determined in this range. The results verify the theory which predicts a dependence of  $W^{5/3}$ . A quantitative analysis of this relation leads to a value of 21 V/cm for the critical electric field  $E_c$  at  $78^\circ$  K. At  $195^\circ$  K  $E_c$  is  $\simeq 220$ V/cm and at  $273^\circ$  K it is  $\simeq 330$ V/cm. These values fall within the range indicated by Shockley's theory. It is the best correspondence between this theory and experiments obtained to date. This makes it possible to relate these results to the energy distribution of the hot holes.

There is an indication that at lower ambient temperatures the distribution tends to become discrete.

These results are the first detailed verification of the validity of the theory of scl current in solids.

The velocity of the hot holes is known to saturate at fields of approximately  $10^4$  V/cm. When this value was reached in one sample (8.3  $\mu$  sample), the V-I characteristic deviated from the three-halves power relationship as expected. The measured peak current density of  $180a/cm^2$  exceeds values reported so far on scl current in solids by one order of magnitude.

The theory of the impedance of a solid-state diode has been extended to include the case of a field dependent mobility. A verification of this theory is yet to be presented.

#### CHAPTER II

#### FABRICATION, EVALUATION AND MEASUREMENT

### Introduction

A practical device, which can be represented adequately by the theoretical model for one-dimensional scl current flow in n-type germanium, must be a p-n-p structure with flat, parallel, and abrupt p-n junctions. Furthermore, the ratio of the lateral dimensions to the base width of the structure should be large to minimize edge effects. Finally, the n-type germanium must have a low uniform donor doping concentration and must be of high crystalline quality.

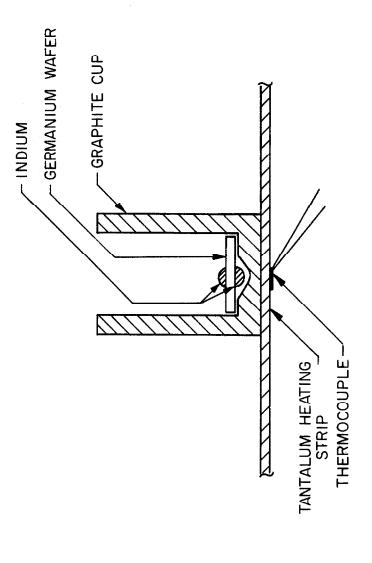

A commercially obtained single crystal of high quality near intrinsic n-type germanium is used for the fabrication of p-n-p structures. Pertinent physical parameters of the single crystal are measured as described in section 1 of this chapter. Since alloyed junctions offer the best approximation to the requirement of abruptness, the experimental devices to be described in this chapter are therefore alloyed p-n-p structures. The condition of flatness is most readily satisfied for junction orientations perpendicular to the [111] axis of the germanium crystal (15). Prior to the cutting and dicing operation, the single crystal must therefore be

crystallographically oriented. The procedure followed is described in section 2. In section 3 the details of the alloying process are presented. The structures obtained are characterized in section 4.

## 1. Measurement of Material Properties

A germanium ingot was obtained from Hughes Semiconductors with the specification that it was n-type and

near intrinsic and that it was grown in the (111)

direction. The density of donors and the charge carrier

mobility in the bulk material were not specified. These

electrical properties had to be determined from the bulk

resistivity and Hall measurements.

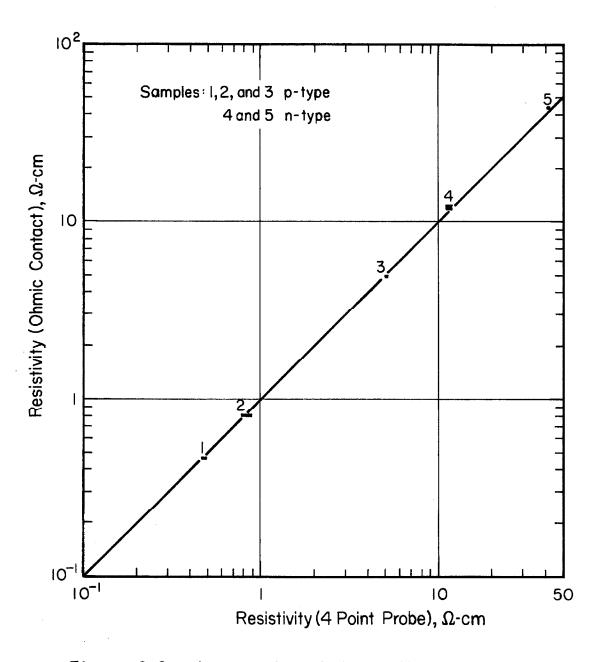

1.1 Resistivity Measurements. A rectangular filament of cross-sectional area  $A = 6.6 \cdot 10^{-2} \text{ cm}^2$  and length L = 1.87 cm. is cut from the near intrinsic n-type germanium ingot with a diamond saw. Electrical contacts (see chapter II, section 4.3) are made to the end faces. It is then mounted on an electrically insulated copper block and immersed in a temperature bath. A direct current I = 1 ma is passed through it. Two tungsten probes positioned by micromanipulators are used to measure the potential drop along the filament. The voltage across the probes is measured with a galvanometer. The advantage of this probing method is that any variations in the bulk resistivity along the filament can be detected and that non-linearities in the end contacts do not affect the result. No variation in the bulk resistivity has been observed. It was also noticed that the electrical contacts were

blocking at temperatures below -100° C. In making resistivity measurements at different temperatures, three different temperature baths are used: liquid xylene for 25° C to 105° C, liquid pentane cooled with liquid nitrogen for 25° C to -125° C, and finally liquid nitrogen for -195° C.

The bulk resistivity  $\rho$  for a rectangular filament at a temperature T is

$$\rho = \frac{A}{L} \left| \frac{V_{p1} - V_{p2}}{I} \right| \tag{2.1}$$

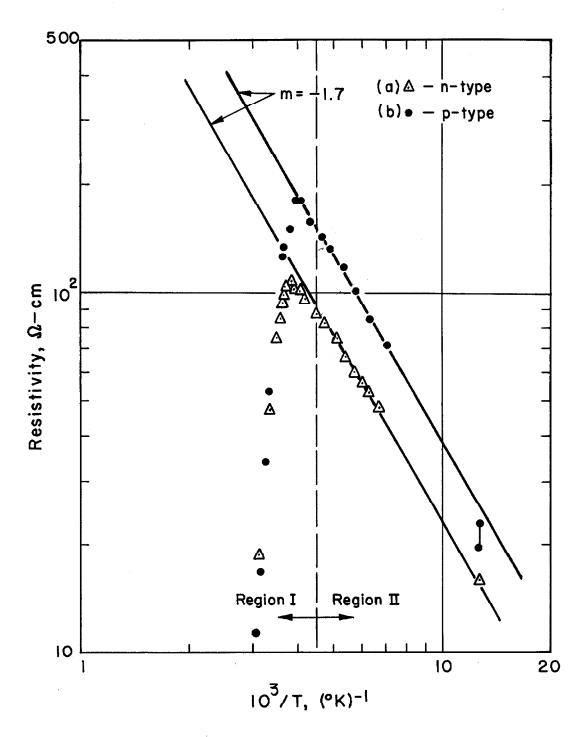

where  $V_{p1} - V_{p2}$  is the potential difference between the two probes. These results are shown graphically in figure 2.1a. The temperature dependence of the bulk resistivity is divided in two regions: for high temperatures the bulk material is intrinsic, and for low temperatures it is extrinsic. For the latter the temperature dependence is

$$\rho(T) = \frac{1}{q \, \mu_{\rm n}(T) N_{\rm D}} \tag{2.2}$$

where  $\mu_n(T)$  is the electron mobility and  $N_D$  the donor density (full ionization assumed). The electron mobility as a function of temperature T is expressed as

$$\mu_{\rm n}(T) = \mu_{\rm n}(300^{\circ} \text{ K}) \left(\frac{T^{\circ} \text{K}}{300^{\circ} \text{K}}\right)^{\rm m}$$

(2.3)

where m is equal to -1.5 for lattice scattering (16). The experimental value of m is -1.7 as obtained from figure 2.1a. This is in good agreement with the value of

Figure 2.1. Resistivity measurements: (a) Hughes Semiconductors germanium crystal; (b) Semimetals' germanium crystal.

-1.64 of Debye and Conwell (17). Similarly the results for a near intrinsic Semimetals' germanium ingot are given in figure 2.1b. This specimen, as determined from Hall measurements, is p-type and not n-type, as specified by the manufacturer. For this case, the majority carrier (hole) mobility  $\mu_p(T)$  as a function of temperature T is

$$\mu_{\rm p}({\rm T}) = \mu_{\rm p}(300^{\circ} \text{ K}) \left(\frac{{\rm T}^{\circ} \text{ K}}{300^{\circ} \text{K}}\right)^{-1.7}$$

(2.4)

Morin and Maita (18) observe a T<sup>-2.33</sup> dependence for the hole mobility in near intrinsic p-type material.

For electron and hole mobility values in germanium of 3900 cm<sup>2</sup>/Vs and 1900 cm<sup>2</sup>/Vs respectively at 300° K (19), a doping density of  $(1.0 \pm 0.1) \ 10^{13} \ donors/cm^3$  and  $(1.1 \pm 0.1) \ 10^{13} \ acceptors/cm^3$  in the near intrinsic n-type and p-type germanium respectively is determined. Furthermore the electron and hole mobility as a function of temperature is  $3900(T/300)^{-1.7}$  and  $1900(T/300)^{-1.7}$  cm<sup>2</sup>/Vs respectively. These are the low field mobility values (see chapter I section 2.3).

An important parameter in the theory of scl current in germanium p-n-p solid-state diode is the minority mobile carrier (hole) mobility. This mobility should have about the same temperature dependence as that of the holes in the near intrinsic p-type germanium.

- 1.2 Hall Effect Measurements. The near intrinsic n-type germanium crystal has been analyzed quantitatively by Hall effect measurements. The procedure followed is that of Debye and Conwell (17). The results are:

- 1. The value of the resistivity as well as its temperature dependence agree completely with the 2 point probe measurements.

- 2. The donor impurity concentration  $N_D$  is (1.1  $\pm$  0.1)  $10^{13}$  cm<sup>-3</sup> if corrections for scattering mechanisms are ignored. This compares well with the value of (1.0  $\pm$  0.1)  $10^{13}$  cm<sup>-3</sup> deduced in the previous section. According to theory,  $N_D$  should be corrected by a factor of 1.18 in the case of pure lattice scattering. However, theory also predicts a temperature independent value of  $N_D$ . But measurements show a variation of about 10% between  $78^{\circ}$  K and  $243^{\circ}$  K, so that corrections of this order of magnitude are uncertain and have been omitted.\*

- 3. The above results confirm that the temperature dependence of the mobility assumed in the previous section is valid.

- 4. Measurements made on the first and the last wafer cut from the crystal differ by less than 10%. The manufacturer considers this an unusually good result, since

$<sup>\</sup>ensuremath{^{*}N_D}$  can also be determined independently from junction depletion capacitance measurements, but not to the same degree of accuracy.

crystals of such low doping concentration often show much greater inhomogeneity.

1.3 Lifetime Measurements. The lifetime of minority charge carriers, which is an important parameter in evaluating the saturation current of a p-n junction, has been determined by the recovery time method (20). The result is 11 µs. This value is approximate since the analysis is based on a low injection model. A much longer lifetime is anticipated for materials of the purity of this near intrinsic n-type germanium single crystal. However, it has been suggested that a large concentration density of dislocations (of the order of 10<sup>3</sup> cm<sup>-2</sup>) might be present which could account for this discrepancy.

## 2. Crystal Alignment

There are two principal methods to determine the orientation of a single crystal of germanium. They are the X-ray diffraction and the etch pit methods (21). The etch pit technique is chosen here for two reasons: first, the measuring apparatus can be constructed rather easily, and second, the necessary cutting, lapping and etching operations are similar to those needed also in fabricating p-n junctions.

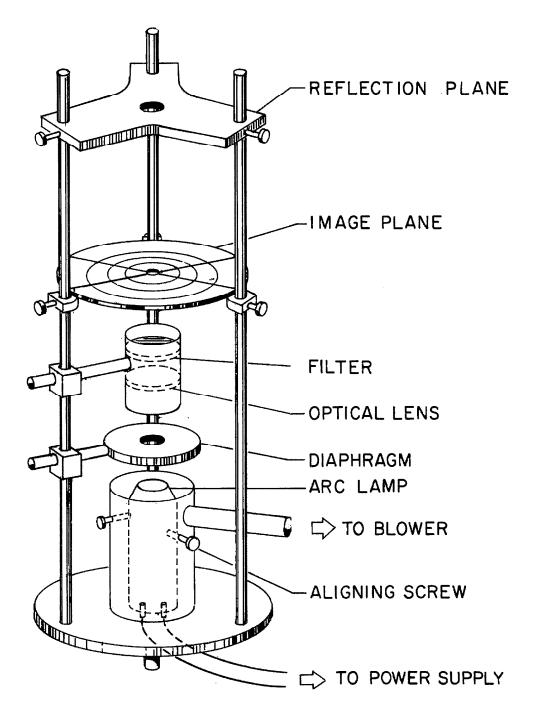

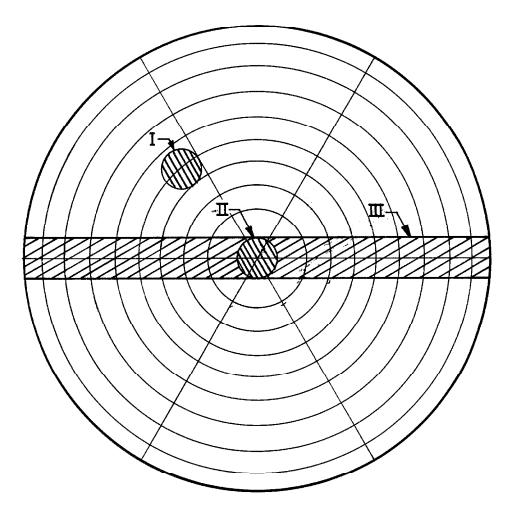

2.1 Optical Apparatus for Crystal Alignment. The optical system consists of a collimated beam of light generated in an arc lamp. This beam is directed at a right angle to the etched germanium surface from which it is reflected onto a graduated image plane (figure 2.2). The distance of separation between the reflecting surface and the image plane is determined by the focal length of the lens and its distance from the surface. The focused image of the light source appears on the image plane.

An etched reflecting surface can be represented by a set of non-parallel reflecting planes. There will be an image for each one of these reflecting planes. The etched surface of a germanium crystal whose orientation is approximately perpendicular to the [111] axis can be represented by five non-parallel planes. Four of them correspond to

Figure 2.2. Optical apparatus for crystal alignment.

Drawn approximately to 1/4 of actual size.

the facets of the etch pits which have the form of truncated triangular pyramids. The germanium surface itself corresponds to the fifth plane. There will be five images corresponding to these five planes. The position of these images on the focal plane reveals the relative angular orientation of these planes.

If the germanium surface is perpendicular to the [111] direction, then the reflecting plane corresponding to the truncated bottom of the etch pit pyramids is parallel to the crystal surface. Also, the three planes corresponding to the three sides of the etch pits will form the sides of a regular triangular pyramid. This will be indicated by a three-fold symmetry of the image pattern. The image pattern of an aligned crystal is shown in figure 2.3. The images do not have well defined but rather diffuse boundaries caused by small inequalities among the facets of different etch pits. The accuracy with which crystal alignment can be determined is limited to the accuracy with which the center of each image can be located.

If the germanium surface is not perpendicular to the [111] direction, then there will be five distinct images. Due to the preferential action of the etch, the bottom of the etch pits remains closely aligned with the (111) plane so that the corresponding image can be used as a reference for the alignment of the crystal.

Figure 2.3 Image pattern of an etched (III) germanium crystal plane.

2.2 Crystal Preparation for Alignment. The face of the germanium ingot to be aligned crystallographically is etched with a superoxol etchant (22) to obtain a first approximate location of the (111) crystal planes. The ingot is then cemented with wax (Apiezon W) on a jig that is rigidly fastened to the horizontal cutting table of the diamond saw. Two horizontal lines are then scribed on the face of the ingot. A slice of approximately 1.5 mm thickness is cut from the ingot. This cut is oriented as closely as possible into the direction of the (111) plane as previously determined by rotating the table of the saw.

The pre-oriented side of the slice is lapped by hand on a 600A silicon carbide paper to remove the coarse mechanical damage, and then lapped to a fine uniform texture on 3200 mesh grinding compound on a glass plate. The slice is then cut along the scribed lines and the two ends of the remaining wafer are truncated also so that the wafer fits into a wafer holder. These last two cuts are not made parallel to each other to assure that the position of the wafer with respect to the ingot is not lost. The wafer is removed from its cutting jig with trichlorethylene which dissolves the wax, is washed in acetone to remove the trichlorethylene, rinsed in distilled water and dried by absorbing the water with Kimwipe tissue. The wafer is now cemented with its unlapped side on the wafer holder of the

orienting jig. This jig allows one to vary and set the angle of the lapping operations to follow.

The wafer surface is de-oxidized with a concentrated solution of HF for two minutes, rinsed thoroughly with distilled water, immersed in a concentrated solution of  $\rm H_2O_2$  for ten minutes, and finally rinsed thoroughly with distilled water. The surface is then etched for about five minutes at room temperature with an etchant of 3 ppv concentrated  $\rm H_2O_2$  and 1 ppv concentrated HF, then thoroughly rinsed in distilled water and dried with Kimwipe tissue. If the reflection pattern of the surface is not well defined, the etching procedure is continued in one minute steps until a maximum of definition and intensity is obtained in the pattern. This etchant produces a relatively small density of large and well defined etch pits on the germanium surface, which gives a clear reflection pattern with little scatter.

2.3 Crystal Alignment. If the etched surface of the wafer is not well aligned with the (lll) plane of the crystal, then there will appear five distinct images on the focal plane of the alignment apparatus. The wafer is then adjusted in the lapping jig until the image corresponding to the bottom plane of the etch pits coincides with the center of the focal plane. The wafer is re-lapped, re-etched,

and readjusted and these operations are repeated until the final adjustment compensates for the last differences in the relative intensities and for the deviations from the three-fold symmetry in the reflection pattern. An image of the pattern for an aligned crystal is shown in figure 2.3.

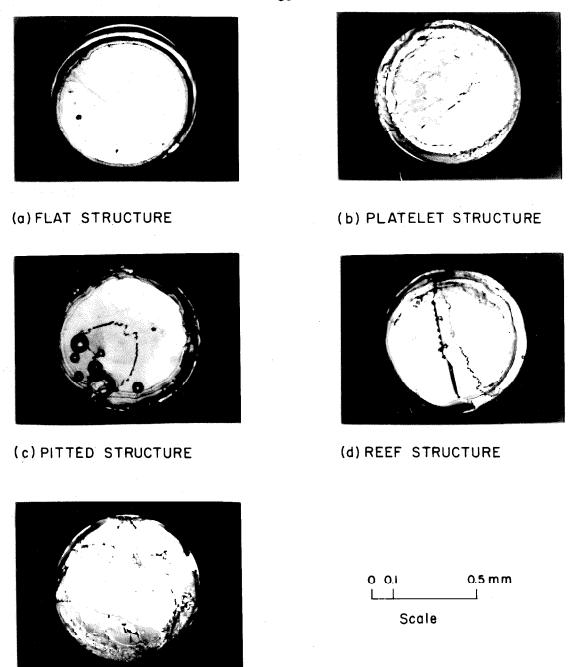

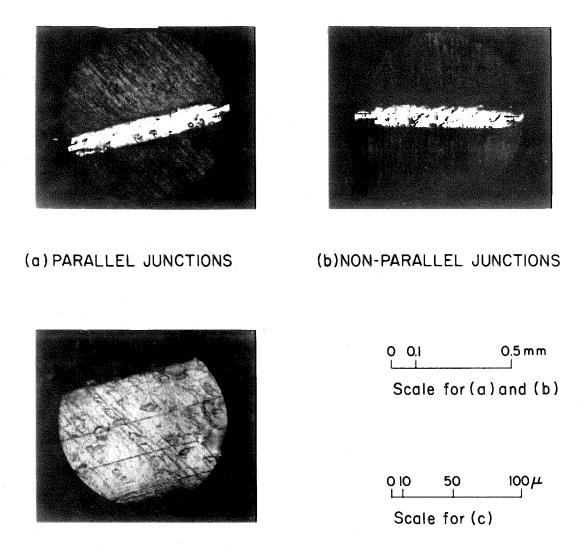

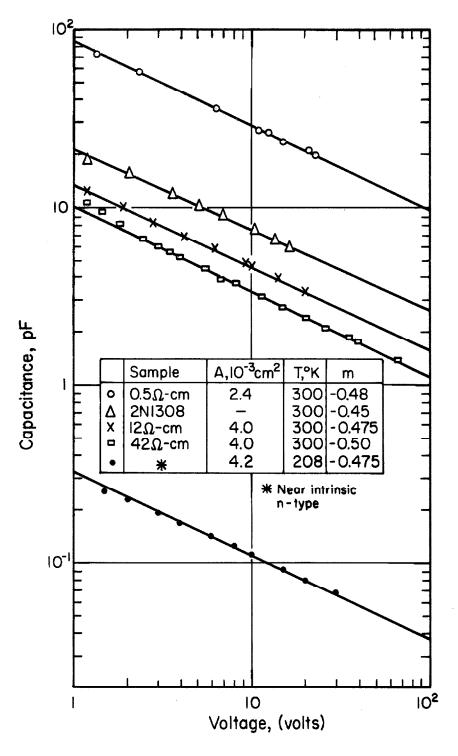

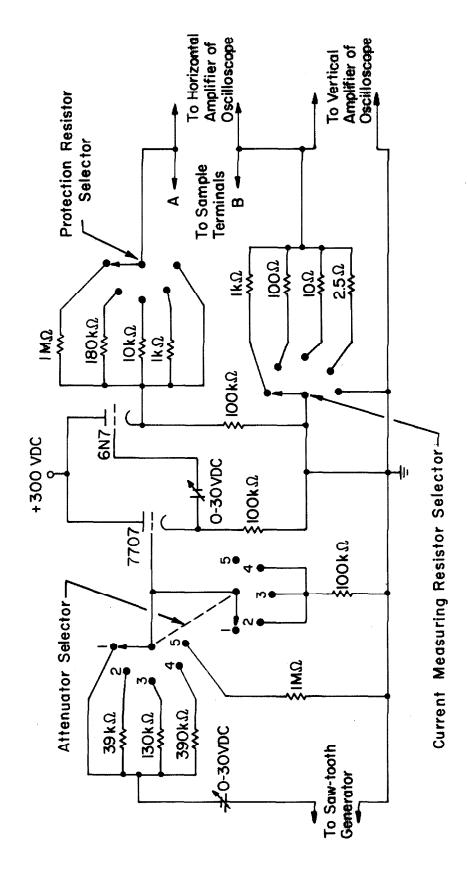

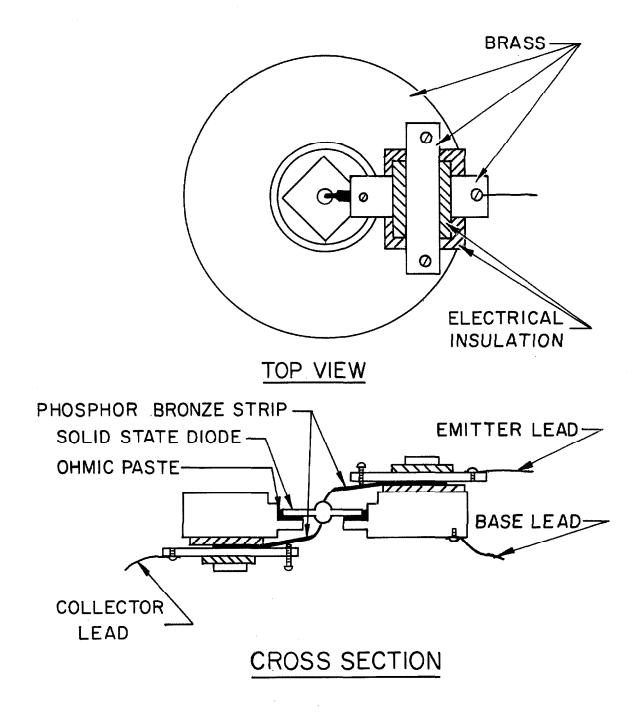

Once the wafer is aligned, its orientation relative to the original cut has to be measured. For this purpose, a section of the wafer surface had been covered by wax prior to the initial etch. Care was taken to protect this section from further lapping or etching during alignment. In a final operation, the aligned surface is re-lapped, the wax protecting the section of non-aligned surface is removed, and the whole surface is etched in a diluted superoxol etchant long enough to produce a polished texture. The surface of the wafer now forms two reflecting planes corresponding to the aligned and the original non-aligned surface. Lines parallel to the parallel sides of the wafer are scribed on the non-aligned section of the surface. reflection pattern now consists of two images, corresponding to the two planes, and a narrow ribbon of light which is reflected from the scribed lines and is in a direction perpendicular to that of the lines. Such a pattern is shown in figure 2.4. The position of the images relative to the ribbon of light permits one to determine the angular dis-(111) crystal plane with respect to the placements of the