# PROPERTIES OF AN ARBITRARILY DOPED FIELD-EFFECT TRANSISTOR

Thesis by

Ira Richer

In Partial Fulfillment of the Requirements

For the Degree of

Doctor of Philosophy

California Institute of Technology

Pasadena, California

1964

(Submitted May 21, 1964)

## ACKNOWLEDGMENT

I thank Dr. R. D. Middlebrook whose guidance and encouragement underlie this work. I am grateful to the National Science Foundation for their financial support under the Graduate Fellowship program.

The following companies donated some of the transistors reported on: Fairchild, Motorola, Siliconix, and Texas Instruments. Their help is appreciated.

Miss Doris A. Barnhart, who typed the manuscript, deserves special thanks for her patience and cooperation. Finally, I would like to acknowledge my colleagues at Caltech for numerous helpful discussions during the course of this research.

#### ABSTRACT

The properties of p-n junction field-effect transistors (FET's) are formulated on a general basis, in terms of an arbitrary doping profile (i.e. arbitrary gate-channel impurity distribution). The external behavior is shown to be quite insensitive to the doping profile, provided that the profile satisfies certain weak restrictions. Essentially all practical structures are included in the restricted theory. A theoretical basis is thus provided for the much-used empirical conclusion that widely different types of FET's exhibit similar functional behavior. More specifically, upper and lower bounds are obtained on the normalized transconductance, drain current, input especitance, and bias point for zero temperature coefficient of the drain current, and on the voltage-dependent parts of various figures of merit. In each case the bounds represent the solutions of two analytically simple structures, a step-junction FET and a delta-junction FET. Many practical implications stem from these results.

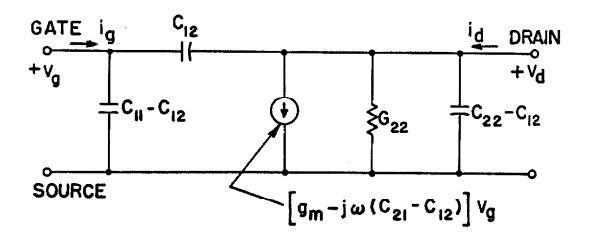

Finally, a complete, small-signal, low-frequency equivalent circuit for an arbitrarily doped FET is developed by considering the capacitive current that flows between the channel and the gate. Beyond pinch-off a "new" element, the forward transfer capacitance, is present in the circuit. Below pinch-off the theory predicts that the output capacitance  $C_{22}$  and the reverse transfer capacitance  $C_{12}$  differ, and in fact that  $(C_{22}-C_{12})<0$ , whereas earlier theories and intuition indicate that  $(C_{22}-C_{12})=0$ . Measurements on a

wide variety of FET's substantiate these theoretical results. The frequency limitations of the equivalent circuit and, indeed, of all the results obtained are shown to arise from the breakdown of the gradual approximation.

# TABLE OF CONTENTS

| CHAPTER I    | INTRODUCTION                                                 | 1                    |

|--------------|--------------------------------------------------------------|----------------------|

| CHAPTER II   | ANALYSIS OF A STEP-JUNCTION FIELD-EFFECT TRANSISTOR          | 3                    |

| 2.1.         | Model                                                        | ٤                    |

|              | Assumptions                                                  | 11                   |

|              | D-C and A-C Analysis Below Pinch-Off                         | 13                   |

|              |                                                              | 1                    |

|              | .3.1. D-C Analysis: Drain Current and Channel Curves         | 14                   |

| 2            | -3.2. A-C Analysis: Small-Signal Equivalent Circuit          | 21                   |

| 2.4.         | Extension of Results Beyond Pinch-Off                        | 32                   |

|              | .4.1. Drain Current                                          | 34                   |

| 2            | .4.2. Small-Signal Equivalent Circuit                        | 37                   |

| 2.5.         | Conclusions                                                  | 43                   |

| CHAPTER III  | VALIDITY OF THE ASSUMPTIONS USED IN THE                      |                      |

|              | STEP-JUNCTION ANALYSIS                                       | 14.14                |

| 3.1.         | Deviations from Idealized Geometry                           | 45                   |

| _            | The Built-In Potential                                       | 14.9                 |

|              | Non-Constant Mobility                                        | 51                   |

|              | Validity of the Gradual Approximation                        | 45<br>49<br>51<br>57 |

|              |                                                              |                      |

| 3.6.         | Conclusions                                                  | 71                   |

| CHAPIFR IV   | ANALYSIS OF AN ARBITRARILY DOPED FIELD-<br>EFFECT TRANSISTOR | 73                   |

| 1 -          |                                                              | 13                   |

| 4.1.         | A Simple, Approximate Derivation of FET                      | 1                    |

| 4.2.         | Characteristics                                              | '74                  |

|              | General Treatment Applications of the General Treatment      | 77                   |

|              | Conclusions of the General Treatment                         | 91                   |

| T•T•         | CONCIUSIONS                                                  | 102                  |

| CHAPTER V    | BOUNDS ON THE PARAMETERS OF AN ARBITRARILY                   |                      |

|              | DOPED FIELD-EFFECT TRANSISTOR                                | 104                  |

| 5.1.         | Preliminary Derivations                                      | 105                  |

| 5.2.         | Transconductance                                             | 112                  |

| 5•3•         | Drain Current                                                | 114                  |

| 5.4.         | input Charge-Capacitance                                     | 120                  |

| 5.5.         | Figures of Merit                                             | 120                  |

| 5.6.         | Temperature Compensation                                     | 132                  |

| 5.7.<br>5.8. | Power-Law Nature of the Transfer Characteristics Conclusions | 140                  |

| ノ***         | CONCERNING                                                   | 147                  |

| CHAPTER VI                | COMPLETE FIRST-ORDER EQUIVALENT CIRCUIT OF AN ARBITRARILY DOPED FIELD-EFFECT TRANSISTOR                                                       | 149                      |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| 5.1.                      | Differential Equation for the Channel Potential, Including the Effects of Gate-Channel Current                                                | 150                      |

| 6.2.                      | Approximate Solution for the Drain and Gate Currents                                                                                          | ·                        |

| 6.3.                      | Equivalent Circuit Below Pinch-Off;                                                                                                           | 154                      |

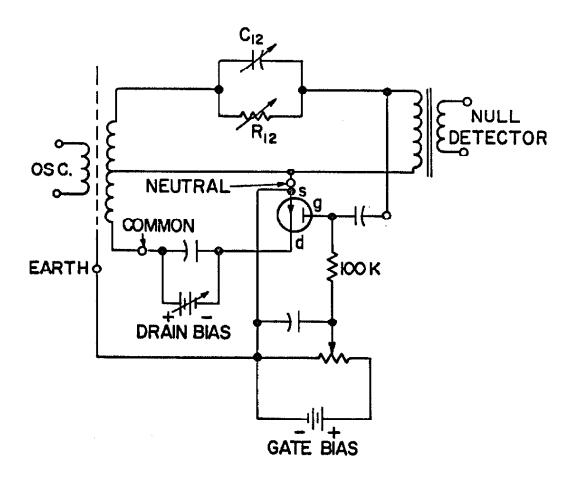

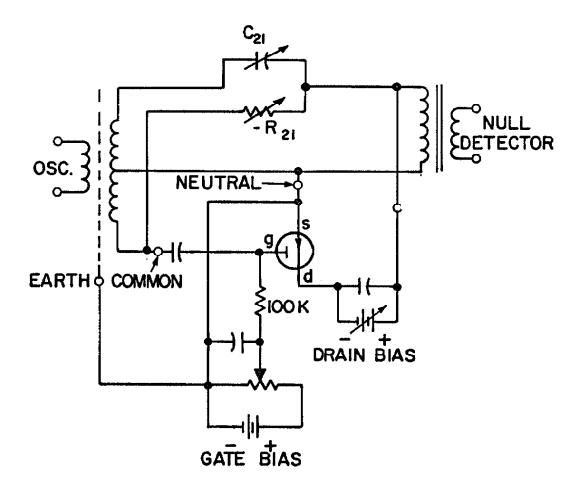

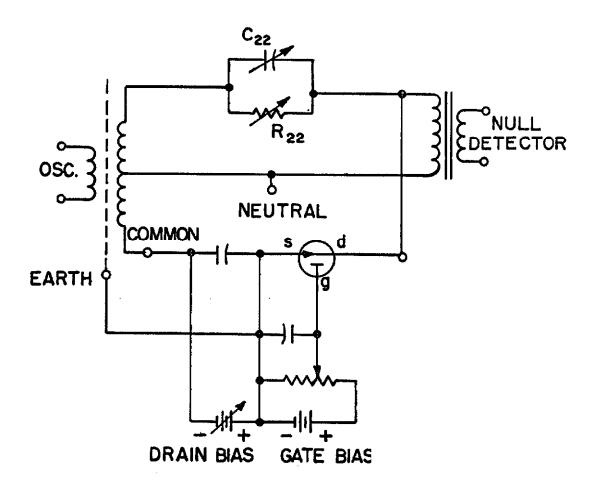

| 6.4.                      | Experimental Verification of (C <sub>22</sub> - C <sub>12</sub> ) as a "New" Circuit Element Equivalent Circuit Beyond Pinch-Off;             | 160                      |

| 6.6.                      | Experimental Verification of C <sub>2l</sub> as a "New" Circuit Element Validity of Results Some Further Practical Considerations Conclusions | 173<br>178<br>185<br>190 |

| CHAPTER VII               | CONCLUSIONS                                                                                                                                   | 192                      |

| APPENDIX A                | BOUNDS IN THE NORMALIZED INPUT CHARGE-<br>CAPACITANCE                                                                                         | 197                      |

| APPENDIX B                | EXPERIMENTAL SETUPS                                                                                                                           | 198                      |

| LIST OF PRINCIPAL SYMBOLS |                                                                                                                                               | 4CS                      |

| REFERENCES                |                                                                                                                                               | 207                      |

#### CHAPTER I

### INTRODUCTION

The fundamental principle underlying the operation of fieldeffect devices, namely, the modulation of the current flow between two

electrodes by the application of an electric field, was conceived as

early as 1928 [1]. Since then, and especially in recent years, these

semiconductor devices have aroused much interest because of their

singular properties and diverse potentialities. In this work we shall

restrict our attention to field-effect transistors (FET's), which are

three-terminal structures whose external characteristics are similar

to those of vacuum pentodes, and which therefore complement in some

aspects the characteristics of "conventional" transistors.

In 1948 Shockley and Pearson [2] built a prototype FET by using a thin layer of semiconductor as one plate of a parallel-plate capacitor. A potential applied to the other (metal) plate controlled the longitudinal conductivity of the semiconductor by inducing charges in it. The degree of control was much less than that predicted theoretically, the difference being attributed to the presence of surface states [3] which immobilized many of the induced charges. In the first practical FET's, deleterious surface effects were avoided because the free surface was replaced by a p-r junction. More recently, insulated-gate FET's (thin-film devices equivalent to Shockley's

<sup>\*</sup> These FET's are sometimes referred to as metal-oxide-semiconductor (MOS) transistors or simply as thin-film transistors (TFT's).

prototype) have been fabricated. At present, however, most commercially manufactured FET's contain p-n junctions because some surface problems are still extant in the insulated-gate types.

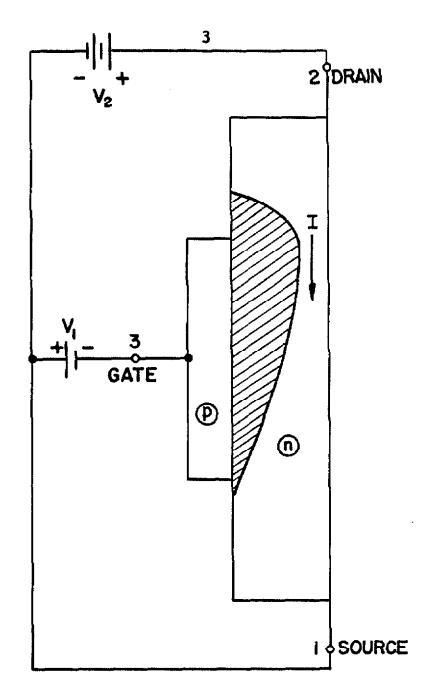

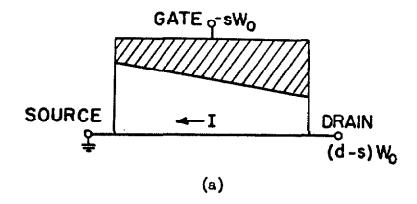

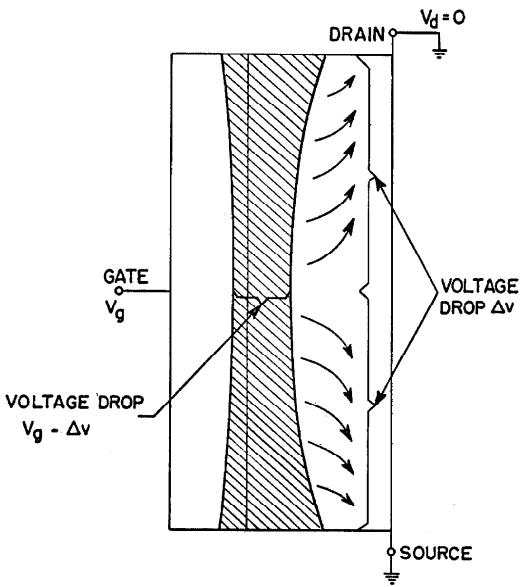

The essential features of FET operation may be apprehended from the representative model of Fig. 1.1, in which a two-dimensional. planar device with a high-conductivity p-region is shown. If the p-n junction is reverse-biased by a voltage  $V_{\gamma}$  between terminals l and 3, the resulting space-charge (or charge-depletion) region penetrates preferentially into the lower conductivity n-region. When a longitudinal field is applied by means of a voltage  $V_2$  between terminals 1 and 2, a current flows through the channel - the undepleted portion of the n-region. The current carriers flow into the channel from terminal 1, which is therefore called the source. carriers flow out of the channel at terminal 2, the drain. Terminal 3 is the control electrode and is called the gate. Now, because of the potential drop in the direction of current flow, the space-charge region does not have uniform width, but has the general shape shown. There are effectively no free carriers in the space-charge region, so that the (static) drain-source conductance is determined wholly by the shape of the neutral channel and, consequently, depends upon the gate-source bias  $V_1$ . Therefore, the potential applied to the gate modulates the current flow between the drain and the source.

The presence of an insulating layer between the gate and the channel in insulated-gate FET's permits the biasing of these devices with gate-source voltages of either polarity. However, in this

Fig. 1.1. Representative model of FET. Shaded area denotes space-charge region. The arrow indicates the direction of conventional current flow; current carriers (electrons, in this case) always flow from source to drain.

report we shall consider only the mode of operation corresponding to charge depletion within the channel. Thus, the FET's we shall investigate possess a current flow that is controlled by conductance modulation (via alteration of the shape of a conducting path), rather than by conductivity modulation.

The drain characteristics of an FET are similar to the plate characteristics of a vacuum pentode (cf. Fig. 2.7). For a given gate voltage the drain current at first increases with the drain voltage, and then, in the so-called pinch-off range, the drain current is practically independent of the drain voltage. The finite incremental output conductance that is present in the pinch-off range in an actual FET is small and is neglected in this work. Also, the gate-channel junction behaves like a reverse-biased diode, so that the input conductance is extremely small and is also neglected.

An important feature of FET's is that they are unipolar, i.e. only one type of carrier, the majority carrier, is involved in the dominant current flow mechanisms. This is in marked contrast to conventional transistors, in which both minority and majority carriers are essential to the total current flow in normal operation. The unipolar nature of the FET endows this device with several desirable properties. Most important, the current carriers travel by drift only. Hence, good frequency response, and, in particular, better frequency response than that of conventional transistors is expected. (Also, there will be no effect analogous to the minority carrier storage of the ordinary transistor.) Since recombination is not an important factor, technologically inferior materials can be

tolerated in the structure of an FET.

Although FET's have been commercially available for only a few years, many companies now produce these devices. The essential differences between various FET's are in the type of gate-channel junction, i.e. in the doping profile (impurity distribution), and in the geometry. It is easy to show that most FET geometries (excluding cylindrical) can be reduced with excellent accuracy to a single, simple, ideal structure (cf. Section 3.1). In other words, geometrical variations affect only the magnitudes of FET parameters, not their functional behavior. Doping-profile variations, however, are of a more fundamental nature. Moreover, existing profiles are almost as numerous and disparate as the manufacturing companies themselves: Some FET's contain alloy junctions; some are epitaxially grown; some contain a single diffused junction; others are double-diffused; and some contain an insulated gate. Yet, despite these very basic internal differences, the external properties of the FET's are strikingly similar. For example, particular transistors from different manufacturers may have output currents that differ by orders of magnitude at the same normalized gate bias; however, if the currents are normalized to their respective maximum values, then at any normalized gate bias these normalized currents can be so close as to be experimentally indistinguishable. The empirical results thus belie intuition: variations in the doping profile have in fact only a slight effect on the functional behavior of FET parameters.

In this work we shall attempt to establish a theoretical basis for the empirical observation that diverse types of FET's behave similarly. The problem is dealt with in Chapters II through V. The first two of these chapters provide background material. Chapter II consists in large part of a rederivation of familiar results for a step- or abrupt-junction FET; Chapter III comprises an evaluation of the approximations used in the step-junction analysis. Before the desired goal can be approached, the equations describing the operation of an FET must be written in a general form, in terms of an arbitrary doping profile. This is done in Chapter IV. Then, in Chapter V it is proved that most FET's do indeed have very similar characteristics. This result justifies certain simple approximations to the equations describing the operation of FET's, and, equally important, allows us to appreciate the range of validity of these approximations.

As another major problem in this work we investigate the equivalent circuit for an FET. Heretofore, equivalent circuits were generally semi-empirical, and if the capacitive elements were treated theoretically, they were defined in terms of voltage rates of change of the charge in transit. In Chapter VI we derive, for an arbitrary FET, the actual equivalent circuit, i.e. with capacitive as well as conductive elements expressed as ratios of a-c components of current and voltage. Two previously unpredicted capacitive elements are included in the complete circuit, and the presence of these elements

is confirmed by measurements on a wide variety of FET's. Finally, by revealing a shortcoming in one of the key approximations that is almost universally employed, the treatment of Chapter VI points out the frequency limitations of the results obtained from this and many other analyses.

#### CHAPTER II

## ANALYSIS OF A STEP-JUNCTION FIELD-EFFECT TRANSISTOR

In this chapter we shall analyze the step-junction FET in some detail, because the physical insight gained from the solution of this specific doping profile will be helpful when we consider the general profile in Chapter IV. In fact, most of the conclusions regarding the operation of a step-junction FET may be directly applied - in a qualitative manner - to an arbitrarily doped FET.

We begin in the first two sections by setting up a general model and summarizing the assumptions to be applied to this model. Then, in the remaining sections, we restrict our attention to the step-junction device and derive and interpret the equations describing its operation.

## 2.1 Model

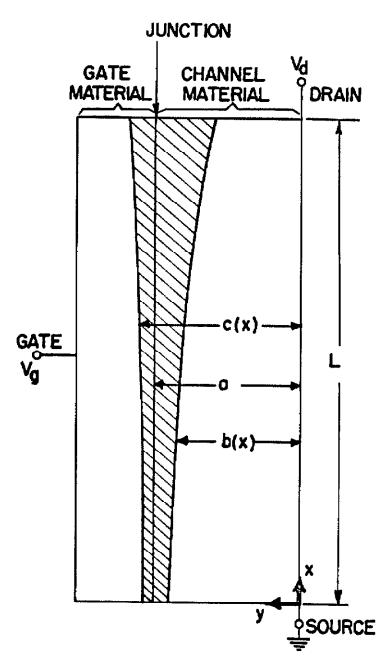

Figure 2.1 shows the model we shall use for the FET throughout this report. As mentioned in Chapter I, the principle of operation of an FET is that the potential applied to one electrode - the gate - controls the current flowing between two other electrodes - the source and the drain - by altering the shape of a space-charge or depletion region. The potential of the gate (with respect to circuit ground) is denoted by  $V_{\rm g}$ . The source and the drain are separated by the distance L; the source is grounded, and the drain is biased at

Fig. 2.1. Model of FET used in the analysis.

The device has depth A perpendicular to the x-y plane. Shaded area denotes space-charge region.

${

m V_d}^*$ . The subscript s, d, or g on any quantity indicates that the quantity pertains to the source, drain, or gate, respectively. The origin of the coordinate system is at the source electrode, with x measured in the direction of the drain and y measured in the direction of the gate. Our model is two-dimensional: we assume a uniform depth A perpendicular to the x-y plane.

The applied potentials set up a space-charge region of width (c-b). Of course, (c-b) is a function of the bias voltages, and, in general, is also a function of x. We assume that there are no free carriers in the depletion region, so that current flows between the source and drain only within the charge-neutral channel; the width of the channel is denoted by b(x).

The excess density of donors over acceptors, <u>multiplied by the magnitude of the electronic charge</u>, is called the doping or impurity density (or profile) and is denoted by  $\rho$ . Practical devices have one-dimensional doping profiles, so that  $\rho = \rho(y)$ . In n-type semiconductor  $\rho > 0$ , while in p-type  $\rho < 0$ . (The sign of  $\rho$  is the same as the sign of the charges in the depletion region.) The gate material and the channel material are separated by a junction at y = a. That is, c(a) = 0. We assume that all impurities are ionized at normal operating temperatures. Then the mobile charge density, denoted by  $\rho_m$ , is equal to  $-\rho$  in the charge-neutral channel.

<sup>\*</sup> Our model is symmetrical and hence is unaffected by an interchange of source and drain. Actual devices may have some non-symmetries, so that an interchange of source and drain will modify the numerical values of device parameters.

## 2.2. Assumptions

In this section we list carefully the assumptions and approximations used in the subsequent analysis. The validity of these assumptions is discussed fully in the next chapter. The following list is very roughly in order of decreasing validity. The first two hypotheses will be entirely removed in subsequent chapters; the next two are generally well justified; the last three require some analysis for their justification.

Our first assumption arises because at present we are considering a step-junction FET.

(1) The doping profile is given by

$$\rho(y) = \begin{cases} +\rho_{C}, & 0 \le y < a \\ -\beta\rho_{O}, & a < y \end{cases}$$

(2.1)

where  $\rho_{\rm O}$  and  $\beta$  are positive constants. We have chosen an n-channel device. For simplicity, we assume that  $\beta \gg 1$ , so that the conductivity of the gate material is much greater than that of the channel material. When the p-n junction is reverse biased, essentially all of the space-charge region appears in the channel material, and

$$c(x) = a = constant$$

(2.2)

(2) The built-in potential is negligible compared with the gate-channel potential. The difference between the Fermi levels of the p- and n-regions produces a contact or built-in potential across

the gate-channel junction. For silicon, this potential is of the order of 0.5v.

- (3) The drain current is carried only by majority carriers (electrons, for the doping profile given in Eq. 2.1).

- (4) Direct gate current is negligible. This current, which consists of the normal saturation current of a reverse-biased junction and possibly of recombination-generation current produced in the space-charge region, is small in comparison with the drain current.

- (5) The carrier mobility is constant.

- (6) The boundary between the depletion region and the channel is sharp. This assumption enables us to define accurately the channel, and to assert that the drain current flows entirely within this channel (since in this case  $\rho_m = 0$  in the depletion region).

The foregoing assumptions are not uncommon in the consideration of many devices involving p-n junctions. The following two approximations, however, are peculiar to FET's and are necessary for an analytically simple solution.

(7) (a) In the channel the magnitude of the y-component of the electric field E is much smaller than the magnitude of the x-component:

$$|E_y| \ll |E_X|$$

,  $0 \le y \le b$  (2.3)

(b) If  $\epsilon$  is the permittivity of the semiconductor material, then in the space-charge region

$$\left|\frac{\partial \Xi_{\mathbf{X}}}{\partial \mathbf{X}}\right| \ll \left|\frac{\rho}{\epsilon}\right| , \qquad \mathbf{b} \leq \mathbf{y} \leq \mathbf{c} \qquad (2.4)$$

Assumption (7) constitutes the "gradual approximation" [4] since it implies that the channel width does not change rapidly. The motivation for this assumption arises when an FET is analyzed with  $V_{\dot{q}}\approx 0$ . In this case  $b(x)\approx constant$ , and the gradual approximation is well justified because the channel field is essentially one-dimensional in the x-direction, while the field in the space-charge region is almost wholly in the y-direction. In order to maintain a one-dimensional problem, the gradual approximation is applied even when  $V_{\dot{q}}$  is not small.

In Section 2.4, one additional assumption will be made. It is not included here because some preliminary analysis is necessary before it can be properly understood.

## 2.3. D-C and A-C Analysis Below Pinch-Off

Now that the model has been explained and the assumptions set down, we are ready to derive the equations governing the operation of the step-junction FET. The principal results of the d-c solution are the expressions for the drain current and for the channel boundary; the a-c solution yields the small-signal equivalent circuit. Except for the capacitances, the formulae obtained in this section are given by Shockley [4], so that most of the actual analysis performed

here will be brief.

## 2.3.1. D-C Analysis: Drain Current and Channel Curves

Doth the space-charge region and the channel for two relations between the channel width and the potential along the channel boundary, and then matching the two relations to obtain a consistent result. Actually, we proceed by immediately incorporating the space-charge-region result into the equations describing the channel. Then the solution of the latter equations yields the quantities of interest directly.

Let V(x,y) be the potential at the point (x,y). In the space-charge region, V obeys Poisson's equation. Because of the gradual approximation - in particular, Eq. 2.4 - we have

$$\frac{\partial^2 v}{\partial x^2} = -\frac{\rho(y)}{\epsilon}, \qquad b(x) \le y \le c(x) \qquad (2.5)$$

At the channel edge of the depletion region the electric field is zero [because of assumption (6)],

$$E_{y} = -\frac{\partial V}{\partial y} = 0 \qquad \text{at} \qquad y = b(x) \qquad (2.6)$$

and the potential along the gate edge of the depletion region is  $v_{\rm g}$ ,

$$V[x,c(x)] = V_g$$

(2.7)

Equations 2.6 and 2.7 are the boundary conditions on 2.5. Using the step-junction profile Eq. 2.1 defined in the previous section, we easily integrate 2.5 to get for the potential in the space-charge region

$$V(x,y) = V_g + \frac{2}{2\epsilon} [(a - b)^2 - (y - b)^2], \quad b(x) \le y \le a$$

(2.8)

since c(x) = a because of the high conductivity of the gate material. Again because of the gradual approximation - this time Eq. 2.3 - the current from the drain to the source flows parallel to the x-axis, and hence the potential at any point (x,y) within the channel is equal to the potential at the point [x,b(x)]:

$$V(x,h) = V_g + \frac{\rho_0}{2\epsilon} [a - h(x)]^2$$

$$= V_g + V_0 \left[ 1 - \frac{h(x)}{a} \right]^2, \qquad 0 \le y \le h(x) \quad (2.9)$$

where

$$W_{o} = \frac{\rho_{o}a^{2}}{2\epsilon} \tag{2.10}$$

From Eq. 2.9 we see that if  $V - V_g = W_0$ , then b(x) = 0. That is,  $W_0$  is the magnitude of the reverse bias on the gate-channel function which causes the channel width to become zero; or, more descriptively, the potential  $W_0$  causes the channel to become "pinched-off." For

this reason, Wo is referred to as the pinch-off voltage.

In order to simplify many of the formulae that we shall derive, we define several normalized parameters:

$$u(x) \equiv \frac{b(x)}{a}$$

: the fractional width of the channel material occupied by the channel (2.11)

$$s = \frac{|v_g|}{w_o}$$

: the magnitude of the ratio of the source-gate potential to the pinch-off voltage (2.12)

$$d = \frac{|v_g - v_d|}{|v_o|} : \text{ the magnitude of the ratio of the drain}_{\overline{*}}$$

gate potential to the pinch-off voltage (2.13)

Thus, s and d are normalized potentials that are measured with respect to the gate; below pinch-off their values lie in the range  $0 \le s, d \le 1$ . With this notation Eq. 2.9 becomes

$$\frac{V(x,b)}{W_0} = -s + (1 - u)^2$$

(2.14)

<sup>\*</sup> The built-in potential is included in the more accurate definitions of s and a given in Eqs. 3.6 and 3.7.

because  $V_{\rm g}<0$  in an n-channel device. This equation, and most of the equations that follow, is valid for both n- and p-channel FET's if the appropriate sign of V is used.

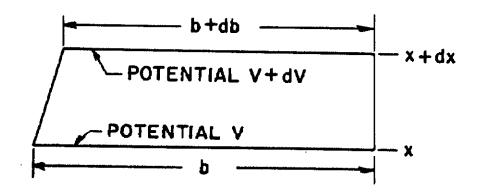

Consider now the differential element of channel pictured in Fig. 2.2. The resistance between the x- and (x+dx)-planes is

$$dR = \frac{dx}{\mu \rho_0 bA} = \frac{1}{\mu \rho_0 aA} \frac{dx}{u}$$

where  $\mu$  is the mobility of majority carriers in the channel. The voltage drop across the element is -dV, which, by 2.14 may be expressed as

$$-dV = 2W_o(1 - u) du$$

Hence, the magnitude of the current flowing through any section of channel is (since du/dx < 0)

$$I = \frac{dV}{dR} = -2G_oLW_ou(1 - u)\frac{du}{dx}$$

(2.15)

in Which

$$G_{o} = \frac{\mu \rho_{o} a \Lambda}{L} \tag{2.16}$$

is the conductance of the channel in the absence of biases.

Fig. 2.2. Differential element of channel.

Because no current flows through the space-charge region, I is not a function of x, and Eq. 2.15 may easily be integrated. Also, the drain current and the source current are identical and may be unambiguously identified by the same symbol I. For convenience in later discussions we shall always consider the drain current to be a positive quantity even though I may flow into or out of the drain, depending on whether the channel is n- or p-type, respectively. From Eq. 2.14 we see that

$$u(0) = 1 - \sqrt{s + \frac{V(0,5)}{W_0}} = 1 - \sqrt{s}$$

$$u(L) = 1 - \sqrt{s + \frac{V(L, b)}{W_o}} = 1 - \sqrt{\frac{V_d - V_g}{W_o}} = 1 - \sqrt{d}$$

so that integration of 2.15 over the whole channel length yields

$$I \int_{0}^{L} dx = -2G_{0}LW_{0} \int_{1-\sqrt{s}}^{1-\sqrt{d}} u(1-u) du$$

OΓ

$$I(s,\bar{a}) = I_0 \left[ (1 - \sqrt{s})^2 (1 + 2\sqrt{s}) - (1 - \sqrt{\bar{a}})^2 (1 + 2\sqrt{\bar{a}}) \right]$$

(2.17)

The multiplicative factor  $I_o$  in this equation is given by

$$I_{o} = I(0,1)$$

(2.18)

$$=\frac{G_0 W_0}{3} \tag{2.19}$$

and is, as we shall show in Section 2.4, the maximum drain current that flows through the device without forward bias on the gate-channel junction. If the potential  $W_{\rm O}$  were applied across a par of material of conductance  $G_{\rm O}$ , a current  $I = G_{\rm O}W_{\rm O}$  would flow. With  $W_{\rm O}$  applied across the length of the channel of an FET, the current is some factor less than  $G_{\rm O}W_{\rm O}$  because of the presence of the depletion region. For a step junction FET (with  $V_{\rm g}=0$ ) we see from Eq. 2.19 that this reduction factor is 3.

Consistent with the assumptions made in Section 2.2, Eq. 2.17 for the drain current is valid for voltages up to pinch-off, but not beyond; i.e. for  $s < d \le l$ , where the first inequality arises because the drain-gate potential must always be greater in magnitude than the source-gate potential under normal bias conditions (current flowing into the drain in an n-channel device). We defer discussion of Eq. 2.17 until we extend it to voltages d > l in Section 2.4.

We now derive the equation for the channel shape by integrating Eq. 2.15 over only part of the channel length, from x=0,  $u=u(0)=(1-\sqrt{s})$  to the arbitrary channel boundary point (x,u):

$$I_{\frac{X}{L}} = I_0 \left[ (1 - \sqrt{\epsilon})^2 (1 + 2\sqrt{\epsilon}) - u^2 (3 - 2u) \right]$$

The current I may be climinated by use of 2.17 to give x as a function of u with s and d as the only parameters:

$$\frac{x}{L} = \frac{(1 - u)^{2}(1 + 2u) - s(3 - 2\sqrt{s})}{d(3 - 2\sqrt{d}) - s(3 - 2\sqrt{s})}$$

(2.20)

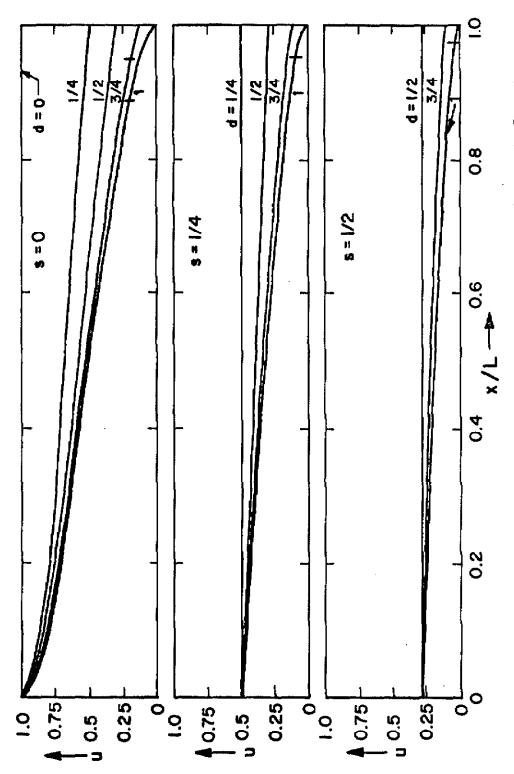

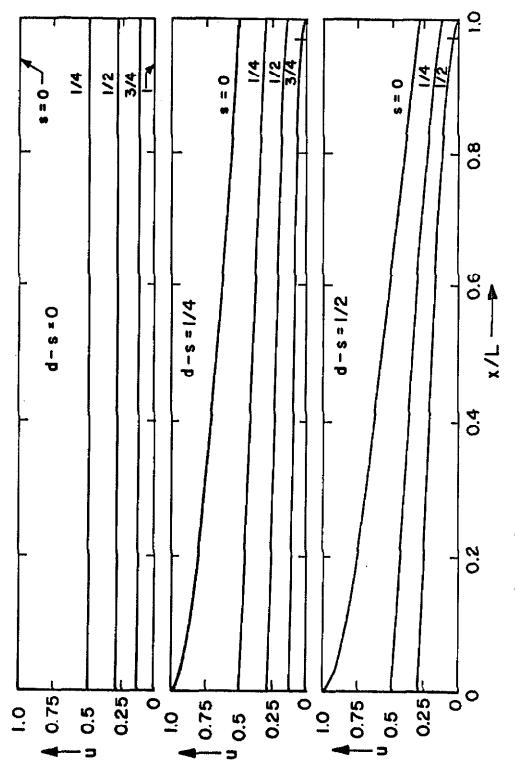

The curves drawn in Fig. 2.3 show u versus x/L with s (or  $V_g$ ) fixed and d (or  $V_d$ ) as a parameter, and with d - s (or  $V_d$ ) fixed and s (or  $V_g$ ) as a parameter. The vertical marks on some channel curves indicate, for the particular case L/a=10, the maximum values of x/L for which the gradual approximation is valid. These maximum values are based on the analysis of Section 3.4. Curves with no marks are valid for their entire length. These curves should be studied carefully, because a clear understanding of how the channel shape is altered as the biases are changed gives much insight into the characteristics of the FET.

## 2.3.2. A-C Analysis: Small-Signal Equivalent Circuit

We are now able to determine the small-signal, short-circuit admittance parameters. From Eq. 2.17 we easily obtain the (forward) transconductance and the output conductance below pinch-off. Since both s and d depend on  $V_{\rm g}$ , the transconductance  $g_{\rm m}$ , defined by

$$g_{m} = \left| \frac{\partial I}{\partial V_{g}} \right| \tag{2.21}$$

is

$$g_{m} = G_{O}(\sqrt{d} - \sqrt{s})$$

(2.22)

which is the same as the conductance of a channel of constant frac-

on some curves denote, for the particular case L/a=10, the maximum values of x/L that are consistent with the gradual Channel curves for the step-junction FET. The vertical marks approximation. Curves with no marks are accurate for their entire length. Hg. 2.3.

Channel curves with s as the running parameter. Fig. 2.3 (cont'd).

tional width u(0) - u(L). For d = s,  $g_m = 0$ . This is logical because for these biases the channel is uniform and no current flows, and a charge in the gate voltage cannot alter these conditions. The output conductance is defined by

$$G_{22} = \left| \frac{\partial I}{\partial V_{d}} \right| \tag{2.23}$$

and has the value

$$G_{22} = G_0(1 - \sqrt{a})$$

(2.24)

. We note that  $G_{22}$  is equal to the conductance of a channel of constant fractional width u(L); i.e.  $G_{22}$  depends only on the draingate potential and goes to zero when that potential equals  $W_0$ .

The remaining elements in the equivalent circuit are capacitive. We define the short-circuit input "charge-capacitance"  $C_{11}^*$  and output "charge-capacitance"  $C_{22}^*$  in terms of the voltage rate of change of the charge Q in transit between the source and the drain\*:

<sup>\*</sup> More precisely,  $c_{\rm ll}^* = {\rm dq_{in}/dV_g}$  where  ${\rm q_{in}}$  is the charge placed on the gate. But for every element of input charge  ${\rm q_{in}}$ , an equal amount of charge goes into the space-charge region from the channel. Hence,  ${\rm dq_{in}/dQ} = -1$ , and Eq. 2.25 is valid.

$$C_{11}^{*} = \begin{vmatrix} \frac{\partial Q}{\partial V_{g}} \end{vmatrix}$$

(2.25)

$$C_{22}^* = \begin{vmatrix} \frac{\partial Q}{\partial V_{\tilde{G}}} \end{vmatrix}$$

(2.26)

These quantities may differ from the "real" short-circuit input and output capacitances  ${\rm C}_{11}$  and  ${\rm C}_{22}$ , which are defined by

$$c_{11} = \frac{1}{\omega} \frac{1}{v_g}$$

[quadrature component of  $i_{g^*v_g=0}$  (2.27)

$$C_{22} = \frac{1}{\omega} \frac{1}{v_d}$$

[quadrature component of  $i_d$ ]  $v_g = 0$  (2.28)

where  $\omega$  is the radian frequency and v and i respectively denote the a-c components of voltage and current. The capacitances denoted by C are the real circuit parameters since they are the values that would be measured experimentally at the device terminals. The charge-capacitances  $C^*$  are useful quantities, however, because we shall see in Chapter VI that they do appear in the "real" equivalent circuit. In fact,  $C^*_{11}$  is identical to  $C_{11}$ , and  $C^*_{22}$  is the fraction of  $C_{22}$  that appears between the gate and the drain. Since the method of computation implied by Eqs. 2.25 and 2.26 is significantly easier than that implied by 2.27 and 2.28, and since the former approach is easier to visualize physically, we shall continue the analysis by calculating  $C^*_{11}$  and  $C^*_{22}$  and discussing them in some detail.

For a uniformly doped channel, Q is simply proportional to the channel area. Thus, since  $u(0) \ge u(L)$ ,

$$\mathcal{L} = \rho_0 \text{ aAL} \left[ u(L) + \int_{u(L)}^{u(0)} \left( \frac{x}{L} \right) du \right]$$

A straightforward calculation using 2.20 gives

$$Q = \frac{\rho_0 \epsilon_{AL}}{2} \left[ 1 + 3 \frac{d(1 - \sqrt{d})^2 - s(1 - \sqrt{s})^2}{d(3 - 2\sqrt{d}) - s(3 - 2\sqrt{s})} \right]$$

(2.29)

and application of Eqs. 2.25 and 2.26 yields

$$c_{11}^{*} = c_{0}^{*}(\sqrt{a} + \sqrt{s}) \frac{(1 - \sqrt{d})^{2} + 4(1 - \sqrt{d})(1 - \sqrt{s}) + (1 - \sqrt{s})^{2}}{[3(\sqrt{a} + \sqrt{s}) - 2(a + \sqrt{ds} + s)]^{2}}$$

(2.30)

$$C_{22}^* = C_0^* (\sqrt{d} + \sqrt{s}) \frac{(1 - \sqrt{d})^2 + 2(1 - \sqrt{d})(1 - \sqrt{s})}{[3(\sqrt{d} + \sqrt{s}) - 2(d + \sqrt{ds} + s)]^2} +$$

$$+ C_{o}^{*}(\sqrt{d} - \sqrt{s}) \frac{(1 - \sqrt{d})(1 - \sqrt{s})}{[3(\sqrt{d} + \sqrt{s}) - 2(d + \sqrt{ds} + s)]^{2}}$$

(2.31)

where we have defined

$$c_{o}^{*} = c_{11}^{*}(0,1)$$

$$= 3\epsilon A \frac{L}{a} \qquad (2.32)$$

These formulae are invalid near s = d = 0 since we have neglected

the built-in potential.

It is appropriate, here, to discuss an error that is committed by several authors [5]. A planar junction of area A dx with a depletion-region thickness (a - b) has a capacitance  $dC = (\epsilon A dx)/(a - b)$ . Thus, we might be tempted to assert that the input capacitance of an FET should be

$$\frac{\epsilon A}{a} \int_{0}^{L} \frac{dx}{1 - u} = C_{0}^{*} \frac{(1 - \sqrt{d}) + (1 - \sqrt{s})}{3(\sqrt{d} + \sqrt{s}) - 2(d + \sqrt{ds} + s)}$$

where dx was calculated from 2.20. This expression differs from the previous expression 2.30 for the input charge-capacitance. The misunderstanding is that by integrating, we have tacitly assumed that the differential, parallel-plate capacitors are all connected in parallel. This is not true. The capacitors do have one common terminal (the gate), but the current flowing through the resistance of the channel results in the other terminals having a difference of potential.

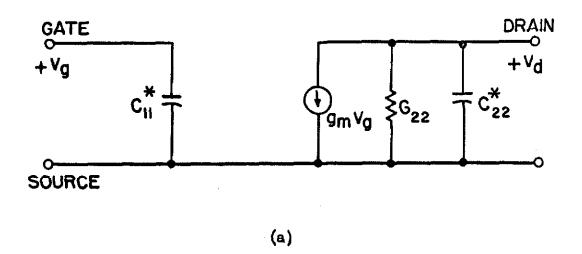

In Fig. 2.4a we show the equivalent circuit whose element values are computed in Eqs. 2.22, 2.24, 2.30, and 2.31. These elements, by definition, are short-circuit quantities, so that part of them may appear between the gate and the drain. Actually, the geometry of the FET suggests that  $C_{22}^*$  should appear entirely between the gate and the drain, for both  $C_{11}^*$  and  $C_{22}^*$  arise only from the field in the

<sup>\*</sup> This statement is true except when s = d. In this case we expect the above formula to be correct, and indeed, it is.

Fig. 2.4. Small-signal equivalent circuits for the step-junction FET: (a) General circuit; (b) Modified circuit suggested by arguments in the text.

space-charge region. But all the field lines in the space-charge region emanate from the gate; i.e. none of these field lines exist between the source and the drain. Therefore, no capacitance should appear between the source and the drain.

This intuitive conclusion is supported by two theoretical arguments. First consider the case when s=d  $(V_d=0)$ . Then the channel is of uniform width  $b=a(1-\sqrt{s})$ , and the input charge-capacitance from Eq. 2.30 is

$$C_{11}^* = \frac{\varepsilon LA}{a\sqrt{s}}$$

, (s = d)

This is merely the capacitance of a reverse-biased, planar p-n junction of area LA with depletion region thickness  $(a\sqrt{s})$ , and is the result expected. But in our model, when  $V_d = 0$ , the source and the drain are indistinguishable, so we must have equal capacitances between each of these electrodes and the gate. If  $C_{dg}^*$  represents the drain-gate charge-capacitance, then the source-gate charge-capacitance is  $C_{sg}^* = (C_{ll}^* - C_{dg}^*)$  and we have

$$(C_{11}^* - C_{dg}^*) = C_{\tilde{\alpha}g}^*, \qquad \text{or} \qquad C_{11}^* = 2C_{dg}^*$$

<sup>\*</sup> Of course, whenever current flows between the source and the drain, there are field lines between these two terminals. These field lines generate the drain-source interelectrode capacitance, which, since it is an extrinsic parameter, is not significant in this discussion.

By Eq. 2.31, when s = d the output charge-capacitance is

$$C_{22}^* = \frac{1}{2} \frac{\epsilon LA}{a\sqrt{s}} = \frac{C_{11}^*}{2} = C_{\bar{\alpha}g}^*$$

indicating that the actual equivalent circuit is that shown in Fig. 2.4b. (Since the input resistance is infinite, there is no ambiguity in the position of  $\mathfrak{G}_{22}$ .)

Now consider the general case. We observe from Eqs. 2.30 and 2.31 that  $\sigma_{11}^{*}$  may be expressed as

$$C_{11}^{*}(s,d) = C_{22}^{*}(s,d) + C_{22}^{*}(d,s)$$

(2.33)

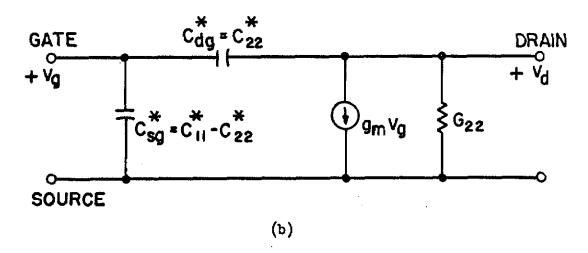

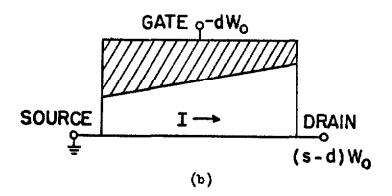

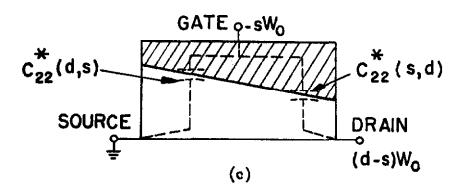

This is an interesting result. An instructive interpretation of this relation may be obtained by reference to Fig. 2.5. In parts (a) and (b) we schematically show two n-channel transistors with biases (a)  $V_g = -sW_0$ ,  $V_d = (d-s)W_0 > 0$ , and (b)  $V_g = -aW_0$ ,  $V_d = (s-d)W_0 < 0$ . Interchanging s and d does not signify interchanging the gate and arain voltages: the drain voltage is given by  $(d-s)W_0$ . Interchanging s and d reverses the orientation of the channel boundary; the channel shape is maintained.\* From Eq. 2.33 we see immediately that the short-circuit input charge-capacitance is the same in case (a) and in case (b). Thus,  $C_{11}^*$  is independent of the direction of current flow, but

<sup>\*</sup> This is obvious since with s and d interchanged the gatesource and the gate-drain potentials are interchanged.

Fig. 2.5. Pertinent to the derivation of the equivalent circuit of Fig. 2.4b. Shaded area denotes space-charge region.

depends somehow upon the overall channel shape. On the other hand,  $C_{22}^*$  depends both upon the direction of current flow and upon the channel shape. Or, equivalently, we may say that  $C_{22}^*$  depends only upon the channel shape "near" the drain. These remarks and the antisymmetry of Figs. 2.3a and 2.5b suggest the interpretation of the input and output charge-capacitances shown in Fig. 2.5c. This particular interpretation satisfies Eq. 2.33 and also predicts correct results under an interchange of s and d. The equality of  $C_{22}^*$  and  $C_{dg}^*$  follows at once from Fig. 2.5c, thereby indicating the general validity of the modified equivalent circuit of Fig. 2.4b.

The description of the step junction FET developed in this section is only partially complete, since we have not yet considered the important pinch-off range of operation. However, all the necessary derivations have been performed because, as we now show, values beyond pinch-off are obtained very simply from values below pinch-off.

#### 2.4. Extension of Results Beyond Pinch-Off

As mentioned earlier, the results of Section 2.3 are valid for potentials satisfying  $s \le \tilde{a} \le 1$ . In order to extend the formulae to

<sup>\*</sup> In normal operation - as in Fig. 2.5a - the channel is narrower near the drain. Capacitance varies inversely with the width of the space-charge region. Therefore, the capacitance associated with the part of the channel near the drain is smaller than the capacitance associated with the part of the channel near the source. These arguments, coupled with the fact that  $C_{22}^*(d,s) \geq C_{22}^*(s,d) \quad \text{(which follows easily from 2.31) justify the above assertion.}$

- d > 1, we make the one further assumption, in addition to the seven listed in Section 2.2. This new assumption is fundamental in all the first-order theory to be developed in this work:

- (8) (a) At pinch-off ( $\hat{a} = 1$ ) all the previously derived results are valid.

- The effect of  $\hat{a}$  for  $\hat{a} > 1$  may be neglected. Crude as this approximation may seem, it does give an accurate representation of the operation of an FET. The drain is at potential  $\mathrm{dW}_{\mathrm{O}}$ with respect to the gate. If we temporarily assert that the channel is pinched-off at any point whose potential is  $W_{c}$  (or greater) with respect to the gate, then, in effect, (b) implies that the finite voltage drop  $(d-1)W_0$  appears across a zero length of space-charge region. Actually, the channel never really pinches-off, because then no drain current would be able to flow through the resulting spacecharge region. This physical fact is allowed for mathematically by a breakdown of the gradual approximation at points in the channel where the potential with respect to the gate is near Wo. Instead of pinching off (u = 0), the channel merely becomes very narrow  $(u \approx 0$ , but u > 0), and the electric field is very high. But a high electric field means that a large voltage drop occurs in a relatively short distance, and the potential  $(d - 1)W_0$  appears across a very small length of channel. The above-mentioned implication of assumption (b) is, therefore, not so farfetched as it seemed at first glance. Furthermore, we should note that (b) follows almost directly from (a). For we see from Eqs. 2.24 and 2.31 that

when d=1,  $G_{22}=0$  and  $C_{22}^*=0$ : the drain-current - drain-voltage curves are horizontal and the incremental equivalent circuit contains no drain-voltage dependent elements. These heuristic arguments are borne out empirically because the characteristics of FET's are practically independent of drain voltage in the pinch-cff range.

#### 2.4.1. Drain Current

Applying assumption (8), we obtain the drain current beyond pinch-off by substituting d = 1 into Eq. 2.17:

$$I(s,d) = I_0(1 - \sqrt{s})^2(1 + 2\sqrt{s})$$

,  $d \ge 1$  (2.34)

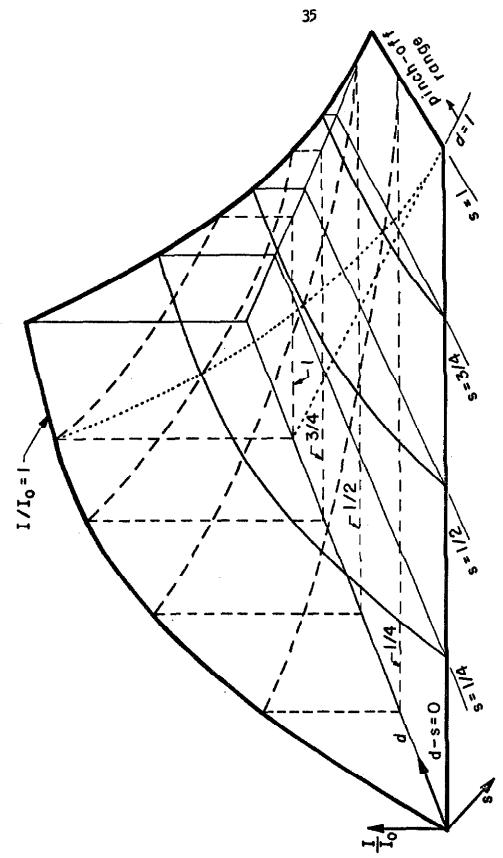

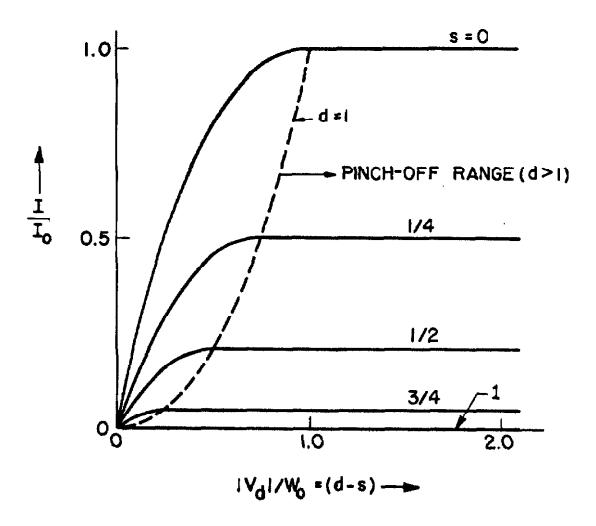

The normalized current obtained from Eqs. 2.17 and 2.34 is plotted as a function of s and d in Fig. 2.6. Because our model is symmetrical, T(s,d) = -I(d,s); that is, the surface of Fig. 2.6, if extended, would be antisymmetric about the line s = d. The dashed curves on the surface represent the drain current for constant (d - s) (i.e. constant  $V_d$ ); along these curves the current decreases as a increases, until at s = 1 the current is zero. The solid curves represent the current for constant s (i.e. constant s). These curves, when drawn from a common origin, are the normalized drain characteristics as shown in Fig. 2.7. The dashed curve in Fig. 2.7 gives the current for s = 1. It separates the pentode-like characteristics into two regions: below pinch-off s = 1. Where the current curves are rising, and beyond pinch-off

Fig. 2.6. Drain current as a function of the source-gate and the drain-gate potentials.

Fig. 2.7. Normalized drain characteristics of a step-junction FET.

(d > 1), where the curves are flat and the current is independent of the drain voltage. (This latter region is sometimes referred to in the literature as the "current-saturation" region.)

# 2.4.2. Small-Signal Equivalent Circuit

The first-order equivalent circuit beyond pinch-off is similarly obtained from the appropriate equations of Section 2.4:

$$g_m = G_0(1 - \sqrt{s})$$

(2.35)

$$c_{11}^* = c_0^* \frac{1 + \sqrt{s}}{(1 + 2\sqrt{s})^2}$$

(2.36)

$$C_{33}^* = G_{33} = 0$$

(2.37)

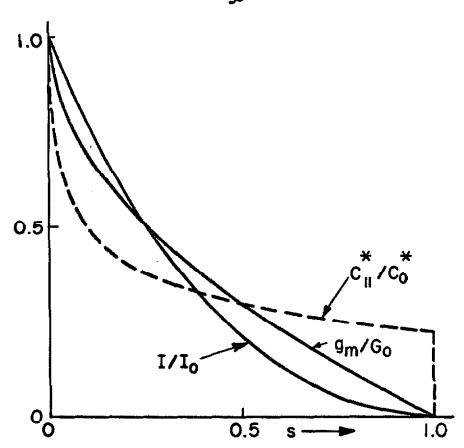

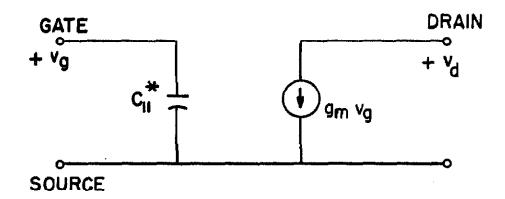

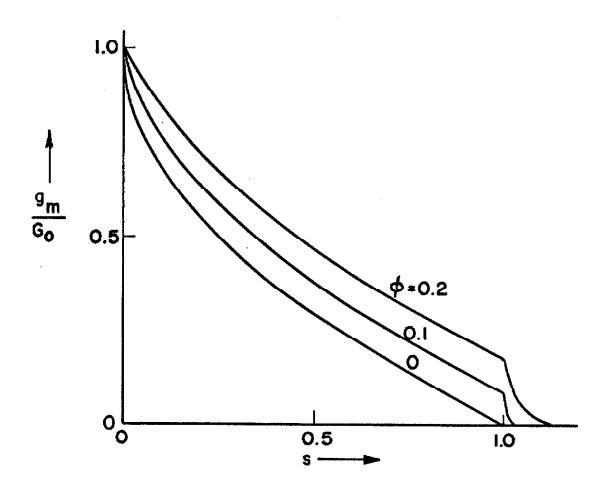

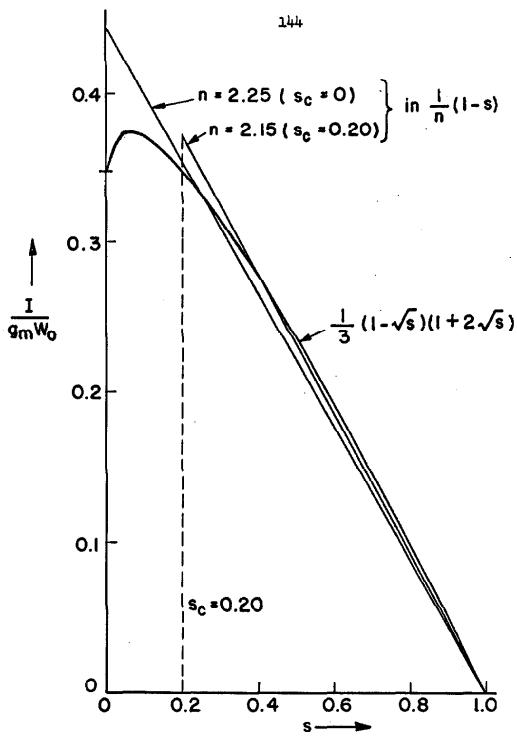

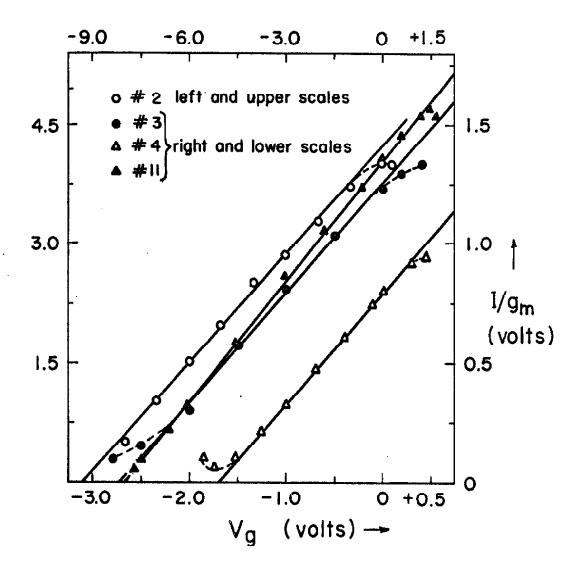

Equations 2.35 and 2.36, along with the transfer characteristics I(s,1), Eq. 2.34, are drawn in Fig. 2.8 with each quantity normalized to its value at s=0. Figure 2.9 shows the equivalent circuit expressed by Eqs. 2.35 - 2.37. It is interesting to note that this circuit contains only those elements which, according to the charge-control approach [6], are essential to the operation of the device.

An error seemingly is apparent in Eq. 2.36, for that equation gives  $C_{11}^* = (2/9)C_0^*$  at s=1, while if we substitute d=s in Eq. 2.30, the original formula for  $C_{11}^*$ , and then let s=1, we arrive at  $C_{11}^* = (1/3)C_0^*$ . Mathematically, this discrepancy arises because the point s=d=1 is a singularity of Eq. 2.30, and hence we may realize different limits upon approaching this point from

Fig. 2.8. Plots of normalized I,  $g_m$ , and  $c_{11}^*$  vs. s in the pinch-off range (d > 1).

Fig. 2.9. Equivalent circuit beyond pinch-off.

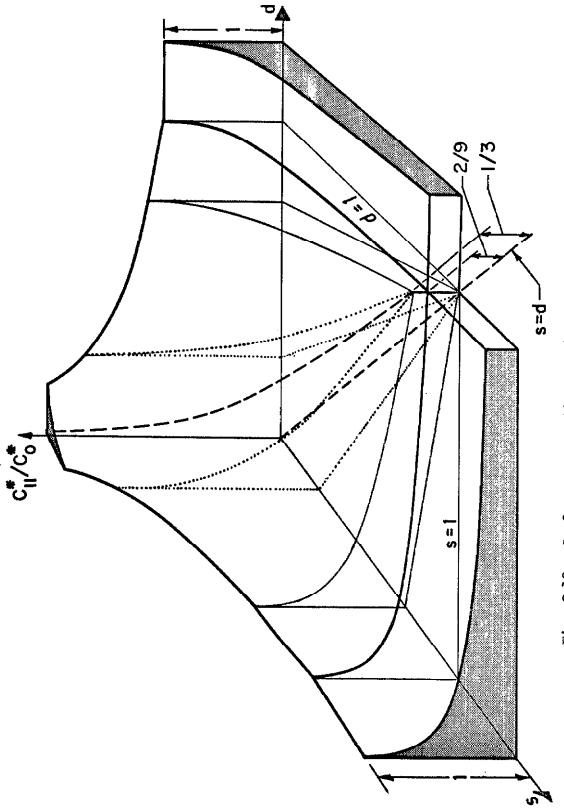

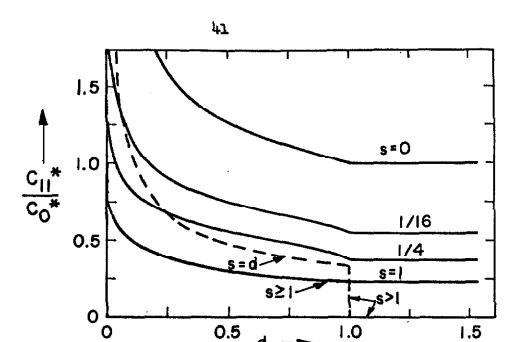

different directions. Physically, we expect unusual behavior because when s = 1 the space-charge region occupies all the channel material. Since no free carriers remain to be incorporated in the depletion region, a further increase in s cannot add any more spacecharge to the channel, and the input capacitance must vanish for s > 1. Both the mathematical and the physical viewpoints may be better comprehended by reference to Fig. 2.10. There we show a drawing of the theoretical surface that represents the input chargecapacitance  $C_{11}^*/C_o^*$  as a function of s and d. Although normal device operation implies  $s \le d$ , the range s > d is included in the diagram for completeness. Our model is symmetrical, so that  $C_{1,1}^{*}(s,d) = C_{1,1}^{*}(d,s);$  i.e. the surface is symmetrical about the line s = d. For s, d < 1,  $C_{11}^*(s, d)$  is given by Eq. 2.30; for  $s \le 1$ ,  $d \ge 1$ ,  $C_{11}^*(s,d) = C_{11}^*(s,l)$ ; for s,d > 1,  $C_{11}^*(s,d) = 0$ . The point s = d = l is a singularity, and, as mentioned above, the value of  $c_{11}^*$  at this point depends upon the direction of approach. The dashed curve in Fig. 2.10 represents the direction s=d, along which  $c_{11}^{\star}$ approaches the value  $(1/3)C_0^*$ ; the curves in the directions d = 1 and s = 1 approach the value  $(2/9)C_0^*$ ; curves in intermediate directions approach intermediate values. Figure 2.11 shows several cross sections of the surface of Fig. 2.10. The solid curves represent cuts by planes parallel to the d-axis, and the dashed curve is a cut in the direction s=d  $(v_{d}=0)$ .

Fig. 2.10. Surface representing the input charge-capacitance.

Fig. 2.11. Cross sections of the surface of Fig. 2.10.

Fig. 2.12. Experimental curves analogous to those of Fig. 2.11.

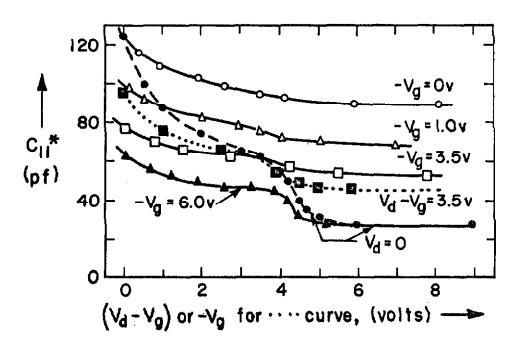

Most commercial FET's do exhibit noticeable jumps in  $C_{11}^*$ the channel becomes completely pinched-off. Of course, these jumps will not be infinitely steep, but some units, notably those manufactured by Motorola, do give exceptionally sharp drops. Experimental curves analogous to the theoretical curves of Fig. 2.11 are presented in Fig. 2.12. (Data are from type MM765, epitaxial-junction FET; measuring setup is shown in Appendix B.) The presence of a finite built-in potential means that  $V_g = 0$  does not correspond to s = 0, and the steep slope in  $C_{11}^*$  near  $s=\tilde{c}=0$  is not displayed. From the abrupt drop in the  $V_{d} = 0$  curve we see that the pinch-off voltage is roughly 5 volts. The finite value of capacitance beyond pinch-off (- $V_g > 5v$  with  $V_d = 0$  and  $V_d - V_g > 5v$  with  $V_g = -6.0v$ ) is due to interelectrode and other spurious effects, and since this capacitance is essentially independent of bias, it may be considered mcrely as stray capacitance. As expected, the singularity at s = a = 1 has been smoothed out. The ratio of the drop in  $C_{11}^*$ along the line  $V_g = -6.0v$  to the drop along the line  $V_d = 0$ theoretically should equal 0.67, but experimentally equals approximately 0.59. The error may be attributed in part to the smoothness of the drop-off and the resulting inaccuracies in computing the jumps.

<sup>\*</sup> Strictly speaking, measured input capacitances should be denoted by  $c_{11}$  rather than by  $c_{11}^*$ . In Chapter VI, however, these two quantities are shown to be identical, so that for clarity, only the symbol  $c_{11}^*$  is used here.

The dotted curve represents a cut parallel to the s-axis  $(c_{11}^* \text{ vs. -V}_g \text{ with } V_d - V_g = 3.5\text{v})$  and theoretically should be identical to the corresponding cut parallel to the d-axis  $(c_{11}^* \text{ vs. } V_d - V_g \text{ with } V_g = -3.5\text{v})$ . The difference between the two curves arises because the actual FET lacks the symmetry assumed in the model.

#### 2.5. Conclusions

In this chapter we have given a rather complete, albeit terse analysis of the step-junction FET. Although the results for I and  $\mathbf{g}_{\mathrm{m}}$  are now standard, the solutions for  $\mathbf{C}_{11}^{*}$  and  $\mathbf{C}_{22}^{*}$  have not been given before. For this reason these quantities were discussed in detail, especially in their relation to the small-signal equivalent circuit of the FET. A not-uncommon pitfall in the calculation of the input capacitance was mentioned, and some of the singular properties of  $\mathbf{C}_{11}^{*}$  were discussed, along with experimental verification of the predicted conclusions.

This chapter has provided the necessary background for the treatment of an arbitrarily doped FET. Before we begin this general treatment, however, we shall, in the next chapter, investigate the validity of the assumptions used in the preceding derivations.

#### CHAPTER III

# VALIDITY OF THE ASSUMPTIONS USED IN THE SIEP-JUNCTION ANALYSIS

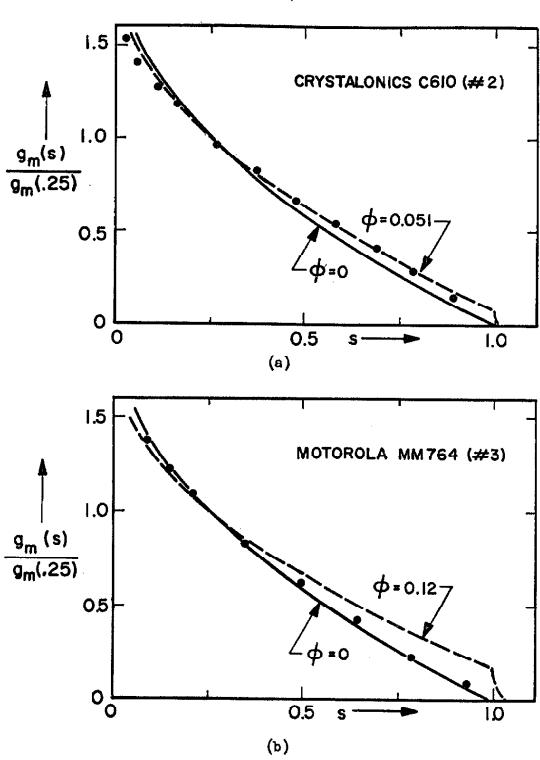

Our primary purpose in this chapter is to determine the usefulness and the limitations of the step-junction analysis by an examination of the assumptions and the approximations of the previous chapter. Despite the simplicity of the step-junction treatment, the theoretical results do agree with the experimental measurements on most units tested (see also published data, e.g. in [7], [8], and [9]). Nevertheless, some FET's that were tested in the present investigation differed qualitatively in  $\mathbf{g}_{\mathbf{m}}$  from the results of Chapter II. Near gate pinch-off (where  $\mathbf{g}_{\mathbf{m}}=0$ ) the curve of transconductance versus gate voltage theoretically should give a slope that is much shallower than the small-bias slope; some units, however, showed an almost uniform slope. Our secondary purpose in this chapter is to explain this deviation.

The most fundamental hypothesis of the previous chapter was the choice of a model for the FET. In Section 3.1 we show the suitability of the ideal model by comparing it with commercial structures. In that section we also dispense quickly with four of the eight listed assumptions of Chapter II. The remaining four assumptions are treated in the subsequent sections. The procedure given in Section 3.2 shows how the built-in potential may be easily included in previous formulae; in Sections 3.3. and 3.4 we affirm that the constant-mobility assumption and the gradual approximation are

reasonably well justified in practice; by means of an approximate analysis in Section 3.5, we conclude that the boundary on the space-charge region may be considered abrupt.

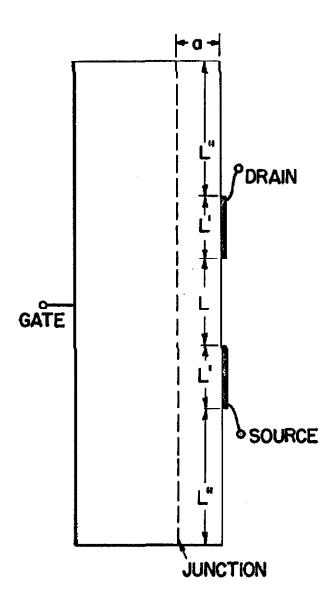

#### 3.1. Deviations from Idealized Geometry

Although some commercial FET's (e.g. Motorola units [10], [11]) closely approximate the geometry of our model, others (especially diffused types) apparently differ significantly from this ideal. We shall examine one typical case (three-terminal, single-diffused Texas Instruments units; no type number available) and prove that the use of the idealized geometry is an excellent approximation. Most other non-ideal transistors can be treated in a similar manner with a similar conclusion.

A cross section of the device to be considered is shown in Fig. 3.1. The ratio  $A/L \approx 40$ , so that three-dimensional effects are unimportant. The source and drain contacts are not negligible in size, but have length  $L^1 \sim L$ . This condition raises doubts as to the applicability of our previous results and is therefore discussed below.

<sup>\*</sup> FET's with concentric geometries (such as certain Crystalonics units) are described by equations with functional dependences identical to the dependences in the corresponding planar-geometry equations. The exact formulae for the concentric devices may be obtained from the planar formulae with the replacements  $(L/A) \to (1/2\pi) ln(r_2/r_1) \quad \text{and} \quad (LA) \to \pi(r_2^2 - r_1^2), \quad \text{in which } r_1 \quad \text{and} \quad r_2 \quad \text{are respectively the inner and outer radii of the channel (corresponding to <math>x = 0$  and x = 1).

Fig. 3.1. Cross section of practical FET with non-ideal geometry.

For simplicity we consider the channel material to be a uniformly doped, unit-conductivity semiconductor. With no bias on the gate or drain, the ideal model predicts a source-drain resistance

$$R_{sd} = \frac{1}{\Lambda} \frac{T_s}{a}$$

We now calculate the actual source-drain resistance  $R_{sd}^{\prime}$  and show that  $R_{sd}^{\prime}\approx R_{sd}$  .

Since the distances I" are of the order of a few L', we may, with no loss in accuracy, assume that  $L'' \to \infty$ . Now, if  $C'_{sd}$  is the capacitance between source and drain, then we have [12],

$$R_{s\bar{d}}^{\dagger} = \frac{1}{C_{s\bar{d}}^{\dagger}}$$

assuming, for convenience, that  $\varepsilon=1$ . The solution to the capacitance problem has been worked out in detail [13] with the result

$$C_{S\bar{Q}}^{\dagger} = \frac{A}{2} \frac{K(k')}{K(k)} \tag{3.1}$$

where K is the complete elliptic integral, and where

$$k = \frac{\tanh \frac{\pi L}{4a}}{\tanh \left(\frac{\pi L}{2a} + \frac{\pi L}{4a}\right)}, \qquad k^{2} = 1 - k^{2}$$

A useful approximation to Eq. 3.1 may be obtained for  $1/a \gg 1$ , since then

$k \approx 1$

$$k' \approx 2e^{-\pi L/4a} \sqrt{\frac{2 \tanh (\pi L^1/2a)}{1 + \tanh (\pi L^1/2a)}}$$

and [1]+]

$$K(k) \approx \frac{\pi}{2}$$

$$K(k') \approx ln (4/k') \approx ln 2 + \frac{\pi L}{4a}$$

for L'  $\gtrsim$  a. Thus,

$$C_{sd} \approx \frac{A}{2} \frac{a}{(L/2) + 0.44a}$$

Although derived for  $L/a \gg 1$ , this approximation is within 1% even for L/a = 2 [15]. The desired result is then\*

$$R_{sd}^{\dagger} \approx \frac{1}{A} \left[ \frac{L}{a} + 0.88 \right] \approx R_{sd}$$

(3.2)

since L/a > 10 in practice.

As mentioned in the introduction, several of the listed assumptions of Chapter II may be dismissed briefly. The hypothesis of a step-junction doping profile will be removed in the next chapter.

<sup>\*</sup> Equation 3.2 also obtains if  $L^1 \to \infty$ .

In practice, the direct gate current is several orders of magnitude less than the direct drain current, and the resistivities and contact fabrication are such that the drain current is carried completely by majority carriers. The empirical and heuristic justification for the assumption that extended the below-pinch-off formulae of Section 2.3 to voltages above pinch-off has already been given in Section 2.4. The remaining assumptions are now examined in detail.

## 3.2. The Built-In Potential

By means of a simple redefinition of s and d, the built-in potential may be incorporated into the previous formulae, and the results effectively remain unchanged. We shall treat this discussion on a general basis since the results are directly applicable to all doping profiles.

First, it is necessary to distinguish between applied or "external" potentials and total or "internal" potentials. The latter quantities include the built-in potential. Unless otherwise specified, henceforward the symbol V (with various subscripts) signifies an external voltage, and W signifies the magnitude of an internal voltage. We define the built-in potential to be  $V_c$ , and the applied gate voltage necessary for pinch-off to be  $V_p$ . Thus, the magnitude of the internal pinch-off voltage is

<sup>\*</sup> The data sheet of any manufacturer may be consulted for proof of this fact.

xx Qualitative discussion on this point is given in [8].

$$W_{o} = \left[V_{e} + V_{p}\right] \tag{3.3}$$

the magnitude of the internal gate voltage is

$$W_g = |V_c + V_g| \tag{3.4}$$

and the magnitude of the internal drain potential is simply

$$W_{\vec{a}} = |V_{\vec{a}}| \tag{3.5}$$

because  $V_{\rm d}$  is measured from drain to source. For reverse bias on the gate-channel junction,  $V_{\rm c}$  and  $V_{\rm g}$  add directly, regardless of the type of channel. The presence of a finite built-in potential permits the application of  $V_{\rm g}$  of sign opposite to that of  $V_{\rm c}$ . These forward-bias values of  $V_{\rm g}$  must be small enough to ensure that the gate current remains negligible.

All our theoretical expressions are written in terms of the internal quantitites s and à. Detailed transformation into expressions involving external voltages is unnecessary, for we observe that

$$s = \frac{v_g}{v_o}$$

$$= \frac{v_c}{v_c + v_p} + \left(\frac{1}{v_c + v_p}\right) v_g$$

(3.6)

$$d = \frac{V_d + W_g}{V_o}$$

$$= \frac{V_c}{V_c + V_p} + \left(\frac{1}{V_c + V_p}\right) V_g - \left(\frac{1}{V_c + V_p}\right) V_d$$

(3.7)

The above equations include the built-in potential and are more general than Eqs. 2.12 and 2.13. Therefore, Eqs. 3.6 and 3.7 replace these earlier definitions of s and â. Because s, for example, is linearly related to the applied voltage  $V_g$ , any curve plotted as a function of s will have the same shape if it is plotted as a function of  $V_g$ . In order to compare theory and experiment we simply add  $V_c$  to  $V_g$ , and then normalize this sum with respect to  $(V_c + V_p)$  to obtain s. Excess gate current will flow if  $V_g = -V_c$ , so that experimental points will only lie within some fraction of the theoretical range  $0 \le s \le 1$ . Small errors in  $V_c$  are critical when the slope of the quartity of interest is steep near s = 0, as, for example, in the case of  $C_{11}^*(s,1)$ . Remarks similar to those given above apply to the Internal gate-drain potential a.

#### 3.3. Non-Constant Mobility

The hypothesis of constant carrier mobility  $\mu$  will break down if the channel field is higher than the so-called critical field  $E_{\rm C}$  [16]. Beyond this field the mobility first varies as  $E^{-1/2}$ , and then, in the velocity-limited range, varies as  $E^{-1}$ . Dacey and Ross [8] have computed I and  $g_{\rm m}$  for a step-junction FET under the assumption that over the whole channel length the electric field is greater than  $E_{\rm c}$ , but less than the limiting-velocity field. That is,

they assume that  $\mu=\mu_{C}$   $(E_{C}/E)^{1/2}$ , in which  $\mu_{O}$  is the low-field mobility. In the pinch-off range their results are

$$I = I_{c} \left( \frac{3}{2} \frac{E_{c}}{W_{o}/L} \right)^{3/2} \left[ \frac{1}{2} (1 - \sqrt{s})^{3} - 3(1 - \sqrt{s})^{4} \right]^{1/2}$$

(3.8a)

$$g_{\rm m} = G_0 \left( \frac{3}{2} \frac{E_c}{W_0/L} \right)^{1/2} \left[ \frac{1 - \sqrt{s}}{1 + 3\sqrt{s}} \right]^{1/2}$$

(3.8b)

In being the zero-bias drain current for the constant mobility case. The analysis leading to these equations is valid only if  $W_0/L \gg E_c$ , i.e. if the average channel field is considerably greater than critical. As expected, the zero-bias current and transconductance are reduced because of the lowered mobility. Aside from the normalization, Eq. 3.8a does not differ appreciably from the constant-mobility transfer characteristics 2.34; the transconductance, given by Eq. 3.8b, does differ, however, by having a slightly concavedownward shape near s=1.

The above results may be applicable to some experimental FET's and, perhaps, to a few commercial models, but the parameters of most commercial FET's preclude the possibility of non-constant mobility being significant at normal operating temperatures. For example, Crystalonics type C610 and Motorola type MM764 both have n-type silicon channels, for which the critical field is 2500v/cm [16]. However, the average channel field for each of these units is roughly 500v/cm, so that Eqs. 3.8 do not apply.

### 3.4. Validity of the Gradual Approximation

The gradual approximation, which formed the basis of our derivations, is described by

$$|E_y| \ll |E_x|, \qquad 0 \le y \le 5$$

(3.9)

$$\left|\frac{\partial \mathbb{E}_{\mathbf{x}}}{\partial \mathbf{x}}\right| \ll \left|\frac{\mathbf{p}}{\mathbf{\epsilon}}\right|, \qquad \mathbf{b} \leq \mathbf{y} \leq \mathbf{c} \tag{3.10}$$

in which  $\rho = \rho_0$  and c = a for the step-junction device under consideration. We now show, with actual calculations, that even under worst-case conditions these inequalities are satisfied for roughly 90% of the channel length.

First consider Eq. 3.9. When a finite drain current flows we know that the channel becomes progressively narrower in the direction of increasing x. That is, the channel boundary b(x) has a negative slope everywhere. Since the channel boundary delimits the current flow, we must have  $E_y \neq 0$  at y = b, so that, by continuity,  $E_y \neq 0$  for y near b. But  $E_y = 0$  at y = 0, and hence the maximum value of  $E_y$  within the channel occurs at y = b. Furthermore, the slope of the channel boundary, db/dx, gives the direction of the field at the boundary. These arguments enable us to assert that inequality 3.9 will be fulfilled if

$$\left| \frac{\mathbb{E}_{\mathbf{y}}}{\mathbb{E}_{\mathbf{x}}} \right|_{\mathbf{y}=\mathbf{b}} = \left| \frac{\tilde{\mathbf{c}}\mathbf{b}}{\tilde{\mathbf{d}}\mathbf{x}} \right| \ll 1 \tag{3.9a}$$

is fulfilled. From Eq. 2.20 we get

$$\left| \frac{db}{dx} \right| = \frac{d(3 - 2\sqrt{d}) - s(3 - 2\sqrt{s})}{6(L/a) u(1 - u)}$$

(3.11)

Therefore, to satisfy 3.9 we need

$$u(1-u) \gg \frac{d(3-2\sqrt{d})-s(3-2\sqrt{s})}{6(L/a)} \equiv h$$

(3.12)

The right-hand side of this inequality, h, is small because the numerator is at most unity, and L/a is much greater than one.

The arguments for Eq. 3.10 run similarly. Inside the space-charge region  $\partial E_{\chi}/\partial x \neq 0$ . On the boundary y=a, however,  $\partial E_{\chi}/\partial x=0$ , so that, as with 3.9, the worst violation of 3.10 occurs at y=b. Equation 2.8 yields  $\partial E_{\chi}/\partial x$  in the space-charge region:

$$\left| \frac{\partial E_{x}}{\partial x} \right| = \left| \frac{\partial^{2} v}{\partial x^{2}} \right| = 2W_{0}(1 - \frac{y}{2}) \left| \frac{d^{2} u}{dx^{2}} \right|$$

We evaluate  $\ddot{a}^2u/dx^2$  from 3.11 to get

$$\frac{u^{3}(1-u)^{2}}{|2u-1|} \gg \left[\frac{d(3-2\sqrt{d})-s(3-2\sqrt{s})}{6(L/a)}\right]^{2} = h^{2}$$

(3.13)

as the condition necessary to satisfy inequality 3.10.

Inequalities 3.12 and 3.13 are both violated near u=1 and near u=0. The failure of the gradual approximation near u=1 does not introduce any error into the analysis because of the

relatively large channel conductance in that region. The error near u=0 represents the significant breakdown of the gradual approximation. For definiteness, we now consider ">> 1" to mean "> H," where H is some number greater than one. Then (disregarding the violation near u=1), the values of u for which the gradual approximation holds are given by the narrower of the two pairs of bounds

$$\frac{1}{2} - \frac{1}{2} \sqrt{1 - 4hH} \le u \le 1 \tag{3.14a}$$

and

$$(h^2H)^{1/3}\left[1-\frac{1}{3}(h^2H)^{2/3}-\frac{2}{3}(h^2H)\right] \le u \le 1$$

(3.14b)

The lower bound in 3.14a is an exact solution of 3.12, while the lower bound in 3.14b is an approximate solution of 3.13 for  $h^2H \ll 1$ . The relative magnitudes of h and H determine which condition is stronger.

We now consider the worst-case condition,  $\bar{a}-1$ , and by means of Eq. 2.20 for x/L convert Eqs. 3.14 into inequalities for x/L:

$$0 \le \frac{x}{L} \le 1 - \frac{1}{4} \frac{\left(1 - \sqrt{1 - 4hH}\right)^2 \left(2 + \sqrt{1 - 4hH}\right)}{\left(1 - \sqrt{s}\right)^2 \left(1 + 2\sqrt{s}\right)}$$

(3.15a)

$$0 \le \frac{x}{5} \le 1 - \frac{(h^2 H)^{2/3} [3 - 2(h^2 H)^{1/3}]}{1 - s(3 - 2\sqrt{s})}$$

(3.15b)

The maximum values of x/L such that H > 10 (i.e. such that the right-hand and left-hand sides of each of the gradual-approximation inequalities 3.9 and 3.10 differ by at least an order of magnitude) are given for various values of s and L/a in the following table:

| ន   | L/a      | (x/L) <sub>max</sub> |   |           |

|-----|----------|----------------------|---|-----------|

| 0   | 10<br>20 | 0.89                 | } | Eq. 3.15a |

| 1/4 | 10<br>20 | 0.95<br>0.98         |   |           |

| 1/2 | 10<br>20 | 0.97<br>0.99         |   | Eq. 3.15b |

We see from this table that the gradual approximation is valid for at least 89% of the channel length, and is usually valid over a much wider range. The maximum values of x/L for L/a = 10 and for various values of s and d are illustrated on the channel curves drawn in Fig. 2.3.

Furthermore, with non-uniform channel doping, as is present, for example, in single- or double-diffused structures, the gradual approximation will be more accurate than with uniform doping, because in the former case the channel conductivity is (in general) larger at y = 0 than at y = b, and hence the current flow tends to be more one-dimensional.

### 3.5. Non-Abrupt Boundary on the Space-Charge Region

The only assumption remaining from Chapter II is that of the abrupt boundary between the space-charge region and the neutral channel. Actually, the transition from neutrality to almost complete free carrier depletion occurs in a length on the order of the Debye length of the channel material [17]. Thus, we expect the abrupt-boundary assumption to break down when the channel width a is comparable with In. The ratio of these two quantities is

$$\frac{\Sigma_{D}}{a} = \frac{1}{a} \sqrt{\frac{\epsilon kT}{q\rho_{O}}} = \sqrt{\frac{(kT/q)}{\rho_{C}a^{2}/\epsilon}} = \sqrt{\frac{V_{t}}{2W_{O}}}$$

(3.16)

where  $W_t = kT/q$ , k is Boltzmann's constant, T is the absolute temperature, and q is the electronic charge.\* For FET's with small pinch-off voltages this ratio may be large enough to necessitate the introduction of significant correction terms in the previous formulae. We shall attempt to find a second-order correction to the first-order theory. Since the problem involves second-order effects, we shall feel justified in making several broad simplifying assumptions in the following analysis.

The method we shall adopt is to assume that some mobile carriers remain on the depletion-region side of the first-order sharp boundary of the channel. We consider a>1, and we divide the channel into two regions,  $0 \le x \le L_1$  and  $L_1 < x \le L$ . In the first region

<sup>\*</sup> The last equality in Eq. 3.16 is valid only for step-junction FET's that have very high gate conductivities, i.e. only when  $W_O = \rho_O a^2/2\varepsilon$ .

$|V(x,C)| \leq W_O$ , so that  $k \geq 0$  and the conduction is due mostly to carriers in the neutral channel  $0 \leq y \leq b$ , but partly to carriers within b < y < a; the second region has  $|V(x,0)| > W_O$ , and hence there is no neutral channel, the conduction being entirely due to the small number of free carriers in the (partial) depletion region  $0 \leq y < a$ . We solve each region for the current and then eliminate  $L_1$  from the two resulting equations. The analysis predicts normalized transconductances that are slightly larger than the first-order values for the same s. The amount of the correction increases with the ratio  $W_t/W_O$ . When compared with experimental results, we find that the theory provides the proper qualitative corrections in  $g_m$  to account for the errors in the first-order theory, but that the magnitude of the corrections is somewhat large.

We begin the analysis by assuming that the previously derived expression 2.9 for the channel boundary b(x) is valid. Now, however, instead of assuming that the mobile-charge density is (in magnitude)

$$\left| \rho_{m} \right| = \begin{cases} \rho_{0}, & 0 \leq y < b \\ 0, & b < y \leq a \end{cases}$$

we assume the distribution\*

<sup>\*</sup> In this section we shall assume that the built-in potential is included in the potentials denoted by V.

$$|\rho_{m}| = \begin{cases} \rho_{0}, & C \leq y \leq b \\ \rho_{0} = \sqrt{(x,y) - V(x,b)} / W_{t}, & b < y \leq a \end{cases}$$

(3.17)

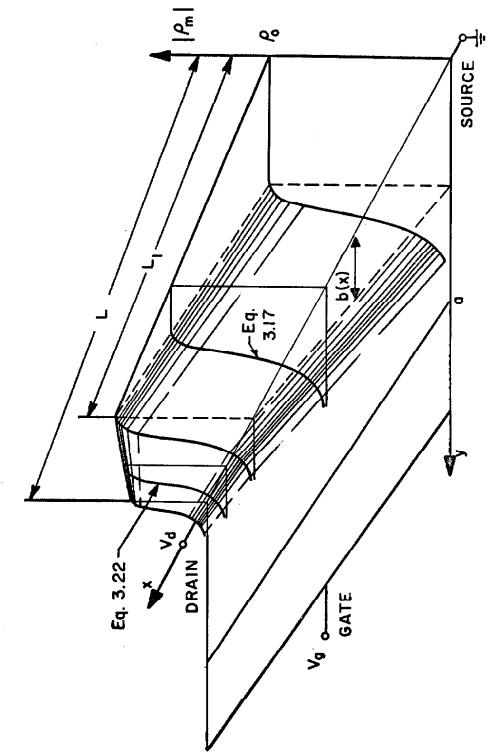

The last expression represents a Boltzmann falloff of free carriers within the depletion region and is the second-order correction to the first-order abrupt falloff. See Fig. 3.2 for a sketch of the density profile 3.17.

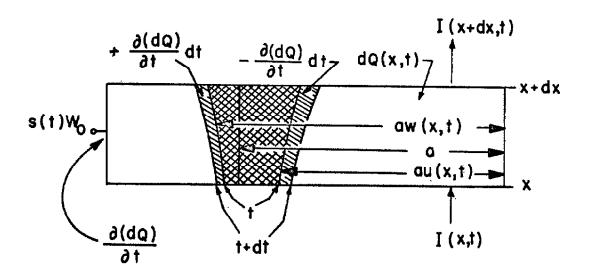

We shall consider operation beyond pinch-cff (d  $\ge$  1) because the non-abruptness of the channel boundary has the greatest effect in that range. The condition d > 1 means that some interval of the channel material, say  $L_1 < x \le L$ , will have, in the y = 0 plane, a potential with respect to the gate greater than  $W_0$ . In this interval, then, b = 0, and space charge is present over the entire width  $C \le y \le a$ . Furthermore, the gate potential  $\|V_g\| = W_0$ , while previously resulting in I = 0, now permits a finite drain current to flow. (The situation will be illustrated in Fig. 3.2.) The two-dimensional density of free carriers in a differential element of channel material in the interval  $0 \le x \le L_1$  is obtained by integrating Eq. 3.17 from y = 0 to y = a. The resistance dR of this element is then  $(A \ dx)/\mu$  divided by this integral, and the current is

$$I = \mu \Lambda \frac{dV(x,b)}{dx} \left[ \int_{0}^{b} \rho_{o} dy + \int_{b}^{a} \rho_{o} \exp\{-|V(x,y)-V(x,b)|/W_{t}\} dy \right]$$

The first integral in the square brackets is the first-order contribution; the second is the additional term that results from the mobile carriers in the depletion region. By employing Eq. 2.8 for V(x,y) we obtain

$$I = \mu \Lambda \rho_{O} \frac{dy}{dx} \left[ b + \int_{b}^{a} \exp\{-\frac{W_{O}(y}{W_{t}(a - u)^{2})} dy \right]$$

$$= G_0 L \frac{dV}{dx} \left[ u + \beta \frac{\sqrt{\pi}}{2} \operatorname{erf}(\frac{1 - u}{\beta}) \right]$$

(3.18)

where we have defined\*

$$\phi^2 \equiv \frac{2\epsilon W_t}{\rho_0 a^2} = \frac{W_t}{W_0} \tag{3.19}$$

and where

$$\operatorname{erf} x = \frac{2}{\sqrt{\pi}} \int_{0}^{x} e^{-t^{2}} dt$$

is the standard definition of the error function. Using Eq. 2.14 for V(x), we may integrate Eq. 3.18 over the range  $0 \le x \le L_1$ ,  $0 \le V \le W_0(1-s)$  to get

<sup>\*</sup> Cf. footnote page 57.

$$I = I_{c} \frac{L}{L_{1}} \left[ (1 - \sqrt{s})^{2} (1 + 2\sqrt{s}) + \frac{3\sqrt{\pi}}{2} \phi^{3} \int_{\sqrt{s}/\phi}^{1/\phi} 2t \text{ erf t at} \right]$$

(3.20)

where  $I_{0}$  is the zero-bias current for the first-order abruptboundary case and is slightly smaller than the new zero-bias current

$$T_{o}\left[1 + \frac{3\sqrt{\pi}}{2} \phi^{3} \int_{0}^{1/\phi} 2t \text{ erf } t \text{ dt}\right]$$

The integral appearing in 3.20 may be solved,

$$\int_{0}^{x} 2t \ \text{erf t dt} = \left(x^{2} - \frac{1}{2}\right) \text{erf } x + \frac{1}{\sqrt{\pi}} x \text{e}^{-x^{2}}$$

(3.21)

but we shall retain the unintegrated expression for convenience.

We now determine another expression relating I and  $L_1$  by considering the space-charge region defined by  $L_1 < x \le L$ . In a one-dimensional treatment of the space-charge region the maximum potential that can appear across the width a is  $W_0 = \rho_0 a^2/2\varepsilon$ . But at y=0, for every  $x > L_1$  the potential with respect to the gate is greater than  $W_0$ . In order to maintain a one-dimensional problem while still utilizing our simple model, we shall assume that the y-dependence of the potential in the space-charge region is unchanged, but that  $\rho_0$  is replaced by the x-dependent density  $\rho^*$ . Thus, for  $L_1 < x \le L$  the potential obeys

$$V(x,y) = V_g + \frac{\rho^*(x)}{2\epsilon} (a^2 - y^2)$$

In the interior of the channel in the first-order theory we always had  $|v-v_g| < w_o$  and b>c, so that no quantity analogous to  $t_o^*$  was needed. The present second-order treatment necessitates the consideration of two-dimensional effects, and  $\rho^*$  is introduced to account for these effects. Along the plane y=0 (which, in the interval  $L_1 < x < L$ , corresponds to the channel boundary y=b in the interval  $0 \le x \le L_1$ ) the potential is

$$V(x,0) = V_g + \frac{\rho^*(x)a^2}{2\epsilon}$$

This equation is the analog of Eq. 2.9 for the potential in the neutral channel. We note that  $V(L_1,0)\equiv V_g+W_o$  and that  $V(L,0)=V_d$ , so that  $\rho^*(L_1)=\rho_c$  and  $\rho^*(L)=\rho_o(V_d-V_g)/W_o=\rho_o d$ . It is the x-directed electric field resulting from V(x,0) that enters into the current-flow equation.

As in the treatment for  $0 \le x \le L_1$ , we still assume a Boltzmann falloff of the free-carrier density in the y-direction, but now this falloff is from y=0 rather than from y=b. Also, as we increase x from  $L_2$ , along the plane y=0 say, we expect the free-carrier density to decrease because we are traveling away from the neutral channel. Our final assumption is that the free-carrier density experiences a Boltzmann falloff in the x-direction for  $x>L_1$ . Thus, in the interval  $L_1< x\le L$  we have

$$|\rho_{\rm m}| = \rho_{\rm o} \exp[-|V(x,0) - V(L_{\rm l},0)|/W_{\rm l}] \exp[-|V(x,y) - V(x,0)|/W_{\rm l}]$$

(3.22)

The complete mobile-carrier density is depicted in Fig. 3.2. For  $0 \le x \le L_1$ ,  $|\rho_m|$  is given by Eq. 3.17; for  $L_1 < x \le L$ , it is given by Eq. 3.22. In the first-order theory  $L_1 = L$ , and  $|\rho_m|$  is a sharp-cornered, weage-shaped surface bounded by the surface y = b(x).

Some of the above hypotheses may seem unreasonable, but, as mentioned at the beginning of this section, we are being guided by the fact that our goal is merely a correction to the almost-satisfactory first-order theory. Further, although the hypotheses themselves may seem unreasonable, the resulting mobile-carrier distribution pictured in Fig. 3.2 is quite plausible.

Combining the preceding remarks and equations for the region  $L_2 < x < L$ , we obtain the drain current in the following straightforward steps:

$$I = \mu \Lambda \frac{dV(x,0)}{dx} \int_{0}^{a} |\rho_{m}| dy$$

$$= \mu \Lambda \left(\frac{a^{2}}{2\epsilon} \frac{d\rho^{*}}{dx}\right) \rho_{0} \exp \left[-\frac{(\rho^{*} - \rho_{0})a^{2}}{2\epsilon W_{t}}\right] \int_{0}^{a} \exp \left[\frac{c^{*}y^{2}}{2\epsilon W_{t}}\right] dy$$

$$= \mu \alpha AW_{0} \sqrt[p]{\sqrt{\frac{\rho_{0}}{\pi}}} \exp \left[-\frac{(\rho^{*} - \rho_{0})}{\rho_{0} \sqrt[p]{2}}\right] \frac{\sqrt{\pi}}{2} \operatorname{erf} \left[\frac{1}{\sqrt{p}} \sqrt{\frac{\rho_{0}}{\rho_{0}}}\right] \frac{d\rho^{*}}{dx}$$

$$\int_{1}^{\pi} I dx = 3LI_{0} \sqrt[p]{\frac{\sqrt{\pi}}{2}} \exp \left(\frac{1}{\sqrt{p^{2}}}\right) \int_{1}^{a} \sqrt{\frac{\rho_{0}}{\epsilon}} \exp \left(-\frac{c^{*}}{\sqrt{p^{2}}}\right) \operatorname{erf} \left(\frac{1}{\sqrt{p}} \sqrt{\frac{\rho_{0}}{\rho_{0}}}\right) d\left(\frac{\rho^{*}}{\rho_{0}}\right)$$

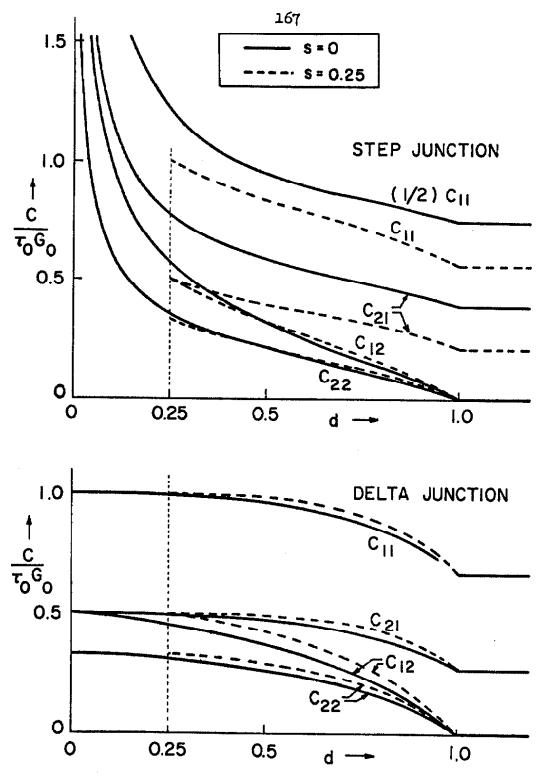

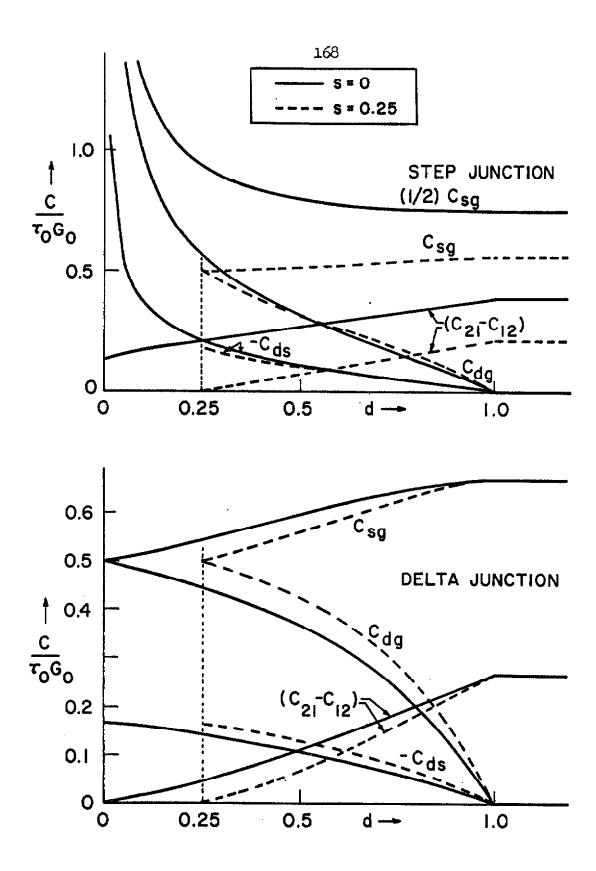

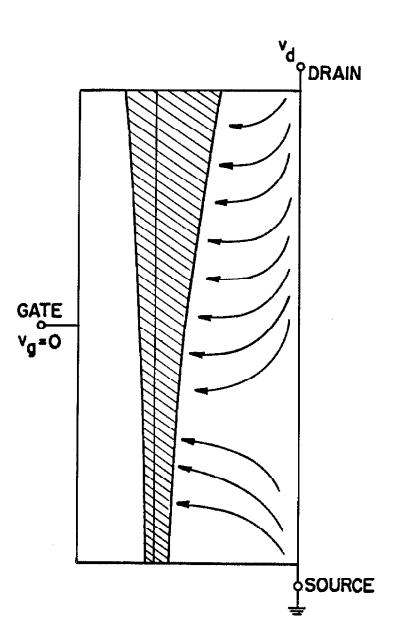

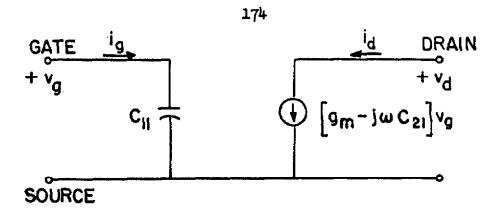

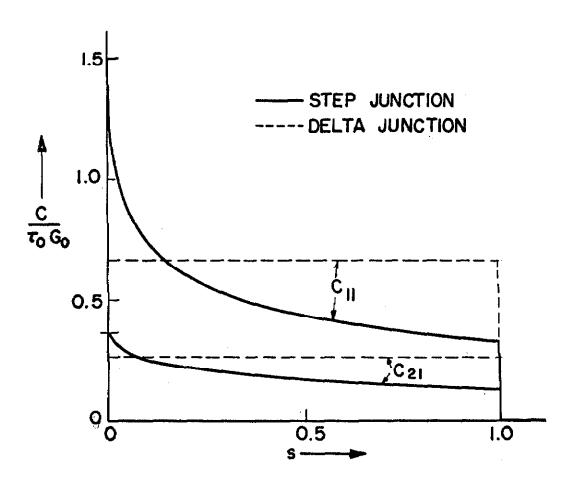

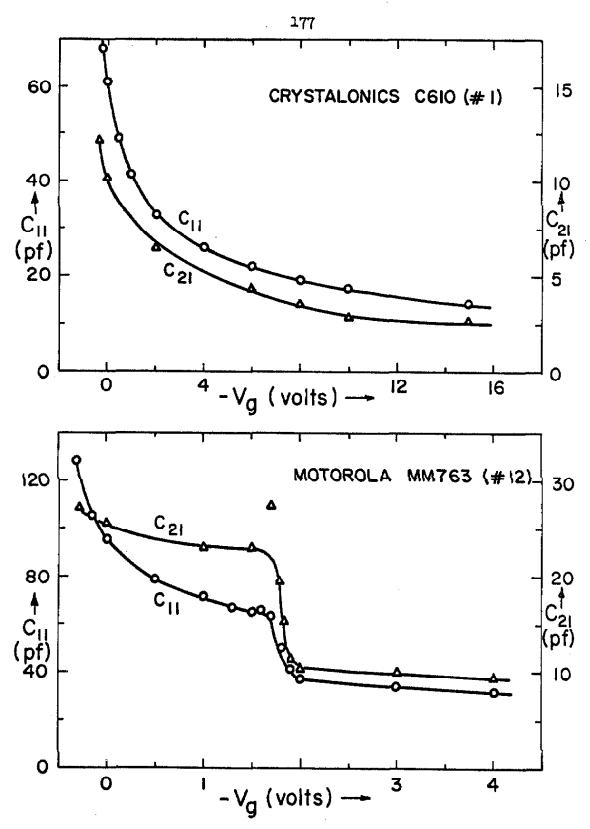

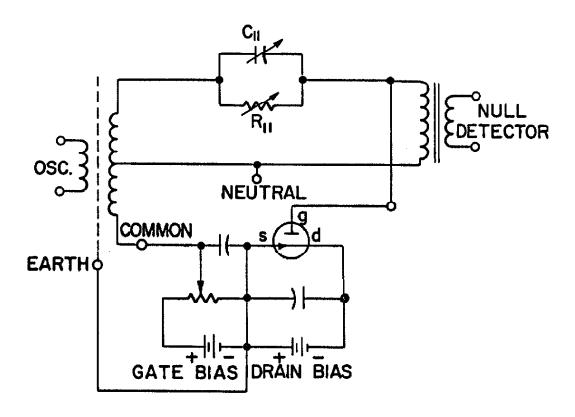

$$(3.23)$$