## Silicon Heterojunctions

Thesis by Per-Olov Pettersson

In Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

California Institute of Technology Pasadena, California

1996

(Defended May 6, 1996)

© 1996 Per-Olov Pettersson All rights reserved

To Krista

## Acknowledgments

I am happy to have had the opportunity to work with Tom McGill. He stayed out of the way of the experiments while giving critical guidance when necessary. In addition, he taught me some of the most important skills needed in today's environment – communication, presentation, marketing, and fund raising skills.

I have very much enjoyed working in the informal teams that carried out the research presented here. Robert Miles did the AFM measurements in the silicon on calciumfluoride project. In addition to the measurements, he brought guidance, encouragement, and a loud laughter to the project. Thank you, Rob.

I have also had the pleasure to work with Ed Croke and Andy Hunter at Hughes Research Laboratories. Ed started me out on the small custom MBE machine and also grew the  $Si_{1-y}C_y$  superlattices. Both Ed and Andy provided invaluable discussions and advice. Channing Ahn and Carol Garland were critical to the TEM characterization of these superlattices not only in training me to prepare the samples and using the TEM, but also in discussing and acquiring the data. I'd also like to thank Maggie Taylor and Prof. Atwater for the RBS measurements and analysis as well as helpful discussions.

The largest team consisted of Paul Bridger, Erik Daniel, Harold Levy, Ogden Marsh, and Amikam Zur. We had a lot of fun investigating a metal insulator semiconductor switch for use in an SRAM that Harold had invented. Erik and Paul measured the devices and Amikan simulated them. Ogden provided crucial insights and experience in processing the devices for which I am very grateful.

He was also very supportive and enthusiastic of our efforts, which made it all so much easier and fun. Although Amikam's simulations never agreed with what we measured, I don't hold that against him – he brought many good stories and encouragement in addition to rigor. Erik, the skeptic, never let us get carried away and actually believe that we understood how the device works. Paul kept measuring the optical characteristics, never giving up on getting that wavelength data. Harold was the virtual guru who got us into this business in the first place and whose insight is phenomenal.

All the other members of the group were very helpful, contributed to spirited discussions and great atmosphere in general. I would like to acknowledge Chris Springfield, Alicia Alonzo, Xiao-Chang Cheng, Zvonimir Bandic, Mark Phillips, David Reich, Doug Collins, Ron Marquardt, Yixin Liu, Shaun Kirby and Johannes Swenberg.

I am also grateful to the middle management: David Ting was, and here I quote Mark Phillips, "an unusually practical and useful theorist" as well as a great guy. Marcia Hudson kept us all out of trouble, staying on top of the administrative detail required to keep the group functioning.

Finally, I wish to thank my wife, Krista, for many years of encouragement and support.

### List of Publications

Work related to this thesis has been, or will be, published under the following titles:

Surface morphology of silicon grown on  $CaF_2/Si$  by electron-beamassisted molecular-beam epitaxy,

P.O. Pettersson, R.J. Miles, and T.C. McGill, J. Appl. Phys. **76**, 7328 (1994).

Temperature dependence of surface morphology of silicon grown on CaF<sub>2</sub>/Si by electron beam assisted MBE,

P.O. Pettersson, R.J. Miles, and T.C. McGill, Mat. Res. Soc. Symp. Proc. Vol. 367, 305 (1995).

Sb-Surfactant-Mediated Growth of  $Si/Si_{1-y}C_y$  Superlattices by Molecular-Beam Epitaxy,

P.O. Pettersson, C.C. Ahn, T.C. McGill, E.T. Croke, and A.T. Hunter, Appl. Phys. Lett. 67, 2530 (1995).

Characterization of  $Si/Si_{1-y}C_y$  Superlattices Grown by Surfactant Assisted Molecular Beam Epitaxy,

P.O. Pettersson, C.C. Ahn, T.C. McGill, E.T. Croke, and A.T. Hunter, Accepted for publication, J. Vac. Sci. Technolog. **B** (1996).

Dependence of the I/V curve of a Metal Insulator Semiconductor Switch on insulator thickness - an experimental and theoretical investigation,

P.O. Pettersson, A. Zur, E.S. Daniel, H.J. Levy, O.J. Marsh, and T.C. McGill, To be submitted, IEEE Electron Devices (1996).

### Abstract

The three topics presented in this thesis all concern silicon heterojunction growth and device applications. We developed growth techniques for two relatively immature material systems, silicon/calciumfluoride (Si/CaF<sub>2</sub>) and silicon/silicon-carbon (Si/Si<sub>1-y</sub>C<sub>y</sub>), and fabricated devices which take the mature silicon/silicon dioxides (Si/SiO<sub>2</sub>) material system to new limits in terms of oxide thickness.

We applied novel growth techniques in the undeveloped material systems with the ultimate goal of producing device quality material suitable for quantum device fabrication. In the Si/CaF<sub>2</sub> material system, we used a new technique known as Electron Beam Assisted Molecular Beam Epitaxy to improve the morphology of silicon grown on calciumfluoride. The result was a decrease in roughness of the silicon overlayer. In the silicon/silicon-carbon material system, we employed Surfactant Assisted Molecular Beam Epitaxy to grow smooth high carbon content silicon-carbon on silicon. Here, the result was a greatly improved surface morhology and the technique looks promising for applications requiring high carbon concentrations.

In the mature and extremely important (from a technological and commercial point of view) Si/SiO<sub>2</sub> material system, we fabricated Metal Insulator Semiconductor Switches devices in a study of the dependence of the I/V curve on the insulator thickness. While the primary objective of this study was to optimize the I/V curve, we learned that this material system is not very well understood, neither from a theoretical nor experimental standpoint, when the oxide is extremely thin.

## Contents

| A  | cknov                     | wledgn           | nents                                              |  | iv                     |

|----|---------------------------|------------------|----------------------------------------------------|--|------------------------|

| Li | ostract vist of Figures x | vi               |                                                    |  |                        |

| A  | bstra                     | ct               |                                                    |  | viii                   |

| Li | st of                     | Figure           | es                                                 |  | xiii                   |

| Li | st of                     | Tables           | s                                                  |  | $\mathbf{x}\mathbf{v}$ |

| 1  | $\mathbf{Intr}$           | $\mathbf{oduct}$ | ion                                                |  | 1                      |

|    | 1.1                       | Overv            | riew of Thesis                                     |  | 2                      |

|    | 1.2                       | The S            | li/CaF <sub>2</sub> Material System                |  | 2                      |

|    |                           | 1.2.1            | Background                                         |  | 2                      |

|    |                           | 1.2.2            | Potential Applications                             |  | 3                      |

|    |                           | 1.2.3            | Growth                                             |  | 5                      |

|    |                           | 1.2.4            | Experiment                                         |  | 7                      |

|    |                           | 1.2.5            | Summary                                            |  | 8                      |

|    | 1.3                       | The S            | $\mathrm{Si/Si}_{1-y}\mathrm{C}_y$ Material System |  | 9                      |

|    |                           | 1.3.1            | Background                                         |  | 9                      |

|    |                           | 1.3.2            | Potential Applications                             |  | 10                     |

|    |                           | 1.3.3            | Growth                                             |  |                        |

|    |                           | 134              | Summary                                            |  | 13                     |

|   | Refe       | erences                           |                                                                       | 14         |

|---|------------|-----------------------------------|-----------------------------------------------------------------------|------------|

| 2 | Intr       | oducti                            | ion to the SRAM/MISS                                                  | 16         |

|   | 2.1        | Introd                            | uction                                                                | 16         |

|   |            | 2.1.1                             | Background                                                            | 16         |

|   |            | 2.1.2                             | The Memory Cell                                                       | 19         |

|   |            | 2.1.3                             | Addressing Scheme                                                     | 20         |

|   | 2.2        | MISS                              | Experiment                                                            | 21         |

|   | 2.3        | Summ                              | nary                                                                  | 23         |

|   | Refe       | erences                           |                                                                       | 24         |

| 9 | C          | Cono N                            | Jambalam of Silican Crown on CaE /Si Dr. Floatner                     |            |

| 3 |            |                                   | forphology of Silicon Grown on ${ m CaF_2/Si}$ By Electron sisted MBE | $f{25}$    |

|   |            |                                   |                                                                       |            |

|   | 3.1        |                                   | Charter Abstract                                                      |            |

|   |            | 3.1.1                             | Chapter Abstract                                                      |            |

|   |            | 3.1.2                             | Motivation and Background                                             |            |

|   | 2.0        | 3.1.3                             | Outline of Chapter                                                    |            |

|   | 3.2        |                                   | iment                                                                 |            |

|   |            | 3.2.1                             | Sample structure                                                      |            |

|   |            | 3.2.2                             | Sample preparation                                                    |            |

|   | 3.3        |                                   | cterization                                                           |            |

|   |            | 3.3.1                             | Atomic Force Microscopy                                               |            |

|   |            | 3.3.2                             | X-ray Photoemission Spectroscopy                                      |            |

|   | 3.4        |                                   | ssion                                                                 |            |

|   | 3.5        | Chapt                             | ser Summary                                                           | 41         |

|   | Refe       | erences                           |                                                                       | 42         |

| 4 | Si/S       | $\mathbf{Si}_{1-y}\mathbf{C}_{i}$ | Superlattices Grown by Surfactant Assisted Molecular                  | r          |

|   | ·          | ım Epi                            | , <del>-</del>                                                        | <b>4</b> 4 |

|   | <i>4</i> 1 | Introd                            | luction                                                               | 44         |

|   |                 | 4.1.1                                                                  | Chapter Abstract                                                                                                                                                             | 44                                                 |

|---|-----------------|------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

|   |                 | 4.1.2                                                                  | Introduction and Background                                                                                                                                                  | 45                                                 |

|   |                 | 4.1.3                                                                  | Outline of Chapter                                                                                                                                                           | 46                                                 |

|   | 4.2             | Exper                                                                  | iment                                                                                                                                                                        | 47                                                 |

|   |                 | 4.2.1                                                                  | Sample Growth                                                                                                                                                                | 47                                                 |

|   |                 | 4.2.2                                                                  | Characterization                                                                                                                                                             | 47                                                 |

|   | 4.3             | Result                                                                 | ts                                                                                                                                                                           | 48                                                 |

|   |                 | 4.3.1                                                                  | Analysis of RHEED Video                                                                                                                                                      | 48                                                 |

|   |                 | 4.3.2                                                                  | Analysis of TEM Micrographs                                                                                                                                                  | 52                                                 |

|   |                 | 4.3.3                                                                  | Analysis of HRXRD Data                                                                                                                                                       | 52                                                 |

|   |                 | 4.3.4                                                                  | Analysis of AFM Micrographs                                                                                                                                                  | 55                                                 |

|   |                 | 4.3.5                                                                  | Large Scale Defects                                                                                                                                                          | 56                                                 |

|   | 4.4             | Discus                                                                 | ssion                                                                                                                                                                        | 56                                                 |

|   | 4.5             | Chapt                                                                  | zer Summary                                                                                                                                                                  | 59                                                 |

|   | Refe            | erences                                                                |                                                                                                                                                                              | 60                                                 |

|   |                 |                                                                        |                                                                                                                                                                              |                                                    |

| _ | D               |                                                                        | and the I/W Comment of Matel Insulation Commission duration                                                                                                                  |                                                    |

| 5 | _               |                                                                        | ace of the I/V Curve of a Metal Insulator Semiconductor                                                                                                                      |                                                    |

| 5 | Swi             | tch on                                                                 | Insulator Thickness                                                                                                                                                          | 61                                                 |

| 5 | _               | tch on                                                                 | Insulator Thickness                                                                                                                                                          | <b>61</b>                                          |

| 5 | Swi             | tch on                                                                 | Insulator Thickness                                                                                                                                                          | <b>61</b>                                          |

| 5 | Swi             | tch on<br>Introd                                                       | Insulator Thickness                                                                                                                                                          | 61<br>61                                           |

| 5 | <b>Swi</b> 5.1  | Introd<br>5.1.1<br>5.1.2                                               | Insulator Thickness duction                                                                                                                                                  | 61<br>61                                           |

| 5 | <b>Swi</b> 5.1  | Introd<br>5.1.1<br>5.1.2                                               | Insulator Thickness duction                                                                                                                                                  | 61<br>61<br>62<br>65                               |

| 5 | <b>Swi</b> 5.1  | Introd<br>5.1.1<br>5.1.2<br>Exper                                      | Insulator Thickness duction                                                                                                                                                  | 61<br>61<br>62<br>65                               |

| 5 | <b>Swi</b> 5.1  | Introd<br>5.1.1<br>5.1.2<br>Exper<br>5.2.1                             | Insulator Thickness duction                                                                                                                                                  | 61<br>61<br>62<br>65<br>65                         |

| 5 | <b>Swi</b> 5.1  | Introd<br>5.1.1<br>5.1.2<br>Exper<br>5.2.1<br>5.2.2<br>5.2.3           | Insulator Thickness duction                                                                                                                                                  | 61<br>61<br>62<br>65<br>65<br>66                   |

| 5 | Swi 5.1 5.2     | Introd<br>5.1.1<br>5.1.2<br>Exper<br>5.2.1<br>5.2.2<br>5.2.3<br>Result | Insulator Thickness luction                                                                                                                                                  | 61<br>61<br>62<br>65<br>65<br>66<br>67             |

| 5 | Swi 5.1 5.2 5.3 | Introd<br>5.1.1<br>5.1.2<br>Exper<br>5.2.1<br>5.2.2<br>5.2.3<br>Result | Insulator Thickness luction Chapter Abstract Motivation and Background Timent Device Structure Electrical Measurements SiO <sub>2</sub> Thickness Estimate                   | 61<br>61<br>62<br>65<br>65<br>66<br>67<br>68       |

| 5 | Swi 5.1 5.2 5.3 | Introd<br>5.1.1<br>5.1.2<br>Exper<br>5.2.1<br>5.2.2<br>5.2.3<br>Result | Insulator Thickness cluction  Chapter Abstract  Motivation and Background  Timent  Device Structure  Electrical Measurements  SiO <sub>2</sub> Thickness Estimate  ts  ation | 61<br>61<br>62<br>65<br>65<br>66<br>67<br>68<br>68 |

| 5.5  | Discussion | ٠ | ٠ |  | ٠ |  |   |  |  |  |  |  |  |  |  |  |  |   | 7  |

|------|------------|---|---|--|---|--|---|--|--|--|--|--|--|--|--|--|--|---|----|

| 5.6  | Summary    |   |   |  |   |  |   |  |  |  |  |  |  |  |  |  |  |   | 80 |

| Refe | erences    |   |   |  |   |  | ٠ |  |  |  |  |  |  |  |  |  |  | ٠ | 8  |

# List of Figures

| 1.1 | The Resonant Tunneling Diode – how it works                              | 4  |

|-----|--------------------------------------------------------------------------|----|

| 1.2 | RTD device structure and I/V curve with definition of peak-to-valley     |    |

|     | voltage                                                                  | 6  |

| 2.1 | The conventional SRAM cell                                               | 17 |

| 2.2 | The conventional DRAM cell                                               | 18 |

| 2.3 | The SRAM memory cell based on a MISS                                     | 19 |

| 2.4 | Reading the memory cell                                                  | 20 |

| 2.5 | Writing to the memory cell                                               | 21 |

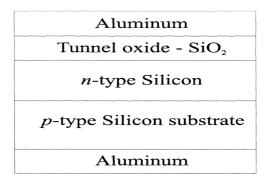

| 2.6 | MISS device structure                                                    | 22 |

| 3.1 | AFM 3D micrograph of silicon grown on $CaF_2(111)$ by standard           |    |

|     | MBE at high temperature (650°C)                                          | 29 |

| 3.2 | AFM 2D micrograph of silicon grown on $CaF_2(111)$ by standard           |    |

|     | MBE at high temperature (650°C)                                          | 30 |

| 3.3 | AFM micrograph of silicon grown on $\mathrm{CaF}_2(111)$ by standard MBE |    |

|     | at low temperature (500°C)                                               | 31 |

| 3.4 | AFM micrograph of silicon grown on $\mathrm{CaF}_2(111)$ by EB MBE at    |    |

|     | 650°C. Dose 1.0 mC/cm <sup>2</sup>                                       | 31 |

| 3.5 | AFM micrograph of silicon grown on $CaF_2(111)$ by EB MBE at high        |    |

|     | temperature (650°C). Dose 1.0 mC/cm <sup>2</sup>                         | 32 |

| 3.6 | AFM micrograph of silicon grown on $CaF_2(111)$ by EB MBE at                                           |    |

|-----|--------------------------------------------------------------------------------------------------------|----|

|     | medium temperature (575°C). Dose 1.0 mC/cm <sup>2</sup>                                                | 33 |

| 3.7 | RMS of the silicon overlayer versus the electron dose used in the EB                                   |    |

|     | MBE growth step for three different substrate temperatures                                             | 35 |

| 3.8 | The silicon crystal habit                                                                              | 38 |

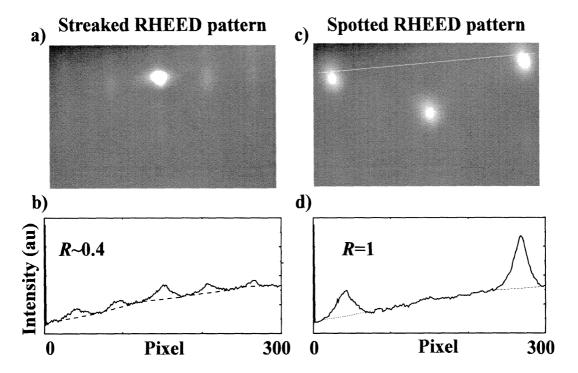

| 4.1 | Analysis of the RHEED pattern                                                                          | 49 |

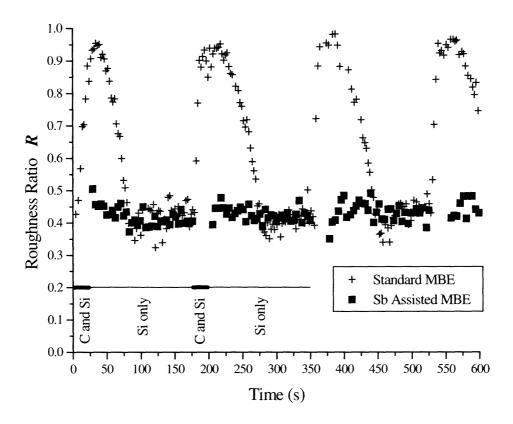

| 4.2 | Roughness ratio $R$ versus growth time                                                                 | 51 |

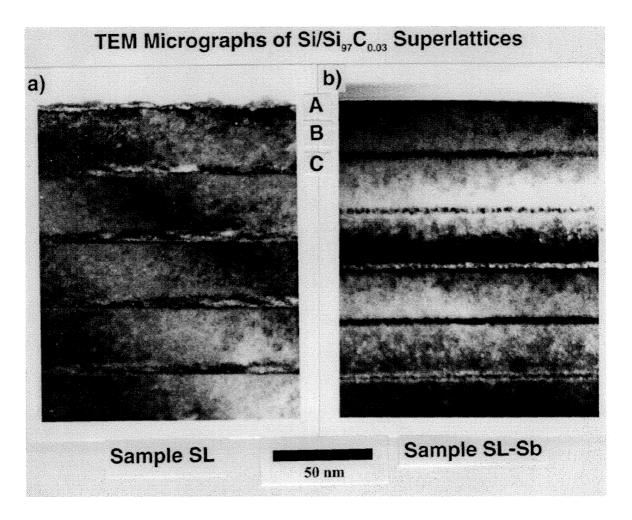

| 4.3 | Cross-sectional TEM images of the superlattice samples                                                 | 53 |

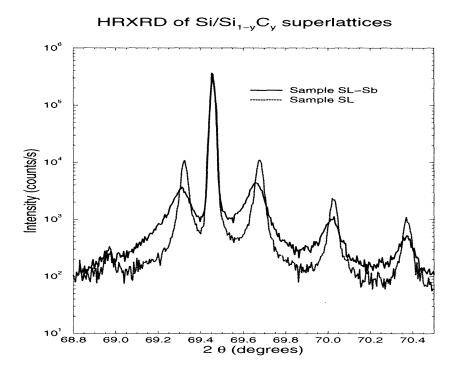

| 4.4 | HRXRD of a 15 period $\mathrm{Si/Si_{0.97}C_{0.03}}$ superlattices grown by stan-                      |    |

|     | dard MBE and by Sb assisted MBE                                                                        | 54 |

| 4.5 | AFM micrograph of the top layer (Si $_{0.97}$ C $_{0.03}$ ) of a 15 period Si/Si $_{0.97}$ C $_{0.03}$ | 03 |

|     | superlattice grown by standard MBE                                                                     | 55 |

| 5.1 | MISS device structure                                                                                  | 62 |

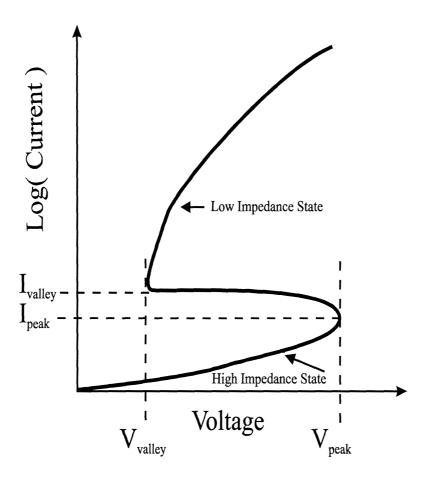

| 5.2 | The generic MISS I-V curve                                                                             | 64 |

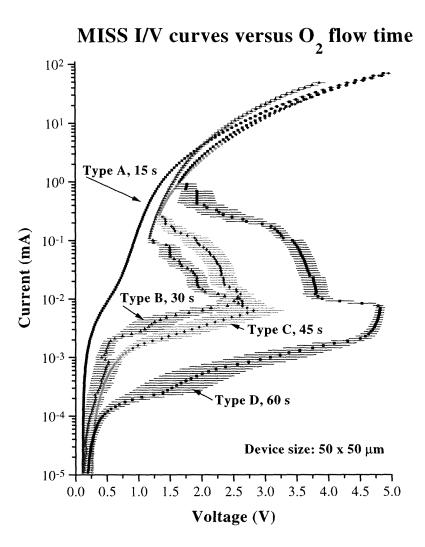

| 5.3 | I-V curves of the MISS devices as a function of oxygen flow time                                       | 69 |

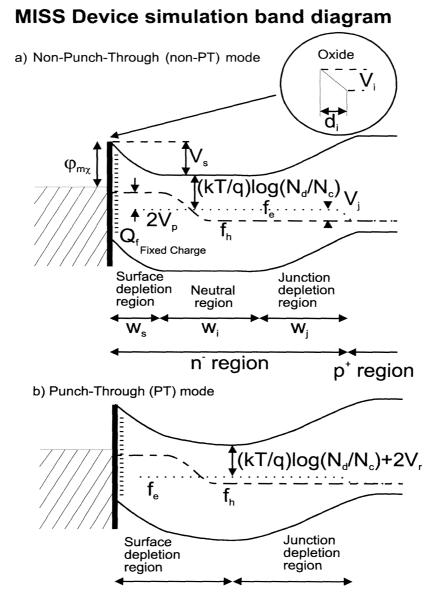

| 5.4 | Band diagram for the simulation                                                                        | 71 |

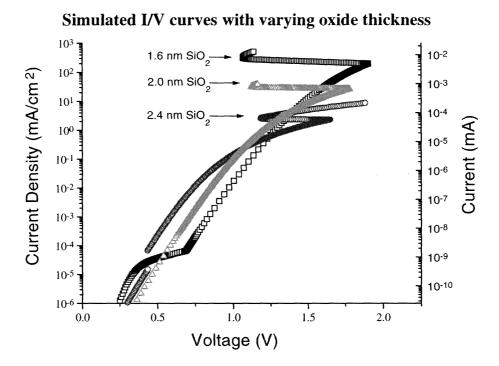

| 5.5 | Calculated J/V curves of the MISS devices as a function of oxide                                       |    |

|     | thickness.                                                                                             | 76 |

## List of Tables

| 3.1 | Calcium to silicon and fluorine to silicon XPS peak ratios of silicon |    |  |  |  |  |  |  |  |  |  |  |

|-----|-----------------------------------------------------------------------|----|--|--|--|--|--|--|--|--|--|--|

|     | grown on CaF <sub>2</sub> EB MBE at high temperature (650°C)          | 36 |  |  |  |  |  |  |  |  |  |  |

| 5.1 | Device types                                                          | 66 |  |  |  |  |  |  |  |  |  |  |

| 5.2 | The parameters used in the simulations                                | 75 |  |  |  |  |  |  |  |  |  |  |

## Chapter 1

### Introduction

The three topics presented in this thesis all concern silicon heterojunction growth and device applications. We developed growth techniques for two relatively immature material systems and fabricated devices which take the mature silicon/silicon dioxides material system to new limits in terms of oxide thickness.

We applied novel growth techniques in the undeveloped material systems with the ultimate goal of producing device quality material suitable for quantum device fabrication. In the silicon/calciumfluoride material system, we used a new technique known as Electron Beam Assisted Molecular Beam Epitaxy to improve the morphology of silicon grown on calciumfluoride. In the silicon/silicon-carbon material system, we employed Surfactant Assisted Molecular Beam Epitaxy to grow smooth high carbon content silicon-carbon on silicon.

In the mature and extremely important (from a technological and commercial point of view) Si/SiO<sub>2</sub> material system, we fabricated Metal Insulator Semiconductor Switches devices in a study of the dependence of the I/V curve on the insulator thickness. While the primary objective of this study was to optimize the I/V curve, we learned that this material system is not very well understood, neither from a theoretical nor experimental standpoint, when the oxide is extremely thin.

The uniting theme of these studies is that they all involve silicon heterojunc-

tions and that they embody the spirit of *applied* physics in the sense that they all drive toward making useful devices.

#### 1.1 Overview of Thesis

The three related topics are presented in chapters 3, 4, and 5. The first two topics, silicon overgrowth on  $CaF_2/Si$  and surfactant assisted growth of  $Si_{1-y}C_y/Si$ , are introduced in this chapter. The final topic, fabrication of a Metal Insulator Semiconductor Switch and study of the influence of the oxide thickness on the I/V curve of the device, is introduced in chapter 2.

### 1.2 The Si/CaF<sub>2</sub> Material System

#### 1.2.1 Background

This material system had been investigated extensively by the time we started working in the area. CaF<sub>2</sub> had been grown on silicon about ten years earlier[1] and many studies of this material system had subsequently been reported. For a review of the field, see Schowalter[2]. Interestingly, only a few reports had been published on the silicon overgrowth on CaF<sub>2</sub>. For some examples, see Isiwara[1], Asano[3], and Fathauer[4]. One reason for this is that while it is easy to grow high quality CaF<sub>2</sub> on silicon, the quality of a silicon overlayer, when grown on CaF<sub>2</sub>, is poor.

Some methods for improving the silicon overlayer quality had been proposed, but they relied on growing a poor quality (low growth temperature) initial layer of silicon and then annealing it. One would then grow a thick silicon (high growth temperature) layer where the quality improved as the thickness increased[3]. Unfortunately, this method would not work in our application as we needed an extremely thin high quality silicon layer. Thus, we had to apply another method

to improve the silicon quality. We chose to apply a novel technique, known as Electron Beam Assisted MBE, that had previously been used to improve Ge [2] and GaAs [3] overgrowth on CaF<sub>2</sub>. Before we continue to describe the details of the experiment, we will take a moment to motivate our interest in this material system by pointing out some of the interesting device applications.

#### 1.2.2 Potential Applications

If the silicon/calciumfluoride material system could be made to work, it might be one way to integrate quantum devices with standard CMOS electronics on a single silicon chip. The reason for wanting to integrate these devices is that the support electronics necessary to make an interesting, commercially viable, circuit could then easily be built using the surrounding silicon. One envisions making ultra dense digital memory circuits, neural networks, ultra high speed analog to digital converters and other high speed electronic circuits. In addition to making quantum devices, this material system could also be used to provide silicon on insulator technology and 3D electronics, which could be used to speed up standard devices in integrated circuits and allow for more complicated circuits respectively.

#### Quantum Devices

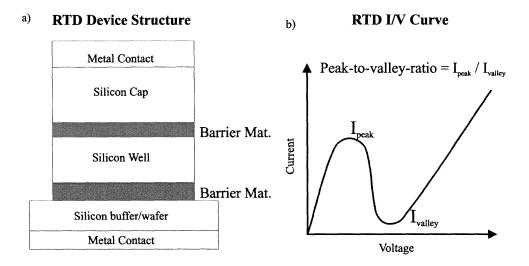

In Fig. 1.2a, we show a resonant tunneling diode (RTD). This device was invented some 24 years ago[7] and demonstrated shortly thereafter[8]. The device had since been built with great success in many configurations in III-IV material systems[9], but the efforts to make them work in silicon had been less fruitful. For instance, these devices had been built in the Si/SiGe material system, but the peak-to-valley ratio was only 1.2 for *n*-type RTDs[10] and 1.5 for *p*-type[11] RTDs at room temperature. For a generic I/V curve of these devices with the peak-to-valley ratio defined, see Fig. 1.2b.

While tunneling and device theory are beyond the scope of this thesis, we

### Resonant Tunneling Diode

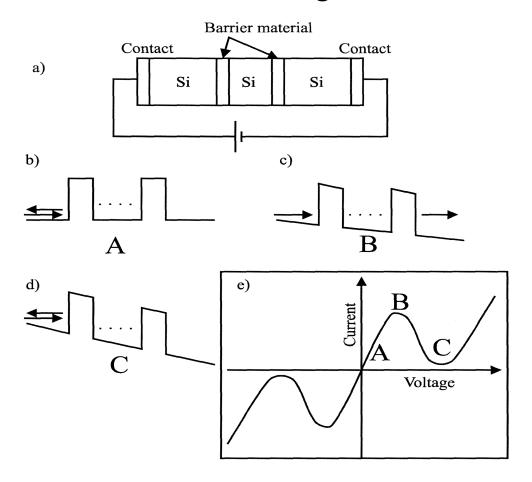

Figure 1.1: (a) RTD. (b) Schematic band diagram of an RTD. An electron incident from the left (at low bias) will have a very low transmission coefficient through the structure, as there is no state available in well region between the two barriers. (c) By biasing the device, one can line up the energy of the incident electrons with one of the semi-bound state of the well. (d) By increasing the bias further, the incident electron energy no longer is lined up with the semi-bound state in the well. (e) The resulting I/V curve.

provide a simple explanation for how these devices work here. In Fig. 1.1b we show a schematic band diagram of an RTD. An electron incident from the left (at low bias) will have a very low transmission coefficient through the structure, as there is no state available in well region between the two barriers. The result is that the current increases slowly with the voltage. This region of the I/V curve in Fig. 1.1e is denoted by A. By biasing the device, one can line up the energy of the incident electrons with one of the semi-bound state of the well (see Fig. 1.1c). In this case the electron is easily transmitted through the device. This corresponds to point B in the I/V curve shown in Fig. 1.1e. If the energy of the incident electron is increased further (see Fig. 1.1d), the transmission coefficient becomes smaller as there is no state in the well that can transmit the electron (point B in Fig. 1.1e). Thus, the current through device decreases as the voltage increases giving rise to negative differential resistance shown in the I/V curve as a downward slope. In order to achieve good confinement of the semi-bound states in the well, the conduction band offset has to be at least an order of magnitude larger than kT. The negative resistance region of the I/V curve can be used to make ultra fast amplifiers and memory circuits.

#### 1.2.3 Growth

Having described a possible application of the material system, we now turn back to fabrication issues. From a growth point of view, the important thing to notice is that in order to build this device, one has to grow the structure using two different materials (see Fig. 1.2a). As one can see in the figure, the barrier material has to be grown on the substrate material and then the well/substrate material has to be grown on top of the barrier material. Given that we want to use a silicon substrate, we are constrained to materials that match silicon in several respects. The list below show some, but by all means not all, of the constraints that have to be met:

Figure 1.2: RTD device structure and I/V curve with definition of peak-to-valley voltage.

- Lattice constant match

- Appropriate band alignments

- Thermal stability up to normal silicon processing temperatures

- Thermal expansion coefficient match

- Surface free energy match

From a practical point view, we also had to be able to evaporate the material in our MBE machine.

Calcium fluoride meet the first three requirements. The lattice match is pretty good (only 0.6% mismatch) and the band offsets are large in both the conduction and valence bands. The high melting temperature of CaF<sub>2</sub> also leads one to believe that it would remain stable during silicon processing temperatures. Unfortunately, the thermal expansion coefficients are very different. In fact, at the growth temperature, the lattice mismatch increases to about 2.5%. This mismatch is probably still small enough to maintain good crystal quality, provided that the barriers are

kept thin enough (below critical thickness). In contrast, we believe that the surface free energy mismatch turns out to be fatal.

#### CaF<sub>2</sub> Growth on Silicon

Thanks to the favorable matches mentioned above, CaF<sub>2</sub> grows nicely on silicon(111)[2]. We used LEED to characterize the CaF<sub>2</sub> and it shows the expected 1x1 reconstruction signifying good ordering of the surface. This is partially due to the low free energy (350 ergs/cm<sup>2</sup>) of the CaF<sub>2</sub>(111) surface, as compared to the high (1200 ergs/cm<sup>2</sup>) free energy of the silicon(111) surface. If the growth process is close to thermal equilibrium, the system will strive to reach the state of lowest Helmholtz surface free energy. Since the CaF<sub>2</sub> has a much lower surface free energy, the thermodynamic driving force would tend to maximize the low surface free energy CaF<sub>2</sub> surface and completely cover up the high energy silicon surface.

#### Silicon Overgrowth

Here, the difficulties begin. AFM micrographs show that the silicon does not wet the CaF<sub>2</sub> surface. Instead, the silicon forms hexagonal islands and defects are generated as these islands coalesce. One possible reason for the silicon to islands is that the system reaches its lowest free energy by minimizing the silicon surface area and maximize the CaF<sub>2</sub> surface area.

#### 1.2.4 Experiment

In order to alleviate the islanding, we modified the  $CaF_2$  surface prior to silicon overgrowth by irradiating the surface with low energy electrons. It has been shown that low energy electron radiation desorbs fluorine as  $F^+$  from  $CaF_2(111)$ , creating a calcium rich surface with an ordered array of surface F-centers[6]. This array of F-centers will have a higher surface free energy than the normal  $CaF_2$  surface and should thus favor 2D growth or at least lower the contact angle in 3D growth of

silicon on  $CaF_2$ .

We then studied the surface morphology of silicon, grown on top of the modified CaF<sub>2</sub>/Si surface, using atomic force microscopy (AFM), x-ray photoelectron spectroscopy (XPS) and low energy electron diffraction (LEED). We found an optimal range of electron beam exposure for high temperature (650°C) growth of the silicon overlayer that minimizes the roughness of the silicon overlayer. The observed hexagonally shaped microcrystals formed by the silicon during high temperature growth were explained by a simple model based on thermodynamics.

We observed a similar optimal range of exposures that minimized the surface roughness of the silicon overlayer during medium (575°C) and low (500°C) temperatures growth. We explained this based on kinetics.

#### 1.2.5 Summary

In summary, we improved the surface morphology of silicon grown on calciumfluoride in an effort to make the silicon/calciumfluoride material system a basis for quantum device integration on silicon substrates. We reduced the roughness of silicon grown on CaF<sub>2</sub>/Si using electron beam assisted molecular beam epitaxy. We found that the roughness of the silicon overlayer was minimized by exposing the CaF<sub>2</sub> to an electron dose of 1.0 mC/cm<sup>2</sup> in the high temperature case (650°C) before growing the epitaxial silicon overlayer. The medium (575°C) and low (500°C) temperature samples showed smoother surfaces at the cost of crystalline quality. The AFM results were consistent with the LEED and XPS data. We presented a simple model based on thermodynamics which explained the data well in the high temperature case. An explanation based on kinetics was put forward for the low and medium temperature cases.

Although these results indicate that it is currently impractical to manufacture RTDs, which require thin smooth films of silicon on CaF<sub>2</sub> through electron irradiation of the CaF<sub>2</sub> surface and kinetic constraints, there is some hope for this

material system. The most fruitful approach would probably be to find a substance that could either lower the Si-CaF<sub>2</sub> interface free energy or passivate the silicon surface during the growth. Hydrogen and antimony might be interesting candidates.

### 1.3 The $Si/Si_{1-y}C_y$ Material System

#### 1.3.1 Background

Looking at column IV of the periodic system (C, Si, Ge, Sn, Pb), we see that one might consider alloys of the first two (C, Si) with one of the larger atoms (Ge, Sn, and perhaps Pb) a potential material system that would be suitable for silicon based electronics. Here, we consider the first three (C, Si, and Ge). Since the crystal structure is the same for these elements (diamond) and lattice constants increase monotonically ( $a_C$ =0.3567 nm,  $a_{Si}$ =0.543 nm, and  $a_{Ge}$ =0.5658 nm), it might be possible to generate device quality alloys that would be perfectly lattice matched to a silicon substrate.

Unfortunately, carbon does not easily mix with the other materials. The C-Ge phase diagram shows that the mutual solubilities are negligible and there is no evidence of germanium carbide formation[13]. Similarly, the solid solubility for carbon in silicon is in the range of  $10^{-3}$  to  $10^{-4}$  atomic %. However, in this case there is formation of silicon carbide and its many poly types. In contrast to the carbon alloys, the silicon germanium phase diagram shows no such miscibility gap. Thus, it is no surprise that while SiGe alloys with a wide range of composition have been grown on silicon substrates[15], high crystal quality  $Si_{1-y}C_y$  alloys have been grown only for small y[14].

#### 1.3.2 Potential Applications

In addition to the RTDs mentioned earlier, the SiGe/Si material system has produced devices such as HJBTs and p-channel FETs using the valence band offset. For a recent review of these devices, see Whall[15]. One of the main limitations of the system is that strain always have to be taken into account since SiGe alloys will have larger lattice constants than silicon. Another limitation is that while the valence band offset is large enough for device applications, the conduction band offset is negligible. The reason for this is that the compositional shift of the conduction band cancels the shift due to strain, when SiGe is grown coherently strained to silicon. While conduction band offsets can be achieved in the  $Si/Si_{1-x}Ge_x$  system by growing tensile-strained layers on relaxed  $Si_{1-x}Ge_x$  buffer layers, the incorporation of carbon may provide this desirable feature without the substantial defect densities and complicated processing inherent for growth on relaxed buffer layers.

By introducing carbon into the system, the cancellation mentioned above could perhaps be removed. The carbon could be used to increase the lattice constant of a SiGeC alloy to match the silicon and thus reduce the strain in the system. This would remove the shift in the conduction band due to strain and leave the system with a compositional shift in the conduction band which could lead to a significant conduction band offset. This offset would then open up the possibilities for electron, as opposed to hole, based devices such as n-RTDs without having to use strained layers.

#### 1.3.3 Growth

As mentioned earlier, the miscibility gap in the C-Si binary alloy phase diagram make it difficult to grow these alloys with the carbon concentration required to obtain a substantial conduction band offset. We have found that surface of the growth roughens during MBE growth of  $Si_{1-y}C_y$  on silicon(100) for carbon concentrations larger than 2%. To eliminate this roughening we employed a technique

called surfactant assisted MBE.

### Surfactant Assisted Growth of $Si_{1-y}C_y$

In surfactant assisted MBE one adds an adsorbate, the surfactant, either before or during the growth. In general, the surfactant could play many roles. It could change the surface free energies of the materials at the growth front, relieve strain, or change the growth kinetics as to improve the growth. I think it is fair to say that the atomic level processes are not yet well understood. In our case we used Sb as a surfactant to reduce the roughening mentioned above.

To test the effectiveness of the Sb as a surfactant, we grew Si/Si<sub>0.97</sub>C<sub>0.03</sub> superlattices on Si(001) substrates by surfactant assisted molecular beam epitaxy (MBE) and characterized them by *in situ* reflection high energy electron diffraction (RHEED), atomic force microscopy (AFM), transmission electron microscopy (TEM), and high resolution x-ray diffraction (HRXRD). The RHEED showed that, in absence of Sb, the growth front roughers during Si<sub>0.97</sub>C<sub>0.03</sub> growth and smoothens during subsequent Si growth.

In contrast, when Sb was present, the growth front remained smooth throughout the growth. We confirmed this observation by cross-sectional (TEM) which revealed that for samples grown without the use of Sb, the Si/Si<sub>0.97</sub>C<sub>0.03</sub> interfaces (Si<sub>0.97</sub>C<sub>0.03</sub> on Si) were much more abrupt than the Si<sub>0.97</sub>C<sub>0.03</sub>/Si interfaces. In the case of Sb assisted growth, there were no observable difference in abruptness between the two types of interfaces. AFM micrographs of the Si<sub>0.97</sub>C<sub>0.03</sub> surface revealed features that could be the source of the roughness observed by RHEED and TEM.

Although our experiment gave no direct evidence on exactly what goes on at the growth front, we think that the surfactant changed the growth kinetics rather than energetics in this case. This is the case in the Sb assisted growth of germanium on silicon[6]. The reason for this is that the change in surface free

energy due to the carbon probably is fairly small considering that the carbon concentration was only about 3%. Furthermore, a reduction in the surface free energy of the  $Si_{0.97}C_{0.03}$  layer would lead to increased islanding, contrary to our observation. Instead, we think that one or more of the species in the carbon flux disrupted the epitaxial growth of  $Si_{0.97}C_{0.03}$  on Si. These species formed surface nucleation centers where diffusing adatoms could incorporate in competition with surface steps, resulting in 3D growth.

All of the multiple carbon species, which remained undissociated on the surface, are potential candidates for having nucleated the rough growth. The diffusion length of these dimers and trimers is expected to be negligible compared to that of the monomers because of the large activation energy due to the bond bending and stretching required for a dimer or trimer to move on the surface. Thus, while the monomers might diffuse to a step and thus contribute to step flow growth, the dimers or trimers will incorporate at the site of impingement and form nucleation centers.

The nucleation center density generated by the dimers and trimers was large enough for 3D growth to dominate over 2D step flow growth. We speculate that in the case of Sb assisted growth, where the surface stayed smooth throughout the growth, the surfactant assisted growth mechanism prevented the dimers and trimers from forming effective nucleation centers. The primary role of the Sb was to ride as a surface layer burying the carbon dimer and trimers. Although there was some Sb incorporation during growth, as measured by Rutherford backscattering spectrometry<sup>1</sup>, the concentration of the incorporated Sb was too small to provide significant strain relief for the Si<sub>0.97</sub>C<sub>0.03</sub> layers. Instead the growth kinetics was most likely modified. An impinging silicon adatom diffused on the Sb-layer until it reached a proper site. At that site, the adatom underwent an exchange with a surfactant atom and incorporated. Again, the carbon clusters did not diffuse on the

<sup>&</sup>lt;sup>1</sup>We would like to thank Maggie Taylor for the RBS measurement and analysis.

surface, rather they were incorporated immediately by some exchange mechanism. Since direct contact between Si adatoms and the carbon clusters was reduced, the clusters no longer served as effective nucleation centers and the growth stayed relatively smooth as shown by AFM and the streaked RHEED pattern.

#### 1.3.4 Summary

In order to grow smooth layers of high carbon content (larger than 2% carbon) silicon carbon on silicon, we employed surfactant assisted molecular beam epitaxy using Sb as the surfactant. The silicon/silicon carbon, like the silicon/calciumfluoride material systems could be used to integrate quantum devices like RTDs on standard silicon substrates. We grew Si/Si<sub>0.97</sub>C<sub>0.03</sub> superlattices on Si(001) substrates and characterized them by *in situ* RHEED, AFM, TEM, and HRXRD. The RHEED showed that, in absence of Sb, the growth front roughened during Si<sub>0.97</sub>C<sub>0.03</sub> growth and became smooth again during subsequent Si growth.

In contrast, when Sb was present, the growth front remained smooth throughout the growth. We confirmed this observation by TEM which revealed that for samples grown without the use of Sb, the  $\mathrm{Si/Si_{0.97}C_{0.03}}$  interfaces ( $\mathrm{Si_{0.97}C_{0.03}}$  on Si) were much more abrupt than the  $\mathrm{Si_{0.97}C_{0.03}/Si}$  interfaces. In the case of Sb assisted growth, there were no observable difference in abruptness between the two types of interfaces. AFM micrographs of the  $\mathrm{Si_{0.97}C_{0.03}}$  surface revealed features that could be the source of the roughness observed by RHEED and TEM.

Thus, the surfactant assisted growth method worked well for  $Si_{0.97}C_{0.03}$  growth on silicon(100). This result, if it can be extended to higher carbon concentrations, could greatly extend the reach of the SiGeC material system.

## Bibliography

- [1] Hiroshi Ishiwara and Tanemasa Asano, Appl. Phys. Lett. 40(1), 66 (1982).

- [2] Leo J. Schowalter and Robert W. Fathauer, CRC Critical Reviews in Solid State and Materials Sciences 15 (4), 367-421 (1989).

- [3] Tanemasa Asano, Shinichi Wakabayashi, and Hiroshi Ishiwara, J. Appl. Phys. 55(10), 3566 (1984).

- [4] R.W. Fathauer, N. Lewis, L.J. Schowalter, and E.L. Hall, J. Vac. Sci. Technol. B 3(2), 736 (1985).

- [5] Seigo Kanemaru, Hiroshi Ishiwara, and Seijiro Furukawa, J. Appl. Phys. 63 (4), 1060 (1988).

- [6] H.C. Lee, H. Ishiwara, S. Furukawa, K. Saiki, and A. Koma, Applied Surface Science 41/42, 553 (1989).

- [7] R. Tsu and L. Esaki, Appl. Phys. Lett. 22, 562 (1972).

- [8] L.L. Chang, L. Esaki and R. Tsu, Appl. Phys. Lett. 24, 593 (1974).

- [9] D.A. Collins, "Growth And Characterization of Novel, III-V Semiconductor Heterostructures," Ph.D. diss., California Institute of Technology, 22 (1993).

- [10] K. Ismail, B.S. Mayerson, P.J. Wang, Appl. Phys. Lett. **59**(8), 973 (1991).

- [11] U. Gennser, V.P. Kesan, S.S. Iyer, T.J. Bucelot, and E.S. Yang, J. Vac. Sci. Technol. B 8(2), 210, (1990).

- [12] Kouji Miura, Kazuhiko Sugiura, and Hiroshi Sugiura, Surface Science Letters 253, L407 (1991).

- [13] Thaddeus B. Massalski, ed., Binary Alloy Phase Diagrams, vol 1 2nd edition, ASM International, 849 (1990).

- [14] K. Eberl, S.S. Iyer, J.C. Tsang, M.S. Goorsky, and F.K. Legoues, J. Vac. Sci. Technol. B 10(2), 934, (1992).

- [15] T.E.Whall and E.H.C. Parker, J. of Mat. Sci.: Materials in Electronics 6, 249 (1995).

- [16] H. J. Osten, Appl. Phys. Lett. **64**, 2356 (1994).

### Chapter 2

## Introduction to the SRAM/MISS

#### 2.1 Introduction

In this chapter, we introduce the third topic of the thesis – the static random access memory (SRAM) based on a memory cell consisting of a metal insulator semiconductor switch (MISS) in series with a resistor. This SRAM was originally proposed by Harold Levy[2]. We provide background and motivation for the theoretical and experimental study of the influence of oxide thickness on the I/V of the MISS device presented in chapter 5. We will motivate the research by describing current limitation of the conventional SRAM architecture and describe Harold's new approach based on the memory cell mentioned above. In addition to describing the device and the cell, we will also discuss the appropriate reading and writing addressing schemes. Finally, we will provide an overview of the detailed oxide thickness study.

#### 2.1.1 Background

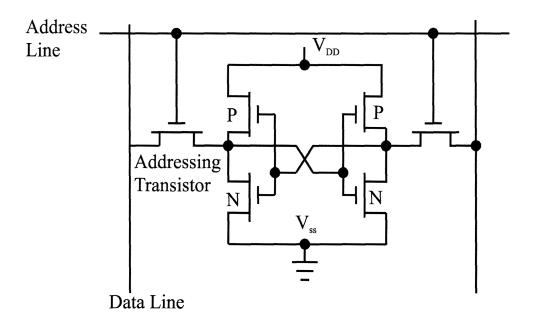

The standard static random access memory (SRAM) cell is large and fast. As you can see in Fig. 2.1, it takes at least four transistors to make the cell itself and then another transistor to address the cell. The addressing transistor is necessary as

Figure 2.1: The conventional SRAM cell consists of a bistable flip-flop made of four transistors. The two extra addressing transistors serve to isolate the cell from the other cells in the memory. A bit is sensed by detecting a certain amount of charge (around 100fC). As the memory cell can source a large amount of current through the saturated transistors, it is fast.

the bit is stored as a voltage state of a bistable flip-flop and thus would short out, unless isolated. A bit is sensed by detecting a certain amount of charge (around 100fC). Thus, the time it takes to detect whether the bit is one or zero is inversely proportional to the current sourced by the memory cell. As the memory cell can source a large amount of current through the saturated transistors, it is fast.

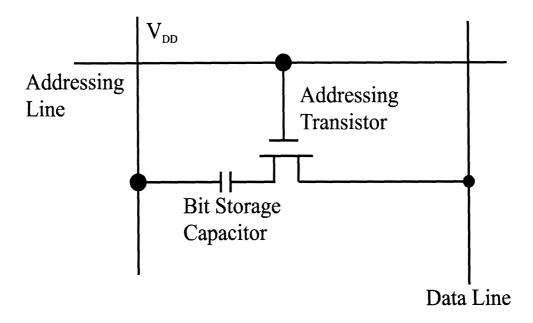

A dynamic random access (DRAM) memory cell is, au contraire, small and slow. The design consists of a capacitor and an isolation transistor (see Fig. 2.2). The reason for the cell being slow is that the current is limited by the discharge characteristics of a capacitor; i.e., the current decays exponentially. Another problem with this design is that the cell has to be refreshed as the capacitor slowly leaks out the stored charge.

Figure 2.2: The conventional DRAM cell consists of a capacitor and a transistor. The addressing transistor isolates the cell from the other cells in the memory. The cell is small, but slow due to the discharge characteristics of the capacitor.

Given the need for large amounts of fast memory, current memory architecture relies on fast, but expensive, on-CPU-chip SRAM cache memory and off-chip large and relatively cheap DRAM memory. This way, most of the CPU reads and writes are serviced fast while a large amount of memory is available. The benefit of our approach is that the SRAM density can be increased by a factor of about 20. This would allow up to 5MB of SRAM cache on a CPU instead of today's 256kB. Or, one could decrease the area now used for SRAM which is up to 50% now to less than 5%. If our revolutionary memory design could be fabricated at a cost similar to that of standard SRAM, there could be an immediate worldwide commercial demand for the product.

Figure 2.3: The SRAM memory cell based on a MISS.

#### 2.1.2 The Memory Cell

The basic memory cell in our scheme is a metal insulator semiconductor switch (MISS) in series with a resistor where the bit is stored in current state rather than a voltage state. This allows for a transistor less addressing scheme leading to a fast memory with a small footprint.

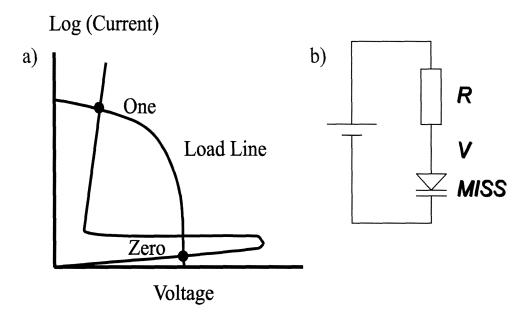

The MISS, invented some 24 years ago by Yamamoto[1], is a two terminal device with an current-voltage (I/V) curve which exhibits a high and a low impedance state, as seen in Fig. 2.3a. The simple memory cell is shown in Fig. 2.3b with the load line solution depicted in Fig. 2.3a. The low current state would correspond to a "zero" and the high current state to a "one." The memory would be built by arranging these cells in a grid with proper addressing electronics along the sides of the grid.

Figure 2.4: Reading the memory cell.

#### 2.1.3 Addressing Scheme

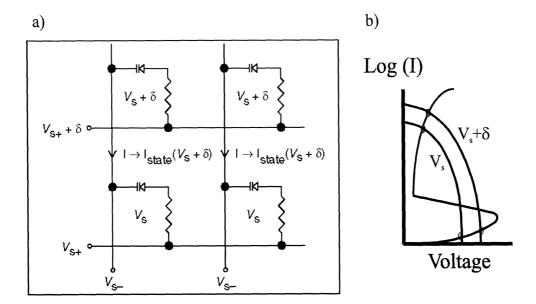

#### Read

To read the cell, say the one in the upper left corner in Fig. 2.4, one would bias the corresponding horizontal line slightly higher than the quiescent bias required to maintain the state and then measure the current in the left vertical line. If the state were a "one," then the slight increase in voltage would result in a large increase in the current and thus a large amount of charge delivered to the sense amplifier which would read a "one". On the other hand, if the state were a "zero," the current would hardly increase, leading to a zero state being read. The time it would take to read the state would be determined by the charge necessary to detect a "one" divided by the amount of current sourced in the "one" state.

#### Write

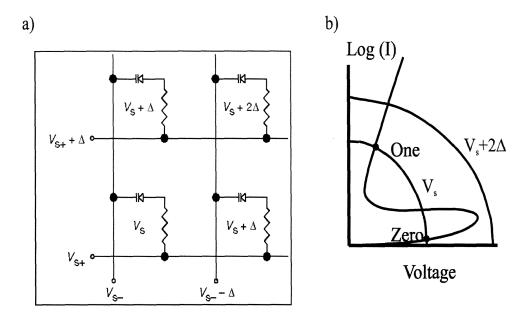

To write a "one" to the upper right cell in Fig. 2.5, one would bias the corresponding horizontal and vertical lines positively  $(+\Delta)$  and negatively  $(-\Delta)$  respectively.

Figure 2.5: Writing to the memory cell.

The cell would see a  $2\Delta$  increase in bias, which would be large enough to switch the state from a "zero" to a "one." The other cells on the vertical and horizontal lines in question would only see a bias of  $\Delta$  which would not be enough to change their states. To write a "zero" the biases would be reversed.

### 2.2 MISS Experiment

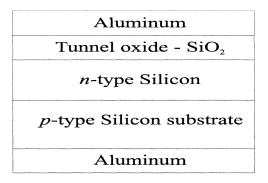

The device consists of a metal/SiO<sub>2</sub>/Si(n)/Si(p<sup>+</sup>)/metal structure (see Fig. 2.6, where the insulator is thin enough to pass a direct tunnel current, but not so thin that holes cannot accumulate at all.

Although the metal insulator semiconductor switch had been investigated for quite some time, there had been no systematic report on the influence of the oxide thickness on the I/V curve. In chapter 5 we describe our experiment determining this dependence both experimentally and by simulation.

We fabricated four types of metal insulator semiconductor switches where the

### Device Structure

Figure 2.6: The MISS device consists of a thin insulator layer on an n-p (or p-n) junction. The top and back contacts are made of aluminum. The figure is not drawn to scale.

only intentional difference was the thickness of the oxide. There were three processing steps. First, we cleaned a silicon chip consisting of n-type Si epi on a p-type Si substrate. Next, we grew the oxide by rapid thermal oxidation. Finally, the contacts were sputtered and defined by photolithography.

The I/V curve showed the expected switching behavior although the details such as switching currents and voltages did not agree with simulations. Despite the disagreement between the experiment and the theory, we found that the simulation provided some insight to how the device operates. We observed that the I/V curves of these devices are very sensitive to the oxide thickness. The onset of the negative resistance region in the curve is so sensitive to the electron and hole tunneling currents that these devices could be used to characterize ultra thin oxides.

Another important observation was that the I/V curve changed after the first switching event and then remained fairly constant. Extremely high current densities  $(10^3 \text{ A/cm}^2)$  could be driven through the ultra thin oxides without changing the device characteristics. We believe this is the highest, non-destructive current density through an oxide reported to date.

### 2.3 Summary

In this chapter, we introduced a static random access memory (SRAM) concept in which a Metal Insulator Semiconductor Switch (MISS) device is the basis for the memory cell. We showed that this device, in series with a resistor, could be used with a transistor less addressing scheme to increase the SRAM density by a factor of 20 compared to current technology.

The influence of the oxide thickness on the I/V curve of the MISS device was studied both experimentally and by simulation, and we found that the I/V curve showed the expected switching behavior although the details such as switching currents and voltages did not agree with simulations. Despite the disagreement between the experiment and the theory, the simulation provided some insight into how the device operates. We observed that the I/V curves of these devices are very sensitive to the oxide thickness.

Another important observation was that the I/V curve changed after the first switching event and then remained fairly constant. Extremely high current densities  $(10^3 \text{ A/cm}^2)$  could be driven through the ultra thin oxides without changing the device characteristics. We believe this is the highest, non-destructive current density through an oxide reported to date.

Although the fabricated devices still need to be refined in order to serve as the basis for an SRAM with acceptable specifications in terms of power consumption and speed, we have showed that this approach to increasing SRAM density is promising.

# **Bibliography**

- [1] H.J. Levy, "Application and Intergration of Quantum-Effect Devices for Cellular VLSI," Ph.D. diss., California Institute of Technology, 89 (1995).

- [2] T. Yamamoto and M Morimoto, Appl. Phys. Lett. 20, 269 (1972).

## Chapter 3

# Surface Morphology of Silicon Grown on CaF<sub>2</sub>/Si By Electron Beam Assisted MBE

### 3.1 Introduction

### 3.1.1 Chapter Abstract

The surface morphology of silicon, grown on epitaxial CaF<sub>2</sub>/Si by electron beam assisted MBE, is studied using atomic force microscopy (AFM), x-ray photoelectron spectroscopy (XPS) and low energy electron diffraction (LEED). We find an optimal range of electron beam exposure for high temperature (650°C) growth of the silicon overlayer that minimizes the roughness of the silicon overlayer. The observed hexagonally shaped microcrystals formed by the silicon during high temperature growth are explained by a simple model based on thermodynamics.

We observe a similar optimal range of exposures that minimizes the surface roughness of the silicon overlayer during medium (575°C) and low (500°C) temperatures growth. We present an explanation for this based on kinetics.

### 3.1.2 Motivation and Background

As discussed in chapter 1, one way of realizing ultra dense digital memory circuits, neural networks, and high speed electronics is to integrate quantum devices such as resonant tunneling diodes which exhibit negative differential resistance with standard VLSI silicon circuitry. The  $Si/CaF_2$  material system is a promising candidate for this integration effort since the lattice mismatch is small (0.6% at room temperature) and the crystalline structures are similar. Another application of this material system is as the insulator in silicon on insulator. Consequently, the system has been studied extensively and it has been found that while  $CaF_2$  grows in a two dimensional epitaxial fashion on silicon (111), silicon islands on  $CaF_2$  [1]. In this chapter, we report on our efforts to reduce the tendency of the silicon to island by using a technique known as electron beam assisted molecular beam epitaxy (EB MBE). This technique has been used to improve growth of both Ge [2] and GaAs [3] on  $CaF_2$ , but as far we know, there has not been any reports, apart from our own [4][5], on its use in growth of silicon on  $CaF_2$ .

In EB MBE, the  $CaF_2$  surface is exposed to electrons to desorb fluorine from the  $CaF_2$ , prior to silicon overgrowth. It has been shown that low energy electron radiation desorbs fluorine as  $F^+$  from  $CaF_2(111)$ , creating a calcium rich surface with an ordered array of surface F-centers[6]. A detailed mechanism for the desorption process which involves excitations of the Ca 3p core level has been proposed by Chakarian [7]. The array of F-centers will have a higher surface free energy than the normal  $CaF_2$  surface and should thus favor 2D growth or at least lower the contact angle in 3D growth of silicon on  $CaF_2$ .

### 3.1.3 Outline of Chapter

In the experimental section we describe the sample structure and growth. LEED, AFM, and XPS data is presented in the characterization section, and in the discussion section we explain these results using a simple thermodynamical model for

the high growth temperature case and an argument based on kinetics for the low temperature results. In the final section, we summarize the results and suggest future directions for research is this area.

### 3.2 Experiment

### 3.2.1 Sample structure

The samples consist of three layers: 50 nm silicon on 10 nm CaF<sub>2</sub> on a 100 nm thick silicon buffer grown on a silicon (111) wafer. The reason for choosing a thick CaF<sub>2</sub> layer is to prevent the electron beam from penetrating it. Early TEM studies showed that 10 nm is sufficient for this purpose. Since the AFM measurements were performed in air, we chose a relatively thick (50 nm) silicon overlayer to ensure that the surface features due to oxidation are about a factor of 10-50 times smaller than the features due to the electron beam exposure.

### 3.2.2 Sample preparation

### MBE Growth

Before growth, we degreased the 2 inch (boron doped,  $3 \times 10^{18}$  cm<sup>-3</sup>) silicon wafer and dipped it in a 25% HF solution in order to remove the contaminated native oxide and terminate the surface with hydrogen. Samples were grown at three different substrate temperatures during silicon deposition. The high temperature sample was grown at 650°C, the medium temperature sample at 575°C, and the low temperature sample was grown at 500°C. During CaF<sub>2</sub> deposition, the substrate temperature was kept at 700°C for all samples. Each wafer was exposed to the electron beam at four different locations in order to reduce scatter in the data due to variations in surface preparation and growth conditions. The total time required for the 4 exposures was about 1.5 hours for each sample. The background

pressure in the MBE machine was about  $10^{-9}$  Torr during electron beam exposure and  $10^{-8}$  Torr during growth. The deposition rates were 0.05 nm/s for the silicon growth and 0.04 nm/s during CaF<sub>2</sub> growth.

### Electron Beam Exposure

The buffer layer exhibited the customary sharp 7x7 LEED pattern. This pattern changed to the expected 1x1 pattern after the  $CaF_2$  had been deposited. To expose the surface, we defocused the LEED beam to a spot diameter of about 4 mm and set the dose rate to  $0.85 \ \mu\text{A/cm}^2$  for the samples with doses ranging from zero to  $1.0 \ \text{mC/cm}^2$  and  $12 \ \mu\text{A/cm}^2$  for the samples with doses ranging from  $0.5 \ \text{to} \ 50 \ \text{mC/cm}^2$ . The dose rate was measured by shuttering the electron beam and measuring the current from the shutter to ground. The LEED pattern remained the same during the exposure (except the spots were larger due to the defocusing) for the doses up to  $1.0 \ \text{mC/cm}^2$ . The unchanging LEED pattern shows that the surface remains ordered, indicating that the F-centers created by fluorine desorption form an ordered array [6]. For higher doses the LEED pattern lost contrast, which we interpret as a disordering of the  $CaF_2$  surface by the electron irradiation. The low temperature silicon overlayer exhibited a weak  $1\times1$  whereas the medium and high temperature silicon overlayers exhibited strong 1x1 patterns. In all cases, the spot size was larger than that of the silicon buffer layer.

### 3.3 Characterization

### 3.3.1 Atomic Force Microscopy

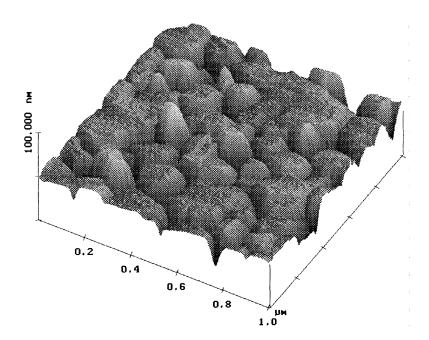

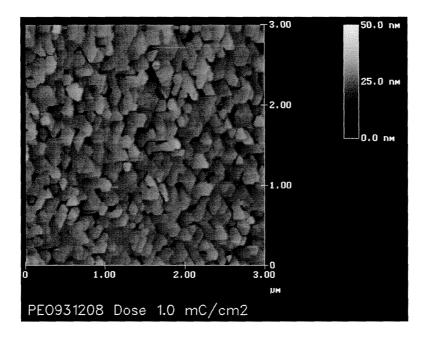

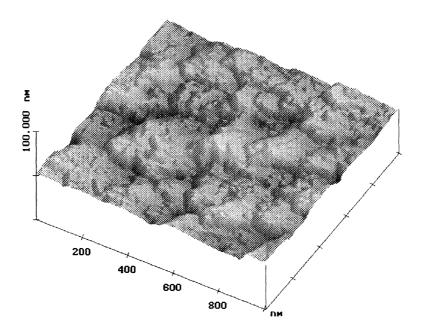

Figure 3.1 shows a 3D view of the surface morphology (as measured by AFM) of the silicon overlayer grown at high temperature with zero electron dose (since there are electron guns in the MBE system, there is a background of electrons, but this dose is compared to the doses used in this experiment). As you can see in the

Figure 3.1: AFM micrograph of silicon grown on CaF<sub>2</sub>(111) by standard MBE at high temperature (650°C). This 3D view emphasizes the roughness of the silicon layer; note that the scale along the x and y axes are 10 times that of the z axis. Given that the nominal thickness of the silicon overlayer is 50 nm, one sees that the silicon is not wetting the CaF<sub>2</sub>; there are islands and the coverage is incomplete. The 2D view of the same sample, shown in figure 3.2, emphasizes the hexagonal shape of the islands.

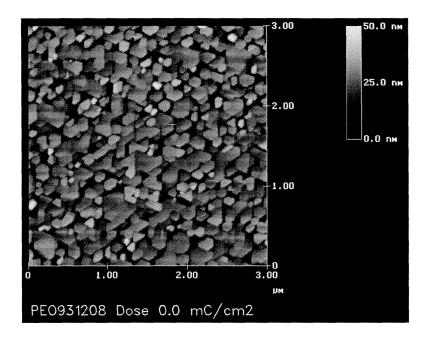

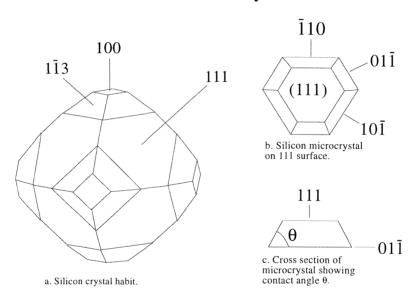

2D view (figure 3.2), the islands are about 100-300 nm in diameter and many are hexagonal. The sides of the islands are aligned along what we believe to be the {011} directions of the substrate.

The contact angles (defined in figure 3.8c) of the islands vary over a large range (0°-50°). This variation is probably due to the fact that the islands are in various stages of coalescing at the Si/CaF<sub>2</sub> interface. Experimentally we see that, in general, the stronger the coalescence, the lower the contact angle. "Free standing faces," faces that are comparatively far from other islands, have a contact angle of  $39^{\circ} \pm 5^{\circ}$ .

The surface morphology of the zero electron dose medium temperature sample is similar to that of the zero dose high temperature sample, except that the typical

Figure 3.2: AFM micrograph of silicon grown on  $CaF_2(111)$  by standard MBE at high temperature (650°C). This 2D view shows that many of the islands are hexagonal and that sides of the islands are aligned along what we believe to be the  $\{011\}$  directions of the substrate.

island size is smaller (100 - 200 nm diameter).

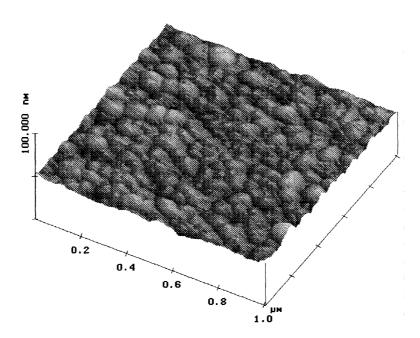

Figure 3.3 shows the morphology of the silicon overlayer grown at low temperature with zero electron dose. Unlike the high and medium temperature samples, this sample has no well defined islands and the silicon overlayer appears to cover the CaF<sub>2</sub> completely.

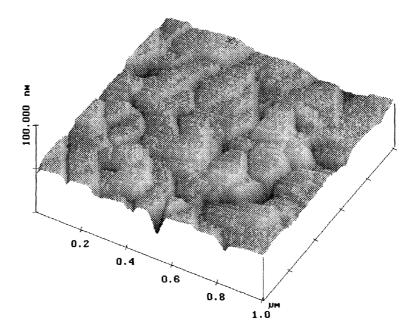

The surface morphology of the high temperature sample irradiated with a dose of  $1.0 \text{ mC/cm}^2$  is shown in figure 3.4. The islands have the same general shape and size distribution as in the high temperature zero dose case, as you can see in figure 3.5, but they have coalesced to a large degree and the surface is much smoother than that of the zero dose. There are fewer islands that are comparatively far from other islands and thus the contact angles are smaller; for the "free standing faces" the contact angles are  $32^{\circ} \pm 5^{\circ}$ .

The island shape changes in the medium temperature case with an electron dose

Figure 3.3: AFM micrograph of silicon grown on CaF<sub>2</sub>(111) by standard MBE at low temperature (500°C). In contrast to the high temperature case (figure 3.1), there are no well defined islands and the surface is relatively smooth.

Figure 3.4: AFM micrograph of silicon grown on CaF<sub>2</sub>(111) by EB MBE at 650°C. Dose 1.0 mC/cm<sup>2</sup>. Compared to the zero dose case (figure 3.1), this sample appears smoother although it still is islanded.

Figure 3.5: AFM micrograph of silicon grown on CaF<sub>2</sub>(111) by EB MBE at high temperature (650°C). Dose 1.0 mC/cm<sup>2</sup>. This 2D view shows that the islands have the same hexagonal shape as the non irradiated high temperature sample (figure 3.2).

of 1.0 mC/cm<sup>2</sup>. As you can see in figure 3.6, the islands have lost their hexagonal shape. The triangular shapes are due to the morphology of the underlying CaF<sub>2</sub>. The smoothest overlayer was obtained with an electron dose of 0.5 mC/cm<sup>2</sup> in the low temperature case, but the difference in roughness and morphology between this case and the zero dose case is small.

The high temperature and high electron dose cases can be characterized as follows. At a dose of 10 mC/cm<sup>2</sup>, the islands are shapeless, tall and spaced far apart. The islands do not to seem to have any specific crystal faces, instead their shape appears to be flattened spheres. In general, they stand about 50 nm tall with base diameter of about 200 nm and the spacing between them is about 2.5  $\mu$ m. All of these values are rough means with large (50% of mean) standard deviations. The surface between the islands does not show any specific crystalline faces either. The reason for this change in surface morphology is probably due to the CaF<sub>2</sub>

Figure 3.6: AFM micrograph of silicon grown on  $CaF_2(111)$  by EB MBE at medium temperature (575°C). Dose 1.0 mC/cm<sup>2</sup>. At this temperature, the silicon surface seems to be continous (the hexagonal islands have disappeared). The triangular shapes are due to the morphology of the underlying  $CaF_2$  layer.

surface being randomized by the electron beam as indicated by the LEED. At a dose of 50 mC/cm<sup>2</sup>, there are 40 nm deep triangular pinholes spaced about 1  $\mu$ m apart instead of islands. The surface between the holes also shows triangular features. Again, we think that the damage done to the CaF<sub>2</sub> during the electron beam exposure is the reason for this change in surface morphology.

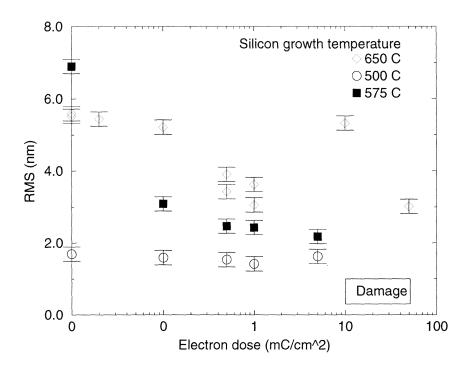

Since the histograms of the AFM micrographs acquired in the constant force mode are unimodal and gaussian-like, the root mean square (RMS) of the data is a good measure of the surface roughness. The measured roughness depends not only on the surface morphology, but also on the magnitude of the force, the scanning rate, and the condition of the tip. Thus, to ensure that the measurements were quantitatively comparable, we used a small repulsive force (8 - 25 nN) and a slow scan rate (15 min/image). To check for tip modification, we scanned a calibration sample between each roughness measurement. Figure 3.7 shows that the roughness is significantly lower for the irradiated samples in the high temperature case (the lines drawn in the picture are there only to guide the eye). The roughness exhibits a broad minimum followed by an increase in roughness at 10 mC/cm<sup>2</sup>. In the medium temperature case, the roughness also decreases with increased electron dose. In the low temperature case, the roughness has a broad but shallow minimum around 1.0 mC/cm<sup>2</sup>.

### 3.3.2 X-ray Photoemission Spectroscopy

The  $CaF_2/Si$  XPS peak ratios for the high temperature case, shown in table 3.1, support the notion that the silicon nearly covers the  $CaF_2$  in the 1.0 mC/cm<sup>2</sup> case whereas the coverage is incomplete in the zero dose case. The fluorine/silicon ratio is largest in the zero dose and diminishes significantly for the 1.0 mC/cm<sup>2</sup> surface. After sputtering about 3 nm, the calcium and fluorine peaks vanish in all but the zero dose case. This is consistent with the model that the zero dose morphology consists of tall islands with valleys between whereas the  $CaF_2$  surface in the 1.0

## Surface roughness versus electron dose

Figure 3.7: In this figure, we show RMS of the silicon overlayer versus the electron dose used in the EB MBE growth step for three different substrate temperatures. For the high and medium temperature cases, we see that there is a large improvement in terms of roughness for electron doses around 1 mC/cm<sup>2</sup>. The roughness increases at a dose of 10 mC/cm<sup>2</sup> due to damage to the CaF<sub>2</sub> layer caused by the electron dose. At 50 mC/cm<sup>2</sup>, the damage is more severe and the surface morphology is completely different. The surface is relatively smooth in the low temperature case and there is no significant change in surface morphology due to the electron dose.

Table 3.1: Calcium to silicon and fluorine to silicon XPS peak ratios of silicon grown on CaF<sub>2</sub> using electron assisted MBE (EB MBE) at high temperature (650°C). The dose refers to the electron dose used in the EB MBE growth. The samples were sputtered about 3 nm; the table shows the ratios both before and after the sputtering.

| Dose        | Ca/Si       |              | F/Si        |              |

|-------------|-------------|--------------|-------------|--------------|

| $(mC/cm^2)$ | pre sputter | post sputter | pre sputter | post sputter |

| 0           | 0.45        | 0.07         | 0.45        | 0.13         |

| 1           | 0.30        | 0            | 0.07        | 0            |

| 10          | 0.33        | 0            | 0.14        | 0            |

| 50          | 0.33        | 0            | 0.04        | 0            |

$mC/cm^2$  case is nearly completely covered with silicon. The tall islands might shield the  $CaF_2$  during sputtering, thus only the zero dose case shows calcium and fluorine peaks after sputtering. The calcium to silicon ratio is about the same for all samples before sputtering which is explained by the fact that calcium is known to surf on top of silicon [8]. The AFM micrographs show that there are valleys that probably reach down to the  $CaF_2$  layer in the zero dose case, but not in the  $1.0 \ mC/cm^2$  case. Since this agrees well with the model explaining the XPS data, we conclude that the silicon almost covers the  $CaF_2$  completely in the  $1.0 \ mC/cm^2$  case whereas the coverage is incomplete in the zero dose case.

At 10 mC/cm<sup>2</sup>, in the high temperature case, the pre sputter fluorine to silicon XPS peak ratio increased from the value at 1 mC/cm<sup>2</sup>. Since we expect the fluorine to silicon ratio to decrease monotonically with increased electron dose in the absence of shadowing effects, the increase in the ratio is most likely due to less complete coverage. This is supported by the extraordinary islanding observed by AFM. At 50 mC/cm<sup>2</sup>, the pre sputter fluorine to silicon XPS peak ratio decreases. This is probably due to the large electron dose having desorbed most of the fluorine.

### 3.4 Discussion