# A Wide Bandwidth Pulsar Timing Machine

Thesis by

José Navarro

In Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

California Institute of Technology Pasadena, California

> 1994 (Submitted May 27, 1994)

© 1994 José Navarro All rights reserved

Typeset with  $\LaTeX$ .

# Abstract

Pulsar timing has turned millisecond pulsars into powerful tools for the study of neutron star physics, time-keeping, astrometry, the interstellar medium and binary systems. It uses millisecond pulsars as probes of the gravitational fields of their companions, of globular clusters and of the Galaxy, and provides information on the dynamics of the solar system. It has also confirmed predictions of general relativity, for which Joe Taylor and Russell Hulse received the 1993 Nobel Prize in Physics. Vasts amounts of information are expected as the current searches continue to discover new millisecond pulsars.

This thesis describes the design and construction of the Caltech Fast Pulsar Timing Machine and some preliminary results at the Parkes Observatory. The FPTM is a wide band timing machine built around a digital correlator for long-term timing stability and has a large observing bandwidth to time millisecond pulsars at high radio frequencies, where propagation effects are minimized.

It is the combination of the 128 MHz bandwidth, the 512 lag digital correlator and the 1024 period phase bins with a minimum size of 2.7  $\mu$ s that gives the FPTM its power. The large bandwidth makes new observations of faint pulsars possible above 1 GHz, where current receivers easily provide radio signals with more than 100 MHz of bandwidth. The large number of channels reduces the dispersion smearing of distant millisecond pulsars, which often defines the timing floor in timing systems, and the 1024 phase bins of 2.7  $\mu$ s or more ensure that the pulsar profile is adequately sampled.

The FPTM is currently at Parkes Observatory, in Australia, where we are undertaking a long-term precision timing program for millisecond pulsars. We frequently observe the bright binary millisecond pulsar J0437-4715 with sub-microsecond times-of-arrival, and have already found interesting features in the pulse profile that could not be resolved with previous timing systems. Nevertheless, we still find drifts in the timing residuals of as much as a few  $\mu$ s over several hours which we do not yet understand (even though they are also seen by the other timing system at Parkes!). We are confident that we will solve these residuals and consistently time PSR J0437-4715 at the level of 100 ns or better.

We also present the discovery of J0218+4232, a very luminous binary field millisecond pulsar. Its 2.3 ms pulsations were only detected after an exhaustive search that involved building new hardware.

# **Preface**

Six years ago I visited Caltech as a prospective graduate student. I was impressed with Shri's research and resolved to read more about pulsars. I had been taught about neutron stars with superfluid interiors and exotic particle cores, and suddenly I could see pulsars as observable sources of which we catch only a glimpse every period. And it is ironically the short pulses that convey so much information about the neutron star within, and of what is between it and us.

Shri's plans to build a pulsar timing machine were starting to sound more and more interesting, indeed fascinating. The number of things we could study with such an instrument were almost too good to be true! It was going to be a large project, so I started working on it right away, with the hopes of finishing the hardware in time to get exciting scientific results before graduating.

I thought we were building the first timing machine, that we were starting a completely new field of astrophysical research. I didn't know that pulsar timing machines already existed, and I was greatly disappointed when I found that out. Indeed many discoveries had already resulted from pulsar timing, and it seemed that we were just going to make better measurements, but not study anything new.

As it turns out, however, the characteristics of the FPTM are such that we can study new regions of parameter space and discover new phenomena, in addition to timing pulsars more accurately. The main strength of the FPTM lies in the combination of a wide bandwidth, a large number of channels and very fine time resolution. These aspects, combined with its digital nature and resulting long-term stability, make the FPTM an unmatched precision pulsar timing system.

# Acknowledgments

First and foremost, I would like to thank my advisor Shri Kulkarni for getting me involved with pulsars when I first came to visit Caltech and keeping that initial enthusiasm alive over the past six years with a constant deluge of new and exciting projects. I admire his deep knowledge of observational techniques and his ability to identify and attack a target or a project whose time has come. It's been difficult to remain sane sometimes, but it was nothing that hitting a volleyball a little harder couldn't fix. I have tried to learn as much as possible from him and hope to continue having the chance.

Building the FPTM has been an enormous project, and I would like to acknowledge several people who have made it possible. Shri himself has contributed more than his fair share of inspiration, perspiration and money. Steve Padin at OVRO has helped above and beyond the call of duty, fixing digitizers every time we managed to break one and offering advice over E-mail and the telephone when we were stranded in remote islands. Mark Hodges, Russ Keeney and Tim Clark put up with us during our visits to OVRO; Nick Scoville and Tony Readhead made the telescope and other observatory resources available to us; and John Marzano built wooden crates for the machine strong enough to survive two trips around the world and the jungles of Puerto Rico. My thanks too to Igor Lozenicins for helping out with the grunt work in the early stages, and to Reini, Roxanne, Dave Woody and the remaining people who made OVRO a home away from home.

Jagmit Sandhu has redesigned and built new modules for the FPTM, and will soon replace the dual channel IF subsystem with a quad channel system that will make dual frequency, dual polarization possible. He is inheriting the machine, and I am happy to pass along some of the successes as well as the headaches. I wish him good luck.

I am grateful to Dick Manchester, Matthew Bailes, Jonathon Bell and Andrew Lyne for their assistance at Parkes, especially Matthew, who has joined Shri, Jagmit and me deep inside the machine and has taken responsibility for the new data reduction package. I look forward to a fruitful and happy collaboration with the Parkes team in the coming years.

I have learned a lot from astronomers and engineers in other institutions. I want to thank Don Backer, Dan Werthimer, Mike Davis, Daniel Altschuler and Joe Taylor for their encouragement years ago when I had started building the FPTM and could not yet see the light at the end of the tunnel; Dave Fort and Miller Goss for trusting me with their MkIII VLBI recorders; John Middleditch for putting up with a \$90k tab in supercomputer charges; Ger de Bruyn, Dale Frail and Andrew Lyne for their collaboration in the discovery of a binary millisecond pulsar; and above all, Dale, for sharing his enthusiasm on radio astronomy and freshness and altruism in collaborations. I won't forget the freezing nights at the VLA site working with the HTRP, compiling the observing program as the telescopes slew toward the source and having it work on the first try.

Numerous trips to observatories have contributed to my happiness at Caltech, and I would like to salute and thank the friends I have made while traveling. In particular, to Norberto Despiau who made observing too much fun with his stories, don't forget Doña Panchita or else. Thanks to Willy, Willie, Angel and Rey for keeping me alive in the late night hours, to Tony for the double rations of arroz con guinea and to Tony Phillips for not retreating in front of a malta grande. I am also grateful to Marilyn and the maintenance crew, who taught me how to speak Spanish properly, before and after a bottle of Chinchón, and for the many games of dominoes.

I have loved Caltech from the very beginning, and will miss it. Ever since Nick, Wenge and I took Tom as an office refugee, life in the office was more fun than anywhere else except perhaps at Pie & Burger every Monday after turning in the problem set (don't forget that I was the closest to 60%). I don't think I could have found a better companion than Will for the years that we lived in the radio lab. We spent so many hours down in the basement, in front of and behind the computers! I have gained four great friends and I am sorry that we are leaving in different directions. Perhaps we'll meet upstairs in a few years...

I want to thank the people who have made life in Pasadena more exciting: my roommate Dave who builds clocks of the other kind, Candy, Sandi and Alicia, Diane and Gitta, and Helen who can find anything that's ever been written. Also Andy, Mike and Maureen, my partners in crime; Steve, for the water hole and the snakes; and Helen Johnston, for her affable personality. Gautam got closer to giving me an ulcer than Shri ever managed, but has also been a constant source of spontaneity that I appreciate. And thanks, Todd, for holding on to the rope every time I peeled, and for suggesting the trip that led to the rescue and some free gear, if not a romantic dinner.

This thesis is dedicated to my parents, for their love and support over the past twentynine years, and to my sisters, who came to visit me when I was too busy to visit them.

# Contents

| Al | bstract                                                                                                                                                                                                                                                                                                                                                                                                       | iii                                                                 |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| Pr | reface                                                                                                                                                                                                                                                                                                                                                                                                        | iv                                                                  |

| 1  | Introduction  1.1 Millisecond Pulsars  1.2 Timing Observations  1.3 Pulsar Timing  1.3.1 Period and Period Derivative  1.3.2 Position and Frame Tie  1.3.3 Proper Motion and Parallax  1.3.4 Dispersion in the Interstellar Medium  1.4 Precision Timing of Millisecond Timing  1.5 A Survey of Pulsar Timing Machines  1.6 The Caltech Fast Pulsar Timing Machine  1.7 The New Millisecond Pulsar J0218+4232 | 1<br>1<br>1<br>3<br>4<br>4<br>4<br>5<br>6<br>6<br>7<br>8<br>9<br>12 |

| 2  | Technical Design of the FPTM  2.1 Introduction                                                                                                                                                                                                                                                                                                                                                                | 14<br>14<br>15<br>16<br>18<br>19                                    |

| 3  | The Millisecond Binary Pulsar J0437-4715 3.1 Introduction                                                                                                                                                                                                                                                                                                                                                     | 21<br>22<br>23<br>25<br>26                                          |

| 4  | Discovery of a Luminous Binary Millisecond Pulsar 4.1 Introduction                                                                                                                                                                                                                                                                                                                                            | 29<br>29<br>30<br>32                                                |

| 5  | The IF Rack 5.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                  | 37<br>37<br>38<br>38                                                |

CONTENTS

|    |              | 5.2.2 The Upconverter                          | 9 |

|----|--------------|------------------------------------------------|---|

|    |              | 5.2.3 The Baseband Converter                   |   |

|    |              | 5.2.4 Sample Calculations of the Sky Frequency |   |

|    | 5.3          | Power Levels                                   | 5 |

| _  | an I         |                                                |   |

| 6  |              | Digitizer Module 4                             |   |

|    | $6.1 \\ 6.2$ | Introduction                                   |   |

|    | 6.3          | The Digitizer ALCs                             |   |

|    | 6.4          | The Threshold Monitors                         |   |

|    | 6.5          | Count Rates in the Digitizer Module            |   |

|    | 6.6          | Digitizer Tests                                |   |

|    | 0.0          | 2.5.0.0.0.0.0.0.0.0.0.0.0.0.0.0.0.0.0.0.       | 1 |

| 7  | The          | Correlator 5                                   | 2 |

|    | 7.1          | Introduction                                   | 2 |

|    | 7.2          | The Correlator Clocks                          | 3 |

|    | 7.3          | The Correlator Chip                            | 4 |

|    | 7.4          | The JPL Accumulator Chip                       |   |

|    | 7.5          | Correlator Rates                               |   |

|    | 7.6          | Clock and Data Issues                          | 8 |

| 8  | The          | Pulsar Backend 6                               | ^ |

| O  | 8.1          | Pulsar Backend Introduction                    |   |

|    | 8.2          | Folding at the Pulsar Period                   |   |

|    | 8.3          | The Ramadder Boards                            |   |

|    |              | 8.3.1 The RAW Cycles                           |   |

|    |              | 8.3.2 The Maximum Phase Bin Size               |   |

|    |              | 8.3.3 The Output Memories                      |   |

|    |              | 8.3.4 Count Rates in the Ramadder Boards 6     | 7 |

|    |              | 8.3.5 Cross Talk and Double Buffering          | 8 |

|    | 8.4          | The Control Board                              | 9 |

|    |              | 8.4.1 Generating the Pulsar Spin Frequency     |   |

|    |              | 8.4.2 The Start of an Observation              |   |

|    | 0.5          | 8.4.3 Intrinsic Timing Accuracy                |   |

|    | 8.5          | Clock and Data Issues                          | 2 |

| A  | The          | VMEbus 72                                      | 1 |

|    | A.1          | Overview                                       |   |

|    |              | A.1.1 VMEbus Formats                           |   |

|    |              | A.1.2 Termination                              |   |

|    |              | A.1.3 Master and Slave Interfaces              |   |

|    |              | A.1.4 Read and Write Cycles                    |   |

|    |              | A.1.5 Interrupts                               | 9 |

|    | A.2          | The Technical VMEbus                           | 9 |

|    |              | A.2.1 Read and Write Cycles Revisited          | 0 |

|    |              | A.2.2 Interrupts Revisited                     |   |

|    | A.3          | The FPTM VMEbus Interface                      | 2 |

| В  | The          | PIO Board 84                                   | 1 |

| ر. | B.1          | Introduction                                   | _ |

|    | B.2          | Receiving Data                                 | _ |

|    | B.3          | Sending Data                                   |   |

|    | B.4          | Addressing the PIO Board                       |   |

|    |              |                                                |   |

| CONTENTS | ix |

|----------|----|

|          |    |

|              | B.5<br>B.6 | The Status Register              | 86<br>87 |

|--------------|------------|----------------------------------|----------|

| $\mathbf{C}$ | The        | Digital Interface                | 89       |

|              | C.1        | Introduction                     | 89       |

|              | C.2        | Data Flow Overview               |          |

|              | C.3        | Technical Description            | 90       |

|              | C.4        | History of the Digital Interface | 93       |

| $\mathbf{D}$ | The        | Buffer Board                     | 94       |

|              | D.1        | The Front-Panel Input            | 94       |

|              | D.2        | The VMEbus Output                |          |

|              | D.3        | Memory Switching                 | 95       |

|              | D.4        | Selftest Features                |          |

|              | D.5        | Internal Registers               | 96       |

|              | D.6        | Internal Functions               | 97       |

|              | D.7        | CPU Control of the Buffer Board  |          |

|              | D.8        | History                          | 98       |

|              | D.9        | Modifications to the Rev.A PCB   | 99       |

| $\mathbf{E}$ | The        | FPTM at Parkes                   | 100      |

|              | E.1        | Introduction                     | 100      |

|              | E.2        | AC Power                         | 100      |

|              | E.3        | Signal Termination               | 100      |

|              | E.4        | Power Levels                     | 101      |

|              | E.5        | Voltage Levels                   | 101      |

|              | E.6        | The Artificial Pulsar Generator  | 102      |

| $\mathbf{F}$ | Glos       | ssary                            | 103      |

| Bi           | bliog      | raphy                            | 106      |

# List of Figures

| 1.1                             | Synchronous Folding of the Pulsar Signal    | 2                    |

|---------------------------------|---------------------------------------------|----------------------|

| 2.1                             | A Block Diagram of the FPTM                 | 17                   |

| 3.1<br>3.2<br>3.3               | Single Night Timing Residuals With the FPTM | 22<br>23<br>27       |

| 4.1<br>4.2                      | P-band Images of PSR J0218+4232             | 31<br>33             |

| 5.1<br>5.2                      | Downconversion of the 2.4 GHz Band          | $\frac{40}{41}$      |

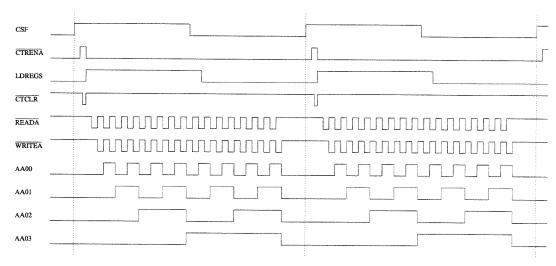

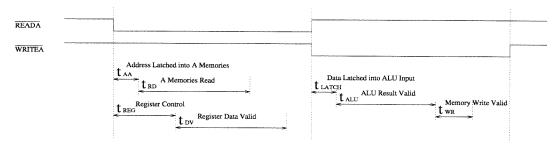

| 7.1<br>7.2<br>7.3               | The Heart of the Correlator                 | 53<br>57<br>59       |

| 8.1<br>8.2<br>8.3<br>8.4<br>8.5 | From Correlator Data to Pulse Profiles      | 61<br>63<br>65<br>66 |

# List of Tables

| 1.1                             | Comparison of Timing Systems                             | 0               |

|---------------------------------|----------------------------------------------------------|-----------------|

| 4.1<br>4.2                      |                                                          | 5<br>6          |

| 5.1<br>5.2<br>5.3               | Sample Setups for the IF Chain                           | 9<br>3<br>5     |

| 6.1<br>6.2                      |                                                          | 9               |

| 7.1<br>7.2                      |                                                          | 4               |

| 8.1                             | Control Signals for the Ramadder Boards                  | 0               |

| A.1<br>A.2<br>A.3<br>A.4<br>A.5 | VMEbus P1 Layout7VMEbus P2 Layout7Address Modifier Bits8 | $5\\6\\7\\0\\1$ |

| B.1<br>B.2                      |                                                          | 6<br>6          |

| C.1<br>C.2<br>C.3               | An Example                                               | 2               |

| D.1<br>D.2<br>D.3               | The Control Register                                     | 7               |

| E.1                             | AC Power Budget                                          | 1               |

| F.1                             | Glossary                                                 | 9               |

# Chapter 1

# Introduction

#### 1.1 Millisecond Pulsars

More than 600 pulsars have been found since PSR B1919+21 was discovered in 1967 by Jocelyn Bell and Anthony Hewish (Hewish et al. 1968). In 1982 a new class of pulsars was revealed with the discovery of the first millisecond pulsar B1937+21 (Backer et al. 1982). They have short periods ( $\leq 20$  ms) and small magnetic field strengths ( $\leq 10^9$  G). We believe that millisecond pulsars are spun up to short periods by accretion of matter from a companion. Indeed many of them are in binary systems with low-mass companions (see Bhattacharya and van den Heuvel 1991 and references therein).

Millisecond pulsars are even better clocks than ordinary pulsars, with rotational stabilities in some cases as small as 1 part in 10<sup>14</sup> (Kaspi, Taylor, and Ryba 1994). This, combined with the fact that their short periods make it possible to measure the pulse times-of-arrival (TOAs) to great accuracy, makes them attractive targets for precision timing observations and the subject of numerous searches (see the review in Camilo 1994).

In this chapter we review the basic principles of pulsar timing, the main scientific objectives of millisecond pulsar timing, and the current state of the art of timing pulsars.

# 1.2 Timing Observations

To "time a pulsar" is to record the times of arrival of its pulses. A time-of-arrival, or TOA, is a time tag that we attach to one of the pulses from the pulsar. It is not necessary to measure a TOA for every pulse that we receive, and indeed in most cases single pulses are too weak to be detected above the noise. Instead, one observes for a few minutes and obtains one global TOA that corresponds to a pulse near the middle of the integration.

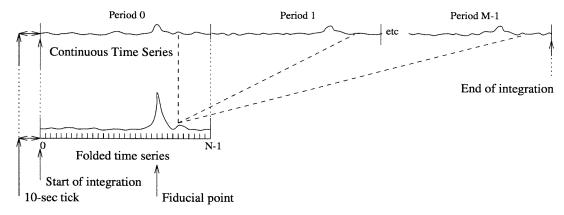

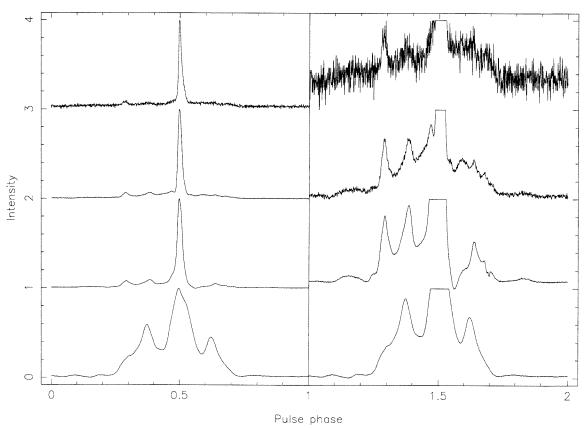

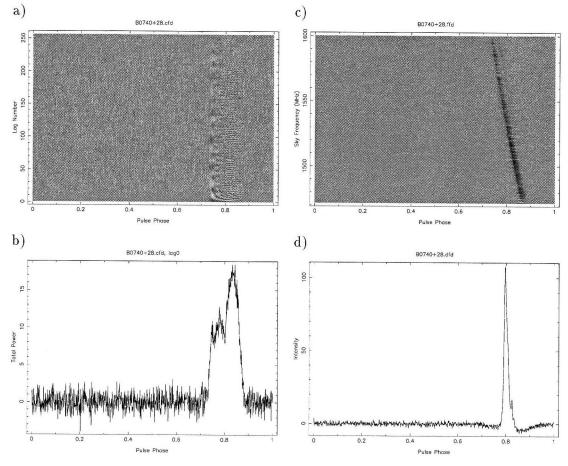

The observations involve folding the pulsar signal synchronously with the pulsar period, so that one ends up with a single pulse profile per frequency channel (figure 1.1). The TOA of that integrated, single pulse is the sum of the start time of the observation and the offset

#### Figure 1.1: Synchronous Folding of the Pulsar Signal

The data from each channel is folded synchronously with the pulsar period into a number of bins (N). The pulse arrival time from that integration is obtained from the start time (the time of the 10-sec tick plus a small, measurable offset) and the offset to the fiducial point in the profile. The location of the fiducial point is found by crosscorrelation of the profile with a standard template.

between the first bin of the pulse profile and the pulse peak. To minimize the effects of errors in the pulsar model, the TOA is normally referred to a period near the middle of the integration instead of the beginning.

A list of TOAs and observing frequencies is obtained after a series of observations, from which a better pulsar model can be derived by means of the TEMPO package (Taylor et al. 1976). TEMPO transfers the topocentric TOA to the solar system barycenter and removes the pulsar's binary orbit if necessary, after which the TOAs should be exact multiples of the pulsar period, with a small growing delay due to the pulsar spin-down. The parameters of the timing model can be kept constant or fit to the input TOAs, depending on the nature of the data. For example, the pulsar dispersion measure can be easily obtained from dual frequency observations, but is best left fixed if the current TOAs are all at the same frequency and cannot provide any new information on the dispersion measure.

The precision of a TOA is given roughly by the pulse width divided by the signal-tonoise ratio of the observation. For the pulsar J0437-4715 a typical one-minute observation at 1500 MHz has an SNR of ~100, which with a main pulse width of 0.12 ms gives a TOA error of ~1.2  $\mu$ s. Longer integrations reduce the TOA error even further, but it is preferable to start a new observation as soon as the single-point TOA gets to an estimated precision near 100 ns, to get an independent timing point and check the internal consistency of the pulsar timing system.

# 1.3 Pulsar Timing

The pulse arrival time  $t_b$  at the solar system barycenter (SSB) can be derived from the topocentric arrival time t from (Taylor and Weisberg 1989)

$$t_b = t + (\mathbf{r} \cdot \hat{\mathbf{n}})/c - D/f_b^2 + \Delta_{E\odot} - \Delta_{S\odot}. \tag{1.1}$$

In this equation  $t_b$  is measured at the barycenter in units of barycentric dynamical time (TDB) and t is measured at the topocenter in terrestrial dynamical time (TDT).  $\hat{\mathbf{n}}$  is a unit vector toward the pulsar,  $\mathbf{r}$  is a vector from the SSB to the phase center of the telescope at the time of observation, and c is the speed of light.  $\Delta_{E\odot}$  is the solar system "Einstein delay," the combined effect of gravitational redshift and time dilation due to Earth's motion, and  $\Delta_{S\odot}$  is the "Shapiro delay" caused by propagation of the pulsar signal through curved spacetime near the Sun (Shapiro 1964).

The term  $D/f_b^2$  removes the dispersive delay and converts the arrival time to infinite frequency. The observing frequency  $f_b$  is expressed in the rest frame of the SSB, and the dispersion constant D is given by

$$D = \frac{e^2}{2\pi mc} \int_0^d n_e dl \equiv \frac{\text{DM}(\text{cm}^{-3}\text{pc})}{2.41 \times 10^{-16}} \text{ s}^{-1},$$

(1.2)

where DM is the "dispersion measure" due to the column density of free electrons toward the pulsar.

The conversion of t to  $t_b$  requires the pulsar position and a model of the solar system, but it is the pulse *phase* as a function of barycentric time that conveys the remaining information about the pulsar. The pulse phase  $\phi(t_b)$  at any given time is given by

$$\phi(t) = \phi_0 + \nu_0(t - t_0) + \frac{1}{2}\dot{\nu}(t - t_0)^2 + \frac{1}{6}\ddot{\nu}(t - t_0)^3 + \dots$$

(1.3)

where  $\phi_0$  is the pulse phase at  $t = t_0$ , and  $\nu(t) = 1/P(t)$  is the (observed) spin frequency of the pulsar and  $\dot{\nu}$ ,  $\ddot{\nu}$  its derivatives with respect to time. The subscript on barycentric times has been dropped for clarity.

The spin frequency  $\nu$  and its time derivatives are relatively simple functions of time in the case of isolated pulsars (Manchester and Taylor 1977), but can be extremely complicated for binary systems. We will look at this again in the next section, where we explore the applications of pulsar timing in terms of equations (1.1)–(1.3).

The scientific applications of precision pulsar timing are many, and have been extensively reviewed in the literature (see Backer and Hellings 1986, Ryba 1991 and references therein). We now briefly explain how each application is derived from the TOAs at the barycenter and the magnitude of each effect.

#### 1.3.1 Period and Period Derivative

The periods of some millisecond pulsars are known to 1 part in  $10^{14}$  because the individual TOAs can be measured to  $\sim 1~\mu s$  over many years, and  $1~\mu s/yr = 3.2 \times 10^{-14}$ . Period derivatives as small as  $10^{-25}$  s/s can also be measured. In the case of J0437-4715, which we use as an example, the integrated delay on the pulse arrival times over one year of observations due to  $\dot{P}$  would be, from equation (1.3):

$$-\Delta\phi(t) \approx -\frac{1}{2} \dot{\nu} t^2 = \frac{1}{4} \frac{\dot{P}}{P^2} t^2 = \frac{1}{4} \frac{1.2 \times 10^{-19}}{(5.7 \text{ ms})^2} (1 \text{ yr})^2 = 3.9 \text{ periods},$$

(1.4)

or 22.6 ms in one year. This delay is easily observable.

There are several terms that can contribute to the apparent  $\dot{P}$ : the intrinsic  $\dot{P}$  itself, which is always positive and has values between  $10^{-12}$  and  $10^{-20}$  or smaller; the Shklovskii effect due to transverse motion (Shklovskii 1970), which can be significant for fast, nearby pulsars and perhaps the closest known pulsar PSR J0108-1431 (Tauris  $\epsilon t$  al. 1994); and any acceleration caused on the pulsar by strong gravitational fields such as those felt by globular cluster pulsars.

The Shklovskii term has been measured for a few millisecond pulsars (Camilo, Thorsett, and Kulkarni 1993). Once its effect is removed from the apparent  $\dot{P}$ , the intrinsic  $\dot{P}$  and the intrinsic characteristic age  $\tau = P/2\dot{P}$  are known. This effect should be observable in most of the new millisecond pulsars that have been recently discovered and not yet timed.

Some globular cluster pulsars present negative apparent period derivatives. Both the intrinsic  $\dot{P}$  and the Shklovskii  $\dot{P}$  are positive, so any measured negative  $\dot{P}$  must be due to acceleration by the cluster, and gives a lower limit to that acceleration. Phinney 1992 has used the measured negative  $\dot{P}$  to explore the gravitational potentials of clusters.

Equation 1.4 reflects one of the properties of pulsar timing: that the timing residuals produced by an incorrect model can increase as a nonlinear function of time. As a result, while the linear ones like period will improve as  $t^{3/2}$  (a factor of t for time and a factor of  $t^{1/2}$  for the increase in SNR), some of the pulsar parameters will become much more accurate with time. Other parameters, like DM, only get better as  $t^{1/2}$  because the only contributing factor is the number of observations.

#### 1.3.2 Position and Frame Tie

Errors in the pulsar position result in sinusoidal timing residuals with a one year periodicity, the amplitude of which depends on where the pulsar is with respect to the ecliptic plane and can be expressed as

$$[\Delta t]^2 = [4.8 \ \mu s \ \cos \lambda \ \Delta \beta]^2 + [4.8 \ \mu s \ \sin \lambda \ \Delta \lambda]^2,$$

(1.5)

where  $\beta$  and  $\lambda$  are the ecliptic longitude and latitude and their errors are given in milliarcseconds. Several years of timing can produce extremely accurate pulsar positions (0.1 mas for B1937+21 and B1855+09 in Kaspi, Taylor, and Ryba 1994), sometimes better than the VLA or VLBI positions (and needing only a single radio dish). The timing solution is in ecliptic coordinates, while the interferometric position is in equatorial coordinates because it is based on Earth's rotation. The combination of the two positions ties the two coordinate systems and is a step toward what is called "reference frame tie."

Proper frame tie requires the positions of several pulsars distributed all over the sky to be determined very accurately with *both* timing and interferometry. The difficulty in improving the frame tie is that there are few pulsars that can be timed to positions better than 0.1 mas with both methods, as they must be fast for timing and bright for interferometry. The current pulsar searches are improving the prospects of pulsar astrometry by finding many new millisecond pulsars.

#### 1.3.3 Proper Motion and Parallax

A model error in the proper motion of a pulsar is equivalent to a position error that changes with time and produces annual sinusoidal residuals whose amplitude grows linearly with time. If we rewrite equation (1.5) as

$$\Delta t \approx 4.8 \ \mu s \ \Delta \rho, \qquad [\Delta \rho]^2 = [\cos \lambda \ \Delta \beta]^2 + [\sin \lambda \ \Delta \lambda]^2,$$

where  $\Delta \rho$  is a measure of the position error, still in milliarcseconds, then an error in the proper motion will correspond to a timing residual of

$$\Delta t = 4.8 \ \mu s \ \Delta \rho = 2.4 \ \mu \frac{\mu s}{\text{yr}} = 2.4 \ V_{10} \ d_{\text{kpc}}^{-1} \frac{\mu s}{\text{yr}},$$

(1.6)

where the proper motion  $\mu$  is given in mas/yr, and where  $V_{10}$  is the transverse velocity in units of 10 km/s and  $d_{\rm kpc}$  is the distance to the pulsar in kiloparsecs.

The distance to the pulsar can be measured through parallax, since parallax will also produce annual sinusoidal residuals:

$$\Delta t = 1.2 \cos \lambda \ d_{\text{kpc}}^{-1} \ \mu \text{s.} \tag{1.7}$$

Parallax is the only direct way to obtain the distance to a pulsar, and is instrumental to understanding the electron distribution in the local insterstellar medium. For example, the parallax measurements of PSR B1451-68 improved the estimate of the electron density in the direction of the pulsar from  $0.029\pm0.014$  cm<sup>-3</sup> (Salter, Lyne, and Anderson 1979) to  $0.019\pm0.003$  cm<sup>-3</sup> (Bailes *et al.* 1990).

Proper motion, when measured simultaneously with pulsar timing and interferometry,

is useful for understanding the relative orientation and rotation of the different solar system ephemerides in use. If combined with parallax measurements or more approximate distance estimators such as from interstellar scattering observations, proper motion gives the transverse velocity of the pulsar (eq. 1.6), which can be used to constrain pulsar formation scenarios (Phinney and Kulkarni 1994).

### 1.3.4 Dispersion in the Interstellar Medium

The term  $-D/f^2$  in equation (1.1) is a correction for the dispersion of the radio signals in the interstellar medium. This term is only quadratic, however, and does not correct the delays due to the interstellar medium perfectly. We can obtain a better estimate of the delay by deriving it from its source, the frequency-dependent group velocity of radio waves in a cold plasma (Manchester and Taylor 1977)

$$v_g = c (1 - \omega_p^2 / \omega^2)^{1/2}, \qquad \omega_p^2 = \frac{4\pi n_\epsilon e^2}{m_\epsilon},$$

(1.8)

from which we can calculate the travel time for a wave of frequency  $f = \omega/2\pi$ :

$$t = \int_0^d v_g dl \approx \frac{1}{c} \int_0^d dl + \frac{e^2}{2\pi m_e c} \int_0^d n_e dl \frac{1}{f^2} + \frac{3e^4}{8\pi^2 m_e^2 c} \int_0^d n_e^2 dl \frac{1}{f^4}$$

$$= \frac{d}{c} + \frac{\text{DM}(\text{pc cm}^{-3})}{2.41 \times 10^{-16}} \frac{1}{f^2} + \frac{\text{EM}(\text{pc cm}^{-6})}{4.00 \times 10^{-24}} \frac{1}{f^4}$$

where DM is the "dispersion measure" and EM is the "emission measure." If the plasma is magnetized, there will be a term depending on  $RM/f^3$ , where RM is the rotation measure and depends on the magnetic field along the line-of-sight. From Phillips (1992),

$$t = \frac{d}{c} + \frac{\text{DM(pc cm}^{-3})}{2.41 \times 10^{-16}} \frac{1}{f^2} + p \frac{\text{RM(rad m}^{-2})}{1.75 \times 10^{-17}} \frac{1}{f^3} + \frac{\text{EM(pc cm}^{-6})}{4.00 \times 10^{-24}} \frac{1}{f^4}$$

where p is +1 for RCP and -1 for LCP. The cubic and quartic terms are usually negligible except at very low frequencies f<100 MHz.

What is more important than the  $f^{-3}$  and  $f^{-4}$  terms is the time variability of the  $f^{-2}$  term, the dispersion term, which produces time-variable delays and residuals. One way to avoid contamination of the timing residuals from changes in dispersion is to measure the DM during every observation. This is impractical because it requires observations at two frequencies with the associated receiver change. Alternative, one can observe at very high frequencies alone, where the variations become smaller. The best solution altogether is to observe at two high frequencies to obtain the DM and to be immune from the other propagation effects. This is exactly what Kaspi, Taylor and Ryba (1994) do for PSR B1937+21. They alternate measurements at 1.4 and 2.4 GHz, and measure DM drifts

of 0.001 pc cm<sup>-3</sup> per year, which are equivalent to 1.5  $\mu$ s/yr at a frequency of 1.4 GHz. It is clear that observations at two frequencies are necessary for submicrosecond timing.

# 1.4 Precision Timing of Millisecond Timing

So far we have discussed the basic applications of pulsar timing. When the pulsar is in a binary system, the delays due to the motion of the pulsar within the binary orbit must be considered. In tight binaries with massive companions, general relativistic effects can be very important. Indeed this is a fruitful field of astronomy, and recently Joe Taylor and Russell Hulse were awarded the Nobel Prize for the discovery of the eccentric binary pulsar B1913+16, with which Taylor and co-workers were able to verify the radiative predictions of general relativity.

A number of new applications emerge from precision timing when the times-of-arrival can be measured at the microsecond level. As explained above, millisecond pulsars are ideal for these applications because of their short periods and inherent stability. Examples of these applications are the following:

- a) The use of TOAs to constrain or perhaps even detect a cosmic gravitational wave background (akin to the 3 K photon background). In the wavelength regime of  $10^6$ – $10^8$  s, the most sensitive method presently available for the detection of a stochastic background is timing of millisecond pulsars (Stinebring et al. 1990). The lower limit of  $10^6$  s is set by the integration time needed to beat down the residuals, and the upper limit of  $10^8$  s is determined by the uncertainties in the solar system ephemerides, which are needed to evaluate the large term  $(\mathbf{r} \cdot \hat{\mathbf{n}})/c$  in equation (1.1).

- b) The determination pulsar binary parameters including the masses of the companion, as in PSR B1855+09 (Thorsett et al. 1993). A similar and important application comes from the fact that in low mass systems, like J0437-4715, we do not expect any significant contribution to the orbital period derivative  $\dot{P}_b$  due to general relativity. The measured  $\dot{P}_b$  can be attributed entirely to the differential acceleration caused by the Galactic disk on the pulsar system and on the solar system, and can yield a unique constraint on the mass distribution of our Galactic disk.

- c) The determination of parallax to probe the large scale structure of the interstellar plasma. Proper motion measurements lead to space velocities which are fundamental toward understanding the formation of millisecond pulsars.

- d) Multi-frequency pulsar timing to probe the large scale structure of the interstellar plasma. The pulsar signal is scattered by irregularities in the ionized interstellar medium, which results in scatter broadening of the pulse features, and in stochastic shifts in the TOAs as the irregularities drift across our line-of-sight. Millisecond pulsars can be used to measure these shifts, and from the observed residuals one can derive the power spectrum

of the irregularities. Foster and Cordes (1990) discuss the limitations to pulsar timing due to interstellar scattering.

The ultimate limit to pulsar timing is naturally the pulsar itself. However, as stated earlier, it appears that millisecond pulsars, especially those with old ages (>10<sup>9</sup> yr, e.g., B1855+09) are essentially noiseless. If so, the limitations to precision timing are propagation in an irregular ISM, radiometric noise in the telescope receiver, and the pulsar timing backend. The first limitation can be overcome by timing pulsars at high frequencies where the scattering effects caused by the interstellar plasma become very small, and at two different frequencies if possible to remove all trace of variations in dispersion measure. The second limitation can be overcome with a timing machine capable of processing wide band signals, since radiometric noise is proportional to  $B^{-1/2}$ . Finally, the pulsar timing backend should be able to process the wide band signals and have many spectral channels and high time resolution. A fully digital system is favored since all the applications discussed above require long term stability.

All these considerations led us to the concept of a wide band digital correlator system for pulsar timing, specifically to be used to time pulsars at the highest possible frequency.

# 1.5 A Survey of Pulsar Timing Machines

Interstellar dispersion produces a frequency-dependent delay in the pulsar's signal. The detection of the signal collapses all the delays with the effective result of smearing the pulse profile. In the case of millisecond pulsars, the smearing can be so large as to completely wash out the pulsations and render the observation useless. The dispersion is reversible, however, if one can delay the different frequencies in the observing bandwidth by different amounts before adding them. This leads to several techniques for dedispersion that can be classified into two groups: coherent and incoherent dedispersion, also called pre-detection and post-detection dedispersion.

Coherent dedispersion applies a transfer function to the radio waves that exactly counters the dispersion from the interstellar medium. After coherent dedispersion one still possesses a radio signal that can be upconverted, downconverted, filtered or detected. It is the ideal way to dedisperse pulsar signals, but is difficult to do because of the extreme computational requirements. So far it has only been used in small bandwidth timing systems, and with a limitation to small dispersion measures. Don Backer at Berkeley is constructing a large bandwidth coherent dedispersion pulsar timing machine that uses custom VLSI technology.

Post-detection or incoherent techniques rely on passing the radio signal through a filterbank, detecting each channel separately and then adding them all with appropriate delays. These techniques are normally preferred over coherent dedispersion because filterbanks are relatively easy and inexpensive to make. However, filterbanks are analog devices and the passband shapes are variable from filter to filter and can change with time. The individual filter shapes must be measured regularly to account for the systematic delays introduced by scintillation through gradients of intensity as a function of observing frequency. As a result, filterbanks may lack long-term stability, which makes them potentially undesirable for long-term precision pulsar timing. An alternative to working in the frequency domain is offered by the correlator approach. A correlator-based pulsar timing system folds the autocorrelation (or crosscorrelation) function of the incoming signal at the pulsar period, instead of the individual frequency channels.

Table 1.1 shows the characteristics of the pulsar timing machines in use today. The highest time resolution is achieved with pre-detection systems, but they are limited to small bandwidths (except for the Berkeley CDRP, which will come on-line in the next few years). On the other hand, post-detection systems have larger bandwidths but are limited by their sampling rates and the relatively small number of channels.

# 1.6 The Caltech Fast Pulsar Timing Machine

The Caltech FPTM is a precision pulsar timing machine built around a wide band digital correlator. Its primary characteristics are a maximum input bandwidth of 128 MHz, a large number of channels (512 total) and excellent time resolution (a minimum of 2.7  $\mu$ s per phase bin). The 512 channels are actually 512 lags in the correlator, which can be converted into frequency channels prior to dedispersion during data reduction.

The FPTM correlator is very flexible and its 512 lags can be configured in many ways in groups of 64. The standard configurations are  $2\times256$  lags for pure timing observations and  $4\times128$  lags for polarization observations. More specifically, if L and R are the IF signals corresponding to the left and right circular polarizations, then standard timing observations use 256 lags for LL and 256 for RR to record only intensity in each polarization. On the other hand, polarization observations use 128 lags for each of LL, RR, LR and RL, from which the Stokes parameters I, V, Q, and U can be obtained.

The idea of a building a pulsar timing machine arose with the OVRO Millimeter Correlator. In most correlators the outputs of the multipliers are accumulated in the same chip that does the multiplications, and data are read out at most once every few milliseconds (the phase switching period in some interferometers). As a result, the time resolution of these correlators is poor, and cannot be used for millisecond pulsar timing. The OVRO correlator is different because the accumulation is done off-chip. Hence there is a point on the correlator boards between the correlator chips and the accumulator chips that we can tap to perform our own specialized, pulsar synchronous accumulation.

The Caltech Fast Pulsar Timing Machine was designed and built around the mm-array

#### Table 1.1: Comparison of Timing Systems

A comparison of the existing timing systems. The configurations listed here are those using the maximum bandwidth in two polarizations, with no sampling of the cross-polarizations. Maximum bandwidths are in MHz and minimum sampling times are in  $\mu$ s.  $N_{chan}$  is the number of channels across the entire bandwidth and  $N_{bins}$ , the number of phase bins across and entire pulse period. For short period pulsars  $N_{bins}$  is effectively decreased because the minimum phase bin size is  $\Delta t_{min}$ . The number of phase bins for a 1.5 ms pulsar is given in the next column. The type column lists the method used to break the spectrum into channels, and the pol column lists whether cross-polarization observations are possible.

FPTM: Caltech Fast Pulsar Timing Machine at Parkes; MK3-VLA: at the Very Large Array (Thorsett 1991); MK3-AO: Princeton Mark III system at Arecibo (Ryba 1991); MK3-GB: at Green Bank 85 ft (Stinebring et al. 1992); SP: Spectral Processor at Green Bank 140 ft (Fisher 1989); SP': New Spectral Processor (Fisher 1994); FPSM: Berkeley Fast Pulsar Search Machine at Arecibo (Backer et al. 1990); HTRP: High Time Resolution Processor at the VLA (McKinnon 1992); PKS-FB: Parkes Filterbank System, a search machine that can be used for timing (Johnston et al. 1993); AOC: Arecibo Correlator (Hagen 1987); MK3-CD: Princeton Mark III Coherent Dedispersion System (Ryba 1991); NSLO: Nançay Swept Local Oscillator timing machine at Nançay (Lestrade et al. 1990); CDRP: Berkeley Coherent Dispersion Removal Processor (Backer et al. 1994), which will be installed at the Green Bank 140 ft telescope.

| System    | $\mathrm{BW}_{max}$ | $\Delta t_{min}$ | $N_{chan}$                             | $N_{bins}$ | $N_{bins}^{1.5~\mathrm{ms}}$ | Type                    | Pol          |

|-----------|---------------------|------------------|----------------------------------------|------------|------------------------------|-------------------------|--------------|

| FPTM      | 128                 | 2.7              | 256                                    | 1024       | 561                          | corr                    | у            |

| MK3-VLA   | 46                  | 11.4             | 14                                     | 1024       | 131                          | filter                  | у            |

| MK3-AO    | 40                  | 11.4             | 16                                     | 1024       | 131                          | $\operatorname{filter}$ | у            |

| MK3- $GB$ | 16                  | 11.4             | 16                                     | 1024       | 131                          | filter                  | y            |

| SP        | 20                  | 12.8             | 256                                    | 128        | 117                          | fft                     | n            |

| SP'       | 10                  | 25.6             | 512                                    | 64         | 58                           | fft                     | n            |

| FPSM      | 40                  | 25.0             | 128                                    | 1024       | 60                           | corr                    | n            |

| HTRP      | 28                  | 140.0            | 14                                     | 1024       | 10                           | filter                  | У            |

| PKS-FB    | 320                 | 150.0            | 64                                     |            | 10                           | filter                  | у            |

| AOC       | 20                  | 500.0            | 128                                    | 1024       | 3                            | corr                    | У            |

| MK3-CD    | 4                   | 1.4              | _                                      | 8192       | 1071                         | pre-det                 | У            |

| NSLO      | 10                  | 1.2              | nume.                                  | 2500       | 1250                         | pre-det                 | $\mathbf{n}$ |

| CDRP      | 64                  | 1.0              | ************************************** | 1024       | 1024                         | pre-det                 | У            |

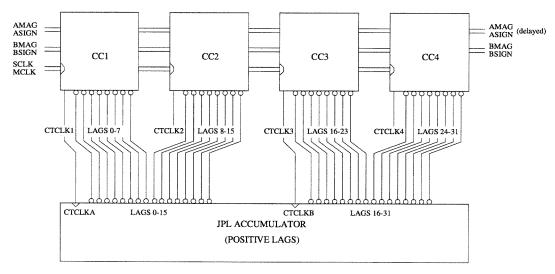

correlator chip. For this I had to clone one baseline of the correlator, which involved duplicating 8 correlator boards and all the support hardware. The correlator boards were especially challenging because of the high speed ECL signals, which at 256 MHz are very difficult to handle. I had to learn them inside out, and in the process of testing and debugging my copies of the boards I found and fixed some "bugs." The correlator boards are described in chapter 7.

The most important bug involved some swapped clocks, and was not important at low clock rates but prevented the boards from functioning above 220 MHz. The fix was to swap 18 pairs of signals per board by means of a socket-to-socket patch underneath the JPL accumulator chips. This happened at the same time that OVRO was putting together its first three correlator baselines, and they were able to take advantage of my modifications and observe with bandwidths larger than 110 MHz. The changes have now been incorporated into the printed circuit correlator boards (PCBs) that were built for the expansion of the mm-array to more than 3 antennas. The correlator boards had other problems, most of which were not fundamental but made operation more difficult. I found some design errors in the bus readout circuitry, that happened to work by chance. My changes were also incorporated in the new PCB version of the correlator boards.

I learned a lot about radio astronomy instrumentation when duplicating the modules associated with correlator, especially the digitizer and the clock generation and distribution modules, and the IF subsystem. While debugging the IF chain, starting with a noise source and ending with the digitizer, I found a bug in the digitizer which Steve Padin had independently found and fixed in the OVRO versions. Chapters 5 and 6 describe the IF subsystem and the digitizer.

Instead of a using a commercial VMEbus data I/O board to exchange data (and programs) between the correlator and control computers, I built my own digital I/O boards. This allowed me to give the PIO boards the features I wanted: choice of polled or interrupt driven, parallel digital buffered data and simultaneous input and output. The PIO board is described in appendix B. Learning the VMEbus well enough to design my own VMEbus boards was a painful process, and I summarize the essentials of the bus in appendix A to provide a reference more basic than the existing literature.

The PIO board is also used for the digital interface, a fan-out box with several modules that can be inserted into other boxes to provide computer control. Each control module contains two 32-bit registers that can be used in a synchronous or asynchronous way, and with two control lines per register for the instrument to be controlled. I designed the digital interface after realizing that having to set all the front panel switches by hand to configure the FPTM is impractical, especially if when trying to do remote observing. The digital interface gives the control computer complete power to configure the FPTM from the software. It is described in appendix C.

Most of the design effort went into the pulsar backend. From the hardware point of view, it involved building the ramadder boards and the control board. The ramadder boards are described in chapter 8 and were the most challenging, partly because I designed them early on when I had less experience, but also because they are quite complex per se. Each board must fold 2 Gbit of data per second from the associated correlator board, and it can only do so by being very parallel. The time resolution of 2.7  $\mu$ s per phase bin was hard to achieve, but it perfectly complements the qualities of the correlator for millisecond pulsar timing, as can be seen in table 1.1. It also made the control board harder to design, as the 60+ control signals that it provides to the ramadder boards have to be properly phased.

The software effort that went into the pulsar backend is considerable. After much consideration I decided to use OS9, a real-time operating system that looks much like Unix and runs in embedded computers. The observing programs are written in OS9/C and the data reduction package is in Unix/C. Part of the data reduction package was written by Will Deich (Deich 1994), but I had to provide interface for the FPTM data. The correlator computer also runs OS9, but off a ROM chip because it does not have a hard disk. The test and setup programs for the correlator are loaded into the correlator RAM via the PIO boards.

To date, the FPTM has observed pulsars at OVRO, Arecibo and Parkes. Each observatory has supplied a number of challenges, perhaps the biggest of which were the ground loops at Arecibo. Things are not good when plugging a BNC cable into the machine means a shower of sparks, or when lightning destroys your hard disk. However, each observing trip has been equally rewarding both on a personal level and from an astronomical point of view, and I hope they continue to be. Chapter 2.5 shows some of the results from Parkes.

## 1.7 The New Millisecond Pulsar J0218+4232

The original plan for my thesis was to search for new millisecond pulsars and simultaneously build the FPTM to time them. I started a pulsar search from Arecibo, but it was not very successful, and soon I was fully involved in the timing machine and had no time to continue with undirected searches.

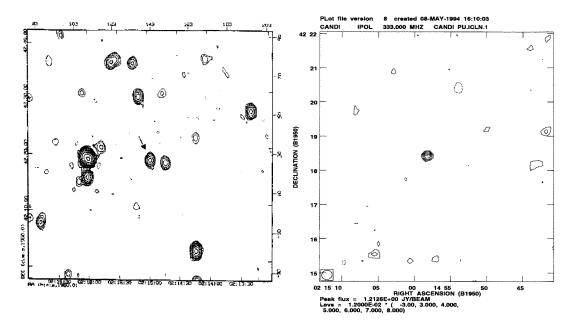

In 1991 we serendipitously discovered a highly polarized, compact radio source that had all the looks of a pulsar, and started a pulse search from the VLA. The fact that we didn't see any pulsations made the search all the more interesting, for now the pulsar had to be very fast or not at all, and this side project took a new intensity.

Unfortunately, this source lies just 4° North of the Arecibo declination range, and the pulsar search hardware available at the VLA was inadequate. We decided to try a completely new approach, for which I designed a new digital board to interface an OS9

computer to a MkIII VLBI recorder, and replay the MkIII baseband signals through the OS9 system an onto a Unix workstation where they could be analyzed. We eventually discovered the source to be a 2.3 ms pulsar in a 2 day binary orbit around a 0.15  $\rm M_{\odot}$  star. It is probably the most luminous known millisecond pulsar and it is presented in chapter 4.

# Chapter 2

# Technical Design of the FPTM

### 2.1 Introduction

The Fast Pulsar Timing Machine is a correlator-based pulsar timing machine with a maximum bandwidth of 128 MHz. It has an IF subsystem that operates in the range 0–1 GHz and converts the radio signals down to baseband, filters, a dual digitizer, a digital correlator and a pulsar backend that averages the correlator output.

The digital correlator is highly modular and can be configured in many ways. What is described here is the Parkes configuration of early 1994, with a dual IF subsystem, a fast digitizer, possible bandwidths of 2, 8, 32 and 128 MHz and a maximum of 512 lags. In this configuration, the 512 lags of the correlator can be organized for autocorrelation or crosscorrelation of the two input polarizations, in groups of 64 lags, and the lag data can be folded at the pulsar period into at most 1024 phase bins, with a minimum bin size of  $2.7 \mu s$ .

All the basic modules of the FPTM are described in detail in chapters 5–8 and appendices A–F. Many of the modules were cloned from the Owens Valley Millimeter Array, in particular the baseband converters, the digitizer, the clock generator, the clock distribution module and the correlator. Some of these we modified to suit our needs and repackaged in a more convenient form for the FPTM. Some we redesigned and improved on, like the clock generator and the clock distribution module, which we converted from gallium arsenide to ECLps technology when the new generation silicon chips first appeared. The pulsar backend was designed and built from scratch, with the hardware for communications and computer control, the artificial pulsar, and the software to test and run the entire timing machine.

The strength of the machine lies in the combination of all its parts: a wide bandwidth IF subsystem, a fast digitizer, a fast digital correlator with a large number of lags, and a pulsar backend with fine time resolution. In addition, the fact that it can easily be configured through software makes testing and observing easier. A sophisticated software

package already exists to analyze the timing data (Deich 1994), which we are extending to include polarization analysis and other routines specific for the FPTM.

# 2.2 A Historical Perspective

The idea of building a new pulsar timing machine occurred to my advisor Shri Kulkarni in 1987, at the same time that the Owens Valley Radio Observatory started to develop a large bandwidth digital correlator for its Millimeter Array (Padin  $\epsilon t$  al. 1993). M. S. Ewing was designing the high speed correlator chip, and was upset that he could not fit enough bits of accumulation inside the chip itself for lack of available gates. The limitations of ECL gate array technology at that time turned out to be a blessing for the timing machine project, for now external accumulation was necessary and it could be done in a pulsar synchronous manner (§7.3). Had it been possible to accumulate further in the correlator chip, it is very likely that the outputs would have been too slow to time millisecond pulsars.

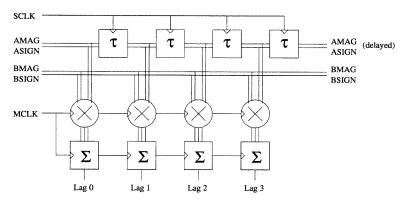

Marty Ewing, having worked on pulsars in the past (Filippenko, Readhead, and Ewing 1983), was also interested in the possibility of using the correlator for pulsar timing, and laid out the correlator boards with traces and connectors to make off-board accumulation possible. All we had to do was connect ribbon cables to the correlator boards and design a backend that would process the correlator data. No easy task, though, as the total output from the correlator amounts to no less than 2 Gbyte per second.

In 1988 we submitted a President's Fund Proposal for seed money to build the pulsar backend. The original proposal called for a 256 lag timing machine with 256 phase bins per period, and a double buffering scheme for reading out the folded data without interrupting the observations. This proposal was approved and we started to design and build the timing machine, adding on its capabilities when possible, until it became a 512 lag, 1024 phase bin monster. It currently weighs 1500 lbs!

The correlator requires a series of other modules in order to function, and with the help of the OVRO staff, we cloned most of those from the OVRO millimeter correlator project, mainly the baseband converter, digitizer, clock generator and clock distribution module. At the same time we gave the millimeter correlator project some feedback, helping them debug the correlator boards, and later by designing ECLps versions of the clock distribution box and the clock generator.

The FPTM was mostly designed at Caltech in the Radio Lab (Robinson 004) and was put together at OVRO, where it saw first noise (the correlator equivalent of optical first light) on October 8, 1992. The first astronomical observations were done at Arecibo, where the machine spent all of Winter '92. At that time the FPTM only had 256 functional lags and some systematic noise that we did not understand. We concentrated on ISS observations, taking advantage primarily of the large bandwidth, and polarization observations of

millisecond pulsars, using here both the large bandwidth and the fine time resolution.

Since November '93 the FPTM has been at Parkes Observatory in Australia, undertaking a long term pulsar timing program. Most of the hardware bugs have been ironed out and the current effort is going into the observing and data analysis software. We routinely observe the bright millisecond binary pulsar J0437-4715, which has helped us immensely in the process of debugging the timing offsets.

Caltech graduate student Jagmit Sandhu is also working on the FPTM, his thesis project being the addition of another IF subsystem and digitizer, which will provide the capability to do dual frequency, dual polarization observations. We hope that the expanded machine will overcome the problems that potentially plague analog timing systems, and routinely do 100 ns timing or better.

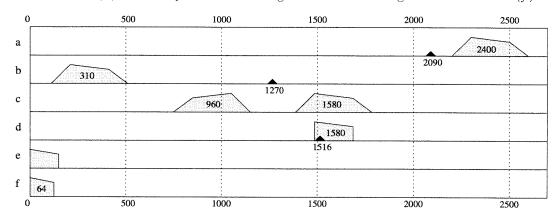

## 2.3 The Data Path

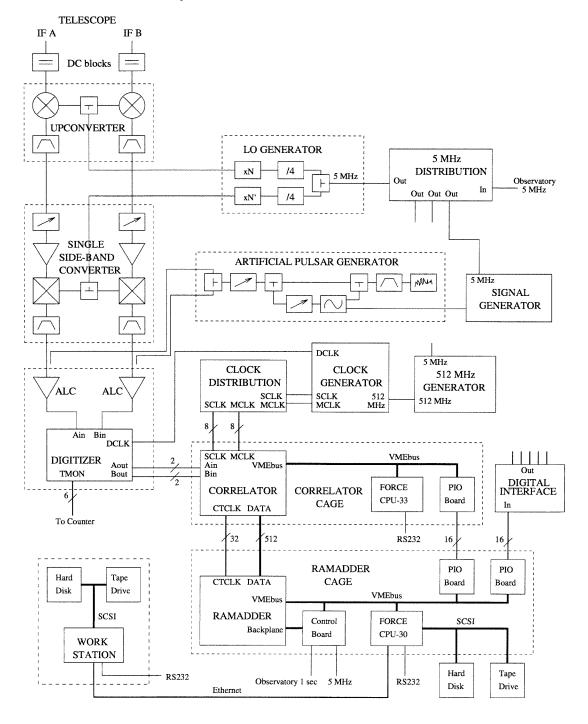

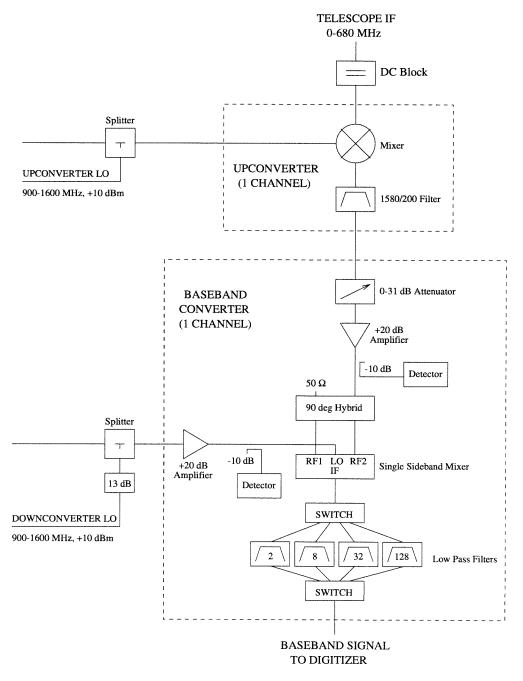

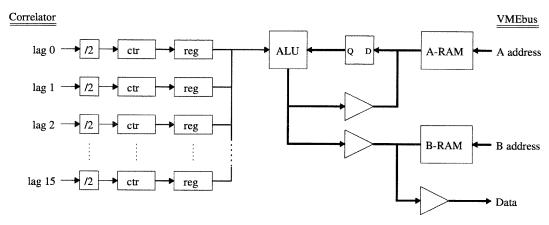

It is useful to look at the functional block diagram of the FPTM in figure 2.1. It shows the major building blocks of the timing machine and the interconnections between them. This section focuses on the data path, from the telescope IF to the pulse arrival times.

The IF subsystem takes two IF radio signals from the telescope and downconverts them to baseband. The two IF signals are usually the two polarizations from the receiver and come at the same frequency between 0 and 1 GHz. This frequency may be the observing frequency itself, or some lower, intermediate frequency that the observing frequency is downconverted to for convenience. As an example, at Arecibo most receivers produce outputs at 260 MHz, and the control room has entire racks of equipment to process signals at 260 MHz.

Inside the FPTM, the process of downconversion is done in three steps: upconversion to 1580 MHz, filtering through a 200 MHz bandpass filter, and single sideband downconversion to baseband or video frequencies. The initial upconversion and filtering allows us to use the baseband converter units from the Owens Valley Millimeter Array, which work with inputs in the 1–2 GHz range. The twin baseband converters also filter the baseband signals to 2, 8, 32 or 128 MHz of bandwidth, depending on the observing setup.

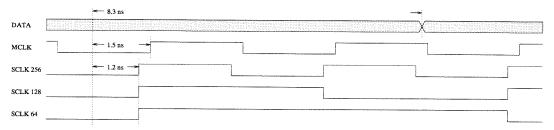

The digitizer takes the two baseband signals, that now have the correct bandwidth and power levels, and samples them at 256 MHz with a resolution of 2 bits. The sampling rate is independent of the bandwidth of the signals, even when it is less than 128 MHz. The digital outputs are ECL signals and they are buffered into several copies so that the digitized signals can be provided to several correlator boards at the same time.

The correlator boards can process signals from several sources, normally the digitizer or the output of other correlator boards. The source of input data for each correlator board is chosen from the software, and determines how the correlator will be configured. The two

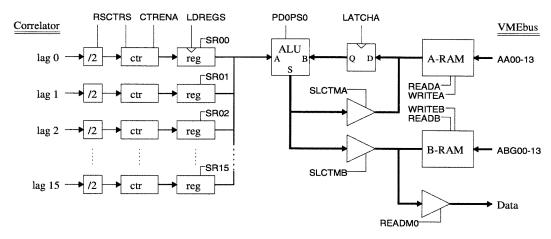

## Figure 2.1: A Block Diagram of the FPTM

The main functional blocks of the FPTM and the main interconnections between them. The signal path starts with the two IF signals from the telescope, which are upconverted and filtered, downconverted and filtered again, digitized, correlated, folded and read into the workstation. Each downconversion is done in single sideband mode (USB) with a 90° hybrid and a quadrature mixer. In addition to the two IF signals, the FPTM needs a 1 second time reference and a 5 MHz frequency reference from the observatory.

standard setups are autocorrelation with 256 lags per polarization, and crosscorrelation with 128 lags for each of the two polarizations and each of the two cross-polarizations.

The 512 lag data outputs from the correlator boards, with the 32 signals that clock them, go to the ramadder boards in the pulsar backend by means of a bundle of ribbon cable. In the ramadder boards each lag gets accumulated further and binned or folded into 1024 phase bins according to the rotational phase of the pulsar. Every minute or so the ramadder boards are read into the pulsar backend computer and stored onto a hard disk. The data set consists of 1024 lag profiles, an array of  $512 \times 1024$  words. Thanks to a double buffering scheme, the ramadder boards can continue to accumulate data from the correlator while being read, so that no astronomical data is lost.

A raw dump of the ramadder boards is not very useful in itself, without being processed into pulse profiles. Once the ramadder boards have been read into the VMEbus computer, the data is transferred over the ethernet to a workstation and analyzed, summarized and archived. Two versions of the data are typically kept after the observations are over. The raw data from the FPTM, in the standard correlator folded data format, is written to tape, while the dedispersed pulse profiles are stored on the disk and used to obtain pulse times-of-arrival. The lists of arrival times are important because they reveal right away whether the timing system is producing results that are consistent with the previous observations, whether we can continue the observations or must debug the system immediately. In the long term, of course, the arrival times are the rotational history of the pulsar.

## 2.4 The Artificial Pulsar

The artificial pulsar generator simulates the signal from a pulsar at baseband. It is a broadband noise source modulated by an external signal generator. Pulsars of any period, duty cycle and strength can be generated. When the digitizer is connected to the artificial pulsar box instead of the baseband converter, the astronomical signal path bypasses the IF subsystem completely. Tests with the artificial pulsar isolate the digital part of the FPTM.

The observing routine requires that we always look at the artificial pulsar before the start of an observing run, as a way of testing the FPTM and ensuring that everything works properly by the time the observations begin. If we can see the pulsar at the the right period and in all the lags, then the control board in the pulsar backend must be providing the correct timing signals. A more subtle point is that the artificial pulsar must appear with the correct strength or signal-to-noise ratio, or else there must be an extraneous source of noise that is unaccounted for. The noise test is fundamental because during astronomical observations it is difficult to tell whether the noise levels are reasonable or not. After all, pulsars are intrinsically variable in many time scales and it would be easy to blame the lack of signal on the pulsar.

# 2.5 Timing and Support Signals

There are two fundamental signals that do not come from the telescope receiver but which are also external to the FPTM, and without which pulsar timing cannot be done. They are the 1 second UT reference and the 5 MHz frequency reference. The arrival times of pulsars are measured with respect to this globally accepted time, and the frequency reference ensures that we can exactly reproduce the pulsar frequency within the duration of an observation. At Parkes both references are generated from the same hydrogen maser (stability of 1:10<sup>14</sup>), and the resultant 1 second clock is regularly compared to a GPS signal obtained from the Deep Space Network station at Tidbinbilla. Typical errors are of less than 30 ns (see also §3.4).

All the clocks in the FPTM are tied to the 5 MHz reference. For this reason the 5 MHz reference goes through a distribution box that provides copies to several modules: the signal generator for the artificial pulsar, the LO generator, the clock generator for the digitizer and the correlator, and the control board in the pulsar backend.

The LO frequencies for the FPTM are generated from the 5 MHz reference essentially by frequency multiplication. The reference is first divided by 4 into 1.25 MHz, then multiplied by an integral factor up to the desired frequency between 900 and 1600 MHz. For this reason the possible LO frequencies are quantized and must be multiples of 1.25 MHz (see §5.2.2). The first LO is used to upconvert the telescope IF signals to the 1.5 GHz range, the second LO to mix them from 1.5 GHz down to baseband. The values chosen for the LOs depend on the IF band presented to the FPTM, which in turn depends on the receiver used. The most common observing and intermediate frequencies used at Parkes Observatory are listed in table 5.1.

There are over one thousand digital signals running around in the FPTM, some of them at frequencies as high as 256 MHz. The most important ones in the block diagram are the fast ones, namely the digitizer clock (DCLK) and the shift and multiply clocks for the correlator (SCLK and MCLK). DCLK goes to the digitizer module directly from the clock generator, while SCLK and MCLK are buffered and distributed to all eight correlator boards. The precise timing relationships between the three clocks need to be held constant at the ideal values, or else propagation delay errors would result in an incorrect correlation. The clocks are generated from a high stability 512 MHz clock oscillator that is phase locked to the observatory 5 MHz. The 512 MHz generator is very stable and will not lock to a reference that is more than 0.01% off from the nominal 5 MHz.

The 512 lags from the correlator are clocked into the ramadder boards by 16 clocks at a rate of 32 MHz. These clocks are generated independently by frequency division of MCLK, and will have random relative phases unless they are synchronized. Given that the 512 lags are treated synchronously in the ramadder boards, it is very important to phase lock the 32 MHz clocks not only with each other but with the ramadder 32 MHz clock

as well. This is described in detail in §8.5, as the advantages of a digital correlator and backend disappear if the clocks are out-of-phase and result in misscounts.

# Chapter 3

# The Millisecond Binary Pulsar J0437–4715

### 3.1 Introduction

The Fast Pulsar Timing Machine is currently at Parkes Observatory, in Australia, where we have started a long term timing program of the southern pulsars. As part of the installation of the FPTM, we have been observing the bright millisecond binary pulsar J0437–4715. The observations have been performed in parallel with the filterbank system used for timing by the Australian team (Johnston et al. 1993), and have been extremely useful in the debugging of the FPTM. At the same time, they have helped us understand the limitations of both the FPTM and the Australian filterbank, and have already yielded some interesting results on the pulsar itself, which we present here.

PSR J0437-4715 was found in 1993 by Johnston *et al.* in a systematic survey of the southern sky with the Parkes radiotelescope. At a distance of 150 pc, J0437-4715 is the second closest known pulsar (after J0108-1431, see Tauris *et al.* 1994) and for that reason is also extremely bright, at times exceeding 1 Jy at 430 MHz. It is in a 5.74 day binary orbit around a 0.14  $M_{\odot}$  star, and has a spin period of 5.757 ms.

Its brightness makes it a useful calibrator for two reasons: first, because an accurate time-of-arrival (TOA) can be achieved in just a few minutes, and second, because while other pulsars fade away at high radio frequencies, J0437-4715 is still visible at frequencies of several GHz. This has allowed us to study the pulse profile and its many components in detail and as a function of frequency.

PSR J0437-4715 has been timed at Parkes since its discovery more than two years ago. There is a timing solution from the filterbank system that gives timing residuals of the order of a few  $\mu$ s. With the FPTM we are attempting to lower the residuals and improve the pulsar model and, at the same time, understand what the limitations are for timing

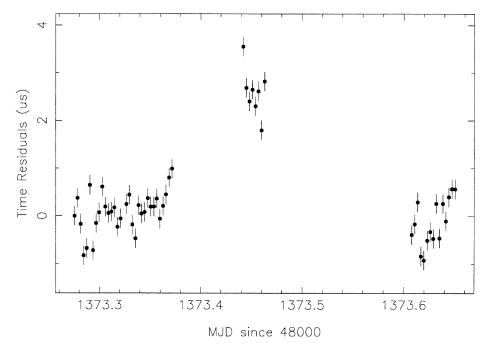

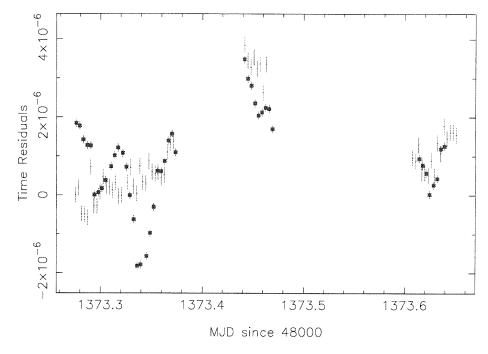

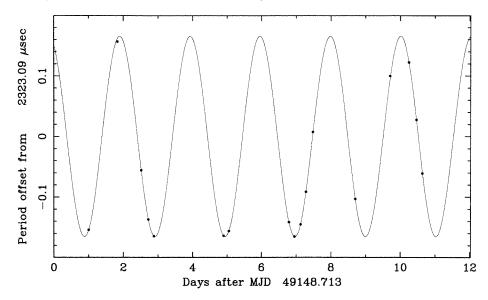

Figure 3.1: Single Night Timing Residuals With the FPTM

Pulse time-of-arrival residuals for J0437-4715 during a period of 9 hours, on 21-Jan-94. The observations were done at a central frequency of 1520 MHz with the 210 ft radiotelescope at Parkes Observatory. The arrival times were calculated from the pulse profile of the sum of the two linear polarizations. The residuals are deviations of the arrival times from those predicted by the pulsar timing model, and show an offset in the second group of points. This offset may be instrumental or due to an inaccurate pulsar model.

this and other pulsars.

# 3.2 Current Status of the Timing Results

Typical observing sessions last a few days and allow us to observe J0437-4715 for several hours per transit. Short integrations (5 minutes is typical) yield times-of-arrival accurate to within a fraction of a  $\mu$ s, depending on the observing frequency. The residuals from different observations are consistent as long as the observations are done within the same hour, but show drifts and jumps of as much as a few  $\mu$ s over several hours or days.

The drifts we have observed in the TOAs have been as large as 3  $\mu$ s per hour, and the jumps could well be the result of a steady drift in TOA while we are not observing. Figure 3.1 shows an example of a jump of 2.5  $\mu$ s that occurred within a single transit. Interestingly, the same drifts and jumps are seen by both the FPTM and the filterbank, which points that the causes of these timing errors are external to either timing system yet common to both through some shared signal (1 s or 5 MHz references) or resource (pulsar timing parameters). The TOAs from the two systems track each other faithfully,

Figure 3.2: A Comparison of Residuals From the FPTM and the Filterbank Pulse time-of-arrival residuals for J0437–4715 during a period of 9 hours, on 21-Jan-94, as deduced from both the FPTM and the Parkes filterbank. The FPTM data is the same as in figure 3.1 and is shown here as small circles (·) with dotted error bars. The filterbank residuals are pictured with solid squares (•) and display drifts and wanders larger than those of the FPTM. The error bars in the filterbank data are underestimated and should be approximately  $\pm 0.5~\mu s$ .

the filterbank showing a bit more scatter than the FPTM (see figure 3.2).

The drifts and jumps seen in the PSR J0437-4715 data are never larger than a few  $\mu$ s, and in the long term the observed TOAs agree with the predicted TOAs to within several  $\mu$ s as well.

# 3.3 A Short History of the Residuals

We installed the FPTM at Parkes in November 1993, and from the very beginning the TOAs we obtained for PSR J0437-4715 produced residuals consistent with the Australian timing solution. By "consistent" I mean that the residuals were small compared with the pulsar period, in this case less than 100  $\mu$ s compared with 5.75 ms. These residuals were still huge, though, compared with what we hoped to get, and we did not discover their origin until several weeks later, when we found that they followed a  $\sim$ 6 day periodicity. This is significant because J0437-4715 has an orbital period of 5.7 days. It turned out that we were using the wrong directory for the pulsar ephemeris file, and this directory just happened to contain an old ephemeris file for J0437-4715, which predicted a slightly incorrect orbital phase.

This was exciting because the FPTM data was already producing TOAs good enough to start the feedback loop between pulsar model and residuals that is the foundation of pulsar timing.