## Parallel Analog Computation with Charge Coupled Devices

Thesis by

Charles F. Neugebauer

## In Partial Fulfillment of the Requirements

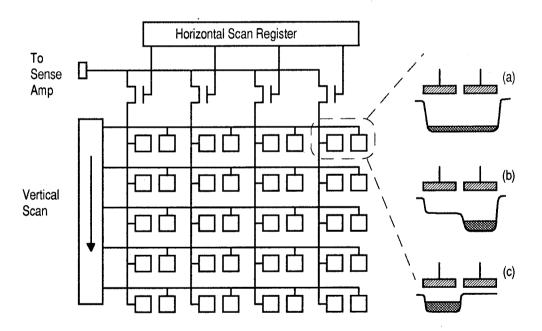

for the Degree of

Doctor of Philosophy

#### CALIFORNIA INSTITUTE OF TECHNOLOGY

**Applied Physics Department**

Pasadena, Califomia

1993

(Defended May 12, 1993)

© 1993

Charles Francis Neugebauer

All Rights Reserved

## Acknowledgments

I would like to thank Amnon Yariv for providing an ideal environment for the pursuit of this research as well as unwavering support and encouragement. I am very grateful to Ron Agranat, whose ideas and backing helped start me in this direction. Gert Cauwenberghs and Volnei Pedroni deserve special recognition for their help honing the ideas presented here. Carver Mead and the people in his lab are unique in their openness and enthusiasm and have greatly enriched my time at Caltech.

I am grateful to Barbara Yoon at ARPA and Jim Mulligan of the Army CSW for providing financial support for this work. Thanks to the National Science Foundation and AT&T for graduate fellowship support.

Lastly, I would like to thank Ann Lewis, my family and all my friends for their unceasing support for everything I try to do.

### **Abstract**

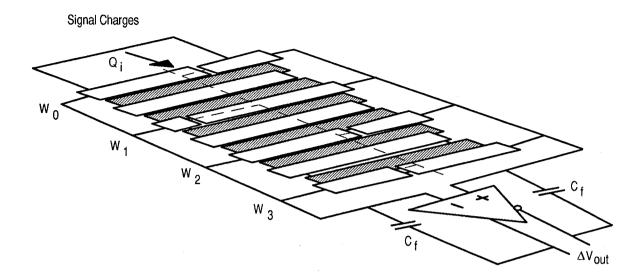

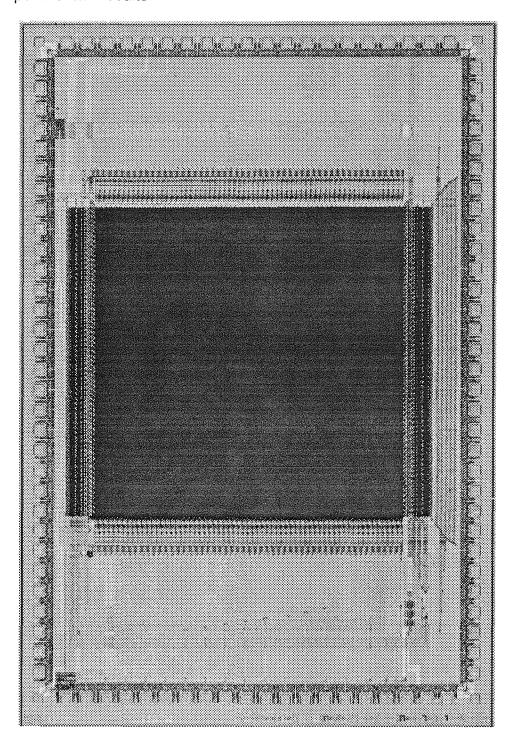

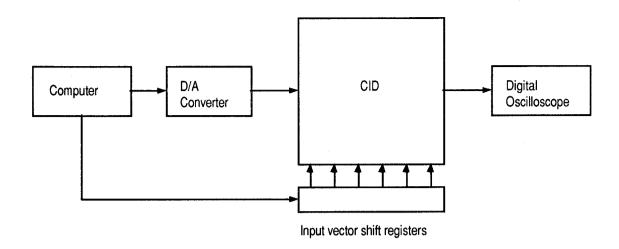

Many signal processing and neural network algorithms can be mathematically described in terms of vector matrix multiplication. This thesis introduces two new architectures for computing high-speed vector matrix multiplication using charge coupled devices. These integrated circuits have been designed to accept optical matrix input as well as direct electrical matrix input. In both architectures, the matrix elements are stored as analog charge packets in CCD wells while the vectors are communicated to and from the integrated circuits by electrical means.

The first architecture accomplishes the vector matrix product using a semiparallel computation scheme that requires N clock cycles of the device to complete one vector matrix multiplication where N is the length of the input vector. An analysis of the linearity and charge transfer induced errors is given. The circuit represents an advance over other analog signal processors in density and speed but has serious shortcomings in accuracy, particularly the limited precision of the input vectors.

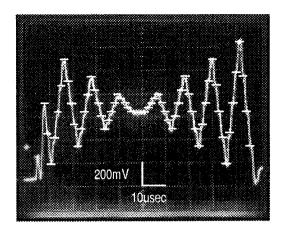

The second architecture is based on charge injection device (CID) imager arrays and addresses many of the inadequacies of the semiparallel architecture. A fully parallel circuit, the CID has similar density and much higher computation speed and accuracy. A novel digital input method is introduced that extends the input vector precision significantly. In addition, accuracy issues related to charge transfer efficiency are resolved. An analysis of linearity and accuracy is provided showing the advantages of the architecture over previous implementations.

## Contents

| Acknowledgments                                       | iii     |

|-------------------------------------------------------|---------|

| Abstract                                              | v       |

| Contents                                              | vii     |

| 1. INTRODUCTION                                       | 1       |

| 1.1 Neural Networks and Adaptive Signal Processing    | 3       |

| 1.2 Vector Matrix Multiplication                      | 7       |

| 1.3 Technologies for Parallel Computation             | 7       |

| 1.4 Architectural Considerations                      | 11      |

| 1.5 References:                                       | 14      |

| 2. CHARGE COUPLED DEVICES                             | 17      |

| 2.1 MOS Capacitor Physics                             | 17      |

| 2.2 The CCD Shift Register                            | 20      |

| 2.3 Charge Transport in CCDs                          | 21      |

| 2.4 Charge Transfer Efficiency and Dark Current       | 23      |

| 2.5 Surface Channel Devices                           | 26      |

| 2.6 Buried Channel Devices                            | 27      |

| 2.7 Charge Input                                      | 43      |

| 2.8 Charge Output                                     | 48      |

| 2.9 References:                                       | 57      |

| 3. SEMIPARALLEL CCD PROCESSOR                         | 61      |

| 3.1 Historical Background                             | 61      |

| 3.2 System Description                                | 64      |

| 3.3 Analysis of Charge Storage Capabilities and Linea | arity66 |

| 3.4 Experimental Results                                    | 69  |

|-------------------------------------------------------------|-----|

| 3.5 Limitations of the Semiparallel Architecture            | 73  |

| 3.6 References:                                             | 74  |

| 4. PARALLEL CHARGE INJECTION DEVICE PROCESSOR               | 77  |

| 4.1 Background                                              | 77  |

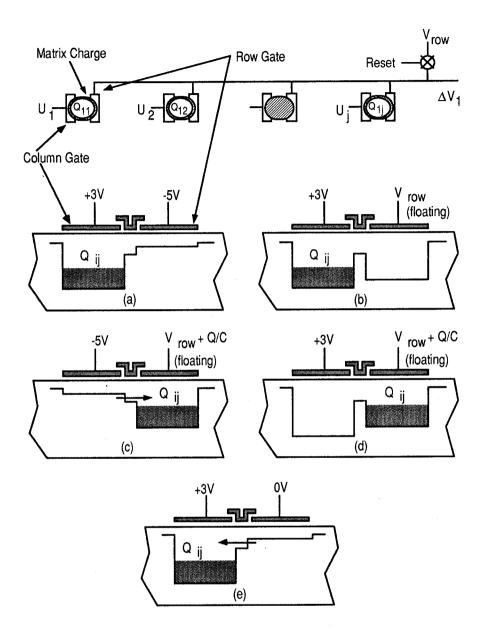

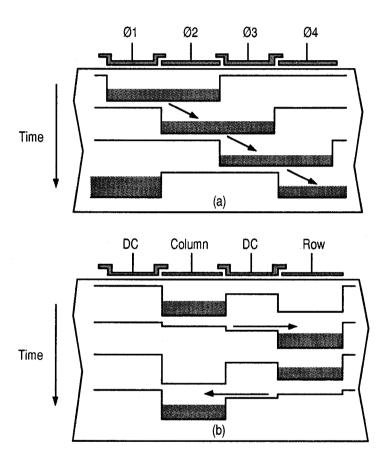

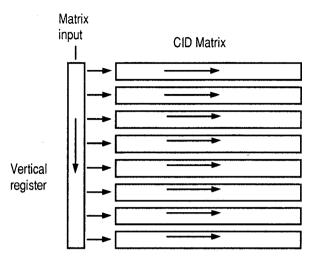

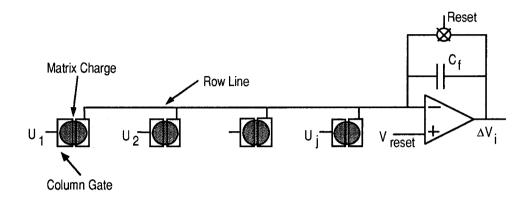

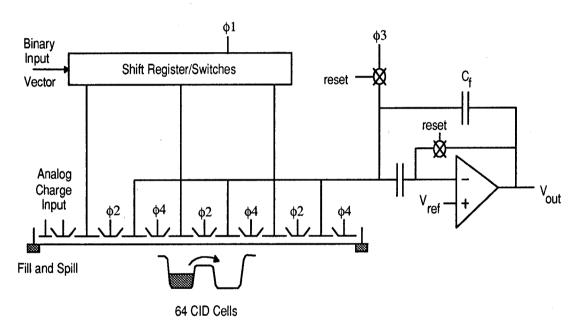

| 4.2 System Description                                      | 79  |

| 4.3 Loading the Matrix                                      | 82  |

| 4.4 Improving Linearity                                     | 84  |

| 4.5 Extending Input Vector Precision                        | 88  |

| 4.6 Charge Storage Capabilities                             | 90  |

| 4.7 Input and Output Compatibility Issues                   | 91  |

| 4.8 Experimental Results                                    | 92  |

| 4.9 Power Dissipation                                       | 97  |

| 4.10 Comparison with Semiparallel Processor                 | 98  |

| 4.11 Future Directions                                      | 98  |

| 4.12 References:                                            | 100 |

| 5. COMPARISONS                                              | 103 |

| 5.1 Analog vs. Digital                                      | 103 |

| 5.2 Other Technologies for Analog Computation               | 105 |

| 5.3 Comparison of the CID Processor with Other Technologies | 106 |

| 5.4 References:                                             | 109 |

| 6. SUMMARY                                                  | 111 |

| 6.1 References:                                             | 112 |

## Chapter 1

## 1. Introduction

This thesis discusses the electronic implementation of biologically inspired signal processing algorithms. One feature common to most of these neural computation algorithms is the high degree of interconnection between neurons. Compared to traditional computing structures, neural architectures derive most of their computational abilities from the connections between processors as opposed to the processors themselves. The majority of neural network implementations tend to focus on the interconnect problem and not the neuronal simulation.

It is important to note the physical limitations of trying to map biological networks which have three dimensions at their disposal to form connections onto man-made technologies. The dominant implementation technology for computing devices is silicon, which is essentially restricted to two dimensions for communication. While optical and chip stacking technologies have emerged as solutions to the interconnect density problem, the displacement of conventional flat silicon by these and other esoteric approaches is unlikely in the near future. As such, the circuit designer is left to grapple with the transformation of three-dimensional circuits to two dimensions.

The application of CCD signal processing techniques to parallel computation is addressed in this thesis. Analog CCD signal processing circuits have been described in the past and have the

advantageous features of dense integration, small size, low power, and high speed. Exploiting these features in the hope of creating a compact neural signal processor is the goal of this work. As in most analog hardware of this sort, the choice of information representation is tightly coupled with the resulting circuit implementation. The primary emphasis of this thesis is on the device analysis at the simple connection level and how this pertains to system level performance with the proper choice of information representation.

The thesis is organized as follows:

- Chapter 1 presents an overview of system level considerations which influence the choice

of interconnection devices. A cursory description of algorithms is given and

various computation schemes and technologies are presented.

- Chapter 2 gives an introduction to CCD device physics and develops a simple formalism

for the performance analysis of these CCD circuits relevant to the architectures

discussed in this thesis. A new set of practical voltage limits is derived for buried

channel devices.

- Chapter 3 deals with the first circuit implementation of a vector matrix multiplier using a semiparallel CCD architecture.

- Chapter 4 describes a fully parallel CID architecture that supersedes the one described in Chapter 3 by virtue of its improved speed, accuracy and density.

- Chapter 5 comments on the relative performance of these architectures versus other implementations.

Due to the limited exposure most readers have to CCD signal processing devices, an introductory text on CCD circuits such as [Séquin et al., 1975] or [Beynon et al., 1980] can be useful for understanding this thesis. Although an introduction to CCD devices is given in Chapter 2, the historical background and device evolution presented in the introductory texts is of significant value as it provides a proper perspective from which to view this work.

Also, the short introduction to neural networks is only intended to illuminate the implementation details necessary for developing the devices. The reader is encouraged to read [Kohonen, 1984][McClelland et al., 1986][Lippmann, 1987] if further background information is required.

#### 1.1 Neural Networks and Adaptive Signal Processing

The development of computational models of biological neurons has been undertaken to understand the principle mechanisms of neural system behavior and to mimic this behavior in artificial machine-based neurons. Various levels of abstraction characterize the major theories' mathematical descriptions of the operation of neurons. Real neurons are naturally very complex, responding to both electrical and chemical stimuli often from thousands of other neurons with diffusion constants, electrical spike generation and propagation and a multitude of interaction pathways complicating the mathematical analysis. While detailed simulation of most of these attributes is possible, the significant computational resources required precludes this approach in cases where many neurons interact. The incorporation of the adaptive mechanisms of neuron behavior to the model, specifically synaptic plasticity and long term potentiation, complicate matters even further. A mathematical abstraction takes place at some level in all simulations, the real question being what level abstraction is necessary to capture the essential behavior without unnecessarily complicating the analysis. While much of the answer to this question depends on the system being studied, a number of useful descriptions of neurons have evolved that provide

adaptive behavior with a minimal amount of computation.

One of the simplest descriptions of the aggregating properties of neurons [Minsky et al., 1969] treats connections (i.e., synapses) as simple linear elements which weight signals. In this model, input signals are multiplied by the connection strength and added together to form the post-synaptic potential. The model lumps excitatory and inhibitory synapses into the same connection by allowing it to be positive or negative. This is the only form of stimulus considered and no synaptic time constants are included. This primitive model can effectively simulate some of the behavior of real neurons, proving that in some cases simple linear synaptic connections are adequate models.

A further abstraction can be made with respect to the electrochemical stimulus of the neurons. A quantity called the excitation is introduced which roughly corresponds to the instantaneous firing rate of a neuron. The effect of pulses can be compressed into a pulse rate, effectively removing the time dimension from the simulation. While this results in significant computational savings, the essential time domain behavior of neurons is lost. The penalties associated with this abstraction vary from system to system and can be significant for coherence sensitive problems such as auditory localization [Mead, 1989]. For a large class of simple problems, however, this abstraction is not detrimental [McClelland et al., 1986].

In [Hopfield, 1982], Hopfield describes a simple distributed neural system that behaves as a content addressable memory. In a later model [Hopfield, 1984] the neuron activity is represented as a single number corresponding to the firing rate. The set of neuron activities was described as a vector while the synaptic strengths were encoded as a matrix. Dynamic interactions were given by a simple differential equation that governed the reaction of each neuron to its input. Implicit in the mathematical description was the connectivity of the neurons expressed as a matrix. The computation involved repeated multiplication of the matrix by the neuron activation vector. In addition, a soft thresholding function related the aggregated input to the neuronal output. This

nonlinearity gives neural networks the ability to perform complex mappings given multiple layers [Minsky et al., 1969][McClelland et al., 1986].

The linear synapse model is the most common description of synaptic activation as it seems to capture enough of the real behavior of neurons to be useful for many problems. In a signal processing sense, the input vector corresponds to an input signal and the matrix corresponds to a linear transform. The information processing capabilities of neural networks are enhanced significantly when the matrix is adaptively modified to improve performance. Such learning behavior in simple linear transforms was first described in [Widrow et al., 1960] and has found widespread use in communications systems. The algorithm was developed by first quantifying the performance of the network into a single number, the global error, then finding the derivative of this error with respect to the matrix elements. The matrix elements are then modified slightly in proportion to the error gradient and the error measurement process is repeated. This incremental learning method is referred to as gradient descent for obvious reasons. While the recipe for gradient descent has been modified extensively for performance reasons, the basic tenet of reducing a global error remains true.

Gradient descent was mathematically motivated by a signal processing need. It is safe to say that biology does not use a simple gradient descent for adaptive behavior. While not biologically motivated, gradient descent is a simple solution to a significant signal processing problem where adaptive systems are needed.

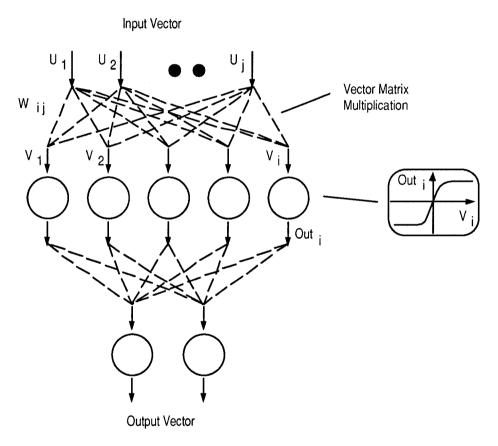

The integration of neural network models and gradient descent occurred in the mid-1980's when back propagation was introduced. Partially motivated by biology in structure and by signal processing in adaptation, back propagation provided a formalism for adapting the weights of a feed-forward nonlinear network [McClelland et al., 1986]. The concept of a multilayer network with multiple stages of neurons feeding into more neurons is diagrammed in Figure 1.1.

Information enters at the top and percolates down. Each layer consists of a vector matrix multiplication and a soft nonlinearity. Such a feed-forward network, when presented patterns at the top as input and a requested target at the bottom as desired output, is able to learn the association or mapping between input and output vectors under certain conditions. The learning process is governed by

Figure 1.1. A feed forward neural network with a single hidden layer. Information flow is top to bottom. The input vector pattern U<sub>j</sub> is linearly weighted and summed by vector-matrix multiplication with the W<sub>ij</sub> matrix. A sigmoidal function is applied to the aggregated signals to form the output of the hidden layer. This output is similarly weighted, summed and put through the sigmoidal nonlinearity to form the final output vector.

gradient descent, which is not guaranteed to converge for multilayer nonlinear networks and makes

the entire procedure fraught with pitfalls in the areas of choosing network size, learning parameters, etc.. While of limited usefulness in understanding and mimicking neurobiology, the back propagation approach has proven to be useful in applications where the relationship between input and output data is unknown and target outputs are easily generated for teaching purposes.

#### 1.2 Vector Matrix Multiplication

The algorithms described above center around vector matrix multiplication which typically constitutes the bulk of the processor load when such algorithms are simulated on a computer. Obvious advantages exist in implementing the algorithms in special purpose hardware to take advantage of the inherent parallelism of neural calculations, although the general purpose flexibility of a conventional computer is lost. Mapping the connectivity to a matrix is a natural process for two-dimensional silicon technology. The work described in this thesis is targeted at efficient silicon implementations of the vector matrix multiplication.

The vector matrix product is useful in a number of other signal processing applications. Correlations, pattern matching and simple linear transforms such as wavelet and chirp-z transforms are all functionally described as vector matrix multiplication. Hence the functionality of the devices presented extends beyond the field of neural networks.

#### 1.3 Technologies for Parallel Computation

The success of digital computing is due to a number of factors such as its programmability, high accuracy, noise insensitivity and low cost. Although limited in accuracy, analog circuits have held the promise of performing a given computation much more efficiently in terms of area, power and

speed than their digital functional equivalent. Neural network models are intentionally robust with respect to accuracy limitations and offset errors due to their distributed and adaptive behavior, making them ideal candidates for analog implementations. Furthermore, the real world sensor data that most neural systems deal with is often low accuracy and high bandwidth, such as imager data which typically comes from an analog CCD sensor. Thus for certain low accuracy problems, the precision limitations of analog circuitry are far outweighed by the potential gains in speed, density and reduced power consumption. Although analog circuitry will never match digital in terms of accuracy and flexibility, for certain niche markets analog has the upper hand.

The choice of implementation technology relies on the consideration of a number factors. Computational devices require information storage, either short term or long term depending on the application. For the systems mentioned above, the need for accurate long term storage is a primary concern as the matrices are often fixed or adapt slowly. On the other hand, time multiplexing a single chip with a few hundred neurons to take the place of hundreds of thousands of neurons requires that the many different connection matrices be swapped quickly, implying off-chip long term storage.

Many methods of storing information in silicon technology, including DRAMs, EPROMs and CCDs, involve charge storage on a capacitor. Except for floating gate capacitors, these MOS capacitors exhibit leakage currents which tend to degrade the stored information within tens of milliseconds. Floating gate structures, while exhibiting extremely long storage times, are characterized by a number of inconveniences such as slow write times and a limited number of write cycles. The loading limitations on floating gate circuits precludes them from consideration for time multiplexed neural systems.

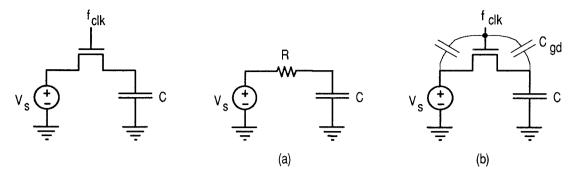

**Figure 1.2.** Error sources in switched capacitor circuits. The clock signal controls the gate of the MOSFET device which has a finite 'on' resistance shown in (a) and contributes Johnson noise. The parasitic capacitance of the clock signal to the storage capacitor,  $C_{\rm ed}$ , is another source of errors.

The comparison of conventional switched capacitor storage [Kub et al., 1990] and CCD circuits is straightforward since they both use capacitors as the storage medium. Voltages in switched capacitor circuits are transferred from place to place through a series of amplifiers, switches and capacitors. In a typical arrangement shown in Figure 1.2, switched capacitor circuits store charge on a capacitor by using a FET as a switch connected to a voltage source, which is most often an on-chip operational amplifier. The two dominant error sources are thermal noise and clock feedthrough, shown schematically in Figures 1.2(a) and 1.2(b). Thermal noise is due to the finite 'on' resistance of the FET during the write procedure which introduces a Johnson noise-induced voltage variation on the storage capacitor given by

$$\overline{V}_{n}^{2} = \frac{kT}{C}$$

(1.1)

which is derived in Chapter 2. Note that the FET 'on' resistance does not appear in Equation 1.1. The parasitic capacitive coupling between the drain and gate of the switch transistor causes a voltage variation on the storage capacitor given approximately by

$$\Delta V_{c} \cong \frac{C_{gd}}{C + C_{gd}} \left( V_{S} + V_{T} + \gamma \left[ \sqrt{2|\phi_{F}| + V_{S}} - \sqrt{2|\phi_{F}|} \right] \right)$$

(1.2)

where  $V_s$  is the source voltage,  $\gamma \approx 0.7 V^{1/2}$  is the bulk threshold parameter and  $\phi_F \approx 0.7 V$  is the strong inversion surface potential [Allen et al., 1987]. Here it is important to note that the parasitic gate-to-drain capacitor is in general proportional to the size of the FET. An engineering trade-off exists between the speed of the circuit and the amount of clock feedthrough error. If the FET is too small, the circuit will be speed-limited by the RC circuit formed by the FET and the storage capacitor. In practice, however, a minimum sized switch requires a relatively large capacitor to achieve even modest levels of accuracy due to the combination of these two error sources. This large capacitor requirement sets a density limit of switched capacitor storage circuits.

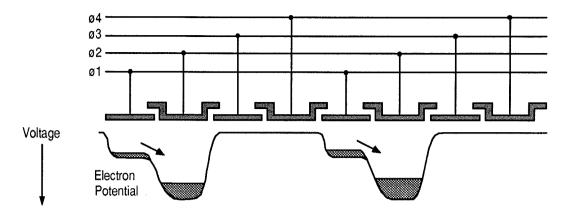

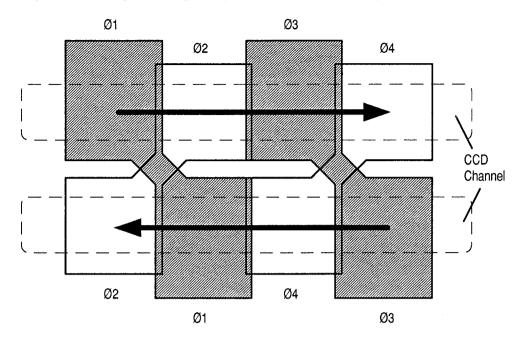

In contrast, CCD circuits move charge between elements as shown in Figure 1.3 which depicts a simple four phase CCD shift register. Clock feedthrough, i.e., a modification of the stored charge due to a transition of one of the clocked electrodes, does not occur due to charge conservation within the CCD. Also, thermal noise associated with creating charge packets is reduced since charge can be loaded optically or with a charge creation circuit designed to minimize this effect. The chip area penalty for low noise charge loading is negligible for large CCD arrays since one large charge creation area can be used to create the charge for many small storage areas. The upshot of these differences between CCD and switched capacitor circuits is that the capacitor storage cells can be made much smaller for CCD circuits (i.e., much higher density) without sacrificing accuracy. In addition, the natural ability of CCDs to form multiplexors, analog shift registers and to be optically loaded is very useful for signal processing systems. For these reasons, CCD technology was chosen.

**Figure 1.3.** CCD shift register side view. Electron potential is an inverted plot of surface voltage of the channel. The surface potential is controlled by the polysilicon gates connected to the four-phase clock. The charge behaves like a fluid, moving to its local potential minimum.

#### 1.4 Architectural Considerations

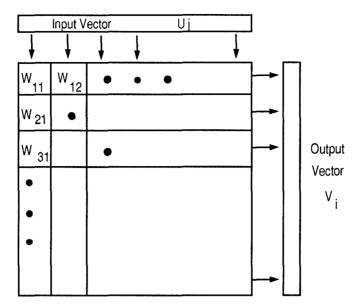

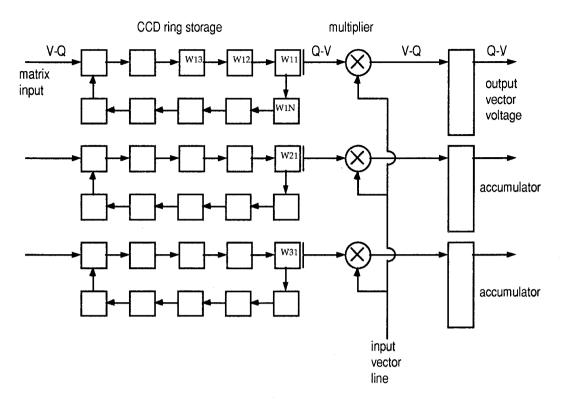

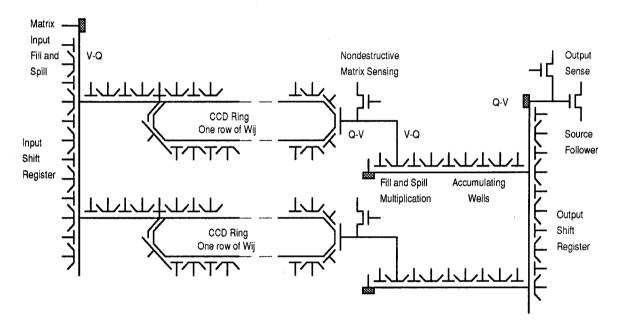

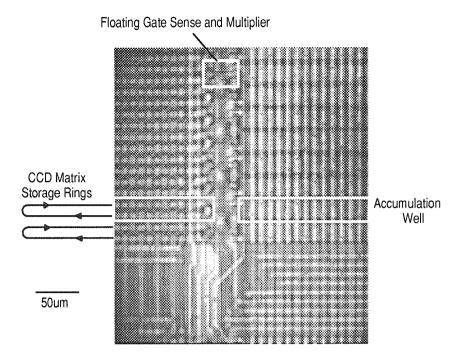

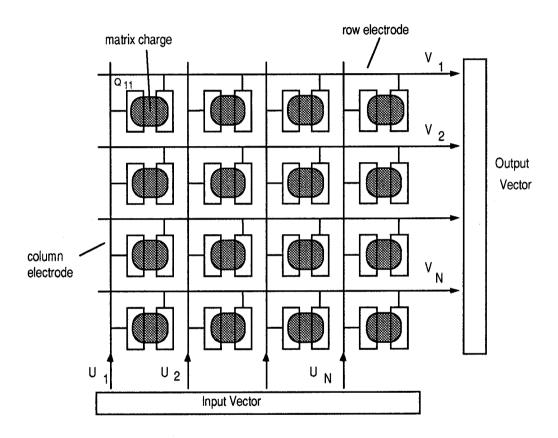

The essential element of an analog vector matrix multiplier is the matrix element which performs the synaptic weighting function. Each matrix element in the circuits of this thesis stores a given weight,  $W_{ij}$ , as a charge packet and performs a multiply-accumulate operation. The input vector element  $U_j$  is multiplied by  $W_{ij}$  at each matrix element and the product is added to the output vector element,  $V_i$ . A typical vector matrix multiplier chip block diagram is shown in Figure 1.4. Given that both input and output vectors are O(N) in size, the matrix contains  $O(N^2)$  elements and typically requires the most chip area for large N. Thus it is important to concentrate on minimizing the matrix element size for large matrix designs.

**Figure 1.4.** Vector Matrix Multiplier (VMM) block diagram. Each matrix element performs a multiply accumulate function to form the output vector. Weights are physically stored as charge packets in the array.

CCD technology has experienced widespread use in the field of electronic imaging where pixel density and analog performance are constant areas of improvement. The high quantum efficiency and low noise of CCD detectors make them ideal for light sensing applications. The stated goal of vector matrix multiplication can exploit this aspect of CCDs as a means of matrix input. Two-dimensional imager arrays can be used as the storage medium for matrix elements. The use of optical input as a parallel matrix communication scheme increases the bandwidth of the system beyond traditional pin limited designs and takes advantage of the parallelism of optics in a simple, implementable way.

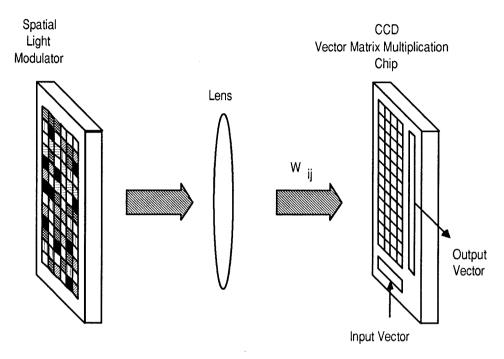

The optoelectronic computation scheme is shown in Figure 1.5 where a spatial light modulator creates a two-dimensional pattern of optical intensities encoding the matrix which is projected onto the CCD vector matrix multiplier chip. This concept of hybrid CCD/optical systems is not new -- in [Copeland et al., 1976] for example, an optically encoded filter characteristic is loaded onto an IC for subsequent FIR filtering of an electrically input signal. Although spatial light modulator technology lags significantly behind silicon technology, the advent of sophisticated holographic

crystal storage mechanisms and other exotic technologies may lead to significant system performance enhancements.

**Figure 1.5.** Optical matrix input. The matrix elements of the CCD VMM chip are light sensitive allowing matrix input to be performed optically. The pattern of intensities on the spatial light modulator is imaged onto the CCD chip for a brief period of time to accomplish loading.

Another option for creating a matrix of stored charge is an electrically controlled charge generator, described in Chapter 2. The charge generator creates precise charge packets which can then be shifted by CCD registers to the proper locations. This mode of operation makes for very compact systems without the need for a complicated optical arrangement at the expense of complex clocking and a significant reduction in matrix input bandwidth.

As mentioned above, the matrix cell size must be kept as small as possible which, in turn, implies a simple cell. The standard figures of merit for a given implementation are its power-delay product for functional efficiency and its area-delay product for silicon efficiency. As CCDs are inherently

low power and dense, the circuits presented here are expected to fare well by these measures. It is important to avoid comparisons with general purpose digital hardware such as microprocessors. The accuracy and programmability of conventional digital machines limits their efficiency of implementation by these two metrics. Only comparisons with special purpose digital hardware that has been optimized for one specific task with limited accuracy are valid. Such comparisons are presented in Chapter 5.

Given the task of computing a vector matrix multiplication, CCDs are one of many technologies that can be used, each of which has its own advantages and disadvantages. In the following chapter, the limitations of CCD devices in performing analog computation are explored at the device level. In later chapters, the specific architectures are discussed.

#### 1.5 References:

- [Allen et al., 1987] P.E. Allen and D.R. Holberg, *CMOS Analog Circuit Design*. New York: Holt, Rinehart and Winston, 1987.

- [Beynon et al., 1980] J.D.E. Beynon and D.R. Lamb, *Charge Coupled Devices and Their Applications*. London: McGraw-Hill, 1980.

- [Copeland et al., 1976] M.A. Copeland, D. Roy, J.D.E. Beynon and F.Y.K. Dea, "An optical CCD convolver," *IEEE Transactions on Electron Devices*, vol. ED-23, pp. 152-155, 1976.

- [Hopfield, 1982] J.J. Hopfield, "Neural networks and physical systems with emergent collective computational abilities," in *Proceedings of the National Academy of Sciences*, USA, vol. 79, pp. 2554-2558, 1982.

- [Hopfield, 1984] J.J. Hopfield, "Neurons with graded response have collective computational properties like those of two-state neurons," in *Proceedings of the National Academy of Sciences, USA*, vol. 81, pp. 3088-3092, 1984.

1.5 References: 15

[Hopfield et al., 1986] J.J. Hopfield ad D.W. Tank, "Computing with neural circuits: a model," *Science*, vol. 233, pp. 625-633, 1986.

- [Howes et al., 1979] M.J. Howes and D.V. Morgan, *Charge Coupled Devices and Systems*. London: John Wiley & Sons, 1979.

- [Kohonen, 1984] T. Kohonen, *Self-Organization and Associative Memory*. Berlin: Springer-Verlag, 1984.

- [Kub et al., 1990] F.J. Kub, K.K. Moon, I.A. Mack and F.M. Long, "Programmable analog vector-matrix multipliers," *IEEE Journal of Solid State Circuits*, vol. SC-25(1), pp. 207-214, 1990.

- [Lippmann, 1987] R.P. Lippmann, "An introduction to computing with neural networks," *IEEE ASSP Magazine*, pp. 4-22, 1987.

- [McClelland et al., 1986] J.L. McClelland and D.E. Rumelhart, *Parallel Distributed Processing, Explorations in the Microstructure of Cognition*. Cambridge, MA: MIT Press, 1986.

- [Mead, 1989] C.A. Mead, *Analog VLSI and Neural Systems*. Reading, MA: Addison-Wesley, 1989.

- [Minsky et al., 1969] M. Minsky and S. Papert, *Perceptrons: An Introduction to Computational Geometry*. Cambridge, MA: MIT Press, 1969.

- [Roth, 1988] M.W. Roth, "Neural-network technology and its applications," in *Johns Hopkins APL Technical Digest*, vol. 9(3), 1988.

- [Séquin et al., 1975] C.H. Séquin and M.F. Tompsett, *Charge Transfer Devices*. New York: Academic Press, 1975.

- [Tank et al., 1987] D.W. Tank and J.J. Hopfield, "Collective computation in neuron-like circuits," *Scientific American*, vol. 257, pp. 104-114, 1987.

[Widrow et al., 1960] B. Widrow and M.E. Hoff, "Adaptive switching circuits," in *IRE Western Electronic Show and Convention*, Part 4, pp. 96-104, 1960.

# Chapter 2

### 2. CHARGE COUPLED DEVICES

The charge coupled device was conceived in 1970 [Boyle et al., 1970][Amelio et al., 1970] as a replacement for bucket brigade devices that had been used as analog delay lines. A good review of the history of charge transfer devices can be found in [Séquin et al., 1975]. CCDs were later adapted for use as imaging devices, a market they currently dominate. The basic principals of CCDs are presented in condensed form in this chapter with some new results regarding voltage limits, and then a framework for understanding the nonlinear effects inherent in charge manipulation is developed. In the following chapters, significant use of this formalism will be made to explain the limitations of analog CCD computation architectures.

#### 2.1 MOS Capacitor Physics

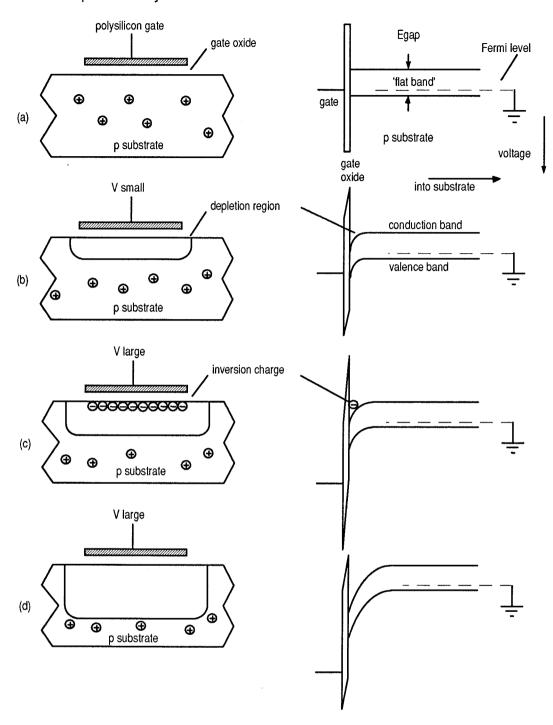

The basic MOS capacitor is constructed of a polysilicon gate above a p-type substrate separated by silicon dioxide. The well known behavior of this device is best illustrated by the energy band diagrams of Figure 2.1. It is assumed the reader is familiar with this representation of semiconductor devices. A good introduction for the uninitiated can be found in [Sze, 1985]. All semiconductor voltages are given with respect to the conduction band and the gate voltages with

respect to the flat band voltage as in [Howes et al., 1979]. Figure 2.1(a) shows the flat band condition where the gate is grounded. For small positive gate voltages, the area beneath the polysilicon is depleted of majority carriers (holes) resulting in band bending in the depletion region, depicted in Figure 2.1(b), due to the space charge.

At higher gate voltages, minority carriers can accumulate beneath the gate, a condition called inversion, which is shown in Figure 2.1(c). Inversion charge can be generated by a number of sources with the major generation mechanism for a simple isolated MOS capacitor being thermal generation of charge due to traps [Howes et al., 1979].

Dynamically, if the gate is kept at a low voltage and then pulsed to a high voltage, the inversion charge will not have time to accumulate. This situation is referred to as deep depletion and is a pseudo-equilibrium state that exists before thermal inversion charge is accumulated. Shown in Figure 2.1(d), deep depletion is the mode in which the CCD circuits operate. The surface potential is a strong function of the gate voltage and forms a potential well for inversion electrons. The higher the gate voltage, the deeper the well. A MOS capacitor can hold varying amounts of inversion charge in the short time span (less than 100 milliseconds, typically) in which this pseudo-equilibrium approximation is valid. This charge can encode a signal level, as in CCDs, and can be moved by changing the potential of adjacent polysilicon gates as explained below.

Figure 2.1. MOS capacitor band diagrams. In (a), the substrate is in thermal equilibrium with a uniform hole concentration (majority carriers) determined by the substrate doping density. In (b) the gate voltage is raised, repelling the holes in the substrate immediately beneath the gate to create the depletion region. Raising the gate voltage further (c) attracts electrons to the surface to form an inversion charge layer. In (d), if the gate is pulsed quickly to a high voltage, electrons do not have time to accumulate and a deep depletion is formed.

#### 2.2 The CCD Shift Register

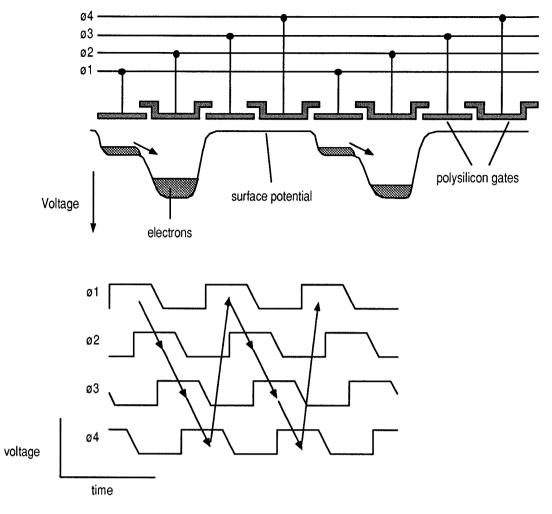

To introduce the operation of CCDs, the example of a shift register is explored. A CCD shift register consists of multiple overlapping polysilicon gates that are connected to time varying potentials, shown in Figure 2.2. The surface potential of the CCD channel is manipulated by the voltages on the polysilicon gates. Charge can be abstracted to behave as a fluid, moving to find the minimum potential (i.e., maximum voltage) level. In this abstraction, the gate voltages set the depth of the potential wells and hence control the relative potential energy of the electrons beneath the gates. If one gate is at a higher voltage with respect to its neighbors, its potential well is deeper and it will attract the electrons from under the neighboring gates. CCD shift register operation occurs when the polysilicon gates are driven with overlapping four-phase clock signals as depicted in Figure 2.2. Charge introduced from the left is moved to the right by the four-phase clock signals which act to repeatedly create a deeper potential well to the right of the charge packet, inducing the charge to move.

**Figure 2.2.** Clock voltages used to operate a CCD shift register. The charge is moved left to right by application of the four-phase clock signals to the polysilicon gates. The arrows on the voltage waveforms signify the charge packet following the voltage maximum in the channel.

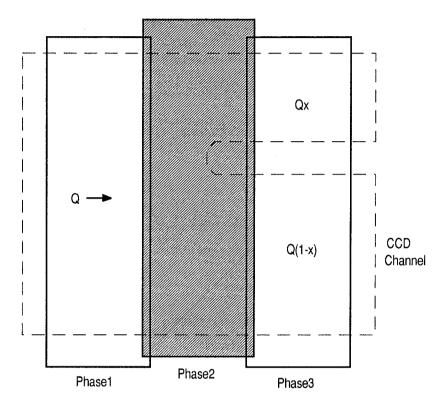

#### 2.3 Charge Transport in CCDs

Charge transport in CCDs is due to two fundamental processes, drift and diffusion. The condensed material presented here is based on the work of [Carnes et al., 1971] and that found in [Howes et al., 1979]. When the channel potential profile is changed to move charge from one gate to another, the initial movement of charge is primarily due to self-induced drift. Once a significant fraction of the charges have moved, diffusion takes over and empties the source well further. After almost all of the electrons have left the initial gate area, diffusion is no longer a strong driving force and

electric field induced drift completes the transfer. In typical CCDs the transfer of the last few electrons determines the transfer performance. Horizontal electric fields, also known as 'fringing fields', directly beneath a gate sweep out this small remaining charge. The time required to transfer the last few electrons is dependent on the gate length and the fringing field and is approximated by

$$\tau_{\rm E} \approx \frac{L_{\rm gate}}{E_{\rm fringe} \mu_{\rm e-Si}} \tag{2.1}$$

A first-order approximation to the fringing fields along the channel for a surface channel threephase device can be found in [Carnes et al., 1971] and is given by

$$E_{\text{fringe}} \approx 6.5 \frac{t_{\text{ox}} V}{L_{\text{gate}}^2} \left[ \frac{\frac{5x_d}{L_{\text{gate}}}}{\frac{5x_d}{L_{\text{gate}}} + 1} \right]^4$$

(2.2)

where  $X_D$  is the depletion depth and V is the voltage difference between gates. Thus transfer time varies as

$$\tau_{\rm E} \propto \frac{L_{\rm gate}^3}{t_{\rm ox} V} \quad \text{to} \quad \frac{L_{\rm gate}^7}{t_{\rm ox} V}.$$

(2.3)

Short gates are thus a prerequisite for high-speed CCD circuits, noting the strong dependence on gate length. A more complete review with numerical simulations can be found in [Mohsen et al., 1973][Mohsen et al., 1975] and more recently in [Bakker, 1991].

#### 2.4 Charge Transfer Efficiency and Dark Current

The simple operation of the shift register is complicated by the effects of incomplete charge transfer [Berglund et al., 1973]. Fabrication process, clock voltages and edge rates all have significant effects on charge transfer. Charge Transfer Efficiency (CTE) is the common performance measure of CCDs and is defined as the fraction of charge that is actually transferred from one gate to an adjacent gate. Some fraction,  $\varepsilon$ , is left behind and is added to the trailing charge packet in the shift register. More advanced abstractions of CTE beyond this simple linear (i.e., fractional) model have been studied [Séquin et al., 1975], but for this analysis, the simple model will suffice. In the following sections, clock voltage ranges and edge rate limits are examined with the performance criterion of maximizing CTE.

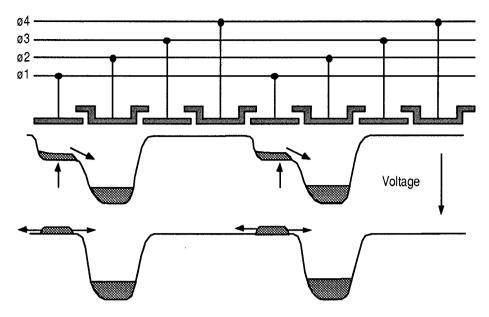

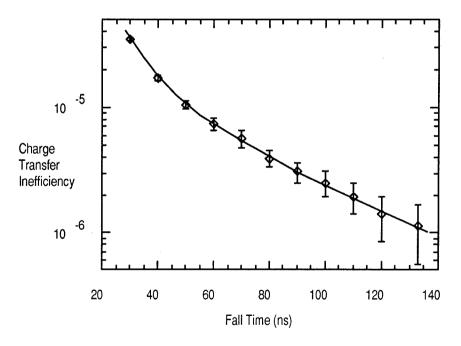

An easily controllable source of transfer inefficiency is fast clock edge rates. The dynamics of the fluid-like charge cause it to equilibrate with a design-dependent time constant as discussed in Section 2.3. Referring to Figure 2.3, if a gate voltage transition occurs quicker than the charge can equilibrate, a small amount of charge can be transferred backwards in a shift register operation [Singh et al., 1974]. This results in a smearing of the charge encoded data residing in the shift register. In practice, gate voltage fall times must be limited to prevent this type of transfer inefficiency. An experimental measurement of transfer efficiency loss is shown in Figure 2.4 where a buried channel shift register was clocked with a variable edge rate clock.

**Figure 2.3.** Incomplete charge transfer caused by rapid clock voltage fall times. If clock voltages fall too quickly, charge remaining in the collapsing well will not have time to transfer completely, causing the remaining charge to diffuse along the channel and corrupt the stored information.

Figure 2.4. Experimental charge transfer inefficiency as a function of fall time. The test was performed on a 724 stage buried channel shift register with 8um channel length per phase at 1MHz clock frequency. The fall time of only one clock phase was varied -- the other three phases were held at a constant rise/fall time of 200ns.

Another less controllable form of charge loss is caused by electron traps, which are very dense at the substrate/oxide interface. If charge is introduced into a previously empty CCD shift register, the traps under each gate will capture a fraction of the electrons from the first charge packet. These electrons are randomly released from the traps at various later times with time constants ranging out to milliseconds. The charge retention behavior of the traps tends to smear out information between charge packets after they have been shifted many times. By encoding the zero signal level at some finite amount of charge [Strain, 1972] (a technique called 'fat zero') some of the traps are kept constantly filled and the overall CTE can be improved.

Errors also arise from thermal generation of charge in the substrate which causes potential wells to slowly fill. The quality of the substrate and fabrication process heavily influences this effect. In CCD cameras, a non-illuminated CCD will integrate this thermal charge and output an image of the thermal generation current, which is commonly called 'dark current'. Due to the fabrication dependent nature of the generation sites, the patterns of dark current seen on wafer scale plots are often large swirls, the remnants of a spin-on fabrication step. Locally, over a few pixels distance, the dark current is relatively uniform except where there are crystal dislocation faults, which cause large dark current spikes [Howes et al., 1979]. In signal processing designs, the effect of dark current can be effectively canceled out to first order by implementing differential charge storage.

Charge levels are easily controlled in signal processing CCD circuits to implement the 'fat zero' technique to improve CTE. Clock edge rates are also easily controlled to improve CTE. However, a certain amount of CTE loss always exists and must be considered when designing large signal processing architectures where many transfers are needed.

#### 2.5 Surface Channel Devices

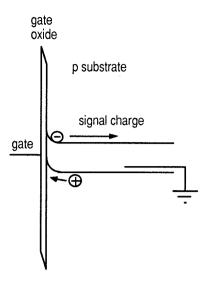

The simple shift register described in section 2.2 is called a surface channel CCD in which the signal charge resides at the substrate/oxide interface. An optimal clock voltage range can be determined from analysis of the device. With respect to low clock voltages, the intent of a low voltage on the gate is to prevent charge from moving along the channel. The charge barrier along the channel obviously cannot be lower than the intrinsic barrier of the substrate, or else charge will be injected into the substrate, so it makes no sense to lower gate voltages below ground. Furthermore, the surface channel CCD gate voltage must remain above zero to prevent any charge at the oxide interface from being injected into the substrate and to prevent holes from accumulating A 'softer' limit for surface channel devices is to at the interface, as depicted in Figure 2.5. require that the gate voltages should always be above V<sub>T</sub>, the inversion threshold of the substrate, to ensure that the depletion region boundary remains at least a fixed minimum distance from the interface [Singh et al., 1976]. A more negative gate voltage during one of the clock phases can eject trapped charge into the substrate or accumulate holes which rapidly recombine with trapped signal electrons, causing net charge loss. Transmission line effects, which result in ringing of long clock electrodes, can cause the gate voltage to momentarily dip below ground and must be considered for fast circuits. It is also important to control the size of CCD gates properly. If a large charge packet is moved under a small gate, charge will spill out into adjacent cells or the substrate. For a positive voltage limit, surface channel devices have an upper gate voltage limit which is determined by the breakdown voltage of the oxide, a limit that is rarely reached in practice.

**Figure 2.5.** Slightly negative clock voltages cause electron injection into the substrate. Holes can also accumulate at the surface, resulting in recombination and charge loss. Fast edge rates and negative clock voltages can result in significant loss of charge to the substrate.

In addition to preventing ringing, slew rate limited clock drivers are essential to proper operation of surface channel CCD circuits. The backflow of charge caused by rapid fall times can significantly impact CTE as discussed in Section 2.3 and in [Singh et al., 1974], especially in devices such as the surface channel CCD where fringing fields are low. The slew limits required for near optimal CTE are the dominant factor in determining the maximum clock rate of the device.

#### 2.6 Buried Channel Devices

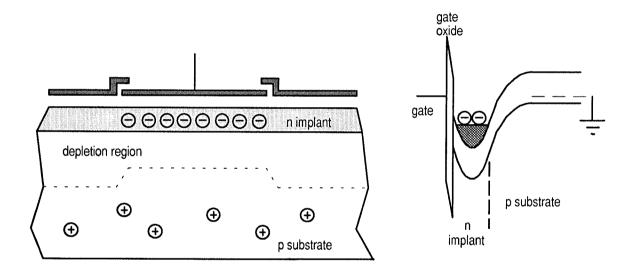

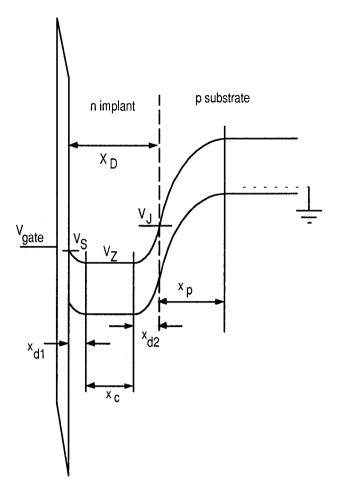

A clever fabrication enhancement can significantly improve the CTE and speed of surface channel devices by forcing the charge to travel beneath the surface in a 'buried channel' [Walden et al., 1972][Kim et al., 1972][Esser, 1972]. By introducing a weak n-type implant at the substrate surface beneath the gates, the potential energy bands can be made to curve the opposite direction near the surface, shown in Figure 2.6. The solution to the one-dimensional Poisson equation with the depletion approximation (i.e., uniform space charge) is a parabola with the curvature dependent

on the sign of the space charge. A representative energy band diagram of the structure under operating conditions is shown in Figure 2.6. Note that the potential minimum has been shifted beneath the substrate surface which causes signal charge to travel beneath the surface, effectively isolating the charge packets from the oxide/substrate interface traps. Buried channel CCDs are widely used in commercial imagers since they permit high speed operation and high transfer efficiency. However, buried channel devices often require clock voltages that are outside the normal TTL voltage levels and cannot easily be generated on-chip. The tradeoffs between buried channel and surface channel CCDs are extremely system dependent, since computing architectures can be designed to counter the effects of the poor CTE and low speed of surface channel devices.

**Figure 2.6.** The buried channel CCD implant causes the potential minimum to move away from the surface. Charge introduced into the channel resides beneath the surface and encounters fewer traps than surface channel devices which results in improved transfer efficiency. In addition, the higher fringing fields of buried channel devices allow much higher clock frequencies.

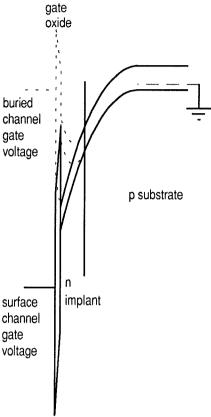

Voltage levels required for buried channel devices are somewhat different than those for surface channel CCDs. As shown in Figure 2.7, the introduction of the n-type implant beneath the gates reverses the sign of electric field in the gate oxide. Thus to achieve similar potential minimums, the

buried channel gate voltage must be significantly less than the surface channel gate voltage.

**Figure 2.7.** Buried channel gate voltages compared to surface channel gate voltages. The n implant reverses the sign of curvature of the bands, resulting in opposite sign field in the oxide. For equivalent depth potential wells, the buried channel voltage is significantly lower than that of the surface channel device.

Buried channel devices have a more complicated set of voltage limits. In practice, the buried channel n-type implant is positively biased through taps at the ends of the CCD channel so that the n-implant is completely depleted. The potential minimum in the semiconductor with no charge can be calculated using the depletion approximation. The equations presented here follow [Beynon et al., 1980]. Assuming a gate voltage  $V_{\text{gate}}$  and a uniform n-type implant of  $N_{\text{D}}$  density and  $X_{\text{D}}$  depth with a substrate doping of  $N_{\text{A}}$ , the voltage is given by the solution of the one-dimensional Poisson Equation

$$\frac{\mathrm{d}^2 V}{\mathrm{d}x^2} = -\frac{q(N_+ - N_-)}{\varepsilon_{\mathrm{si}}} \tag{2.4}$$

which, when integrated twice results in the general solution

$$V = -\frac{q(N_{+} - N_{-})x^{2}}{2\varepsilon_{si}} + C_{1}x + C_{0}$$

(2.5)

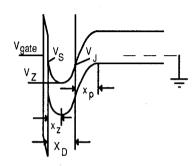

Figure 2.8. Buried channel energy band diagram. The potential minimum of the channel,  $V_Z$ , is located at a depth  $X_Z$  from the substrate surface.

When there is no charge in the channel, the buried channel n-implant is completely depleted and its maximum voltage can be calculated as a function of the gate voltage. Using the distances and voltages labeled in Figure 2.8 and starting from the right (i.e., the substrate), the potential at the metallurgical junction,  $V_{\rm J}$ , can be written as

$$V_{J} = \frac{qN_{A}X_{p}^{2}}{2\varepsilon_{Si}}.$$

(2.6)

The electric field between the n-implant and p-substrate must be continuous, which requires

$$\frac{qN_AX_p}{\varepsilon_{si}} = E_J = \frac{qN_D(X_D - X_Z)}{\varepsilon_{si}}.$$

(2.7)

The potential minimum of the channel (i.e., maximum voltage,  $V_z$ ) is given by

$$V_{Z} = \frac{qN_{A}X_{p}^{2}}{2\varepsilon_{Si}} + \frac{qN_{D}(X_{D} - X_{Z})^{2}}{2\varepsilon_{Si}}.$$

(2.8)

Continuing left, the voltage at the oxide/substrate interface is given by

$$V_{\rm S} = V_{\rm Z} - \frac{q N_{\rm D} X_{\rm Z}^2}{2\varepsilon_{\rm Si}}.$$

(2.9)

Setting the displacement fields equal across the interface results in

$$qN_DX_Z = D_S = \frac{(V_S - V_{Gate})}{t_{ox}} \varepsilon_{SiO_2}.$$

(2.10)

These equations can be manipulated to solve for the maximum channel voltage,  $V_Z$  [Séquin et al., 1975][Beynon et al., 1980].

$$\begin{split} V_Z &= \frac{q\epsilon_{Si}N_A \left(N_A + N_D\right)}{2N_D} \Bigg[ \sqrt{\beta^2 + \frac{2}{N_A\epsilon_{Si}} \bigg( \frac{V_{Gate}}{q} + N_D X_D \bigg( \beta - \frac{X_D}{2\epsilon_{Si}} \bigg) \bigg)} - \beta \, \Bigg]^2 \\ \text{where} \quad \beta &= \frac{t_{ox}}{\epsilon_{SiO_2}} + \frac{X_D}{\epsilon_{Si}} \, . \end{split} \tag{2.11}$$

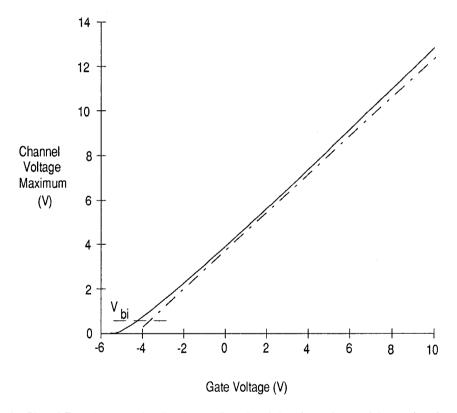

Channel voltage thus depends nonlinearly on the gate voltage, the non linearity being most severe when the gate voltage is at its most negative. This function is plotted in Figure 2.9 along with a straight-line reference for the fabrication process listed in Table 2.1. The lower limit of channel voltage is the 'built-in' potential of the channel-substrate diode,  $V_{\rm bi}$ .

| N A             | 1x10 <sup>15</sup>     |

|-----------------|------------------------|

| ND              | 3.5x10 <sup>16</sup>   |

| t ox            | 450Å <b>°</b>          |

| ε <sub>Si</sub> | 9.74x10 <sup>-13</sup> |

| εSiO 2          | 2.66x10 <sup>-13</sup> |

| V <sub>bi</sub> | 0.67V                  |

| Х <sub>D</sub>  | 0.3um                  |

**Table 2.1.** Process parameters of the 2um buried channel CMOS process used in this thesis. The effective uniform channel doping N<sub>D</sub> is calculated from measurements of the depletion mode FET formed by the channel.

Figure 2.9. Plot of Equation 2.11 showing the nonlinearity of the channel potential as a function of gate voltage along with a straight-line reference. The channel voltage cannot go below  $V_{\rm bi}$ , since this would forward bias the implant/substrate diode and cause hole accumulation.

To determine the operating conditions for CCDs, the analysis found in [Séquin et al.,

1975][Beynon et al., 1980] is extended here. The voltage limits determined in what follows are not generally known and are of practical importance. The minimum gate voltage for a buried channel device occurs when the channel voltage maximum,  $V_Z$ , equals the built in voltage,  $V_{bi}$ , of the implant-substrate diode, which is given by [Sze, 1985]

$$V_{bi} = \frac{kT}{q} \ln \left( \frac{N_A N_D}{n_i^2} \right). \tag{2.12}$$

The gate voltage with  $V_Z = V_{bi}$  as shown in Figure 2.10 is given by

$$V_{\text{gate}}^{\text{(min)}} = V_{\text{bi}} - \frac{qN_{\text{D}}}{2\varepsilon_{\text{Si}}} X_{z}^{2} - \frac{qN_{\text{D}}t_{\text{ox}}}{\varepsilon_{\text{SiO}_{2}}} X_{z}, \qquad (2.13)$$

where  $\boldsymbol{X}_{Z}$  is the potential minimum distance from the surface for the potential minimum of  $\boldsymbol{V}_{bi}$

$$X_{z} = X_{D} - \sqrt{\frac{2\varepsilon_{Si}V_{bi}}{qN_{D}\left(1 + \frac{N_{D}}{N_{A}}\right)}}$$

(2.14)

which for the fabrication process listed in Table 2.1 results in

$$V_{\text{gate}}^{(\text{min})} \approx -4v. \tag{2.15}$$

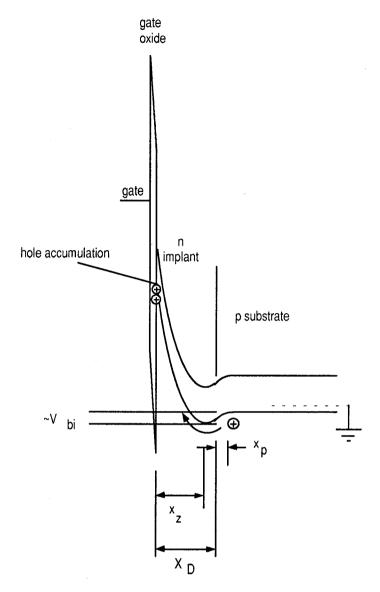

**Figure 2.10.** Past the minimum gate voltage, holes can jump the barrier and accumulate at the surface. Electrons in the well are injected into the substrate. More negative voltages are completely compensated by hole accumulation at the surface and only result in increased electric field across the oxide.

For more negative gate voltages, any charge left under the gate will be pushed into the substrate via the forward biased diode and holes are allowed to accumulate at the surface, as shown in Figure 2.10. As with the surface channel CCD, the minimum gate potential is intended to act as a barrier to the flow of charge along the channel. The minimum gate voltage described by Equation 2.13 presents the same barrier as the substrate, hence lower gate voltages are not beneficial. A two-

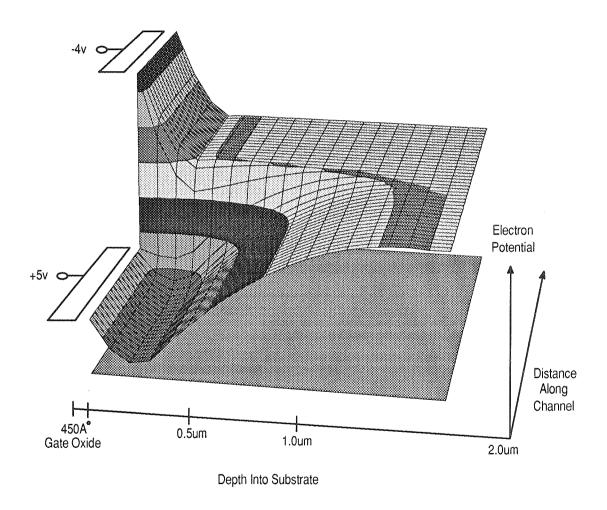

dimensional Poisson simulation of the process of Table 2.1 is shown in Figure 2.11 with two gates, one at a positive voltage and the other at the voltage given by Equation 2.15. Further reducing the gate voltage would cause holes to accumulate at the interface, as shown in Figure 2.10, which would compensate for any additional negative gate voltage changes. Thus lower gate voltages would not modify the potential well diagram of Figure 2.11 and would only cause hole accumulation at the surface, which can adversely impact performance.

Figure 2.11. Simulated electron potential well diagram of the process listed in Table 2.1 with +5 and -4v gates and no charge. The -4v gate should not be lowered further since hole accumulation at the surface would compensate for any additional negative gate voltage excursion.

This negative gate voltage limit is not found in the literature and has added to the misconception

that CCDs are unpredictable and that finding proper operating voltages is a special art.

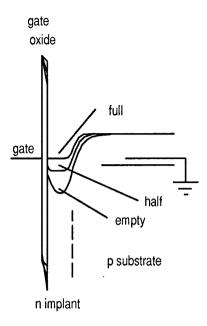

In order to elucidate the maximum allowable clock voltages, the behavior of the device with a charge packet needs to be analyzed. When charge is introduced into a buried channel device, a portion of the n implant returns to its undepleted neutral state. Electrons in buried channel devices are majority carriers and have a charge density equal to the doping density of the n-implant. The charge packet has a physical volume and depth from the surface determined by the doping profile of the implant, the gate voltage and the number of electrons in the charge packet. This is in sharp contrast to surface channel devices in which electrons are minority carriers and aggregate in a thin sheet of charge at the oxide/substrate interface with much higher charge density. A diagram showing a buried channel with some charge is shown in Figure 12. The neutral region (i.e., flat band) in the middle of the implant is the signal charge. Its width,  $X_{\rm C}$ , determines the amount of charge in the packet, namely

$$Q = qX_{C}AN_{D}$$

(2.16)

where A is the area of the gate. The potential of the channel holding charge Q and with gate voltage  $V_{\text{gate}}$  can be easily calculated using a similar procedure to that used above and the nomenclature of Figure 2.11.

Figure 2.12. Buried channel band diagram with charge. The charge packet forms a neutral region in the n implant that has a charge density equal to that of the doping density. This packet occupies physical volume in contrast to surface channel devices in which charge resides in a thin sheet at the oxide/substrate interface.

The sum of the depleted and neutral region thicknesses in the implant are constrained by

$$X_{d1} + X_{d2} + X_c = X_D. (2.17)$$

The surface voltage can be calculated from these quantities using the depletion approximation, giving

$$V_{s} = V_{J} + V_{Z} - \frac{qN_{D}X_{d1}^{2}}{2\varepsilon_{si}} = \frac{q}{2\varepsilon_{si}} \left(N_{A}X_{p}^{2} + N_{D}\left(X_{d2}^{2} - X_{d1}^{2}\right)\right). \tag{2.18}$$

Using the electric field at the substrate-oxide interface, we can calculate the gate voltage given the

thickness of the oxide and its permittivity as before

$$V_{\text{gate}} = V_{\text{s}} - \frac{t_{\text{ox}} q N_{\text{D}}}{\varepsilon_{\text{SiO}_2}} X_{\text{dl}}$$

(2.19)

The fact that the electric field is zero inside the charge packet requires

$$N_{\rm D}X_{\rm d2} = N_{\rm A}X_{\rm p} \tag{2.20}$$

which gives the gate voltage as a function of the signal charge

$$V_{\text{gate}} = \frac{qN_{\text{D}}}{2\varepsilon_{\text{si}}} \left[ \left( 1 + \frac{N_{\text{D}}}{N_{\text{A}}} \right) \left( X_{\text{D}} - \frac{Q_{\text{sig}}}{qAN_{\text{D}}} - X_{\text{d1}} \right)^{2} - X_{\text{d2}}^{2} \right] - \frac{t_{\text{ox}}qN_{\text{D}}X_{\text{d1}}}{\varepsilon_{\text{SiO}_{2}}}.$$

(2.21)

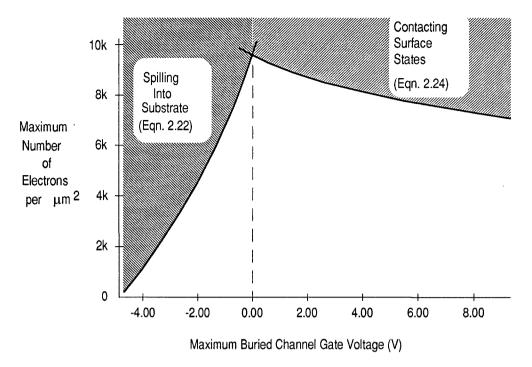

Equations 2.16-2.21 parallel those found in one of the basic texts on CCDs [Séquin et al., 1975][Howes et al., 1979][Beynon et al., 1980]. The limitations of upper clock voltages is briefly touched upon in [Gunsagar et al., 1973] and [Howes et al., 1979], but in inadequate detail. In what follows, a detailed analysis of the limitation of upper clock voltages is developed from equations 2.16-2.21. With respect to maximum gate voltages, the common wisdom is that the more positive the gate voltages, the larger the maximum signal charge packet [Esser, 1972][Beynon et al., 1980]. A voltage limit does exist, however, and it is not simply determined by oxide breakdown. To start, a plot of the maximum charge capacity as a function of voltage is shown in Figure 2.13, which has two different phenomena responsible for its shape which are explained below.

**Figure 2.13.** Theoretical maximum charge packet size as a function of positive gate voltage swing. The gate voltage is with respect to the flat band gate voltage of Figure 2.1(a). For gate voltages less than the flat band voltage, charge added to the channel will spill into the substrate. For higher gate voltages, contact with surface states limits the charge packet size.

Starting from the left of Figure 2.13 where the gate voltage does not swing very high, the channel charge capacity is limited by charge spilling into the substrate. This occurs when the channel potential with charge Q reaches the built in diode voltage,  $V_{\rm bi}$ . Adding more charge forward biases the substrate diode and leads to charge loss. This limit restricts the channel charge capacity. Given that the gate voltage is defined as zero in the flat band condition of Figure 2.1(a) and using Equations 2.16-2.21, the maximum charge capacity as a function of gate voltage is derived

$$Q_{\text{max}} = AN_{D} \left( X_{D} - X_{\text{bi}} - \frac{t_{\text{ox}} \varepsilon_{\text{Si}}}{\varepsilon_{\text{SiO}_{2}}} \left( \sqrt{1 - \frac{2\varepsilon_{\text{SiO}_{2}}^{2} V_{\text{gate}}}{q N_{D} \varepsilon_{\text{Si}} t_{\text{ox}}^{2}}} - 1 \right) \right) \qquad V_{\text{gate}} < 0$$

(2.22)

where the built-in depletion width to the left of the metallurgical junction,  $X_{\rm bi}$ , is given by

$$X_{bi} = \sqrt{\frac{2\varepsilon_{Si}V_{bi}}{qN_{D}\left(1 + \frac{N_{D}}{N_{A}}\right)}}.$$

(2.23)

Note that when the gate voltage is at zero, the channel is completely neutral except for the intrinsic diode depletion. Greater gate voltages invoke the next limiting situation which occurs when signal charge introduced into the buried channel comes in contact with the interface traps, which causes a loss of transfer efficiency. As shown in Figure 2.14, for larger amounts of signal charge, the boundary of the upper depletion region moves closer to the surface. The maximum gate potential is directly related to the maximum charge capacity if the interface traps are to be avoided. From Equations 2.16-2.21 the maximum charge packet that avoids interface traps is given by

$$Q_{\text{max}} = AN_{D} \left( X_{D} - \sqrt{\frac{2\varepsilon_{Si} \left( V_{\text{gate}} + V_{\text{bi}} \right)}{qN_{D} \left( 1 + \frac{N_{D}}{N_{A}} \right)}} \right) , \quad V_{\text{gate}} > 0 . \tag{2.24}$$

**Figure 2.14.** Buried channel potential diagram. As the channel fills up, the charge can come in contact with surface states which degrade CTE to that of a surface channel device.

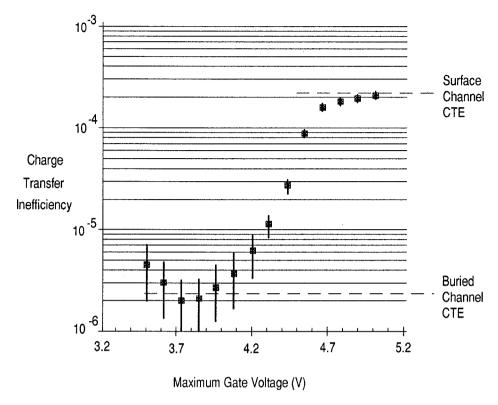

To see the effects on charge transfer efficiency, an experiment was performed on a buried channel shift register. A near maximum size charge packet with near optimal CTE was introduced into the shift register and the maximum voltage of the four-phase clock was varied. The result, shown in Figure 2.15 demonstrates the charge packet coming in contact with interface states.

Figure 2.15. Experimental charge transfer loss as a function of maximum gate voltage showing effect of surface states on buried channel performance. A constant size charge packet was input into a buried channel CCD shift register while the maximum voltages of the four central clock lines were varied. Above ~4.2v for this particular size charge packet, the charge comes in contact with surface states which degrade the performance to that of a surface channel device.

As can be seen, higher gate voltages reduce the charge handling capability of the buried channel CCD, a result which is not found in the literature. However, higher gate voltages also increase the fringing fields in Equation 2.2 and hence speed up operation. For imagers where charge packet size is rarely near maximum, the upper gate voltage limit is not restrictive in practice. In signal processing devices, however, the charge packets are of user controllable size and these limits must be understood.

The restricted voltage swing of the buried channel devices typically requires clock drivers which are able to pulse gate voltages lower than the substrate voltage. Unfortunately, this often prevents the inclusion of on-chip clock generation due to the nature of the fabrication process.

#### 2.7 Charge Input

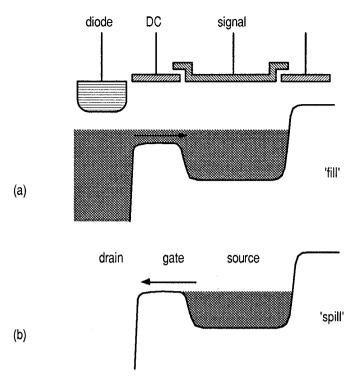

A number of structures exist for the creation of a charge packet based on a voltage level. One circuit in particular will be examined here as it has the best noise performance and is used almost exclusively in the field for CCD charge input. The circuit consists of an input diode and two gates which set the size of the charge packet, as shown in Figure 2.16, and is called a *potential equilibration* circuit or more commonly a 'fill-and-spill' circuit [Carnes et al., 1973][Tompsett et al., 1973][Tompsett, 1975]. The operation of the device occurs in two phases. In the fill phase, the diode supplies electrons up to a certain potential level and fills the structure above the potentials of the DC and Signal gates, as in Figure 2.16(a). The second phase occurs when the diode potential is dropped and charge spills back out of the region, shown in Figure 2.16(b). The charge left underneath the signal gate is proportional to the channel potential level difference between the Signal and DC gates. Once the charge packet is created, it can be shifted to the right using a CCD shift register.

Figure 2.16. Potential equilibration charge input structure. During the 'fill' phase, the input diode is pulse to a low voltage to inject electrons into the channel. The diode is then returned to a high voltage, causing excess electrons to flow out of the channel, leaving a charge packet proportional to the difference of the DC and signal gates. The operation can also be thought of in terms of an n-channel MOSFET device where the drain is the input diode, the DC CCD gate acts as the gate and the substrate beneath the signal gate acts as the source. The 'fill' phase is an 'on' transistor with mobile charge in the channel. When the diode (drain) is pulled high, the substrate beneath the signal gate (source) goes as high as the gate will let it until the transistor shuts 'off' due to lack of gate-source voltage.

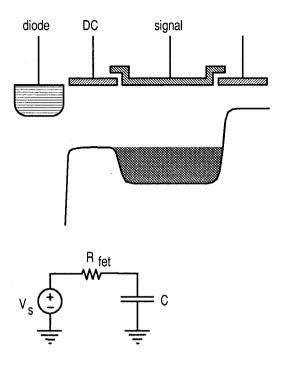

This device exhibits the same noise qualities of the switched capacitor storage device mentioned in Chapter 1 and is fully examined in [Mohsen et al., 1975]. The DC gate acts as the FET and the Signal gate as the storage capacitor. The noise analysis of the fill-and-spill circuit is the same as that for a Johnson noise calculation of a RC circuit. When the circuit is in the spill phase, the finite channel resistance underneath the DC gate exhibits Johnson noise which is given by

$$\overline{V}_{r}^{2}df = 4kTR_{fet}df \qquad (2.25)$$

where  $\overline{V}_r^2$  is the mean squared thermal voltage of the equivalent resistor in the bandwidth df. The equivalent circuit is shown in Figure 2.17.

**Figure 2.17.** Equivalent circuit of the 'fill and spill' circuit for noise analysis. The finite 'on' resistance of the FET channel underneath the DC gate contributes a Johnson noise component to the forming charge packet.

Passed through the low-pass filter of Figure 2.17 results in a noise voltage on the capacitor in band df of

$$\overline{V}_{c}^{2} df = \frac{4kTR_{fet}}{1 + \omega^{2}C^{2}R_{fet}^{2}} df \qquad (2.26)$$

The integral of the response of the RC circuit over all frequencies results in the well known noise voltage

$$\overline{V}_{n}^{2} = \int_{0}^{\infty} \overline{V}_{c}^{2} df = \frac{kT}{C}$$

(2.27)

Note that the resistance of the channel does not influence the noise of the circuit. Another source

of noise is the phenomena of charge splitting, where charge left under the DC gate is split, with the noise level determined by how much remains under the Signal gate.

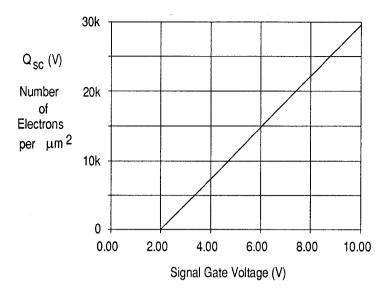

The linearity of the fill-and-spill circuit, i.e., voltage to charge linearity, can be calculated to first order by finding the  $Q_{\rm sig}$  that results from a given voltage difference on the two gates of the circuit of Figure 2.16. For surface channel devices, the charge at the interface can be modeled as a thin sheet of charge,  $Q_{\rm sig}$ . The amount of charge left behind in the spill phase adjusts the surface potential under the signal gate until it equals that of the DC gate. For different signal voltages, the surface voltage remains the same -- only the amount of charge changes. The charge is thus linearly proportional to the signal gate voltage

$$Q_{\text{sig}} = \frac{A\varepsilon_{\text{SiO}_2}}{t_{\text{ox}}} \left( V_{\text{gate}}^{\text{sig}} - V_{\text{gate}}^{\text{dc}} \right)$$

(2.28)

the proportionality constant being the characteristic capacitance of the oxide. Note that the nonlinearities of the MOS capacitor are not present, simply due to the fact that the depletion regions under the DC and Signal gates are the same depth after the spill phase regardless of signal charge size. A plot is given in Figure 2.18 using the process parameters listed in Table 2.1. Nonlinearities occur in practice due to dynamic fluctuations and channel widening in the two dimensions not covered in this analysis which limit the performance to approximately 50-60dB linearity [Mohsen et al., 1975].

Figure 2.18. Simulated linear charge generation with the surface channel fill-and-spill circuit. The DC gate is held at 2V. The proportionality between charge and voltage is simply the oxide capacitance ( $C_{ox} = t_{ox} / \epsilon_{SiO_2}$ ). Second-order effects such as dynamic fluctuations and channel widening limit linearity to < 60dB in practice.

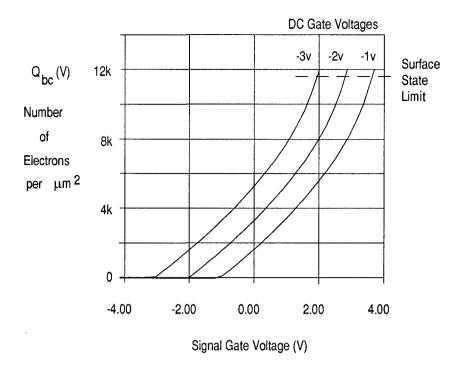

For the buried channel device, the calculations require more algebra and yield

$$Q_{sig} = qAN_{D} \left[ X_{D} - \sqrt{\frac{2\epsilon_{Si}V_{Z}^{dc}}{qN_{D}\left(1 + \frac{N_{D}}{N_{A}}\right)}} + \frac{t_{ox}\epsilon_{Si}}{\epsilon_{SiO_{2}}} - \epsilon_{Si}\sqrt{\left(\frac{t_{ox}}{\epsilon_{SiO_{2}}}\right)^{2} - \frac{2\left(V_{gate}^{sig} - V_{Z}^{dc}\right)}{qN_{D}\epsilon_{Si}}} \right]$$

(2.29)

where  $V_Z^{dc}$  is the potential minimum of Equation 2.11 for the DC gate. A family of curves is plotted in Figure 2.19 for the process listed in Table 2.1. Due to the inherent linearity of surface channel devices, they are preferentially used for charge input. It is common in signal processing devices to use surface channel input structures with buried channel transfers [Wen, 1976]. The conversion functions shown in Figures 2.18 and 2.19 are labeled  $Q_{sc}(V)$  and  $Q_{bc}(V)$  for surface channel and buried channel, respectively, for use in later chapters.

**Figure 2.19.** Simulated charge generation linearity for a buried channel fill-and-spill circuit is shown for various DC gate voltages for the process of Table 2.1. The nonlinearity is due to the depletion depth changes which significantly modify the total capacitance seen by the charge.

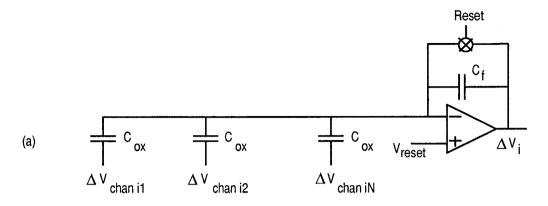

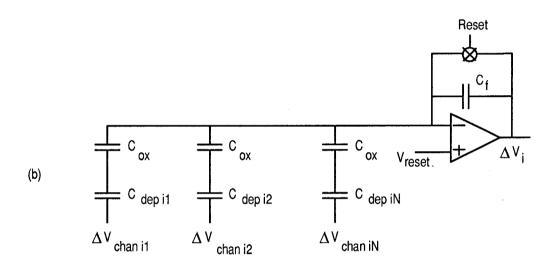

# 2.8 Charge Output

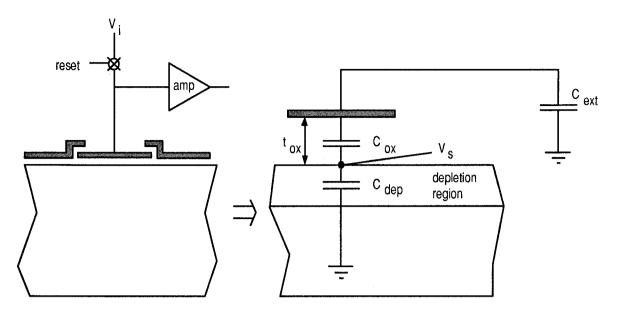

CCD output circuits convert a charge packet to a voltage, usually by transferring the charge packet of interest onto a capacitor, which experiences a voltage change. This capacitor is typically either a floating diffusion or a floating gate [Engeler et al., 1970][Séquin et al., 1975]. Diffusion sensing destroys the charge packet being sensed, making it less attractive for signal processing where utilization of the same charge for many computations is required. For the purposes of this thesis, floating gate sensing is examined exclusively as it provides the nondestructive sensing required for the signal processing devices discussed in later chapters. The equivalent circuit of Figure 2.20 is used to analyze the charge-to-voltage conversion.

49

**Figure 2.20.** In the floating gate charge sensing output circuit the sense gate is reset to a known voltage then the charge is moved beneath it. The charge sees a capacitance shown in the model to the right and produces a surface voltage change. The surface potential change is seen at the output through the capacitive divider formed by the oxide and external capacitances.

In operation, the sense gate is reset to a particular voltage,  $V_i$ , with no charge beneath it and then allowed to float. When the charge is transferred underneath the sense electrode by the action of the neighboring gates, the sense electrode experiences a voltage change.  $C_{\rm ext}$  is the parasitic capacitance of the sensing gate which includes all sidewall and amplifier input capacitance. Because the depletion boundary changes with the amount of charge present, the capacitance to the substrate introduces a nonlinear component into the charge-to-voltage conversion. In the surface channel device of Figure 2.20, the capacitance the signal charge sees [Séquin et al., 1975] is given by

$$C_{tot}(V_S) = \frac{C_{ox}C_{ext}}{C_{ox} + C_{ext}} + C_{dep}(V_S)$$

(2.30)

The depletion layer capacitance depends on the surface potential,

$$V_{\rm S} = \frac{qN_{\rm A}}{2\varepsilon_{\rm Si}} X_{\rm p}^2 \tag{2.31}$$

which inserted into

$$C_{dep}(V_S) = \frac{A\varepsilon_{Si}}{X_p}$$

(2.32)

results in

$$C_{\text{dep}}(V_{\text{S}}) = A \sqrt{\frac{q N_{\text{A}} \varepsilon_{\text{Si}}}{2 V_{\text{S}}}}$$

(2.33)

Adding dQ charge into the channel causes a voltage change via the relationship

$$dQ = C_{tot}(V_S)dV_S (2.34)$$

Integrating from the surface potential to the final surface potential

$$Q_{\text{sig}} = \int_{V_{i}}^{V_{f}} \left( \frac{C_{\text{ox}} C_{\text{ext}}}{C_{\text{ox}} + C_{\text{ext}}} + A \sqrt{\frac{q N_{A} \varepsilon_{\text{Si}}}{2 V}} \right) dV$$

(2.35)

results in the following expression for the change in surface potential when solved for the channel potential change  $\Delta V_s$ .

$$\Delta V_{S} = V_{f} - V_{i} \cong V_{i} \left[ \frac{Q_{sig}}{\beta V_{i} + \frac{\alpha \sqrt{V_{i}}}{2}} + \frac{Q_{sig}^{2}}{8\alpha^{2}V_{i} \left[ \frac{\beta \sqrt{V_{i}}}{\alpha} + \frac{1}{2} \right]^{3}} + \dots \right]$$

$$\alpha = A\sqrt{2qN_{A}\epsilon_{Si}} \qquad \beta = \frac{C_{ox}C_{ext}}{C_{cx} + C_{cx}}$$

(2.36)

The output voltage that enters the amplifier is related to the channel potential change of Equation 2.36 through the capacitive divider

$$\Delta V_{\text{out}} = \Delta V_{\text{S}} \frac{C_{\text{ox}}}{C_{\text{ox}} + C_{\text{ext}}}$$

(2.37)

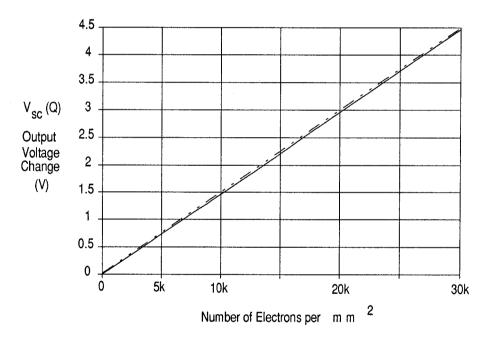

The relationship between charge and output voltage is graphed in Figure 2.21 for a reset voltage of 5v along with a straight line reference. In later chapters this function for surface channel devices is referred to as  $V_{\rm sc}(Q)$ .

Figure 2.21. Simulated voltage output linearity of surface channel floating gate sense circuit for the process of Table 2.1 which is reset to an initial voltage of 5v. The parasitic capacitance  $C_{\rm ext}$  is 100fF. The nonlinear depletion capacitance limits accuracy to ~ 40dB.

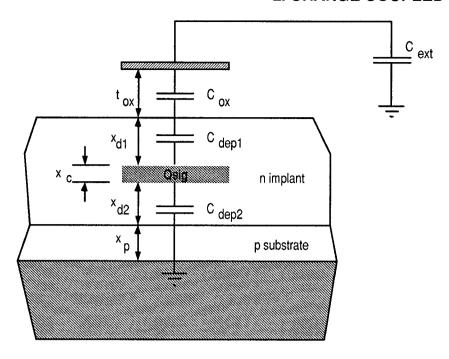

**Figure 2.22.** Buried channel sensing has to contend with two depletion depths, one above and the other below the charge packet. The additional nonlinear capacitors depend strongly on reset voltage and add significantly more nonlinearity compared to surface channel devices.

For the buried channel device, the analysis follows a similar path. Complications arise because the signal charge is spatially distributed in the channel which leads to additional capacitance variations. The model used in this analysis of the buried channel output circuit is shown in Figure 2.22. Because the potential within the charge packet is uniform, it acts as a single node whose capacitance to ground is given by

$$C_{tot} = \frac{1}{\frac{1}{C_{dep1}} + \frac{1}{C_{ox}} + \frac{1}{C_{ext}}} + C_{dep2}$$

(2.38)

The depletion layer thicknesses are given by

$$X_{d2} + X_{p} = \sqrt{\frac{2}{q} \left( \frac{1}{N_{D}} + \frac{1}{N_{A}} \right)} \varepsilon_{Si} V_{chan}$$

(2.39)

and

$$X_{d1} = X_{D} - X_{d2} + \frac{Q_{sig}}{qAN_{D}}$$

(2.40)

so that the capacitance of the signal charge region as a function of channel voltage and charge is

$$C_{tot} = \frac{1}{\frac{1}{C_{ext}} + \frac{t_{ox}}{A\epsilon_{SiO_2}} + \frac{X_D - \sqrt{\frac{2\epsilon_{Si}V_{chan}}{qN_D(1 + N_D/N_A)} + \frac{Q_{sig}}{qAN_D}}{A\epsilon_{Si}}}{A\epsilon_{Si}} + A\sqrt{\frac{q\epsilon_{Si}}{2V_{chan}\left(\frac{1}{N_D} + \frac{1}{N_A}\right)}}.$$

(2.41)

The numerical solution to the differential equation governing the charge to voltage relationship

$$\frac{\mathrm{dQ}}{\mathrm{dV}_{\mathrm{chan}}} = C_{\mathrm{tot}}(Q, V_{\mathrm{chan}}) \tag{2.42}$$

results in the channel potential change,  $\Delta V_{\text{chan}}$  due to the added charge. The voltage seen at the output is through the capacitive divider

$$\Delta V_{\text{out}} = \Delta V_{\text{chan}} \frac{1}{1 + C_{\text{ext}} \left( \frac{1}{C_{\text{dep1}}} + \frac{1}{C_{\text{ox}}} \right)}.$$

(2.43)

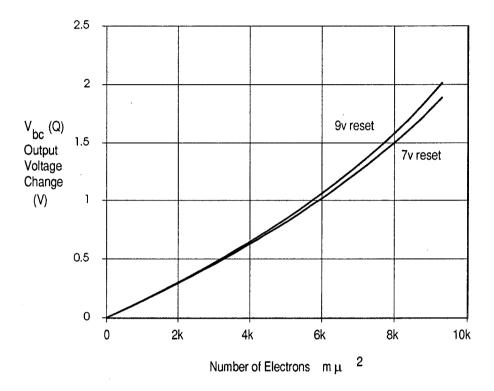

and is shown in Figure 2.23 for various initial sense gate voltages given the process of Table 2.1. This buried channel charge to voltage function is labeled  $V_{\infty}(Q)$  for future use. As can be seen,

the linearity of the buried channel is significantly less than that of the surface channel CCD. The cause is simply the increased role of the voltage dependent depletion layer capacitances in  $C_{tot}$ . Also, the voltage change for the maximum size charge packet is significantly less than that of the equivalent surface channel device of Figure 2.21.

Figure 2.23. A numerical simulation of the buried channel sensor output voltage as a function of charge for two different reset voltages for the process listed in Table 2.1 and an external capacitance of 100fF. The nonlinear capacitance of the channel varies with reset voltage resulting in different Q-V transform curves.

It is important to choose operating conditions, such as reset voltage and limited charge packet sizes, to optimize linearity. In the architectures discussed in the following chapters, the operating points have other constraints and such optimizations are not always possible.

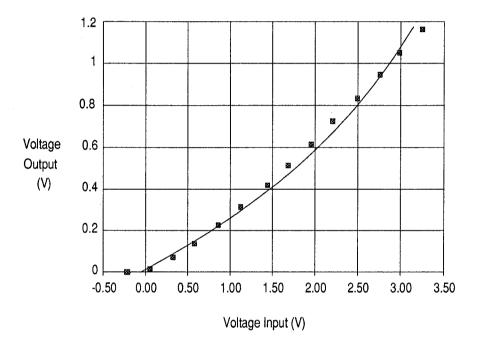

A complete voltage-to-charge and back to voltage conversion adds significant nonlinearities to any

signal processing system. Figure 2.24 shows the simulated and measured input and output curves for a buried channel CCD shift register. By choosing different operating points for the charge input and output circuits, the shape of the response can be modified somewhat. The nonlinearity shown in Figure 2.24 illustrates the points that the buried channel devices are not inherently linear and that the plethora of user defined operating parameters have significant effects on linearity.

**Figure 2.24.** Experimental voltage-charge-voltage conversion of a buried channel CCD. Experimental data taken at 1MHz shift rate with an input DC gate of -0.3v, a reset voltage of 9v and an estimated parasitic capacitance of 100fF.

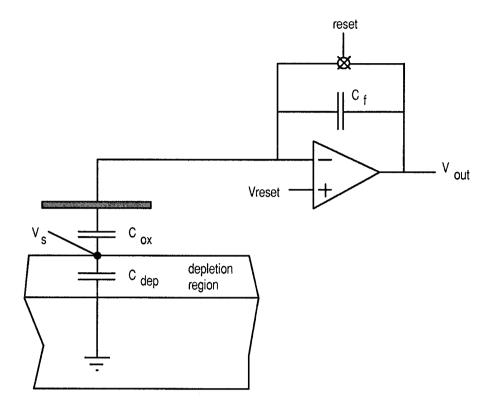

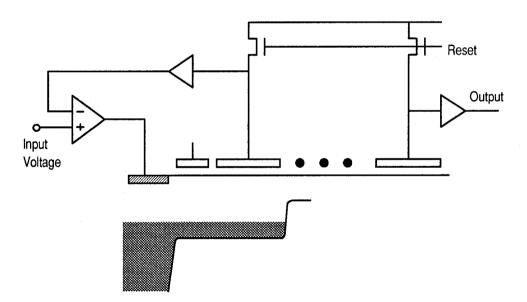

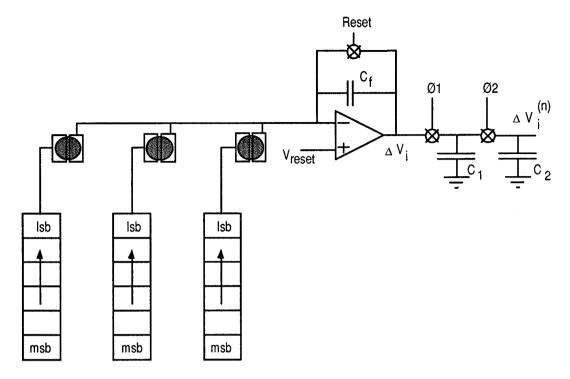

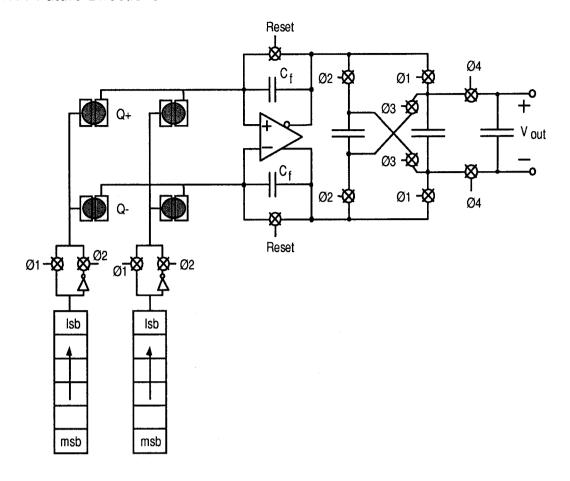

Figure 2.25. Charge feedback sense amplifier. The polysilicon sense gate is held at a virtual ground by the amplifier feedback loop which increases the sensitivity. Additionally, nonlinear parasitic capacitance is canceled and the gain of the sense amp can be specified by selecting the proper  $C_{\rm f}$  independent of polysilicon gate size.

Using a different sensing arrangement like the one shown in Figure 2.25 can increase the sensitivity of the circuit by forcing the gate to remain at a constant potential via the feedback action of the sensing amplifier and feedback capacitor [Beynon et al., 1980][Miida et al., 1991]. The previous analysis can be used by letting  $C_{\rm ext} \to \infty$  and using the following relationship for surface channel devices

$$\Delta V_{\text{out}} = \Delta V_{\text{S}} \frac{C_{\text{ox}}}{C_{\text{f}}}$$

(2.44)

and for buried channel

2.9 References: 57

$$\Delta V_{\text{out}} = \Delta V_{\text{chan}} \frac{C_{\text{ox}} C_{\text{dep1}}}{C_{\text{f}} (C_{\text{ox}} + C_{\text{dep1}})}$$

(2.45)

In contrast to Equations 2.37 and 2.43, these equations can produce voltage gain for small  $C_f$ . Linearity is improved since the linear oxide capacitance has effectively been increased by holding the gate at a virtual ground. For future use, the feedback sensing Q-V transforms for surface and buried channel devices are referred to as  $V_{fsc}(Q)$  and  $V_{fbc}(Q)$  respectively.