# On The VLSI Decompositions for Complete Graphs, DeBruijn Graphs, Hypercubes, Hyperplanes, Meshes, and Shuffle-Exchange Graphs

Thesis by

Tsz-Mei Ko

In Partial Fulfillment of the Requirements

for the Degree of

Doctor of Philosophy

California Institute of Technology

Pasadena, California

1993

$({\bf Defended\ August\ 3,\,1992})$

©1993 Tsz-Mei Ko All Rights Reserved To all complex systems that process and communicate  $\$

#### Acknowledgements

Special thanks to Dr. Robert J. McEliece for his extraordinary supervision during my three years of graduate studies at Caltech. His directions have led me to the insights for the solutions of many problems.

Thanks to Dr. Edward Posner, Dr. Yaser Abu-Mostafa, Dr. Charles Seitz, and Dr. Alain Martin for their valuable comments that have improved the readability and correctness of this thesis.

Thanks to Dr. Sam Dolinar, Dr. Kar-Ming Cheung, Dr. Ivan Onyszchuk, Dr. Laif Swanson, and other members of the Advanced Error Correcting Code Research and Development Team at the Jet Propulsion Laboratories for their inspiring discussions. I have learnt many practical aspects of coding and decoding from them. Thanks also go to Dr. Oliver Collins, from the Johns Hopkins University, who originally formulated the VLSI decomposition problem when he was doing research at Caltech/JPL. Dr. Collins has also taught me Theorem 6.2 and its proof.

Thanks to Dr. Michael Little, Dr. Michael Yung, Dr. Michael Campbell, and other members of the 3D Microelectronics Group at the Hughes Research Laboratories. They have helped me in understanding the connectivity issue and other limitations in the current VLSI technology.

Thanks to the National Security Agency and the Hughes Aircraft Company to provide the fundings that made this research possible. This research was partially supported by the National Security Agency under Grant Number MDA904-90-H-1007 and partially supported by a Hughes Doctoral Fellowship.

Thanks to all the people in the Caltech/JPL community. They have truely created an enjoyable research environment. I have learnt a lot through the continuous interaction with all of them.

Thanks to Ms Debbie McGougan and other secretaries in the Electrical Engineering Department for their assistances. They have saved me a great deal of time.

Thanks to all my teachers, colleagues, relatives, and friends. They have made this universe a much more wonderful place to live.

Last but not the least, a googolplex of special thanks to my parents, Wa and Kwok-Lin Ko, and my brother, Tze-Man Ko, for their unlimited support.

#### Abstract

A C-chip VLSI decomposition of a graph G is a collection of C vertex-disjoint subgraphs of G which together contain all of G's vertices and a subset of its edges. If the vertex-disjoint subgraphs are isomorphic to each other, we call one of these isomorphic subgraphs a building block. The efficiency of a VLSI decomposition is defined to be the fraction of edges of G that are in the subgraphs. In this thesis, motivated by the need to construct large Viterbi decoders, we study VLSI decompositions for deBruijn graphs. We obtain some strong necessary conditions for a graph to be a building block for a deBruijn graph, and some slightly more restrictive sufficient conditions which allow us to construct some efficient building blocks for deBruijn graphs. By using the methods described in this thesis, we have found a 64-chip VLSI decomposition of the deBruijn graph  $B_{13}$  with efficiency 0.754. This decomposition is being used by JPL design engineers to build a single-board Viterbi decoder for the K=15, rate 1/4 convolutional code which will be used on NASA's Galileo mission.

Furthermore, we study VLSI decompositions for the families of complete graphs, hypercubes, hyperplanes, meshes, and shuffle-exchange graphs. In each of these cases, we obtain very efficient or even optimal decompositions. We also prove several general theorems that can be applied to obtain bounds on the efficiencies for VLSI decompositions of other complex graphs. In general, the results presented in this thesis are useful for implementing massively parallel computers.

# **Table of Contents**

| I.   | Introduction                                                             |

|------|--------------------------------------------------------------------------|

| II.  | The VLSI Decomposition Problem                                           |

| III. | Complete Graphs, Hypercubes, Hyperplanes, Meshes                         |

|      | 3.1. An Easy Case: Complete Graphs $K_n$                                 |

|      | 3.2. Binary $n$ -Cubes $\Gamma_n$                                        |

|      | 3.3. <i>n</i> -Dimensional Hyperplanes $\Gamma_n(l_1, l_2, \ldots, l_n)$ |

|      | 3.4. d-Dimensional Meshes $M_d'(n)$ Without Wrap-Around                  |

|      | 3.5. d-Dimensional Meshes $M_d(n)$ With Wrap-Around                      |

| IV.  | DeBruijn Graphs                                                          |

|      | 4.1. Binary DeBruijn Graphs $B_n$                                        |

|      | 4.2. $q$ -ary DeBruijn Graphs $B_n^q$                                    |

|      | 4.3. Properties of DeBruijn Graphs $B_n^q$                               |

|      | 4.4. C-Chip VLSI Decompositions for DeBruijn Graphs $B_n^q$              |

|      | 4.5. DeBruijn Building Blocks                                            |

|      | 4.6. Universal DeBruijn Building Blocks                                  |

|      | 4.7. An Example For Building $B_n^q$                                     |

|      | 4.8. The Most Efficient Known Universal DeBruijn Building Blocks 40      |

| V.   | Shuffle-Exchange Graphs                                                  |

|      | 5.1. Binary Shuffle-Exchange Graphs $\Psi_n$                             |

|      | 5.2. Properties of Shuffle-Exchange Graphs $\Psi_n$                      |

|      | 5.3. C-Chip VLSI Decompositions for Shuffle-Exchange Graphs $\Psi_n$ 52  |

|      | 5.4. Shuffle-Exchange Building Blocks                                    |

|      | 5.5. Universal Shuffle-Exchange Building Blocks                          |

|      | 5.6. An Example For Building $\Psi_n$                                    |

|      | 5.7. The Most Efficient Known $\Psi_k(T_k)$ Building Blocks                              | . 59 |

|------|------------------------------------------------------------------------------------------|------|

| VI.  | Some General Theorems                                                                    | . 65 |

|      | 6.1. A Classification of Graphs                                                          | . 65 |

|      | 6.2. Directed Graph Bounds                                                               | . 66 |

|      | 6.3. Undirected Graph Bounds                                                             | . 71 |

|      | 6.4. Bounds on Graphs with Both Directed and Undirected Edges                            | . 74 |

| VII. | Conclusions and Summary                                                                  | . 80 |

|      | 7.1. Notations                                                                           | .80  |

|      | 7.2. Complete Graph $K_n$                                                                | . 82 |

|      | 7.3. n-Dimensional Hyperplane $\Gamma_n(l)$ and Binary n-Cube $\Gamma_n=\Gamma_n(l=2)$ . | .83  |

|      | 7.4. <i>n</i> -Dimensional Hyperplane $\Gamma_n(l_1, l_2, \dots, l_n)$                   | .84  |

|      | 7.5. d-Dimensional Mesh $M'_d(n)$ Without Wrap-Around                                    | . 85 |

|      | 7.6. d-Dimensional Mesh $M_d(n)$ With Wrap-Around                                        | . 86 |

|      | 7.7. DeBruijn Graph $B_n^q$                                                              | .87  |

|      | 7.8. Binary Shuffle-Exchange Graph $\Psi_n$                                              | . 88 |

| VIII | . References                                                                             | . 89 |

#### I. Introduction

There are two major problems in designing massively parallel computers—(i) choose the appropriate interconnection network; and (ii) implement the choosen architecture in minimum cost. In this thesis, we will concentrate on the second problem.

For the first problem, the solution usually relies on the effectiveness for the different architectures to implement certain applications and algorithms. Many researches [Leig92] have been done to compare the algorithmic times for different interconnection schemes. As an example, the hypercube and the hypercubic derived networks, e.g., the shuffle-exchange graph, have efficient implementations for the Fast Fourier Transform, sorting algorithms, and many other useful applications. We will discuss the multi-chip implementation for some of these architectures in this thesis. In particular, we discuss the implementation for the deBruijn graph extensively in Chapter 4. We focus on this family of graphs because they represent the circuit diagrams for fully parallel Viterbi decoders. In fact, the binary deBruijn graph  $B_{K-2}$  (to be defined in Section 4.1) represents the fully parallel Viterbi decoder for a constraint length K, rate 1/n convolutional code; and NASA is using a K = 15, rate 1/4 convolutional code on the Galileo mission.

For the second problem, the solution usually relies on the effectiveness on using the resources, i.e., the available chip area and the available number of pins per chip. With the recent advances in VLSI technologies, the transistor sizes have been greatly reduced and the die size, i.e., the available chip area, has simultaneously been largely increased. As a result, many processors can be built inside one single chip. Unfortunately, the slow progress in packaging technology has left us a bottleneck on the number of available pins. Thus many recent circuit designs are limited by the available number of pins and/or I/O capability. In this thesis, we attempt to find methods to take full advantage of the precious pins by minimizing the number

of external inter-chip connections. The exact problem, which we call the VLSI decomposition problem, is precisely defined in Chapter 2.

In Chapters 3–5, we reveal our attempts to solve the VLSI decomposition problem for the families of complete graphs, hypercubes, hyperplanes, meshes, deBruijn graphs, and shuffle-exchange graphs. For all these cases, we have found optimal or relatively good solutions. In Chapter 6, we present several general theorems and some general techniques that can be used to obtain bounds on the number of inter-chip connections for a given graph. These theorems and techniques can be applied to many other graphs that are not discussed in this thesis. Finally, in Chapter 7, we summarize all the important results that are presented in this thesis.

### II. The VLSI Decomposition Problem

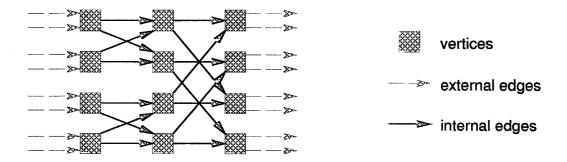

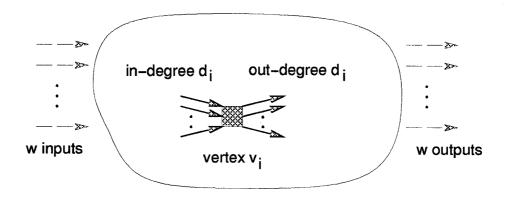

Let G be a graph that represents an interconnection network for a complex circuit, such as a high-speed parallel computer. The vertices of G correspond to arithmetic processors and the edges of G correspond to data paths connecting the processors. Furthermore, we use directed and undirected edges to represent simplex and duplex links respectively.

In modern VLSI technology, if the circuit is too large to fit on a single chip, it may be possible to build it by wiring together two or more appropriately designed chips. Each processor must then be placed on one of the chips, but the wires of the circuit may be either internal to the chips (intrachip wires) or external (interchip wires). Thus we are motivated to define a C-chip VLSI decomposition of a graph G as a collection of C vertex-disjoint subgraphs of G which together contain all of G's vertices, and a subset of its edges. The edges contained in the collection of subgraphs are called internal edges. Since we can reduce the total number of pins on the chips by including as many internal edges as possible in the decomposition, we define the efficiency of a C-chip VLSI decomposition of G into subgraphs  $H_1, H_2, \ldots, H_C$  as

(2.1)

$$\operatorname{eff}(H_1, H_2, \cdots, H_C \mapsto G) = \frac{\sum_{i=1}^{C} \operatorname{E}(H_i)}{\operatorname{E}(G)}$$

where  $E(\mathcal{G})$  denotes the number of edges in graph  $\mathcal{G}$ . The number of vertices in the subgraph  $H_i$  is called the *size* (or the *chip size*) of  $H_i$ . Let  $k_i$  denote the size of  $H_i$  and  $|\mathcal{G}|$  denote the number of vertices in  $\mathcal{G}$ . Then

$$k_1+k_2+\cdots+k_C=|G|.$$

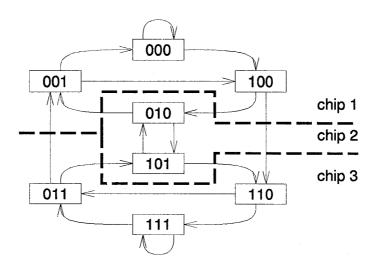

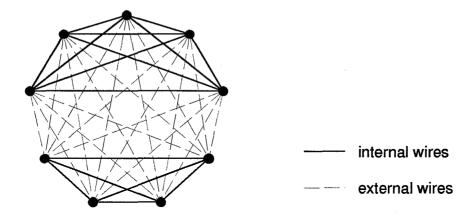

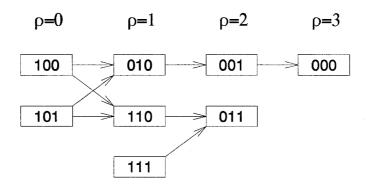

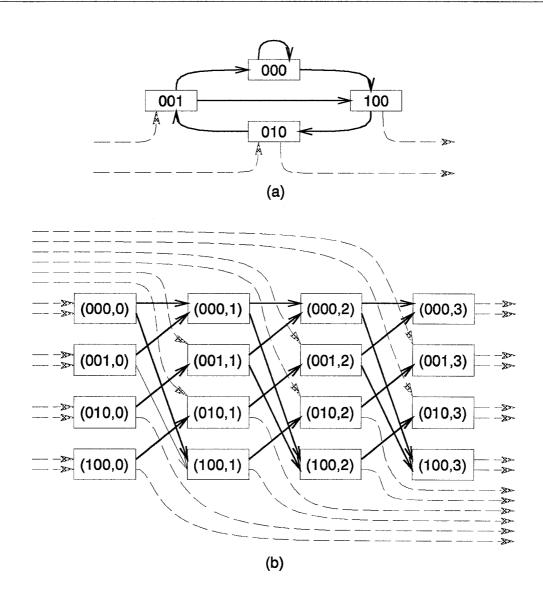

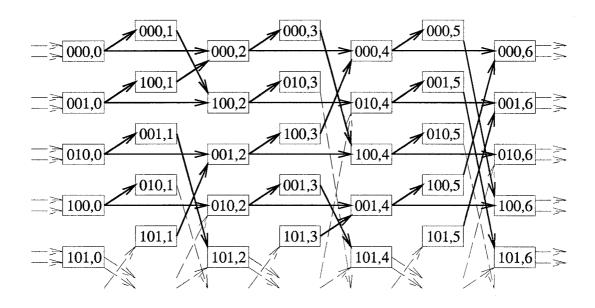

An example of a three-chip VLSI decomposition for the deBruijn graph  $B_3$  (to be defined in Section 4.1) into chip sizes 2, 3 and 3 with an efficiency of 0.625 is shown in Figure 2.1.

In a VLSI decomposition of G into subgraphs  $H_1, H_2, \ldots, H_C$ , it is normally desirable for the subgraphs  $H_i$  to be isomorphic since the cost of fabricating multiple

Figure 2.1. A three-chip VLSI decomposition for the de-Bruijn graph  $B_3$  with an efficiency of 0.625.

copies of one chip is much less than designing several kinds of chips. For the case  $H_1 \equiv H_2 \equiv \cdots \equiv H_C \equiv H$ , we call one of these isomorphic subgraphs H a building block for the graph G. The size k = |H| of a building block for G must be a factor of |G|. In addition, we use the shorthand notation  $\operatorname{eff}(H \vdash G)$  to denote the efficiency of the VLSI decomposition for G into building blocks H. Thus, by (2.1),

(2.2)

$$\operatorname{eff}(H \vdash G) = \operatorname{eff}(H, H, \dots, H \mapsto G) = \frac{|G|}{|H|} \cdot \frac{\operatorname{E}(H)}{\operatorname{E}(G)}.$$

We also call  $eff(H \vdash G)$  the efficiency of the building block H for the graph G. If a building block can be used to build any graph in a fixed set of graphs  $\{G_n\}$ , we call it a universal building block for  $\{G_n\}$ . The efficiency of a universal building block H for the set of graphs  $\{G_n\}$  is usually a function of n, i.e.,

(2.3)

$$\operatorname{eff}(H \vdash G_n) = \frac{|G_n|}{|H|} \cdot \frac{\operatorname{E}(H)}{\operatorname{E}(G_n)}.$$

However, there are special cases, such as the universal deBruijn building blocks (c.f. Section 4.8), that have an efficiency independent of n.

In this thesis, we consider the following VLSI decomposition problems:

- [1] Given a graph G and chip sizes  $k_1, k_2, \ldots, k_C$  (where  $k_1 + k_2 + \cdots + k_C = |G|$ ), what are the most efficient VLSI decompositions for G into C chips of sizes  $k_1, k_2, \ldots, k_C$ ?

- [2] Given a graph G and a non-negative integer k (where k divides |G|), what are the most efficient VLSI decompositions for G into C chips (that are not required to be isomorphic) of equal sizes k?

- [3] Given a graph G and a non-negative integer k (where k divides |G|), what are the most efficient building blocks of size k for G?

- [4] Given a family of graphs  $\{G_n\}_{n\geq N}$  and a non-negative integer k (where k divides  $|G_n|$  for each  $n\geq N$ ), what are the most efficient universal building blocks of size k for  $\{G_n\}_{n\geq N}$ ?

A related problem, usually called the "pin limitation" problem, is to determine the maximum possible number  $\mathrm{E}_G^*(k)$  of interconnecting edges in a subgraph of G with k vertices. If  $\mathrm{E}_G^*(k)$  is known for a graph G, the efficiency for the C-chip VLSI decomposition of graph G into subgraphs  $H_1(k_1), H_2(k_2), \cdots, H_C(k_C)$  of sizes  $k_1, k_2, \ldots, k_C$  respectively is bounded above by

$$(2.4) \quad \text{eff}(H_1(k_1), H_2(k_2), \cdots, H_C(k_C) \mapsto G) \leq \frac{\mathbf{E}_G^*(k_1) + \mathbf{E}_G^*(k_2) + \cdots + \mathbf{E}_G^*(k_C)}{\mathbf{E}(G)}.$$

In particular, for the case  $k_1 = k_2 = \cdots = k_C = k$ , we obtain

$$(2.5) e_{\text{I}}(G;k) \le e_{\text{NI}}(G;k) \le \frac{C \cdot \operatorname{E}_{G}^{*}(k)}{\operatorname{E}(G)},$$

where  $e_{NI}(G;k)$  denotes the efficiency of the most efficient VLSI decomposition into C chips (which are not required to be isomorphic) of equal sizes k and  $e_I(G;k)$  denotes the efficiency of the most efficient VLSI decomposition into C isomorphic chips (i.e., building blocks) of size k for the graph G.

In the following chapters, we reveal some efficient VLSI decompositions for several graph families. In some cases, (2.4) and (2.5) together with previous results on the studies of "pin limitations" [Harp64,Lind64,Snir81,Cyph90] provide proofs that the known VLSI decompositions are optimal.

### III. Complete Graphs, Hypercubes, Hyperplanes, Meshes

### 3.1. An Easy Case: Complete Graphs $K_n$

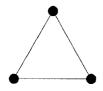

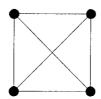

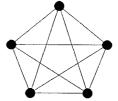

The complete graph  $K_n$  consists of n vertices and  $\binom{n}{2}$  edges, each connecting two distinct vertices. Figure 3.1 shows the complete graphs  $K_3$ ,  $K_4$ , and  $K_5$ . Note that any induced subgraph of  $K_n$  with m vertices (where  $m \leq n$ ) is isomorphic to the complete graph  $K_m$ . Thus the most efficient C-chip VLSI decomposition of  $K_n$  into chip sizes  $k_1, k_2, \ldots, k_C$  (where  $k_1 + k_2 + \cdots + k_C = n$ ) consists of the C smaller complete graphs  $K_{k_1}, K_{k_2}, \ldots, K_{k_C}$  with an efficiency of

(3.1)

$$\operatorname{eff}(K_{k_1}, K_{k_2}, \cdots, K_{k_C} \mapsto K_n) = \frac{\binom{k_1}{2} + \binom{k_2}{2} + \cdots + \binom{k_C}{2}}{\binom{n}{2}}.$$

An example of an optimal two-chip VLSI decomposition of  $K_9$  into chip sizes 4 and 5 with an efficiency of 4/9 is shown in Figure 3.2.

**Figure 3.1.** The complete graphs  $K_3$ ,  $K_4$  and  $K_5$ .

By letting  $k_1 = k_2 = \cdots = k_C = k$  in (3.1), the most efficient VLSI decomposition of  $K_n$  into chips (which are not required to be isomorphic) of equal sizes k

$<sup>^{\</sup>dagger}$  An induced subgraph H is a subgraph that contains all edges with both endvertices in H.

**Figure 3.2.** An optimal two-chip VLSI decomposition of  $K_9$  into chip sizes 4 and 5.

(where k|n) consists of n/k complete graphs  $K_k$  with an efficiency of

(3.2)

$$e_{NI}(K_n; k) = eff(K_k, K_k, \dots, K_k \mapsto K_n) = \frac{\binom{k}{2} \cdot \frac{n}{k}}{\binom{n}{2}} = \frac{k-1}{n-1}.$$

Consequently, the complete graph  $K_k$  is the most efficient  $K_n$  building block of size k with an efficiency of

(3.3)

$$e_{\mathbf{I}}(K_n; k) = \text{eff}(K_k \vdash K_n) = \frac{\binom{k}{2} \cdot \frac{n}{k}}{\binom{n}{2}} = \frac{k-1}{n-1}.$$

Since (3.3) holds for all n that are multiples of k, the complete graph  $K_k$  is also the most efficient universal building block (of size k) for the family of complete graphs  $\{K_n\}_{kN|n}$  where N is a positive integer.

### **3.2.** Binary *n*-Cubes $\Gamma_n$

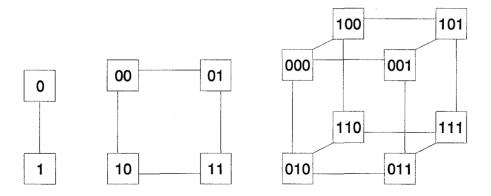

The binary n-cube  $\Gamma_n$  has  $2^n$  vertices, labelled by the binary n-tuples  $\{0,1\}^n$ , and  $n \cdot 2^{n-1}$  edges, each connecting two vertices with labels different in one position. Figure 3.3 shows the binary n-cubes  $\Gamma_1$ ,  $\Gamma_2$  and  $\Gamma_3$ .

Let H(m) be the induced subgraph<sup>†</sup> containing m vertices of  $\Gamma_n$  that have labels equivalent to the binary expansion of the first m non-negative integers  $0,1,\ldots,m-1$ . Harper[Harp64,Bern67,Hart76] showed that the subgraph H(m) has the maximum number of edges among all subgraphs of  $\Gamma_n$  with m vertices (where  $m \leq 2^n$ ). Consider a vertex of H(m). Each "one" in the label indicates that the vertex with a "zero" in the same position is also in H(m) and thus indicates the presence of an edge in H(m). Therefore the total number of edges in H(m) is

(3.4)

$$\mathrm{E}_{\Gamma_n}^*(m) = \mathrm{E}(H(m)) = \sum_{i=0}^{m-1} \mathrm{weight}(i)$$

where weight(i) denotes the number of "one"s in the binary expansion of i. From (3.4) and (2.4), the efficiency for a C-chip VLSI decomposition of  $\Gamma_n$  into chip sizes  $k_1, k_2, \ldots, k_C$  (where  $k_1 + k_2 + \cdots + k_C = 2^n$ ) is bounded above by

(3.5)

$$\frac{1}{\mathrm{E}(\Gamma_n)} \sum_{i=1}^C \left( \sum_{j=0}^{k_i - 1} \mathrm{weight}(i) \right).$$

For the case  $k_1 = k_2 = \cdots = k_C = 2^k$ , the expression (3.5) can be simplified to

(3.6)

$$e_{NI}(\Gamma_n; 2^k) \le \frac{1}{E(\Gamma_n)} \sum_{i=1}^C \left( k \cdot 2^{k-1} \right) = \frac{(k)(2^{k-1})(2^{n-k})}{(n)(2^{n-1})} = \frac{k}{n}.$$

The upper bound (3.6) can be achieved if we decompose  $\Gamma_n$  into  $2^{n-k}$   $\Gamma_k$ -chips. We can show that such a decomposition is possible by construction, i.e., finding a one-to-one mapping between the vertex set V of  $\Gamma_n$  and the set of ordered pairs

<sup>†</sup> Induced subgraph is defined in the footnote on page 7.

**Figure 3.3.** The binary *n*-cubes  $\Gamma_1$ ,  $\Gamma_2$  and  $\Gamma_3$ .

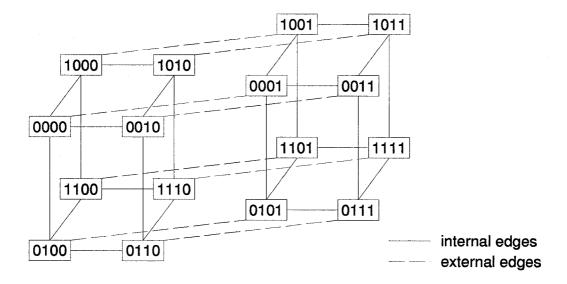

(i,j), where i denotes the chip number and j denotes a vertex inside chip i, such that if two vertices are connected inside a  $\Gamma_k$ -chip, then those two vertices are also connected in the graph  $\Gamma_n$ . Now let the  $2^{n-k}$   $\Gamma_k$ -chips be numbered in binary from  $00\cdots 0$  to  $11\cdots 1$ . For each of these  $2^{n-k}$  chips, we use conventional labels for its vertices, i.e., each vertex is labelled by a binary k-tuple and two vertices are connected iff their labels are different in exactly one position. We can map vertex  $v_1v_2\cdots v_n$  of  $\Gamma_n$  onto the  $\Gamma_k$ -chip numbered  $v_{k+1}v_{k+2}\cdots v_n$  at location  $v_1v_2\cdots v_k$ . Note that this one-to-one mapping satisfies the above mentioned requirement, i.e., if two vertices are connected inside a  $\Gamma_k$ -chip, then those two vertices are also connected in the graph  $\Gamma_n$ . Figure 3.4 shows an example of an optimal two-chip VLSI decomposition of  $\Gamma_4$  into two  $\Gamma_3$ -chips by using the above mapping procedure.

By (3.6) and the argument above, the decomposition of  $\Gamma_n$  into  $2^{n-k}$  binary k-cubes is an optimal  $C = 2^{n-k}$  chip (of chip sizes  $k_1 = k_2 = \cdots = k_C = 2^k$ ) VLSI decomposition. The efficiency is

(3.7)

$$e_{\mathbf{I}}(\Gamma_n; 2^k) = e_{\mathbf{NI}}(\Gamma_n; 2^k) = \text{eff}(\Gamma_k \vdash \Gamma_n) = \frac{(k)(2^{k-1})(2^{n-k})}{(n)(2^{n-1})} = \frac{k}{n}.$$

Since (3.7) holds for all  $n \geq k$ , the binary k-cube  $\Gamma_k$  is also the most efficient

Figure 3.4. An optimal two-chip VLSI decomposition of  $\Gamma_4$  into  $\Gamma_3$ -chips with an efficiency of 3/4.

universal building block for the family of binary n-cubes  $\{\Gamma_n\}_{n\geq N}$  where  $N\geq k$ .

# 3.3. *n*-Dimensional Hyperplanes $\Gamma_n(l_1, l_2, \dots, l_n)$

An *n*-dimensional hyperplane  $\Gamma_n(l_1, l_2, \ldots, l_n)$  consists of vertices  $v_1 v_2 \cdots v_n$ , where  $0 \leq v_i \leq l_i - 1$ , and two vertices are connected iff their labels are different in one position. Thus there are  $l_1 l_2 \cdots l_n$  vertices and  $(l_1 + l_2 + \cdots + l_n - n)(l_1 l_2 \cdots l_n)/2$  edges in  $\Gamma_n(l_1, l_2, \ldots, l_n)$ . (Note that the binary *n*-cube is a special case of an *n*-dimensional hyperplane with  $l_i = 2$  for  $1 \leq i \leq n$ .) Since the hyperplane  $\Gamma_n(l_1, l_2, \ldots, l_n)$  is isomorphic to  $\Gamma_n(l'_1, l'_2, \ldots, l'_n)$ , where  $l'_1, l'_2, \ldots, l'_n$  is a permutation of  $l_1, l_2, \ldots, l_n$ , we may assume

$$l_1 \geq l_2 \geq \cdots \geq l_n$$

without loss of generality.

For each vertex  $v = v_1 v_2 \cdots v_n$  in  $\Gamma_n(l_1, l_2, \dots, l_n)$ , we may assign a distinct non-negative integer N(v) defined by

$$N(v) = N(v_1v_2\cdots v_n) = v_1 + l_1v_2 + l_1l_2v_3 + \cdots + l_1l_2\cdots l_{n-1}v_n.$$

Let H(m) be the induced subgraph<sup>†</sup> of  $\Gamma_n(l_1, l_2, \ldots, l_n)$  (where  $l_1 \geq l_2 \geq \cdots \geq l_n$ ) with m vertices such that vertex v is in H(m) iff N(v) < m. Lindsey [Lind64] generalized Harper's result [Harp64] and showed that the subgraph H(m) has the maximum number of edges among all subgraphs of  $\Gamma_n(l_1, l_2, \ldots, l_n)$  with m vertices (where  $m \leq l_1 l_2 \cdots l_n$ ). Similar to the case of the binary n-cube, the number of edges in H(m) is

(3.8)

$$E_{\Gamma_n(l_1, l_2, \dots, l_n)}^*(m) = E(H(m)) = \sum_{i=0}^{m-1} \text{weight}(i)$$

where weight(i) denotes the sum of the digits in  $N^{-1}(i)$ , i.e., if  $N(v_1v_2\cdots v_n)=i$ , then weight(i) =  $v_1 + v_2 + \cdots + v_n$ . By (3.8), the number of internal edges in a C-chip VLSI decomposition of  $\Gamma_n(l_1, l_2, \ldots, l_n)$  with chip sizes  $k_1, k_2, \ldots, k_C$  (where  $k_1 + k_2 + \cdots + k_C = l_1 l_2 \cdots l_n$ ) is bounded above by

(3.9)

$$\sum_{i=1}^{C} \left( \sum_{j=0}^{k_i - 1} \operatorname{weight}(i) \right).$$

For the case  $k_1 = k_2 = \cdots = k_C = l_1 l_2 \cdots l_k$ , the expression (3.9) can be simplified to

$$\sum_{i=1}^{C} \left( \frac{l_1 + l_2 + \dots + l_k - k}{2} (l_1 l_2 \dots l_k) \right) = \frac{l_1 + l_2 + \dots + l_k - k}{2} (l_1 l_2 \dots l_n).$$

This upper bound can be achieved if we decompose  $\Gamma_n(l_1, l_2, \ldots, l_n)$  into k-dimensional sub-hyperplanes  $\Gamma_k(l_1, l_2, \ldots, l_k)$  by mapping vertex  $v_1 v_2 \cdots v_n$  of  $\Gamma_n(l_1, l_2, \ldots, l_n)$  onto location  $v_1 v_2 \cdots v_k$  in the chip numbered  $v_{k+1} v_{k+2} \cdots v_n$ . The

<sup>†</sup> Induced subgraph is defined in the footnote on page 7.

efficiency of such an optimal  $C = l_{k+1}l_{k+2}\cdots l_n$  chip (of chip sizes  $k_1 = k_2 = \cdots = k_C = l_1 l_2 \cdots l_k$ ) VLSI decomposition for  $\Gamma_n(l_1, l_2, \ldots, l_n)$  is

(3.10)

$$e_{\mathrm{I}}(\Gamma_{n}(l_{1}, l_{2}, \dots, l_{n}); l_{1}l_{2} \cdots l_{k}) = e_{\mathrm{NI}}(\Gamma_{n}(l_{1}, l_{2}, \dots, l_{n}); l_{1}l_{2} \cdots l_{k}) \\ = \mathrm{eff}(\Gamma_{k}(l_{1}, l_{2}, \dots, l_{k}) \vdash \Gamma_{n}(l_{1}, l_{2}, \dots, l_{n})) = \frac{l_{1} + l_{2} + \dots + l_{k} - k}{l_{1} + l_{2} + \dots + l_{n} - n}.$$

Since (3.10) holds for all  $n \geq k$ , the k-dimensional hyperplane  $\Gamma_k(l_1, l_2, \ldots, l_k)$  (where  $l_1 \geq l_2 \geq \cdots \geq l_k$ ) is also the most efficient universal building block for the family of hyperplanes  $\{\Gamma_n(l_1, l_2, \ldots, l_n)\}_{n \geq N}$  where  $N \geq k$  and  $l_i \leq l_k$  for  $k < i \leq n$ .

As a final remark, if we consider only the hyperplanes  $\Gamma_n(l)$  that denotes  $\Gamma_n(l_1, l_2, \ldots, l_n)$  with  $l_1 = l_2 = \cdots = l_n = l$ , the optimal  $C = l^{n-k}$  chip VLSI decomposition (with chip sizes  $k_1 = k_2 = \cdots = k_C = l^k$ ) for  $\Gamma_n(l)$  consists of  $l^{n-k}$  copies of  $\Gamma_k(l)$ . By letting  $l_1 = l_2 = \cdots = l_k = l$  in (3.10), we obtain the efficiency as

$$(3.11) e_{\mathbf{I}}(\Gamma_n(l); l^k) = e_{\mathbf{N}\mathbf{I}}(\Gamma_n(l); l^k) = \operatorname{eff}(\Gamma_k(l) \vdash \Gamma_n(l)) = \frac{kl - k}{nl - n} = \frac{k}{n}.$$

Again, since (3.11) holds for all  $n \geq k$ , the hyperplane  $\Gamma_k(l)$  is also the most efficient universal building block for the family of hyperplanes  $\{\Gamma_n(l)\}_{n\geq N}$  where  $N\geq k$ .

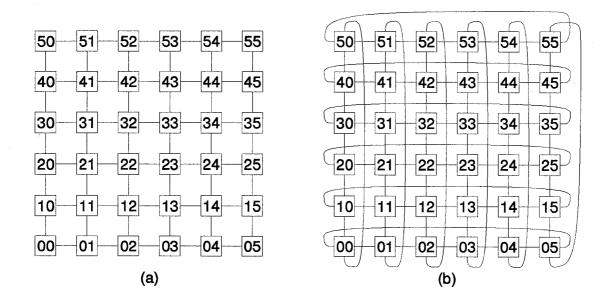

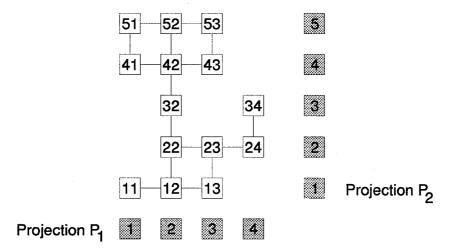

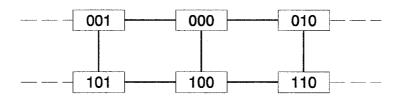

# 3.4. d-Dimensional Meshes $M'_d(n)$ Without Wrap-Around

A d-dimensional mesh of side length n has  $n^d$  vertices labelled by the n-ary d-tuples  $\{0,1,\cdots,n-1\}^d$ . For the mesh  $M'_d(n)$  without wrap-around, two vertices are connected by an edge iff their labels are different in one position and the difference of the two digits in that position is one. (The mesh  $M_d(n)$  with wrap-around is defined in the next section.) Thus there are  $(d)(n-1)(n^{d-1})$  edges in  $M'_d(n)$ . Note that a basic difference between meshes and hyperplanes is that we normally consider family of meshes  $\{M'_d(n)\}_{n\geq k}$  that have different side lengths in contrast with family of hyperplanes  $\{\Gamma_n(l)\}_{n\geq k}$  that have different dimensions. Figure 3.5 shows the two-dimensional meshes  $M'_2(6)$  and  $M_2(6)$ .

**Figure 3.5.** Two dimensional meshes: (a)  $M'_2(6)$  without wrap-around and (b)  $M_2(6)$  with wrap-around.

Let  $H'_d(m)$  be a subgraph of  $M'_d(n)$  with m vertices and let  $V(H'_d(m))$  be the vertex set of  $H'_d(m)$ . Let  $P_r(H'_d(m))$ , where  $1 \leq r \leq d$ , be the set of (d-1)-tuples  $(x_1, x_2, \cdots, x_{d-1})$  such that  $(x_1, x_2, \cdots, x_{d-1}) \in P_r(H'_d(m))$  iff there exists  $(x_1, x_2, \cdots, x_{r-1}, j, x_r, x_{r+1}, \cdots, x_{d-1}) \in V(H'_d(m))$  for some j. (Intuitively, we may consider  $P_r(H'_d(m))$  as the (d-1)-dimensional projection of a d-dimensional object.) Figure 3.6 shows a subgraph  $H'_2(14)$  with  $P_1(H'_2(14)) = \{1, 2, 3, 4\}$  and  $P_2(H'_2(14)) = \{1, 2, 3, 4, 5\}$ . Note that the number of edges that are in the rth dimension, i.e., those connecting vertices  $(x_1, x_2, \cdots, x_{r-1}, j, x_r, x_{r+1}, \cdots, x_{d-1})$  and  $(x_1, x_2, \cdots, x_{r-1}, j + 1, x_r, x_{r+1}, \cdots, x_{d-1})$ , in  $H'_d(m)$  is  $\leq m - |P_r(H'_d(m))|$  (where the notation |R| denotes the number of elements in the set R). Thus the total number of edges in  $H'_d(m)$  is bounded above by

(3.12)

$$E(H'_d(m)) \le dm - \sum_{r=1}^d |P_r(H'_d(m))|.$$

Figure 3.6. A subgraph  $H'_2(14)$  of  $M'_2(6)$ .  $P_1(H'_2(14)) = \{1, 2, 3, 4\}$  and  $P_2(H'_2(14)) = \{1, 2, 3, 4, 5\}$ .

Cypher [Cyph90] proved that  $\sum_{r=1}^{d} |P_r(H'_d(m))| \ge dm^{\frac{d-1}{d}}$ . Thus, by (3.12), the maximum number of edges in the subgraph  $H'_d(m)$  is bounded above by

(3.13)

$$E_{M'_d(n)}^*(m) \le d \cdot (m - m^{\frac{d-1}{d}}).$$

From (2.4) and (3.13), the efficiency for a C-chip VLSI decomposition of  $M'_d(n)$  into chip sizes  $k_1, k_2, \ldots, k_C$  (where  $k_1 + k_2 + \cdots + k_C = n^d$ ) is bounded above by

(3.14)

$$\frac{1}{\mathrm{E}(M'_d(n))} \sum_{i=1}^C \left( d \cdot (k_i - k_i^{\frac{d-1}{d}}) \right) = \frac{1}{(n-1)(n^d)} \sum_{i=1}^C \left( k_i - k_i^{\frac{d-1}{d}} \right).$$

For the case  $k_1 = k_2 = \cdots = k_C = k^d$ , the expression (3.14) can be simplified to

(3.15)

$$e_{\text{NI}}(M'_d(n); k^d) \le \frac{1}{(n-1)(n^d)} \sum_{i=1}^C \left(k^d - k^{d-1}\right) \\ = \frac{\left(\frac{n}{k}\right)^d (k^d - k^{d-1})}{(n-1)(n^d)} = \frac{(n)(k-1)}{(n-1)(k)}.$$

The upper bound (3.15) can be achieved if we decompose  $M'_d(n)$  into  $(n/k)^d$   $M'_d(k)$ chips by mapping vertex  $(v_1, v_2, \dots, v_d)$  of  $M'_d(n)$  onto position  $(r_1, r_2, \dots, r_d)$  in the

chip numbered  $(q_1, q_2, \dots, q_d)$  where  $q_i$  and  $r_i$  are the quotient and the remainder respectively when  $v_i$  is divided by k. Thus the decomposition of  $M'_d(n)$  into  $(n/k)^d$ d-dimensional  $M'_d(k)$  meshes is an optimal  $C = (n/k)^d$  chip (of chip sizes  $k_1 = k_2 =$  $\cdots = k_C = k^d$ ) VLSI decomposition with an efficiency of

(3.16)

$$e_{\text{I}}(M'_d(n); k^d) = e_{\text{NI}}(M'_d(n); k^d) \\ = \text{eff}(M'_d(k) \vdash M'_d(n)) = \frac{(n/k)^d (d)(k^{d-1})(k-1)}{(d)(n^{d-1})(n-1)} = \frac{(n)(k-1)}{(n-1)(k)}.$$

Since (3.16) holds for all n that is a multiple of k, the mesh  $M'_d(k)$  is also the most efficient universal building block for the family of meshes  $\{M'_d(n)\}_{kN|n}$  where N is a positive integer.

### 3.5. d-Dimensional Meshes $M_d(n)$ With Wrap-Around

A d-dimensional mesh  $M_d(n)$  (with wrap-around) of side length n has  $n^d$  vertices labelled by the n-ary d-tuples  $\{0, 1, \dots, n-1\}^d$ . Two vertices are connected by an edge iff their labels are different in one position and the difference of the two digits in that position is  $1 \mod n$ . Thus there are  $dn^d$  edges in  $M_d(n)$ . Figure 3.5(b) shows the mesh  $M_2(6)$ .

By using the same argument introduced by Cypher [Cyph90], we can prove that for meshes  $M_d(n)$ ,

(3.17)

$$E_{M_d(n)}^*(m) \le \frac{n+1}{n} \cdot dm - dm^{\frac{d-1}{d}}.$$

Thus the efficiencies for  $M_d(n)$  building blocks of size  $k^d$  (where k|n) are bounded above by

(3.18)

$$e_{\text{I}}(M_d(n); k^d) \le e_{\text{NI}}(M_d(n); k^d) \\ \le \left(\frac{n+1}{n} \cdot dk^d - d \cdot (k^d)^{\frac{d-1}{d}}\right) \cdot \frac{\left(\frac{n}{k}\right)^d}{dn^d} = \frac{k-1}{k} + \frac{1}{n}.$$

The upper bound (3.18) can almost be achieved if we decompose  $M_d(n)$  into  $(n/k)^d$   $M'_d(k)$  meshes (without wrap-around) by mapping vertex  $v_1v_2\cdots v_d$  of  $M_d(n)$  onto

position  $r_1 r_2 \cdots r_d$  in the chip numbered  $q_1 q_2 \cdots q_d$ , where  $q_i$  and  $r_i$  are the quotient and the remainder respectively when  $v_i$  is divided by k. The efficiency of this decomposition is

(3.19)

$$\operatorname{eff}(M'_d(k) \vdash M_d(n)) = \frac{(d)(k-1)(k^{d-1})(\frac{n}{k})^d}{dn^d} = \frac{k-1}{k}.$$

By (3.18), the efficiency for a universal  $M_d(n)$  building block of size  $k^d$  is bounded above by  $\frac{k-1}{k}$  since a universal  $M_d(n)$  building block is necessary to build  $M_d(n)$  with arbitrary large n. Thus the  $M'_d(k)$  mesh is the most efficient universal building block of size  $k^d$  for the family of meshes  $\{M_d(n)\}_{kN|n}$  where N is a positive integer.

### IV. DeBruijn Graphs

### 4.1. Binary DeBruijn Graphs $B_n$

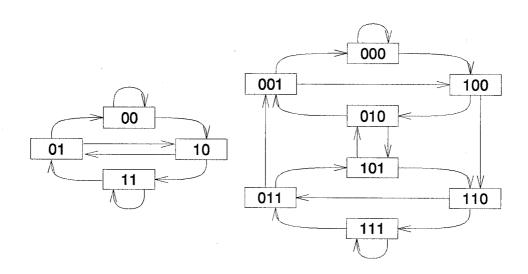

The binary deBruijn graph  $B_n$  can be defined as a directed graph with  $2^n$  vertices, each represented with a binary n-tuple, and  $2^{n+1}$  edges, each labelled with a binary (n+1)-tuple, where the edge  $x_1x_2\cdots x_{n+1}$  is a directed edge from  $x_2x_3\cdots x_{n+1}$  to  $x_1x_2\cdots x_n$ . Figure 4.1 shows the binary deBruijn graphs  $B_2$  and  $B_3$ .

Figure 4.1. The deBruijn graphs  $B_2$  (or  $B_2^2$ ) and  $B_3$  (or  $B_3^2$ ).

Some necessary conditions and a general construction for efficient VLSI decompositions for binary deBruijn graphs are discussed in [Doli92a,Doli92b]. These results can directly be generalized for q-ary deBruijn graphs  $B_n^q$ . This chapter considers VLSI decompositions for deBruijn graphs  $B_n^q$  with emphasis on binary deBruijn graphs  $B_n$  which have practical significance in building fully parallel Viterbi

decoders. In addition, the binary deBruijn graphs  $B_n$  have strong resemblance with the shuffle-exchange graphs  $\Psi_n$  as to be shown in Chapter 5.

## 4.2. q-ary DeBruijn Graphs $B_n^q$

The q-ary deBruijn graph  $B_n^q$  can be defined as a directed graph with  $q^n$  vertices, each represented with a q-ary n-tuple  $\{0,1,\dots,q-1\}^n$ , and  $q^{n+1}$  edges, each labelled with a q-ary (n+1)-tuple  $\{0,1,\dots,q-1\}^{n+1}$ , where the edge  $x_1x_2\dots x_{n+1}$  is a directed edge from  $x_2x_3\dots x_{n+1}$  to  $x_1x_2\dots x_n$ . Figures 4.1 and 4.2 show the deBruijn graphs  $B_2^2$  (or  $B_2$ ),  $B_3^2$  (or  $B_3$ ), and  $B_2^3$ .

Figure 4.2. The deBruijn graph  $B_2^3$ .

In the next section, we derive some properties of deBruijn graphs which are needed to study the VLSI decomposition for these graphs. (Other important properties can be found in [Golo82: Secs. 2.2 and 6.2].)

# 4.3. Properties of DeBruijn Graphs $B_n^q$

We first define some terms for a graph G that may contain both directed and undirected edges. These terms are defined in a general way so that the same terminology may be used on the shuffle-exchange graphs in Chapter 5. Let  $P = (P_1, P_2, \dots, P_{l+1})$  be a sequence of l+1 vertices, and  $E = (E_1, E_2, \dots, E_l)$  be a sequence of l edges (directed or undirected), in a graph G. If, for  $i = 1, 2, \dots, l$ ,  $E_i$  is an edge joining  $P_i$  and  $P_{i+1}$  (in either direction if  $E_i$  is a directed edge), we call (P, E) an ambulance path (in resemblance with the fact that an ambulance need not to obey the street directions during emergency) of length l from  $P_1$  to  $P_{l+1}$ .

By tracing along the ambulance path (P, E) in the order  $P_1, P_2, \ldots, P_{l+1}$ , its edge set E can be divided into three classes—undirected edges, forward edges (directed edges in the same direction as the trace) and backward edges (directed edges in the reverse direction). If there are f forward edges and b backward edges, we define the *net length* of the ambulance path to be |f - b| and the *signed net length* to be f - b.

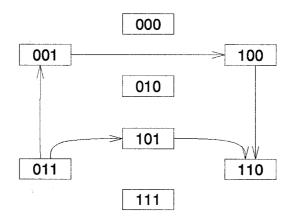

A normal path (or simply called path) is an ambulance path with no backward edge. A normal trail (or trail) is a normal path with distinct edges. A cycle is an ambulance path such that  $P_1, P_2, \ldots, P_l$  are all distinct, but  $P_{l+1} = P_1$ . A cycle in which the number of forward edges equals the number of backward edges is called a balanced cycle. A cycle which is not balanced is called an unbalanced cycle. We also call a cycle with r forward edges and s backward edges an (r,s) cycle. Figure 4.3 shows an unbalanced (3,2) (or (2,3) depending on the direction of the trace) cycle of length 5 in  $B_3$ .

**Theorem 4.1.** If X and Y are vertices in  $B_n^q$ , and l is a positive integer with  $l \leq n$ , then there cannot be more than one path of length l from X to Y.

**Proof:** Let  $X = x_1 x_2 \cdots x_n$ . In a path from X to Y, the vertex immediately

**Figure 4.3.** An unbalanced (3,2) cycle of length 5 in  $B_3$ . The net length is 1.

following X must be  $y_1x_1x_2\cdots x_{n-1}$  for some  $y_1\in\{0,1,\cdots,q-1\}$ . The next vertex must then be  $y_2y_1x_1\cdots x_{n-2}$ , and so on. Thus Y, which is the lth vertex in the path, must be of the form  $Y=y_ly_{l-1}\cdots y_1x_1x_2\cdots x_{n-l}$  (where  $y_1$  has not been shifted out since  $l\leq n$ ). It follows that each vertex on the path, and hence the path itself, is uniquely determined by X and Y.

The following theorem shows that the number of vertex-disjoint unbalanced (r,s) cycles in  $B_n^q$  is bounded above by a number independent of n.

**Theorem 4.2.** In  $B_n^q$ , there are at most  $q^l/l$  vertex-disjoint unbalanced (r, s) cycles, where l = r + s is the length of the cycle.

**Proof:** If  $l \ge n$ , the theorem is trivially true, since  $B_n^q$  has  $q^n$  vertices and thus at most  $q^n/l \le q^l/l$  vertex-disjoint unbalanced cycles of length l. On the other hand, if l < n, let  $A = a_1 a_2 \cdots a_n$  be a vertex which lies on an unbalanced (r, s) cycle. Since a cycle may be traversed in either of two opposite directions, we may assume r > s without loss of generality. After traversing the cycle and returning back to

A, the substring  $a_{s+1}a_{s+2}\cdots a_{n-r}$  will have been shifted to the right r-s positions and so we have

$$A = x_1 x_2 \cdots x_r a_{s+1} a_{s+2} \cdots a_{n-r} y_1 y_2 \cdots y_s.$$

Since this expression must be the same as the original label  $a_1 a_2 \cdots a_n$ , by equating the corresponding bits in positions r+1 through n-s, we obtain the equations

$$(4.1) a_{r+i} = a_{s+i} (1 \le i \le n - s - r).$$

It follows from (4.1) that A is uniquely determined by the l values  $a_1, a_2, \ldots, a_r$  and  $a_{n-s+1}, a_{n-s+2}, \ldots, a_n$ , so that there are at most  $q^{r+s} = q^l$  vertices that can lie on an unbalanced (r, s) cycle. Since each (r, s) cycle contains exactly l vertices, it follows that a set of vertex-disjoint unbalanced (r, s) cycles contain at most  $q^l/l$  members.

Let  $S_n^q$  be the set of all q-ary strings X of length n such that one of the longest run of zeros in X is either at the extreme left or the extreme right. For example,  $0020100,0012003,1234123 \in S_7^5$ , but  $0100230 \notin S_7^5$ . The following theorem shows that the number of edge-disjoint (vertex-disjoint) unbalanced cycles in  $B_n^q$  is bounded above by the number of elements in  $S_{n+1}^q$  ( $S_n^q$ ). In addition, we may remove all unbalanced cycles in  $B_n^q$  by deleting all edges  $E \in S_{n+1}^q$  or all vertices  $V \in S_n^q$ .

**Theorem 4.3.** In an unbalanced cycle in  $B_n^q$ , (i) there exists a vertex  $V \in S_n^q$  and (ii) there exists a directed edge  $E \in S_{n+1}^q$ .

**Proof:** Let  $P_1 = a_1 a_2 \cdots a_n$  be a vertex on an unbalanced (r, s) cycle and we assume r > s without loss of generality. Let  $P_1, E_1, P_2, E_2, \cdots, P_l, E_l, P_{l+1}$  (where  $P_{l+1} = P_1$  and l = r + s) be the sequence of vertices and edges if we trace along the cycle starting from vertex  $P_1$  and back to  $P_1 = P_{l+1}$ . (The directed edge  $E_i$  may

connect the vertices  $P_i$  and  $P_{i+1}$  in either direction.) Let

(4.2)

$$r' = \max_{1 \le i \le l+1} d(P_1, P_i)$$

$$s' = \min_{1 \le i \le l+1} d(P_1, P_i)$$

where  $d(P_1, P_i)$  denotes the signed net length of the ambulance path  $P_1 P_2 \cdots P_i$ . Then  $a_{s'+1} a_{s'+2} \cdots a_{n-r'}$  is the longest substring in  $P_1 = a_1 a_2 \cdots a_n$  that is also a substring in any other vertices  $P_i$ ,  $2 \le i \le l+1$ , i.e., the substring  $a_{s'+1} a_{s'+2} \cdots a_{n-r'}$  is shifted back and forth but never get shifted out when we trace along the cycle.

We first prove part (i) of the theorem. Suppose one of the longest run of zeros in  $P_1 = a_1 a_2 \cdots a_n$  is the substring  $a_u a_{u+1} \cdots a_v$ . If u = 1 or v = n or  $P_1$  does not contain any zero, then  $P_1 \in S_n^q$  and we are done. Otherwise the next vertex  $P_2$  on the unbalanced cycle has the label  $xa_1 a_2 \cdots a_{n-1}$  (if  $E_1$  is a forward edge) or  $a_2 a_3 \cdots a_n y$  (if  $E_1$  is a backward edge). In both cases, either  $P_2 \in S_n^q$  or the substring  $a_u a_{u+1} \cdots a_v$  remains to be one of the longest run of zeros in  $P_2$ . Continuing this way, if  $P_i \notin S_n^q \ \forall 1 \leq i \leq j$ , then either  $P_{j+1} \in S_n^q$  or the substring  $a_u a_{u+1} \cdots a_v$  is one of the longest run of zeros in  $P_{j+1}$ . Now we consider three cases: (a)  $v \geq n - r'$ , (b)  $u \leq s' + 1$ , and (c)  $s' + 1 < u \leq v < n - r'$ .

(a) For the case  $v \geq n - r'$ , let v' be the smallest positive integer such that  $d(P_1, P_{v'}) = n - v$ , i.e.,

$$n - v = d(P_1, P_{v'}) > d(P_1, P_i) \ \forall i < v'.$$

If  $P_i \notin S_n^q \ \forall 1 \leq i < v'$ , then  $P_{v'} \in S_n^q$  since the substring  $a_u a_{u+1} \cdots a_v$  is a suffix of  $P_{v'}$ .

(b) For the case  $u \leq s' + 1$ , let u' be the smallest positive integer such that  $d(P_1, P_{u'}) = u$ , i.e.,

$$u = d(P_1, P_{u'}) < d(P_1, P_i) \ \forall i < u'.$$

If  $P_i \notin S_n^q \ \forall 1 \leq i < u'$ , then  $P_{u'} \in S_n^q$  since the substring  $a_u a_{u+1} \cdots a_v$  is a prefix of  $P_{u'}$ .

(c) For the remaining case  $s' + 1 < u \le v < n - r'$ , we will show that there exists another all zeros substring  $a_{t-u+v} \cdots a_t$  (which is also one of the longest run of zeros) in  $P_1$  where  $t \ge n - r'$  so that case (c) reduces to case (a). First note that vertex  $P_{l+1}$  has the form

$$P_{l+1} = x_1 x_2 \cdots x_{s'+(r-s)} a_{s'+1} a_{s'+2} \cdots a_{n-r'} y_1 y_2 \cdots y_{r'-(r-s)}.$$

By equating the corresponding bits of  $P_{l+1}$  and  $P_1 = a_1 a_2 \cdots a_n$ , we obtain the equations

$$(4.3) a_{r-s+i} = a_i (s'+1 \le i \le n-r').$$

It follows from (4.3) and  $s'+1 < u \le v < n-r'$  that the substring  $a_{r-s+u} \cdots a_{r-s+v} = a_u \cdots a_v$  is also an all zeros substring of length v-u+1. Continuing this way, the substring  $a_{m(r-s)+u} \cdots a_{m(r-s)+v}$  is an all zeros substring if  $(m-1)(r-s)+v \le n-r'$ . By letting t=m(r-s)+v and

$$m-1=\left[rac{n-r'-v}{r-s}

ight]\geq rac{n-r'-v}{r-s}-1$$

where [ ] denotes the greatest integer function, we obtain

$$t=m(r-s)+v\geq \left(rac{n-r'-v}{r-s}

ight)(r-s)+v=n-r'$$

which is what we set out to show.

To prove (ii), we use the result in part (i) which asserts the existence of a vertex  $P_i \in S_n^q$ . Then at least three of the four directed edges  $P_i$ 0,  $P_i$ 1,  $0P_i$ , and  $1P_i$  have the longest run of zeros either at the extreme left or the extreme right. Thus at least one of the two distinct edges  $E_{i-1}$  or  $E_i$  has its longest run of zeros either at the extreme left or the extreme right.

**Theorem 4.4.** (i) In an ambulance path of net length  $\geq n-2$  in  $B_n^q$ , there exists a vertex  $V \in S_n^q$ . (ii) In an ambulance path of net length  $\geq n$  in  $B_n^q$ , there exists a directed edge  $E \in S_{n+1}^q$ .

**Proof:** Let  $P_1 = a_1 a_2 \cdots a_n$  and let  $P_1, E_1, P_2, E_2, \cdots, P_l, E_l, P_{l+1}$  be the sequence of vertices and edges if we trace along an ambulance path from vertex  $P_1$  to  $P_{l+1}$ . Let  $d(P_i, P_j)$  denote the signed net length of the ambulance path from  $P_i$  to  $P_j$ . Without loss of generality, we assume  $d(P_1, P_{l+1})$  to be non-negative.

Suppose one of the longest run of zeros in  $P_1 = a_1 a_2 \cdots a_n$  is the substring  $a_u a_{u+1} \cdots a_v$ . If u=1 or v=n or  $P_1$  does not contain any zero, then  $P_1 \in S_n^q$  and we are done. Thus we only need to consider the case  $2 \le u \le v \le n-1$ . If  $d(P_1, P_{l+1}) \ge n-2$ , there must exist a positive integer v' such that v' is the smallest and  $d(P_1, P_{v'}) = n-v$  since  $n-v \le n-2 \le d(P_1, P_{l+1})$ . If  $P_i \notin S_n^q \ \forall 1 \le i < v'$ , then  $P_{v'} \in S_n^q$  since the substring  $a_u a_{u+1} \cdots a_v$  is a suffix of  $P_{v'}$ .

To prove part (ii), note that if  $d(P_1, P_{l+1}) \ge n$ , then  $d(P_2, P_l) \ge n - 2$ . By the result in part (i), there exists a vertex  $P_i$  ( $2 \le i \le l$ ) that is in the set  $S_n^q$ . Then at least one of the two directed edges  $E_{i-1}$  and  $E_i$  (which are in the form  $P_i$ 0,  $P_i$ 1,  $0P_i$ , or  $1P_i$ ) has its longest run of zeros either at the extreme left or the extreme right.

# 4.4. C-Chip VLSI Decompositions for DeBruijn Graphs $B_n^q$

In Chapter  $6^{\dagger}$ , there are some general theorems that can be used to obtain upper bounds on the efficiency for some VLSI decompositions. In particular, Theorem 6.3 together with Theorem 4.1 give a lower bound on the number of input edges w (defined in Section 6.1) for any subgraph of  $B_n^q$ .

Let H(m) be an induced subgraph  $^{\dagger\dagger}$  of  $B_n^q$  with m vertices. Let  $E_{\rm ext}$  be the set of edges  $e_i$  in  $B_n^q$  such that  $e_i$  has one endvertex in H(m) and the other endvertex not in H(m). Let  $H_{\rm ext}(m)$  be the union of H(m) and  $E_{\rm ext}$ . (As in Section 6.1, we call  $H_{\rm ext}(m)$  a subgraph with external edges.) By letting  $d_i = q$  for all the m vertices in the vertex set V of  $H_{\rm ext}(m)$  in Theorem 6.3, we obtain

$$(l+1)\sum_{v_i \in V} (q\log q) \le (wl + \sum_{v_i \in V} q)\log(wl + \sum_{v_i \in V} q) \qquad \forall l \le n$$

or

$$(4.4) (l+1)(qm) \le (wl+qm)\log_q(wl+qm) \forall l \le n.$$

Since  $(wl + qm)\log_q(wl + qm)$  is a monotonic increasing function of w, there exists an integer  $w_{\min}(q, m, l)$  which is the smallest among all integers w that satisfy Inequality (4.4) for a given q, m and l. By noting that (4.4) holds for all  $l \leq n$ , we obtain the lower bound

$$(4.5) w \ge w_{\text{lowerbound}}(q, m, n) = \max_{l \le n} w_{\min}(q, m, l)$$

on the number of input edges on any subgraph  $H_{\text{ext}}(m)$  of  $B_n^q$ . Consequently, since each vertex in  $H_{\text{ext}}(m)$  has in-degree q, the number of edges in any subgraph H(m) of  $B_n^q$  is bounded above by

(4.6)

$$E_{B_n^q}^*(m) \le qm - w_{\text{lowerbound}}(q, m, n).$$

<sup>†</sup> Most of Chapter 6 does not use results from other chapters and can be read independently.

<sup>†</sup> Induced subgraph is defined in the footnote on page 7.

It follows from (2.4) and (4.6) that the efficiency for a C-chip VLSI decomposition of deBruijn graph  $B_n^q$  into subgraphs  $H_1(k_1), H_2(k_2), \dots, H_C(k_C)$  of sizes  $k_1, k_2, \dots, k_C$  respectively is bounded above by

$$(4.7) \ \text{eff}(H_1(k_1), H_2(k_2), \cdots, H_C(k_C) \mapsto B_n^q) \le 1 - \frac{1}{q^{n+1}} \sum_{1 \le i \le C} w_{\text{lowerbound}}(q, k_i, n).$$

| <i>m</i> | n           | $w_{ m lowerbound}(q\!=\!2,m,n)$ |

|----------|-------------|----------------------------------|

| 1        | $n \geq 1$  | 1                                |

| 2        | $n \geq ~2$ | 1                                |

| 3        | $n \geq 8$  | 2                                |

| 4        | $n \geq 6$  | 2                                |

| 5-7      | $n \geq 5$  | 2                                |

| 8        | $n \ge 15$  | 3                                |

| 16       | $n \geq 12$ | 4                                |

| 32       | $n \geq 25$ | 7                                |

| 64       | $n \ge 36$  | 12                               |

| 128      | $n \geq 45$ | 21                               |

| 256      | $n \ge 59$  | 38                               |

| 512      | $n \geq 81$ | 70                               |

**Table 4.1.** Some values of  $w_{\text{lowerbound}}(q, m, n)$  for q = 2 and n sufficiently large.  $w_{\text{lowerbound}}(q, m, n)$  is defined in Equation (4.5).

Table 4.1 lists some values of  $w_{\text{lowerbound}}(q, m, n)$  for q = 2 and n is sufficiently large. Table 4.2 lists some other values of  $w_{\text{lowerbound}}(q, m, n)$  for q = 2 and m = 128. As an example, referring to Table 4.2,  $w_{\text{lowerbound}}(2, 128, 13) = 13$ . Thus if we

decompose  $B_{13}$  into 64 chips of equal sizes 128, there will be at least  $13 \times 64 = 832$  external wires or efficiency  $\leq 0.949$  as imposed by the upper bound in (4.7). From this example, (4.7) does not seem to be a tight upper bound (since the best decomposition we are able to find has an efficiency far less than 0.949). However, we will see that (4.7) is a rather good upper bound for large values of m and n when we study the asymptotic behavior of  $w_{\text{lowerbound}}(q, m, n)$  as  $m \to \infty$  and compare the result with Theorem 4.12.

| n                 | $w_{	ext{lowerbound}}(q\!=\!2,m\!=\!128,n)$ |

|-------------------|---------------------------------------------|

| 8                 | 4                                           |

| 9                 | 6                                           |

| 10                | 8                                           |

| 11                | 10                                          |

| 12                | 11                                          |

| $13 \le n \le 14$ | 13                                          |

| 15                | 14                                          |

| 16                | 15                                          |

| $17 \le n \le 18$ | 16                                          |

| $19 \le n \le 21$ | 17                                          |

| $22 \le n \le 25$ | 18                                          |

| $26 \le n \le 31$ | 19                                          |

| $32 \le n \le 44$ | 20                                          |

| $45 \le n$        | 21                                          |

**Table 4.2.** Some values of  $w_{\text{lowerbound}}(q, m, n)$  for q = 2 and m = 128.  $w_{\text{lowerbound}}(q, m, n)$  is defined in Equation (4.5).

**Lemma 4.5.** Let X and Y be positive integers such that  $X \ge b$  and  $Y \ge 1$ . If  $X \le Y \log_b Y$ , then  $Y \ge X/(\log_b X)$ .

**Proof:** We have

$$\begin{split} \frac{X}{\log_b X} \log_b \left( \frac{X}{\log_b X} \right) &= \frac{X}{\log_b X} \left( \log_b X - \log_b \log_b X \right) \\ &\leq \frac{X}{\log_b X} (\log_b X) = X \leq Y \log_b Y \end{split}$$

and  $Y \log_b Y$  is a monotonic increasing function for  $Y \geq 1$ .

We may apply Lemma 4.5 on Inequality (4.4) to obtain

$$egin{aligned} w_{ ext{lowerbound}}(q,m,n) &\geq rac{(l+1)(qm)}{l\log_q\left((l+1)(qm)

ight)} - rac{qm}{l} \ &= rac{(qm)(l+1-\log_q(l+1)-\log_q(qm))}{(l)(\log_q(l+1)+\log_q(qm))} \qquad orall l \leq n \end{aligned}$$

or

$$(4.8) w_{\text{lowerbound}}(q, m, n) \ge \max_{l \le n} \frac{(qm)(l + 1 - \log_q(l + 1) - \log_q(qm))}{(l)(\log_q(l + 1) + \log_q(qm))}.$$

For  $n \ge (\log_q m)^{1+\alpha}$  where  $\alpha$  is a constant > 0, we may let  $l = (\log_q m)^{1+\alpha}$  in (4.8) to obtain

$$\begin{split} w_{\text{lowerbound}}(q,m,n) &\geq \frac{(qm)((\log_q m)^{1+\alpha} + 1 - \log_q((\log_q m)^{1+\alpha} + 1) - \log_q(qm))}{((\log_q m)^{1+\alpha})(\log_q((\log_q m)^{1+\alpha} + 1) + \log_q(qm))} \\ (4.9) & \qquad \qquad \asymp \frac{qm}{\log_q m} \qquad \text{as} \quad m \to \infty. \end{split}$$

That is, if a large deBruijn graph  $B_n^q$  is decomposed into sufficiently small chips of sizes  $k_1, k_2, \ldots, k_C$ , then there are at least

$$\sum_{i=1}^{C} \frac{qk_i}{\log_q k_i}$$

external wires.

### 4.5. DeBruijn Building Blocks

From Theorems 4.1 and 4.2, we obtain two necessary conditions for deBruijn building blocks.

**Theorem 4.6.** If a graph H of size  $q^k/C$  is a building block for the deBruijn graph  $B_n^q$ , then

- (i) For any two vertices X and Y in H, there cannot be more than one path of the same length  $l \leq n$  from X to Y.

- (ii) H does not contain any unbalanced cycle of length  $l < \log_q C$ .

**Proof:** Part (i) follows immediately from Theorem 4.1 since H is a subgraph of  $B_n^q$ . To prove (ii), note that Theorem 4.2 implies that  $C \leq q^l/l \leq q^l$ .

We may use the results in Section 4.4 to obtain an upper bound for the efficiency of deBruijn building blocks. By letting  $k_1 = k_2 = \cdots = k_C = q^k$  in Equation (4.7), the efficiency for a building block of size  $q^k$  for the deBruijn graph  $B_n^q$  is bounded above by

(4.10)

$$e_{\mathbf{I}}(B_n^q; q^k) \le e_{\mathbf{N}\mathbf{I}}(B_n^q; q^k) \le 1 - \frac{w_{\text{lowerbound}}(q, q^k, n)}{q^{k+1}}$$

where

(4.11)

$$\liminf_{k \to \infty} w_{\text{lowerbound}}(q, q^k, n) \ge \frac{q^{k+1}}{k}$$

for  $n \ge k^{1+\alpha}$  (where  $\alpha > 0$ ) as implied by (4.9). That is, if a large deBruijn graph  $B_n^q$  is decomposed into sufficiently small subgraphs of equal sizes  $q^k$ , then the set of external edges will contain at least 1/k of the edges in  $B_n^q$ .

### 4.6. Universal DeBruijn Building Blocks

We consider universal deBruijn building blocks for the family of deBruijn graphs  $\{B_n^q\}_{n\geq N}$ . Since a universal deBruijn building block is necessary to build deBruijn graphs  $B_n^q$  with arbitrary large n, it follows from Theorem 4.6 that

- (i) A universal deBruijn building block cannot contain two vertices X and Y such that there are two paths of the same length from X to Y.

- (ii) A universal deBruijn building block cannot contain any unbalanced cycle.

Condition (ii) is equivalent to the statement that a universal deBruijn building block must be a *graded* digraph. In the following, we first introduce the notion of a graded digraph and then prove the equivalence between digraphs with no unbalanced cycle and graded digraphs in Lemma 4.7.

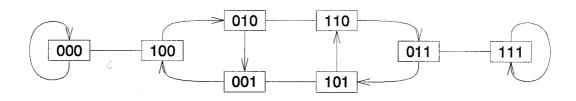

A digraph G with vertex set V is graded of rank m if there is a mapping  $\rho$  from the vertex set V to the set  $\{0, 1, ..., m\}$ , such that, for  $x, y \in V$ ,  $\rho(y) = \rho(x) + 1$  if there is a directed edge from x to y. We call  $\rho(x)$  the rank of x.

**Lemma 4.7.** Let H be a digraph. H is a graded digraph of rank m iff all cycles in H are balanced and all ambulance paths in H have net length  $\leq m$ .

**Proof:** We will first prove the "if" portion and then the "only if" portion of the lemma.

Suppose all cycles in H are balanced and all ambulance paths in H have not length  $\leq m$ . Let V be the vertex set of digraph H. We will prove that H is a graded digraph of rank m by constructing a rank function  $\rho$  that maps the vertex set V to the set  $\{0,1,\ldots,m\}$ . Without loss of generality, H is assumed to be a connected graph. Otherwise, if H is the union of two disjoint subgraphs  $H_1$  and  $H_2$  whose rank functions (defined in this proof) are  $\rho_1$  and  $\rho_2$  respectively, then, for each vertex v in graph H, we may let  $\rho(v)$  to be  $\rho_1(v)$  (or  $\rho_2(v)$ ) if v is in

the subgraph  $H_1$  (or  $H_2$ ).

To construct  $\rho$ , we first choose an arbitrary vertex  $v_0 \in V$  and assign an arbitrary integer  $N(v_0)$  to this vertex. For each of the other vertices  $v \in V$  ( $v \neq v_0$ ), there must be at least one ambulance path from  $v_0$  to v since H is connected. If there is an ambulance path with f forward edges and b backward edges from  $v_0$  to v, we assign the integer

$$N(v) = N(v_0) + f - b$$

to vertex v. If there are two ambulance paths, say  $P_1$  and  $P_2$ , from  $v_0$  to v, we obtain the same assignment N(v) independent of the path  $P_1$  or  $P_2$  that is used. Such a consistency exists since all cycles in H are balanced by hypothesis and thus the cycle that is composed of  $P_1$  and  $P_2$  ( $P_2$  being traced from v to  $v_0$ ) must also be balanced.

Now let  $N_{\min}$  (which may be negative) be the smallest integer in the set  $\{N(v), v \in V\}$ . (A minimum exists since there is a finite number of elements in the set  $\{N(v), v \in V\}$ .) For each  $v \in V$ , we assign the rank

$$\rho(v) = N(v) - N_{\min}.$$

To show that the mapping  $\rho$  is indeed a rank function, we need to prove that  $\rho(w) = \rho(v) + 1$  if there is a directed edge from v to w. This can be shown by considering the cycle composed by path  $P_v$  (an ambulance path from  $v_0$  to v), the directed edge from v to w, and path  $P'_w$  (an ambulance path from w to  $v_0$ ). Let  $P_v$  ( $P'_w$ ) contains  $f_v$  ( $f'_w$ ) forward edges and  $b_v$  ( $b'_w$ ) backward edges. Since all cycles in graph H are balanced by hypothesis,

$$f_v - b_v + 1 + f'_w - b'_w = 0.$$

Consequently,

$$\rho(v) - \rho(w) = N(v) - N(w) = (f_v - b_v) - (b'_w - f'_w) = -1$$

which is set out to be shown.

In addition, since all ambulance paths in graph H have net length  $\leq m$  by hypothesis and  $\ell = |N(x) - N(y)|$  indicates the existence of a path of net length  $\ell$  between vertices x and y,

$$0 \le \rho(v) = |\rho(v)| = |N(v) - N_{\min}| \le m$$

for any  $v \in V$ . Thus  $\rho$  is a mapping from the vertex set V of graph H to the set  $\{0,1,\ldots,m\}$  and H is a graded digraph of rank m.

We need to prove that (i) all ambulance paths in H have net length  $\leq m$  and (ii) all cycles in H are balanced.

To prove (i), consider any ambulance path of net length  $\ell$  between vertices v and w. Then

$$\ell = |\rho(v) - \rho(w)| \le \rho(v) - 0 \le m$$

by hypothesis. Thus all ambulance paths in H have not length  $\leq m$ .

To prove (ii), let A be a vertex on a cycle in graph H. This cycle can also be considered as an ambulance path of net length  $\ell = \rho(A) - \rho(A) = 0$  that starts from vertex A and back to A. Thus this cycle must be a balanced cycle.

Theorem 4.8 summarizes the necessary conditions for universal deBruijn building blocks.

**Theorem 4.8.** If a digraph H is a universal deBruijn building block for the family of deBruijn graphs  $\{B_n^q\}_{n\geq N}$ , then

- (i) H cannot contain two vertices X and Y such that there are more than one path of the same length from X to Y.

- (ii) H is a graded digraph.

**Proof:** Condition (i) follows from Theorem 4.6 (i). Condition (ii) follows from Theorem 4.6 (ii) and Lemma 4.7.

Many digraphs satisfy the two necessary conditions listed in Theorem 4.8. In particular, any spanning subgraph  $^{\dagger}$  H of  $B_k^q$  that is a graded digraph will definitely satisfy condition (ii). If we further restrict the rank of H to be  $\leq k$ , condition (i) will also be satisfied by Theorem 4.1 and Lemma 4.7. Surprisingly, these two conditions, i.e.,

- (iii) H is a graded digraph.

- (iv) H has rank  $\leq k$ .

are actually sufficient conditions for any spanning subgraph H of  $B_k^q$  to be a universal deBruijn building block for the family of deBruijn graphs  $\{B_n^q\}_{n\geq k}$ .

**Theorem 4.9.** Any spanning subgraph of  $B_k^q$  that is a graded digraph of rank  $\leq k$  is a universal deBruijn building block for the family of deBruijn graphs  $\{B_n^q\}_{n\geq k}$ .

We first prove two lemmas that are necessary to prove Theorem 4.9. For convenience, we define  $V_n^q$  to be the set of all n-dimensional q-ary vectors. For a fixed q, we define three linear mappings L, R, and C ("left," "right," and "center") from  $V_n^q$  to  $V_{n-1}^q$ . (Technically, the mappings L, R, and C are each families of mappings, one for each  $n \geq 2$ .) If  $x = [x_1, \ldots, x_n]$  is a q-ary vector of length n, then

$$Lx = (x_1, \dots, x_{n-1})$$

$Rx = (x_2, \dots, x_n)$

$Cx = (x_1 - x_2, \dots, x_{n-1} - x_n) \pmod{q}.$

For example, for q=2, if x=[10110], then Lx=[1011], Rx=[0110], and Cx=[1101].

<sup>&</sup>lt;sup> $\dagger$ </sup> A spanning subgraph H of graph G is a subgraph that contains all vertices of G.

**Lemma 4.10.** The mappings L and R commute with C, i.e., CLx = LCx and CRx = RCx for any q-ary vector x of length  $\geq 3$ .

**Proof:** By direct computation we find that if  $x = [x_1, \ldots, x_n]$ , then

$$CLx = LCx = [x_1 - x_2, \dots, x_{n-2} - x_{n-1}];$$

$CRx = RCx = [x_2 - x_3, \dots, x_{n-1} - x_n].$

We now define the burst agreement B(x,y) between two n-vectors x and y as the length of the largest block of consecutive components on which x and y agree. For example if x = [11010010] and y = [01110001], then B(x,y) = 3 because x and y agree in positions 4, 5, and 6, but in no set of four or more consecutive positions.

**Lemma 4.11.** If x and y are two n-vectors with  $C^r x = C^r y$ , and  $B(x,y) \ge r$ , then x = y.

**Proof:** We use induction on r. For r=1, the assertion is that if Cx=Cy, and if x and y agree in at least one coordinate, then x and y are identical. To see that this is so, note that C is a linear mapping from  $V_n^q$  to  $V_{n-1}^q$ . Its nullspace, i.e., the set of x's such that Cx=0, is the set of vectors  $[x_1,\ldots,x_n]$  such that  $x_1-x_2=x_2-x_3=\cdots=x_{n-1}-x_n=0$ . This set contains only the q vectors  $[00\cdots 0], [11\cdots 1], \ldots, [q-1,q-1,\cdots,q-1]$ . Thus if Cx=Cy, then either x=y or  $x=y+[ii\cdots i]$   $(1\leq i\leq q-1)$ , i.e., x and y differ in all n positions. It follows that if Cx=Cy and if x and y agree in at least one place, then x=y. This completes the proof for r=1.

We now assume  $r \geq 2$ , and that the lemma has been proved for all r' < r. If  $B(x,y) \geq r$ , i.e., if x and y agree on r consecutive positions, then clearly Cx and Cy agree on at least r-1 positions. Thus if we let x' = Cx and y' = Cy, then  $B(x',y') \geq r-1$ . Also, the hypothesis  $C^rx = C^ry$  is equivalent to  $C^{r-1}x' = C^{r-1}y'$ . Thus by the induction hypothesis, x' = y', i.e., Cx = Cy. But also  $B(x,y) \geq r \geq 1$ ,

so that by the r = 1 case of the lemma, which has already been proved, x = y.

We now return to prove Theorem 4.9 by showing that any spanning subgraph of  $B_k^q$  that is a graded digraph of rank k builds  $B_n^q$  for all  $n \ge k$ .

**Proof of Theorem 4.9:** Let  $H_k^q$  be a spanning subgraph of  $B_k^q$  that is also a graded digraph of rank k. Let  $\rho$  be the rank function that maps the vertex set  $V_k^q$  of  $H_k^q$  to the set  $\{0,1,\ldots,k\}$ . For any  $X=[X_1,X_2,\ldots,X_n]\in V_n^q$ , suppose that  $C^{n-k}X=x\in V_k^q$ , and  $\rho(x)=i$ . We define the (n-k)-bit chip number of X, denoted by  $\operatorname{num}(X)$ , as

$$(\tilde{4}.12) \qquad \text{num}(X) = [X_{i+1}, \dots, X_{i+n-k}].$$

Note that since  $0 \le i \le k$ , then  $1 \le i+1 \le i+n-k \le n$ , so that the chip number as defined in (4.12) "fits" within the field of X. In building  $B_n^q$  with  $q^{n-k}$  copies of  $H_k^q$  ("chips"), numbered  $[0,0,\cdots,0]$  to  $[q-1,q-1,\cdots,q-1]$ , we place vertex X on the chip numbered num(X), at the location corresponding to  $x=C^{n-k}X$ . Lemma 4.11 shows that no two vertices of  $B_n^q$  can be assigned the same location on the same chip, so that each of the  $q^n$  vertices in  $B_n^q$  is assigned a unique "home" on one of the  $q^{n-k}$  chips. What remains to show is that the connections within the chips correspond to connections in the big graph  $B_n^q$ , i.e., that if  $\operatorname{num}(X) = \operatorname{num}(Y)$  and if  $C^{n-k}X$  and  $C^{n-k}Y$  are connected on  $H_k^q$ , then X and Y are connected in  $B_n^q$ , i.e., LX = RY.

To see this, we reason as follows. Since  $C^{n-k}X$  and  $C^{n-k}Y$  are connected on  $H_k^q$ , then  $\rho(C^{n-k}Y) = \rho(C^{n-k}X) + 1$ . Thus if  $\rho(C^{n-k}X) = i$ , then  $\rho(C^{n-k}Y) = i + 1$ , and so, since  $\operatorname{num}(X) = \operatorname{num}(Y)$ , we have

$$[X_{i+1},\ldots,X_{i+n-k}]=[Y_{i+2},\ldots,Y_{i+n-k+1}].$$

Thus LX and RY agree on n-k consecutive positions, i.e.,

$$(4.13) B(LX,RY) \ge n - k.$$

But also, since  $C^{n-k}X$  and  $C^{n-k}Y$  are connected on  $H_k^q$ , we have  $LC^{n-k}X = RC^{n-k}Y$ , which, by Lemma 4.10, implies

$$(4.14) C^{n-k}LX = C^{n-k}RY.$$

Combining (4.13) and (4.14), using Lemma 4.11, we find that LX = RY, which is what we set out to prove.

There is a small gap between the necessary conditions (Theorem 4.8) and the sufficient conditions (Theorem 4.9) on universal deBruijn building blocks. If H is a spanning subgraph of  $B_k^q$  such that H satisfies the necessary conditions (in Theorem 4.8) and H has rank > k, it is not known, in general, whether or not H is a universal deBruijn building block. All the graphs that have been found in this "gap" have been shown to be universal deBruijn building blocks. As an example, a Hamilton path of  $B_k^q$ , which falls into this "gap", is a universal deBruijn building block since all deBruijn graphs  $B_n^q$  are Hamiltonian [Golo82]. However, the construction in Theorem 4.9 fails to provide a general proof since num(X) in Equation (4.12) does not "fit" within the field of X.

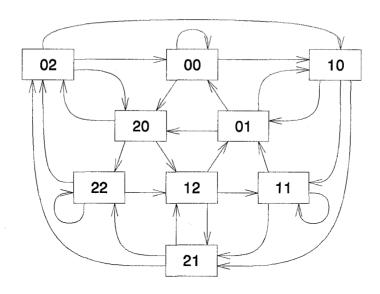

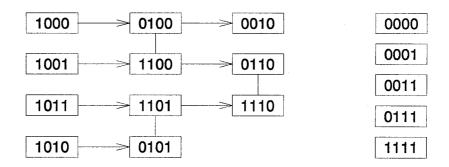

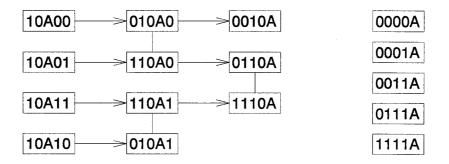

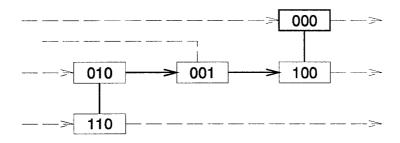

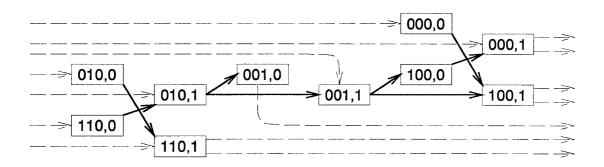

## 4.7. An Example For Building $B_n^q$

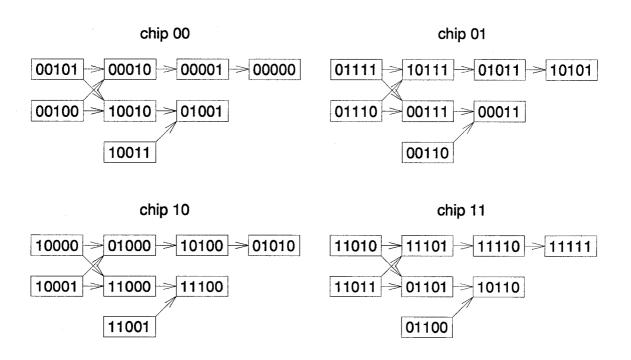

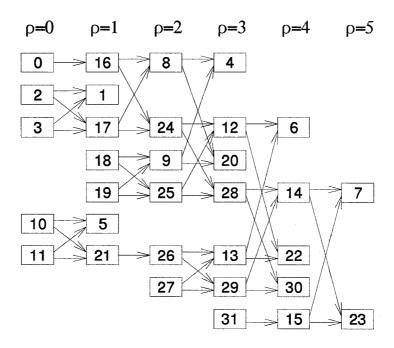

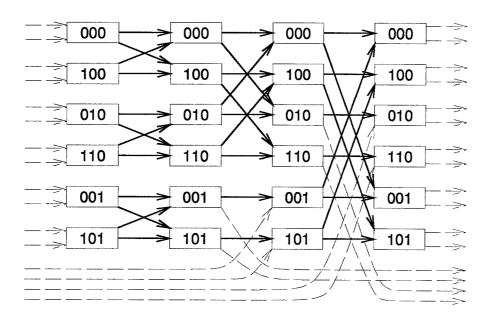

In Figure 4.4, the graph  $B_3(\rho)$  is both a spanning subgraph of  $B_3$  and a graded digraph of rank 3. By Theorem 4.9,  $B_3(\rho)$  is a universal deBruijn building block for the family of deBruijn graphs  $\{B_n\}_{n\geq 3}$ . We illustrate the construction in the proof of Theorem 4.9, by building the graph  $B_5$  with four copies of the universal deBruijn building block  $B_3(\rho)$ . We begin with Table 4.3, which lists, for each of the 32 possible 5-bit vectors X, the 3-bit vector  $x = C^2X$ , and the corresponding rank  $\rho(x)$ .

We number the four copies of  $B_3(\rho)$  00, 01, 10 and 11. Table 4.3 can be used to find the chip number and the location within a chip of each 5-bit vector X, as

Figure 4.4. The universal deBruijn building block  $B_3(\rho)$ .

Figure 4.5. Four copies of the graph  $B_3(\rho)$  in Figure 4.4 labelled to form a spanning subgraph of  $B_5$ . This is a four-chip VLSI decomposition of  $B_5$  of efficiency 0.50.

| X              | $x = C^2 X$ | ho(x) | X                              | $x = C^2 X$ | ho(x) |

|----------------|-------------|-------|--------------------------------|-------------|-------|

| 000 <u>00</u>  | 000         | 3     | $\overline{\underline{10000}}$ | 100         | 0     |

| 00 <u>00</u> 1 | 001         | 2     | $\underline{10}001$            | 101         | 0     |

| 0 <u>00</u> 10 | 010         | 1     | 1 <u>00</u> 10                 | 110         | 1     |

| 00 <u>01</u> 1 | 011         | 2     | 1 <u>00</u> 11                 | 111         | 1     |

| <u>00</u> 100  | 101         | 0     | 10 <u>10</u> 0                 | 001         | 2     |

| <u>00</u> 101  | 100         | 0     | 101 <u>01</u>                  | 000         | 3     |

| 0 <u>01</u> 10 | 111         | 1     | 10 <u>11</u> 0                 | 011         | 2     |

| 0 <u>01</u> 11 | 110         | 1     | 1 <u>01</u> 11                 | 010         | 1     |

| 0 <u>10</u> 00 | 010         | 1     | 1 <u>10</u> 00                 | 110         | 1     |

| 01 <u>00</u> 1 | 011         | 2     | 1 <u>10</u> 01                 | 111         | 1     |

| 010 <u>10</u>  | 000         | 3     | <u>11</u> 010                  | 100         | 0     |

| 01 <u>01</u> 1 | 001         | 2     | <u>11</u> 011                  | 101         | 0     |

| 0 <u>11</u> 00 | 111         | 1     | 11 <u>10</u> 0                 | 011         | 2     |

| 0 <u>11</u> 01 | 110         | 1     | 1 <u>11</u> 01                 | 010         | 1     |

| <u>01</u> 110  | 101         | 0     | 11 <u>11</u> 0                 | 001         | 2     |

| <u>01</u> 111  | 100         | 0     | 111 <u>11</u>                  | 000         | 3     |

**Table 4.3.** A table for building  $B_5$  from 4 copies of the graph  $B_3(\rho)$  in Figure 4.4.

follows. For a given X, the value  $x = C^2X$  gives the location, and the two bits of X in positions  $\rho(x) + 1$  and  $\rho(x) + 2$ , which are underlined in the table, give the chip number. For example, consider X = 11000. According to the table, x = 110,  $\rho(x) = 1$ , and the underlined bits are 10. Thus X is placed in location 110 in the chip numbered 10. The complete assignment of vertices of  $B_5$  to the four chips is shown in Figure 4.5. Note that these four chips can be wired together to form  $B_5$  with an efficiency of 0.50.

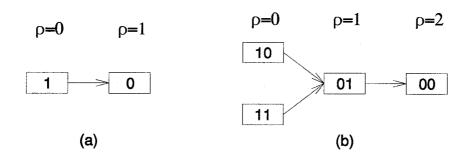

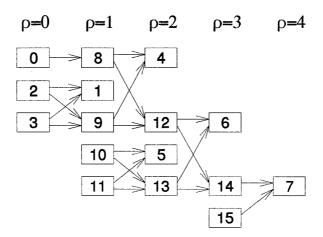

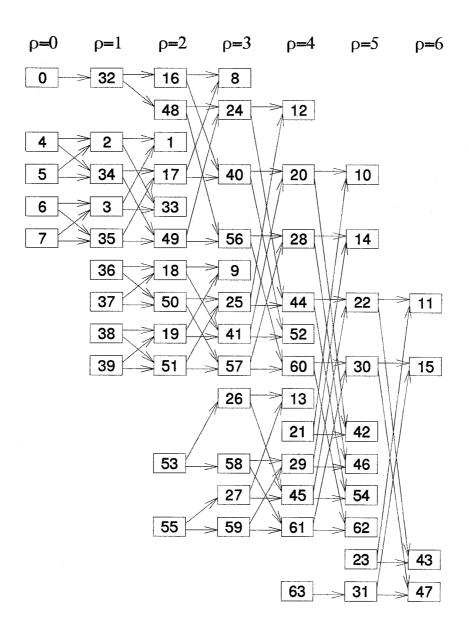

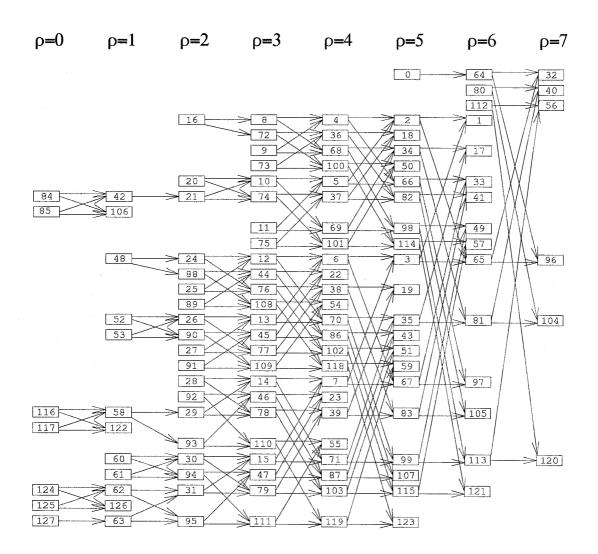

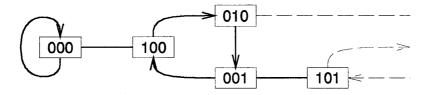

### 4.8. The Most Efficient Known Universal DeBruijn Building Blocks

From Theorem 4.9, we can obtain universal deBruijn building blocks  $U_{(q,k)}$  of size  $q^k$  for the family of deBruijn graphs  $\{B_n^q\}_{n\geq k}$  by searching for spanning subgraphs of  $B_k^q$  that is a graded digraph of rank  $\leq k$ . Figures 4.4 and 4.6–4.10 show the most efficient  $U_{(2,k)}$  building blocks we have been able to find, using ad hoc methods, for  $1\leq k\leq 7$ . In particular, Figure 4.10 shows the most efficient known  $U_{(2,7)}$  building block that is being used to build the single board Viterbi decoder for the Galileo code. (In Figures 4.7–4.10, the vertex labels shown are the decimal equivalents of the actual binary labels.) For each of the most efficient known  $U_{(2,k)}$  building blocks, we list, in Table 4.4, the number of edges  $E(U_{(2,k)})$  and the efficiency

(4.15)

$$\operatorname{eff}(U_{(q,k)} \vdash B_n^q) = \frac{q^{n-k} \operatorname{E}(U_{(q,k)})}{q^{n+1}} = \frac{\operatorname{E}(U_{(q,k)})}{q^{k+1}}$$

which is independent of n. That is, the efficiency of a universal deBruijn building block  $U_{(q,k)}$  is independent of the size of the deBruijn graph  $B_n^q$  which it is used to build.

**Figure 4.6.** (a) The most efficient  $U_{(2,1)}$  building block. (b) The most efficient  $U_{(2,2)}$  building block.

The building block for k=5 was discovered by Gordon Oliver and the building blocks for k=6 and k=7 were discovered by Sam Dolinar, both from the Jet Propulsion Laboratories. Gordon has also found a building block for k=8 with 398 edges.

| k | $U_{(2,k)}$   | $\mathrm{E}(U_{(2,k)})$ | $\operatorname{eff}(U_{(q,k)} \vdash B_n^q)$ | $c_{(2,k)}$ | $\mathbf{E}_{	ext{	t ubound}}(U_{(2,k)})$ |

|---|---------------|-------------------------|----------------------------------------------|-------------|-------------------------------------------|

| 1 | Fig. 4.6(a)   | 1                       | 0.250                                        | 1.500       | 1                                         |

| 2 | Fig. $4.6(b)$ | 3                       | 0.375                                        | 1.875       | 4                                         |

| 3 | Fig. 4.4      | 8                       | 0.500                                        | 2.000       | 9                                         |

| 4 | Fig. 4.7      | 19                      | 0.594                                        | 2.031       | 22                                        |

| 5 | Fig. 4.8      | 43                      | 0.672                                        | 1.969       | 48                                        |

| 6 | Fig. 4.9      | 92                      | 0.719                                        | 1.969       | 101                                       |

| 7 | Fig. 4.10     | 193                     | 0.754                                        | 1.969       | 209                                       |

| 8 | Fig           | 398                     | 0.777                                        | 2.004       | 431                                       |

**Table 4.4.** The most efficient known  $U_{(2,k)}$  building blocks, for  $1 \leq k \leq 8$ .  $c_{(2,k)}$  and  $E_{ubound}(U_{(2,k)})$  are defined in Equations (4.19) and (4.17).

We have been able to show by exhaustive search that the entries for  $1 \le k \le 4$  are optimal in Table 4.4. For larger values of k, we can determine how much improvement may be possible by obtaining an upper bound for the number of edges in a  $U_{(q,k)}$  building block. We note that there is at most one path between any two vertices X and Y in a universal deBruijn building block as implied by necessary conditions (i) and (ii) in Theorem 4.8. Thus we may apply Theorem 6.2 to obtain a lower bound on the number of input edges w (defined in Section 6.1) for any universal deBruijn building block  $U_{(q,k)}$  with  $q^k$  vertices. By letting  $d_i = q$  for all the  $q^k$  vertices  $v_i$  in Theorem 6.2, we obtain

$$(4.16) q^{k+1} \le w \log_q w.$$

Since  $w \log_q w$  is a monotonic increasing function, there exists an integer  $w_{\min}(q, k)$ , for a given q and k, which is the smallest among all integers w that satisfy Inequal-

Figure 4.7. The most efficient  $U_{(2,4)}$  building block. The edge count is 19.

ity (4.16). Then the number of edges in any universal de Bruijn building block  $U_{(q,k)}$  is bounded above by

(4.17)

$$E(U_{(q,k)}) \le E_{\text{ubound}}(U_{(q,k)}) = q^{k+1} - w_{\min}(q,k).$$

The values of  $E_{ubound}(U_{(2,k)})$ , for  $1 \leq k \leq 8$ , are listed in Table 4.4.

Similar to the derivation in Section 4.4, we may apply Lemma 4.5 on Inequality (4.16) to obtain

$$w \ge \frac{q^{k+1}}{k+1}.$$

Thus (4.17) becomes, after dividing both sides by  $q^{k+1}$ ,

(4.18)

$$\operatorname{eff}(U_{(q,k)} \vdash B_n^q) \le 1 - \frac{1}{k+1}.$$

The following theorem gives a general construction for universal deBruijn building blocks that have an efficiency very close to the upper bound (4.18).

**Theorem 4.12.** Let  $S_n^q$  be the set of all q-ary strings X of length n such that one of the longest run of zeros in X is either at the extreme left or the extreme right.

Figure 4.8. The most efficient known  $U_{(2,5)}$  building block. The edge count is 43.

Let  $H_k^q$  be a spanning subgraph of  $B_k^q$  that does not contain any edge  $\in S_{k+1}^q$  and contains all edges  $\notin S_{k+1}^q$ .  $H_k^q$  is a universal deBruijn building block for the family of deBruijn graphs  $\{B_n^q\}_{n\geq k}$  with an efficiency  $> 1 - 2q^2/(k+3)$ .

**Proof:** By Theorems 4.3, 4.4, and Lemma 4.7,  $H_k^q$  is a graded digraph of rank  $\leq k$ . Since  $H_k^q$  is also a spanning subgraph of  $B_k^q$ , by Theorem 4.9,  $H_k^q$  is a universal deBruijn building block for the family of deBruijn graphs  $\{B_n^q\}_{n\geq k}$ .

To obtain the efficiency, we use an idea from Schwabe [Schw91] to count the number of elements in the set  $S_{k+1}^q$ . Let  $Y \subset S_{k+1}^q$  be the set of q-ary strings X of length k+1 such that one of the longest run of zeros in X is at the extreme left. Consider the mapping  $Y \to 0Y1$ . This is a one-to-one mapping of strings  $\in Y$  to strings of length k+3 that have a unique longest run of zeros at the extreme left

Figure 4.9. The most efficient known  $U_{(2,6)}$  building block. The edge count is 92.

and are lexicographically least among their cyclic shifts. The size of this set and thus the number of elments in Y is  $< q^{k+3}/(k+3)$ . Similarly, the number of q-ary strings  $X \in S^q_{k+1}$  such that one of the longest run of zeros in X is at the extreme right is also  $< q^{k+3}/(k+3)$ .

**Figure 4.10.** The most efficient known  $U_{(2,7)}$  building block. The edge count is 193.

Consequently, the number of elements in  $S_{k+1}^q$  is  $< 2q^{k+3}/(k+3)$  and the efficiency is

$$\operatorname{eff}(H_q^k \vdash B_n^q) > 1 - \frac{2q^2}{k+3}$$

as stated in this theorem.

Combining (4.18) and Theorem 4.12, we obtain

$$(4.19) 1 - \frac{2q^2}{k+3} < \liminf_{k \to \infty} e_{(q,k)}^* \le \limsup_{k \to \infty} e_{(q,k)}^* \le 1 - \frac{1}{k+1}$$

where  $e_{(q,k)}^*$  denotes the efficiency for the most efficient universal deBruijn building block  $U_{(q,k)}$ .

We may obtain similar asymptotic behavior for general VLSI decomposition for deBruijn graphs  $B_n^q$ . Combining (4.10), (4.11) and Theorem 4.12, we obtain

$$(4.20) 1 - \frac{2q^2}{k+3} < \liminf_{k \to \infty} e_{\text{NI}}(B_n^q; q^k) \le \limsup_{k \to \infty} e_{\text{NI}}(B_n^q; q^k) \le 1 - \frac{1}{k}$$

and

$$(4.21) 1 - \frac{2q^2}{k+3} < \liminf_{k \to \infty} e_{\mathfrak{I}}(B_n^q; q^k) \le \limsup_{k \to \infty} e_{\mathfrak{I}}(B_n^q; q^k) \le 1 - \frac{1}{k}.$$

By comparing (4.19) with (4.20) and (4.21), we can conclude that it is not a severe restriction in requiring the subgraphs to be both "isomorphic" and "universal" in a VLSI decomposition of deBruijn graphs  $B_n^q$  into a large number of subgraphs.

In Table 4.4, we also list the values of  $c_{(q,k)}$  which is defined by

(4.22)

$$\operatorname{eff}(U_{(q,k)} \vdash B_n^q) = 1 - \frac{c_{(q,k)}}{k+1}.$$

It seems that the efficiency for the most efficient  $U_{(2,k)}$  building block approaches 1-2/(k+1) as  $k\to\infty$ .

### V. Shuffle-Exchange Graphs

### 5.1. Binary Shuffle-Exchange Graphs $\Psi_n$