# Accurate and Precise Computation using Analog VLSI, with Applications to

Computer Graphics and Neural Networks

Thesis by

David B. Kirk

In Partial Fulfillment of the Requirements

for the Degree of

Doctor of Philosophy

California Institute of Technology

Pasadena, California

1993

(Defended March 16, 1993)

Copyright © 1993

David B. Kirk

All Rights Reserved,

Except Permission Granted to Caltech to Reproduce Free of Charge.

#### Acknowledgements

Thanks to both Alan Barr and Carver Mead for ideas, encouragement, and support for this project.

This thesis is a synthesis based on inspiration from work being done in both Alan Barr's Graphics

Lab and Carver Mead's Physics of Computation Lab. In particular, Al has been especially helpful to me in choosing a productive path from myriad possibilities.

Many, many thanks to my collaborators, Kurt Fleischer, Lloyd Watts, and Douglas Kerns for their dedication and interest in making our joint projects successful. Special thanks to Kurt, who has been a frequent and important collaborator. Thanks to John LeMoncheck for help getting our physical chip testing setup together, and generally helping me to get chips built. I am also indebted to all of the members of the graphics lab, for moral support, tool support, technical advice, and in general making the lab a productive place to work.

This work was supported in part by an AT&T Bell Laboratories Ph.D. Fellowship, and by grants from Apple, DEC, Hewlett Packard, and IBM. Additional support was provided by NSF (ASC-89-20219), as part of the NSF/DARPA STC for Computer Graphics and Scientific Visualization. All opinions, findings, conclusions, or recommendations expressed in this document are those of the author and do not necessarily reflect the views of the sponsoring agencies.

#### Abstract

This thesis develops an engineering practice and design methodology to enable us to use CMOS analog VLSI chips to perform more accurate and precise computation. These techniques form the basis of an approach that permits us to build computer graphics and neural network applications using analog VLSI. The nature of the design methodology focuses on defining goals for circuit behavior to be met as part of the design process.

To increase the accuracy of analog computation, we develop techniques for creating compensated circuit building blocks, where compensation implies the cancellation of device variations, offsets, and nonlinearities. These compensated building blocks can be used as components in larger and more complex circuits, which can then also be compensated. To this end, we develop techniques for automatically determining appropriate parameters for circuits, using constrained optimization. We also fabricate circuits that implement multi-dimensional gradient estimation for a gradient descent optimization technique. The parameter-setting and optimization tools allow us to automatically choose values for compensating our circuit building blocks, based on our goals for the circuit performance. We can also use the techniques to optimize parameters for larger systems, applying the goal-based techniques hierarchically. We also describe a set of thought experiments involving circuit techniques for increasing the precision of analog computation.

Our engineering design methodology is a step toward easier use of analog VLSI to solve problems in computer graphics and neural networks. We provide data measured from compensated multipliers Abstract

built using these design techniques. To demonstrate the feasibility of using analog VLSI for more quantitative computation, we develop small applications using the goal-based design approach and compensated components. Finally, we conclude by discussing the expected significance of this work for the wider use of analog VLSI for quantitative computation, as well as qualitative.

#### Contents

| Acknowledgements |                                                     |                                                                    |    |  |  |

|------------------|-----------------------------------------------------|--------------------------------------------------------------------|----|--|--|

| $\boldsymbol{A}$ | Abstract                                            |                                                                    |    |  |  |

| In               | dex o                                               | $f\ Figures$                                                       | xi |  |  |

| 1                | Inti                                                | $\operatorname{roduction}$                                         | 1  |  |  |

|                  | 1.1                                                 | Why Use Analog VLSI?                                               | 2  |  |  |

|                  |                                                     | 1.1.1 Why Not Analog VLSI                                          | 4  |  |  |

|                  |                                                     | 1.1.2 Our Approach: Kill the "Why-nots"                            | 5  |  |  |

|                  | 1.2                                                 | Describing the Physical World with Mathematical Models and Goals   | 5  |  |  |

|                  | 1.3                                                 | Advantages and Disadvantages of Simulation using Digital Computers | 7  |  |  |

|                  | 1.4                                                 | Advantage and Disadvantages of Simulation using Analog Computation | 9  |  |  |

|                  | 1.5                                                 | Using Goals for Analog VLSI Computation                            | 11 |  |  |

|                  | 1.6                                                 | Thesis Roadmap                                                     | 12 |  |  |

| 2                | Approaching Quantitative Computation in Analog VLSI |                                                                    |    |  |  |

|                  | 2.1                                                 | Goals and Representations for Computation                          | 15 |  |  |

|                  | 2.2                                                 | Complexity of Analog Computation                                   | 16 |  |  |

|                  |                                                     | 2.2.1 Complexity for "continuous" Analog Signals                   | 17 |  |  |

| Co | onten                      | ts                                                                                | vii |

|----|----------------------------|-----------------------------------------------------------------------------------|-----|

|    | 2.3                        | The Importance of Precise and Accurate Computation                                | 19  |

|    |                            | 2.3.1 Feynman's Treatment of Accuracy and Precision in Physics                    | 21  |

|    |                            | 2.3.2 Accuracy and Precision as Goals                                             | 21  |

|    | 2.4                        | Summary                                                                           | 22  |

| 3  | $\mathbf{Re}_{\mathbf{I}}$ | presenting Numbers and Functions in Analog and Digital Computation                | 23  |

|    | 3.1                        | Representing Numbers in Digital Computation                                       | 24  |

|    | 3.2                        | Representing Numbers in Analog Computation                                        | 25  |

|    | 3.3                        | Representation of Functions in Analog and Digital Computation                     | 25  |

|    | 3.4                        | Solving Differential Equations more Precisely                                     | 27  |

|    | 3.5                        | Mapping Numbers and Functions to and from Analog Signals                          | 28  |

|    |                            | 3.5.1 Extracting Numbers from Signals                                             | 31  |

|    | 3.6                        | Summary: Finding Accuracy and Precision within Analog VLSI                        | 32  |

| 4  | $\mathbf{Pre}$             | cision from Analog VLSI, or, "knowing what you've got"                            | 33  |

|    | 4.1                        | Multi-wire Analog Signal Representations                                          | 34  |

|    |                            | 4.1.1 Signal Duplication                                                          | 34  |

|    |                            | 4.1.2 "Analog Bits" and Coordinate Charts                                         | 37  |

|    |                            | 4.1.3 Range Decomposition Block Implementation                                    | 40  |

|    |                            | 4.1.4 An Example Problem for the Multi-wire Signal Representations                | 43  |

|    | 4.2                        | Using Analog and Digital VLSI Together                                            | 47  |

|    | 4.3                        | Summary                                                                           | 49  |

| 5  | Acc                        | uracy from Analog VLSI, or, "getting what you want"                               | 50  |

|    | 5.1                        | Accuracy through Goal-based Design                                                | 50  |

|    | 5.2                        | Constrained Optimization Applied to the Parameter Setting Problem for Analog Cir- |     |

|    |                            | cuits                                                                             | 51  |

|    |                            |                                                                                   |     |

| C | onten                               | ts                                                                    | viii |

|---|-------------------------------------|-----------------------------------------------------------------------|------|

|   | 5.3                                 | Implementation                                                        | 52   |

|   | 5.4                                 | A Generic Physical Setup for Optimization                             | 53   |

|   | 5.5                                 | The Experiments                                                       | 53   |

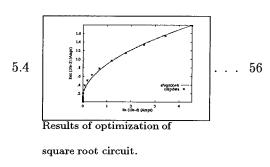

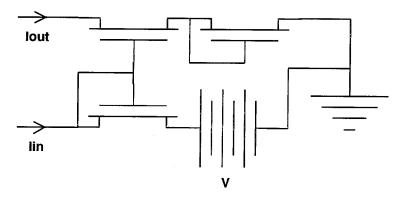

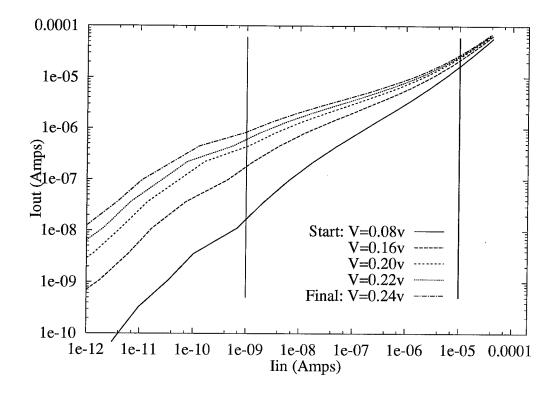

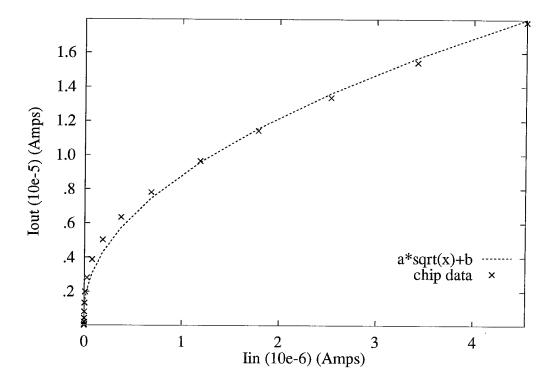

|   |                                     | 5.5.1 Square Root Experiment                                          | 54   |

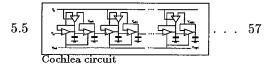

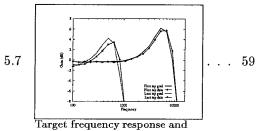

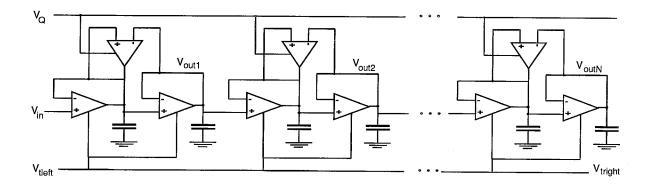

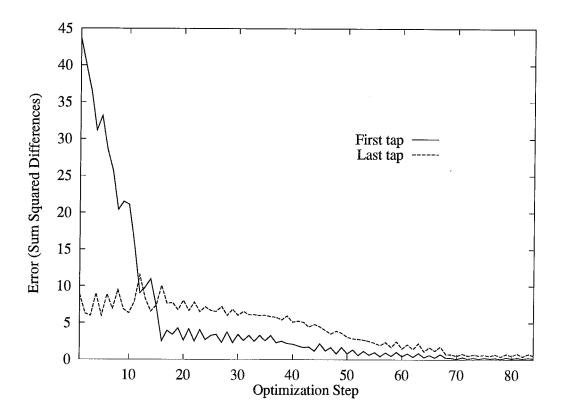

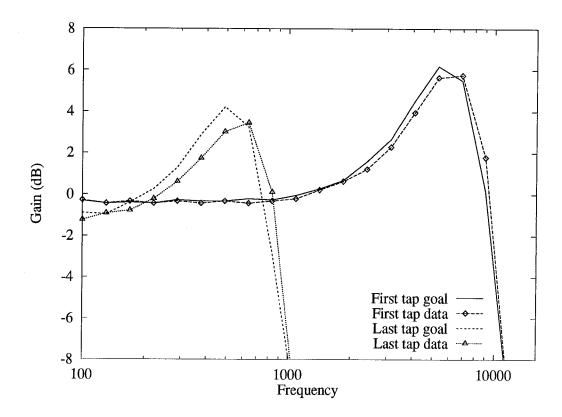

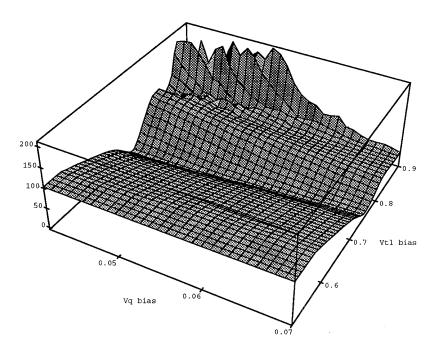

|   |                                     | 5.5.2 Analog VLSI Cochlea                                             | 56   |

|   | 5.6                                 | Choosing An Appropriate Optimization Method                           | 60   |

|   | 5.7                                 | Conclusions                                                           | 62   |

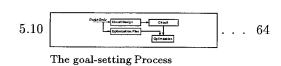

|   | 5.8                                 | The Goal-based Engineering Design Technique                           | 63   |

| 6 | $\mathbf{A}\mathbf{p}_{\mathbf{j}}$ | plying the Goal-based Design Methodology                              | 65   |

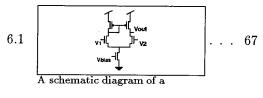

|   | 6.1                                 | Circuits with "knobs"                                                 | 66   |

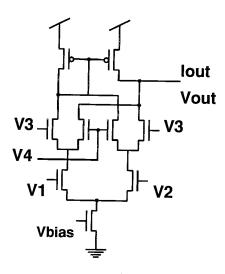

|   | 6.2                                 | Constructing a Compensated Amplifier                                  | 66   |

|   |                                     | 6.2.1 Equations of Operation                                          | 69   |

|   | 6.3                                 | Differential Multipliers                                              | 70   |

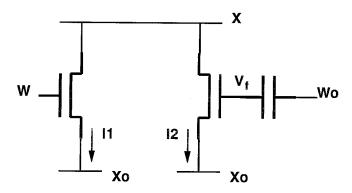

|   |                                     | 6.3.1 Two-transistor Multiplier                                       | 70   |

|   |                                     | 6.3.2 Four-transistor Multiplier                                      | 72   |

|   |                                     | 6.3.3 Gilbert Multiplier                                              | 73   |

|   | 6.4                                 | Constructing a Compensated Multiplier                                 | 73   |

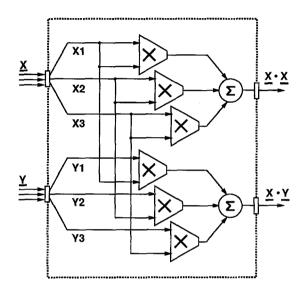

|   |                                     | 6.4.1 Constructing a Well-Behaved Inner-Product (dot product) Circuit | 78   |

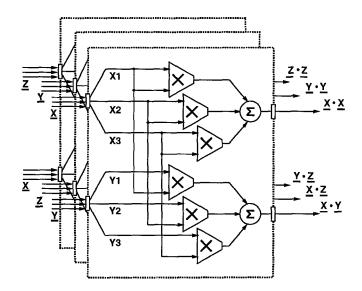

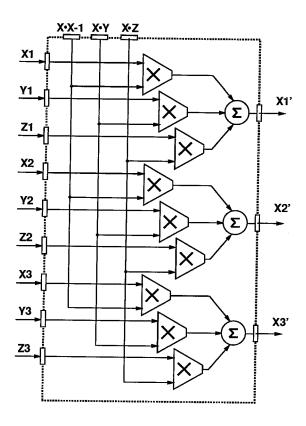

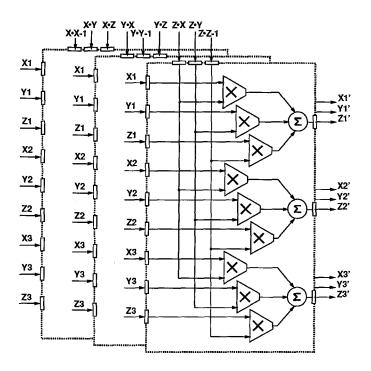

|   |                                     | 6.4.2 Constructing a Well-Behaved Matrix Multiply                     | 83   |

|   | 6.5                                 | Summary                                                               | 84   |

| 7 | Imp                                 | plementing Rotation Constraints in Analog VLSI                        | 85   |

|   | 7.1                                 | Analog VLSI for Constraint Satisfaction                               | 86   |

|   |                                     | 7.1.1 The Rotation Matrix Constraint                                  | 87   |

|   | 7.2                                 | The Constraint Algorithm                                              | 88   |

|   | 7.3                                 | Applying Analog VLSI to the Constraint Problem                        | 90   |

| C  | onteni                                                           | :s                                                               |     |  |  |

|----|------------------------------------------------------------------|------------------------------------------------------------------|-----|--|--|

|    | 7.4                                                              | Results                                                          | !   |  |  |

|    | 7.5                                                              | Summary                                                          | ,   |  |  |

| 8  | Toward On-chip Learning: Optimization, Adaptation, and Annealing |                                                                  |     |  |  |

|    | 8.1                                                              | Styles of Optimization                                           | 10  |  |  |

|    | 8.2                                                              | Analog VLSI Implementation of Multi-dimensional Gradient Descent | 10  |  |  |

|    | 8.3                                                              | The Gradient Estimation Technique                                | 10  |  |  |

|    | 8.4                                                              | Multi-dimensional Derivation                                     | 10  |  |  |

|    | 8.5                                                              | Elements of the Multi-dimensional Implementation                 | 10  |  |  |

|    | 8.6                                                              | Chip Results                                                     | 10  |  |  |

|    | 8.7                                                              | Summary                                                          | 10  |  |  |

| 9  | Con                                                              | nclusions                                                        | 11  |  |  |

|    | 9.1                                                              | Engineering Design Methodology for Analog VLSI                   | 11  |  |  |

|    | 9.2                                                              | Toward Harnessing Analog VLSI for Quantitative Computation       | 11  |  |  |

|    | 9.3                                                              | Future Work                                                      | 11  |  |  |

|    |                                                                  | 9.3.1 Design for Testability in Analog Circuits                  | 11  |  |  |

|    |                                                                  | 9.3.2 Automatic Configuration and Adaptation in Analog Circuits  | 11  |  |  |

|    |                                                                  | 9.3.3 Low-power Computer Graphics Subsystems                     | 11  |  |  |

|    |                                                                  | 9.3.4 On-chip Learning for Neural Networks                       | 11  |  |  |

| ΑĮ | pen                                                              | dices:                                                           |     |  |  |

| A  | Equ                                                              | ations of Operation of a Compensated Amplifier                   | 11  |  |  |

| В  | Equ                                                              | ations of Operation of Compensated Gilbert Multiplier            | 12  |  |  |

| C  | Des                                                              | cription of Operation of N-Dimensional Bump Circuit              | 12' |  |  |

| D  | Deri                                                             | ivation of Rotation Constraint Equations                         | 133 |  |  |

| Contents     | x   |

|--------------|-----|

| Glossary     | 137 |

| Bibliography | 140 |

#### Index of Figures

#### Ch. 1. Introduction

and source-drain I-V relationships.

### Ch. 2. Approaching Quantitative Computation in Analog VLSI

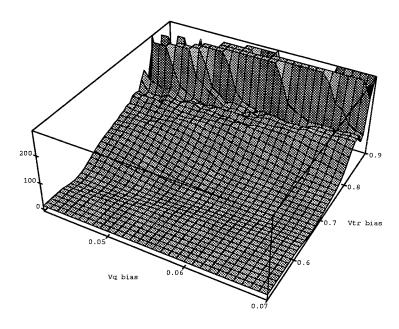

2.2 An example of a potentially accurate but imprecise measurement (Chip data for 1D

Gradient Estimate).

# Ch. 3. Representing Numbers and Functions in Analog and Digital Computation

### Ch. 4. Precision from Analog VLSI, or, "knowing what you've got"

Index of Figures

# 5.6 Error metric trajectories for

gradient descent on cochlea

#### Ch. 5. Accuracy from Analog VLSI,

or, "getting what you want"

response for optimization of square root circuit.

Trajectory of input-output

gradient descent optimized

data for cochlea

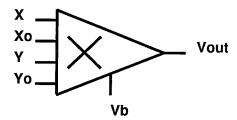

#### Ch. 6. Applying the Goal-based

#### Design Methodology

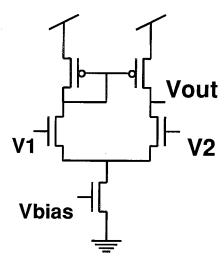

transconductance amplifier.

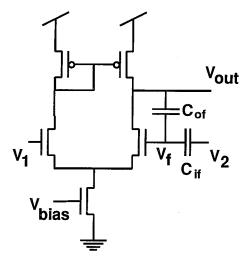

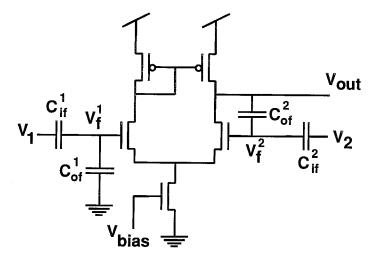

transconductance amplifier with a capacitive input divider for offset compensation.

transconductance amplifier

with two capacitive input

dividers for offset

compensation.

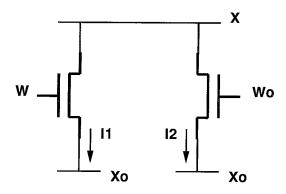

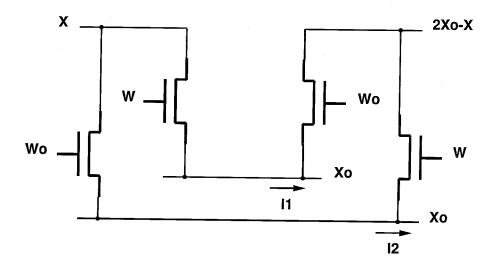

four-transistor multiplier.

Index of Figures

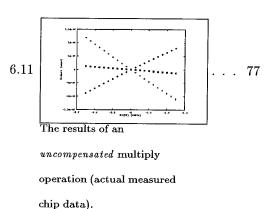

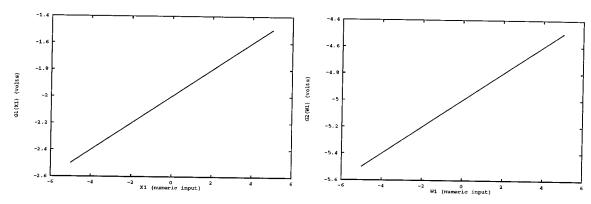

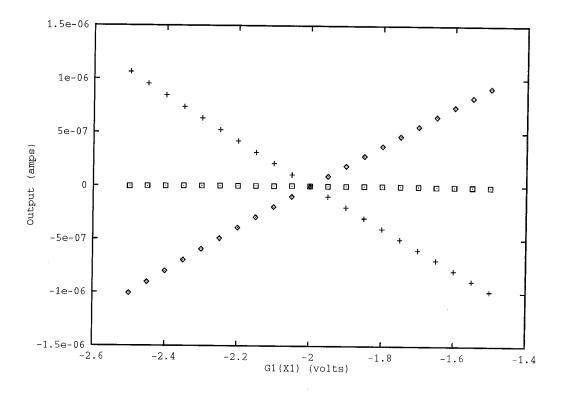

two transistor multiply circuit (actual measured chip data).

The input offset error is less than 1 mV (0.1% of the input range), and the maximum deviation from linearity

(relative error) is 2.2%.

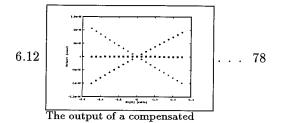

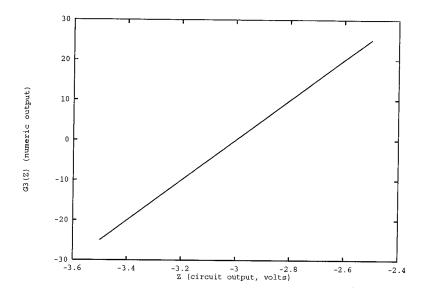

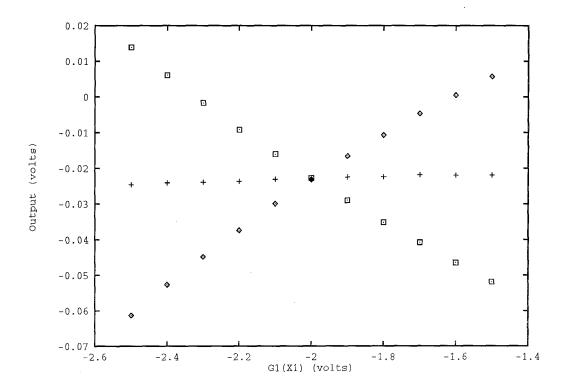

after nearly linear current-to-voltage conversion (actual measured chip data).

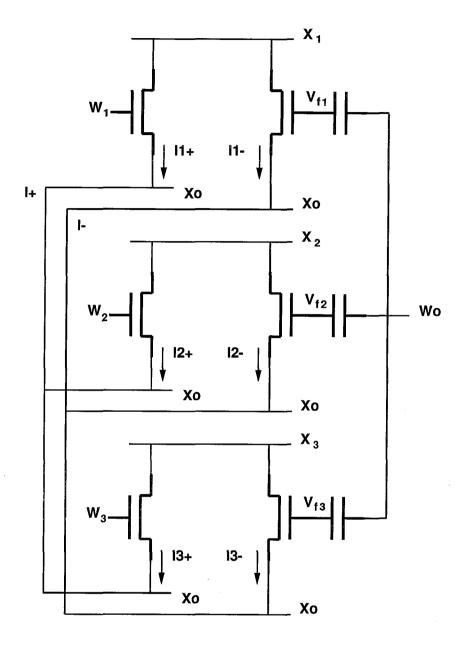

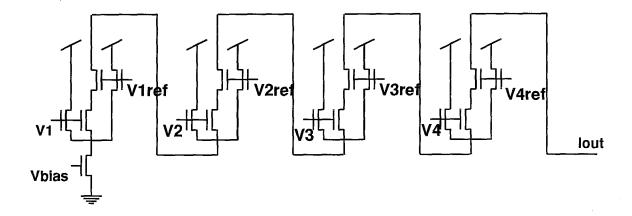

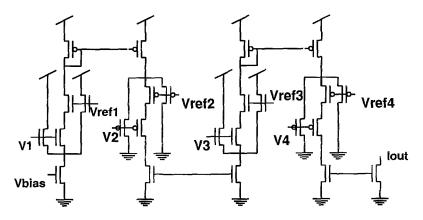

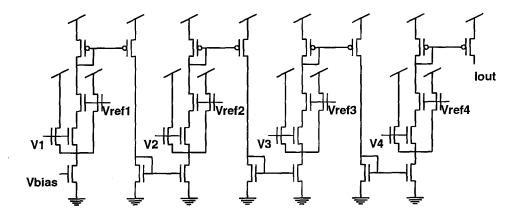

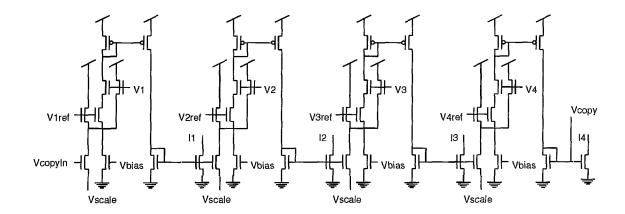

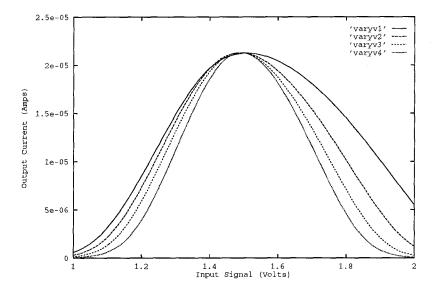

multipliers with floating gate compensation capability, connected to form a dot product calculation.

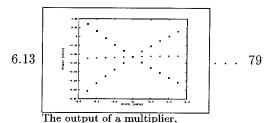

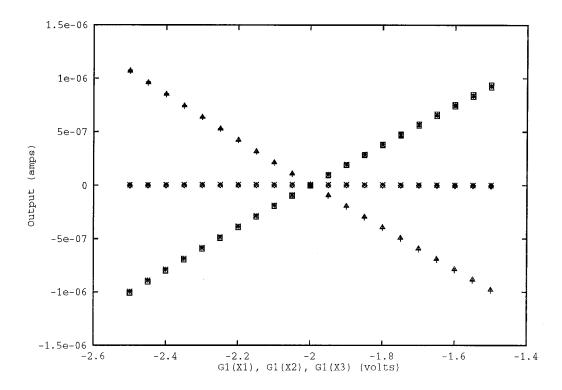

product (actual measured chip data). The characteristics of the three multiply operations are similar, with respect to the input offset magnitudes and shape of nonlinearities.

### Ch. 7. Implementing Rotation Constraints in Analog VLSI

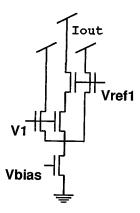

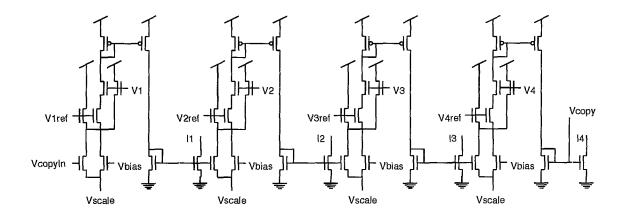

product blocks.

This computational element implements the rotation matrix constraint for one of the three

matrix column vectors.

blocks. The combination of these three constraint blocks and the three dot product blocks forms the gradient calculation hardware.

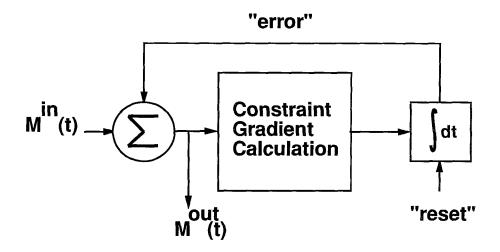

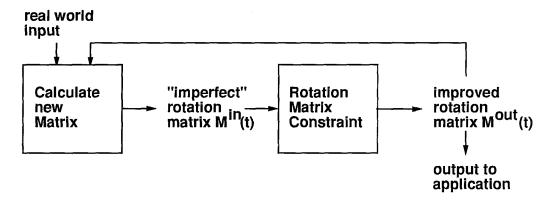

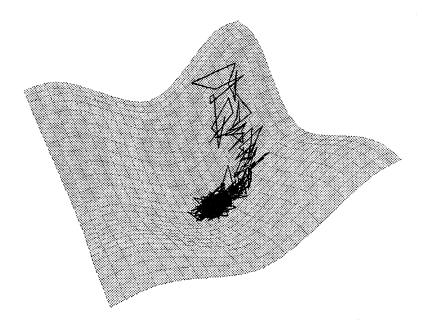

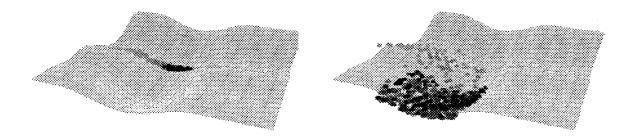

7.5. 95 An example of a gradient descent process, as employed to enforce the rotation matrix constraint.

7.6 95 A system-level view of the rotation matrix constraint enforcement, and how the result of applying the constraint might be used.

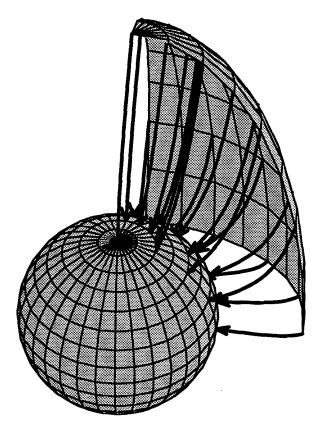

simulation of our constraint solution technique in action.

#### Ch. 8. Toward On-chip Learning: Optimization, Adaptation, and Annealing

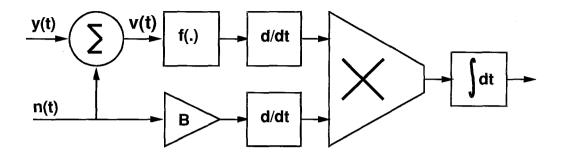

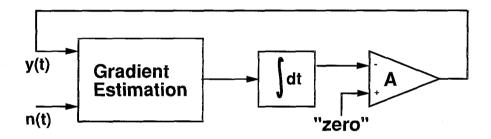

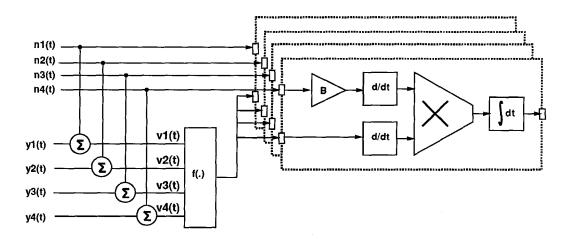

8.1 . . 104 Gradient estimation technique from [Anderson, Kerns 92]

8.2 . . . 104 Closing the loop: performing gradient descent using the gradient estimate.

Gradient Estimate.

Gradient Descent.

#### Ch. 9. Conclusions

### App. A. Equations of Operation of a Compensated Amplifier

# App. B. Equations of Operation of Compensated Gilbert Multiplier

Gradient Descent.

### App. C. Description of Operation of N-Dimensional Bump Circuit

App. D. Derivation of Rotation

Constraint Equations

(analog circuit simulation).

#### Chapter 1

#### Introduction

This thesis is a small step toward a long-term goal of producing a new type of hardware for computer graphics and neural networks. Chapters 1 and 2 describe the philosophical basis of our work, including a brief review of previous work. Chapters 3 and 4 describe numeric representation and thought experiments for circuit techniques to improve the precision of analog computation. Chapters 5, 6, and 8 describe research and experiments that we have done, including measurements from chips that we have built.

As a part of our discussion, it is important to describe the motivation for our work. In computer graphics, a need exists for faster calculations in many areas, including geometric modeling, rendering, physically-based modeling, constraint calculations, and virtual environments. Computation speed also limits the size and complexity of neural networks that can be built and simulated. There also exist applications in other areas of endeavor that require interaction with the real world in real time, such as speech recognition and synthesis, vision, robotics, and interactive input and display devices.

In each case, we need to compute values of mathematical functions, solutions to linear systems of equations, roots of nonlinear equations, solutions of differential equations, solutions to constrained minimization problems, and other large problems.

We also desire techniques and computational media that scale well for problems that are large in dimension or complexity. In order to effectively address these computational needs, we require quantitative computation at a high rate of speed. This thesis proposes techniques for improving the quantitative performance of analog VLSI sufficiently that we can consider using analog VLSI for some of the applications described above.

We present a world view for computation and simulation that includes goal-setting and satisfaction behavior as a key component. The goal-setting is part of a design methodology for making accurate and precise analog circuits. We present designs and test results for circuits which implement the goal-based design ideas. We also describe techniques for choosing parameters for these circuits, both externally and on-chip. Finally, we present some small systems which are built using these circuits and the techniques hierarchically. We also provide some zeroth-order analysis of the expected performance of the analog circuits as compared to a typical digital computer realization. In conclusion, we also discuss the expected significance of this work for future applications involving quantitative computation using analog VLSI.

#### 1.1 Why Use Analog VLSI?

Currently available digital hardware is simply not fast enough for the real-time tasks described above, and massive parallelism in digital computers has so far failed to deliver on its great promise in many contexts. Why is there any reason to believe that analog computation will be more fruitful? And, why should we consider analog VLSI? Part of the reason is that analog computation can be very fast: analog circuits can compute approximate solutions to differential equations, constraint problems, etc., very rapidly. Some problems are inherently analog, and their discretization is an

artifact of the dominance of digital computers. In addition, we would like to take advantage of some of the benefits of VLSI fabrication. For instance, integrated circuit technology scales well with problem size, in that large and complex circuits can be fabricated on a single chip. Also, VLSI design and fabrication techniques are developing rapidly. Analog VLSI can be a very efficient use of silicon and power, producing compact and low-power implementations.

There has been increasing interest recently in using analog VLSI [Mead 89] for a variety of computational tasks. Mead and others have pursued the paradigm of using individual analog transistors to model components of neural systems. One of Mead's insights is that rather than developing an entirely new manufacturing technology for producing analog VLSI chips, we can produce analog CMOS VLSI chips using standard digital CMOS VLSI processes. The key element in this strategy is to produce designs that are tolerant to the device variations that are present in a digital production process.

Much of Mead's work has been in an area where actual biological systems (esp. individual neurons, synapses, and networks of neurons) are used as metaphors for the design of analog circuits. The architecture of biological neural systems guides the construction of the analog VLSI circuits. Mead and others have pursued the paradigm of using individual analog transistors and small circuits to model components of neural systems. An important component of this work lies in the attempt to mimic the adaptation that real biological neurons are able to do. Modeling analog VLSI simulations of neural systems requires producing circuits that are intrinsically adaptive. Another component of this design philosophy is the exploration of architectures and circuits that are tolerant of device variations, and perform computations collectively.

Other research has focused on increasing the accuracy and precision of computation with analog VLSI, and on developing a design methodology for creating analog VLSI circuits which can

<sup>&</sup>lt;sup>1</sup>One view of the desirability of "intrinsically adaptive" circuits is that real biological neurons are inaccurate computational elements, and yet must adjust to real inputs. To produce a reasonable analog VLSI model of neurons' behavior, the circuits must be intrinsically adaptive as well.

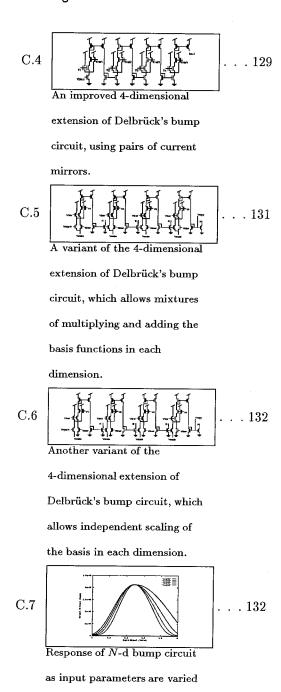

Figure 1.1: a) shows the drain current of a single transistor, as the gate voltage is varied from 0 to 5 volts. The family of curves represents varying the difference between the source and drain voltage. b) shows the drain current as the source-to-drain voltage difference is varied from 0 to 5 volts. The family of curves represents varying the gate voltage. The analog VLSI multipliers discussed in Chapter 6 operate in the nearly linear region to the right of a) and to the left of b).  $\Box$

be adjusted to perform to the desired accuracy [Kirk 91]. This work can be characterized as using adaptation and optimization to harness analog VLSI for more "conventional computing" applications. This approach is attractive because analog transistors provide a rich computational substrate. Figure 1.1a) shows the current flowing through an analog transistor as its gate voltage is varied. Figure 1.1b) shows the current as the source-to-drain voltage is varied, while holding the gate voltage constant. These figures are meant as a qualitative demonstration of the variety of current-voltage responses available from a single transistor. Note the regions of qualitatively different behavior, such as roughly linear, exponential, and quadratic I-V relation.

#### 1.1.1 Why Not Analog VLSI

Given all of these exciting features of analog computing, why don't we compute everything with analog circuits? And, furthermore, why not analog VLSI? With current technology, offsets and other variations in individual devices and circuit components can easily vary by 10-20%. So, if we are constructing our circuits from discrete analog components, we can hand-select them to minimize variations. This quickly becomes impractical for any large system, and we would like to have greater

integration, in terms of the number of components on a chip. If we construct our circuit in analog VLSI, however, we then cannot replace or rearrange the components within the chip.

Although there are, as described above, exciting regions of nearly linear and exponential behavior, analog devices are plagued by nonlinearity and nonlogarithmy. Analog chips are ultimately imperfect and difficult to control. We must also be prepared for noise in our circuits, as an artifact of a direct signal representation. Consequently, analog circuit design has a reputation as being "black magic."

The resulting effects are problems with accuracy and precision in analog computation.

#### 1.1.2 Our Approach: Kill the "Why-nots"

A reasonable approach to exploiting a technology with advantages and drawbacks is to try to use the good parts and avoid the bad. We propose to devise circuits and techniques to improve accuracy and precision in analog VLSI. We then proceed to develop these techniques into a design methodology. This design methodology is then used to construct some example applications.

## 1.2 Describing the Physical World with Mathematical Models and Goals

The research described in this thesis is motivated by a goal-based view of modeling and simulation. A model can be posed in terms of a goal or set of goals, and the purpose of a simulation can be to meet some goal or set of goals. Goal-setting and goal satisfaction are reasonable and desirable ways to achieve success in parts of a simulation.

We can create a goal-based model for an analog chip's behavior, and we can use this model to control the analog VLSI chip and improve the accuracy and precision of the chip's performance. So, goal-based modeling operates at several levels, both within our simulation of the chip's behavior and within the actual circuits.

We wish to use analog VLSI to implement approximations to mathematical models, since we

believe that the physical world can be described by a set of mathematical models, often including differential equations. Accordingly, we proceed by choosing some portion of the physical world to model, and formulating a set of equations to model it.

We subscribe to a structured modeling approach described in [Barzel 92]. We choose some portion of the world to model, and decide which aspects of that portion of the world are of interest. We then formulate equations which describe the behavior of the portion of interest.

We then solve the equations (techniques discussed in Sec. 1.4 and Sec. 1.3), often in the context of a simulation of the model. We evaluate the results in terms of accordance with model intent: did the simulation provide the desired information? We may then potentially reformulate the model, to redo the simulation in order to learn more. Our *explicit goals* for the simulation help us to evaluate our results.

The equations which we have formulated to describe the physical world may be used as the basis for a computational simulation. Parameters of the simulation may be derived from the scope of the region of interest of the physical world. The simulation goals are derived from the model equations.

We wish to choose a solution technique that has the potential to meet the stated goals, and choose a computational substrate on which to implement the chosen solution technique. One way to solve the equations for our simulation is using analog computation. In theory, analog computation is ideal, because analog circuits are excellent substrate for solving ODE's - the normal operation of an analog circuit continuously solves ODE's! Part of the challenge is to construct a circuit that solves the ODE's that we wish to solve. This idea will be developed further in Sec. 1.4.

We prefer to approach the simulation using "direct" methods. A direct method is one which guarantees solution of the problem, by solving the problem explicitly, rather than implicitly. A direct method implies that there is a high probability that satisfying the goal will produce a solution to the problem:

(1.1) satisfaction of direct method goal  $\equiv$  solution to problem

An important part of the use of direct methods is to understand the problem that you are trying to solve, and formulate goals that are guaranteed to solve that problem. We would like to contrast this approach with an alternate approach involving the use of indirect methods.<sup>2</sup>

We encourage the use of direct methods in modeling and simulation, to guarantee that the actual goals will be met. The explicit choice of goals is an exercise that has many benefits over tacit choice of goals. Using this approach to guide the design of a model increases the chances that the model will provide the desired effects. We attempt to use this approach in the work presented in this thesis, choosing goals which guarantee success; the goals are identical to our objectives in creating the model. We wish to avoid tacit or implied goals.

#### 1.3 Advantages and Disadvantages of Simulation using Digital

#### Computers

One method which can be used to effect a simulation of the model equations is to solve the equations on a digital computer. For the case of differential equations, solution implies integration though time. A number of software packages or libraries provide this capability in some form. We can also use general purpose tools, rather than special one-time-use programs, and it is convenient to pursue the simulation in this way.

This approach has a number of advantages, as well as some disadvantages. One of the greatest advantages of digital simulation is that by and large, digital computation is a proven technology. Digital computers have been manufactured for a number of years. They work. In fact, they work

Alternatively, we could state the goal as "we wish to mop the floor," (confusing the goal with a method for pursuing the goal), or "we wish the floor to be wet," (confusing the goal with one of the likely consequences of the satisfaction of the goal). Satisfaction of one of these stated goals does not guarantee that the actual goal will be satisfied.

<sup>&</sup>lt;sup>2</sup>Let us assume that we wish the floor to be clean. If we have stated the goal explicitly and directly as "we wish the floor to be clean," then it is easy to see that satisfaction of the stated goal will actually result in satisfaction of the true goal.

repeatably and (often) identically. They have routinely been used to design chips, simulate circuits, even write dissertations.

Another important advantage of performing simulations using digital computers is that simulations will automatically get faster over time. How can this be so? As long as some care has been taken to write a portable program, the simulation can be run on almost any (uniprocessor) digital computer. Over time, it has been seen that the performance of digital computers increases by roughly constant factors per year. This geometric increase in simulation performance is available without any algorithmic or modeling expense. With additional effort, the program can be run on a multiprocessor computer system, and there is the potential for nearly N-fold speedup, where N is the number of processors. In practice, for many types of problems, the N-fold speedup is not achieved, however, and is often not very closely approached.

Even with all of the advantages described above, digital simulation of the model equations can still be painfully slow, particularly in the case of integrating differential equations. The main reason for this is that the differential equations are meant to describe a continuous process which is being approximated by a sequence of discrete steps, since digital computers do not operate in continuous time.

We may often spend lots of time and lots of work for simple things. An example of this is seen in attempts to solve stiff differential equations. We also have only coarse control of error tolerances, specified over the range of a problem, whereas we may be much more concerned with details of one particular part of the simulation. The overall lack of speed in digital computing may cause unwanted approximations in the model or the accidental neglect of important details.

Another potential problem with digital computation is quantization errors. Digital representation is inexact, in the form of discrete bits. The floating point representation of numbers makes the errors worse since the absolute precision varies with the size of the signal. We can use fixed point fractional arithmetic, but the range of our representation is then limited. In either case, sequences of digital arithmetic operations must be re-quantized at each step. The process of repeated quantization

causes roundoff errors to accumulate throughout the process of the computation. This accumulation can cause instability when roundoff occurs at a critical point in computation. Integration over time accumulates roundoff errors, and differentiation may cause errors, too (particularly, a small difference between large numbers).

#### 1.4 Advantage and Disadvantages of Simulation using Analog

#### Computation

Another alternative for a computational medium for simulation is to use adaptive analog VLSI. As discussed in earlier sections, analog VLSI has many potential benefits, including speed, scale and efficiency of integration, and low power. Using analog VLSI, we can directly simulate more details of our model by designing those details into our circuits. The potential drawbacks are limited accuracy and precision, and problems with repeatability of our computation.

We can compare a very large computation, such as a climate simulation on a Cray supercomputer to an analog implementation. The digital simulation may be solved using finite elements, discrete time steps, and must forego consideration of many details to scale the problem down to a manageable size. Using an analog circuit to directly model parameters and simulate in continuous time may produce a result that is both qualitatively and quantitatively different. Which approach is better? It's hard to say. Analog VLSI is similar in some ways to old analog computers, and so a consideration of their strengths and weaknesses may be helpful.

There is a long history of analog computing. Engineers and scientists solved many problems in the 1940s and 50s with analog computers. Most analog computers (ACs) were special purpose, built to solve one problem only, although some were configurable general purpose machines. The configuration process was physical, though, requiring connections and components to be changed by hand. ACs were expensive, physically large, and generally unreliable.

In addition, just as when using analog VLSI today, accuracy was a problem for ACs. Some of the

same reasons apply; individual components' variation from nominal values, nonlinearities, and non-ideal behavior prevented significant quantitative computation. Analog computers often produced results that varied with the physical environment: temperature changes affected the computation results. Subsequently, analog computers were devoured by digital computers in the marketplace. Reasons for the decline of analog computing included analog computers' large size, expense, low reliability, and limited accuracy and precision. The old analog computers could mostly be used for qualitative computation.

Analog VLSI, implemented in a state-of-the-art CMOS technology, can compute many functions quite rapidly, although approximately. Due to the levels of integration that are possible today, we can produce compact, low power implementations in analog VLSI. In addition to the analogy to historical analog computers, there are some key differences. It is difficult to build a good inductor using analog VLSI, and so we must operate with only resistances, capacitances, and transistors. Even large resistances are difficult to produce in a standard CMOS VLSI process.

As stated earlier, some of the main drawbacks of analog VLSI are the problems of accuracy and precision. We must accept statistical variations of device parameters, which produce "non-ideal" devices (non-linear, non-exponential, or non-whatever-we-wanted). Since we are using representations where the absolute level of a signal contains the information, we are susceptible to contamination by noise, and must be concerned about precision and repeatability of computations. Adaptive circuits can help to solve some of these problems, and we will discuss this further in the following sections.

Due to the problems with accuracy and precision at the scale of individual components, it can be very difficult to design and produce a useful large-scale analog system. It is very hard to design a large deterministic system with nondeterministic components. How can one solve this conundrum? One potential solution might be to construct our circuit using only ideal devices. Unfortunately, with currently available VLSI fabrication processes, this is not reasonable to consider. We can, however, make better devices by using some well-known design techniques. An example of such a technique is common-centroid layout, which can be used to reduce the effects of production variations such

as dopant concentration gradients or oxide thickness. [Allen 87] and [Millman 79] describe circuit and layout techniques to reduce the effects of some common production variations.

Even with clever layout tricks, we still need a reliable way to control analog circuits containing only a few components, so we can use them consistently in larger circuits. We also would like to control larger scale circuits, to have them perform according to our desires. We propose to use various automatic optimization techniques to compensate for undesirable device and circuit behaviors.

#### 1.5 Using Goals for Analog VLSI Computation

We propose to use goal-based (teleological) modeling to control analog circuits and cause them to meet our expectations for circuit performance. Our goals for analog circuits will typically be a computation that we would like to perform accurately, with a specified level of precision. We first define goals for the desired circuit behavior. We then propose an analog circuit to perform the desired task. Through analog circuit simulation, we can verify that the circuit can perform the task, at least in an approximate fashion.

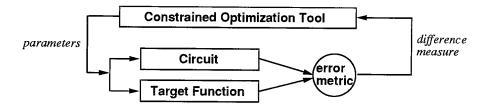

We can then use goals to guide a constrained optimization process to make the circuit perform our desired task as well as possible, given the actual devices. The optimization process is a way of controlling the accuracy of an analog circuit. This technique will be discussed in more detail in Ch. 5.

A model is provided for the proper behavior of each circuit or circuit element. The provided model is the goal which we desire that the actual component will meet. We require:

- circuit components (nonideal)

- a means of controlling or adjusting the circuits

- goal-directed criteria for making adjustments

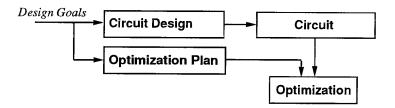

The design process becomes the combination of designing a circuit and devising explicit goals for

1.6 Thesis Roadmap

how it should behave. We have the expectation that we can use the goals to guide the adjustment of the circuit subsequent to its fabrication. By making explicit demands on circuit performance, we have a metric by which we can measure our satisfaction with the circuit realization in silicon. Consequently, we have a concrete measure of error, based on the extent of goal satisfaction. We can therefore improve the quality of quantitative computation using analog VLSI.

In order to make the goal-based design process tenable, we need to be flexible in our definition of goals, to allow the meeting of our goals and the actual capabilities of our circuits. We will therefore attempt whenever possible to define goals in terms of circuit signals. We can interpret results in terms of a model for whatever we desire to compute.

The process of goal-based modeling can be applied hierarchically. Individual circuit components can be compensated using a set of goals and circuitry for compensation. These compensated components can then be composed into a larger circuit, which can be again adjusted to perform such that it meets some larger-scale goals. The satisfaction of the various levels of goals can occur simultaneously, or as a sequential hierarchical process.

These goal-based techniques facilitate modular circuit and system design strategies for analog VLSI similar to commonly used techniques for design of digital VLSI systems. Realistically, it's more complex than that, since even compensated analog components are still imperfect. This work is, however, the first step on the path towards the goal of being able to reliably design and produce analog circuits to perform complex computations.

#### 1.6 Thesis Roadmap

Ch. 2 discusses accuracy and precision, the difference between them, and why this is important to analog computation. We also discuss some issues of complexity in simulation, particularly using analog computing. Ch. 3 discusses how we represent numbers and functions as analog signals, and also how we extract numbers (answers) from analog signals.

1.6 Thesis Roadmap

Ch. 4 describes several circuit building approaches for increasing the precision of analog computation. Ch. 5 describes techniques for using constrained optimization to increase the accuracy of analog computation. We also introduce the goal-based design methodology in Ch. 5. In Ch. 6, we use the goal-based design methodology to construct some compensatable components (specifically, a family of multipliers). We also describe the hierarchical compensation process used to combine three compensated multipliers to compute a dot product. In Ch. 7, we use the components developed in Ch. 6 to construct a small system. The system is a collection of circuits that use gradient descent to solve a system of constraint equations which orthonormalize an approximate rotation matrix.

In Ch. 8, we describe some key differences between continuous and discrete optimization strategies. We present an implementation of circuits that perform on-chip continuous multi-dimensional optimization through gradient estimation, descent, and annealing.

Ch. 9 discusses the contributions of this thesis as a whole, and identifies future areas of potentially productive work that may proceed from this thesis.

#### Chapter 2

#### Approaching Quantitative

#### Computation in Analog VLSI

The intent of this chapter is to describe one way to think about computation, and why we believe it to be appropriate for some types of quantitative analog computation for computer graphics and neural networks. We also discuss accuracy and precision and how these qualities guide our thinking about computation with analog VLSI. Although there are numerous ways to think about computation, we focus on those that have been useful in developing the strategies described in this thesis.

Discrete information theory and complexity of discrete computation has long been used to assist in algorithm development for digital computers. Given the current level of interest in analog computation in general and analog VLSI in particular, there is a surprising dearth of research results in the area of analog information and complexity theory. The field of analog information theory is

fragmented, and has yet to produce any truly strong results. We wish to explore analog information theory and continuous complexity to guide us in our work designing analog circuits.

A rigorous treatment of analog information theory is beyond the scope of this thesis, but we feel that we must briefly describe the landscape of existing work in this area. To motivate our discussion of analog complexity, we discuss a few results in that area, and draw some of our own conclusions. We begin by describing what we are hoping to achieve, and the process by which we go about it.

#### 2.1 Goals and Representations for Computation

An appropriate first step in performing any computation is the choice of goals. The main question that we are asking is: What to compute? We must first explicitly decide what it is that we wish to compute, before we can begin to make other decisions about the computation, let alone perform the actual computation itself.

Many researchers have determined that integrating goal-setting behavior into the design process has many benefits [Ullman 92]. We encourage this approach, and desire to make the choice of goals explicit, not tacit. Explicit and detailed enumeration of design goals is a powerful tool for producing successful projects. We don't mean to imply that most designers create products without having goals beforehand. We simply wish to emphasize that there is great value in making the goal-setting process as explicit and detailed as possible. The more detailed and well-defined the goals are, the better we are able to evaluate our results.

It is helpful to explicitly record goals at the initiation of a project and update them as the project evolves and the goals change. Explicit goals help to provide a yardstick for the success of the project, and to keep the project on-track. Goal-setting is an intrinsic part of our design approach, so it is forced to be explicit, and that is not a bad thing. The existence of explicit goals makes it clear to us where we are succeeding, and where we are failing in our objectives.

The goals determine what the end product of the computation will be. Making an explicit goal

for a computation is like making a business plan for a corporation. The goals and plans determine the path to be taken. The goal-setting process forces the details to be worked out in advance.

After the goals have been chosen, one must choose a representation or framework in which to express the goals, and organize the computation. We must also be concerned about being able to measure the satisfaction of the goals within the chosen representation. And, we must be concerned about our ability to pose the problem accurately within the chosen representation. It is also important that the representation permit efficient computation toward the goals, unless we have infinite resources.

Thus, the complexity of the computation is also an important issue, both in terms of the innate complexity of the problem as well as the complexity of computation on the chosen substrate, within the chosen representation for the problem.

#### 2.2 Complexity of Analog Computation

Although we will not present any new results in complexity theory, we believe that a brief review of some existing work will set the stage for our discussion of analog computation. We hope to see future research address the problem of developing a better measure of information in analog signals. It would then be possible to develop a measure of complexity based on that definition of information. Such a measure of analog complexity would be very useful in comparing the potential benefits of analog computation as opposed to digital computation. In the absence of such criteria, we will make a preliminary comparison of the computations of some analog circuits with their digital counterparts. We will make use of some work in the area of discrete information theory and complexity to help us to think about analog complexity.

Discrete information theory deals with ideal mathematical models, and not real physical sources and real physical channels. Nonetheless, the theory is useful in that it provides a framework within which to consider more detailed models of real systems. The theory also helps to give us a feel for the type of cost/performance tradeoffs that are involved in real computation problems. As an example, mutual information, as defined in [Gallager 68], serves to provide us with a measure of how much the occurrence of a particular event tells us about the probability of occurrence of some other event. Mutual information thus provides us with a tool to assist us in predicting the probable behavior of a system, given partial knowledge. We can use information theoretic tools to build an understanding of space-time and other resource tradeoffs to be made in computation. We are particularly interested in tradeoffs between accuracy, precision, and resources such as time and circuit size (silicon area).

Traub's Information-Based Complexity (IBC) studies the computational complexity of infinite dimensional problems [Traub 88]. Such problems arise in continuous mathematical models as are often used in engineering, particularly when integration, optimization, and/or differentiation are involved. Since digital computers can represent only a finite set of numbers, then many continuous inputs and outputs can only be approximated. The input is often contaminated by the discretization, so the original continuous mathematical problem may be only approximately solved.

IBC considers the tradeoff between the cost and the quality of the approximation. If we consider analog computation to be continuous in nature, then IBC has some relevance. For the simulation of continuous models, analog computation may be more suitable for obtaining an acceptable approximation with a small cost.

#### 2.2.1 Complexity for "continuous" Analog Signals

For continuous signals, a measure of information content and complexity should be affected by the overall "size" of the signal. A truly continuous mathematical signal has effectively infinite bandwidth, and therefore by some measures it has infinite information capacity. It may be possible to develop an information theory for infinite capacity channels, but it is not directly useful for analog computation. Any physically realizable signal has a finite bandwidth and therefore finite information capacity.

For a real physical circuit, there is a limited information processing capacity. Each signal is composed of a finite number of electrons. Therefore, we can apply discrete information theory to analog signals using electrons as an ensemble. We believe that this may be an important direction for future research. At the high end of the bandwidth, there is a limit due to the slew rate limits of the circuit. At the low end of the bandwidth, there is a limit due to the number of electrons and the consequent number of transitions that can occur.

Although we have stated that there is a dearth of work in the area of analog complexity theory, there is some work. Vergis et al [Vergis 86] discusses the complexity of mechanical analog computation for a very restricted class of problems. Their analysis explicitly rules out quantum mechanics, other probabilistic behavior, and nonlinear devices as not applicable to their analysis. By eliminating nonlinearities, Vergis explicitly excludes those things that we are most interested in exploiting.

Vergis proves for this restricted class of devices that analog computers cannot solve NP-complete problems using less than polynomial resources, where resources include time, space, and material. Vergis describes problems that are "easy" to solve using digital computers, but are inherently difficult for analog computers. We assert that there exist problems, especially those of a continuous nature, for which the converse is true.

An example of such a problem is the classical physical N-body problem, with gravitational or electrical forces. The naive algorithm for solving for the interaction forces has a computational complexity of  $N^2$ , where N is the number of bodies. An improved, hierarchical algorithm has a complexity of order  $N \log N$ , due to the properties of the spatial hierarchy. An approximate solution can be obtained in linear time [Greengard 88]. A mechanical analog computer can calculate the exact solution in real (linear) time. The exact mechanical analog computer that we would choose is the actual N body mechanical system! From this example, we can draw the following conclusion: for simulation of continuous mathematical models, there may be special advantages for analog computation. The N-body problem, when analyzed in these terms, also brings up an interesting related question. For a circuit or system that operates in continuous time, what does it mean to require polynomial resources? Can we consider time to be infinitely divisible? In this

thesis, we won't attempt to answer any of these questions, but they give some insight as to why the analysis of analog complexity is hard.

#### 2.3 The Importance of Precise and Accurate Computation

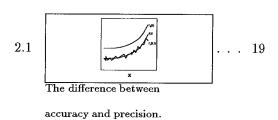

Although we might prefer exact computation, we must usually settle for an approximation. Given that we accept approximate computation, there are two important issues that should concern us: accuracy and precision. These concepts describe the quality of the approximation. We describe accuracy and precision first in terms of definitions, and then in terms of computation and simulation. Figure 2.1 provides one view of the difference between accuracy and precision.

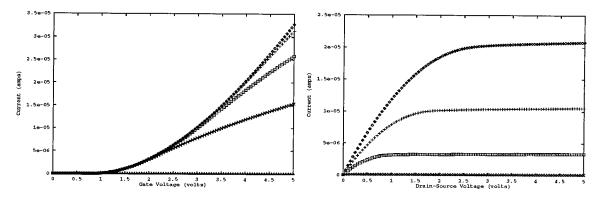

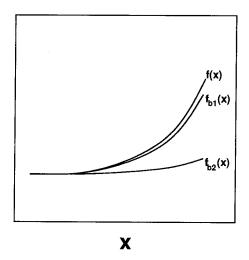

Figure 2.1: The difference between accuracy and precision. The curve f(x) is approximated by the curves  $f_1(x,t)$  and  $f_2(x)$ . Although  $f_1(x,t)$  is more accurate than  $f_2(x)$ , as an approximation to f(x), it may be that  $f_2(x)$  is more precise.  $\Box$

In Fig. 2.1, the function that we wish to represent is f(x). One representation,  $f_2(x)$ , repeatably produces identical values with successive measurements. Although the function  $f_2(x)$  is very precise (perhaps infinitely so), it does not accurately represent f(x). In Fig. 2.1,  $f_1(x,t)$  does not repeatably produce the identical response with successive measurements.  $f_1(x,t)$  represents the function f(x) plus some additive noise contribution:

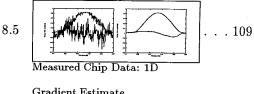

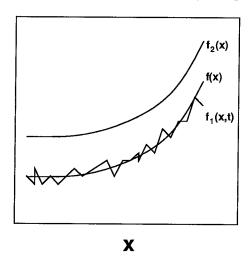

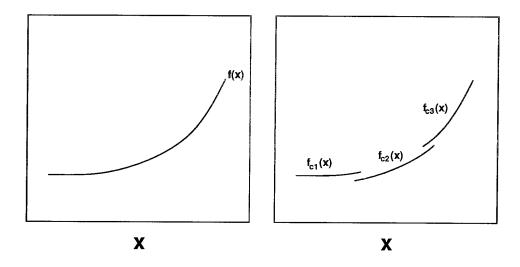

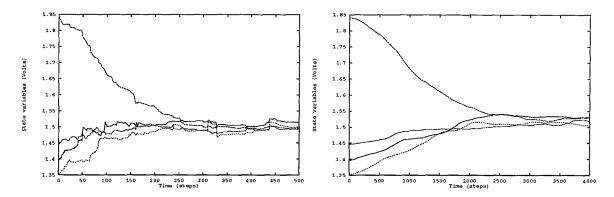

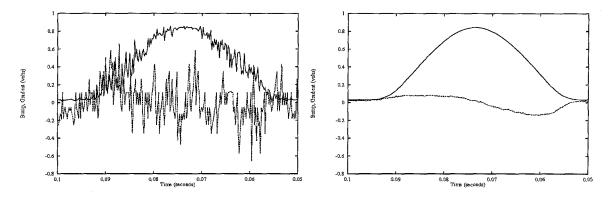

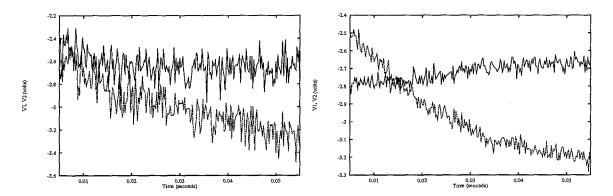

Figure 2.2: An example of a potentially accurate but imprecise measurement (Chip data for 1D Gradient Estimate). The curves above are data measured from the gradient estimation chip described in Ch. 8. (left) raw data, and (right) average of 1024 runs. Although the curves on the left are an imprecise representation of a bump function and its gradient, we see from the averaged curves on the right that the representation is moderately accurate: we can see the bump function and its qualitative gradient estimate.

(2.1)

$$f_1(x,t) = f(x) + \alpha n(t).$$

The function  $f_1(x,t)$  is a more accurate representation of f(x) than is  $f_2(x)$ , but  $f_1(x,t)$  is less precise. Averaging together successive measurements could improve the precision of  $f_1(x,t)$ , and we will discuss this technique in Ch. 4.

Fig. 2.2 shows some data measured from a chip that we built which is described in Ch. 8. The data is presented here as an example of a measurement that is somewhat accurate, but very imprecise.

Precision can be defined as "the degree of agreement of repeated measurements of a quantity" and, as such, is a quantification of how much useful information is present in a measurement. A commonsense definition for precision is "knowing what you've got, to some degree of exactness." Precision is based on a determination of how much useful information you have.

Accuracy can be defined as "the degree of conformity to some recognized standard value" and, as such, is a quantification of how closely a measurement agrees with our expectations. A commonsense

definition for accuracy is "getting what you want." Accuracy is based on some concept of what result you should get.

As a practical matter, accuracy is often expressed as a binary judgement: either a representation or computation is accurate, or not. Precision is measured and discussed in many different ways, however. One way of measuring precision is as a ratio of the smallest representable signal to the largest representable signal. We could also be more concerned about the repeatability of measurements, and therefore express precision as the size of the noise floor, or its ratio to our signal range. Finally, in discrete computations, we might choose to think of precision in terms of the smallest amount by which we can reliably increment a signal, and still perceive the altered signal as different. Each of these ways of considering precision is appropriate for different ways of thinking about computation. When we are discussing precision in the remainder of this thesis, we will be careful to describe which definition we are using.

### 2.3.1 Feynman's Treatment of Accuracy and Precision in Physics

Feynman [Feynman 82] discusses some of the problems associated with simulation of physics using computers. Using a general model of discrete (digital) computation, Feynman describes the simulation of "discrete" physics, a fiction created for the purposes of the discussion. He also describes some simulation problems that are ill-suited to be solved using discrete computation. Among these problems are those that are continuous in nature and defy discretization. Specific examples are probability based problems which suffer irrecoverable loss of precision in the discretization, and thus do not accurately reflect the original model. Quantum mechanical simulation on digital computers can also lead to paradoxical and contradictory solutions.

#### 2.3.2 Accuracy and Precision as Goals

Accuracy and precision are not important to us as goals unto themselves. Accuracy and precision are important to us inasmuch as they help us to satisfy the broader goals of our computation; i.e., to

2.4 Summary 22

ensure that our simulation reflects what we are attempting to model. This is primarily an issue of accuracy, with precision a subordinate goal. We are more concerned, in general, that our simulation retain the desired character of the thing being modeled, than the precision of the result. However, given that the model is accurate, we also desire as much precision as is practical, so that we may know as much about the model as we are able.

We will pose goals for the accuracy of our computations, and will meet them with the precision with which we are able to measure the satisfaction of the goals. Thus, the precision is largely a side-effect. In addition, we can choose a representation for our signals in which the precision is maximized in the region of the goals. Issues of signal representation are discussed in more detail in Ch. 3.

# 2.4 Summary

We have presented a cursory overview of some important ideas in information theory and complexity.

We have also provided a few examples of work toward extending these ideas to analog complexity,

and a glimpse of the difficulties involved.

The nature of physical computation involves compromises and approximations, and we can consider these approximations in terms of accuracy and precision of the computation. In this chapter, we have provided definitions for accuracy and precision, and examples of the application of those concepts. In the next chapter, we will discuss the representation of numbers and functions in both analog and digital computers. In Ch. 4, we will discuss techniques for increasing the precision of analog computation. We will consider accuracy in more detail in Ch. 5.

# Chapter 3

# Representing Numbers and Functions in Analog and Digital Computation

This chapter discusses some ways to think about how numbers and functions can be represented and used, both in digital and analog computing. We first briefly mention features of representing numbers in digital computing, and then describe how analog representations may differ. We also discuss techniques for mapping mathematical numbers and functions into analog circuit quantities for the purpose of analog computing. Finally, we describe how to extract information from an analog computation, in order to return to the mathematical world to interpret our results.

# 3.1 Representing Numbers in Digital Computation

In digital computation, we can build precision progressively by assembling hierarchies of bits. The first, lower-order bit represents a quantity half of the size of the next higher bit. By stringing together a sequence of N bits, we can represent  $2^N$  unique numbers. There may be an implied (tacit) offset and scale factor involved in the interpretation of the bits.

For integers, the tacit scale factor is one. We may also assume or provide some other scale factor, to represent numbers over some range. The combination of bits then provides some amount of precision within that range. The key feature of the approach of stringing together bits is that each additional bit divides the size of the uncertainty in half.

We may also attempt to use strings of bits to represent real numbers in a digital computer. One problem with this attempt is that the real numbers are infinite, while the string of bits represents only a finite subset. We must choose some way to map the real numbers onto the subset that we can represent with our bit string. One mapping that is commonly used is floating point. In addition to the original string of bits, there may be an explicit scale factor.

The scale factor enables us to represent numbers at various scales. One drawback of this representation is that the absolute precision varies with different scale factors. This difference in absolute precision can cause problems in computation. For real numbers, we can think in terms of using operators such as +,-,\*,/, etc. We must approximate these operations as applied to our discrete representation of numbers for digital computation.

We now turn to examining the problems involved in representing numbers in analog, and compare and contrast with digital representations.

# 3.2 Representing Numbers in Analog Computation

We'll avoid attempting to represent integers exactly using analog signals and proceed to consider the representation of the real numbers. A number, as represented in analog, may be a voltage, a current, or some other electrical quantity.

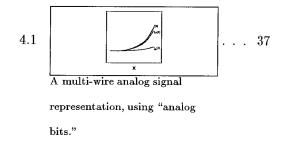

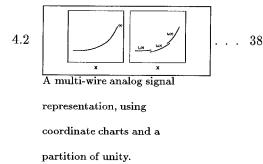

We mostly consider a direct representation of a number as a single physical quantity, rather than as an aggregate as in the use of a string of digital bits, although we describe a thought experiment using "analog bits" in Sec. 4.1.2. Ch. 4 discusses signal mappings which preserve precision, and considers multi-wire, multi-signal mappings.

Unlike the rigid nature of bits, analog signals may assume any value in some range, to the precision permitted by the size of the charge on an electron, or other physical parameters. Rather than choosing a one or zero (on/off) as in a digital representation, we are interested in the value. Unlike digital, it is difficult to error-correct an analog signal, or provide a "restoring force" to protect the integrity of the signal, since it is exactly the tenuous level of the signal that interests us. We are therefore much more susceptible to measurement errors, noise, and other distortions of the signal. We must also be concerned about the repeatability of the measurements. Any time-varying noise that is introduced into the computation or the measurement affects our precision. So, instead of arbitrary, but fixed, discretizations (digital), we are faced with arbitrary and variable errors (analog).

# 3.3 Representation of Functions in Analog and Digital Computation

Functions can be thought of as "numbers that change over time," or that change as some other parameter changes. For functions, we can think in terms of operators and functions such as y' = f(y), g(y), etc. In digital computation, functions are subject to the discretization of the numeric representation (floating point, for example). Digital implementations of functions are also subject to the discretization and errors caused by the algorithm or step size used to calculate the function.

Analog circuits compute functions of time and other input parameters as an essential part of

their operation. Analog circuits are susceptible to errors based on the numeric representation, but the errors are likely to be different than those in the digital domain. It is difficult to say which representation, analog or digital, is more susceptible to discretization errors without considering a specific problem. Analog circuits are certainly more susceptible to errors due to noise and device variations, however.

It's more difficult to choose a metric for the accuracy of a function, than for a number. Correctness is evaluated in terms of a *gestalt*, or within the context of the total range, rather than in terms of individual numerical values. Among the difficult issues are deciding which parts of the domain and range of the function are most important. This topic will be discussed in more detail in Ch. 5. We will also consider issues of choosing a signal representation to improve precision for an analog computation in Ch. 4.

It is hard to map the concept of bits and building precision by strings of static signals (ones and zeros) onto analog computation. For analog circuits, it is meaningful to think of the units of computation as functions to be composed together to form a hierarchy. A computation is embodied in the connection of the functions, which together compute the desired result. Accuracy is provided by the proper choice of the building blocks to implement the functions, and in their use.

In Ch. 4, we will explore several ways of getting more precision from analog circuits. The issue of precision in analog computation is often related to measurement error, and producing repeatable measurements. Consequently, many of our discussions in Ch. 4 will focus on reducing noise susceptibility. We will consider device variations and offsets more in the context of improving the accuracy of analog computation, which we will describe in Ch. 5. Within the world view of computation as a composition or hierarchy of functions, we can use goal-based modeling to improve the accuracy and precision of computation.

# 3.4 Solving Differential Equations more Precisely

Much research in computation involves attempts to solve differential equations more precisely. As discussed in Ch. 2, there are reasons why this will always be difficult for certain types of problems, especially when using discrete numeric representations and digital computers. Given that we are attempting to model and simulate some "thing," one of the first abstractions that is made is from the model to the differential equations which describe its behavior. As described in [Barzel 92], the next conceptual step lies in the solution of the equations.

A key component of the solution is the numeric technique chosen to use in order to solve the equations, as well as the type of computation to use (analog or digital). Often, problems are formulated as differential equations, which are then solved using some discrete step technique implemented on a digital computer. An alternative approach is to cast the differential equation into an analog circuit. We hope that we can obtain more accurate solutions of differential equations using analog circuits.

Mahowald and Douglas [Mahowald 91] described an implementation of a "silicon neuron" which faithfully models some of the electrical behavior of biological neurons. The electro-chemical behavior of neurons is quite complex and requires significant processing time to simulate on a digital computer. Due to the processing time required, it is unreasonable to attempt to simulate a large population of neurons on a single digital computer. Mahowald thus set out to produce an analog VLSI analog of a neuron that could be used to simulate a large network of neurons.

The approach that was used is extremely interesting; the physical properties of the transistors are used to directly simulate the physics of the electrochemical reactions of the actual neurons. Each of the ion currents, sodium, potassium, and chlorine, is modeled using a few transistors. These rates are exponential functions of the reversal voltages and the membrane voltage, and are thus quite suitable for implementation using transistors. This direct modeling of a set of differential equations using

analog transistors is an an excellent example of the potential of analog VLSI to solve differential equations for many other applications.

It is possible to generalize from the ideas behind Mahowald's neuron, to produce components that can be configured and used to solve other problems involving differential equations.

# 3.5 Mapping Numbers and Functions to and from Analog Signals

Analog circuits don't compute with real numbers. Analog circuits compute using current and voltage values that change over time. Everything in analog circuits is charge-based, including current and voltage. Current is charge movement over time. Voltage is a potential difference with respect to some reference, based on a quantity of charge. Electrical charge is available only in discrete quanta; charge is not continuous. Even so, we can often use the continuous approximation to think about the operation of circuits.

With the present device geometries and subthreshold transistor operation, the number of electrons involved is relatively small. Given a certain computation speed and permissible power level, there are concrete limitations to the possible precision. There are  $1.602 \times 10^{-19}$  Coulombs/electron, and 1 Ampere is 1 Coulomb/second. So, 1 Ampere consists of  $6.24 \times 10^{18}$  electrons/second. 1 nano-Ampere consists of  $6.24 \times 10^9$  electrons/second. For a computation at the nano-Ampere level, completed in 1 microsecond, we have on the order of  $6.24 \times 10^3$  electrons to work with. At this level, a difference of one electron per microsecond changes the current by 0.16%!

This small number of electrons poses a potential problem for analog circuits in the near future, as device sizes continue to shrink, and operating voltage ranges narrow as well. In fact, given the analysis in the previous paragraph, it is not surprising that noise and precision are problems with analog computing with current geometries, particularly operating at the subthreshold level. The small number of electrons involved in an analog computation indicates that our choice of signal representation will be of paramount importance in determining the quality of our analog computation.

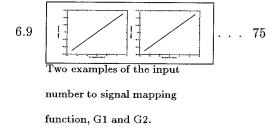

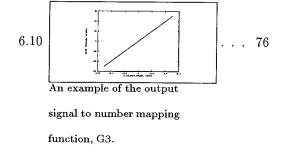

We must find ways to reliably and repeatably map from real numbers and real-valued functions to circuit quantities: we call this process the number to signal mapping function, "G."

We must worry about the useful range, in voltage or current, within which a circuit can operate, as well as what precision is needed for the signal. Explicit consideration of these factors as part of the circuit/computation design can increase the precision and accuracy of our results. We can then use an analog circuit to compute something of value. After performing the computation, we must find some way to extract the useful information from the results of the computation. This extraction involves computing a robust inverse mapping  $G^{-1}$ , which we can use to convert voltage and current signals back to numbers and mathematical functions (or floating point or fixed point digital representation, for digital computers).

We must first choose the range of the representation. Some issues that should concern us as we make this choice relate to characteristics of accuracy and precision requirements. If we expect the signal to vary "linearly" over some fixed range, or "exponentially" over a larger range of scales, we will choose differing signal representations. These decisions are related to choices made in digital computation about number representation using fixed point or floating point.

One of our biggest decisions relates to absolute/relative error criteria and the range of signal. Voltages may range from some ground reference to Vdd, which is typically a 5 volt range, and our absolute precision is typically on the order of millivolts. So, a useful computing range for voltage is about 3 orders of magnitude.

The useful computing range for currents spans more orders of magnitude than that of voltage. Our current signal noise floor is on the order of pico-Amperes, and we can consider computing with currents as large as micro-Amperes or milli-Amperes. So, we have a useful computing range of 6-9 orders of magnitude. Thus, as a rule of thumb, currents are a more appropriate representation for signals that have a larger range of operation.

We have other choices to make in determining our signal representations. For example, we must choose the limits of the computation representation. Often, we will want to choose some other value than zero (0 volts or 0 amperes) to represent a mathematical zero for the purposes of our computation. The value of "zero" that is appropriate for integrating a gradient signal over time is not necessarily 0 volts, and this issue is discussed in Ch. 7. The choice of "zero" is frequently important if we wish to represent negative quantities, particularly with voltages, since we cannot easily use voltages below ground (0V) in a silicon chip. We can choose to represent values with respect to some reference other than zero, providing a differential signal. We also may not know the ideal value for our reference in advance, and will have to discover it as part of our optimization process. We will see why unknown reference values are important, and some techniques for determining appropriate reference values in Ch. 8.

As in the previous chapter, we will prefer to think of functions as "numbers that vary over time" or that vary as some other parameter(s) change. We will, therefore, assume that all of the issues pertaining to mapping numbers to signals are also relevant to mapping functions to analog signals.

There is some analogy in the operation of our number to signal mapping function G to the oft-lamented "scaling problem" in the analog computers from the 1940s and 50s [Tomovic 62] [Soroka 54]. The scaling problem deals with choosing analog signals to represent numbers. We are addressing a similar need to map a desired computation onto some substrate. Thus, the scaling problem is a subset of the problem we are addressing. An important aspect of our work is that we will be concerned with accuracy and the quantitative character of our computation, and we will attempt to enforce it through the use of goal-based design techniques.