# Experiments in Very Large–Scale Analog Computation

Thesis by Douglas A. Kerns

In Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

> California Institute of Technology Pasadena, California 1993 (Defended 30 September 1992)

Copyright © 1993 Douglas Kerns All rights reserved

## Acknowledgments

Thanks to God, who made the world for us all to play in.

Thanks to my parents, who brought me into that world and taught me how to play.

Thanks to my wife, Beth Kerns, who supported me both financially and emotionally through the research and writing, and stayed with me all the way to the end.

Thanks to my advisor, John Hopfield, who gave me the freedom to explore, and to Carver Mead, who acted as unofficial advisor for many of my wanderings.

Thanks to the various administrative support people involved in my life at Caltech, who helped me take care of business: Debbie Chester, Chris Favata, Helen Derevan, Donna Fox.

Thanks to my fellow students, past and present, for discussion and support: Brooke Anderson, Ron Benson, Carlos Brody, Tobi Delbrück, Steve DeWeerth, Dawei Dong, Bhusan Gupta, John Harris, David Kewley, John Lazzaro, John LeMoncheck, David MacKay, Mary Ann Maher, Misha Mahowald, Marcus Mitchell, Andy Moore, Rahul Sarpeshkar, Mass Sivilotti, Grace Tsang, Lloyd Watts (and his family).

Thanks to the following organizations for support of various kinds: the National Science Foundation, DARPA, and the Office of Naval Research for financial support and funding of chip fabrication, MOSIS for administration of chip fabrication, JPL and Tanner Research for summer jobs and the resulting income and engineering experience. I want to especially acknowledge the help of specific individuals in these organizations: Silvio Eberhardt, Raoul Tawel, and Anil Thakoor of JPL, and John Tanner of Tanner Research. Without these organizations, virtually none of my graduate career could have happened.

## Abstract

The easy and inexpensive availability of microelectronic prototype fabrication allows us to perform many kinds of experiments in the construction of electronic computational machinery. There has been a recent resurgence in analog computation in various guises: electronic implementations of neural networks, other kinds of neuromorphic circuits, and electronic simulations of various physical systems.

This text documents a set of experiments in analog computation in silicon, and includes a short discussion of the relative advantages of analog vs digital computation. The most generally useful result of the work is the development of a set of techniques that allow analog circuits to automatically trim themselves, turning marginal components into devices of good precision.

# Contents

| 1 | Int  | roducti | <b>ion</b>                               |       | 1  |

|---|------|---------|------------------------------------------|-------|----|

|   | 1.1  | Syllabi | us                                       | <br>  | 1  |

|   | 1.2  |         | analog?                                  |       | 2  |

|   |      | 1.2.1   | Hybrid ICs                               | <br>  | 3  |

|   |      | 1.2.2   | Analog computing                         | <br>  | 4  |

|   |      | 1.2.3   | Brain research tools                     | <br>  | 5  |

|   |      | 1.2.4   | Art and science of efficient engineering | <br>  | 5  |

|   | 1.3  | VLSA    |                                          | <br>  | 6  |

|   |      | 1.3.1   | Component variations                     | <br>  | 7  |

|   |      | 1.3.2   | Representations                          |       | 7  |

|   |      | 1.3.3   | VLSA design                              | <br>• | 9  |

| 2 | Ana  | alog vs | Digital                                  |       | 11 |

|   | 2.1  | _       | mance                                    |       | 11 |

|   | 2.2  |         | g <i></i>                                |       | 14 |

|   | 2.3  | _       | ple: delays                              |       | 23 |

| 3 | Filt | ers and | d Delays                                 |       | 31 |

|   | 3.1  | CT filt | ters                                     |       | 31 |

|   |      | 3.1.1   | The DIFF2 filter                         |       | 32 |

|   | 3.2  | CT del  | lays                                     |       | 48 |

|   |      | 3.2.1   | Analog delays                            |       | 50 |

|   |      | 3.2.2   | Digital delays                           |       | 58 |

| 4 | UV   | Floati  | ng-Gate Techniques                       |       | 62 |

|   | 4.1  |         | notoinjection device characteristics     |       | 62 |

|   |      | 4.1.1   | A simple physical model                  |       | 62 |

|   |      | 4.1.2   | Experimental methods                     |       | 64 |

|   |      | 4.1.3   | Measured device characteristics          |       | 64 |

|   |      | 4.1.4   | UVPI device circuit model                |       | 69 |

|   | 4.2  | UV det  | etector / dosimeter                      |       | 71 |

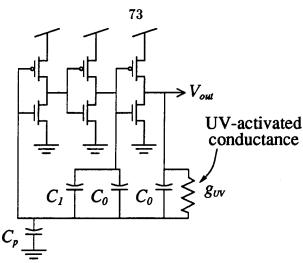

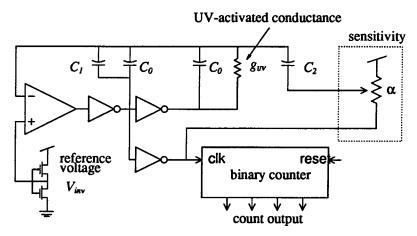

|   |      |         | Detector structures and circuits         |       | 72 |

|   |      |         | Monolithic dosimeter                     |       | 74 |

|   | 4.3  |         | itive networks                           |       | 76 |

|    | 4.4         | Local offset correction                                                                                                                     | 9 |

|----|-------------|---------------------------------------------------------------------------------------------------------------------------------------------|---|

|    | 4.5         | Global offset correction                                                                                                                    | 1 |

| 5  | Ass         | rted Building Blocks                                                                                                                        | 7 |

|    | 5.1         | Conductances and transconductances                                                                                                          | 7 |

|    |             | 5.1.1 sinh resistor                                                                                                                         | 7 |

|    |             | 5.1.2 Arreguit's Early-effect amplifiers                                                                                                    | 9 |

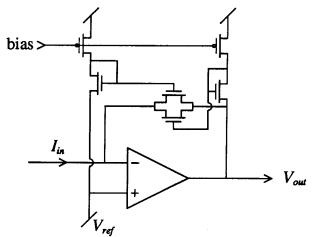

|    | 5.2         | Transimpedances                                                                                                                             | 1 |

|    |             | 5.2.1 Inverse tanh                                                                                                                          | 2 |

|    |             | 5.2.2 Inverse sinh                                                                                                                          | 2 |

|    |             | 5.2.3 Linearized                                                                                                                            | 3 |

|    | 5.3         | Bias generation                                                                                                                             | 3 |

|    |             | 5.3.1 Voltage dividers, $V_{inv}$ bias                                                                                                      | 4 |

|    |             | $5.3.2  V_e \text{ bias} \dots \dots$ | 5 |

| 6  | Fut         | re Directions 98                                                                                                                            | 8 |

|    | 6.1         | Hybrid representations                                                                                                                      | 9 |

|    | 6.2         | Fabrication processes                                                                                                                       | 1 |

| Bi | bliog       | raphy 103                                                                                                                                   | 3 |

| A  | Syn         | pols and Conventions 109                                                                                                                    | Э |

|    | <b>A.</b> 1 | Symbols                                                                                                                                     | 9 |

|    | <b>A.2</b>  | Naming conventions                                                                                                                          | 9 |

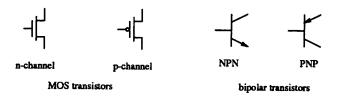

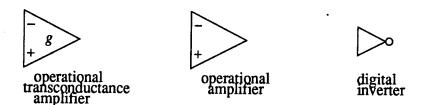

|    |             | Pictorial conventions                                                                                                                       | O |

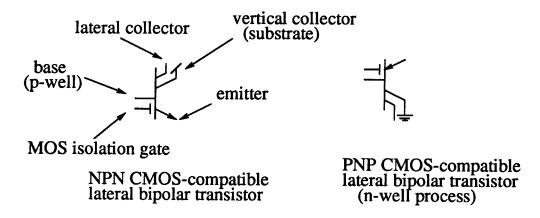

|    |             | A.3.1 Transistors                                                                                                                           |   |

|    |             | A.3.2 Amplifiers                                                                                                                            | 0 |

|    |             | A.3.3 Miscellany                                                                                                                            |   |

# List of Figures

| 2.1  | Discretization of quantities: analog or digital?  |

|------|---------------------------------------------------|

| 2.2  | Circuit area vs precision of comparators          |

| 2.3  | Historical DRAM sense amp data                    |

| 2.4  | Energy cost vs precision of comparators           |

| 3.1  | DIFF2 filter                                      |

| 3.2  | DIFF2 lowpass                                     |

| 3.3  | DIFF2 highpass                                    |

| 3.4  | DIFF2 bandpass                                    |

| 3.5  | DIFF2 bandstop                                    |

| 3.6  | Parasitic capacitance in the OTA                  |

| 3.7  | DIFF2 instability                                 |

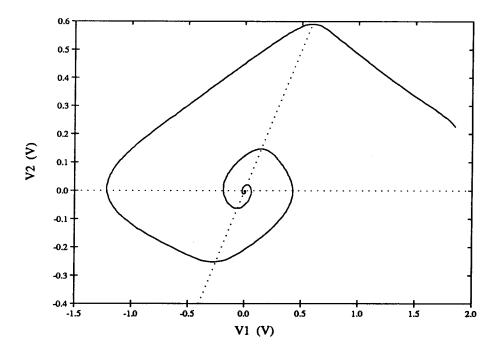

| 3.8  | Large-signal polygonal trajectories: model        |

| 3.9  | Large-signal polygonal trajectories: experiment   |

| 3.10 | DIFF2 large-signal response                       |

| 3.11 | Response of a filter with hardening nonlinearity  |

| 3.12 | Four-transistor filter circuit                    |

| 3.13 | Follower-integrator delay line                    |

| 3.14 | Diffusion in first-order CTCS delays              |

|      | Second-Order Derivative Estimate                  |

|      | Complex pole plot for the second-order delay line |

|      | Impulse response of a second-order delay line     |

|      | Second-order forward difference circuit           |

| 3.19 | Pulses in different CTCS delay lines              |

|      | CTDS delay                                        |

|      | Using a ring oscillator to measure small currents |

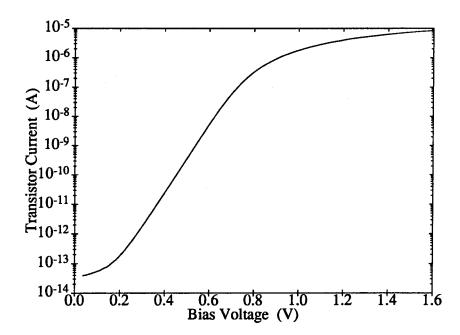

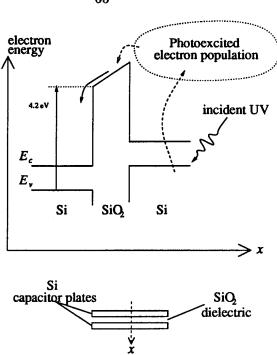

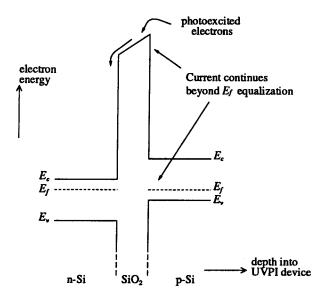

| 4.1  | Band diagram of UV photoinjection device          |

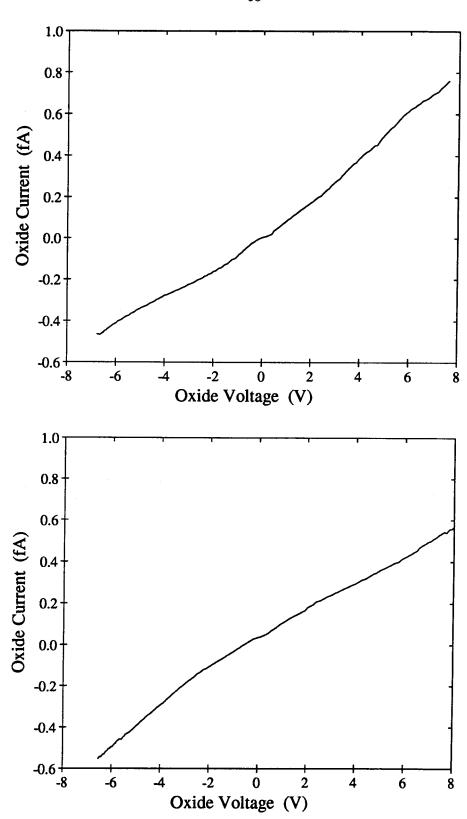

| 4.2  | UV-enabled conduction between poly layers 65      |

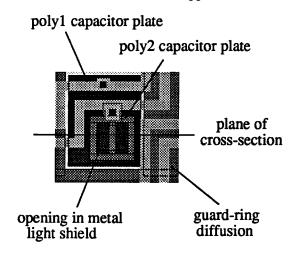

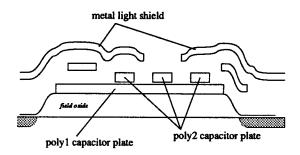

| 4.3  | UVPI structure layout / cross-section             |

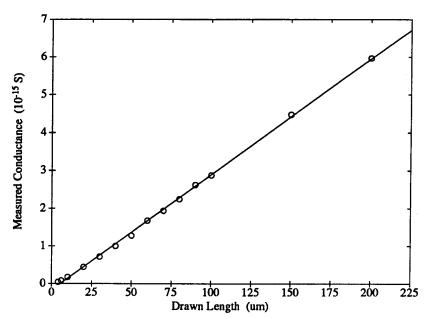

| 4.4  | UVPI conductance vs device size                   |

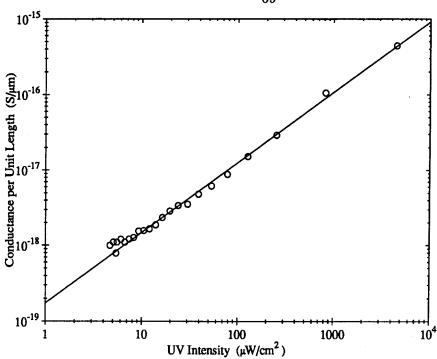

| 4.5  | UVPI conductance vs illumination 69               |

| 4.6  | UVPI device with p-Si and n-Si                    |

| 4.7  | Illustration of work-function mismatch            |

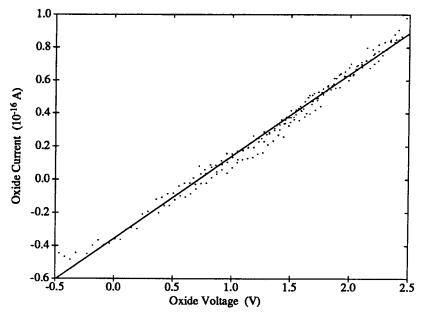

| 4.8        | UVPI device circuit model                           |

|------------|-----------------------------------------------------|

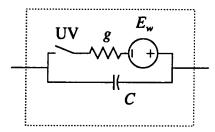

| 4.9        | Simple integrated UV detector                       |

| 4.10       | Monolithic UV dosimeter circuit                     |

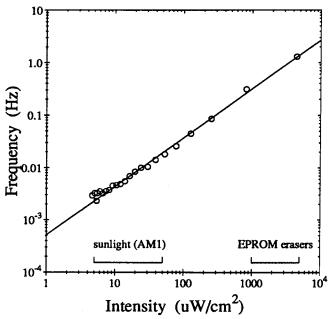

| 4.11       | UV detector intensity response                      |

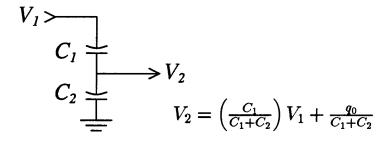

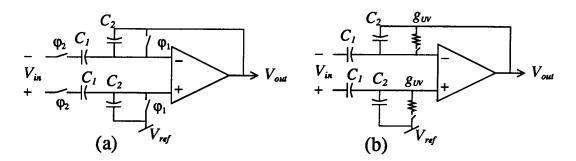

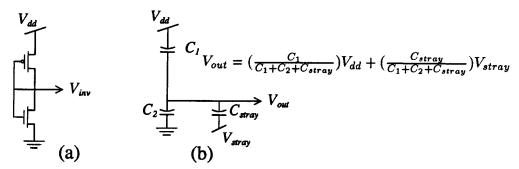

| 4.12       | Capacitive voltage divider                          |

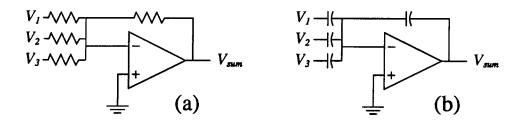

| 4.13       | Integrated voltage summing amplifier                |

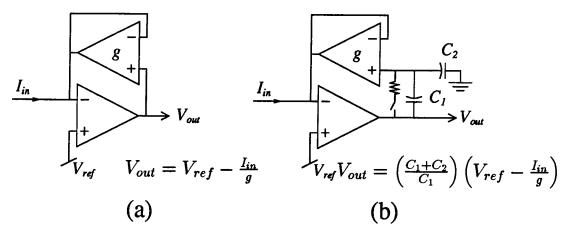

| 4.14       | Transimpedance amplifier using a capacitive network |

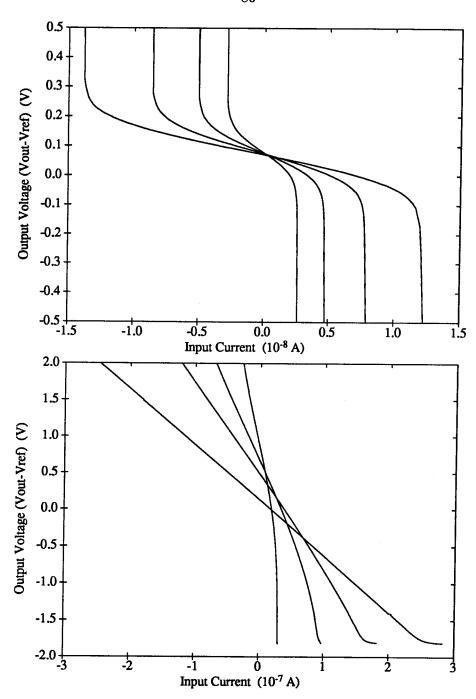

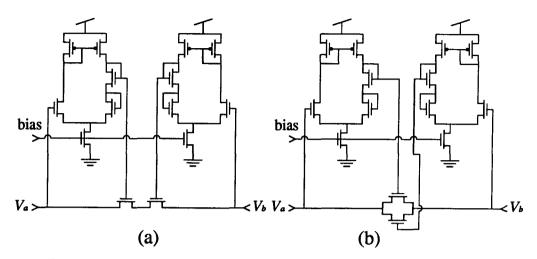

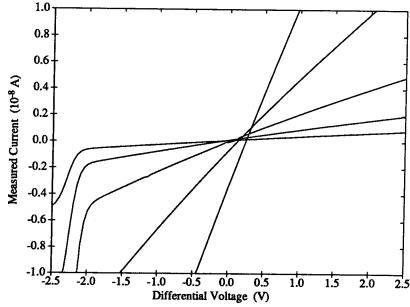

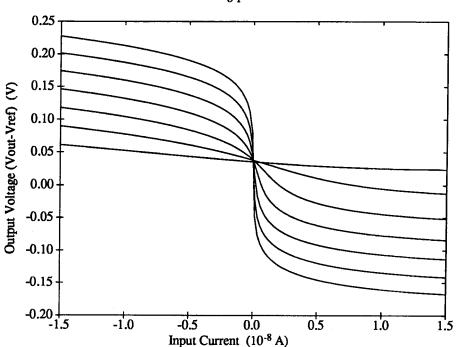

| 4.15       | Experimental data from transimpedance amplifiers    |

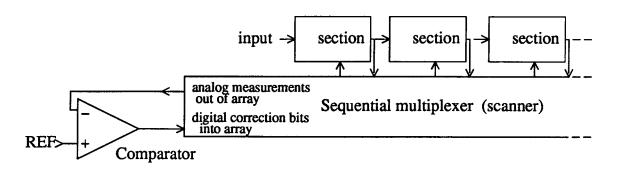

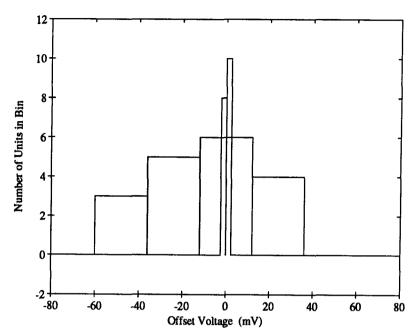

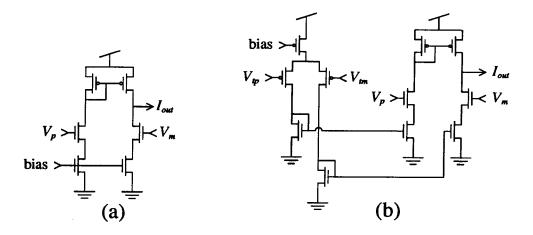

| 4.16       | Local offset nulling circuits                       |

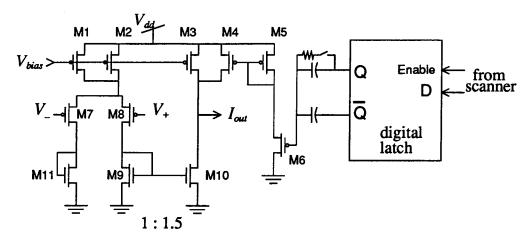

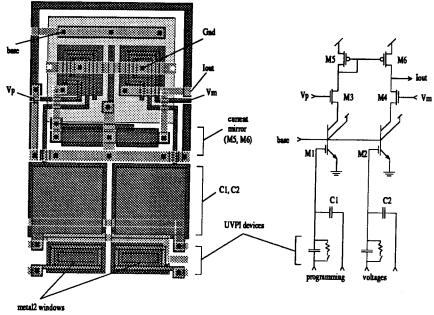

| 4.17       | Diagram of a global trimming circuit                |

| 4.18       | Transistor-level diagram of of a global trim cell   |

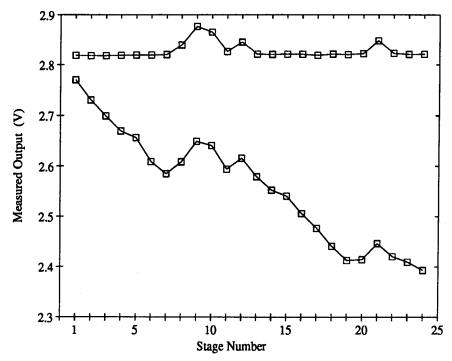

| 4.19       | Global offset trimming data                         |

| 4.20       | Offset reduction using the global trim method       |

| 5.1        | Nonlinear resistance circuits: tanh and sinh        |

| 5.2        | Sinh-resistor data 89                               |

| 5.3        | Early-effect amplifier using lateral bipolars       |

| 5.4        | Early-effect amplifier characteristics              |

| 5.5        | All-MOS Early-effect amplifier                      |

| 5.6        | Inverse sinh circuit                                |

| 5.7        | Inverse sinh data                                   |

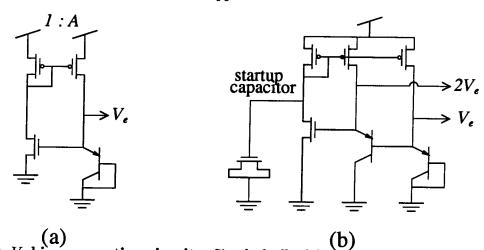

| <b>5.8</b> | Voltage divider references                          |

| 5.9        | $V_e$ bias generation circuit                       |

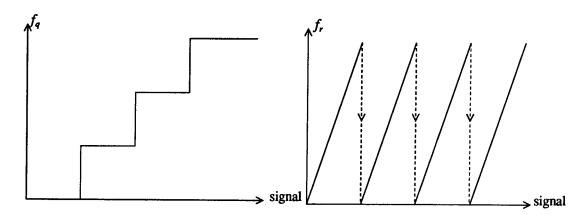

| 6.1        | transfer functions of a subranging ADC section      |

| 6.2        | Continuous ADC transfer functions                   |

| 6.3        | Space-curve representation of an ADC stage 101      |

|            |                                                     |

# List of Tables

| 1.1 | Components available in silicon CMOS            | 9  |

|-----|-------------------------------------------------|----|

|     | Measures of performance for computing machinery |    |

| 3.1 | Table of numerators                             | 35 |

## Chapter 1

## Introduction

This text documents my wanderings in the world of analog computation in silicon. I sought to contribute useful circuits, techniques, and ideas to designers of large-scale analog computing engines. My experiments were confined to  $2\,\mu\mathrm{m}$  silicon CMOS technology because of cost and availability, but many of the circuits and techniques can be used with other circuit fabrication technologies. The limit of application of the ideas depends, as always, on the imagination of the reader.

One will find that it is often worth expending the effort to achieve an improved result by applying more sophisticated circuit engineering to a relatively unsophisticated fabrication process. The prize is ready, inexpensive access to fabrication of the resulting circuits. While many of the circuits and subsystems presented in this writing could probably be greatly improved by a tailor-made fabrication process, it will rarely be worth the relatively great expense and effort of tailoring a fabrication process to a particular project. This reliance on circuit techniques, rather than process techniques, is one of the main driving forces behind the work in my thesis.

#### 1.1 Syllabus

Chapter 1 introduces the utility of analog computational circuitry in various contexts.

Chapter 2 makes some comparisons between analog and digital computations, and sets up some pointers for comparing effectiveness and efficiency of various methods of performing a given computation.

Chapter 3 covers some continuous—time filter and delay circuits. These circuits offer extremely low power consumption in the audio—frequency range, and may prove to be useful in front—end processing of speech or sonar information.

Chapter 4 covers a set of techniques for using UV light to manipulate the charge stored on floating MOS circuit nodes. Silicon MOS technology provides virtually indefinite storage of charge on insulated nodes, so techniques for controlling stored charge allow long-term storage of data and trim parameters.

Chapter 5 is a catch-all bin for useful bits and pieces of circuitry developed by necessity or curiosity. The circuits in this chapter are not outstandingly original or unusual, but are straightforward extensions and adaptations of others' work. They are included as archival reference material.

Chapter 6 speculates on future developments which may stem from this and others' work on integrated analog computation. The first section presents ideas about continuous-valued multiwire signal encoding as a possible means to gain the best parts of both analog and digital circuit techniques. The second section contains some thoughts on using autocorrective circuits in microelectronic fabrication processes.

#### 1.2 Why analog?

With all the great advances in digital signal processing and computing technology, one might ask, why bother at all with analog computing? It turns out that analog computing and signal processing offer some real advantages over digital approaches in certain (fairly common) cases. Even the most staunch supporter of DSP must admit that there is no

substitute for continuous-time filters for antialias operations at the boundaries of DSP systems. There are, in fact, many more places for analog computational or signal processing subsystems.

#### 1.2.1 Hybrid ICs

The idea of "analog VLSI" is growing in popularity in various places and for various reasons. In telecommunications and consumer electronics, it is appealing to integrate all of the control and signal processing functions of a product or subsystem on a single (potentially low-cost) piece of silicon. This ideal usually involves mixing analog and digital information on the same chip, hence the combination of "analog" and "VLSI." Typical components of such mixed-mode systems are filters, amplifiers, A/D and D/A converters, and occasionally "smart" sensors. Often the input to a circuit is analog, and the output is digital, or vice-versa, so the circuit must behave as a computationally enhanced A/D or D/A converter, perhaps with integrated signal conditioning or processing of some sort. Common examples of this sort of device are found in telecom subscriber interface circuits [6] and "smart" sensors [7].

One will frequently find that references combining "analog" and "VLSI" in the same title actually mean this sort of mixing of analog and digital subsystems on a single substrate, and rarely do they refer to analog computation on any scale larger than a simple filtering or scaling operation. The problems faced by the designer of mixed—mode circuitry have much in common with the designer of truly large—scale analog computational circuitry, but there tends to be the additional complication of crosstalk from digital switching circuitry near sensitive analog circuitry [24]. Virtually all commercial mixed—mode electronics restrict the analog portions of the information processing to simple tasks such as gain and filtering operations, pushing the complicated

tasks into a digital circuit of some sort. However, the idea of using analog computation on a large scale or for more complicated processes has recently been gaining momentum, as evidenced in the publication of Mead's text [1].

#### 1.2.2 Analog computing

Historically, analog computers allowed a rapid search of a large parameter space to find singularities and other critical points [14, 15]. While analog computing techniques have been largely neglected in the past decade, the technology now exists to build faster, more compact, and possibly more accurate analog computers than ever before. The same technology that allows us to build high-performance digital computing machines can also be used to build high-performance analog computing machines. The advent of widely available BiCMOS technology allows us to build good operational amplifiers as well as a host of other analog computational circuits, straightforward interfaces to digital computer systems, and even the possibility for integrated programmability from digital host computers [16].

More recent work in analog VLSI has taken advantage of the relatively cheap and easy avaliability of custom silicon circuit fabrication to build a variety of special-purpose analog computers. These analog computers are not generally called "analog computers," but, rather, they are named for the system to which they are analogous, such as the silicon retina, the electronic cochlea, and so on. Just as in the early days of analog computing, however, these modern analog computers allow real-time exploration of a large space of parameters in the system being modeled.

In addition, there has been some activity in the area of actually using these specialpurpose computing engines as pieces of larger systems. This application trend is especially notable in models of brain sensory systems, where immediate applications may be found for good real-world interfaces for computers and robotics [5, 19].

#### 1.2.3 Brain research tools

Analog techniques may also prove to be useful tools in brain research, allowing experiments in "downhill synthesis" [17] as well as providing special-purpose analog computers to emulate real neurons [13]. Examples of synthetic explorations of some merit are found in the vision work of Mahowald and Mead [4], the auditory work of Lyon and Mead [8], Lazzaro [10], and Watts [11], and the work of Ryckebusch in synthesizing various central pattern generators [12].

Such synthetic exploration allows researchers to probe into the hazy area between hardware and software, exploring how various regions of brains might work. Many parts of the brain and many modes of its functioning are inaccessible to current technology, so the ability to synthesize a facile, responsive, and observable model is a great bonus.

#### 1.2.4 Art and science of efficient engineering

There is a strong artistic appeal to using low-level physics directly for a computational task. This aesthetic appeal is complemented by the hard engineering fact of greater efficiency in energy and area; such designs are called "elegant." To further add to the elegance, one finds that thinking in terms of low-level physics can lead to new solutions to old problems, driving the technology into previously unexplored areas, as pointed out by Harris [18]. Some information processing algorithms map very naturally and gracefully onto analog computing hardware, resulting in area—and power—efficient performance. One of the best examples of this is Mead's resistive mesh, which elegantly computes a smoothing function [1]. Extensions of this example can be found in the work of Harris [18] and others [19].

Energy efficiency is becoming a serious consideration in computing machinery, as

advances in fabrication and packaging technology pack more and more machinery into each cubic centimeter. Computation costs energy, and the waste heat must be removed from any computing machine in some way. As packing densities increase, removing this waste heat becomes a more and more serious problem. Any method that increases the amount of computation that can be done for a unit of energy also increases the physical density to which we are allowed to pack the computing machinery before it overheats.

It is interesting to consider a comparison between current commercial computing technology, computing technology that is still in the research labs, such as that described in this text, and the best available examples using any computing technology. Our brains are an existence proof of very powerful and efficient computational algorithms for a variety of tasks. A human brain dissipates about 40 W in a volume of about  $1500 \, \mathrm{cm}^3$ , for a power density of about  $2.7 \times 10^{-2} \, \mathrm{W/cm}^3$ . A standard microprocessor uses roughly 2 W in a volume of about  $10 \, \mathrm{cm}^3$ , for a power density of  $0.2 \, \mathrm{W/cm}^3$ . One order of magnitude doesn't look too bad, if we can ignore the differences in capabilities. However, if we strip off the volume occupied by the package and the mechanical substrate, then the microprocessor is a chunk of silicon about  $1 \, \mathrm{cm}^2$ , of which perhaps a  $30 \, \mu \mathrm{m}$  thickness is required for the computing devices, wiring, and so on, giving the same power dissipation in a volume of  $3 \times 10^{-3} \, \mathrm{cm}^3$ , for a power density of  $670 \, \mathrm{W/cm}^3$ . Clearly, the packaging is necessary in order to reduce the system-level power density to a tolerable level. By contrast, special-purpose analog computers such as a electronic cochlea show a power density of  $4.2 \, \mathrm{W/cm}^3$  using the same technique.

#### 1.3 VLSA

What can be said in general about very large-scale analog computation? As in any analog circuit design, the designer of VLSA circuitry will face the problem of random

component variations. In addition, he/she must synthesize a compatible combination of information representations and electronic circuitry. Robust circuit designs and efficient signal representations are essential to successful VLSA design.

#### 1.3.1 Component variations

Variations in component parameters are a well-known part of all electronic design. Component manufacturers have tried to control variations, and design engineers have tried to design robust circuits. So far, most VLSI manufacturing processes have been aimed at digital circuit fabrication, so fine-scale component variations have gone unnoticed. When one tries to use the same process to fabricate very large-scale analog circuitry (VLSA), one finds the variations, and is faced with the old problem of robust design [21].

VLSA integrated circuitry must either have a low intrinsic sensitivity to component variations, or have the capability to automatically trim out such variations. Truly large-scale circuits would be quite impractical and expensive if the variations had to be manually trimmed, each IC requiring many tens or hundreds of trimming operations. Chapter 4 outlines some techniques for designing automatic trimming into VLSA circuitry, and Chapter 6 speculates on a possible approach for reducing component variations at fabrication time.

#### 1.3.2 Representations

Analog computational circuits can be built to use continuous, discrete, and mixed-mode signal representations in units of voltage, current, or charge. Typical digital circuits use only one unit type (voltage, current, or charge) on a fixed number of discrete levels to represent information. Typical analog circuits use all three unit types, usually in a continuous representation. This flexibility with respect to representation of information

can give analog circuits the advantage of greatly simplified interface structures to real—world inputs (sensors of various types, whether integrated or off-chip) and outputs (actuators of various types).

Each type of representation has its advantages and typical uses. One task of the VLSA designer is to become familiar with the different possible representations of a quantity in order to choose the best possible representation for a given design.

voltage Voltage is the classical electrical quantity for representation of information, mostly because chemistry and physics have conspired to make voltage sources easy to build, while current or charge sources are considerably more difficult. A fixed voltage represents a fixed charge-carrier energy, hence the ubiquity of electrochemical voltage sources.

A voltage may be broadcast on a conductor to as many locations as needed in a system. Duplication of a voltage is as simple as connecting another piece of wire in the circuit. In a graph representation of an electrical network, a voltage is considered to be a node property.

current Current is a dual quantity to voltage; a current is a property of the edges of a graph representation of an electrical network. A current is a flux of charge carriers, so a sum of currents may be obtained simply by connecting circuit branches.

charge In some devices, such as charge-coupled devices (CCDs), one finds electrical charge to be the representation of information. A charge is a quantity of charge carriers, and is therefore the integral of a current over time. Electrical charge as a representation mode gives the designer access to both an integration with respect to time and a summation.

| component  | relative area | comment                                |

|------------|---------------|----------------------------------------|

| wire       | 1             | fundamental component in an IC process |

| capacitor  | 1–10          | (junction of wires)                    |

| transistor | 1–10          | (a special kind of capacitor)          |

| resistor   | $10^2 - 10^3$ | (very long wires)                      |

| inductor   | $10^4 - 10^5$ | (very large wire loops)                |

Table 1.1: Components available in silicon CMOS: Some of the more common analog circuit components are listed. An integrated circuit process also provides the designer with the opportunity to make use of the details of the semiconductor physics to construct devices that are unrealizable as discrete components.

#### 1.3.3 VLSA design

A typical analog circuit design uses the broadcast of voltage, summation of current, and integration of charge in many different and interesting ways. In addition, the specific physical properties of electrical devices, such as transistors, allow more complex interactions between the various electrical quantities in ways that can be used to accomplish computational tasks.

This text documents an exploration of some circuits and techniques for performing analog computations using silicon CMOS technology. This exploration has shown that the success of a circuit design for a task often hinges on the proper choice of data/signal representation at various stages of the computation. It is important to ensure a continuous smooth flow of compatibly represented information among different subcircuits, or the total system design becomes dominated by sections whose sole purpose is a trivial change of representation.

In addition, the fabrication technology restricts our choice of components. Table 1.1 lists some of the standard circuit elements available in silicon CMOS. Any effective VLSA design must make wise use of the capabilities of the fabrication technology. For example, a circuit including inductances will not generally be area—efficient, because of the tiny inductances available to the IC designer. Capacitances, on the other hand, are

readily available. Resistances are often used in traditional analog design, but a no-frills silicon CMOS process has no provision for layers of high resistivity, so resistors become very large, and should be avoided whenever possible.

### Chapter 2

# Analog vs Digital

Which is the better mode for computation, analog or digital? This question is almost meaningless when asked without context. The answers one finds on close examination are tightly bound to the particular problem at hand, and, especially, dependent on the required definition of "good."

#### 2.1 Performance

The definition of "good" is critical to evaluating the performance of a computing machine. For one problem, precision may be of ultimate importance, while speed is relatively unimportant and power consumption is irrelevant. For another problem, speed may be paramount, while the requirement for precision is quite small. Each measure of performance has its own relationship to the circuit techniques used in the design of a computing machine.

Table 2.1 lists performance measures which are considered important in various contexts. In most cases, only a few measures are important for any particular application, while the rest are unimportant or irrelevant.

In either design paradigm, analog or digital, these various performance measures trade off against each other, often in complex ways. Terms such as "efficiency" usually

```

power (usually proportional to speed)

size

speed

dollar cost

design time / effort (often a large fraction of dollar cost)

flexibility or (re)programmability

Shannon information capacity (depends on speed and error rate)

error rate

number of trims

reliability wrt component variations and failures

```

Table 2.1: Measures of performance for computing machinery

refer to ratios of competing measures of goodness, and so are higher-level measures. Some of the measures listed above overlap. For instance, high speed usually implies high Shannon capacity, although the information capacity also depends on the error rate. There is a relatively direct competition between high speed and low power dissipation: each decision made, or signal cycle or bit propagated costs at least some minimum quantum of energy [2].

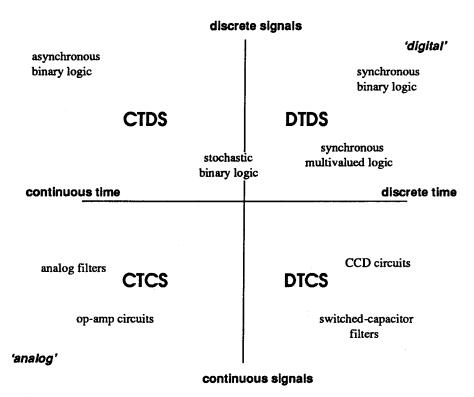

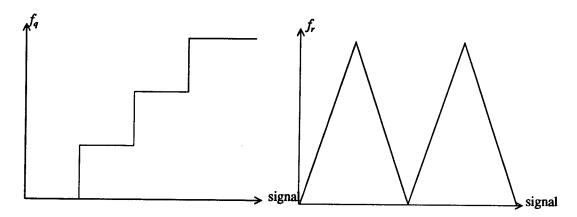

In addition to the confusion over good and evil, one can choose independently whether to work with discrete or continuous signals, and whether to work in discrete time or continuous time. One can find examples of computing machines in all four sections of Figure 2.1. Traditionally, discretized signal representations are called "digital" regardless of the time representation, while continuous signal representations are generally called "analog."

Power density is becoming a concern in the design of computing machinery. Above a critical temperature, integrated device reliability degrades seriously. A critical temperature corresponds to a critical power density. There is perhaps an order of magnitude of variation in critical power density for a given temperature, depending on the details of packaging, but as integration densities increase and processing rates increase, the power density increases in proportion to each. Mead and Conway asserted that a cru-

Figure 2.1: Discretization of quantities: The boundary between analog and digital computations is a hazy one, so one needs to be cautious when making comparisons.

cial measure of computing performance is the unit switching energy [2]. Clearly, as  $E_{sw}$  decreases, the total amount of computation that can be performed, in a unit volume and unit time at the critical power density, increases. One might consider that, for any algorithm for a particular task, there is a critical density of computation.

Part of the resurgence in analog computing techniques of various sorts is due to the promise that new computing algorithms may provide more computation for a given energy, hence boosting the critical density of computation. As denser circuit fabrication techniques are developed, the power density limit will become critical in many designs. Examples of circuit technologies that are pushing the power density limit are the chip lamination packaging process developed by Irvine Sensors of Irvine, California, multilayer MOS processes such as that reported by Kioi et al. [58], and more conventional

multi-chip packaging techniques.

#### 2.2 Scaling

It would be useful, having listed some performance measures, to examine in more detail how analog and digital computations differ along the various axes of performance space. Hopfield showed that it is a straightforward task to discover the scaling laws for various methods of solving a problem [22]. Similarly, Vittoz analyzed analog and digital filters to discover the way in which power dissipation scales with precision [23], and Hosticka presented a simple comparison of CTCS analog, DTCS analog, and DTDS digital circuits based on an information–capacity measure [25]. All three authors discovered very similar results: the algorithmic difference between standard analog and digital techniques for comparable problems give radically different scaling rules for the two modes. Analog circuits tend to be more efficient at low precision, but they scale badly as more and more computational effort is required on a single signal.

Hopfield's analysis centered on a plausible generic electronic technology; the discussion below will use similar methods to examine the real technology of  $2 \mu m$  CMOS. A problem that readily admits both analog and digital solutions is that of comparing two quantities and making a decision about which is greater. We can make the comparison between a typical analog implementation and a typical digital implementation for several standard performance measures: area, energy, and time.

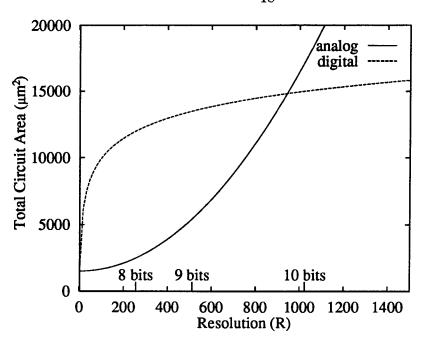

Area An analog comparator capable of resolving differences of  $30 \,\mathrm{mV}$  over a range of  $4 \,\mathrm{V}$  can be built in a  $2 \,\mu\mathrm{m}$  CMOS technology in an area of about  $1500 \,\mu\mathrm{m}^2$ . The resolution of this comparator is 1 part in 130, or about 7 bits. A 7-bit binary comparator constructed with the same technology will occupy an area of about  $10 \,000 \,\mu\mathrm{m}^2$ . As the

precision of comparison scales up, though, the digital circuit begins to win somewhere around 9 or 10 bits, depending on the specific details of the circuits and fabrication process. Trimmable analog circuits can push this tradeoff limit further, to about 12 bits, but the digital circuit still eventually wins, because of its logarithmic scaling. The addition of a single extra bit slice to a digital comparator will double its resolution, while a doubling of resolution of an analog comparator requires approximately a quadrupling of area.

The resolution of the digital comparator is easy to analyze: one simply counts the number of bits in the input word. The resolution R, ratio of the minimum resolvable difference to the maximum representable quantity, is  $2^N$ , where N is the number of bits in each input word to the comparator.

A digital comparator can be built in various ways, but one of the smallest is an iteration of identical bit slices, each of which compares a bit from each input word. The most significant bit passes the result of its comparison to the next comparator slice, and so on. A design of this sort occupies an area that is proportional to N, with a single slice occuping an area of about 1500  $\mu$ m<sup>2</sup> in 2  $\mu$ m CMOS.

The resolution of an analog comparator is trickier to find. Experimentally, one can find the resolution by looking for the smallest resolvable difference and for the largest representable quantity and taking the ratio. How does the design of the comparator circuit influence these quantities? The largest representable quantity can usually be taken to be the power supply magnitude, or, perhaps somewhat less, in order to account for limitations in the circuit. (A typical differential input stage operates correctly over a limited subrange of the power supply, hence the 4V range given above, rather than the full 5V typical power supply). The smallest resolvable difference depends on two properties of the comparator circuit: gain and offset.

The comparator must have sufficient gain to amplify the minimum resolvable difference to an unambiguous decision. We might reasonably state that the gain of the comparator should be sufficient to amplify the minimum resolvable difference to the maximum range, so, then, we require that the comparator gain should be greater than or equal to the resolution R. The gain of a comparator circuit implementation depends on the properties of the transistors, in particular, on the drain conductance. One can find that the gain of an amplifier grows approximately linearly with the length of the transistor channels. In order to maintain a constant bandwidth (or time to complete the computation) the width of the devices also needs to increase, for a net increase in area proportional to the square of the gain increase. In a typical  $2 \mu m$  CMOS process, we can expect a gain of about  $20 \mu m^{-1}$  for a simple output stage, giving an output stage area something like  $A_{ao} = (R^2/400) \mu m^2$ .

The offset of the comparator limits the smallest resolvable difference in a different way. Even with infinite gain, a comparator with an offset will give an incorrect solution to the comparison problem for some set of inputs. The offset of a comparator circuit depends on matching symmetrical circuit elements. In general, better element matching gives a smaller offset. In a typical comparator circuit, the transistors of the differential input stage are of particular importance to the overall offset. The differential pair will have an offset voltage inversely proportional to the square root of the transistor area [21], so, again, for a given proportion of decrease in offset voltage  $\delta V$ , the circuit area must increase quadratically:

Area =

$$\left(\frac{P_{os}}{\delta V}\right)^2$$

(2.1)

Based on data in [21], which fits well with informal observations by myself and others here at Caltech, a typical  $2\,\mu\mathrm{m}$  digital CMOS process will give an input offset coefficient  $P_{os}$  of about  $150\,\mathrm{mV}-\mu\mathrm{m}$ . To design a reliable comparator, one should put at least

two or three standard deviations into the design. The area of the input stage of the comparator will therefore be  $A_{ai} = (R^2/80) \, \mu \text{m}^2$ .

The analog comparator will also use a nearly constant area of about  $1500\,\mu\text{m}^2$  for wiring, contacts, and minor glue circuitry between the input stage and the output stage. We end up with a total analog comparator area of

$$A_{analog} = 1500 + A_{ai} + A_{ao} = 1500 + \left(\frac{R^2}{80}\right) + \left(\frac{R^2}{400}\right)$$

.

We can now directly compare analog and digital comparator areas as functions of the resolution R:

$$A_{analog} = 1500 + \left(\frac{R^2}{80}\right) + \left(\frac{R^2}{400}\right) \qquad A_{digital} = 1500 \log_2 R \quad .$$

(2.2)

These area formulas are plotted in Figure 2.2, where the crossover clearly falls near 10 bits.

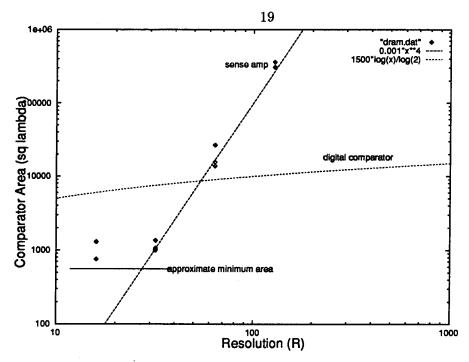

It is interesting to compare the above derivation of analog comparator area scaling with historical data for the area of DRAM sense amplifiers. Figure 2.3 plots the areas of various DRAM sense amplifiers as a function of the number of bit cells attached to the amplifier. A Dynamic random–access memory depends on capacitive storage of a bit value in a capacitor cell, and on active restoration ("refreshing") of the stored charge with a sense amplifier. The sense amplifier is actually a clocked analog comparator that compares the bitline voltage to some reference voltage to determine whether a "1" or a "0" was stored in the addressed cell. On can roughly measure the resolution of a sense amplifier by determining how many bit cells are attached to a single sense amplifier. The data in the figure are given in square lambda, where lambda is half-linewidth in the technology used. For comparison, lambda is equal to  $1\,\mu\rm m$  in the  $2\,\mu\rm m$  technology used for my thesis experiments, so the vertical axis of Figure 2.2 could also read, "square lambda."

Figure 2.2: Circuit area vs precision of comparators: Analog comparators begin much smaller than digital comparators, but as the resolution is increased, digital comparators begin to win because of a more efficient representation of the data. Analog comparators scale as a power law, while digital circuits scale logarithmically with resolution.

The historical data follow a quartic power law, rather than the quadratic power law derived above. The reason for the difference in power law is unclear (keep in mind that the data are from a wide variety of different processes and feature sizes, normalized on the basis of the lithographic process limit, which is assumed to track electrical properties). Nonetheless, it remains that analog comparator areas scale as power law functions of resolution, while digital comparators scale logarithmically.

Because none of the authors directly reported sense amp areas, the data in Figure 2.3 were derived by measurements of the chip photographs presented in the papers. Papers used to obtain the data are reported at the end of the chapter.

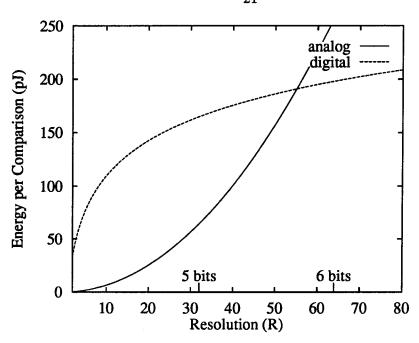

Energy The same scaling properties for area carry over to power consumption. For the comparator example, one can analyze the power consumption and discover that the

Figure 2.3: Historical data on DRAM sense amp areas: sense amp areas (in square lambdas) scale as the fourth power of the number of bit cells attached to the amplifier. Note the rather sharp lower limit, as circuit area becomes dominated by the constant wiring and contact overhead, rather than transistor properties.

analog comparator will consume a total energy proportional to square of the precision of the comparison, while the digital comparator will consume a total energy that is logarithmic in the precision. The physics of typical electronic implementations of the comparators dictate that the analog comparator will use less energy than the digital one up to a precision of about six bits.

The digital comparator is composed of N iterated bit slices, each of which must compute two logical functions of its inputs. The inputs to each slice are a pair of bits, one from each of the input words, and two carry signals from the higher-order slices of the comparator. A straightforward implementation of such a slice as a static CMOS logic element uses 22 transistors, 11 of each type. In the worst imaginable case, all of the transistors need to be switched during one comparison, so the energy expended on a comparison operation is about  $22NE_0$ , where  $E_0$  is the average switching energy of

a single device, about 1.5 pJ for  $2 \mu \text{m}$  CMOS if average wiring and contact strays are included. Thus, the total energy cost for a comparison totals up to  $E_d = 33N \text{ pJ}$ .

The analog comparator discussed above consumes a constant bias current  $I_b$  during operation. For a typical design, half of the bias current is used to charge and discharge internal nodes of the circuit, and the other half is available for charging and discharging the output load capacitance. The time to complete a comparison can be taken to be the time it takes to charge the output load over half of the power supply range. This time estimate is somewhat pessimistic, as in a typical application, half the power supply range is perhaps an order of magnitude larger than the voltage required to saturate a differential input stage. We can reasonably take the load of the comparator to be the input of another comparator, or a substantially similar circuit.

From the area analysis above, we can find the load capacitance as a function of precision. The input stage requires a total transistor area of about  $R^2/400 \,\mu\text{m}^2$ , of which half will be loading the comparator. The gate capacitance in our example  $2 \,\mu\text{m}$  CMOS process is about  $5 \times 10^{-4} \,\text{pF}$  per  $\mu\text{m}^2$ . These parameters allow us to compute the total energy expenditure for a single comparison operation, with a typical  $5 \,\text{V}$  power supply. The energy expenditure of our analog comparator is

$$E_a = I_b V_{supply} T_{comp} = 2.5 \times 10^{-15} V_{supply}^2 R^2 = 6.3 \times 10^{-14} R^2$$

(2.3)

In order to make an easy comparison, then, we can compare the analog and digital energy costs as functions of R:

$$E_a = 6.3 \times 10^{-14} R^2, \qquad E_d = 33 \times 10^{-12} \log_2 R \quad .$$

(2.4)

These functions are plotted in Figure 2.4. The crossover point occurs a little short of six bits for the designs presented above. More ingenious circuit techniques may push

Figure 2.4: Energy cost vs precision of comparators: Analog comparators are much more efficient at low precision, but as the resolution is increased, digital comparators again win because of a more efficient representation of the data.

the crossover out as high as ten bits or so with trimming, but the digital comparator will always eventually win as the resolution of the comparison is increased.

In many discrete-time systems, clocked comparators using feedback are used. A classic example is the DRAM sense-amp, which detects a bit value in a dynamic memory cell by making an analog voltage comparison and generating a digital output value. Comparators which use feedback can be shown to be considerably more efficient than the feedforward analog comparator discussed above. The limitation on the use of a fed-back comparator circuit is that it must be reset before each comparison, and so is intrinsically a discrete-time circuit.

As shown in the historical data for DRAM sense amps, analog comparators still suffer from poor scaling rules in comparison with digital comparators.

Time If we try to estimate the time required for the comparison computation, we run into some interesting results. Digital circuits can be pipelined to yield a constant-time operation with a latency which depends on the word length. An analog comparator uses quite a different comparison algorithm, so the analog comparison takes longer and longer to compute as the resolution increases. This increase comes directly from the fact that the analog algorithm for comparison generally comes down to subtracting currents, and, as the difference current shrinks, the time required to charge a node capacitance to make a decision grows proportionally.

The analog/digital comparison in the previous paragraphs hinges on the fact that digital computations are typically performed using a logarithmic code which is distributed over many wires, while analog computations are typically performed with a linear coding scheme on a single wire. There is no apparent fundamental reason not to try to devise nonlinear coding schemes for analog computations; a simple example is the use of log and antilog scaling units to perform analog multiplications [52]. A more sophisticated approach might attempt to beat the SNR limit by distributing a single signal on many wires, as is done in the digital case. See Section 6.1 for more discussion of this idea.

The relative efficiencies of analog and digital circuitry come from the algorithms implemented in the hardware, and are not tied directly to the hardware itself. The prefactors between various algorithms are determined by the detailed physics of the particular implementation technology, but the scaling laws are intrinsic to the algorithms. The ingenuity of the circuit engineer allows room for advantage to be taken in both areas: better hardware algorithms will have better scaling laws, and better use of the intrinsic device physics will give better scaling coefficients.

#### 2.3 Example: delays

Vittoz presented a detailed analysis of the theoretical power consumption limits of analog and digital filters in a scalable measure of "power per pole" [23].

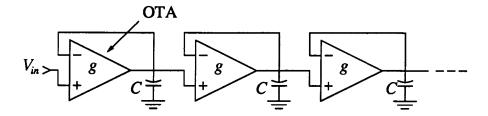

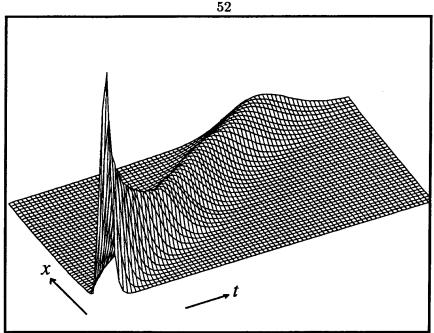

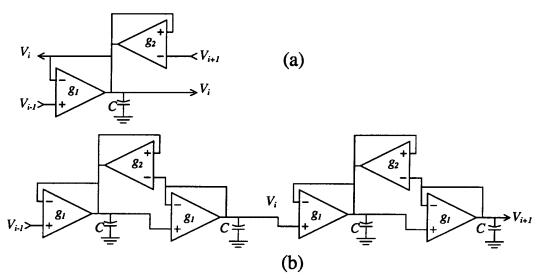

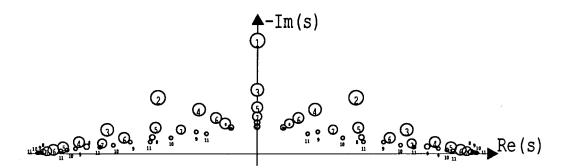

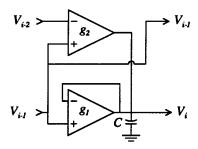

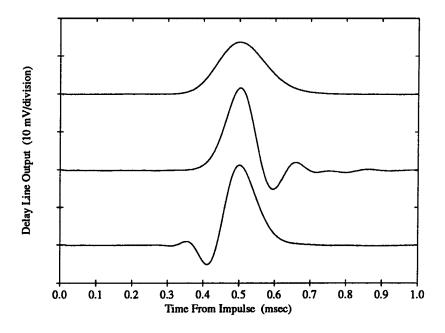

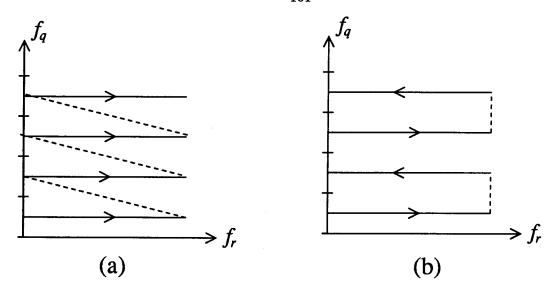

Table 2.2 lists several performance parameters of four types of delay lines: continuous—time, continuous—signal (denoted here by the abbreviation CTCS, these circuits are generally considered "analog"); continuous—time, discrete—signal (CTDS); discrete—time, continuous—signal (DTCS); discrete—time, discrete—signal (DTDS, a "digital shift register"). The CTCS line is built of operational transconductance amplifiers and capacitors (a technique often referred to in the literature as OTA—C) in a structure very similar to the silicon cochlea of Lyon and Mead [8]. The CTDS line is a chain of current—limited digital inverters, and is discussed at greater length in Section 3.2.2. The DTCS line is a chain of sample—and—hold sections. The DTDS line is a digital shift register.

Important measures of delay circuit performance are the area occupied, the power dissipated, the total delay from one end to the other, the bandwidth, and the resolution. From these measures, we can compute some standard figures of merit, such as delay-bandwidth product, information capacity, equivalent switching energy, and so on. Because of the different methods of constructing the delay lines, the basic performance measures will have different interdependencies for the different delay lines. Each will be considered in some detail.

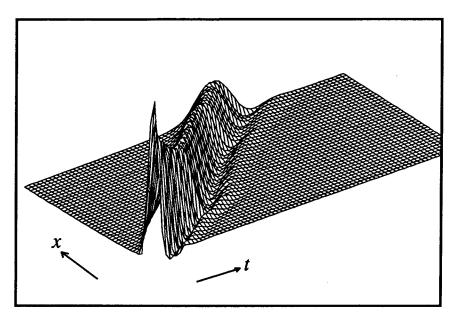

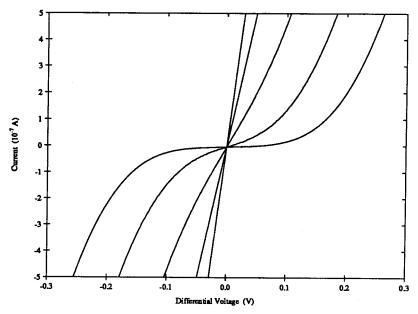

CTCS The CTCS delay line is constructed using OTA-C techniques, using Mead's wide-range OTA ([1], Chapter 5). Each stage of the line occupies an area of (152 × 62)  $\mu$ m<sup>2</sup>, for a total area of 367 536  $\mu$ m<sup>2</sup> for the 39 stages in the test circuit. The power dissipation of the CTCS delay line varies according to the bias currents of the OTAs. In the subthreshold range, the transconductance of an OTA is directly proportional to

the bias current, so there should be a linear relationship between the power dissipation and the bandwidth. Because of the linear filtering operation of each stage, the CTCS delay line should show a constant delay-bandwidth product, giving a linear inverse relationship between power dissipation and total delay. Experimentally, measurements from the CTCS delay line diagrammed in Figure 3.15 show that there is indeed a linear interdependence among power dissipation, bandwidth, and delay time, with coefficients as noted in Table 2.2. In the subthreshold range, the OTAs will operate correctly with signals up to 100 mV peak-to-peak, with a noise floor of about 1 mV.

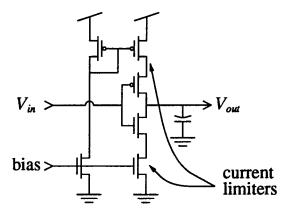

CTDS The CTDS delay line is constructed of a chain of circuits like that diagrammed in Figure 3.20. These delay cells are much like digital CMOS inverters with the addition of current-limiting devices to introduce a controllable transition delay. The CTDS circuit is discussed in more detail in Section 3.2.2. The CTDS delay circuit propagates binary signals in continuous time. The resolution of a single delay line is trivially R=2 distinct signal values. Each section of the line occupies an area of  $(145 \times 148) \, \mu \text{m}^2$ , for a total area of 579  $420 \, \mu \text{m}^2$  for the 27 stages of the test circuit. The power dissipation of the CTDS delay circuit diagrammed in Figure 3.20 is determined partly by the data flowing through it, and partly by the bias currents in the devices. A signal transition on the input costs a unit switching energy due to the capacitive charging of the transistor gates, regardless of the time required to effect the transition. The bias circuit wastes a steady-state current proportional to the current limit of the delay device. The gain stages cost more switching energy units, as well as wasting some current during switching, proportional to the switching transition period. The total power dissipation follows the relation

$$P_{total} = V_{dd}I_{ss} = V_{dd}\left[I_b + \frac{Af_d}{I_b}\right] . (2.5)$$

where  $A = 0.06 \,\mu\text{A}^2/\text{Hz}$ , and  $f_d$  is the instantaneous frequency of the incoming data stream (half the number of edges per second).

Again, we would expect a linear dependence of the maximum transition rate on the bias current, and a constant delay-bandwidth product. The bandwidth can be taken as half the maximum edge rate, by Nyquist's theorem. Experiments bear out this expectation, with the bandwidth varying as  $B \approx 4 \times 10^8 I_b$

DTCS The DTCS delay line is a chain of sample-and-hold sections. Each section occupies an area of  $(200 \times 113) \, \mu \text{m}^2$ , for a total area of 632 800  $\mu \text{m}^2$  for 28 stages. The power dissipation of the delay line has two sources: the clock generation circuitry and the buffer amplifiers. The clock generation circuitry is digital switching elements, with a power dissipation proportional to the sampling rate, while the buffer amplifiers are biased with constant current sources. The clocked portions of the circuit consume a current of  $I_{clock} = 1.2 f_s \, \text{nA}$  at  $V_{dd} = 5 \, \text{V}$ . The bandwidth of the DTCS delay line is determined by the sample rate at low sample rates, and by the transconductance of the buffer amplifiers at high sample rates. For any given bias current, the buffer amplifiers have a particular cutoff frequency. Measurements show that the buffer amplifiers must consume a supply current proportional to the cutoff frequency  $f_c$ :  $I_b = 0.8 f_c \, \text{nA}$ . The total current consumption is thus

$$I_{ss} = I_{clock} + I_b = 1.2 \times 10^{-9} f_s + 0.8 \times 10^{-9} f_c \text{ amperes}$$

(2.6)

The total delay is dependent on the sampling frequency, provided that the buffer amplifier bandwidth is not exceeded. For the 28 stages of sample-and-hold, the total delay is therefore  $28/f_s$ . The buffer amplifiers operate correctly over a range of about 4 V. Switching noise dominates the noise floor, and depends partly on the sampling frequency. Experiments show a switching noise component of  $V_n = 12.7 + 7.2 \times 10^{-5} f_s$  mV

rms, so the resolution is  $R = 4000/(12.7 + 7.2 \times 10^{-5} f_s)$ .

DTDS The DTDS delay line is a digital shift register. The register propagates binary dignals in discrete time, so its resolution is trivially R=2. Each unit of the register occupies an area of  $(50 \times 89) \, \mu \text{m}^2$ , for a total area of 178 000  $\mu \text{m}^2$  for 40 stages. The power dissipation of the shift register is strongly dependent on the data flowing through the register, as each bit transition costs a unit switching energy. In the simple case of a single bit propagating through the register, the switching energy was measured at 48 pJ for  $V_{dd}=5$  V. This measurement can be extended to the typical case of half of the register elements seeing transitions, for an estimated typical power dissipation of  $4.8f_s$  nW. The total delay through the register is dependent on the sample clock rate. Each bit moves one stage per clock cycle, so the total delay is  $40/f_s$ . The shift register propagates bits at a rate of  $f_s$ , which can reasonably be considered to be half the bandwidth of the register, by the Nyquist sampling theorem.

CCD Another type of DTCS delay line exists, in essentially the same technology. Transistor channels can be arranged to form a chain, generally known as a charge—coupled device (CCD). When the CCD gates are clocked with the proper waveform sequence, channel charge is transferred from one gate to the next along the chain. For a generic CMOS process, the charge transfer efficiency of a surface—channel CCD is fairly low, between 0.9990 and 0.9999, giving a total charge loss of a few percent along a chain of a length of 50. This means that the CCD delay line is good for about 7 bits. Except for input and output interface devices, a CCD delay line is a passive device. Some of the signal energy is dissipated in the channel resistance (as charge loss), and all other energy expenditure is in the clock circuitry. Therefore, we could possibly make the statement that a CCD delay line dissipates no energy, but, realistically, we must

include the clock dissipation in the calculations. For a unit gate area of  $400 \,\mu\text{m}^2$  in our  $2 \,\mu\text{m}$  CMOS technology, our hypothetical CCD delay line will consume an average supply current of about  $10^{-11} \, f_s$ . The numbers quoted in Table 2.2 for a CCD delay line are estimates, rather than experimental measurements.

A careful examination of the various delay lines reveals that they each have certain advantages. The continuous-signal lines manage to pack much more resolution into a single stage than do the discrete-signal lines. The continuous-time lines tend to have rather low total information capacity as compared to their discrete-time versions. The power dissipation of the CTCS line is virtually constant, independent of the data, while, at the other extreme, the power dissipation of the DTDS line is almost entirely data dependent. Clearly, the advantage does not belong squarely in any one of the four bins. The VLSA designer must carefully weigh the requirements of the task and choose the most suitable circuit technique.

Moreover, one can see that there are several examples of very different ways of using the same technology to accomplish essentially the same task. This variety of techniques was generated by the imaginations of various designers, and there may well be other possible methods. Creativity and imagination are important engineering tools.

```

CTCS

9 424 \, \mu m^2

unit area:

(2.4 \times 10^{-10}/I_b) seconds

unit delay:

(1.6 \times 10^{10} I_b) Hz

bandwidth:

100

resolution (R):

supply current:

I_b

CTDS

21\ 460\ \mu m^2

unit area:

1.1 \times 10^{-8}/I_b seconds

unit delay:

bandwidth:

3.73 \times 10^8 I_b Hz

resolution:

I_b + (6 \times 10^{-14} f_d / I_b) amperes

supply current:

DTCS:

22\ 600\ \mu m^2

unit area:

unit delay:

1/f_s

bandwidth:

\min\{f_s/2, 1.3 \times 10^9 I_b\} Hz

4\ 000/(13+7.2\times10^{-5}f_s) \le 308

resolution:

I_b + 1.2 \times 10^{-9} f_s amperes

supply current:

DTDS

4 450 \, \mu \text{m}^2

unit area:

1/f_s

unit delay:

bandwidth:

f_s/2

resolution:

2

9.6 \times 10^{-10} f_s amperes (average)

supply current:

CCD

400 \, \mu \text{m}^2

unit area:

1/f_s

unit delay:

bandwidth:

f_s/2

resolution:

100

10^{-11} f_s amperes (average)

supply current:

```

Table 2.2: **Delay line comparison:** four types of delay lines, corresponding to the four regions of Figure 2.1, are compared on the basis of several easily accessible performance measures: area, delay, bandwidth, resolution, and power supply current at 5 V. Standard figures of merit can be easily computed from these measures. Estimates of CCD delay line performance are also included.

## Papers used for DRAM sense amp data

W. M. Regitz, J. A. Karp

Three-Transistor-Cell 1024-Bit 500 ns MOS RAM

IEEE Journal of Solid-State Circuits, vol.SC-5, no.5, pp.181-186 October 1970.

R. A. Abbott, W. M. Regitz, J. A. Karp

A 4K MOS Dynamic Random-Access Memory

IEEE Journal of Solid-State Circuits, vol.SC-8, no.5, pp.292-298 October 1973

H. J. Boll, W. T. Lynch

Design of a High-Performance 1024-b Switched Capacitor p-Channel IGFET Memory Chip

IEEE Journal of Solid-State Circuits, vol.SC-8, no.5, pp.310-318 October 1973

C. N. Ahlquist, J. R. Breivogel, J. T. Koo, J. L. McCollum, W. G. Oldham, A. L. Renninger

A 16 384-Bit Dynamic RAM

IEEE Journal of Solid-State Circuits, vol.SC-11, no.5, pp.570-574 October 1976

K. Itoh, K. Shimohigashi, K. Chiba, K. Taniguchi, H. Kawamoto A High-Speed 16-kbit n-MOS Random-Access Memory

IEEE Journal of Solid-State Circuits, vol.SC-11, no.5, pp.585-590 October 1976

E. Arai, N. Ieda

A 64-kbit Dynamoc MOS RAM

IEEE Journal of Solid-State Circuits, vol.SC-13, no.3, pp.333-338 June 1978

T. Wada, O. Kudoh, M. Sakamoto, H. Yamanaka, K. Nakamura, M. Kamoshida A 64K × 1 Bit Dynamic ED-MOS RAM

IEEE Journal of Solid-State Circuits, vol.SC-13, no.5, pp.600-606 October 1978

T. Wada, M. Takada, S. Matsue, M. Kamoshida, S. Suzuki

A 150 ns, 150 mW 64K Dynamic MOS RAM

IEEE Journal of Solid-State Circuits, vol.SC-13, no.5, pp.607-611 October 1978

M. Kondo, T. Mano, F. Yanagawa, H. Kikuchi, T. Amazawa, K. Kiuchi, N. Ieda, H. Yoshimura

A High Speed Molybdenum Gate MOS RAM

IEEE Journal of Solid-State Circuits, vol.SC-13, no.5, pp.611-616 October 1978

K. Natori, M. Ogura, H. Iwai, K. Maeguchi, S. Taguchi A 64 kbit MOS Dynamic Random Access Memory IEEE Journal of Solid-State Circuits, vol.SC-14, no.2, pp.482-485 April 1979

- J. Y. Chan, J. J. Barnes, C. Y. Wang, J. M. deBlasi, M. R. Guidry A 100ns 5V Only 64K × 1 MOS Dynamic RAM *IEEE Journal of Solid-State Circuits*, vol.SC-15, no.5, pp.839-846 October 1980

- M. Taniguchi, T. Yoshihara, M. Yamada, K. Shimotori, T. Nakano, Y. Gamou Fully Boosted 64K Dynamic RAM with Automatic and Self-Refresh *IEEE Journal of Solid-State Circuits*, vol.SC-16, no.5, pp.492-498 October 1981

- C. A. Benevit, J. M. Cassard, K. J. Dimmler, A. C. Dumbri, M. G. Mound, F. J. Procyk, W. Rosenzweig, A. W. Yanof

A 256K Dynamic Random Access Memory

IEEE Journal of Solid-State Circuits, vol.SC-17, no.5, pp.857-862 October 1982

## Chapter 3

## Filters and Delays

Time-domain information processing is crucial to almost all engineering and control tasks. Filter theory has been developed in order to address this issue in its most common guise: separating a time-varying "signal" of interest from obscuring "noise" or "interference." The difference between a "filter" and some sort of "analog computer" is often one of intent and interpretation, rather than functionality. In this section, I will discuss two particularly useful analog building blocks: (1) continuous-time analog filters, and (2) continuous-time delay elements for both analog and digital signals.

### 3.1 CT filters

Continuous—time filters are indispensable blocks, even in a world dominated by digital signal processing. Most real—world signals originate as electrical analogs of continuously varying signals such as air or water pressure, flow rate, temperature, etc., and the end output quantities are also often continuous. Continuous—time filters are required at the interface between continuous—time and discrete—time signals, in order to prevent frequency aliasing. Continuous—time filters can also yield a substantial savings in circuit area and power cost, as discussed in section 2.3.

As a tool for understanding more general integrated filter circuits, I will analyze a

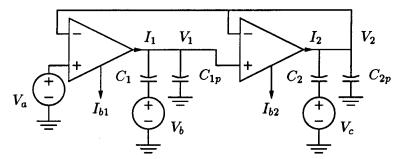

Figure 3.1: DIFF2 filter circuit: explicit capacitance  $C_1$  and parasitics  $C_{1p}$  and  $C_{2p}$  are included

particular filter in great detail. Parts of this section were also published in Caltech CNS Memo 12 (1991). The basic circuit design is from Mead and his research group [1], and my primary contribution in this section is the analysis and use of the circuit as a filter, and the extension of the filter analysis to a related four-transistor circuit.

#### 3.1.1 The DIFF2 filter

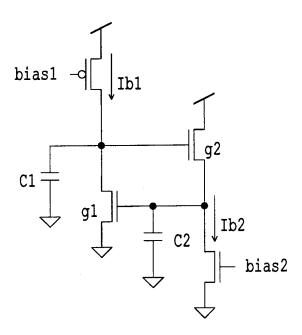

Mead's DIFF2 circuit ([1], pp.169-173) shows resonant behavior due to capacitance on the "output" node. This resonant behavior can be used for second-order filtering operations if the capacitance is explicitly designed into the circuit, as shown in Figure 3.1. This circuit contains the minimum number of components necessary to realize a second-order filter, although an additional active element may be added in order to de-stabilize the circuit [32].

The DIFF2 filter is a member of the general family of OTA-C filters (constructed of Operational Transconductance Amplifiers and Capacitors), which are particularly well-suited to integrated circuit realization of continuous-time filters, as they can be constructed solely of transistors and capacitors.

#### Simple linear analysis

A typical OTA has a transfer function somewhat like,

$$I_{out} = I_0 \tanh \left( \frac{\kappa \Lambda_T}{2} (V_+ - V_-) \right) \quad . \tag{3.1}$$

For sufficiently small differential input voltages, we can approximate the amplifier's transfer function with a linear function:

$$I_{out} = g_0 \left( V_+ - V_- \right) \quad , \tag{3.2}$$

where  $g_0 = \frac{\kappa \Lambda_T}{2} I_0$ .

Such an approximation allows us to do a very simple linear analysis of the DIFF2 filter circuit of Figure 3.1. The basic circuit equations are:

$$I_1 = g_1(V_a - V_2) = C_1(\dot{V}_1 - \dot{V}_b) + C_{1\nu}\dot{V}_1 \tag{3.3}$$

$$I_2 = g_2(V_1 - V_2) = C_2(\dot{V}_2 - \dot{V}_c) + C_{2p}\dot{V}_2$$

(3.4)

or, using Heaviside operational calculus,

$$I_1 = g_1(V_a - V_2) = sC_1(V_1 - V_b) + sC_{1p}V_1$$

(3.5)

$$I_2 = g_2(V_1 - V_2) = sC_2(V_2 - V_c) + sC_{2p}V_2 . (3.6)$$

Notice that I have included the parasitic capacitors  $C_{1p}$  and  $C_{2p}$  in the analysis. There are two reasons for this: first, these parasitics are unavoidably present in any real circuit; second, there are some interesting and potentially useful side effects due to their presence.

A straightforward derivation yields the following result:

$$V_1(s^2 + \tilde{\omega}_2 s + \tilde{\omega}_1 \tilde{\omega}_2) = \frac{C_1}{\tilde{C}_1} s V_b(s + \tilde{\omega}_2) + \tilde{\omega}_1 V_a(s + \tilde{\omega}_2) - \tilde{\omega}_1 \left(\frac{C_2}{\tilde{C}_2}\right) s V_c$$

(3.7)

$$V_2(s^2 + \tilde{\omega}_2 s + \tilde{\omega}_1 \tilde{\omega}_2) = \left(\frac{C_2}{\tilde{C}_2}\right) s^2 V_c + \tilde{\omega}_2 \left(\frac{C_1}{\tilde{C}_1}\right) s V_b + \tilde{\omega}_1 \tilde{\omega}_2 V_a \quad , \tag{3.8}$$

where the following symbols have been defined for brevity:

$$\tilde{C}_1 = C_1 + C_{1p}$$

$\tilde{C}_2 = C_2 + C_{2p}$   $\omega_1 = \frac{g_1}{C_1}$   $\tilde{\omega}_1 = \frac{g_1}{C_1}$   $\omega_2 = \frac{g_2}{C_2}$   $\tilde{\omega}_2 = \frac{g_2}{C_2}$ .

Notice that the forms and coefficients of the left-hand sides of both equations are identical. This is not surprising, since the circuit is the same in both cases, and it has a single resonant frequency and damping coefficient. These can be found by substitution into the canonical second-order ODE form:

$$V(s^2 + 2\xi\omega_0 s + \omega_0^2) = F(s)$$

(3.9)

and so we find

$$\omega_0 = \sqrt{\tilde{\omega}_1 \tilde{\omega}_2} \qquad \xi = \sqrt{\frac{\tilde{\omega}_2}{\tilde{\omega}_1}} \qquad \text{or,} \qquad Q = \frac{1}{2\xi} = \sqrt{\frac{\tilde{\omega}_1}{4\tilde{\omega}_2}} \quad .$$

(3.10)

An important feature to notice is that the damping coefficient  $\xi$  is positive for all achievable values of the circuit parameters. This means that this circuit should be unconditionally stable; we pursue a more detailed discussion of this issue in the detailed linear analysis section.

Various choices of the input nodes and a choice of either node 1 or node 2 as the output change the positions of the filter zeros and hence the overall behavior of the filter. It is possible to realize lowpass, bandpass, highpass, and bandstop characteristics with this circuit, merely by choosing the connections appropriately, so the DIFF2 circuit can be considered a general-purpose filter module.

Table 3.1 lists the possible voltage-in, voltage-out transfer function numerators for various configurations of the DIFF2 filter. The voltage-in, voltage-out transfer function for the filter in any configuration is of the form

$$H(s) = \frac{N(s)}{D(s)}$$

where  $D(s) = (s^2 + \tilde{\omega}_2 s + \tilde{\omega}_1 \tilde{\omega}_2)$

| input node(s)   | output | numerator $N(s)$                                                                                                                                                                   | comments |

|-----------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| $V_a$           | $V_2$  | $	ilde{\omega}_1	ilde{\omega}_2$                                                                                                                                                   | lowpass  |

| $V_b$           |        | $	ilde{\omega}_2\left(rac{C_1}{	ilde{C}_1} ight)s$                                                                                                                                | bandpass |

| $V_c$           | ]      | $\left(rac{C_2}{\tilde{C}_2} ight)s^2$                                                                                                                                            | highpass |

| $V_a, V_b$      |        | $	ilde{\omega}_2\left(rac{C_1}{	ilde{C}_1} ight)(s+\omega_1)$                                                                                                                     |          |

| $V_a, V_c$      |        | $\left(rac{C_2}{	ilde{C}_2} ight)\left(s^2+	ilde{\omega}_1\omega_2 ight)$                                                                                                         | bandstop |

| $V_b, V_c$      |        | $	ilde{\omega}_2\left(rac{C_1}{	ilde{C}_1} ight)(s+\omega_1)$                                                                                                                     |          |

| $V_a, V_b, V_c$ |        | $\left(rac{C_2}{	ilde{C}_2} ight)\left(s^2+\left(rac{C_1}{	ilde{C}_1} ight)\omega_2+	ilde{\omega}_1\omega_2 ight)$                                                               |          |

| $V_a$           | $V_1$  | $	ilde{\omega}_1  (s + 	ilde{\omega}_2)$                                                                                                                                           | DIFF2    |

| $V_b$           |        | $\left(rac{C_1}{	ilde{C}_1} ight)\left(s^2+	ilde{\omega}_2s ight)$                                                                                                                |          |

| $V_c$           |        | $-	ilde{\omega}_1\left(rac{C_2}{	ilde{C}_2} ight)s$                                                                                                                               | bandpass |

| $V_a, V_b$      |        | $\left(\frac{C_1}{\tilde{C}_1}\right)\left(s^2+\left(\tilde{\omega}_1+\tilde{\omega}_2\right)s+\omega_1\tilde{\omega}_2\right)$                                                    |          |

| $V_a,V_c$       |        | $\tilde{\omega}_1 \left( 1 + \left( \frac{C_2}{\tilde{C}_2} \right) \right) \left( s + \tilde{\omega}_2 \left( \frac{\tilde{C}_2}{C_{2p}} \right) \right)$                         |          |

| $V_b, V_c$      |        | $\left(rac{C_1}{	ilde{C}_1} ight)\left(s^2+\left(	ilde{\omega}_2-\omega_1\left(rac{C_2}{	ilde{C}_2} ight) ight)s ight)$                                                          | -        |

| $V_a, V_b, V_c$ |        | $\left(\frac{C_1}{\tilde{C}_1}\right)\left(s^2 + \left(\tilde{\omega}_2 + \omega_1\left(1 - \left(\frac{C_2}{\tilde{C}_2}\right)\right)\right)s + \omega_1\tilde{\omega}_2\right)$ |          |

Table 3.1: Table of Available Numerators: Numerators of transfer functions for different voltage-in, voltage-out configurations of the DIFF2 filter. Unspecified input nodes should be tied to appropriate constant voltages.

and N(s) is a polynomial from table 3.1. The DIFF2 filter is not quite a biquad filter, as zeros cannot be placed arbitrarily, but it can implement many useful filter functions.

There are, of course, more possibilities for using these circuits than just as *voltage*—mode devices, as currents can also be used as the signals.

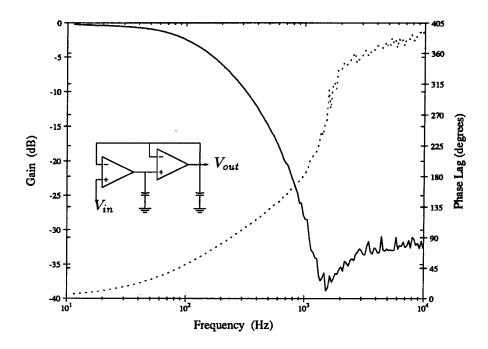

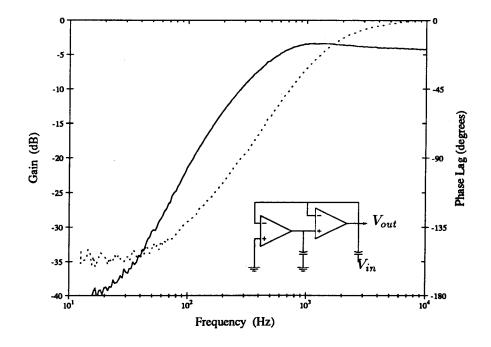

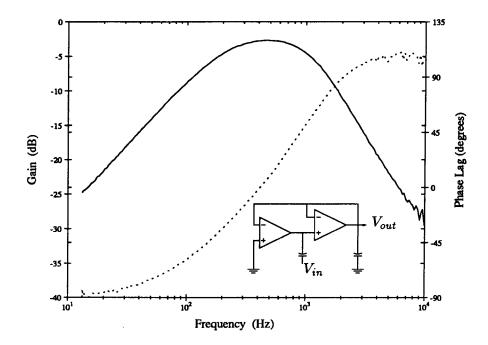

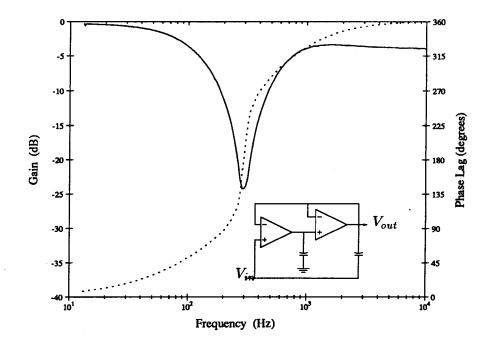

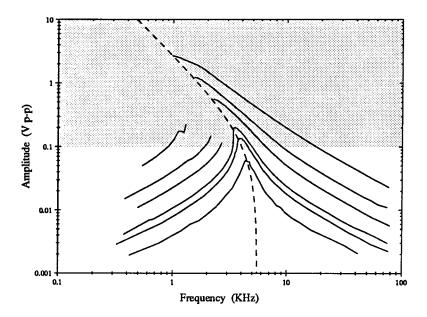

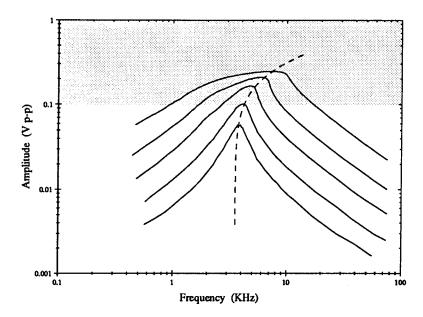

Figures 3.2 through 3.5 show data taken in the small-signal linear range of operation. In order to clearly show the various filter functions at this low amplitude, the noise floor of the data was reduced about 20 dB by averaging.

Figure 3.2: DIFF2 circuit in lowpass configuration

Figure 3.3: DIFF2 circuit in highpass configuration

Figure 3.4: DIFF2 circuit in bandpass configuration

Figure 3.5: DIFF2 circuit in bandstop configuration

All of the data curves show a slight distortion at the high-frequency end which can be attributed to the on-chip buffer amplifier's limited bandwidth. The low-pass filter data shows a rebound above 1 KHz; this may be due to stray feedthrough capacitance in various parts of the instrumentation circuitry. The significant difference in amplitude between the low- and high-frequency ends of the bandstop gain curve is due to the presence of the  $C_{2p}$  parasitic capacitance.

#### Detailed linear analysis

Typical transconductance amplifiers are moderately complicated circuits with several internal nodes, each of which has a small but finite parasitic capacitance to ground and to the other circuit nodes. These parasitics give rise to higher-order behavior in the filter circuit which can lead to instability under certain bias conditions. Standard texts on analog design, such as Gray and Meyer [28], have elaborate transistor models based on the standard small-signal linearization technique, taking account of many details in the behavior of a transistor. Such detail is necessary for designs that push the limits of the technology, but a simple zero-order model of a MOS transistor as a voltage-controlled current source will suffice to illustrate the problems one might encounter with internal amplifier nodes.

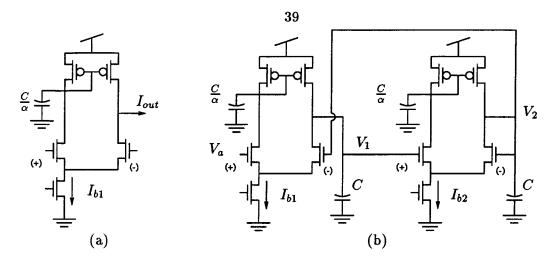

For simplicity, let's begin by using the simple OTA diagrammed in Figure 3.6(a); the DIFF2 is thus a fourth-order circuit, as diagrammed in Figure 3.6(b).

Substitution for the circuit parameters gives, after some work,

$$D(s) = s^4 + s^3 \left[ \alpha \tilde{\omega}_1 + (\alpha + \frac{1}{2}) \tilde{\omega}_2 \right] + s^2 \tilde{\omega}_2 \left[ (\alpha^2 + \frac{\alpha}{2} + \frac{1}{4}) \tilde{\omega}_1 + \alpha \tilde{\omega}_2 \right]$$

$$+ s \tilde{\omega}_1 \tilde{\omega}_2 \left[ \alpha (\alpha + \frac{1}{2}) \tilde{\omega}_2 + \frac{\alpha}{2} \tilde{\omega}_1 \right] + \alpha^2 \tilde{\omega}_1^2 \tilde{\omega}_2^2 , \qquad (3.11)$$

where  $\alpha$  is the ratio of the intended capacitance to the parasitic capacitance.

Figure 3.6: A parasitic capacitance in the DIFF2 circuit: (a) a simple OTA circuit (after Mead[1], chapter 5), and (b) a DIFF2 using this circuit

The key question for stability is whether the zeros of D have negative real parts. To address this, a possible approach is to use the Routh-Hurwitz method (see any control theory text, for example, [27] for more details on this method). The Routh-Hurwitz method gives the following criterion for stability:

$$c_1(g_1,\alpha) = \frac{a_1 a_2 a_3 - a_3^2 - a_1^2 a_4}{a_1 a_2 - a_3} > 0 \quad , \tag{3.12}$$

where the  $a_i$  are the coefficients of D:

$$D(s) = s4 + a1s3 + a2s2 + a3s + a4 . (3.13)$$

If we choose  $\tilde{\omega}_2 = 1$  for scale, then Equation (3.12) gives a function of  $\alpha$  and  $g_1$  that lets us know the regions in which the circuit is stable.

We have assumed two identical OTA-C sections (hence a single parameter  $\alpha$ ), and have made use of the fact that all the time constants associated with a single amplifier are related by the capacitor sizes, because our simple OTA has a single bias current.

It is clear that symbol-manipulation tools such as Mathematica can be very valuable in detailed analysis of even relatively small and simple circuits. Many commercial circuit simulators also perform numerical small-signal analyses, but symbolic analysis often benefits the designer by pointing out critical boundaries and sensitivities.