# Reliable Integration of Terascale Systems with Nanoscale Devices

Thesis by

Helia Naeimi

In Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

California Institute of Technology Pasadena, California

2008 (Submitted January 24, 2008)

© 2008

## Helia Naeimi All Rights Reserved

# Acknowledgements

I would like to thank my adviser, Professor André DeHon. He is a great person; one of those rare idealistic people that always believe in perfection. Learning more in the field of computer science was my first goal from coming to Caltech and working with a great scientist like André, and I have indeed learned many things from him and my other friends in IC group. However, I have learned many things from my adviser besides the technical matters. Specially during the unexpected challenge that our group experienced in the recent years.

I would like to thank my parents Bagher Naeimi and Azam Saatchi for helping me grow up free and boundless. They constantly encourage me to learn and grow. They thought me how to make my very first step and since then, they have supported me to make the steps, one little step at a time, in every aspects of my life specially my education. It was my mother who first thought me how to be a researcher, how to think freely , and her amazing power of thinking creatively has always been a great inspiration for me. I am truly indebt to them for having a vision to observe the nature and a mind to learn from her and respect her. My parents have a true passion for the nature. They always learn something new from the nature and respect her. They grow with any single bud and bloom in every single spring.

I would like to thank Amir Dana, my husband and my friend. who gives my life meaning and challenge. He has been a great support for me during my study at Caltech. From listening to many rounds of practice talks to bringing survival kits during long nights of deadlines to discussing a new idea or carrying heavy books, he was always there.

# Abstract

Nanotechnology design has attracted considerable attention in recent years and seems to be the technology for the future generation of the electronic devices, either as scaled and more restricted conventional lithographic technology [1], or as emerging sublithographic technologies, such as nanowires, carbon nanotubes, NDR (Negative Differential Resistance) devices, or other nanotechnology devices. Each of these technologies provides one or more design benefits including feature-size scaling, high ON–OFF ratios, and faster devices. However, all of these techniques share their most challenging design issue: *reliability*. Providing reliability is becoming constantly more challenging due to increases in both the device failure rate and system complexity. This work develops techniques that make achieving reliability in such systems feasible with practical area overhead and considerable improvement in area overhead and system reliability compared to related techniques.

Conventional reliability techniques focus on low defect and fault rates, i.e., single event upset (SEU). These techniques cannot simply be scaled to larger systems with more unreliable devices. If these techniques are directly applied to the high defect and fault rate of the nanotechnology regime, they suffer impractically high overhead, or they may not achieve the desired reliability. Our approach in this thesis exploits the following design patterns to achieve a considerable area reduction compared to related works and achieve high reliability:

(1) *Fine-grained reliability*: In this technique, the system is partitioned into fine– grained blocks, and the reliability is provided for each block. This technique is used to contain the area overhead and bound the impact on the throughput.

(2) Using alternative resources: This technique improves the design quality by

sparing other resources when system is tight on one resource. In our work we replace some of the spacial redundancies with temporal redundancy to limit the area overhead. We further improve the system throughput to limit the throughput cost as well.

(3) Defect pattern matching: With this techniques, the defective resources are located and the design is reconfigured considering the defect pattern of the chip. Then the design configuration is mapped to the chip. This technique isolates the defective resources and make use of most of defect free resources.

(4) *Global reliability*: This technique is used to unify the reliability techniques used in different parts of the system. When using one unified technique to protect the system, the area overhead provided to protect one resource can be reused to protect other resources as well.

In the present work, we report considerable improvement in the area overhead using the above techniques. We show that using *Fine-Grained Reliability*, *Alternative Resources*, and *Defect Pattern Matching*, high permanent defect rates (e.g., 10%) which is the result of imperfect manufacturing can be tolerated with moderate area overhead (about 30% on average for typical designs). Again *Using Alternative Resources* and *Fine-Grained Reliability* improve the area overhead of the transient fault-tolerant designs by close to an order of magnitude compared to recent reliable works. Finally we report a fully reliable memory system that employs a *Global Reliability* scheme to tolerate permanent defects and transient faults, both in the memory and in the supporting logic and still achieves 100 Gbit/cm<sup>2</sup> density for fault rate of  $10^{-18}$  errors per bit per cycle and 10% junction defect rate.

# Contents

| A | ckno  | wledge | ements                                                   | iii  |  |  |  |

|---|-------|--------|----------------------------------------------------------|------|--|--|--|

| A | bstra | act    |                                                          | iv   |  |  |  |

| 1 | Int   | roduct | ion                                                      | 1    |  |  |  |

|   | 1.1   | Defect | t-Tolerant Approaches                                    | . 4  |  |  |  |

|   | 1.2   | Fault- | ult-Tolerant Approaches                                  |      |  |  |  |

| 2 | Bac   | ckgrou | nd                                                       | 9    |  |  |  |

|   | 2.1   | Reliat | bility in Nanoscale Designs                              | . 9  |  |  |  |

|   |       | 2.1.1  | Permanent Defects                                        | . 10 |  |  |  |

|   |       | 2.1.2  | Transient Faults                                         | . 11 |  |  |  |

|   |       |        | 2.1.2.1 High-Energy Particles                            | . 12 |  |  |  |

|   |       |        | 2.1.2.2 Shot Noise                                       | . 13 |  |  |  |

|   |       | 2.1.3  | Related Reliable Designs                                 | . 15 |  |  |  |

|   |       |        | 2.1.3.1 Defect-Tolerant Works                            | . 15 |  |  |  |

|   |       |        | 2.1.3.2 Fault-Tolerant Works                             | . 18 |  |  |  |

|   |       |        | 2.1.3.3 Majority Multiplexing for Nanotechnology Designs | . 19 |  |  |  |

|   | 2.2   | Subst  | rates                                                    | . 23 |  |  |  |

|   |       | 2.2.1  | Wires                                                    | . 23 |  |  |  |

|   |       |        | 2.2.1.1 Nanowires                                        | . 23 |  |  |  |

|   |       |        | 2.2.1.2 Nanotubes                                        | . 24 |  |  |  |

|   |       | 2.2.2  | Field-Effect Controllable Cross-Point                    | . 25 |  |  |  |

|   |       | 2.2.3  | Programmable Cross-Point                                 | . 25 |  |  |  |

|   | 2.3 | NanoPLA                                                      | 26 |

|---|-----|--------------------------------------------------------------|----|

|   |     | 2.3.1 Programmable Crossbar Array                            | 26 |

|   |     | 2.3.2 Restoration and Inversion Array                        | 27 |

|   |     | 2.3.3 Lithographic to Sublithographic Decoder                | 29 |

|   |     | 2.3.3.1 Nanowire Codes                                       | 31 |

|   |     | 2.3.4 Architecture                                           | 32 |

|   | 2.4 | Nanomemory Architectures                                     | 34 |

|   | 2.5 | More Nanotechnology-Based Architecture                       | 37 |

| 3 | Cos | t of Ignorance and Cost of Knowledge                         | 39 |

|   | 3.1 | Cost of Ignorance in Interconnect                            | 41 |

|   |     | 3.1.1 Ignorant-Based Interconnect Defect-Tolerant Scheme     | 42 |

|   |     | 3.1.2 Knowledge-Based Interconnect Defect-Tolerant Scheme    | 46 |

|   | 3.2 | Cost of Ignorance in Logic                                   | 47 |

|   | 3.3 | Cost of Knowledge                                            | 49 |

|   |     | 3.3.1 NanoPLA Test and Defect Localization                   | 50 |

|   | 3.4 | Summary                                                      | 52 |

| 4 | Per | manent Defect-Tolerant Design Using Reconfiguration          | 54 |

|   | 4.1 | Tolerating Defective Wires                                   | 56 |

|   | 4.2 | Tolerating Defective Cross-Points                            | 58 |

|   |     | 4.2.1 Algorithms                                             | 60 |

|   |     | 4.2.2 Fanin Bounding                                         | 61 |

|   |     | 4.2.3 Guaranteeing Sparseness during Mapping                 | 62 |

|   |     | 4.2.4 Interconnect Nanowire Integration with Logic Resources | 63 |

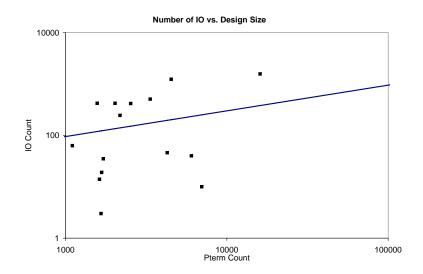

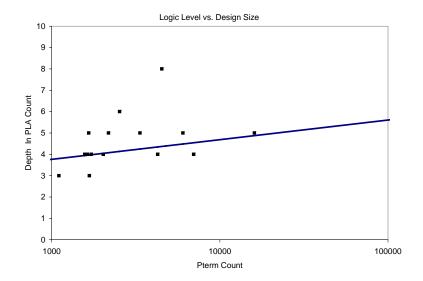

|   | 4.3 | Experimental Results                                         | 64 |

|   | 4.4 | NanoPLA Block Sparing                                        | 66 |

|   | 4.5 | Summary                                                      | 67 |

| 5 | Tra | nsient Fault-Tolerant Design with Rollback Technique         | 68 |

|   | 5.1 | Design Structure                                             | 68 |

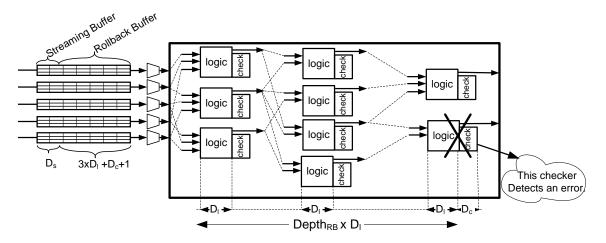

|   |     | 5.1.1  | Detection Block                                         | 70  |

|---|-----|--------|---------------------------------------------------------|-----|

|   |     | 5.1.2  | Rollback Block                                          | 72  |

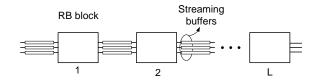

|   |     | 5.1.3  | Streaming Buffer                                        | 74  |

|   |     |        | 5.1.3.1 Reliable Buffered Interconnect                  | 75  |

|   |     | 5.1.4  | Block Size                                              | 77  |

|   | 5.2 | Nanoł  | PLA Implementation                                      | 79  |

|   |     | 5.2.1  | Detection and Rollback Block                            | 80  |

|   |     | 5.2.2  | Buffer Connection                                       | 82  |

|   | 5.3 | Reliat | oility and Area Analysis                                | 82  |

|   |     | 5.3.1  | Error Probability of a Detection Block                  | 84  |

|   |     | 5.3.2  | Undetected Error Probability of an RB Block             | 86  |

|   |     | 5.3.3  | Buffered Connection Reliability                         | 86  |

|   |     | 5.3.4  | Undetected Error Probability of the Complete System     | 87  |

|   |     | 5.3.5  | Redundancy Analysis                                     | 88  |

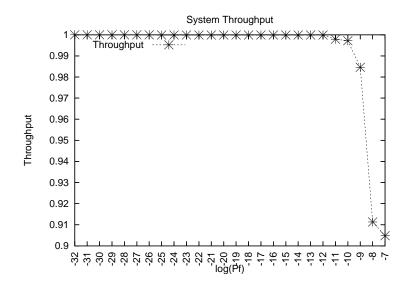

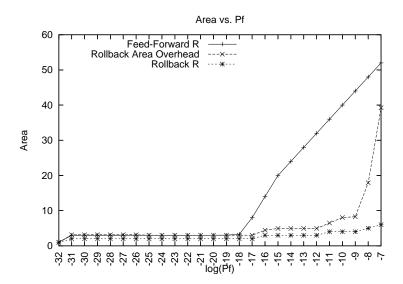

|   | 5.4 | Simula | ation and Comparison                                    | 90  |

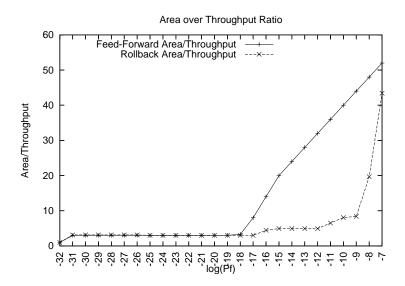

|   |     | 5.4.1  | Area and Throughput Simulation Results                  | 94  |

|   | 5.5 | Summ   | nary                                                    | 98  |

| 6 | Def | ect an | d Fault-Tolerant Nanomemory Design                      | 100 |

|   | 6.1 | Introd | luction and Motivation                                  | 100 |

|   | 6.2 | Relate | ed Works                                                | 102 |

|   | 6.3 | Syster | n Overview                                              | 103 |

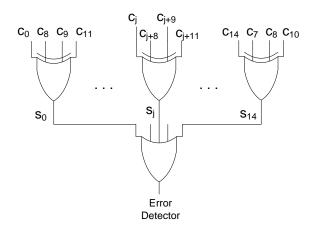

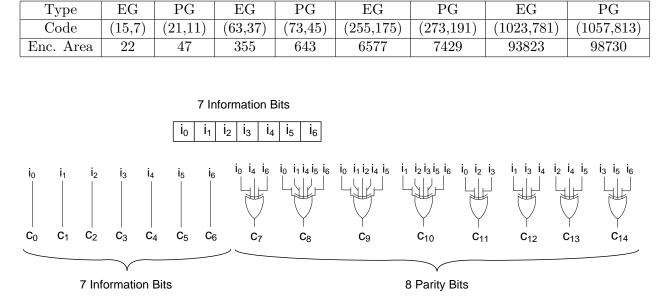

|   | 6.4 | ECCs   | with Fault Secure Detector                              | 107 |

|   |     | 6.4.1  | Error-Correcting Code Reviews                           | 107 |

|   |     | 6.4.2  | FSD-ECC Definition                                      | 109 |

|   | 6.5 | FSD-H  | ECC Example: Euclidean Geometry and Projective Geometry |     |

|   |     | Codes  | · · · · · · · · · · · · · · · · · · ·                   | 110 |

|   |     | 6.5.1  | Euclidean Geometry Code Review                          | 110 |

|   |     | 6.5.2  | Projective Geometry Code Review                         | 112 |

|   |     | 6.5.3  | FSD-ECC Proof for EG-LDPC and PG-LDPC                   | 113 |

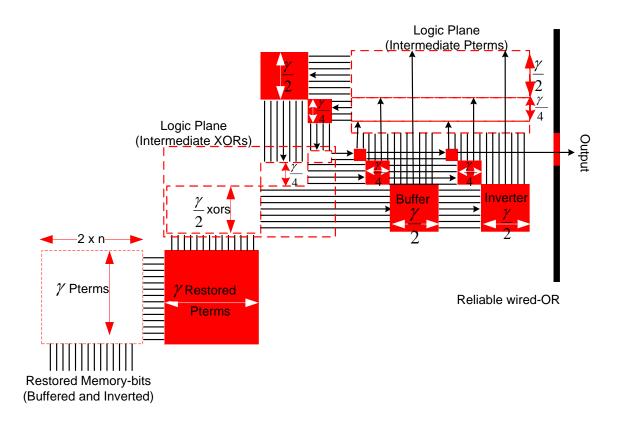

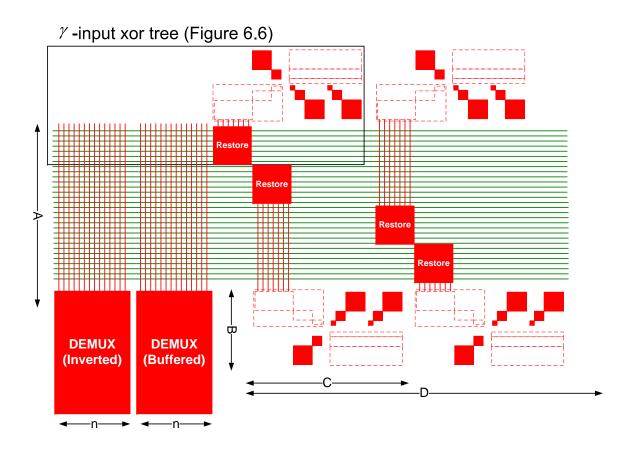

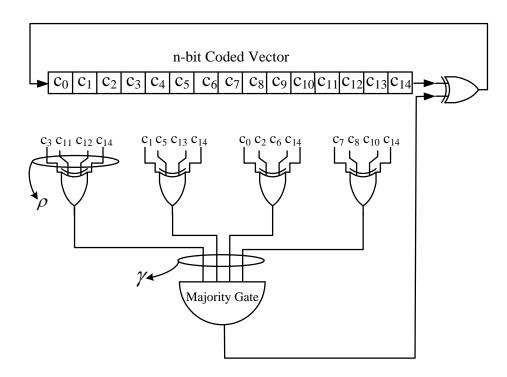

|        | 6.6                               | Design                                                                      | n Structure                                              | 114                                                  |

|--------|-----------------------------------|-----------------------------------------------------------------------------|----------------------------------------------------------|------------------------------------------------------|

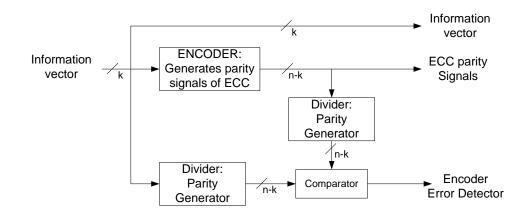

|        |                                   | 6.6.1                                                                       | Fault Secure Detector                                    | 114                                                  |

|        |                                   | 6.6.2                                                                       | Encoder                                                  | 116                                                  |

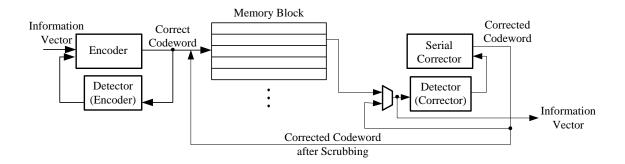

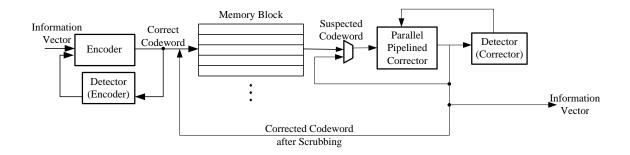

|        |                                   | 6.6.3                                                                       | Corrector                                                | 119                                                  |

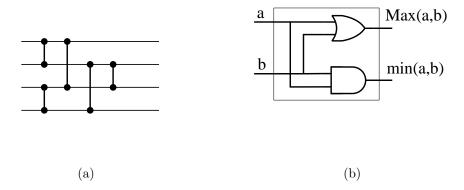

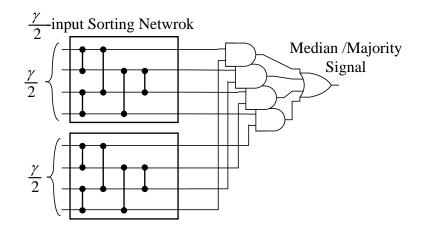

|        |                                   |                                                                             | 6.6.3.1 Majority Implementation                          | 123                                                  |

|        |                                   | 6.6.4                                                                       | Banked Memory                                            | 126                                                  |

|        |                                   | 6.6.5                                                                       | Nanoscale Demultiplexer                                  | 128                                                  |

|        | 6.7                               | Reliat                                                                      | pility Analysis                                          | 132                                                  |

|        |                                   | 6.7.1                                                                       | Analysis                                                 | 133                                                  |

|        |                                   | 6.7.2                                                                       | The Impact of Providing Reliability for Supporting Logic | 136                                                  |

|        | 6.8                               | Tolera                                                                      | ting Permanent Defect in Memory Cells                    | 138                                                  |

|        | 6.9                               | Area a                                                                      | and Performance Analysis and Results                     | 140                                                  |

|        | 6.10                              | Summ                                                                        | ary                                                      | 149                                                  |

|        |                                   |                                                                             |                                                          |                                                      |

| 7      | Sun                               | nmary                                                                       |                                                          | 150                                                  |

| 7<br>8 |                                   | nmary<br>ure W                                                              | ork:                                                     | 150                                                  |

|        | Fut                               | ure W                                                                       | ork:<br>C to Protect Logic Circuit                       | 150<br>153                                           |

|        | Fut                               | ure W                                                                       |                                                          |                                                      |

|        | Fut<br>Usi                        | ure Wang EC<br>Code                                                         | C to Protect Logic Circuit                               | 153                                                  |

|        | Fut<br>Usin<br>8.1                | ure Wo<br>ng EC<br>Code<br>Rando                                            | <b>C to Protect Logic Circuit</b><br>Selection Criteria  | <b>153</b><br>154                                    |

|        | Fut<br>Usin<br>8.1<br>8.2         | ure Wo<br>ng EC<br>Code<br>Rando                                            | C to Protect Logic Circuit<br>Selection Criteria         | <b>153</b><br>154<br>156                             |

|        | Fut<br>Usin<br>8.1<br>8.2         | ure Wo<br>ng EC<br>Code<br>Rando<br>Integr                                  | C to Protect Logic Circuit Selection Criteria            | <b>153</b><br>154<br>156<br>159                      |

|        | Fut<br>Usin<br>8.1<br>8.2         | ure Wang EC<br>Code<br>Rando<br>Integr<br>8.3.1                             | C to Protect Logic Circuit Selection Criteria            | <b>153</b><br>154<br>156<br>159<br>159               |

|        | Fut<br>Usin<br>8.1<br>8.2         | ure Wang EC<br>Code<br>Rando<br>Integr<br>8.3.1<br>8.3.2<br>8.3.3           | C to Protect Logic Circuit Selection Criteria            | <b>153</b><br>154<br>156<br>159<br>159<br>160        |

|        | Fut:<br>Usin<br>8.1<br>8.2<br>8.3 | ure Wang EC<br>Code<br>Rando<br>Integr<br>8.3.1<br>8.3.2<br>8.3.3<br>Prelin | C to Protect Logic Circuit Selection Criteria            | <b>153</b><br>154<br>156<br>159<br>159<br>160<br>161 |

# Chapter 1 Introduction

This thesis presents reliability techniques that make designing in sublithographic and nanometer scale practically feasible.

Considerable amount of research and work is devoted to continue feature size scaling and also invent new nanoscale electronic devices that can potentially replace the conventional lithpgraphic–based designs. Scaling the device feature size provides faster, denser, and consequently more powerful system that can run at higher speeds. In some of emerging technologies with high ON–OFF ratios it is also expected to bound power consumption by cutting off the leakage power. These improvements in area, performance, and power consumption, bring us technical challenges of their own. One of the main challenges (that is the subject of study in this work) is *reliability*. It is expected that devices become less reliable in smaller feature sizes and experience both more permanent defects due to the imperfect manufacturing process and more transient faults due to the effect of noise. Providing reliability is becoming constantly more challenging due to increase in both the device failure rate and system complexity up to the point that the conventional techniques will not be efficient enough or even capable of tolerating these error rates and complexity for the future generation systems.

This thesis presents practical techniques with limited area overhead to achieve reliable systems. To implement such a reliable system we exploit these new design patterns for reliability:

• Fine-grained reliability: This technique is used to limit the area overhead and

bound the impact on the throughput. When the error rate is high, the system must be partitioned into fine-grained block size, where the errors strike in smaller number. Protecting blocks with few errors requires less area overhead.

- Using alternative resources: With this technique, we can shift some of the redundancy from area domain to time domain to limit the area overhead. The time redundancy can then be reduced with some improvement techniques shown in chapter 3 and chapter 5.

- Defect pattern matching: This technique is used to maximize resource utilization, and make use of almost all the defect free resources, isolating defective ones. In this technique the design configuration is restructured to match the defect pattern of the chip.

- *Global reliability*: When using one unified technique to protect the system, the area overhead provided to protect one resource can be reused to protect other resources as well. An instance of this technique, is using the same Error-Correcting Codes (ECCs) to protect against transient faults and permanent defects. With this technique the redundancy in the code will be used more efficiently to protect both errors. Another example is protecting the memory and its supporting logic (e.g., detector circuit), with single ECC.

Before going into the application of these design patterns in our reliable techniques, we review the sources of unreliability. The sources of failure are divided into two main categories, by the nature of the sources and their impacts on the system:

- 1. Permanent defects

- 2. Transient faults

*Permanent defects*: As the result of imperfect fabrication process, devices may have variation in shape and size. When the device structure is very different from the designed structure, the device will not perform as intended and will make a permanent defect. The probability that a node is defective is called the defect rate. These defects could be of the form of a broken interconnect or junction because of lack of deposited molecules, or a too-high resistance interconnect due to lack of proper number of doping atoms, or a misplaced connection between devices because of extra molecule deposition.

In general the feature size scaling reduces control over the fabrication process which result in higher defect rates. Even for well-studied and largely manufactured conventional lithographic systems, the technology is facing reliability challenges. It is expected that Design Rules will become more restricted and require more regular design structure to bound the rate of manufacturing defects [2]. Furthermore, circuit designers can no longer design simply by technology design rules and expect a functional, let alone a scalable design. Designers must know when to use more relaxed rules and not simply relax the rules on the entire design, which negates physical scaling [3]. For emerging nano-technologies the defect rate is even higher due to the small feature size and bottom-up nature of the design. For example, imprint lithography, which provides one of the most reliable nanowire fabrication techniques, is reported to have 15% defective wires [4]. Although defect rate for emerging technologies is expected to decrease once the technologies are more mature, due to the nature of the fabrication process it is still expected to be high [5][4].

Transient faults: When a node in the system loses its effective charge due to ionized particle hit or various source of noises, it may cause the value of a node to be flipped in the circuit. However, the error does not permanently change the circuit, and it only generates a faulty bit value at the node that can last for one or few cycles. The transient fault rate is the probability that a single node loses its correct value during one clock cycle. Feature-size scaling, faster clock cycles and lower power designs increase the transient fault rate. Feature-size scaling and voltage level reduction shrinks the amount of critical charges holding logical state on each node; this in turn makes each node more susceptible to transient faults, e.g., an ionized particle strike has higher likelihood of being fatal as the critical charge is reduced in a node [6], which may cause a glitch or bit-flip. Furthermore operating at higher clock frequency increases the probability that a glitch in the signal is latched and propagated as an erroneous value throughout the circuit.

In the rest of this chapter, we review our defect- and fault-tolerant techniques to protect nanotechnology systems against the sources of unreliability explained above.

## **1.1** Defect-Tolerant Approaches

Traditionally chips were tested and any defective chip would be discarded. However, as the device defect rate increases and the systems become larger, the probability of having a perfect chip will become unreasonably low and removing all chips with any defective node will dramatically decrease the system yield. Therefore, currently in large and regular systems (e.g., memory or PLA), the system is tested and part of the system that is defective is isolated and the rest of the chip will be functional. For example, in memory systems, a row or a column that contains a defective cell will be burnt-out and the rest of the system performs correctly [7][8]. Tolerating a few defective rows or columns in the system increases the system yield. However, as the defect rate increases the probability of having even a single defect free row will become very slim. For example, in a NanoPLA block that contains a  $100 \times 100$ programmable devices and a device defect rate of 10%, the probability that a row of 100 devices is perfect is about  $(0.90)^{100} \approx 2 \times 10^{-5}$ , which makes it very unlikely that there will even be a single perfect row in a block (about 0.2%). Therefore, in order to keep the system yield high and make use of a defective chip with reasonable area cost, one must use a more *Fine-Grained* defect-tolerant technique, which tolerates defects at the device level. We have to make use of the defect free devices on even the nonperfect rows that also contain defective devices. Therefore, we use a *Fine*-Grained Defect Pattern Matching technique, which makes use of almost all the defect free devices in the system, although they belong to a defective part. In this technique the defect pattern of the chip is extracted and then the design configuration will be restructured to be matched to the defect pattern of the system. The system will be configured by this matching design configuration.

This technique requires postfabrication configurability which can be achieved with

various emerging technology devices, e.g., [2]catenane-based molecule [9], mechanical nanotube switch [10] or conventional programmable devices like SRAM-based reprogrammable switches, floating gate transistors, or fuses. The system also requires the appropriate hardware to test and locate defects in the chip.

Defect Pattern Matching is the main focus of chapter 4. In this chapter the defect pattern matching problem is modeled by a graph, and a matching algorithm with low complexity is proposed. Chapter 4 illustrates that the Fine-Grained Matching technique can tolerate 10% defect in the wires and another 10% defect in the programmable devices, in less than 3-fold area for the worst-case design. In contrast, techniques that are not based on fine-grained matching, require larger area overhead; e.g., Gate Multiplexing requires 100-fold area to tolerate up to a  $3 \times 10^{-3}$  device defect rate [11]. The matching technique is feasible since the defect pattern is static and fixed; and once the defect pattern is discovered, it can be used to configure the system.

chapter 3, *Cost of ignorance and cost of knowledge*, quantifies the benefits of exploiting the static defect map with methods like Fine–Grained Matching from area overhead perspective. It illustrates the overhead reduction achieved by exploiting this knowledge compared to the impact of ignoring it. We further introduce the technique to detect permanent defects in a system and discover the defect configuration pattern. The cost of defect pattern extraction is also presented and contrasted with the design costs associated with ignoring this knowledge.

## **1.2** Fault-Tolerant Approaches

Conventional fault-tolerant systems target Single Event Upsets (SEUs). However, due to the increase in the fault rate and system complexity this is not a valid assumption for future systems. For example, in a system with  $10^{12}$  susceptible nodes and fault rate of  $P_f = 10^{-7}$  per node per cycle, the system fails every cycle and the number of failures in the system is about 100,000 errors per cycle in the average which is many more than single failure. Therefore, the traditional system-level SEU tolerant techniques can not provide adequate reliability. When large number of errors occur in the system it is hard to detect the errors. To be able to detect the large number of errors in the system, one must focus on *Fine-Grained* block sizes, where errors occur in smaller number and can be detected more easily with less area overhead.

To detect errors in a block, the simplest way is to duplicate the block and compare the outputs, or to triplicate and perform the majority to actually correct the error. When using replication, the amount of replication factor grows super-linearly as the unit block size under detection and correction grows. Therefore, it seems that using Fine-Grained block size, minimizes the replication factor. Chapter 2 explains this fact in more detail. However, there is a constant area overhead associated with each block that grows with the number of blocks in the system. Therefore, there is an optimum block size that minimizes the total area cost (more detail will be shown in chapter 5). The replication technique is shown not to be the most efficient technique in communication coding theory. However, in the context of combinational logic it is not clear if other complex coding technique can outperform the simple replication scheme.

Furthermore, using only area redundancy to achieve the reliability may increase the area overhead dramatically. It is important to consider *Using Alternative Resources*, e.g., time redundancy, to bound the area overhead. One way of using time redundancy is to repeat the operation to generate a correct result, once an error is detected. The benefits of exploiting time redundancy is that we can only detect errors of a block in area domain and correct it in time domain which reduces the area overhead because the error detection circuit takes less area than error correction circuit (more detail will be shown in chapter 5).

In chapter 5 we suggest a *Fine-Grained Rollback* technique to tolerate high fault rates in a complex system. The *Rollback* technique is essentially detect-and-repeat; i.e., the outputs of the blocks are checked and once an error is detected in a block output, the operation of the block is repeated to generates the correct output. This technique exploits the *Fine-Granularity* error detection as well as *Using Alternative Resources* (time redundancy). In chapter 5 we show that the fault-tolerant system protected with rollback technique will have a more compact, implementation (up to six times less area) compared to a *Feed-Forward* technique, which is mostly used in recent nanotechnology fault-tolerant design in the form of Gate-Multiplexing. *Feed-Forward* techniques correct potential errors with enough information redundancy without requiring recomputations. Furthermore, since in most of the cycles each block runs error free and errors are detected with low frequency, the impact of the rollback technique on the system performance is minimal.

As mentioned above, in our Fine-Grained Rollback design, we use replication to detect errors. The area overhead of this technique can be greatly improved by using a more efficient error detection technique. Error-correcting codes tend to be more efficient for error detection and correction of individual bits; as is the case for data transmission and data storage. However, ECC does not necessarily performs better than replication for protecting arbitrary combinational logic. A potential future work to this thesis would be to find a more efficient error detection and correction technique compared to replication, to further improve the area overhead of our *Fine-Grained Rollback* technique (chapter 8).

In fact, we have solved this problem for a subclass of combination logic circuits: encoder, corrector, and detector circuits [12]. Conventionally, only memory bits were protection against transient faults, however, as the combinational logic are becoming more susceptible to faults, the supporting logic of the memory system must also be protected against faults. Here we can use our fault-tolerant encoder, corrector, and detector circuit to satisfy this demand. In chapter 6, we define a new restriction on error-correcting codes, that guarantees *Fault-Secure* Detector circuit. The *Fault-Secure* detector can detect any error in the received code-vector, despite having faults in the detector circuitry. This is a breakthrough in fault-tolerant design, since the fault-tolerant capability of the detector is achieved by exploiting the structure of the design and using the redundancy already available in the circuit, compared to the traditional approach where the extra circuitry has to be added to the circuit under protection. In chapter 6, we also present a *Global Reliability* technique that protects memory cells and supporting logic all in one-shot, and also uses a unified technique to tolerate permanent defect and transient fault together. We have shown codes that can tolerate fault rate of up to  $10^{-18}$  faults/bit/cycle and defect rate of 1% and still achieve memory density of 100 Gbit/cm<sup>2</sup>. Codes with higher error-correction capability can also be used to tolerate higher fault and defect rates.

All of the above techniques are general enough that they can be applied to any architecture and device substrate. In order to perform a detail analysis of the defect and fault-tolerant technique we analyzed the implementation of the above techniques on NanoPLA [13] and Nanomemory [14] architecture models. Chapter 2 reviews NanoPLA and Nanomemory architectures along with other nanotechnology based architecture models. This chapter also reviews some of the emerging technology devices and substrates.

In summary in this work we design a reliable system for nanotechnology designs, where the conventional techniques of tolerating SEU would not suffice due to high defect and fault rates and large system integration. We present approaches that achieve high reliability with practical area overhead for nanotechnology system.

# Chapter 2 Background

Most of the defect- and fault-tolerant schemes for conventional designs assume Single Event Upset, SEU. This assumption is valid when the error rate is low enough that with very high probability only single error occurs in the system. However, due to the certain decline in the device reliability this assumption may not be valid for future designs. In this chapter, we review some sources of defect and fault and review some of the related works. We illustrate the reasons why we believe the future generations of the electronic systems must have a more robust defect- and fault-tolerant designs.

To analyze the details of our proposed reliable designs, we implement these techniques on two nanowire-based architectures, *NanoPLA* and *Nanomemory*. The second part of this chapter reviews these two architectures and the devices and substrate model that they are built on.

## 2.1 Reliability in Nanoscale Designs

Chemists have successfully shown fabricating nanoscale devices that are below 10 nm wide. At this scale devices are composed of only tens of atoms. We know that atoms and molecules have statistical behavior and we can only control the statistical behavior of these particles. When the devices are made of thousands of atoms and molecules, the shape and the behavior of the devices follow the statistical prediction, almost all the times. However, at the scale of devices with tens of atoms and molecules, the variation in the device shape and behavior will be more visible and at

higher rate.

The variation in shape will cause permanent defect, and the variation in behavior will cause noise and transient fault consequently. Sources of defect and fault will be explained in more detail in the following section.

#### 2.1.1 Permanent Defects

The statistical structure of the devices will results in the following categories of defects in the system.

- Nanowires may break along their axis during assembly. The integrity of each nanowire depends on about 100 atoms in each radial cross-section and the lack of some atoms or atomic bonds may result in a break or high resistance nanowire.

- Nanowire to lithographic scale wire junctions depend on a small number of atomic scale bounds which are statistical in nature and subject to variation.

- Programmable device located between crossed nanowires will be composed of only tens of programmable molecules. The lack of functional molecules results in a high resistance device which is no longer programmable.

- Statistical doping of nanowires may lead to high variation among nanowires. If the doping location or density is sufficiently different from the designed device, a nanowire current may not be controlable or the wire may not conduct properly.

In the above list, we particularly gathered the defects that are related to nanowirebased architectures e.g., NanoPLA and Nanomemory. At this scale, we expect wires and devices to be defective in the 1% - 10% range.

However, since these technologies has not been mass produced and are still under active research, not many device defect rates has been reported. Some of the reported defect rates are given next. For example, an array of 250 nanowire fabrication is reported in [15], the nanowires has width of 100 nm and can be spaced 100 nm apart. The work in [15] reports 95% of the wires measured had good contacts. Another work, reported fabrication of  $6 \times 6$  nanowire crossbar with 40 nm wide nanowires [16]. They reported that 85% of cross-point junctions measured were usable. Both of these are early experiments and we expect the yield rates to improve. However, based on the physical phenomena involved, we anticipate the defect rates will be closer to the few percent range which is quite higher than the defect rates of conventional lithographic processing.

#### 2.1.2 Transient Faults

A transient fault is an event that lasts for about one cycle. If a charge disturbance on a circuit node is smaller than the noise margin, the circuit will continue to operate properly. Otherwise, the disturbed voltage may be interpreted as the opposite logic state and the circuit will malfunction. A transient fault on any node has a finite probability of causing a glitch. There is a difference in the response of static circuits and actively clocked circuits. In a static circuits like memory, a glitch on a node may cause a bit flip. In actively clocked circuits, the glitch may propagate to an input of a sequential cell, get latched as a wrong value, and affect the machine operation. In precharged combinational circuits, a glitch on a node if happens after the precharge phase, gets latched and cause an erroneous signal that can propagate through the system.

However, many transient faults will not be latched. Some of the latched data may not be relevant to machine operation and there will be no perceivable error in the program operation. Hence, the effective error rate of a large combinational circuit needs to be derated. Three types of derating are applied to a typical circuit for calculating its error rate [17].

• Logical masking: If the transient fault strike happens on an input of a 2-input NAND gate, but one of the other inputs is 0, the strike will be completely masked and the output will be unchanged, i.e., this particle strike will not cause a soft error. In order for an error to propagate, there must be a sensitized path from the input to the output.

- Temporal masking: A glitch on a node may be outside the latching window of all the latches in the subsequent paths. Hence, the error will not be latched, and there will be no soft error.

- Electrical masking: The glitch pulse amplitude may reduce after passing through some logic stages, which may cause the glitch to attenuate. This phenomenon is called electrical masking.

In the fault-tolerant analysis in this work, we do the worst-case analysis and assume that any transient fault strike will result in a soft error. However, the real fault rate is less than the worst-case analysis. In order to achieve the exact analysis one must consider the detail of the circuit design and check for the above masking processes.

Many different sources can give rise to transient faults including: high-energy ionized particles impacts, thermal noise, and shot noise. In advanced VLSI systems feature size and voltage scaling lead to small node capacitance and voltage, resulting in decreased critical charge on nodes holding logical states. With fewer electrons representing states, each node in the system becomes more susceptible to charge disruption, that may be caused by any of the sources below.

#### 2.1.2.1 High-Energy Particles

High-energy particles come from two sources

- High-energy alpha particles

- High-energy neutrons.

Alpha particles contains two protons and two neutrons. Alpha particles are emitted by various radioisotopes undergoing radioactive decay [18]. Metals such as lead that are used in packaging materials, emit low-energy alpha particles that can go as deep as 15 to 30  $\mu$ m in silicon and are very effective in causing upsets in circuit. Alpha particles are also generated by elements such as some isotope of natural boron that is contained in the doping material. Boron-related upsets have been demonstrated in DRAMs [19] and SRAMs [20]. It is shown that boron can result in as many as 81% of the SEUs in a 0.25  $\mu$ m SRAM [21]. Alpha particles caused by radioactive impurities from packaging or doping materials remain an important source of errors in SRAMs and other sensitive circuits.

Charged particles, like alpha particles, create a direct ionization in semiconductor devices, causing a current surge that is responsible for errors in the memory and processing elements. However, high-energy neutrons do not have electrical charges; their effects occur through nuclear collisions that give rise to charged particles, which in turn cause ionized particles; thereby causing SEUs and the degradation of electrical properties. The probability of nuclear collisions occurrence is extremely low. It is reported in [22], that one out of 40,000 neutrons hits a silicon nucleus. However, once it hits the silicon nucleus it is very effective and will cause an error.

As mentioned above, not all the high-energy particle hits are fatal, but as the critical charge reduces the probability that a high-energy particle hit becomes fatal increases. It has been shown that the transient fault rates per chip induced by alpha particle increases 30 times as the manufacturing process goes from 0.25  $\mu$ m to 0.18  $\mu$ m and the supply voltage drops from 2 V to 1.6 V; at the same time the transient fault rates per chip due to the neutron's impact increases by 20% [6].

#### 2.1.2.2 Shot Noise

Besides high-energy particles, noise is another source of electrical property disruption. Shot noise is one of the sources of noise that increases as we increase the clock frequency and further reduce supply voltage, and can become a significant source of transient faults. It is shown in [23] how to compute the error rate due to shot noise using Rice's generalized formula [24]. The error rate of a single transistor is

$$Bit\_Error\_Rate = \frac{2}{\sqrt{3}} f_c \exp\left(\frac{-0.09I}{f_c e}\right), \qquad (2.1)$$

where  $f_c$  is the clock frequency, e is the electron charge, and I is the ON-state current of the device. This is with the assumption that the noise margin is 60% of the ON-

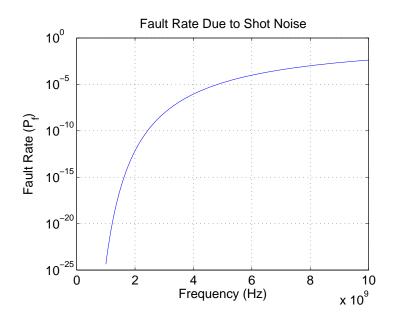

Figure 2.1. The device (e.g., transistor, nanowire) failure rate increases with the system frequency, for current per nanowire of 100 nA.

state current. Fault rate due to shot noise increases as the ON-state current decreases. Next we estimate the ON-state current to predict the device fault rate. The ON-state current is estimated using the maximum tolerable power dissipation in the system. Based on ITRS 2005, the maximum tolerable power dissipation in the system is around  $250 W/cm^2$  [1]. If the system works at 1 V, the maximum current consumed per area is  $250 A/cm^2$ . Using the nanoPLA structure (section 2.3), the nanowire density of this structure is  $\approx 240 \times 10^7 / cm^2$ . Therefore, each nanowire has a drive current around 100 nA. Using (2.1), we can estimate the device fault rate of such a system. Figure 2.1 shows how the fault rate grows as a function of system frequency when ON-state current equals 100 nA. For operating frequencies in the 1–5 GHz range, this model suggests that the individual device (e.g., transistor, nanowire) fault rates,  $P_f$ , are in the  $10^{-20}$  to  $10^{-5}$  range.

The effect of any of the above transient fault sources, ionized particle hit or noise, may ultimately cause a node in the logic circuit or memory unit loses its effective charge and consequently obtain a faulty value. This node can be a transistor or a precharged nanowire. To design a fault-tolerant system we assume the following general fault model for transient faults: A node (e.g., a transistor, or a precharged nanowire) may lose its correct value and holds an erroneous value with random probability. The node holds an erroneous value for as many cycles before obtaining the new value. Further we assume the transient fault has identically independent distribution (iid).

#### 2.1.3 Related Reliable Designs

Now that we know the sources of unreliability, we review some of the conventional reliable designs. We also present the reasons that these conventional reliable design may come short for high defect and fault rate nanotechology designs.

#### 2.1.3.1 Defect-Tolerant Works

In conventional VLSI designs, a system undergoes a chip level test and all the nonperfect chips are discarded. However, as mentioned above, the defect rate of nanotechnology design is expected to be few percentages. With this defect rate almost every system have significant number of defective devices.

For example, assume a system with  $10^{11}$  transistor and the defect rate of 1%. The expected number of defects in this system is 1 in every 100 nodes or  $10^9$  defective node in total, and with probability of 99%, the number of defective nodes is at least  $10^8$ .

At this point most of the fault-tolerant techniques tolerate single error; a simple example is *Triple Modular Redundancy* (TMR) [25], which provides three copies of the system followed by a reliable voter. TMR technique guarantees correcting any single error and multiple errors, as long as they fall in one copy. The reliability of TMR technique can be improved by generalizing the number of copies to N. In N Modular Redundancy, NMR, technique, all defects that cause at most  $\lceil (N-1)/2 \rceil$ erroneous copies are detected. The NMR technique, however, is not practical for the above example, where the system is expected to have  $10^9$  defective nodes. The system would need nine orders of magnitude area overhead!

To tolerate defects in this system with replication based techniques the system

must be partitioned into *Fine-grained* units, and NMR must be applied on each unit. For example, the above system can be partitioned into  $10^{10}$  units each of size 10 nodes, where each node can be defective with 1% probability. In this case, each unit is defective with 9% probability,

$$P_{f\_unit} = 1 - (1 - P_f)^{10} = 1 - (1 - 0.01)^{10} = 0.09.$$

(2.2)

For the sake of simple presentation, we assume that the interconnects are reliable and the error does not accumulate in the system. These may not be practical assumption, however, even with this relaxed assumption the NMR results in impractically large area overhead. As mentioned, the probability of having a reliable system is the probability of having less than  $\lfloor \frac{N-1}{2} \rfloor$  erroneous units.

$$\sum_{i=0}^{\lceil (N-1)/2 \rceil} \binom{N}{i} P_{f\_unit}^{i} (1 - P_{f\_unit})^{N-i} = 0.99.$$

Equating this probability to our target value, we can find the minimum required number of copies of N = 45.

The replication factor of 45 is not the final area overhead of the system. Implementing a reliable voter for each unit of size 10 nodes, require a considerable amount of area. The first approach to design a reliable voter would be to replicate it N times. Furthermore a circuit to take the majority of 45 signals is a huge circuit compared to the 10-node unit. In best case the voter grows linearly with the input size (N), so the voter area in total would grow as  $N^2$ . Therefore, we should expect seeing the final area overhead of this technique at about 2025 times the original area! This is huge area overhead, however, it is a considerable improvement from nine order of magnitude overhead of the system level NMR! In short, the above example, illustrates that NMR technique, even fine-grained NMR technique, will not be practical for nanotechnology defect-tolerant designs.

Another approach which uses the resources more economically compared to NMR, is *Sparing and Reconfiguration* technique. This technique is very popular for regular structures like memory systems [7] [8]. In this technique the resources are overpopulated, and only the nondefective units are used. For example in the memory system some extra columns are considered, the columns are then tested, and those that contain defective cells will be isolated. So this technique can tolerate a few defective cells in the system. However, when the defect rate is high, it will be challenging to find even a single defect free column, let alone a large enough set of columns that can perform as a full memory system. For example in the memory system with columns of length 1000 cells, and the defect rate of 1%, the probability that a single column is defect free is  $4 \times 10^{-5}$ ! So using *Sparing and Reconfiguration* technique alone will not provide a suitable defect-tolerant scheme for nanotechnology designs either.

However, we believe that we can develop a compact defect-tolerant approach for nanotechnology designs, and we present this in chapter 4. We use Defect Pattern Matching reliability design pattern, to achieve a reasonable area overhead for practical designs. In this technique the design of each unit is matched with the defect configuration of that unit, so we can still make use of defective units. The fact that make this possible is that permanent defects are statically located at the system. So if the defects are located, the system can program the design around the defects and still make use of defect free resources even in defective units. This technique is applicable for systems with regular structure and fixed configuration like Read Only Memories (ROM) and Programmable Logic Arrays (PLA), where the rows and columns configuration do not change during the operation. Once the defect pattern of the system is discovered, the row configurations of the system will be compared with the row defect pattern. Each configuration will be mapped to the first row with the compatible defect pattern, i.e., the configuration is mapped to the defect free nodes. Using this matching technique we show the most compact results compared to the related works; it can tolerate 10% defect rate with about 30% area overhead on average (chapter 4).

#### 2.1.3.2 Fault-Tolerant Works

Transient fault-tolerant techniques, can be divided into to two classes: *Rollback* techniques and *Feed-Forward* techniques [26][27, 28].

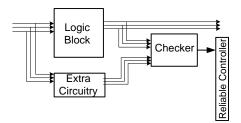

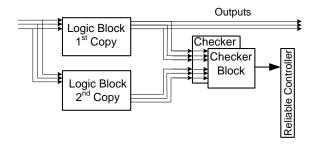

Generally in *Rollback Recovery* techniques, errors are *detected* with *spatial* redundancy (e.g., a duplicated copy of the logic) and *corrected* with *temporal* redundancy (e.g., repeating the operation). The system runs at high speed when there are no errors, but when an error is detected, the system stops and repeats the affected operation to generate the correct result. *Rollback Recovery* schemes exploit the fact that most of the operation cycles pass with no error occurrence, and therefore, the recovery process occurs infrequently and the throughput impact is potentially low. In contrast, *Feed-Forward Recovery* schemes provide enough *spatial* redundancy in the system to *detect* and *correct* errors with no *temporal* redundancy. NMR is a feed-forward technique.

Similar to the discussion on the permanent defect tolerant scheme, the first requirement for our design is *Fine-Grained* reliability. One recent feed-forward approach that has received considerable amount of attention in nanotechnology community is *Majority-Multiplexing*, which provides reliability at the device-level. This technique was originally invented by von Neumann at 1956 [29], and there has been some improvement on the original technique recently [30][31][11]. This technique was the first fault-tolerant approach that specifically targets nanotechnology designs. We bring a brief review of this work in the following section.

This technique is suggested to tolerate errors, cause by permanent defects and transient faults [31][11]. However, the analysis provided for these scheme is more acceptable for permanent defects. The reliability goal of this system is set at 90% defect rate which is reasonable chip yield, but too low for a valid fault-tolerant target. It is shown in [30] that the device defect rate of  $10^{-5}$  to  $10^{-2}$  requires 100 to 1000, replication factor. More efficient Majority-Multiplexing is provided in [11]. However, they show great improvement for lower defect rates (e.g.,  $10^{-8}$ ) and for higher defect rates (e.g.,  $10^{-4} <$ ) it stays close to the original Majority-Multiplexing. Next section

shows the details of the Majority-Multiplexing technique and the replication factor required for this technique, which can go as far as 1000 for the defect rate of 0.01. Later in chapters 4 and 5 we show that we can design defect- and fault- tolerant techniques that are more efficient than Majority-Multiplexing.

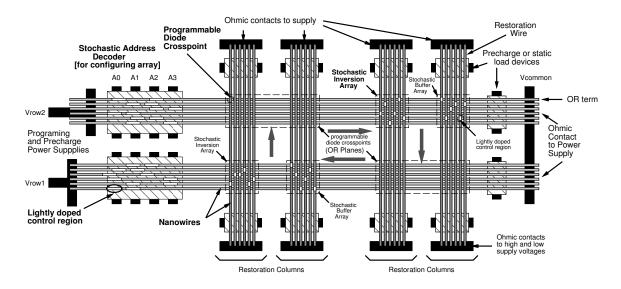

#### 2.1.3.3 Majority Multiplexing for Nanotechnology Designs

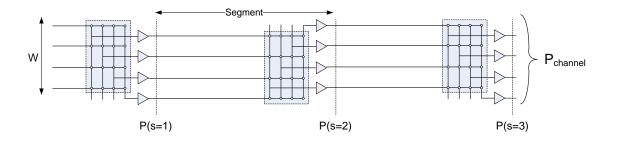

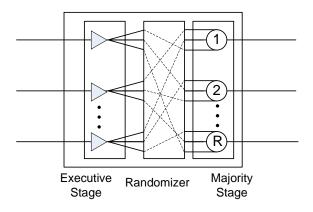

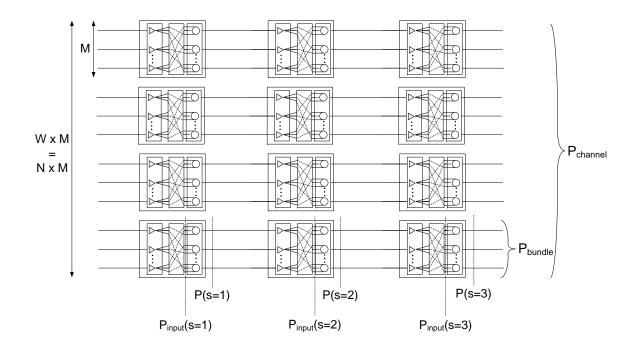

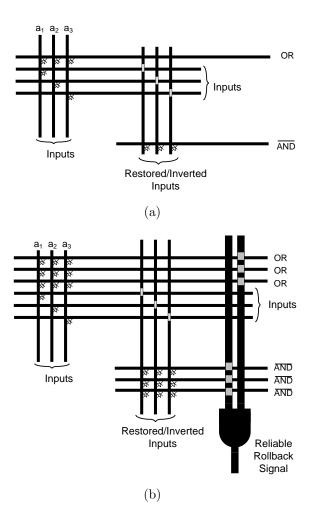

The common, fine-grained *Feed-Forward* fault-tolerant techniques for nanotechnology designs are based on *Multiplexing* the logic gates, which was originally developed by von Neumann as *Nand-Multiplexing* in 1956 [29]. In the *Multiplexing* technique, reliability is achieved by logic replication. Each bit is replicated M times and represented by the bundle of M wires. Computations are also replicated M times. Majority voting corrects errors in the logic. To prevent the voters from becoming a single point of failure, the voters are replicated as well. The trick is to make sure that a stage of computation and voting reduces the number of errors which exist in the bundle of wires which represent each bit.

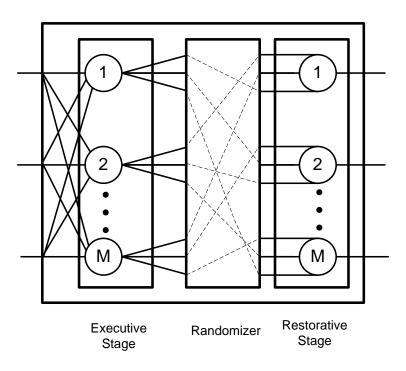

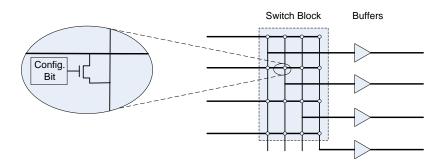

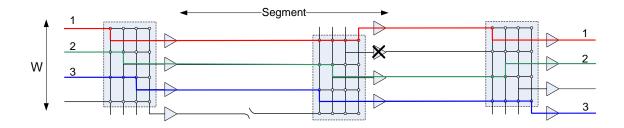

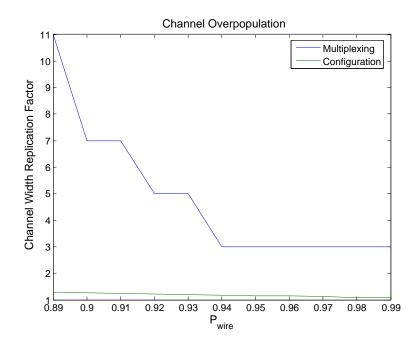

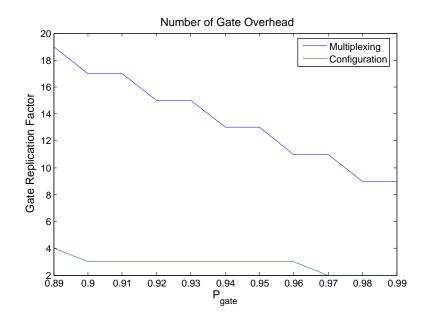

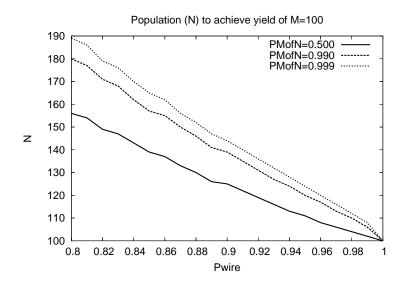

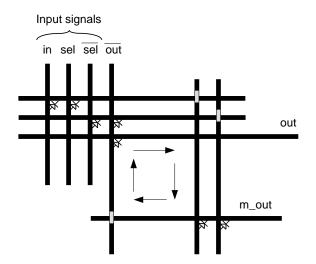

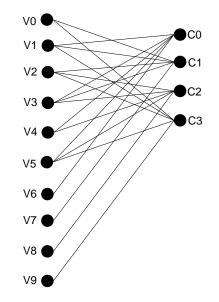

For the multiplexing scheme, each processing unit (NAND gate) is replaced by replicated copies of the processing unit and voters. Each of the M wires of an input bundle has a separate and independent path through the multiplexed unit. A multiplexed unit consists of two stages, each using M processing units (NAND gate) (see figure 2.3). The first stage is the executive stage which performs the actual logic operation and generates replicated results of the logic (NAND function). The second stage is the restorative stage. The restorative stage performs the redundant voting on the output of the executive stage and is responsible for improving the output reliability. The executive stage is connected to the restorative stage through a randomized interconnect; this randomization improves the reliability of the design by guaranteeing errors arriving at the restoration stage are statistically independent (figure 2.3). In recent work [31], it is shown that *Majority* gates perform better than NAND gates, resulting in more compact fault-tolerant designs. All the devices in the first and second levels and the randomized interconnects fail with equal probability. The total area overhead of this design is lower-bounded by its replication factor. The replication factor of this design is  $2 \times M$ . It is shown in [31] that majority multiplexing can be further optimized by sharing one restoration stage among multiple executive stages. Let L be the number of executive stages that share a restorative stage. The value of L, impacts the reliability of the system, and there is a lower bound on it based on the desired system reliability. For a system with M multiplexing factor and L executive stages for one restoration stage, the replication factor is  $((L + 1)/L) \times M$  [11]. We have to note that the total area overhead is larger than the replication factor when considering the wiring area required by the randomized interconnects, particularly when M is large.

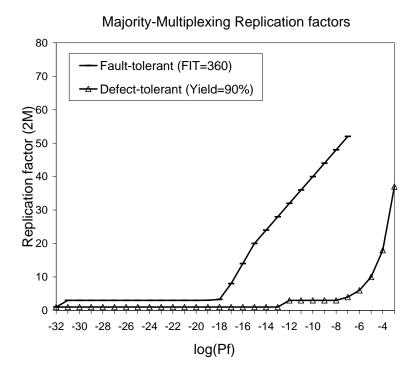

This technique is suggested to tolerate both permanent defects and transient faults [32][11]. In the defect-tolerant application, this method is oblivious to the defect location map, and tolerates defect the same way that it may tolerate transient faults. Depending on the source of the failure (permanent defects, or transient faults), the system has different reliability target; i.e., for tolerating permanent defects a chip yield of around 90% is acceptable yield, while the expected failure probability for transient fault-tolerant application is around  $10^{-18}$ , which makes the Failure In Time (FIT) of 360 for a typical system. *FIT* is an standard way of representing system reliability, and it is the number of failure in  $10^9$  hours of operation. A typical FIT of a commercial system is around couple of hundreds, so we believe that FIT=360, is the right target.

The area overhead of this technique is computed for both permanent defects and transient faults application [11]. The chip size,  $N_{total}$ , is assumed  $10^{12}$  in [11]. In the same work the system is partitioned into units of size  $10^6$  nodes. They assume that the units have a logical depth D = 10. The graph in figure 2.3 plots the area overhead for two cases: (1) when tolerating permanent defects with target chip yield of 90%; (2) when tolerating transient faults with FIT of 360. We would expect that the fault rate would go as far as  $10^{-7}$  at most and the defect rate would be above this value up to a few percent.

Figure 2.2. A reliable multiplexed unit to implement using von Neumann multiplexing technique

Figure 2.3. Replication factor of majority multiplexing for transient fault-tolerant (FIT=360) and defect-tolerant (yield=90%).

### 2.2 Substrates

In the rest of this chapter we review some of the promissing nanotechnology devices, and main building blocks. We then review the a computation (*NanoPLA* [33]) and memory (*Nanomemory* [14]) model built upon these devices. In the following chapters we show the detail implementation of our defect- and fault-tolerant techniques on these architectures.

#### 2.2.1 Wires

This section reviews two of the most studied and developed interconnect wires using nanotechnology: *Nanowire* [34] and *Nanotube* [35]. Both of these wires can be semiconductor and metallic wires, and therefore, they can be both used as interconnect or as active devices, as will be shown later in this chapter.

#### 2.2.1.1 Nanowires

Chemical Technologies have been developed to grow silicon and germanium nanowires [34, 36] which are only nanometers wide. These nanowires can be hundreds of micrometers long [37]. Atomic-scale nanowires can be fabricated in chemistry labs to have a variety of conduction properties (i.e., semiconductor or metal). Nanowires can be grown in the controlled environment using seed catalysts (e.g., gold particles). The size of the seed catalysts define the nanowires diameter. The catalyst constrains the growth of the semiconductor to only one dimension [34]. Nanowires with diameters down to 3 nm have been demonstrated [36, 34]. Seed catalysts with controlled diameter can be produced by self-limiting chemical processes (e.g., [38]). The composition of a nanowire can be varied along its axis and along its radius, which offers a single two-dimensional structure that works as an interconnect and a controllable device at the same time.

Langmuir-Blodgett (LB) flow techniques can be used to align a set of nanowires into a single orientation, close pack them, and transfer them onto a chip surface [15][39]. The resulting wires are all parallel with nematic alignment. By using wires with an oxide sheath around the conducting core, the wires can be packed tightly. The oxide sheath defines the spacing between conductors and can, optionally, be etched away after assembly. The LB step can be rotated and repeated so that we get multiple layers of nanowires [15][39] such as crossed nanowires for building a crossbar array or memory core (section 2.3.1).

The other successful fabrication technique is imprint lithography. Nanowires with sub-10 nm feature size can be made using imprint lithography [40]. This new technique has high throughput and low cost. Imprint lithography includes little damages to sensitive circuit components, including active molecules, which are used in making programmable cross-points (section 2.2.3). Chen et al. have developed an inexpensive process to fabricate nanoscale devices and circuits utilizing imprint lithography, shown in [16]. This technique for fabricating aligned metal nanowires through a onestep deposition process without subsequent etching or lift-off is demonstrated in [41]. Their technique uses Molecular Beam Epitaxy (MBE) to create physical template for nanowire patterning. The template is a selectively etched GaAs/AlGaAs superlattice. The wires are defined by evaporating metal directly onto the GaAs layers of the superlattice after selective removal of the AlGaAs to create voids between the GaAs layers. By depositing the metal solely on the GaAs layers, the wire width is defined by the thickness of the GaAs layers and the separation width by AlGaAs layers. Transfer of the metal nanowires to a silicon wafer is performed by contacting the metal-coated template to a silicon oxide surface with subsequent heating process. Wires deposited with this technique were uniform and continuous over 2 to 3mm length, with very few defects.

#### 2.2.1.2 Nanotubes

Carbon nanotubes that are nanometers in diameter and micrometers long can be fabricated in chemistry labs [42]. Carbon nanotubes can also be grown from seed catalysts with diameters down to roughly 1 nm in diameter and microns long. They can be semiconducting, allowing field-effect control, or metallic, perhaps offering superior electrical properties to silicon nanowires or even copper. To date, we cannot control the conducting properties of nanotubes; i.e., metallic and semiconductor nanotubes cannot be differentiated during the growth process. Unlike nanowires, nanotubes are not rigid, and consequently it is more challenging to align carbon nanotubes into straight, parallel arrays. Some techniques are being developed (e.g., [35]) and more techniques are under research.

#### 2.2.2 Field-Effect Controllable Cross-Point

By controlling the density of doping material in the environment during growth, semiconducting nanowires can be doped to control their electrical properties [34]. Heavily doped nanowires always conduct, while conduction through lightly doped nanowires can be controlled via an electrical field similar to Field-Effect Transistors (FETs) [15]. OFF resistances can be over 10 G $\Omega$  and ON resistances under 0.1 M $\Omega$ , OFF/ON resistance ratios are at least 10<sup>4</sup> [43]. A nanowire field-effect gating has sufficient gain to build restoring gates [44]. The threshold voltage for the nanowires can be controlled by material properties (e.g., doping or composition) and geometry factors.

By changing the density of doping material in the environment during growth, a doping profile can be made along one nanowire, e.g., in a highly doped nanowire that can always conduct only one region can be lightly doped to control the conduction. The differentiated doping profile gives the ability to selectively control the conduction of one nanowire among other nanowires in an array (section 2.3.2).

#### 2.2.3 Programmable Cross-Point

Chen et al. demonstrate a nanoscale Pt-rotaxane-Ti/Pt sandwich which exhibits hysteresis and nonvolatile state storage showing an order of magnitude resistance difference between ON and OFF states for several write cycles [4]. After an initial "burn"-in step, which permanently reduces the the high resistance of > 100 M $\Omega$ to 9 M $\Omega$ , the state of these devices can be switched at ±2 V and read at ±0.2 V. [4] reports a 40 nm×40 nm junctions, with the ON resistance of roughly 500 k $\Omega$  , and the OFF resistance of 9 M $\Omega$ . The exact nature of the physical phenomena involved is the subject of active investigation. The basic hysteretic molecular memory effect is not unique to the rotaxane. Many technologies have been demonstrated for nonvolatile, switched cross-points, where the common features include: (1) resistance which changes significantly between ON and OFF states; (2) the ability to turn the device ON or OFF by applying a voltage differential across the junction; (3) the ability to be placed within the area of a crossed nanowire junction.

LB techniques can also be used to place the switchable molecules between crossed nanowires (e.g., [9]). The molecules are formed into a single monolayer in an LB trough and then transferred onto a set of parallel nanowires [45]. An orthogonal set of nanowires is then transferred on top creating the conductor-device-conductor sandwich for the cross-point array. The  $8 \times 8$  molecular crossbar was constructed using this approach [4].

This programable cross-point is comparable with a SRAM-based programmable switch for reconfigurable systems (e.g., FPGA). However, a typical SRAM-based switch might take about 2500 nm<sup>2</sup> compared to a 5 nm×5 nm bottom level metal wire crossing of molecular switches. Consequently, the molecular cross-points offers 100 times smaller switches.

## 2.3 NanoPLA

In this section we review the building blocks that can be constructed using the techniques in the previous section. These building blocks are useful in developing many system architecture including *NanoPLA*, which will be reviewed later in this section.

#### 2.3.1 Programmable Crossbar Array

Nanowires can be fabricated in tight-pitched parallel arrays, but we cannot fabricate arbitrary geometries with equally tight conductor and device pitches. Assembly process allows crossed nanowires array the switchable resistance from section 2.2.3 in between (see figure 2.4). The effective diode in the junction comes from the crossing

|                      | [                |        |        |                 |                              |

|----------------------|------------------|--------|--------|-----------------|------------------------------|

|                      |                  | ₽<br>₩ | ₩¥     | ₩Ą              | ₽                            |

| P-type               |                  | ₽      | Å<br>Å | Å.              | $\mathbb{A}_{\mathbb{A}}$    |

| P-type _<br>nanowire |                  | ₽₹     | ₽      | ₽ <sup>\$</sup> | $\mathbb{A}_{\mathbb{A}}$    |

|                      |                  | ₽₹     | ₽      | ₽               | $\mathbb{A}_{\underline{k}}$ |

|                      |                  |        |        |                 |                              |

|                      | N-type nanowires |        |        |                 |                              |

Figure 2.4. Programmable nanowire crossbar

nanowires doping. A low resistance junction between an N-typed nanowire and a P-type nanowire works as a diode from the first nanowire to the second one. This nanowire crossbar with programmable junctions is the core of many nanotechnology architectures, including nanoPLA and nanoMemory. This crossbar can be used as memory cores, programmable logic cores, and programmable crossbar interconnect arrays. When crossbar is used as logic core, each horizontal nanowire implements the wire-OR logic function of the selected vertical nanowires with turned ON switches. When the crossbar is used as memory core, each junction stores single memory bit and it can be accessed by putting the appropriate voltage on both nanowires passing the junction. When the crossbar is used as interconnect array, each junction is programmed to route the incoming signals in vertical nanowires to horizontal nanowires.

#### 2.3.2 Restoration and Inversion Array

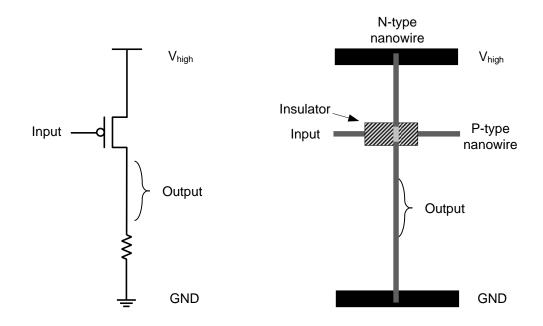

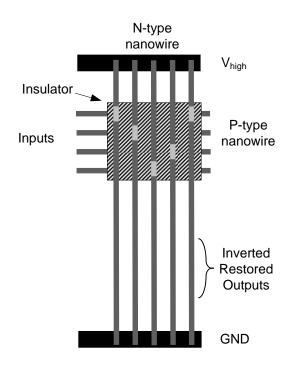

As noted in section 2.3.1, the programmable, wired-OR logic is passive and nonrestoring, drawing current from the input. Further, OR logic is not universal. To generate any arbitrary combinational logic, we need universal building gate and further we need to restore signals to maintain the appropriate voltage level in multilevel circuit implementation. We can achieve all of the above with a restorable inverter integrated with the OR gates, which generate a universal NOR gate. As developed in section 2.2.2, nanowires can be field-effect controlled. This gives us the potential to build FET-like

Figure 2.5. Structure of nanowire inverter

gates for restoration. Using a highly doped nanowire with a lightly doped region as shown in figure 2.5 can provide a gatable junction, where the electrical voltage on the horizontal nanowire, passing through lightly doped region, controls the current on the vertical voltage. If the vertical nanowire is P-type doped and the  $V_{high}$  and GND signals are connected as figure 2.5 then the inverted and restored value of the horizontal nanowire is transferred into the vertical nanowire. If the location of  $V_{high}$ and GND are swapped the vertical nanowire only holds the restored value with no inversion.

These restoration gates can be closed packed to generate a nanowire restoration inverter crossbar as in figure 2.6. In ideal case, each vertical (output) nanowires has exactly one controllable lightly doped region that can be controlled by exactly one horizontal nanowire. However, due to limited control over alignment of nanowires the nanowires with different doping profile is stochastically located. Furthermore, to generate a nanowire set with different doping profiles, each nanowire has to be selected from a bach of grown nanowires with a unique doping profiles. However, with our nanowire assembly technique (section 2.2.1.1) this is practically impossible.

Figure 2.6. Restoration crossbar with nanowire

Instead we can overpopulate the vertical nanowires with various doping profile to make sure that there exists enough correctly aligned and uniquely controlled vertical nanowires (figure 2.5).

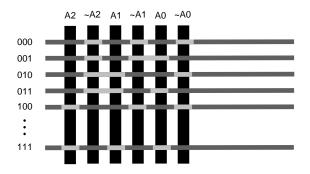

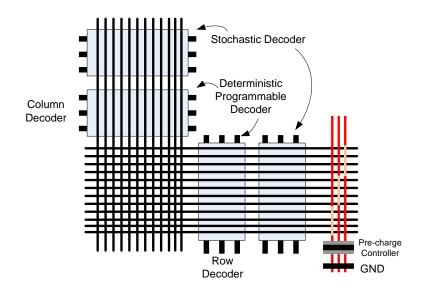

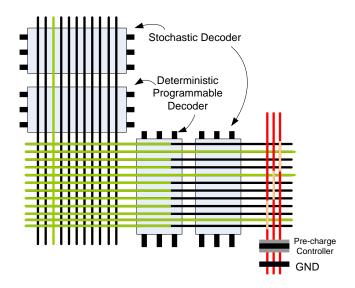

#### 2.3.3 Lithographic to Sublithographic Decoder

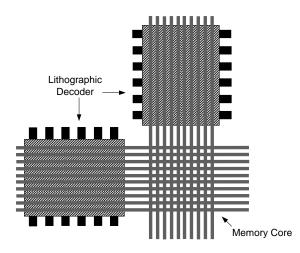

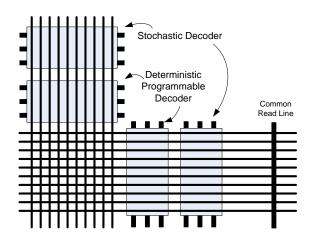

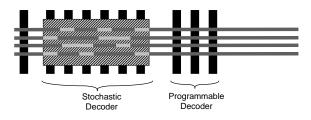

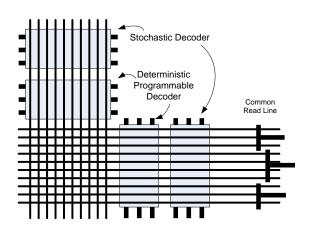

An important challenge is to access nanowires from lithographic scale wires and be able to programm nanowire junctions by applying appropriate differential voltage on the nanowires of each junction. Furthermore, we must be able to drive and sense each nanowire to read back the status of each junction (e.g., in memory cores). A decoder structure from lithographic scale wires to nanowires proposed in [44] provide these functionalities.

To interface with lithographic-scale wires, address bit regions are marked off at the lithographic pitch. Each such region is then either doped heavily so that it is oblivious to the field applied by a crossed lithographic-scale wire or is doped lightly so that it can be controlled by a crossed lithographic scale wire (see figure 2.7). In this way, the nanowires will only conduct if all of the lithographic-scale wires crossing

Figure 2.7. Lithographic to sublithographic Decoder

its lightly doped, controllable regions have a suitable voltage to allow conduction. If any of the lithographic-scale wires crossing controllable regions provide a suitable voltage to turn off conduction, then the nanowire will not be able to conduct.

Now the conduction through the nanowires can be controlled with lithographic scale wires, each nanowire can be selected separately with the following procedure. All the nanowires are either precharged or weakly pulled to a nominal voltage. We then apply the desired nanowire address to the lithographic-scale address lines. We also apply the desired drive voltage to a common line attached to all the nanowires. If the selected address is present in the array, it will allow conduction from the common line into the array charging up the selected nanowire (see left side of figure 2.8). The other nanowire crossing the junction can be selected with the same procedure, and the junction can be programmed by applying the appropriate voltage at the crossing nanowires. Note that there is no directionality to the decoder. Consequently, this same unit can also serve as a multiplexer. That is, when we apply an address to the lithographic scale wires, it allows conduction through the addressing region for only one of the nanowires. Consequently, we can sense the voltage on the common line rather than drive it.

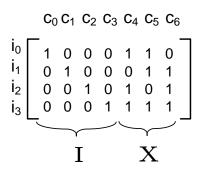

#### 2.3.3.1 Nanowire Codes

A dual-rail binary code is used for each logical lithographic address bit. That is, for each logical address bit, we provide the value and its complement. This results in two bit positions on the nanowire for each logical input address bit, one for the true sense and one for the false sense. To code a nanowire with an address, we simply code either bit position to be sensitive to exactly one sense of each of the bit positions (figure 2.7). This results in a decoder which requires  $2 \log_2(N)$  address bits to address N nanowires. The technique in [44] shows a denser addressing using  $N_a/2$ -hot codes ( $N_a$  is the number of address bits). That is, it simply requires that half of the address bits,  $N_a$ , be set to a voltage which allows conduction and half to be set to a voltage that prevents conduction. This scheme requires only  $\lceil 1.1 \log_2(N) \rceil + 3$  address bits.

If each nanowire in the array has a unique address in our selected coding scheme, we can uniquely address each individual nanowire in the array. However, similar to issue in the restoration plane, our nanowire assembly techniques (section 2.2.1.1) do not allow us to uniquely select and place particular nanowires in particular locations. However, if the code space for the nanowires is large compared to the size of the nanowire array, it is statistically guaranteed that with arbitrarily high probability every nanowire in an array has a unique address. That is, we start with growing a very large number of nanowire codes. We mix up the nanowires before assembly, and randomly select an array of coded nanowires. As long as the array formed is sufficiently small compared to the code space, with high probability each array contains nanowires with unique codes [44]. It turns out that we do not need a large number of address bits in order to guarantee this uniqueness. For example, the  $N_a/2$ hot codes need a total of only  $\lceil 2.2 \log_2(N) \rceil + 11$  bits to achieve over a 99% probability that all nanowires in an array will have unique addresses. If a few duplicates are tolerable, then the codes can be much tighter [46][47]. More information about tolerating nanowire code misalignment can be found in [44].

Figure 2.8. Single nanoPLA block

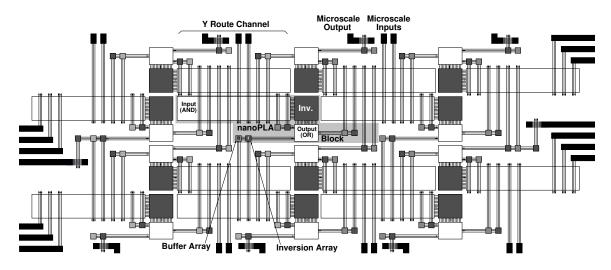

#### 2.3.4 Architecture

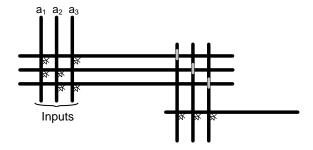

Combining the building blocks introduced above, we can construct complete, programmable logic architectures with all logic, interconnect, and restoration occurring in the atomic-scale nanowires. Programmable switch crossbar (section 2.3.1) provides wired-OR programmable logic, field-effect restoration arrays (section 2.3.2) provide gain and signal inversion, and the nanowires themselves provide interconnect among arrays. Lithographic scale wires provide a reliable support infrastructure which allows device testing and programming, by addressing individual nanowires using the decoders introduced in section 2.3.3. Lithographic-scale wires also provide power and control logic evaluation.

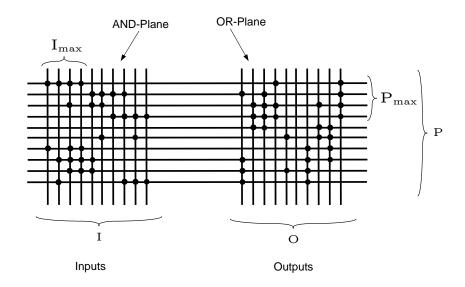

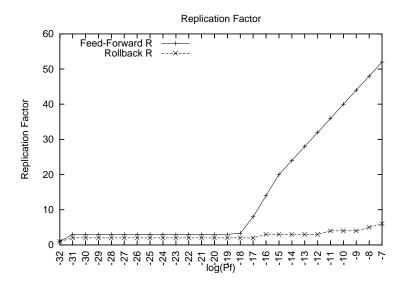

figure 2.8 shows a simple nanoPLA block organization with no interblock routing. The array forms a two-plane PLA cycle. Each plane consists of a programmable cross-point OR array (section 2.3.1) followed by a restoration and inversion array (section 2.3.2). Consequently, each plane is a programmable NOR. The combination of NOR-NOR planes is essentially an AND-OR PLA. As figure 2.8 shows, each horizontal wire forms a wired-OR. Crossed nanowire inputs connected to a horizontal nanowire through a junction programmed into the low-resistance ON state can potentially pull up the nanowire, whereas inputs connected through high-resistance OFF junctions do

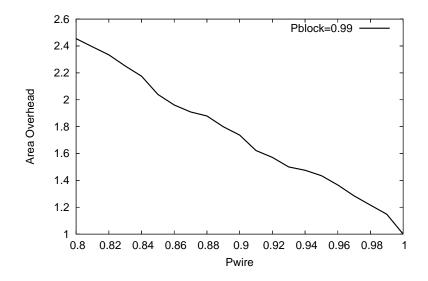

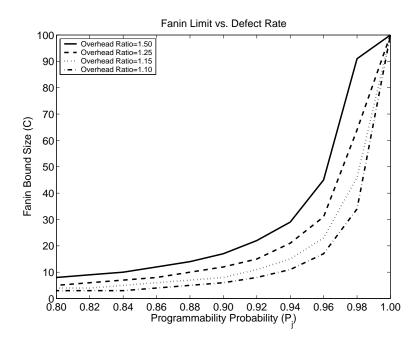

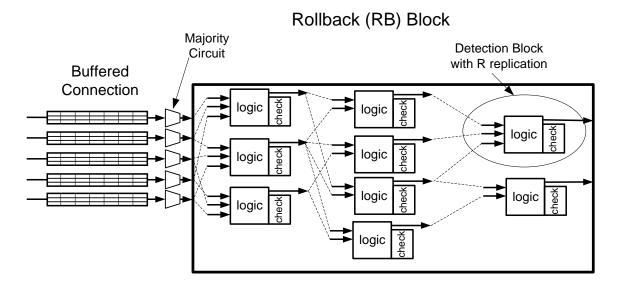

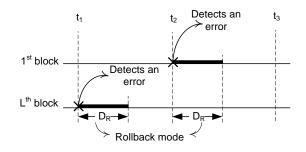

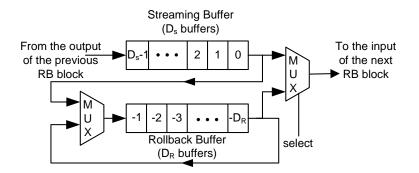

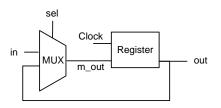

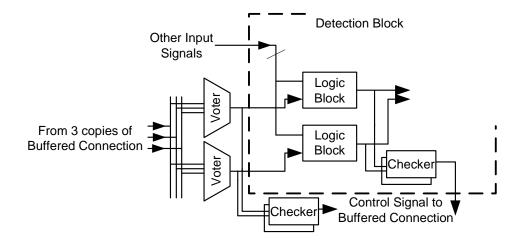

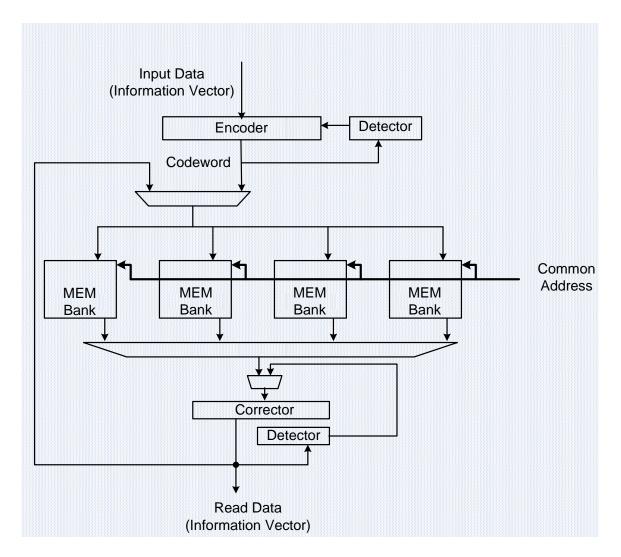

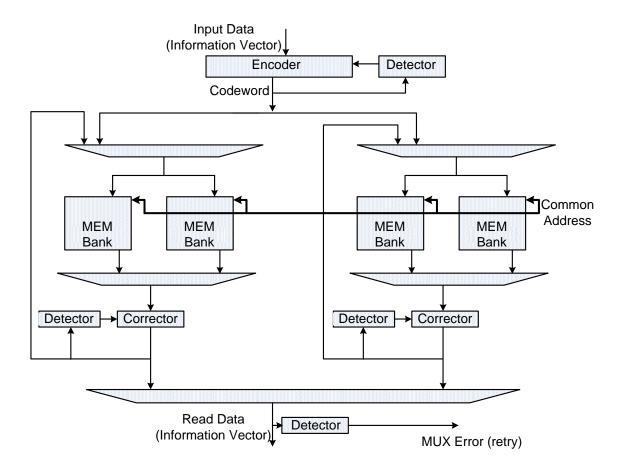

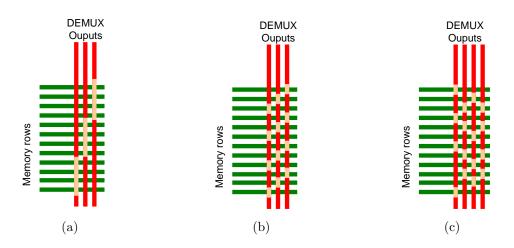

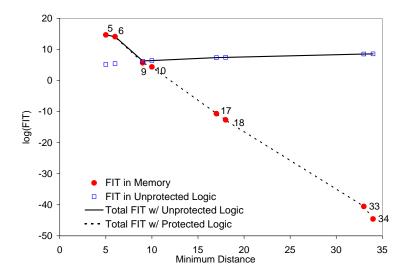

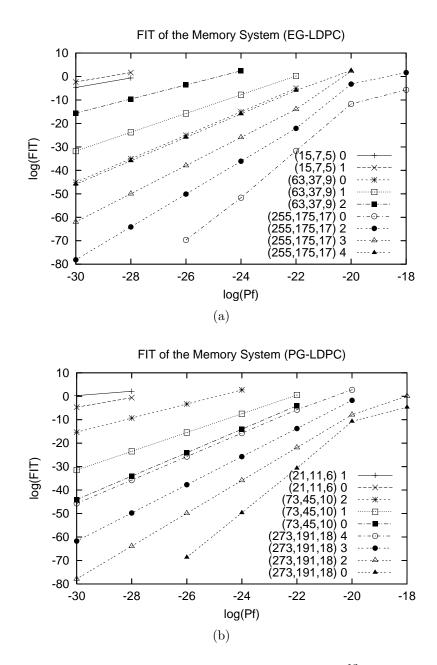

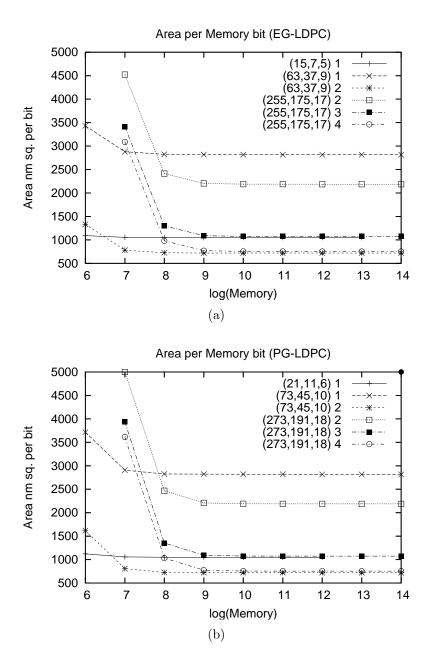

Figure 2.9. Interconnected nanoPLA blocks