# Testing Delay-Insensitive Circuits

Thesis by Pieter Johannes Hazewindus

In Partial Fulfillment of the Requirements

for the Degree of

Doctor of Philosophy

California Institute of Technology Pasadena, California, USA

> 1992 Defended 20 May 1992

©1992

Pieter J. Hazewindus All rights reserved Aan mijn ouders

## Acknowledgements

Niet over rozen gaat het pad Maar zonder vrienden kan ik niet.

— Boudewijn de Groot

Thanking people is my favorite vice.

— Allan Gurganus

Now the fearful trip is done. I have many people to thank for shaping the almost seven years of my stay at Caltech, and its long-awaited completion. The following is but a partial list. Thanks to anyone whom I forgot to mention.

I want to express my gratitude to my advisor, Alain Martin, who invented the delay-insensitive synthesis method, and suggested I look into testing for delay-insensitive circuits. He has guided the development of my research. His suggestions, comments, and criticisms were invaluable. Thank you very much.

My thanks to my thesis committee, Alain Martin, Yaser Abu-Mostafa, Chuck Seitz, Jerry Sussman, and Jan van de Snepscheut, for the time spent reading my thesis, and for suggesting such useful corrections.

My thanks to DARPA for funding my research.

My thanks to Chuck Seitz, who introduced this mathematician to circuit design. He helped Steve Burns, Andy Fyfe, and me develop a standard-cell route-andplacement system, with which our first chips were designed. This system reduced design time considerably, and was a major step forward toward our proving the practicality of delay-insensitive circuit design. Thanks also for the use of the narrow-pitch pads.

My thanks to Mani Chandy, for radically changing my thinking on concurrency and parallel programming.

My thanks to Yaser Abu-Mostafa, for being my best teacher at Caltech. I always learned something from his lectures, even when I already knew the material.

My thanks to Martin Rem, for his help with preparing me for Caltech, and for his help and support during my studies.

My thanks to Steve Burns for the many fruitful discussions on circuit design, from the first day until (almost) the last, and for posing the difficult questions that needed to be answered.

My thanks to the other graduate students in my research group, Dražen Borković, Marcel van der Goot, Tony Lee, Christian Nielsen, and José Tierno, for the discussions and suggestions during many group meetings, and for proofreading this thesis.

My thanks to my officemates for long periods of absence, which gave me a quiet environment in which to work, and for eventually showing me how to complete the work.

My thanks to Rajiv Gupta for his patient ears, for his encouragement, and for his hospitality.

My thanks to David Schweizer, who would bristle at being called a bastion of sanity, but who was one for me. He knew where my towel was.

My thanks to Andy Fyfe for his early work on the route-and-placement system, for his efforts at coercing IATEX into conforming to Caltech thesis standards, and for his understanding of the vagaries of the computer system.

My thanks to Jim Boyk for his music, for his epicurism, and for all the great conversations.

Finally, my thanks to my mother, my father, and my sister, Geertje, for their unwavering support while I took the road less traveled by. They have made all the difference.

"The thing you've got to realize", he said, "is that most of these guys, for all their computer wizardry, don't know very much about the English language. Some of them are positively subliterate."

— David Leavitt, Equal Affections

A special thanks to Dian De Sha, B.A., for diligently proofreading manuscripts, for sharing stories, and for moral support during difficult times. And yes, I know the comma ought to be inside the quotation marks.

#### Abstract

A method is developed to test delay-insensitive circuits, using the single stuck-at fault model. These circuits are synthesized from a high-level specification. Since the circuits are hazard-free by construction, there is no test for hazards in the circuit. Most faults cause the circuit to halt during test, since they cause an acknowledgement not to occur when it should. There are stuck-at faults that do not cause the circuit to halt under any condition. These are *stimulating* faults; they cause a premature firing of a production rule. For such a stimulating fault to be testable, the premature firing has to be propagated to a primary output. If this is not guaranteed to occur, then one or more test points have to be added to the circuit. Any stuck-at fault is testable, with the possible addition of test points. For combinational delay-insensitive circuits, finding test vectors is reduced to the same problem as for synchronous combinational logic. For sequential circuits, the synthesis method is used to find a test for each fault efficiently, to find the location of the test points, and to find a test that detects all faults in a circuit.

The number of test points needed to fully test the circuit is very low, and the size of the additional testing circuitry is small. A test derived with a simple transformation of the handshaking expansion yields high fault coverage. Adding tests for the remaining faults results in a small complete test for the circuit.

# Contents

| f Acknowledgements                                 | v   |

|----------------------------------------------------|-----|

| Abstract                                           | ix  |

| List of Figures                                    | xvi |

| Chapter 1. Introduction                            |     |

| 1. Organization of the Thesis                      | 5   |

| 2. A Note on Notation                              | 6   |

| Chapter 2. Synthesis of Delay-Insensitive Circuits | 7   |

| 1. Introduction                                    | 7   |

| 2. Gates and Circuits                              | 8   |

| 3. The High-Level Specification                    | 12  |

| 3.1. Language Constructs                           | 13  |

| 3.2. Examples of Programs                          | 15  |

| 3.3. Program Decomposition                         | 15  |

| 4. The Handshaking Expansion                       | 16  |

| 4.1. The Probe                                     | 17  |

| 19 Two-Phase Handshaking                           | 17  |

|           | 4.3. Examples                                                  | 18         |

|-----------|----------------------------------------------------------------|------------|

| <b>5.</b> | The Handshaking Expansion for Communication Channels           | 18         |

|           | 5.1. Dual-rail Encoding                                        | 19         |

|           | 5.2. One-hot Encoding                                          | 20         |

|           | 5.3. k-out-of-N Encoding                                       | 20         |

| 6.        | Reshuffling and State Assignment                               | 22         |

| 7.        | The Production Rule Set                                        | 23         |

| 8.        | The Role of the Environment                                    | <b>2</b> 5 |

| 9.        | Acknowledgments and Isochronic Forks                           | 26         |

| Cl        | hapter 3. A Method to Test Delay-Insensitive Circuits          | <b>3</b> 0 |

| 1.        | Introduction                                                   | 30         |

| 2.        | Problems with the Delay Model                                  | 31         |

| 3.        | A Classification of Stuck-At Faults                            | 35         |

| 4.        | Faults Causing the Circuit to Halt During Test                 | 38         |

| <b>5.</b> | A Classification of Inhibiting Faults                          | 42         |

|           | 5.1. Fault stuck-at-0 Inhibits Down-transition                 | 42         |

|           | 5.2. Fault stuck-at-1 Inhibits Up-transition                   | 44         |

|           | 5.3. Fault stuck-at-0 Inhibits Up-transition                   | 44         |

|           | 5.4. Fault stuck-at-1 Inhibits Down-transition                 | 45         |

|           | 5.5. Fault stuck-at-0 Inhibits and Stimulates Both Transitions | 46         |

|           | 5.6. Fault stuck-at-1 Inhibits and Stimulates Both Transitions | 47         |

|           | 5.7. Primary Input or Output of Gate stuck-at-1                | 47         |

| 6.        | Stimulating Faults                                             | 48         |

| 7.           | Fault Analysis of a One-bit Queue Element                  | 51  |

|--------------|------------------------------------------------------------|-----|

| $\mathbf{C}$ | hapter 4. Testing Delay-Insensitive Combinational Logic    | 58  |

| 1.           | Introduction                                               | 58  |

| 2.           | Monotone Circuits                                          | 62  |

| 3.           | Testing Synchronous Combinational Logic                    | 63  |

| 4.           | Sufficient Tests for Delay-Insensitive Combinational Logic | 67  |

| <b>5.</b>    | Application: Combinational Logic in AND-OR Form            | 72  |

| 6.           | Example: Ripple-carry Adder                                | 80  |

| 7.           | The D-algorithm for Delay-insensitive Circuits             | 84  |

|              | 7.1. Forward Propagation                                   | 85  |

|              | 7.2. Backward Propagation                                  | 86  |

|              | 7.3. An Example                                            | 86  |

| Cl           | napter 5. Design for Testability                           | 90  |

| 1.           | Introduction                                               | 90  |

| 2.           | Non-interference                                           | 91  |

| 3.           | Initializing a Faulty Circuit                              | 93  |

|              | 3.1. Cascaded Resets                                       | 96  |

|              | 3.2. Faults on Reset Variables                             | 97  |

| 4.           | Control and Observation Points                             | 98  |

|              | 4.1. Control Points                                        | 100 |

|              | 4.2. Observation Points                                    | 101 |

| <b>5.</b>    | Example: Microprocessor Control                            | 101 |

| 6.           | Design to Minimize Number of Test Points                   | 102 |

| 7. | Test Circuitry                              | 108 |

|----|---------------------------------------------|-----|

|    | 7.1. Queue Element for an Observation Point | 114 |

|    | 7.2. Queue Element for a Control Point      | 119 |

| 8. | Testability of the Test Circuitry           | 121 |

| Cł | napter 6. Test Generation and Other Topics  | 124 |

| 1. | Introduction                                | 124 |

| 2. | Heuristics for Test Generation              | 125 |

| 3. | Fault Location                              | 129 |

| 4. | Stuck-open and Stuck-on Faults              | 132 |

|    | 4.1. Stuck-open Faults                      | 133 |

|    | 4.2. Stuck-on Faults                        | 136 |

|    | 4.2.1.                                      |     |

|    | 4.2.2.                                      |     |

| Ch | napter 7. Conclusions                       | 139 |

| Ap | opendix A. Algorithms                       | 142 |

| 1. | Finding a Test Vector for a Fault           | 142 |

| 2. | Finding Test Points                         | 144 |

| 3. | Finding a Test to Detect all Faults         | 145 |

| 4. | Calculating Fault Coverage for a Test       | 146 |

| Αp | opendix B. Principles of Circuit Testing    | 149 |

| 1. | Introduction                                | 149 |

| 2. | Levels of Fault Modeling                    | 150 |

| 3. | The Single Stuck-At Fault Model             | 151 |

| 4.        | Merits and Shortcomings of the Stuck-At Fault Model | 155 |

|-----------|-----------------------------------------------------|-----|

| <b>5.</b> | Tests                                               | 156 |

| 6.        | Redundancy                                          | 161 |

| 7.        | Testing Combinational Logic                         | 163 |

|           | Boolean Differences                                 | 164 |

| 8.        | The D-Algorithm                                     | 167 |

| 9.        | Testing Sequential Synchronous Circuits             | 172 |

| Bil       | oliography                                          | 176 |

# List of Figures

| 2.1 | Schematic representation of AND gate and C-element                     | 9   |

|-----|------------------------------------------------------------------------|-----|

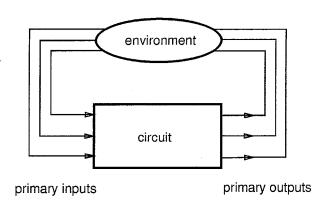

| 2.2 | A circuit and its environment                                          | 10  |

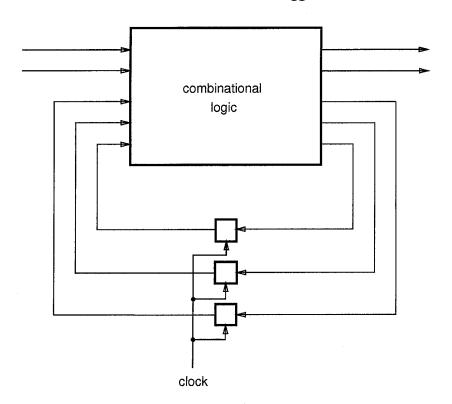

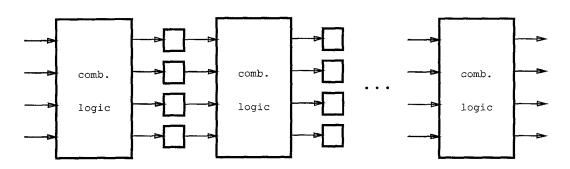

| 2.3 | A synchronous sequential circuit, with clocked state-holding elements  | 11  |

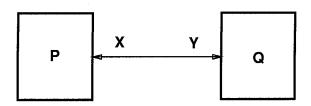

| 2.4 | Channel $(X,Y)$ between processes $P$ and $Q$                          | 13  |

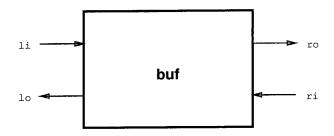

| 2.5 | Buffer process with left and right ports                               | 18  |

| 2.6 | Circuit $C2$ , the D-element buffer process                            | 25  |

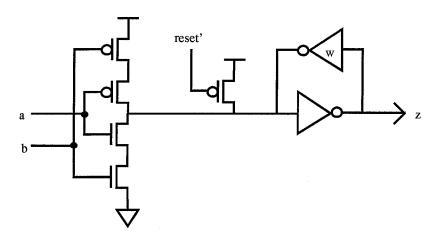

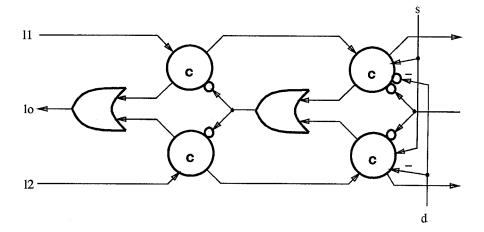

| 3.1 | One-bit wide queue element                                             | 52  |

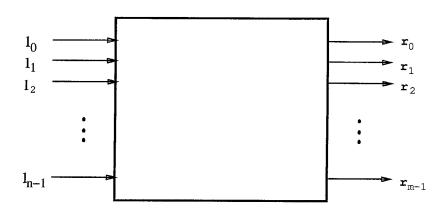

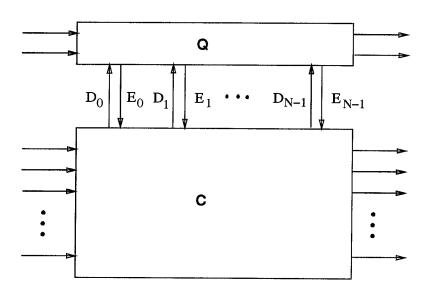

| 4.1 | Model of delay-insensitive combinational logic                         | 60  |

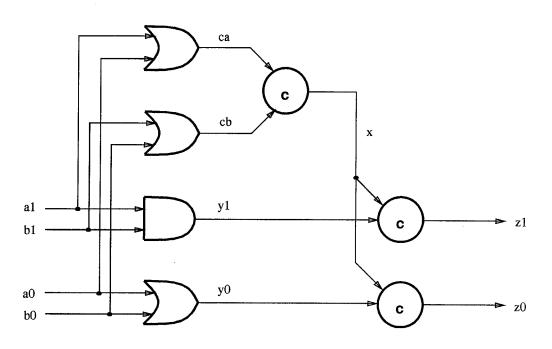

| 4.2 | Dual-rail delay-insensitive circuit for AND operator                   | 64  |

| 4.3 | Equivalent synchronous circuit for AND operator                        | 64  |

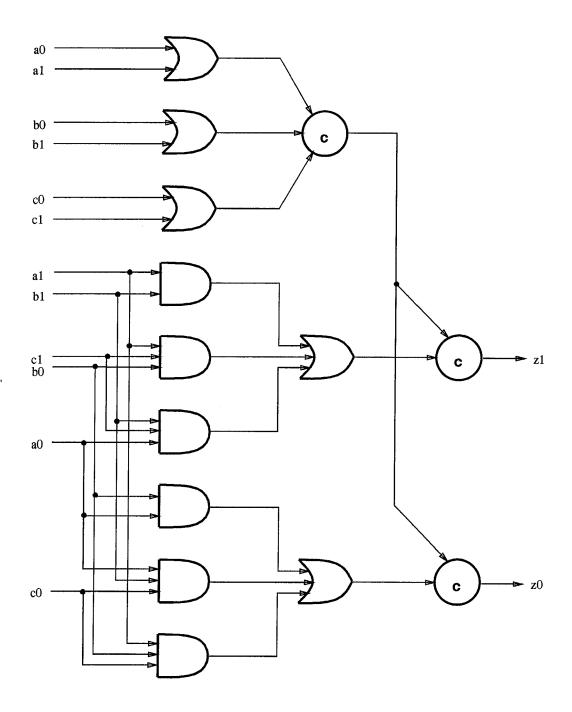

| 4.4 | Majority circuit                                                       | 74  |

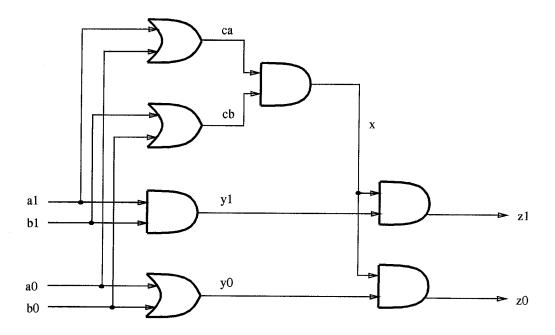

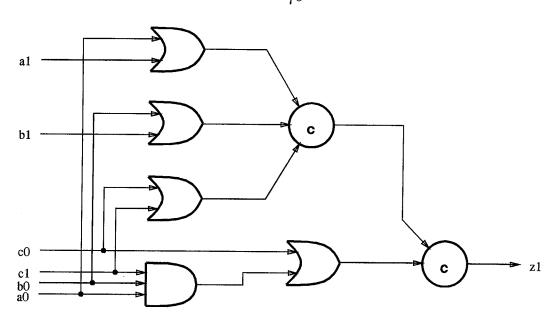

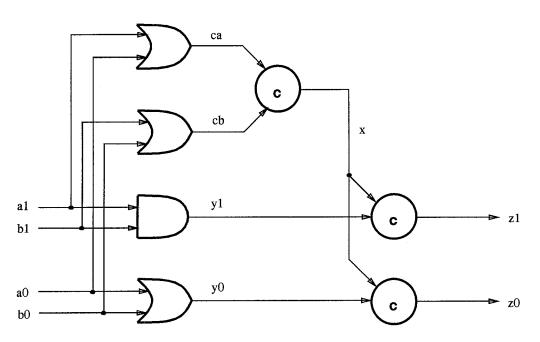

| 4.5 | Implementation of $z1$                                                 | 78  |

| 4.6 | AND operator                                                           | 87  |

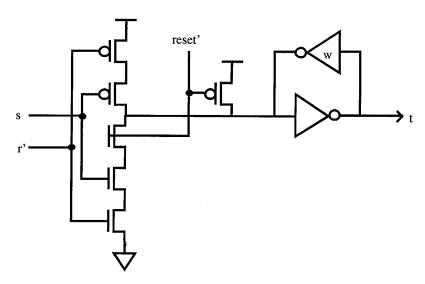

| 5.1 | C-element with added reset transistor                                  | 94  |

| 5.2 | C-element with additional reset transistor, to insure non-interference | 96  |

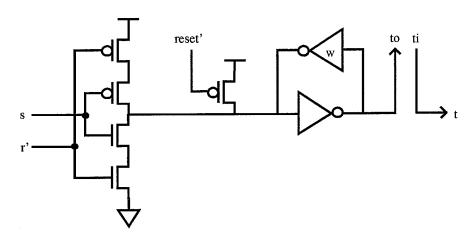

| 5.3 | C-element with output as a test point                                  | 97  |

| 5.4 | Implementation of buffer with two D-elements                           | 107 |

## xvii

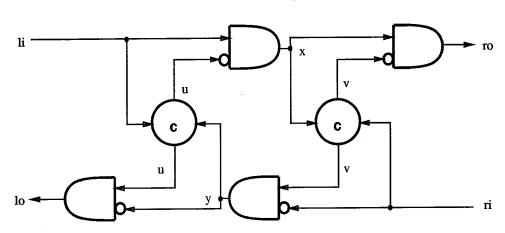

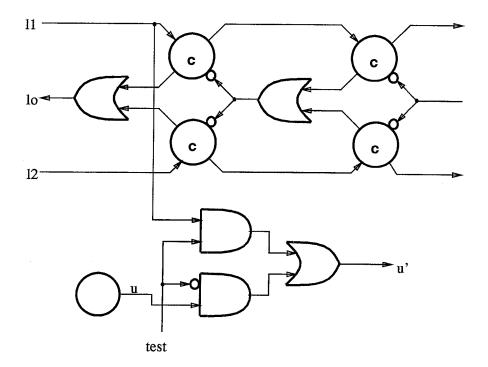

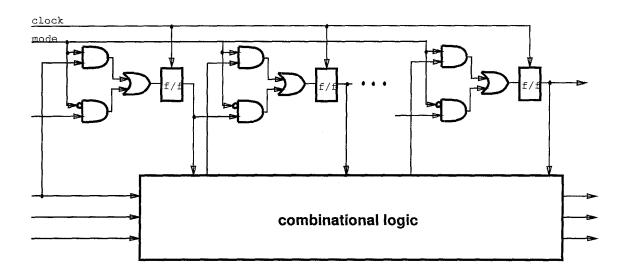

| 5.5 | Schematic of circuit with test queue                               | 110 |

|-----|--------------------------------------------------------------------|-----|

| 5.6 | Circuit of a queue element for an observation point                | 119 |

| 5.7 | Circuit of a queue element for a control point                     | 120 |

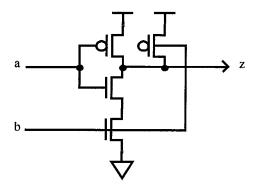

| 6.1 | CMOS implementation of a NAND gate                                 | 133 |

| 6.2 | Dynamic CMOS implementation of a C-element                         | 135 |

| 6.3 | CMOS implementation of a C-element, with weak inverter             | 136 |

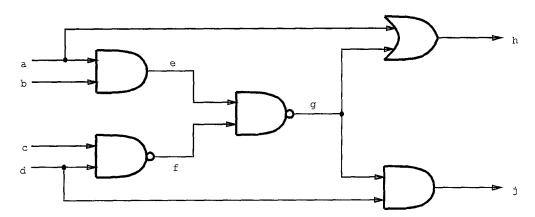

| B.1 | Combinational circuit C1                                           | 152 |

| B.2 | Delay-insensitive circuit $C2$ , a D-element                       | 161 |

| B.3 | Combinational circuit C3. A test for fault e stuck-at-0 is derived |     |

|     | using the D-algorithm                                              | 171 |

| B.4 | Test generation for a sequential circuit by replication            | 172 |

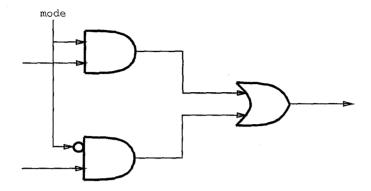

| B.5 | A double-throw switch                                              | 174 |

| B.6 | A sequential synchronous circuit with shift-register modification  | 175 |

|     |                                                                    |     |

#### CHAPTER 1

#### Introduction

Delay is preferable to error

— Thomas Jefferson

In this thesis, I develop a method to test delay-insensitive circuits that have been synthesized from a high-level specification. The fault model is the single stuck-at fault model. A test is derived from the high-level specification of the circuit. Most, but not all, faults cause the circuit to halt during test. For faults that are not guaranteed to be detected by the environment, one or more test points have to be added. The number of test points needed to fully test the circuit is typically small, as is the added testing circuitry. Deriving a test from the high-level specification yields high fault coverage.

Most VLSI circuits currently produced are synchronous circuits; a central clock provides a synchronization mechanism for the computation performed in a system. As the feature size of circuits decreases, the complexity and speed increases. It is becoming difficult to translate this into improved performance. Since each clock pulse has to be distributed over the entire circuit, clock skew is a major obstacle to shortening of the clock cycle.

A way to avoid problems with clocks is to design circuits without clocks – asynchronous circuits. Few asynchronous circuits have been designed, since the design

process was not well understood. It was felt that these circuits are necessarily too big and too slow – if one can even overcome the problem of hazards and critical races.

Alain Martin has constructed a simple and powerful method for the design of delay-insensitive circuits [46, 47]. This type of circuit is a subclass of asynchronous circuits, where propagation delays in wires and gates are assumed to be arbitrary and unbounded (but finite). The delay-insensitive circuits are synthesized from a high-level specification. The specification is proven correct, whereupon a series of semantics-preserving operations are performed, to obtain a delay-insensitive circuit. The resulting circuits are free of hazards, since the synthesis method guarantees the absence of hazards, by construction.

At Caltech, we have designed and fabricated a number of delay-insensitive circuits, including a stack, a mutual exclusion circuit, a multiplier, a router, and a microprocessor [42, 50, 51]. These circuits have been reasonably fast, very robust to variations in temperature, voltage, and fabrication parameters, and have been fully functional on "first silicon".

We have shown that it is possible to design delay-insensitive circuits; that it is possible to design them reliably; and that delay-insensitive circuits can be used for a wide range of applications. A subsequent problem is to show that they can be tested. In this thesis, I investigate how to test delay-insensitive circuits using the stuck-at fault model.

The stuck-at fault model is a widely used model to derive tests for VLSI circuits. Many methods are known to generate minimal tests efficiently for testing synchronous circuits; efforts to adapt these methods to delay-insensitive circuits have not been very successful. I think this is, again, because the discipline of designing delay-insensitive circuits was not well understood, and because most prior efforts consisted of adapting methods for testing synchronous circuits to asyn-

chronous ones. Since the workings of a delay-insensitive circuit – and the methods to derive it – are so different from synchronous circuits, I believe that a different paradigm is needed for the test generation problem for delay-insensitive circuits. Rather than adapt any method for synchronous circuits, I investigate the testing problem based on the synthesis method with which the circuit was generated.

A traditional concern regarding testing of delay-insensitive circuits is the difficulty of testing for hazards and critical races. In order for a hazard to occur, there are constraints on some delays in the circuits; these delays vary with voltage, temperature, and fabrication variances. Moreover, when a hazard occurs in an internal node, it has to be propagated to a primary output, so that the result can be observed. This is exceedingly difficult.

I believe that the testing stage is the wrong level at which to analyze hazards. It is possible to design circuits that are hazard-free, using Martin's synthesis method. Such circuits function correctly regardless of voltage, temperature, and fabrication variances.

The traditional model for synchronous circuits is that of combinational logic to which clocked latches are added to provide feedback; the traditional method to test these circuits is to add test circuitry to the latches, so that the resulting circuit is feedback-free. The emphasis in testing synchronous circuits is on generating efficient tests to test combinational logic.

A similar approach has been proposed for delay-insensitive circuits [33, 61], but is impractical. The ratio of combinational gates to state-holding gates is much smaller than for synchronous circuits; to add test circuitry for each state-holding element in a delay-insensitive circuit is prohibitively expensive. Instead I analyze the circuit as is, and add test circuitry as necessary. The emphasis therefore is on testing sequential circuits.

The fault model I use is the single stuck-at fault model. In this model, a faulty

circuit has one fault; an input or an output of a gate is either permanently at a high voltage (stuck-at-1), or at a low voltage (stuck-at-0). The stuck-at fault model is not a realistic model of actual faults in a circuit. It is widely used, however, since it is conceptually simple, and since there is a strong correlation between faulty circuits and circuits that are rejected with a test for stuck-at faults [5]. A discussion of the accuracy of the stuck-at fault model is beyond the scope of this thesis.

It is of great value in the fault analysis that each delay-insensitive circuit is synthesized from a high-level specification. It is possible to analyze a circuit from just the gate-level specification; the search for test vectors is greatly facilitated if the specification of the circuit is known. For example, the instruction fetch process of the asynchronous microprocessor [51] consists of an if-statement with two cases. A test derived from the specification, consisting of executing each case of the if-statement once, detects 93 of 100 stuck-at faults in the circuit. Deriving the same test from just the gate-level specification of the circuit is vastly more difficult. I use the handshaking expansion as the specification of the circuit. This notation describes the sequence of actions on variables in the specification.

Some authors claim that for a delay-insensitive circuit any stuck-at fault causes the circuit to halt [7]. Consequently, it is not necessary to test a delay-insensitive circuit, since even a faulty circuit will never exhibit faulty behavior, and no test circuitry needs to be added to the circuit. I show that this is not the case for the general stuck-at fault model; some faults on inputs of gates never cause the circuit to halt. It is therefore necessary to test delay-insensitive circuits, and for some circuits test points need to be added to make them fully testable [52].

#### 1. Organization of the Thesis

In the next chapter, I outline the synthesis method for delay-insensitive circuits. The high-level description language is akin to Hoare's CSP (Communicating Sequential Processes). I describe the four-phase handshaking protocol with which processes communicate, and the resulting handshaking expansion, which is the notation from which tests are derived. The circuit itself is described in the form of a production rule set.

Chapter 3 is a description of the general problem of testing delay-insensitive circuits. I discuss the delay assumptions; I describe the two types of stuck-at faults, the inhibiting fault and the stimulating fault; I show that for each fault there is a state in the handshaking expansion where the fault causes a production rule to be inhibited or to fire prematurely; I derive conditions under which a fault inhibits a production rule, or causes a premature firing that is detected by the environment. From these conditions follow a series of simple theorems with which the testability of most faults in a circuit is trivially shown.

Chapter 4 concerns testing of datapaths. A delay-insensitive datapath differs from synchronous combinational logic, since it has state-holding elements; also, it is not implemented as a network of standard gates (AND, OR, inverter), but rather with fewer, more complex gates. The problem is the generation of a reasonably small test set with which to test all testable faults. I show that such a delay-insensitive circuit can be transformed into a circuit with only combinational gates; a test that detects all testable faults for this new circuit will also detect all testable faults in the delay-insensitive circuit, with one exception. I show that the D-algorithm can be adapted for use in delay-insensitive circuits.

In chapter 5 I explore some testing issues that are more technology-dependent, such as the initialization of the circuit, and faults causing interfering production rules. I also derive a design for test circuitry. This design does not use a clock,

but it is necessarily not fully delay-insensitive.

Finally, chapter 6 describes heuristics on how to derive a small test set from the test vectors for each individual fault. I describe a refinement of the stuck-at fault model, a model with stuck-on and stuck-open faults, and explain how to test circuits under this new model.

In appendix A are algorithms to test delay-insensitive circuits. Appendix B is an introduction to circuit testing.

#### 2. A Note on Notation

In the abstract reasoning about circuits, a low voltage is called 0 or false, and a high voltage 1 or true. The delay-insensitive circuit synthesis method is described entirely using false and true. I have followed this convention as much as possible. All boolean conditions are expressed with " $\land$ " and " $\lor$ ", rather than "." and "+".

If I were consistent, I would call the different faults stuck-at-false and stuck-at-true; instead, I have used the standard terms stuck-at-0 and stuck-at-1. For the description of the D-algorithm and the adaptation for delay-insensitive circuits I have also used 0 and 1 (in addition to X, D, and  $\overline{D}$ ), because these notations are well-known.

In boolean expressions,  $\wedge$  has higher binding power than  $\vee$ .

Throughout the thesis, I refer to circuits as delay-insensitive. For such circuits, delays (both for gates and for wires) are assumed to be unbounded (but finite) and arbitrary. An exception is the *isochronic fork*, for which the delays in all branches of the fork are assumed to be roughly the same. Such an assumption is necessary to be able to construct any interesting circuit. Because of the isochronic fork assumption, this class of circuits is sometimes called *quasi-delay-insensitive*.

### CHAPTER 2

## Synthesis of Delay-Insensitive Circuits

La chose importante, c'est la théorie, qui est mind-blowing. Et si j'ai raison, ma théorie va produire un crisis en world thinking et, avec luck, un Prix Nobel. Cela sera beau, n'est-ce pas?

—Miles Kington, L'Origine des Species, Dans une Version Complètement Modernisée

#### 1. Introduction

In this chapter I explain parts of the high-level synthesis method for delay-insensitive circuits that was developed by Martin [41, 42, 44, 45, 46, 47]. The high-level specification for circuits is in a language that is based on Hoare's CSP (Communicating Sequential Processes) [31]. There are several other high-level synthesis methods [17, 55, 70].

The organization of this chapter is as follows. I define gates and circuits; I explain the constructs of the high-level specification language, and the steps of the synthesis method that lead to a delay-insensitive circuit. The first step is at the program level, namely a decomposition of processes into smaller subprocesses. The next step is the generation of a four-phase handshaking expansion that establishes a communication protocol between processes. For communications where no data

are sent (synchronization channels) this is a straightforward transformation. For communication channels, where data are sent, I list several ways to encode data values into bits for use in delay-insensitive circuits. The third step is to transform the handshaking expansion so that each state is unique. This is done by reshuffling of actions and by the addition of state variables. The final transformation is from a handshaking expansion, where each state is unique, to a production rule set.

In addition to these steps of the synthesis method, I explain how a delay-insensitive circuit operates as a series of actions, where each action is acknowledged with the next action. For actions that are not acknowledged, the assumption that all delays are arbitrary and unbounded has to be restricted. I introduce isochronic forks as a way to insure correctness of circuits for which some actions are not acknowledged.

#### 2. Gates and Circuits

A circuit is a network of gates that interacts with its environment.

DEFINITION 2.1 (GATE). A gate is a circuit element with one or more inputs, and one output. It is described as a pair of production rules

$$\begin{cases}

B_u & \to z \uparrow \\

B_d & \to z \downarrow,

\end{cases}$$

where  $B_u$  and  $B_d$  are boolean expressions on the inputs of the gate (known as guards), and z is the output. If condition  $B_u$  holds, output z becomes **true** (denoted  $z\uparrow$ ), and if condition  $B_d$  holds, output z becomes **false** (denoted  $z\downarrow$ ).

An execution of a production rule is called a *firing*. If  $z \uparrow (z \downarrow)$  fires in a state where  $\neg z$  (z) holds, then the firing is *effective*, otherwise it is *vacuous*. Unless otherwise noted, I shall only consider effective firings in the sequel.

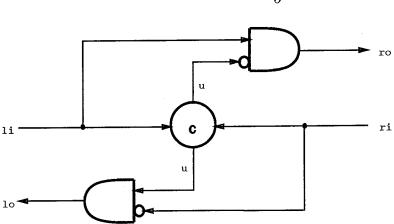

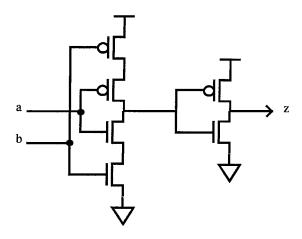

FIGURE 2.1. Schematic representation of AND gate and C-element A two-input AND gate with inputs a and b and output z has production rules:

$$\left\{ \begin{array}{cccc}

a & \wedge & b & \rightarrow & z \uparrow \\

\neg a & \vee & \neg b & \rightarrow & z \downarrow .

\end{array} \right.$$

A Muller C-element [57, 58] with inputs a and b and output z has production rules:

$$\left\{ \begin{array}{cccc}

a & \wedge & b & \rightarrow & z \uparrow \\

\neg a & \wedge & \neg b & \rightarrow & z \downarrow .

\end{array} \right.$$

See figure 2.1.

The guards of the production rules of a gate have to be mutually exclusive. Otherwise it is possible that both production rules can fire at the same time. In an actual implementation this causes a short circuit.

Definition 2.2 (Non-Interference). For a gate with production rules

$$\begin{cases}

B_u & \to z \uparrow \\

B_d & \to z \downarrow,

\end{cases}$$

condition  $\neg B_u \lor \neg B_d$  has to hold at any time. This is known as non-interference.

Note that  $\neg B_u \lor \neg B_d$  is not necessarily a tautology. For instance an SR flip-flop with output q has production rules

$$\left\{ \begin{array}{ccc} s & \to & q \uparrow \\ r & \to & q \downarrow \, . \end{array} \right.$$

This flip-flop has to be used in such a way that s and r are not both true at the same time.

FIGURE 2.2. A circuit and its environment

If  $B_u \equiv \neg B_d$ , then the gate is a combinational gate. All other gates are state-holding elements. Examples of combinational gates are the AND gate, the OR gate, the XOR (exclusive-or) gate, and the inverter. The C-element and the SR flip-flop are both state-holding elements.

DEFINITION 2.3 (CIRCUIT). A circuit is an interconnection of gates, interacting with its environment. Each input of a gate is either connected to the output of another gate, or to the environment. An output of a gate may be connected to any number of inputs of other gates, and to the environment.

An input of a gate that is connected to the environment is a *primary input*; an output of a gate that is connected to the environment is a *primary output*. An output (of a gate) that is input to more than one gate is said to *fork*, as in the implementation there is a forking wire.

The environment of a circuit is also a circuit. The primary inputs of the environment of circuit C are the primary outputs of C; the primary outputs of the environment are the primary inputs of C (figure 2.2). The environment changes its primary outputs in such a way that circuit C operates according to specification. The environment never malfunctions. For most circuits, I shall not give an explicit description of the environment as a set of gates; rather, there is a spec-

FIGURE 2.3. A synchronous sequential circuit, with clocked stateholding elements

ification of the environment, relating the primary outputs to the primary inputs of the environment. I assume that there is a gate-level implementation of such a specification.

A circuit can be represented as a directed graph G, where each node is a gate. If the output of gate  $g_0$  is an input to gate  $g_1$ , then there is an arc from node  $g_0$  to node  $g_1$ . If the graph representation is acyclic, then the circuit is feedback-free.

For synchronous (or clocked) circuits each state-holding element is a clocked memory element. See figure 2.3. Operation of a synchronous circuit is as follows. During each cycle, the value of the output of each memory element is set, and the environment sets the primary inputs. The circuit fires production rules until there are no more effective firings. Then the values of the primary outputs are sent to

the environment, and the value of the output of each memory element is set to the value of its input. A convenient way to describe a synchronous sequential circuit is as a finite-state machine (FSM) [30, 38].

For asynchronous (or delay-insensitive) circuits there is no clocking mechanism to distinguish between cycles. Operation is as follows. Given the value of the output of each gate, and the value of each primary input, repeatedly fire any production rule that can fire. The primary inputs may be changed as long as the handshaking protocol is obeyed. For correct operation, each production rule has to be stable.

DEFINITION 2.4 (STABILITY). Production rule  $B_u \to z \uparrow$  is stable if, whenever  $B_u \land \neg z$  holds,  $B_u$  remains true until  $z \uparrow$  has fired, that is, until z is true. Similarly for  $z \downarrow$ .

A common restriction on the usage of an asynchronous circuit is that it can only be used in *Fundamental Mode*, that is, a primary input may only change value if there is no production rule in the circuit that can fire [57]. All delay-insensitive circuits in this thesis operate correctly even when a primary input changes value concurrently with the firing of a production rule in the circuit, as long as stability of each production rule is guaranteed.

## 3. The High-Level Specification

The high-level specification, from which a delay-insensitive circuit is synthesized, is based on Hoare's CSP [31]. A program consists of one or more concurrent processes. Each process itself is described with a sequential program. There are no shared variables. Instead, processes communicate values via *channels*. Channels are also used as a means of synchronization between processes. A channel connects two processes, and a communication on a channel is slackless [32].

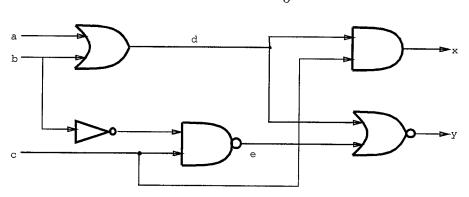

FIGURE 2.4. Channel (X, Y) between processes P and Q

Let (X, Y) be a channel between processes P and Q. See figure 2.4. In process P, X is known as a port. Since the communication is slackless, at any time the number of completed X actions in P is the same as the number of completed Y actions in Q. If process P attempts to do a communication X, while process Q cannot do a communication Y, then process P is suspended until Q does a communication Y. Both X and Y then complete at the same time. As a progress condition, X and Y cannot both be suspended at the same time.

In a digital circuit, each variable is either at a high voltage or at a low voltage. Therefore all variables in the language are boolean variables. It is sometimes advantageous to abbreviate a vector of boolean values with a single identifier, for instance when describing arithmetic operations. It is necessary to describe how each integer value is mapped onto a boolean vector. In section 5 I describe some of the systematic mappings from integers to booleans for delay-insensitive circuits.

- **3.1.** Language Constructs. The constructs in the high-level specification are:

- Parallel composition for processes. The parallel execution of processes P and Q is denoted "P||Q". Parallel composition is associative and commutative.

- Sequential composition of statements S and T is denoted "S;T". Sequential composition is associative.

- Parallel composition of atomic statements s and t is denoted "s,t". Parallel composition is associative and commutative.

- Assignment statement. The assignment operator is ":=". For a boolean variable b the assignment to **true** is abbreviated to  $b\uparrow$  and the assignment to **false** is abbreviated to  $b\downarrow$ .

- Selection. The selection command consists of a number of guards (boolean expressions on the variables in the program),  $G_0, G_1, \ldots, G_{n-1}$ , and an equal number of program parts,  $S_0, S_1, \ldots, S_{n-1}$ , denoted

$$[G_0 \to S_0 | G_1 \to S_1 | \dots | G_{n-1} \to S_{n-1}].$$

A program part  $S_i$  is executed for which  $G_i$  evaluates to true. If more than one guard is true, a nondeterministic choice is made; if no guard evaluates to true, then the process is suspended until a guard is true.

• Repetition. The repetition command also consists of a number of guards and an equal number of program parts, and is denoted

$$*[G_0 \to S_0|G_1 \to S_1|\dots|G_{n-1} \to S_{n-1}].$$

As long as there is a guard that evaluates to true, a program part  $S_i$  is executed for which  $G_i$  is true. If no guard holds, then the repetition terminates.

- Send and receive on a port. Let process P have a port X. Sending the value

of s on port X is denoted X!s, and X?t denotes a receiving communication

on port X whereby the value received is stored in t.

- Probed communication [43]. Let (X, Y) be a channel between processes P and Q. For process P, the probe of X (denoted  $\overline{X}$ ) is a boolean condition that holds when process Q is suspended on a communication Y.

In addition, the only form of recursion in the language is tail recursion.

There are a few abbreviations for constructs. The program part  $*[\mathbf{true} \to S]$ , for indefinite repetition of statement S, is abbreviated to \*[S], and the program part  $[G \to skip]$  (where a process waits for condition G to hold) is abbreviated to [G]. A frequently used notation is  $*[[G_0 \to S_0|G_1 \to S_1]]$ : wait until either  $G_0$  or  $G_1$  holds, then execute an  $S_i$  for which  $G_i$  holds, and repeat the program part.

Some channels are used solely to synchronize two processes. For process P with a port X of such a synchronization channel a communication is simply written "X". Since no data are transmitted, there is no difference between a send and a receive action for a synchronization channel.

3.2. Examples of Programs. A buffer is a FIFO queue. It consists of a number of processes. Each process has two ports, L to a channel connecting the process to its left neighbor, and R to a channel connecting it to its right neighbor. The buffer repeatedly communicates to its left neighbor, then communicates to its right neighbor. If each channel is a synchronization channel then a program for a buffer process is

$$*[L; R].$$

If the buffer sends and receives values, there is one variable, x:

$$*[L?x;R!x].$$

As an example of a probed communication, a buffer that sends the value stored to its right neighbor before it receives a new value has program:

$$*[[\overline{L} \to R!x, L?x]].$$

**3.3. Program Decomposition.** At the program level, it is often advantageous to split a large process up into two or more smaller processes. A number of channels are introduced to connect these subprocesses, while the existing channels to other processes remain the same.

Process decomposition is done using the

**Decomposition Rule:** A process, P, containing an arbitrary program part, S, is semantically equivalent to two processes, P1 and P2, where P1 is derived from P by replacing S with a communication action, C, on the newly introduced channel (C, D) between P1 and P2, and P2 is the process  $*[[\overline{D} \to S; D]]$  [47].

If a process is decomposed into several processes using the decomposition rule, then these subprocesses are never active concurrently. Therefore the subprocesses may use shared variables.

## 4. The Handshaking Expansion

The next step in the synthesis of a delay-insensitive circuit from a high-level specification is the transformation from a program to a handshaking expansion. In the handshaking expansion, the communications with neighboring processes are specified by actions on ports, using the handshaking variables.

Let (X, Y) be a synchronization channel connecting processes P and Q. Port X in P consists of two variables, output xo and input xi, and port Y in Q consists of output yo and input yi. The channel connects the ports with two (directed) wires, from xo to yi, and from yo to xi.

The implementation of a communication on the channel is asymmetric. One port initiates the communication (it sends a "request"), and the other reacts (it sends an "acknowledgement"). The first is known as the *active* port, the latter as the *passive* port. Without loss of generality, assume that X is active, and Y passive. Then each communication X in the program is implemented as the sequence

$$xo\uparrow; [xi]; xo\downarrow; [\neg xi],$$

and each communication Y in the program is implemented as the sequence

$$[yi]; yo\uparrow; [\neg yi]; yo\downarrow$$

.

Initially all variables of the channel are false. Process P initiates the communication by raising xo. After Q has detected this (when yi is true), it acknowledges by raising yo. Then process P resets xo to false, after which process Q resets yo to false. This communication protocol is known as a four-phase handshake.

Notice that there is no concurrency between the processes while a synchronization on the channel is executed. The sequence of events during a communication is:

$$xo\uparrow; [yi]; yo\uparrow; [xi]; xo\downarrow; [\neg yi]; yo\downarrow; [\neg xi].$$

An alternative implementation for the active port is as a *lazy-active* port [11, 47], where the final wait-action is postponed until the next communication on the channel:

$$X \equiv [\neg xi]; xo \uparrow; [xi]; xo \downarrow.$$

- **4.1. The Probe.** If process P initiates a communication X, and Q does not immediately acknowledge with a communication Y, then P is suspended. Process Q detects that P is suspended when yi holds. Therefore an implementation of  $\overline{Y}$  is the condition yi. If a port is probed, it must be implemented as a passive port.

- 4.2. Two-Phase Handshaking. In the four-phase handshaking expansion above, the final two actions in both X and Y are not necessary to achieve a synchronization between processes. These resetting actions can be useful, however, since they insure that for each communication the initial state of all variables is false.

It is possible to expand the odd-numbered communications as

$$X \equiv xo\uparrow; [xi]$$

$$Y \equiv [yi]; yo \uparrow,$$

FIGURE 2.5. Buffer process with left and right ports and the even-numbered communications as

$$X \equiv xo \downarrow; [\neg xi]$$

$$Y \equiv [\neg yi]; yo \downarrow.$$

This is known, for obvious reasons, as a two-phase handshake.

In the sequel I assume that the communication protocol is a four-phase handshake. The testing results are the same for each type of handshaking protocol.

## 4.3. Examples.

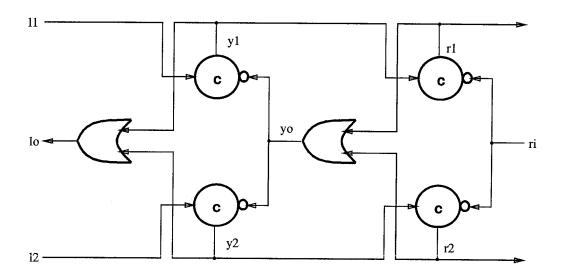

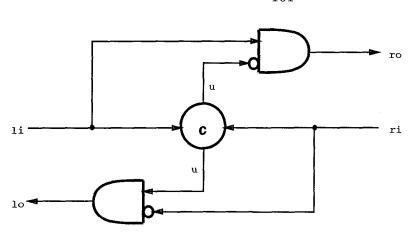

Example 2.1. For the buffer process \*[L;R], with L and R synchronization channels, let L be a passive, and R an active port. Port L has variables to and li, port R has variables ro and ri. See figure 2.5. The handshaking expansion for this buffer is:

$$*[[li];lo\uparrow;[\neg li];lo\downarrow;ro\uparrow;[ri];ro\downarrow;[\neg ri]].$$

Example 2.2. For the process  $*[[\overline{L} \to R; L]]$  port L is probed, and therefore has to be a passive port. If R is an active port the handshaking expansion is:

$$*[[li \rightarrow ro \uparrow; [ri]; ro \downarrow; [\neg ri]; lo \uparrow; [\neg li]; lo \downarrow].$$

## 5. The Handshaking Expansion for Communication Channels

To implement a communication channel (which can transmit data values), more than two wires are needed. Data values are transmitted using communication channels by raising one or more wires of the channel. For instance, consider a one-bit wide data channel A that is implemented with two wires, a0 and a1, in one direction, and one acknowledgment wire in the other. To transmit value "0" over channel A, wire a0 is raised, and to transmit value "1" wire a1 is raised.

For any test that detects all stuck-at faults, every wire in the circuit has to be raised at least once. Therefore both a0 and a1 have to be raised during such a test (but not simultaneously). An equivalent formulation is to require that a "0" and a "1" be sent over channel A during the test. For an arbitrary communication channel a set of data values has to be sent such that each wire of the channel is raised at least once. I call such a set a complete set:

DEFINITION 2.5 (COMPLETE SET OF DATA VALUES). Let A be a communication channel, where each value is encoded on N wires, and let S be the set of values that can be sent over channel A. Let  $w_j(s)$  be the value of the jth wire in the encoding of s. Set  $S_c$  is called a complete set of data values if

$$\forall_{0 \leq j < N} \exists_{s \in S_c} : w_j(s).$$

For the one-bit wide channel above  $S = S_c = \{0, 1\}$ . In general, the smallest complete set of data values for a communication channel is much smaller than the set of all values that can be sent over that channel. I examine a few standard ways to encode data values.

**5.1.** Dual-rail Encoding. For the dual-rail encoding scheme two wires are used for each bit in the binary representation of a number. If the jth bit is 0, wire 2j is raised, if it is 1, then wire 2j + 1 is raised. For N-bit numbers the channel consists of 2N data wires. With  $S = \{0, 1, \ldots, 2^N - 1\}$  a complete set of data values is  $\{0, 2^N - 1\}$ . Another is  $\{2^m - 1, 2^N - 2^m\}$ , for  $N \ge m$ . Dual-rail encoding is a widely used coding scheme.

Example 2.3. For a four-bit wide dual-rail encoded channel eight wires are used. If codewords are represented in the form of a string, then 0 might be encoded as 01010101, 1 as 01010110, etc. There are 16 different codewords, but a minimal complete set of data values has only two codewords, for example  $S_c = \{0, 15\}$ , corresponding to codewords 01010101 and 10101010, or  $S_c = \{5, 10\}$ , corresponding to codewords 01100110 and 10011001.

5.2. One-hot Encoding. If one wire is used per data value that can be transmitted, then the values are said to be one-hot encoded. The only complete set of data values is the set of all data values ( $S_c = S$ ). One-hot coding is only practical for narrow channels.

Example 2.4. For a four-bit wide one-hot encoded channel sixteen wires are necessary, as there are sixteen different codewords. For instance 0 is encoded as 000000000000001, 1 as 000000000000001, etc. The complete set of data values is  $\{0, 1, \ldots, 15\}$ .

5.3. k-out-of-N Encoding. The one-hot encoding scheme is a special case of so-called k-out-of-N codes [71]. To transmit a value over an N-bit wide channel, k wires are raised. A complete set of data values has at least  $\lceil N/k \rceil$  elements. Another special case is an N-out-of-2N code, where N wires are raised out of a total of 2N wires. A minimal complete set of data values has at least two elements, for instance the value corresponding to raising the first N wires and the value corresponding to raising the remaining N wires.

EXAMPLE 2.5. To encode four-bit values on seven wires a 2-out-of-7 code might be used. This code has 21 possible codewords: {0000011,0000101,...,1100000}. Another encoding uses six wires, with a 3-out-of-6 code. It has 20 different codewords: {000111,001011,001101,...,111000}. A complete set of data values to be sent over the channel depends on the mapping of values to codewords (there are

more codewords than values to be encoded). For a 2-out-of-7 code a complete set of data values might be  $\{0000011,0001100,01100000,1100000\}$ , and for a 3-out-of-6 code  $\{000111,111000\}$ .

For other encoding schemes, such as Berger codes [8, 23], it is easy to compute a minimal complete set of data values. For efficient encoding schemes [59], the minimal set is small, and its size independent of the size of the channel. For instance for dual-rail encoding and N-out-of-2N encoding the size of a minimal complete set of data values is two.

For two-phase handshaking protocols, the encoding for data channels is similar to the schemes above, except that a wire is raised or lowered only once per communication. In the case of two-phase communications, there are different ways to interpret the encoded data. As an example, I describe two schemes for dual-rail encoded data.

Consider a one-bit wide channel, A, with data wires a0 and a1. The first scheme is analogous to the one used for the four-phase protocol. For each "0" sent wire a0 is toggled, and for each "1" sent wire a1 is toggled. This scheme is conceptually simple, but has the disadvantage that the values of a0 and a1 alone are not enough to decode the value sent. For instance, if a0 and a1 are both 1, then the last value sent on channel A is either 0, if a0 was raised last, or 1, if a1 was raised last.

For the second scheme, the receiving process does not have to store extra information to decode the value sent. To send a 0, set a0 to 0, and to send a 1, set a0 to 1. Furthermore, if a 0 is sent after a 0, or if a 1 is sent after a 1, then a1 is toggled. For each value sent, exactly one wire is toggled. The value sent is always a0.

The complete set of data values in the first scheme is  $\{0,1\}$ . It is not possible to compute a complete set of data values for the second scheme, as the order in which values are sent over the channel is important. The channel is tested by sending

either a 0 followed by another 0, or by sending a 1 followed by another 1.

#### 6. Reshuffling and State Assignment

The goal of the synthesis method is to derive a delay-insensitive circuit, described as a production rule set. The production rule set should be equivalent to the handshaking expansion, that is, if a production rule can fire in the production rule set, then the corresponding transition in the handshaking expansion can occur, and vice versa. The main difference between the handshaking expansion and the production rule set is that there is explicit sequencing in the handshaking expansion (by means of semicolons), whereas the production rules may fire concurrently.

The task, then, is to remove the sequencing from the handshaking expansion to obtain an equivalent production rule set. Each state in the handshaking expansion must be unique. If two states are identical, one or more *state variables* have to be introduced.

Example 2.6. For the buffer of example 2.2 the handshaking expansion is:

$$*[[li]; ro \uparrow; [ri]; ro \downarrow; [\neg ri]; lo \uparrow; [\neg li]; lo \downarrow].$$

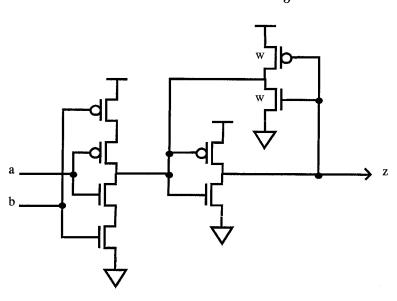

There are two indistinguishable states: the state where transition  $ro\uparrow$  takes place, and the state where  $lo\uparrow$  takes place. With the introduction of a state variable, u, each state is unique, with the following handshaking expansion:

$$*[[li]; ro \uparrow; [ri]; u \uparrow; [u]; ro \downarrow; [\neg ri]; lo \uparrow; [\neg li]; u \downarrow; [\neg u]; lo \downarrow].$$

A second method to make each state in a handshaking expansion unique is to reshuffle actions in the handshaking expansion. For instance, in a buffer with L and R communications, the actions on port L and the actions on port R may be interleaved. A requirement is that the actions on each port not violate the

four-phase handshaking protocol. In addition, for a set of concurrent processes, reshuffling of actions should not introduce a deadlock.

Example 2.7. In the buffer of example 2.1, there are two indistinguishable states: the initial state, and the state where  $ro \uparrow$  takes place. If the first three actions on port R are reshuffled as follows:

$$*[[li]; lo\uparrow; ro\uparrow; [\neg li]; [ri]; lo\downarrow; ro\downarrow; [\neg ri]],$$

then each state in the handshaking expansion is unique.

Reshuffling may drastically change the performance of the circuit [11, 13].

#### 7. The Production Rule Set

After the introduction of state variables, and the reshuffling of actions, each state in the handshaking expansion is unique. It is now rather simple to derive a production rule set. Let x be a variable in the handshaking expansion, and consider a transition  $x\uparrow$ . There is a boolean expression B on the variables in the handshaking expansion, such that B only holds in a state where  $x\uparrow$  occurs. The production rule

$$B \to x \uparrow$$

can then be added to the production rule set.

The next problem is how to derive condition B. If transition  $x \uparrow$  is preceded in the handshaking expansion by a wait action, [z] say, then  $x \uparrow$  can only fire after z has been observed. Hence z has to be included as a term in B. Term z is said to be included in the production rule by syntactic derivation.

EXAMPLE 2.8. For the buffer of example 2.2, with the state variable u of example 2.6, the production rules from the syntactic derivation are:

$$\begin{array}{cccc} li & \rightarrow & ro \uparrow \\ ri & \rightarrow & u \uparrow \\ u & \rightarrow & ro \downarrow \\ \neg ri & \rightarrow & lo \uparrow \\ \neg li & \rightarrow & u \downarrow \\ \neg u & \rightarrow & lo \downarrow \,. \end{array}$$

Syntactic derivation usually is not sufficient for a correct production rule set. For instance, in the above example the production rule for  $lo \uparrow$  may fire in the initial state (since all variables are false in the initial state). It is necessary to strengthen the guards of some production rules to prevent firings that are not in the specification.

Example 2.9. Continuing with the same buffer, the production rules for  $ro \uparrow$  and for  $lo \uparrow$  have to be strengthened, as follows:

After strengthening some guards, the resulting production rule set yields a circuit that is equivalent to the handshaking expansion. A final step that can be done is known as *symmetrization*. An example of symmetrization is to weaken one of a pair of production rules, so that the resulting pair is the specification of a combinational gate, rather than a state-holding element.

Example 2.10. To finish the buffer of example 2.6, weaken the production rule for  $ro \downarrow with \neg li$ . This is allowed since it does not cause the production rule to fire

FIGURE 2.6. Circuit C2, the D-element buffer process in a state where it could not fire before. The resulting pair of production rules is:

$$\left\{ \begin{array}{cccc} li & \wedge & \neg u & \rightarrow & ro \uparrow \\ \neg li & \vee & u & \rightarrow & ro \downarrow . \end{array} \right.$$

This is an AND gate with one inverted input. Weakening the production rule for  $lo\downarrow$  also changes the gate with output lo from a state-holding element to an AND gate with an inverted input:

$$\begin{cases}

\neg ri \land u \rightarrow lo \uparrow \\

ri \lor \neg u \rightarrow lo \downarrow.

\end{cases}$$

Finally, the production rules for u are the specification of a flip-flop. It is possible to strengthen both production rules so that the resulting pair is the specification of a C-element:

$$\begin{cases} li & \wedge & ri & \to & u \uparrow \\ \neg li & \wedge & \neg ri & \to & u \downarrow . \end{cases}$$

The circuit for this buffer is known as a D-element [12, 45]. See figure 2.6.

#### 8. The Role of the Environment

I now investigate the role of the environment of a circuit in the execution of the handshaking expansion. For the D-element, the initial action of the circuit, after it is set to its initial state, is to wait for li to hold. The environment can hold the circuit in this state for an indefinite time by holding li false. By contrast, after the environment has set li to true, transition  $ro\uparrow$  will follow eventually. The environment cannot delay  $ro\uparrow$  at that point. In the former case, the circuit is in a controllable state, whereas in the latter case it is in a transient state.

DEFINITION 2.6 (CONTROLLABLE AND TRANSIENT STATES). Let C be a circuit implementing a handshaking expansion for a single sequential process. A state in the handshaking expansion in which no production rule can fire, and the environment does not change any primary inputs, is a controllable state. Any other state is a transient state.

DEFINITION 2.7 (CONTROLLABLE AND TRANSIENT CONDITIONS). Let C be a circuit implementing a single sequential process, and B a boolean expression on variables of C. If there is a controllable state for which B holds, then B is a controllable condition. If B holds only in transient states, it is a transient condition.

The disjunction of two controllable conditions is a controllable condition, but the conjunction of two controllable conditions is not necessarily controllable. The negation of a transient condition is controllable, if there is at least one controllable state in the handshaking expansion.

For the D-element,  $\neg ro$  holds in the initial state, and is therefore a controllable condition. Also, li and  $\neg u$  are controllable conditions, as is  $li \land \neg u$ , but  $\neg ro \land li \land \neg u$  is a transient condition. The reason is that there is a production rule  $li \land \neg u \rightarrow ro \uparrow$  in the circuit.

### 9. Acknowledgments and Isochronic Forks

In a delay-insensitive circuit there is a strict sequencing of actions. An action can only take place after the previous action has been completed; it acknowledges

the completion of the previous action. After the environment changes the value of some primary inputs, there is a number of transitions in the circuit and some transitions of primary outputs. The transitions of the primary outputs acknowledge the transitions of the primary inputs. Once the environment observes the changes of the primary outputs, the necessary changes of the internal variables are guaranteed to have taken place. Consequently, there is no need to make the assumption that the circuit operates in Fundamental Mode.

DEFINITION 2.8 (ACKNOWLEDGEMENT). Let C be a circuit, and consider a gate with input s and output t. If there is a transition  $t \uparrow$ , following a transition  $s \uparrow (s \downarrow)$ , in the handshaking expansion such that this transition only occurs when  $s (\neg s)$  holds, then  $t \uparrow$  acknowledges transition  $s \uparrow (s \downarrow)$ . Likewise for transition  $t \downarrow$ .

It follows that if s is included in the production rule for  $t \uparrow$  by syntactic derivation or strengthening, then there is a transition  $t \uparrow$  in the handshaking expansion that acknowledges transition  $s \uparrow$ .

Example 2.11. Consider the following production rules for the D-element:

$$\left\{ \begin{array}{cccc} li & \wedge & \neg u & \rightarrow & ro \uparrow \\ \neg li & \vee & u & \rightarrow & ro \downarrow . \end{array} \right.$$

Since  $[\neg ri]$  precedes transition  $ro\uparrow$  in the handshaking expansion,  $ro\uparrow$  acknowledges  $ri\downarrow$ . Condition  $\neg u$  was added to the guard for  $ro\uparrow$  by strengthening, therefore  $ro\uparrow$  also acknowledges transition  $u\downarrow$ . Transition  $ro\downarrow$  acknowledges transition  $u\uparrow$  (syntactic derivation), but not transition  $li\downarrow$ , since  $\neg li$  does not hold when  $ro\downarrow$  fires.

Each transition of a variable (corresponding to the output of a gate) in a delayinsensitive circuit, that is not a primary output, is acknowledged with another transition. A transition of a variable is not necessarily acknowledged by a transition of the output of each gate for which the variable is an input.

All delays are assumed to be arbitrary and unbounded. In case a transition of an input of a gate is not acknowledged with a transition of the output of the gate, the circuit may malfunction [48]. For instance, if a transition  $li \downarrow$  is propagating much slower to the gate with output ro than to the C-element, then a transition  $ro \uparrow$  may occur before transition  $li \downarrow$  has been observed by the gate with output ro. For the circuit to operate correctly, the propagation delay of transition  $li \downarrow$  to the gate with output ro must be shorter than the propagation delay of  $li \downarrow$  to the C-element, plus the propagation delay of transition  $u \downarrow$  to the gate with output ro.

Because of this delay assumption, the fork of variable *li* is known as an *isochronic* fork. Circuits with isochronic forks are sometimes referred to as quasi-delay-insensitive circuits [48].

DEFINITION 2.9 (ISOCHRONIC FORK). Let C be a circuit with a variable s that forks to several gates, including a gate with output t. If there is a transition  $s \uparrow$  or  $s \downarrow$  in the handshaking expansion that is not acknowledged with a transition of t, then the fork of s is an isochronic fork.

For all isochronic forks a delay assumption has to be made to insure correctness of the circuit. For some, the delay assumption is "one-sided". For instance, whereas there is an upper bound on the delay of transition  $li \downarrow$  to the gate with output ro, no such delay assumption is necessary for the propagation delay of any transition of li to the C-element. I therefore refine the concept of an isochronic fork, and call the former branch of the fork an isochronic branch.

DEFINITION 2.10 (ISOCHRONIC BRANCH). Let C be a circuit with a variable s that forks to several gates, including a gate with output t. If there is a transition

$s \uparrow or s \downarrow in the handshaking expansion that is not acknowledged with a transition of t, then the branch of s to the gate with output t is an isochronic branch.$

In addition to the branch of li to the gate with output ro, the D-element also has an isochronic branch for variable ri as input to the gate with output lo.

#### CHAPTER 3

### A Method to Test Delay-Insensitive Circuits

But there was another source of errors in PETER: unreliable soldering points which are very difficult to detect because 99.9 percent of the time they function properly. In the course of time an efficient method was developed to find them. A fist or hammer was used and by banging on the racks numerous weak soldering points were discovered.

— N. C. de Troye, From Arra to Apple

#### 1. Introduction

In this chapter I discuss a method to test delay-insensitive circuits. First I discuss problems associated with testing. In particular the assumption that all delays are finite but unbounded means that no fault is testable. I therefore have to make some assumption on propagation delays.

I show that a stuck-at fault in a delay-insensitive circuit may either cause a production rule to fire when it should not, or not to fire when it should. In the former case the fault is *stimulating*, in the latter it is *inhibiting*. Some faults are both stimulating and inhibiting. For each inhibiting fault there is a state in the handshaking expansion where the fault causes a transition not to take place when

it should; for each stimulating fault there is a state in the handshaking expansion where the fault causes a transition to occur when it should not. The testing problem is to bring the faulty circuit in such a state, and to propagate the result to a primary output, which can be observed by the environment. As a larger example I analyze the faults in a one-bit queue element.

Let a and b be variables in a circuit, where a is an input to the gate with output b. There is a difference between a fault on variable a, that is a primary input or the output of a gate, and the input a of the gate with output b. Since a production rule set typically does not include production rules for forks, this difference is implicit in a production rule set. When it is not clear from the context which variable is being discussed, I denote the input a to the gate with output b as a[b].

In a delay-insensitive circuit there are sequences of transitions, where each transition is acknowledged with the next one. In theorems about faults I frequently have to refer to a "next" transition. It does not matter whether such an acknowledging transition is an up- or a down-transition. For the sake of clarity I shall always assume that it is an up-transition.

Finally, most inhibiting faults are detected when a sequence of acknowledgements does not take place. The environment then detects the fault, as there is a missing transition of a primary output. I have to assume that there is always a next transition of a primary output in each state of the handshaking expansion. In other words, either a program is terminating, and ends with a transition of a primary output, or the program is non-terminating and it is always possible to have a transition of a primary output later.

#### 2. Problems with the Delay Model

The purpose of testing chips is to separate the fully functional ones from the faulty ones. The goal is twofold: first, to accept only those chips that have no

defects, and second, to reject as few as possible (ideally: none) of the chips without defects. The latter objective is typically the easiest to meet; any non-defective chip ought to pass any test. It is, however, impossible to guarantee that only non-defective chips be accepted. Even if we can prove that all faults are detectable by some test, such a proof is given with the assumption of some fault model. There can always be faults that cannot be described in the fault model.

DEFINITION 3.1 (TEST). A test for circuit C is a finite sequence of actions by the environment of C. An action is either setting the value of a primary input of C, or observing the value of a primary output of C.

Executing a test consists of setting the primary inputs of the circuit, and observing the primary outputs. After the correct primary output transitions have been observed, one has to wait for some time before changing the primary inputs again; it is possible that there is another transition of a primary output pending, in a faulty circuit.

I use a straightforward definition of testable faults: a fault is testable if there is a sequence of inputs to the circuit, such that the fault is *guaranteed* to be detected.

DEFINITION 3.2 (DETECTED FAULT). Let T be a test for circuit C. Let circuit C' be the same circuit, but with a single stuck-at fault. If, during execution of test T, there is a point at which a primary output of C' has a value that cannot occur at the same point in the test for circuit C, then the fault is detected.

DEFINITION 3.3 (DETECTABLE FAULT). A fault in circuit C is detectable with test T if the fault is guaranteed to be detected, regardless of the propagation delays in the circuit.

DEFINITION 3.4 (TESTABLE FAULT). A fault in circuit C is testable if there is a test that detects the fault.

For a discussion of these definitions, see appendix B. Unfortunately, with the model for asynchronous circuits, the definition of a testable fault implies that *no* fault is guaranteed to be detected. Recall that for self-timed circuits any gate delay and wire propagation delay is arbitrary and unbounded.

We test a circuit by setting the value of its inputs, and observing the values of its outputs. A circuit is faulty when the value of its outputs is not the same as the value of the outputs for a correct circuit. This can happen when either for the faulty circuit an output changes value when the correct circuit does not, or when for the correct circuit an output changes value when the faulty circuit does not. When there is an unexpected change of an output, then the circuit, obviously, is a faulty one. But if a change of output value does not take place while a change is expected, can we conclude that the circuit is faulty? Since wire delays are assumed to be arbitrary and unbounded, it is possible, at any time, that there will be a change of the output value some time later. I show in this chapter that there is a large number of faults in any circuit that lead to the circuit halting in some state. In an actual test, there is no point in time, at which we can conclude that a circuit with such a fault is to be rejected.

Likewise, if, in some state, a correct circuit does not change its outputs, then the observation that a circuit under test, in the same state, does not change its value either, does not imply that the circuit behaves correctly. It may be the case that there is a change of an output pending, that is not yet observed because of the unbounded wire delay.

An even worse scenario is the following: consider a circuit, delete all internal circuitry, and connect each output pad to a ring oscillator. Assume that each ring oscillator can be reset so that the outputs in the initial state for both the original circuit and the one with the ring oscillators are the same. Then no test will guarantee that the ring oscillators can be distinguished from the original circuit.

With the delay assumptions made here, there is no test that will accept only correct circuits, and there is no test that will reject only defective circuits, since the delay assumptions require that a circuit be observed for an infinite time before any conclusions can be made. From a theoretical point of view, the testing problem cannot be solved.

The problems described above are, however, merely theoretical problems. In any actual test, the difference between any circuit and a ring oscillator will be immediately obvious from the behavior of the circuits. With modern technologies, switching times are on the order of nanoseconds, or even picoseconds, and variations in switching times are relatively minor. A ring oscillator will change the value of the output frequently, so if we do not change the value of the inputs, the original circuit will not change its outputs, whereas the ring oscillator will. Also, if a circuit under test does not switch within, say, a microsecond after a correct circuit switches, then we may safely assume that the circuit is faulty.

There are two types of faults. Some faults cause the circuit to halt entirely, and some faults result in an unspecified output change. I consider such occurrences detectable. I could extend the definition of detectability: in the presence of some faults an output of a circuit will switch faster than expected. However, it may be hard to tell whether such an occurrence takes place because of a fault or because the chip happens to be relatively fast.

To the above observations I add an important caveat, concerning testing of arbitration devices. As is well-known, any arbitration device has a metastable state, when arbitrating between two alternatives. The time that the arbiter takes to leave such a state is arbitrary and unbounded [16]. Therefore it is not enough to wait a microsecond or so for outputs to change. Typically it is possible to test an arbiter by having only one request valid at any time. The arbiter is then considered equivalent to two wires, where the wires are not both high at the same

time. If the actual arbitration is tested, then the methods described here do not apply. The simplest way to test an arbiter is to add test circuitry with which it can be functionally separated from the remainder of the circuit.

#### 3. A Classification of Stuck-At Faults

For a given production rule a fault may reduce the number of states in which the production rule may fire, or it may increase the number of such states. In the former case, the fault *inhibits* the production rule, and in the latter case it stimulates the production rule.

I assume that each circuit is non-redundant. A variable is redundant if each occurrence of the variable in the production rules can be replaced with **true** or **false**. A gate is redundant if its output is redundant. A circuit is redundant if it has a redundant gate, or a gate with a redundant input. See Appendix B. Note that a production rule in a non-redundant circuit may still have a redundant literal, or a redundant term. (A literal is a boolean variable, or its negation.) In particular, weakening production rules introduces redundant literals.

DEFINITION 3.5 (INHIBITING FAULT). Let C be a circuit that has a gate with input s and output t. Consider a production rule for t. If it contains a non-redundant term with literal s ( $\neg s$ ), then fault s stuck-at-0 (s stuck-at-1) is inhibiting the production rule.

DEFINITION 3.6 (STIMULATING FAULT). If a production rule for t contains a non-redundant term with literal s ( $\neg s$ ), then fault s stuck-at-1 (s stuck-at-0) is stimulating the production rule.

An inhibiting fault reduces the set of states in which a production rule may fire. Such a fault may be tested by bringing the circuit in a state where the correct production rule fires, and the production rule with the fault does not. A stimulating fault augments the set of states in which a production rule may fire. Such a fault may be tested by bringing the circuit in a state where the correct production rule does not fire, but the production rule with the fault does. The following theorems state that, both for inhibiting and stimulating faults, there is always such a state in the handshaking expansion.

THEOREM 3.1. Let C be a non-redundant circuit that has a gate with input s and output t. Let s stuck-at-0 be an inhibiting fault. Then there is a state in the handshaking expansion where the fault causes a production rule for t not to fire when it should. Similarly for fault s stuck-at-1.

**Proof:** The general form of the production rules for t is:

$$\begin{cases} s \wedge B_0 & \vee & \neg s \wedge B_1 & \to & t \uparrow \\ s \wedge C_0 & \vee & \neg s \wedge C_1 & \to & t \downarrow, \end{cases}$$

where each  $B_i$  and  $C_i$  is a boolean expression not containing s. Consider fault s stuck-at-0. With this fault, the guard for  $t \uparrow$  reduces to  $B_1$ . The fault inhibits a transition  $t \uparrow$  if there is a state in the handshaking expansion where

$$\neg t \wedge (s \wedge B_0 \vee \neg s \wedge B_1) \wedge \neg B_1,$$

that is

$$\neg t \wedge s \wedge B_0 \wedge \neg B_1$$

.

If s is not redundant in the guard for  $t\uparrow$ , then there is a state in the handshaking expansion where  $t\uparrow$  fires, so that  $t\uparrow$  is an acknowledgement for transition  $s\uparrow$ , and  $s \land B_0$  holds when  $t\uparrow$  fires. If  $B_1$  holds in this state, then  $t\uparrow$  may fire before the gate observes transition  $s\uparrow$ , that is,  $t\uparrow$  does not acknowledge  $s\uparrow$ . Hence  $\neg B_1$  must hold. Therefore there is a state in the handshaking expansion where a transition  $t\uparrow$  is inhibited, if s is not redundant in the up-guard. Similarly if s not redundant in the down-guard.

THEOREM 3.2. Let C be a non-redundant circuit that has a gate with input s and output t. Let s stuck-at-0 be a stimulating fault. Then there is a state in the handshaking expansion where the fault may cause a production rule for t to fire when it should not. Similarly for fault s stuck-at-1.

**Proof:** The general form of the production rules for t is:

$$\begin{cases} s \wedge B_0 & \vee & \neg s \wedge B_1 & \to & t \uparrow \\ s \wedge C_0 & \vee & \neg s \wedge C_1 & \to & t \downarrow, \end{cases}$$

where each  $B_i$  and  $C_i$  is a boolean expression not containing s. Consider fault s stuck-at-0. With this fault, the guard for  $t \uparrow$  reduces to  $B_1$ . The fault may cause a premature transition of  $t \uparrow$  if there is a state in the handshaking expansion where

$$\neg t \wedge B_1 \wedge \neg (s \wedge B_0 \vee \neg s \wedge B_1),$$

that is

$$\neg t \wedge s \wedge \neg B_0 \wedge B_1$$

.

If  $\neg s$  is not redundant in the guard for  $t\uparrow$ , then there is a state in the handshaking expansion where  $t\uparrow$  cannot fire, and where  $s \land \neg B_0 \land B_1$  holds; in this state the fault may cause a premature firing. Similarly for  $\neg s$  in the down-guard.

The next theorem states that any fault on an output of a gate is both stimulating and inhibiting.

Theorem 3.3. Let C be a delay-insensitive circuit. Let s be a variable in C that is either a primary input, or the output of a gate, but not a primary output. Then faults s stuck-at-0 and s stuck-at-1 are both inhibiting and stimulating.

**Proof:** Consider, without loss of generality, the fault s stuck-at-0. Since s is not a redundant variable in C, there is a transition  $s \uparrow$  in the handshaking expansion (or [s] if s is a primary input). Let  $u \uparrow$  be a transition directly following this

transition  $s \uparrow$ . Then s must be an input to the gate with output u, and transition  $u \uparrow$  acknowledges transition  $s \uparrow$ . The production rule for  $u \uparrow$  is of the form

$$s \wedge B_0 \vee B_1 \rightarrow u \uparrow$$

,

where  $s \wedge B_0$  is not redundant. With a fault s stuck-at-0 the same production rule reduces to