## Wiring Considerations in Analog VLSI Systems, with Application to Field-Programmable Networks

Thesis by

Massimo Antonio Sivilotti

In Partial Fulfillment of the Requirements

for the Degree of

Doctor of Philosophy

California Institute of Technology

Pasadena, California USA

1991

(Defended July 17, 1990)

.

## Acknowledgments

I am greatly indebted to Carver Mead, whose unfailing support and guidance through the long years made this work possible. His insight and encouragement were critical components in the process of my learning to do research. The environment that he created for his students was rich and fertile; in leading by example, Carver is a role model for all of us.

I would also like to thank my committee, Professors Yaser Abu-Mostafa, Al Barr, Sandeep Bhatt, Alain Martin, and Carver Mead, for their helpful comments and patient review of this thesis. Their office doors were always open to me, despite pressing commitments and demanding students of their own. It was an honor, and a privilege, to work with these gentlemen.

I owe much gratitude to my colleagues and fellow students in Carver's research group. In particular, the early work on implementations of neural networks was done in conjunction with Michael Emerling. The later work on self-timed retinal architectures was a collaboration with Misha Mahowald. In the intervening years, countless discussions with Steve DeWeerth, Michael, Tor Lande, Mary Ann Maher, Misha, John Tanner and John Wawryznek helped shape my research. Thanks also to the countless people who braved my design tools; even though I was not always as sympathetic as I should have been, their suggestions made it possible for all of us to get real chips done.

I owe what sanity I have today to a fabulous set of friends. Biking, hiking, camping, cooking, "Friday Lunching," WallyBall, indeed... Nan, Andy, SteveB, SteveD, Michael, JohnT, JohnW... what can I say? And what can I say about Ruth, other than, without her constant love and understanding, I would not be writing these words today?

Finally, I must acknowledge the moral support of my family, without which the long journey to Southern California would have been much more difficult.

This research was supported by the System Development Foundation and the Office of Naval Research, and by equipment grants from Hewlett-Packard. Integrated circuit fabrication was generously provided by MOSIS. I was personally supported by NSERC and IBM, for which I am grateful.

#### Abstract

This thesis develops a theoretical model for the wiring complexity of wide classes of systems, relating the degree of connectivity of a circuit to the dimensionality of its interconnect technology. This model is used to design an efficient, hierarchical interconnection network capable of accommodating large classes of circuits. Predesigned circuit elements can be incorporated into this hierarchy, permitting semicustomization for particular classes of systems (e.g., photoreceptors included on vision chips). A polynomial-time programming algorithm for embedding the desired circuit graph onto the prefabricated routing resources is presented, and is implemented as part of a general design tool for specifying, manipulating and comparing circuit netlists.

This thesis presents a system intended to facilitate analog circuit design. At its core is a VLSI chip that is electrically configured in the field by selectively connecting predesigned elements to form a desired circuit, which is then tested electrically. The system may be considered a hardware accelerator for simulation, and its large capacity permits testing system ideas, which is impractical using current means. A fast-turnaround simulator permitting rapid conception and evaluation of circuit ideas is an invaluable aid to developing an understanding of system design in a VLSI context.

We have constructed systems using both reconfigurable interconnection switches and laser-programmed interconnect. Prototypes capable of synthesizing circuits consisting of over 1000 transistors have been constructed. The flexibility of the system has been demonstrated, and data from parametric tests have proven the validity of the approach.

Finally, this thesis presents several new circuits that have become key components in many analog VLSI systems. Fast, dense and provably *safe* one-phase latches and hierarchical arbiters are presented, as are a low-noise analog switch, an isotropic novelty filter, a dense, active high-resistance element, and a subthreshold differential amplifier with a large linear input range.

## Contents

|   | Acl | knowle  | dgments                                              | iii |

|---|-----|---------|------------------------------------------------------|-----|

|   | Ab  | stract  |                                                      | v   |

| 1 | Int | roduct  | ion                                                  | 1   |

|   | 1.1 | Reade   | er's road map                                        | 3   |

| 2 | A I | Novel . | Associative Memory Implemented Using Collective Com- | •   |

|   | put | ation   |                                                      | 5   |

|   | 2.1 | Introd  | luction                                              | 6   |

|   | 2.2 | The C   | Content-Addressable Memory                           | 7   |

|   | 2.3 | The H   | Iopfield Model for Collective Systems                | 8   |

|   |     | 2.3.1   | A Continuous Model                                   | 10  |

|   | 2.4 | VLSI    | Considerations                                       | 12  |

|   |     | 2.4.1   | Cost                                                 | 12  |

|   |     | 2.4.2   | Power                                                | 13  |

|   |     | 2.4.3   | Parameter Variation                                  | 14  |

|   | 2.5 | Design  | and Fabrication of a VLSI Implementation             | 15  |

|   |     | 2.5.1   | Design of the Active Elements                        | 16  |

|   |     | 2.5.2   | Resistive Interconnect                               | 20  |

|   |      | 2.5.3 Programming the $T_{ij}$ Elements                              | 21        |  |

|---|------|----------------------------------------------------------------------|-----------|--|

|   | 2.6  | Fabrication History                                                  | 23        |  |

|   | 2.7  | Experimental Results                                                 | 24        |  |

|   | 2.8  | High-Density Preprogrammed Associative Memories                      | 29        |  |

|   | 2.9  | Summary                                                              | 31        |  |

| 3 | АТ   | Theoretical Model for Estimation of Circuit Wiring Density           | 35        |  |

|   | 3.1  | Introduction                                                         | 35        |  |

|   | 3.2  | Rent's Rule                                                          | 37        |  |

|   | 3.3  | An Operational Definition of Optimal Design                          | 37        |  |

|   | 3.4  | A Model for Circuit Connectivity                                     | 41        |  |

|   | 3.5  | Contact Density                                                      | 43        |  |

|   | 3.6  | Limits on Wire Length                                                | 44        |  |

|   |      | 3.6.1 Area Limits on Average Wire Length                             | 54        |  |

|   | 3.7  | Summary                                                              | 54        |  |

| 4 | A D  | Dynamically Configurable Architecture for Prototyping of Analog      |           |  |

|   | Circ | euits                                                                | <b>56</b> |  |

|   | 4.1  | Introduction                                                         | 57        |  |

|   | 4.2  | Connectivity of Circuits                                             | 60        |  |

|   | 4.3  | Hierarchy and Abstraction in System Design                           | 65        |  |

|   | 4.4  | Embedding a Circuit Graph                                            | 66        |  |

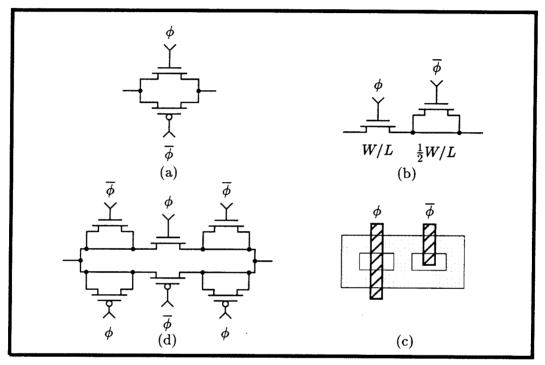

|   | 4.5  | Interconnect Switches                                                | 67        |  |

|   |      | 4.5.1 Reconfigurable Interconnect Switches                           | 67        |  |

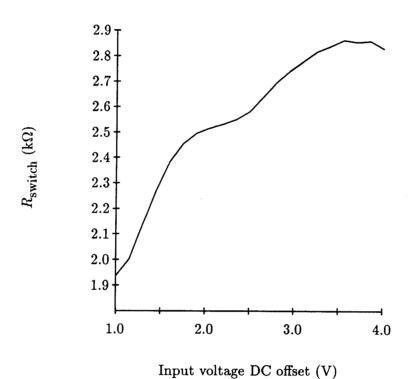

|   |      | 4.5.2 Scaling of Transmission Gate Transistors for Maximum Linearity | 69        |  |

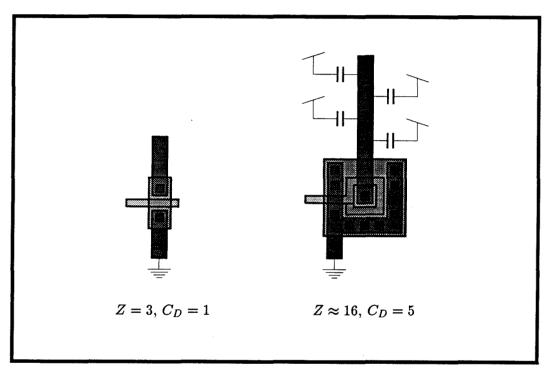

|   |      | 4.5.3 A High-Density Nonvolatile Switch Technology                   | 71        |  |

|   | 4.6  | Compiling a PROTOCHIP                                                | 76        |  |

|   |      | 4.6.1 Leaf Cells                                                     | 77        |  |

|   |     | 4.6.2    | Physical Placement of Leaves and Interconnect          | 82  |

|---|-----|----------|--------------------------------------------------------|-----|

|   | 4.7 | Expe     | riments with the PROTOCHIP                             | 84  |

|   | 4.8 | Sumn     | nary                                                   | 93  |

| 5 | Spe | ecificat | tion of Netlists, Testing of Graph Isomorphism, and En | n-  |

|   | bed | lding c  | of Circuits onto the PROTOCHIP                         | 96  |

|   | 5.1 | NETO     | GEN: A Netlist-Specification Language                  | 98  |

|   |     | 5.1.1    | Natural Support for Common Design Styles               | 99  |

|   |     | 5.1.2    | NETGEN's Internal Representation                       | 100 |

|   |     | 5.1.3    | A Simple Model for Placement and Interconnect          | 103 |

|   |     | 5.1.4    | Scoping Rules for Identifiers                          | 104 |

|   |     | 5.1.5    | Summary                                                | 106 |

|   | 5.2 | Netlis   | et Comparison for Validation of VLSI Systems           | 108 |

|   |     | 5.2.1    | Previous Work                                          | 108 |

|   |     | 5.2.2    | Testing of Graph Isomorphism                           | 109 |

|   |     | 5.2.3    | Enhancements to the Algorithm                          | 116 |

|   |     | 5.2.4    | Implementation and Experience                          | 121 |

|   |     | 5.2.5    | Summary                                                | 127 |

|   | 5.3 | A Bot    | tom Up Graph-Embedding Algorithm                       | 129 |

|   | 5.4 | A Fast   | t Greedy Algorithm for Graph Embedding                 | 136 |

|   |     | 5.4.1    | Greedy Graph Partitioning                              | 136 |

|   |     | 5.4.2    | Analysis of the Greedy Algorithm for Random Graphs     | 137 |

|   |     | 5.4.3    | Summary                                                | 144 |

| 6 | Nov | el Circ  | cuits                                                  | 148 |

|   | 6.1 | An Iso   | otropic Novelty Filter                                 | 150 |

|   |     | 6.1.1    | Series MOS Transistors with Back-Gate Effect           | 150 |

|   |     | 6.1.2    | Multiple Differential Pair Circuit                     | 152 |

|   |     |          |                                                        |     |

|                  |       | 6.1.3  | Summary                                                   | 154 |

|------------------|-------|--------|-----------------------------------------------------------|-----|

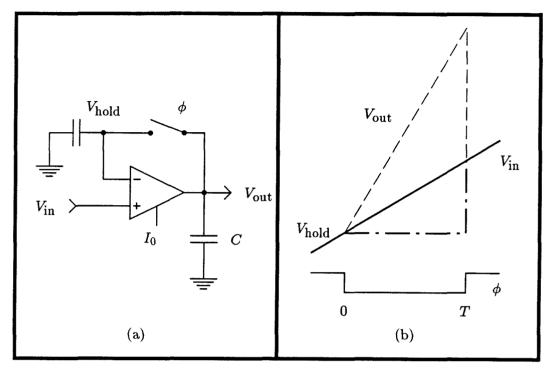

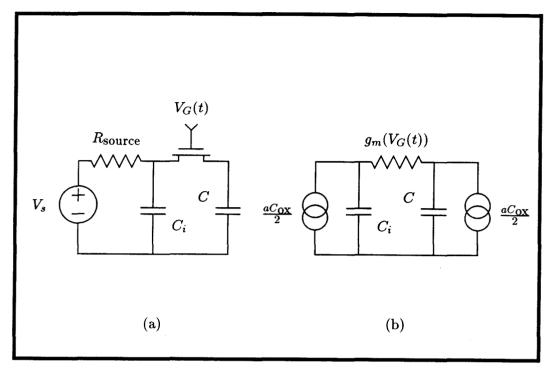

|                  | 6.2   | A Low  | v-Noise Sampling Circuit                                  | 156 |

|                  |       | 6.2.1  | Estimation of Time Derivatives Using Discrete Differences | 156 |

|                  |       | 6.2.2  | Established Circuits for Sampling of Voltages             | 158 |

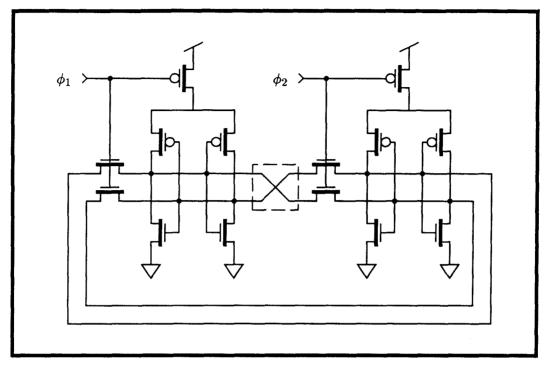

|                  |       | 6.2.3  | A Circuit for Reduced Charge Injection                    | 160 |

|                  |       | 6.2.4  | A Low-Noise Discrete-Time Differentiator                  | 164 |

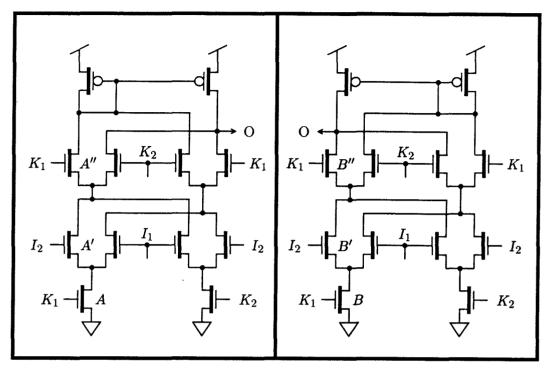

|                  | 6.3   | A Sing | gle-Phase Latch                                           | 166 |

|                  |       | 6.3.1  | A Level-Sensitive Latch                                   | 167 |

|                  |       | 6.3.2  | An Edge-Sensitive Latch                                   | 167 |

|                  |       | 6.3.3  | Analysis of the Edge-Sensitive Latch                      | 170 |

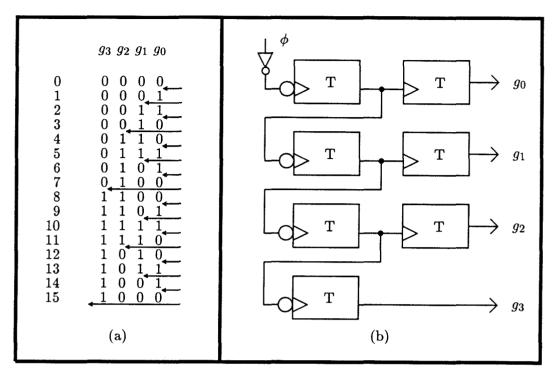

|                  |       | 6.3.4  | Single Phase Toggle Flip-Flops                            | 171 |

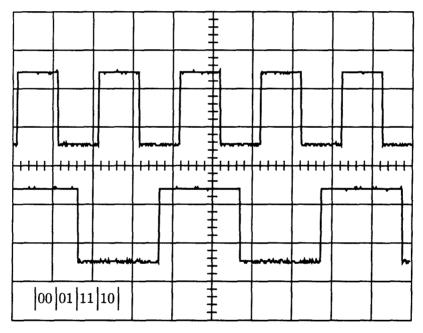

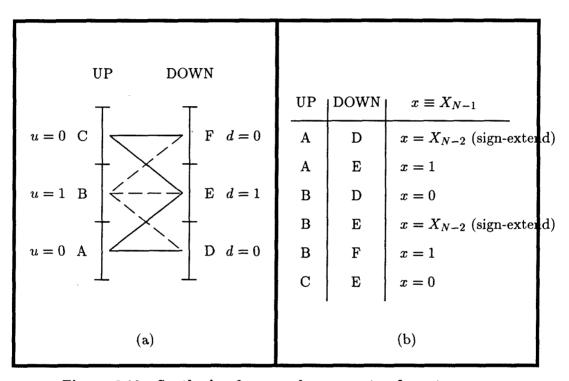

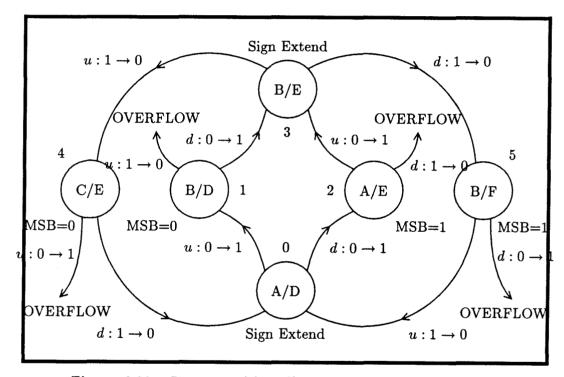

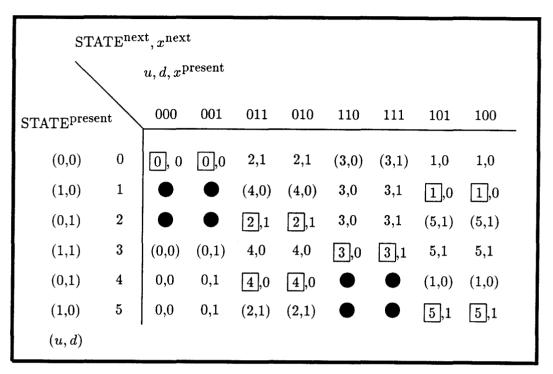

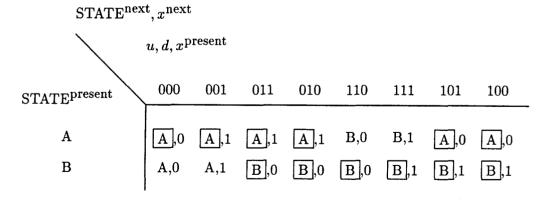

|                  |       | 6.3.5  | Asynchronous Up–Down Counters                             | 176 |

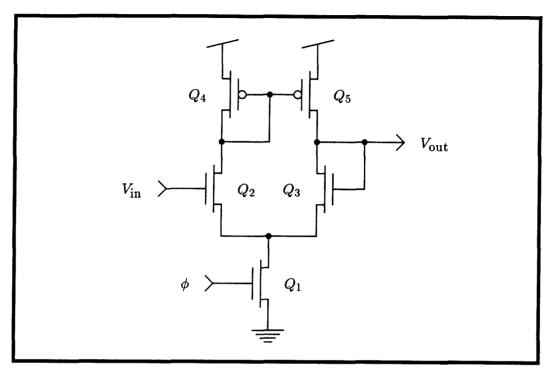

|                  | 6.4   | A Self | -Timed Retina Design Frame                                | 185 |

|                  |       | 6.4.1  | Designing An Efficient Arbiter                            | 186 |

|                  | 6.5   | Summ   | ary                                                       | 195 |

| 7                | Con   | clusio | ns                                                        | 196 |

| $\mathbf{R}_{0}$ | efere | nces   |                                                           | 202 |

## List of Figures

| 2.1  | Hopfield's neural network model                                | 10 |

|------|----------------------------------------------------------------|----|

| 2.2  | Full-wafer current variation in 3x3 micron MOS transistors     | 14 |

| 2.3  | Drain current variation in adjacent $3x3\mu$ MOS transistors   | 15 |

| 2.4  | Drain current variation in adjacent $24x24\mu$ MOS transistors | 15 |

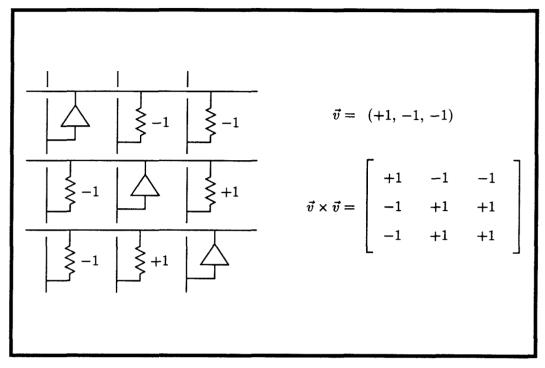

| 2.5  | ASSOCMEM architecture, and outer-product programming           | 16 |

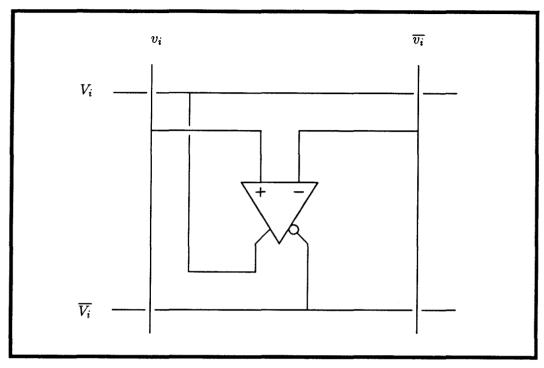

| 2.6  | Dual-rail signal representation                                | 17 |

| 2.7  | ASSOCMEM neuron element                                        | 18 |

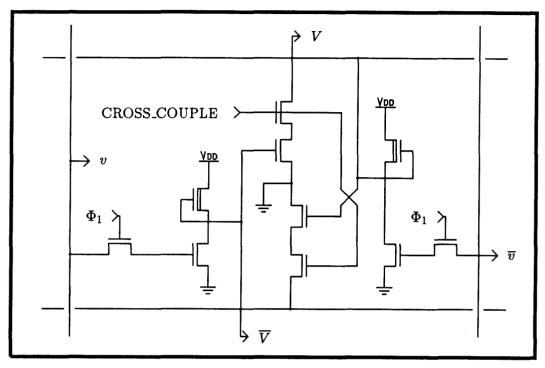

| 2.8  | $T_{ii}$ element schematic                                     | 19 |

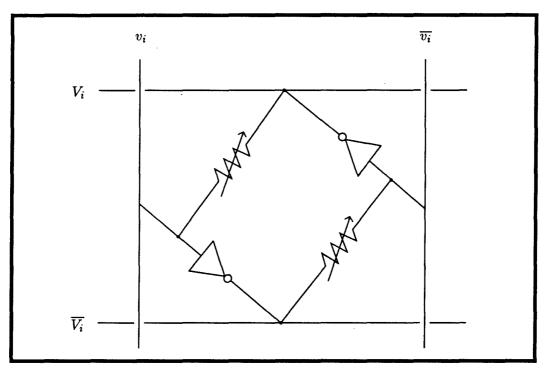

| 2.9  | Resistive interconnect                                         | 20 |

| 2.10 | Programming the $T_{ij}$ matrix                                | 22 |

| 2.11 | Schematic of $T_{ij}$ element                                  | 23 |

| 2.12 | The ASSOCMEM                                                   | 25 |

| 2.13 | $T_{ii}$ transfer characteristic                               | 26 |

| 2.14 | Ring oscillator.                                               | 26 |

| 2.15 | Ring oscillator periods                                        | 27 |

| 2.16 | ASSOCMEM convergence properties                                | 28 |

| 2.17 | Single-step association                                        | 30 |

| 2.18 | $T_{ij}$ yield map                                             | 30 |

| 2.19 | Fully-connected associative memory layout strategies           | 32 |

| 2.20 | Subthreshold CMOS active element                                              | 33 |

|------|-------------------------------------------------------------------------------|----|

| 3.1  | Estimating the number of wires crossing the perimeter                         | 38 |

| 3.2  | A model for circuit connectivity                                              | 40 |

| 3.3  | Model for predicting distribution of wire lengths                             | 45 |

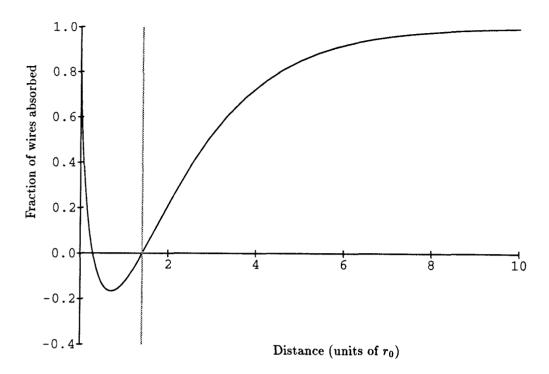

| 3.4  | Predicted probability of wire absorption with distance                        | 48 |

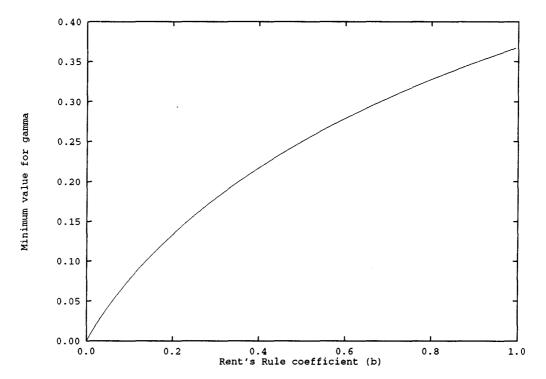

| 3.5  | Range of application of restricted model                                      | 50 |

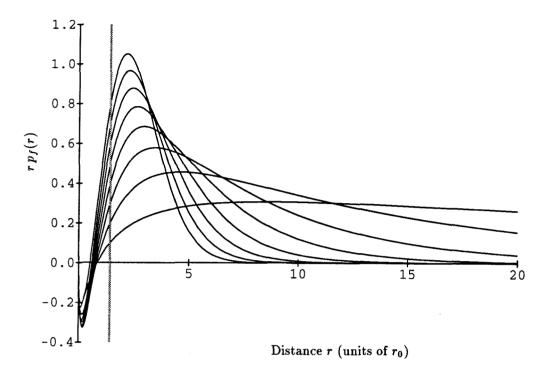

| 3.6  | Integrand of $\int_{r=r_e}^{\infty} r  p_f(r)  dr$                            | 51 |

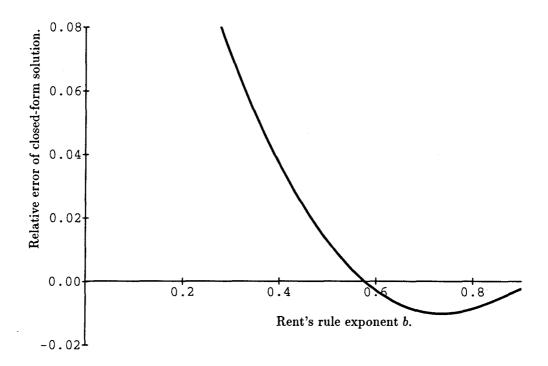

| 3.7  | Relative error introduced by integrating model from $r = 0. \dots$            | 52 |

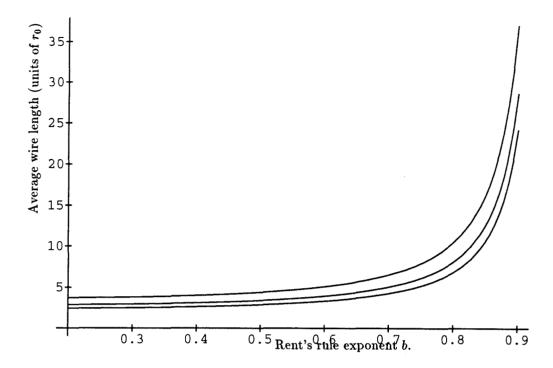

| 3.8  | Average wire length predicted by model                                        | 53 |

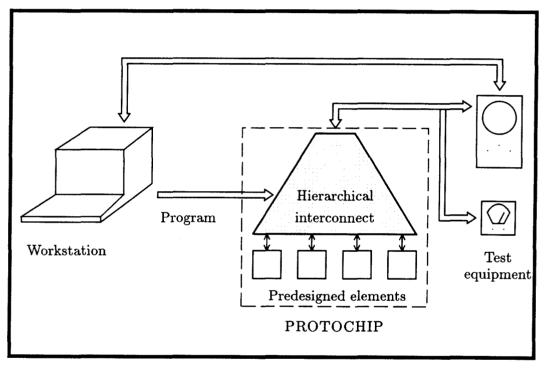

| 4.1  | The PROTOCHIP environment                                                     | 58 |

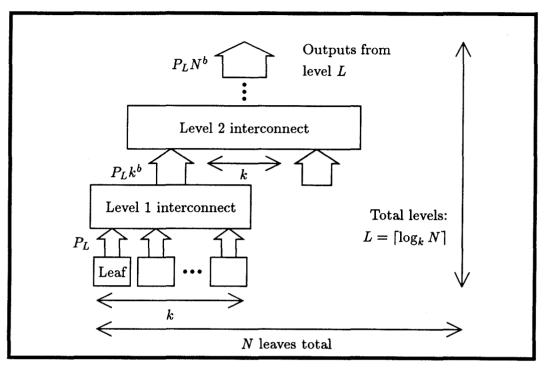

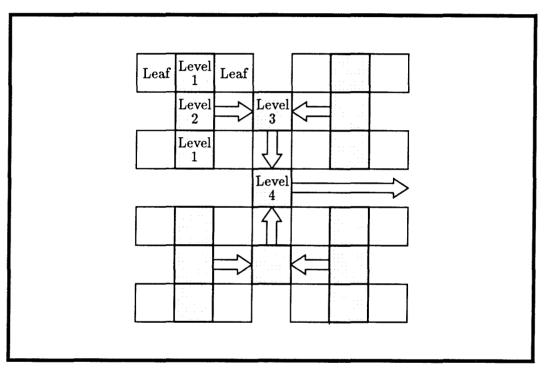

| 4.2  | Hierarchical interconnect parameters                                          | 62 |

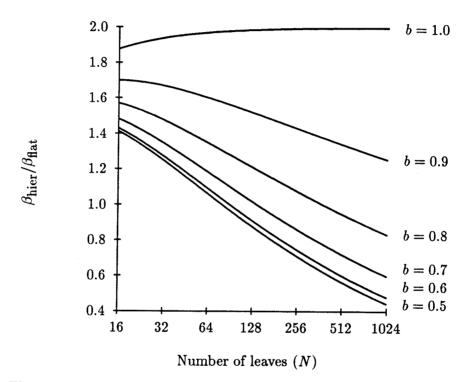

| 4.3  | Efficiency of hierarchical Rent's rule interconnect                           | 64 |

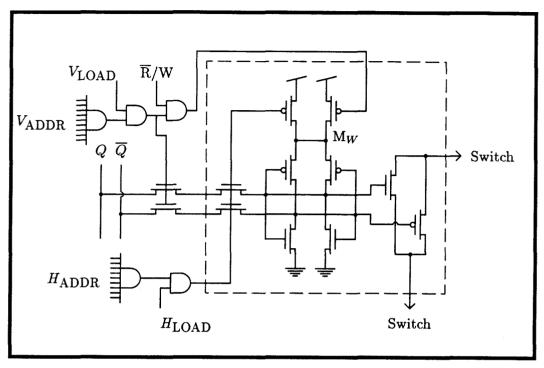

| 4.4  | CSRL static RAM and transmission gate switch                                  | 68 |

| 4.5  | Transmission gate small-signal resistance variation — theoretical             | 71 |

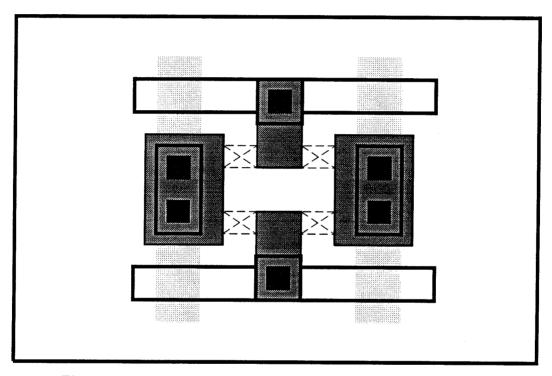

| 4.6  | Layout of $4 \times 4$ laser-programmed switch matrix                         | 73 |

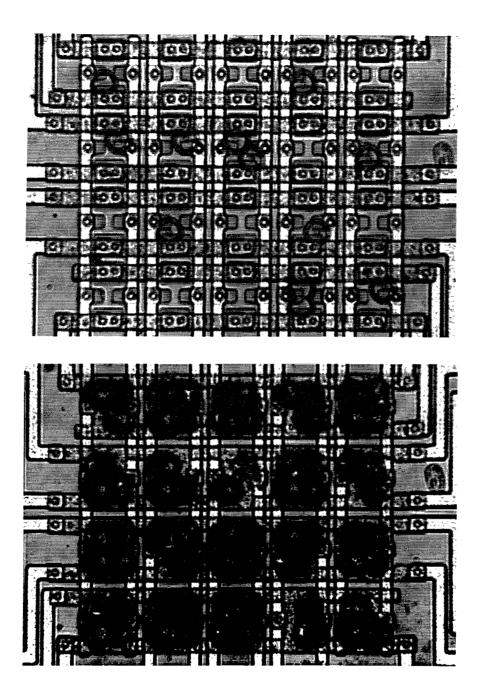

| 4.7  | Photographs of laser-programmed interconnect matrix                           | 74 |

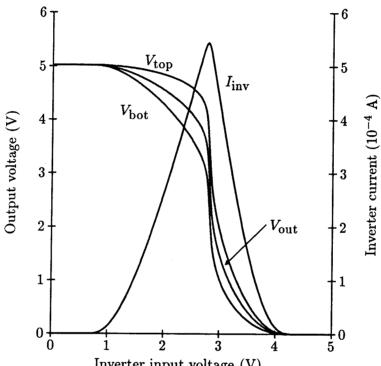

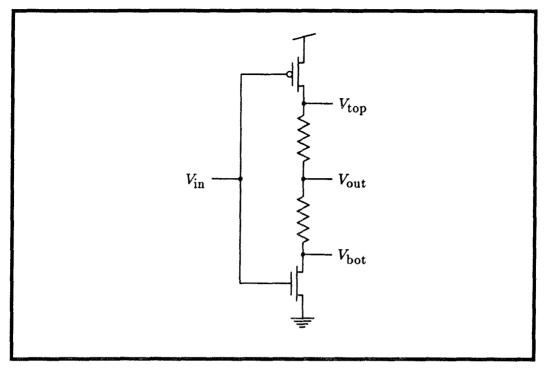

| 4.8  | Transfer characteristic for poor inverter design                              | 75 |

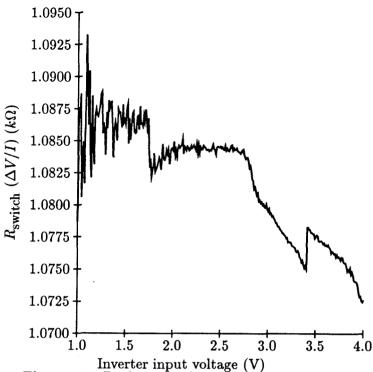

| 4.9  | Resistance of laser-programmed link                                           | 76 |

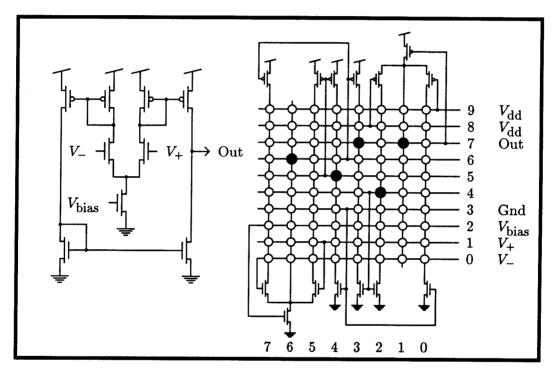

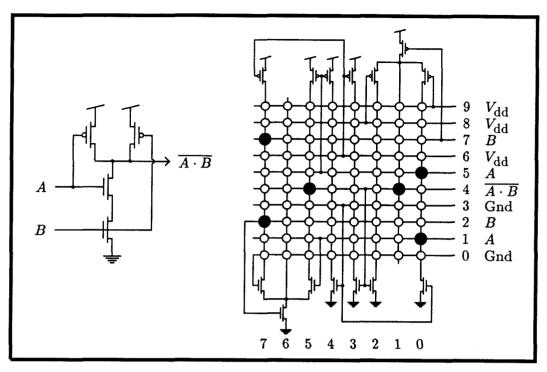

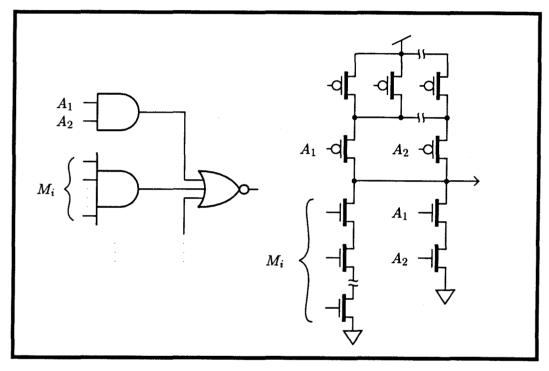

| 4.10 | Programmable analog leaf cell                                                 | 78 |

| 4.11 | Wide-range transconductance amplifier                                         | 79 |

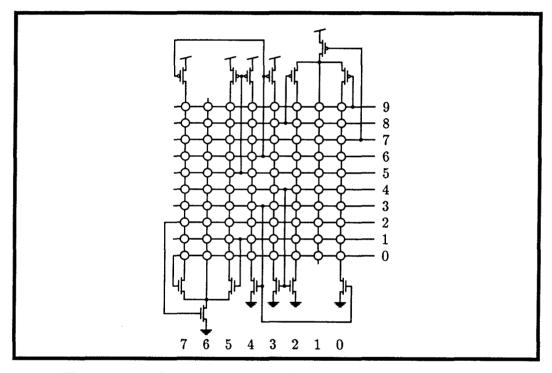

| 4.12 | NAND gate implemented with analog leaf                                        | 80 |

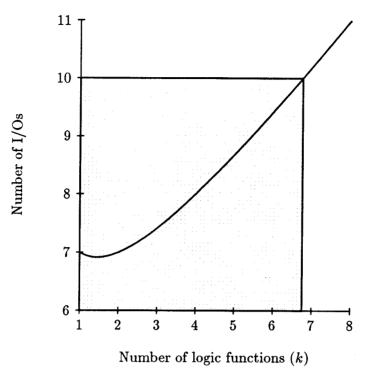

| 4.13 | Tradeoff between inputs and outputs in digital leaf                           | 82 |

| 4.14 | Binary H-tree hierarchical interconnect structure                             | 83 |

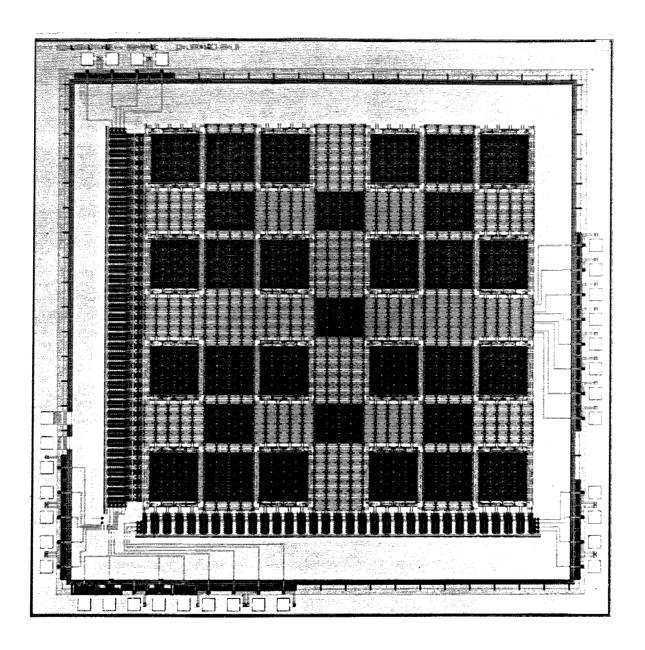

| 4.15 | Photomicrograph of first PROTOCHIP                                            | 85 |

| 4.16 | ${\it Transmission gate small-signal resistance variation experimental.} \ .$ | 86 |

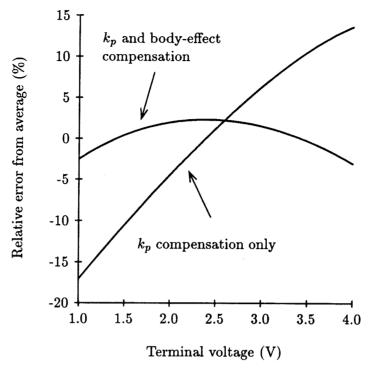

| 4.17 | Scaling transistors to compensate for capacitance of interconnect             | 87 |

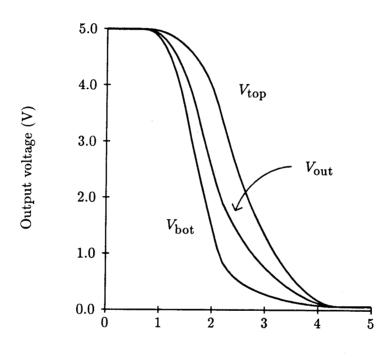

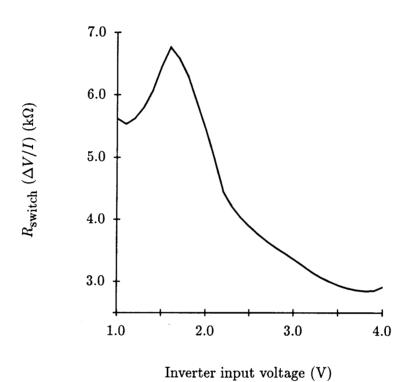

| 4.18 | Inverter with transmission gates in series with high-current path      | 88  |

|------|------------------------------------------------------------------------|-----|

| 4.19 | Transfer curve for inverter in Figure 4.18                             | 89  |

| 4.20 | Effective large-signal resistance of transmission gates in Figure 4.18 | 90  |

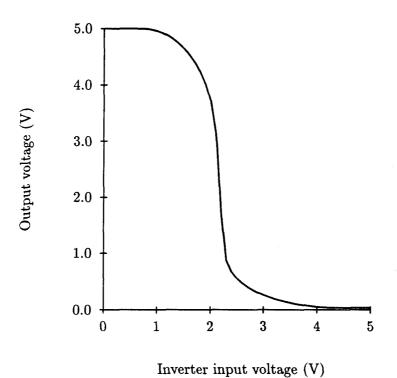

| 4.21 | Transfer curve for an inverter designed with no transmission gates in  |     |

|      | series with high-current path                                          | 91  |

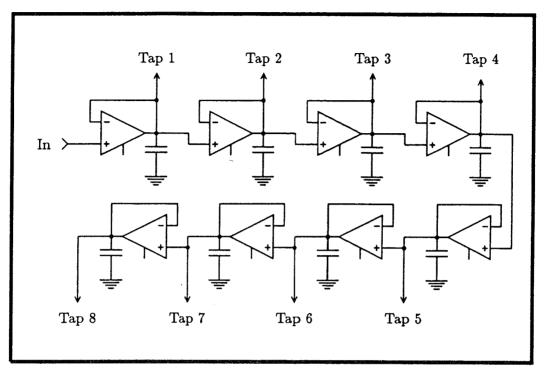

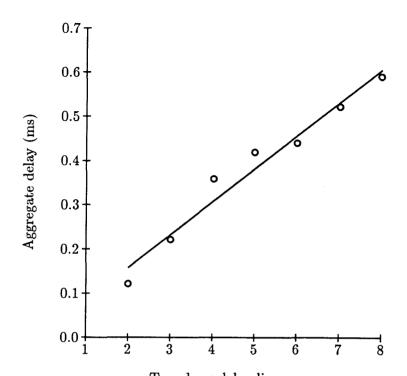

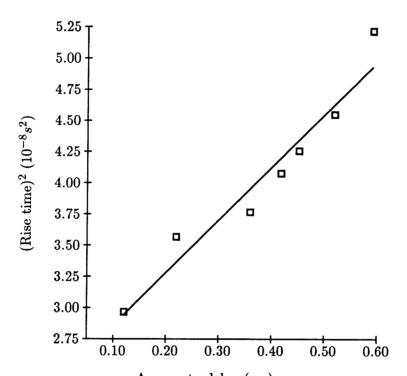

| 4.22 | A follower–integrator delay line constructed of first-order sections   | 92  |

| 4.23 | Waveform delay as a function of distance down the delay line of Fig-   |     |

|      | ure 4.22                                                               | 93  |

| 4.24 | Waveform risetime as a function of delay                               | 94  |

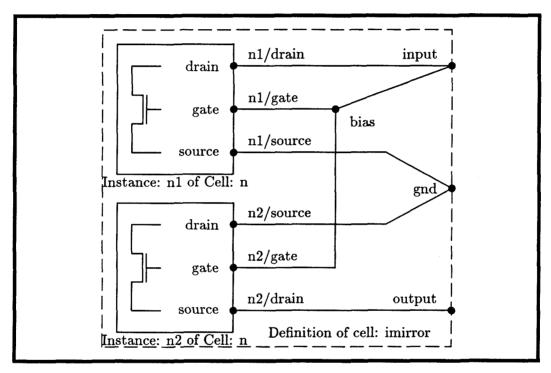

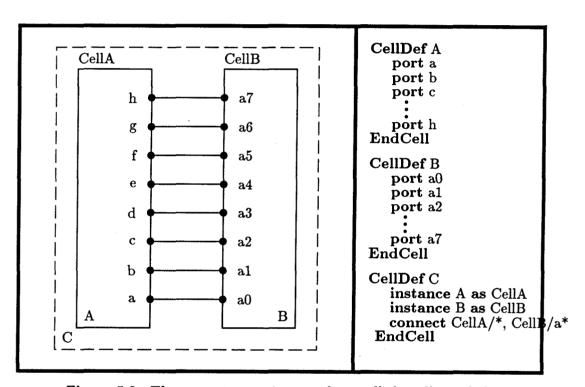

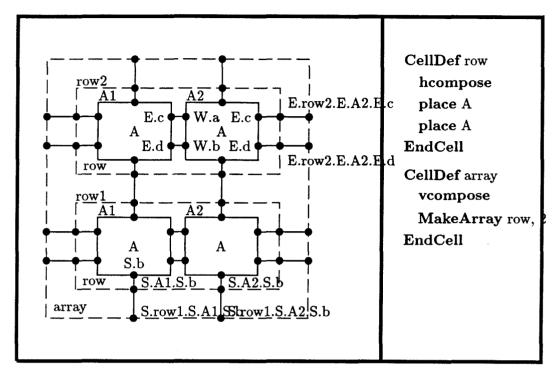

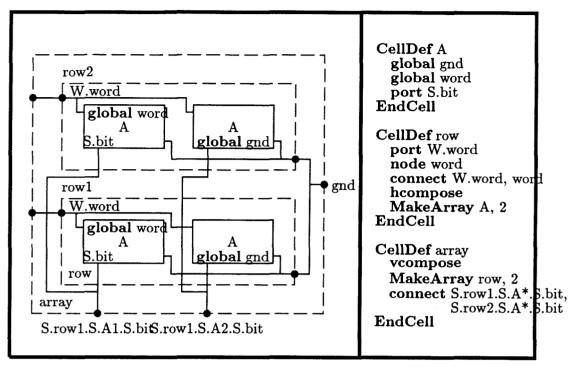

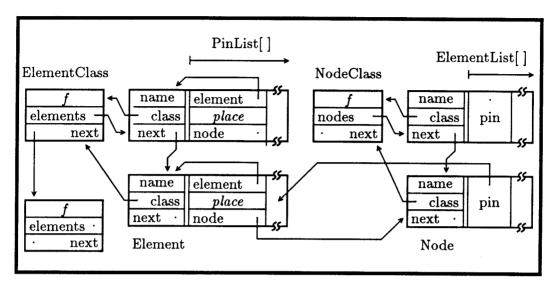

| 5.1  | NETGEN internal representation                                         | 101 |

| 5.2  | The connect operator on lists                                          | 102 |

| 5.3  | NETGEN place operator                                                  | 103 |

| 5.4  | Dynamic scoping of identifiers                                         | 105 |

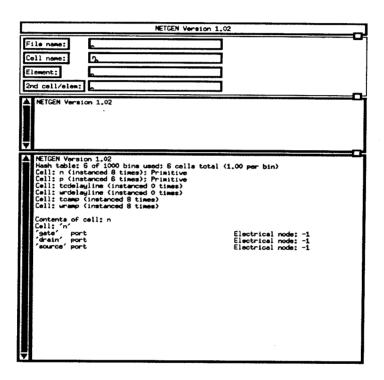

| 5.5  | X Window System interface to NETGEN                                    | 107 |

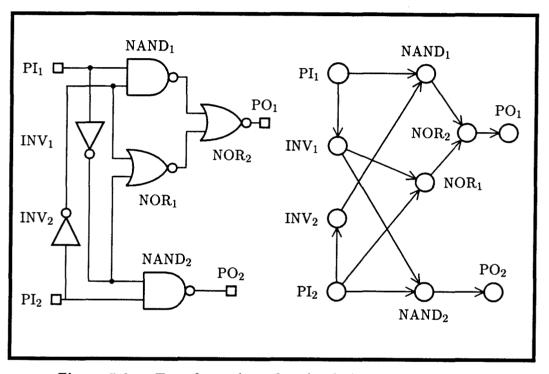

| 5.6  | Transforming a circuit into a graph – 1                                | 110 |

| 5.7  | Transforming a circuit into a graph $-2$                               | 111 |

| 5.8  | Simplified NETCMP algorithm                                            | 113 |

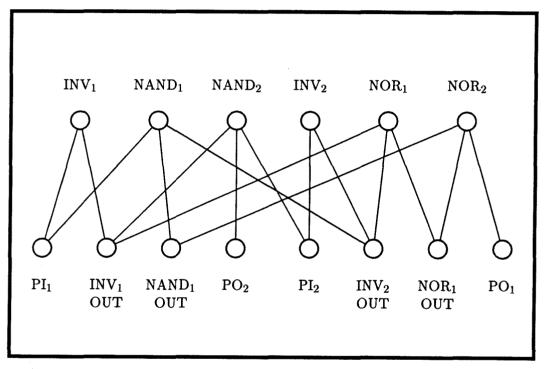

| 5.9  | Failure of the graph partitioning algorithm                            | 114 |

| 5.10 | Sample output from NETCMP                                              | 115 |

| 5.11 | Nearly-symmetric circuits yield hard-to-find errors                    | 116 |

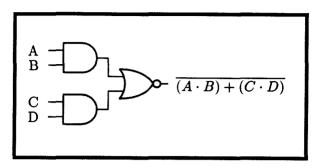

| 5.12 | An And-Or-Invert (AOI) gate                                            | 119 |

| 5.13 | The NETCMP datastructure                                               | 120 |

| 5.14 | AOI gate node count                                                    | 125 |

| 5.15 | Failure of NETCMP algorithm on a real circuit                          | 126 |

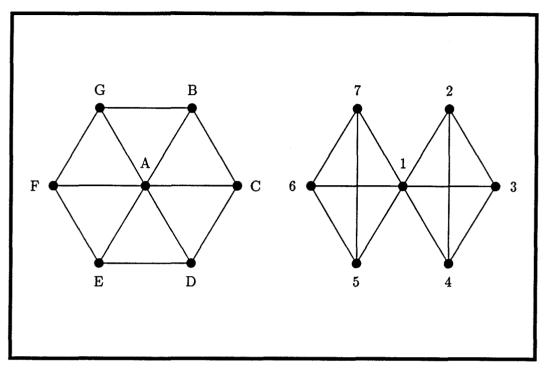

| 5.16 | Embedding a one-phase CSRL toggle flip-flop                            | 132 |

| 5.17 | Output from bottom-up graph embedding algorithm                        | 133 |

| 5.18 | Complexity of circuit partitioning                                      | 134 |

|------|-------------------------------------------------------------------------|-----|

| 5.19 | Treatment of shared nodes by embedding algorithm                        | 135 |

| 5.20 | Breadth-first graph traversal                                           | 137 |

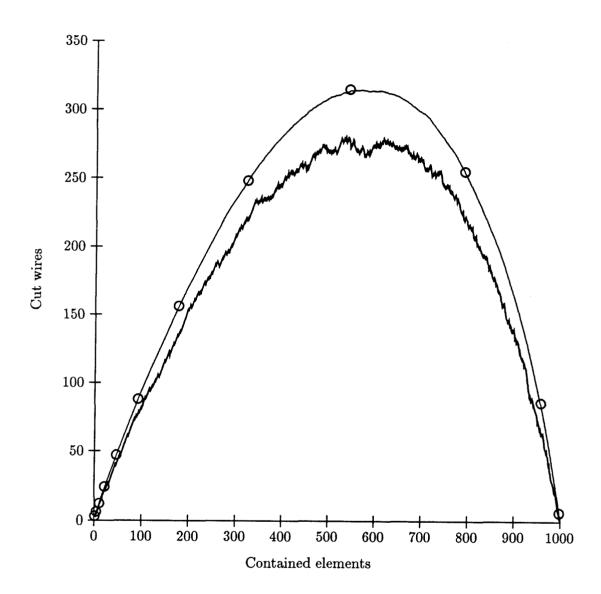

| 5.21 | Analysis of greedy algorithm.                                           | 139 |

| 5.22 | Graph bisection by greedy algorithm                                     | 145 |

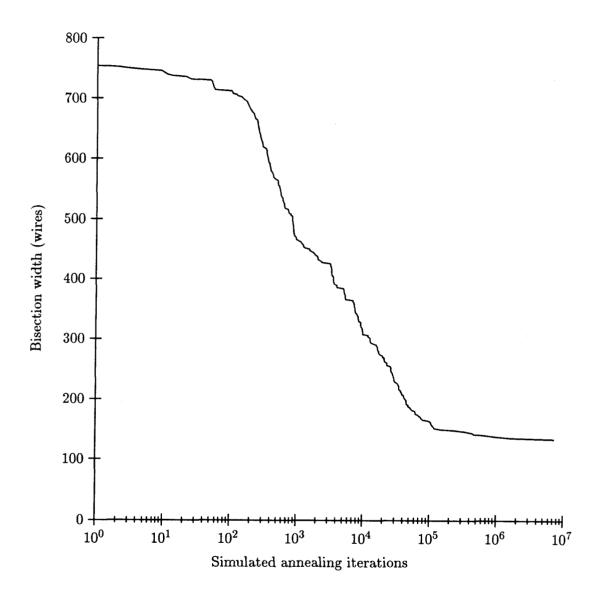

| 5.23 | Graph bisection by simulated annealing                                  | 147 |

| 6.1  | Series MOS transistor chain                                             | 151 |

| 6.2  | Novelty filter circuit                                                  | 153 |

| 6.3  | Approximating derivatives with finite differences                       | 157 |

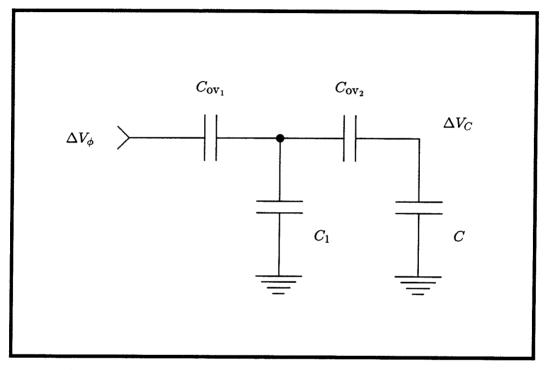

| 6.4  | Compensating for charge injection noise                                 | 159 |

| 6.5  | A model for MOS channel-charge injection                                | 160 |

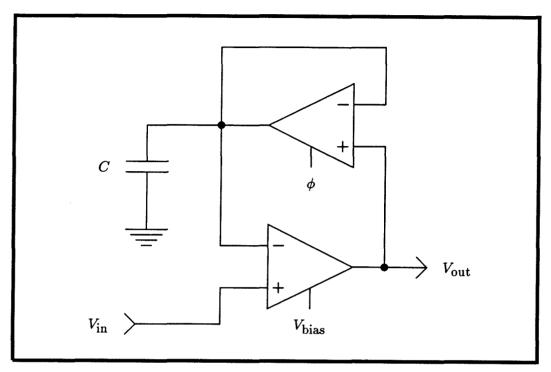

| 6.6  | Low-noise sample-and-hold circuit.                                      | 161 |

| 6.7  | Analysis of low-noise sample-and-hold circuit                           | 163 |

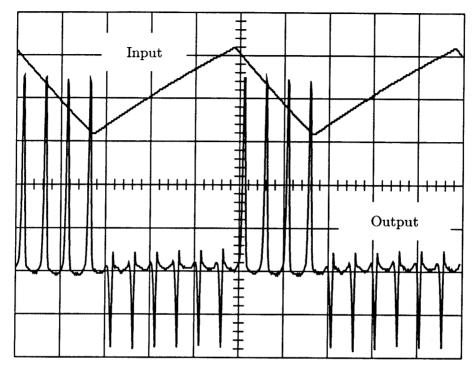

| 6.8  | The discrete-time differentiator.                                       | 164 |

| 6.9  | Operation of the low-noise discrete-time differentiator                 | 165 |

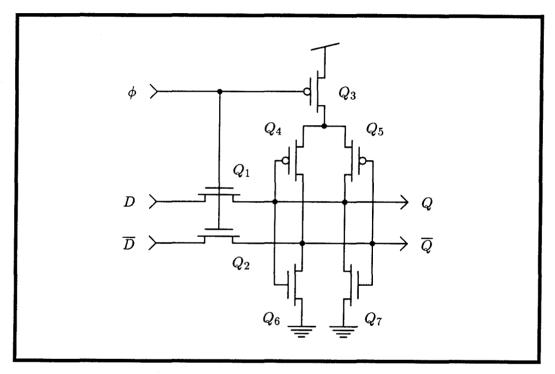

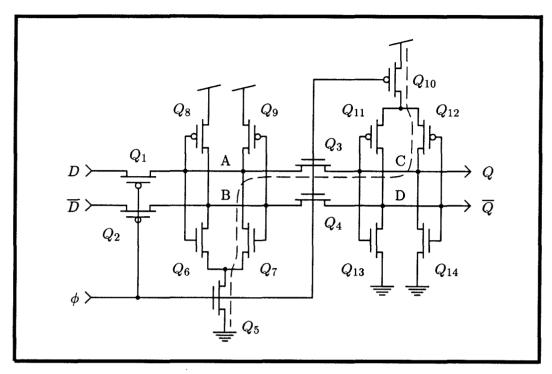

| 6.10 | Single CSRL stage                                                       | 168 |

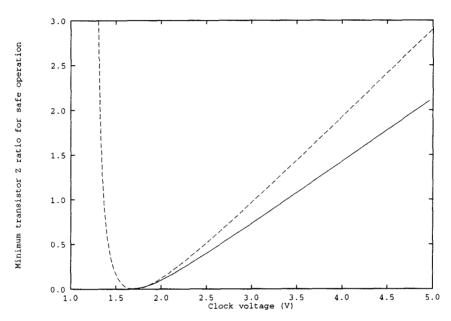

| 6.11 | An edge-sensitive CSRL latch                                            | 169 |

| 6.12 | Minimum geometry factor for safe operation of the edge-sensitive latch. | 172 |

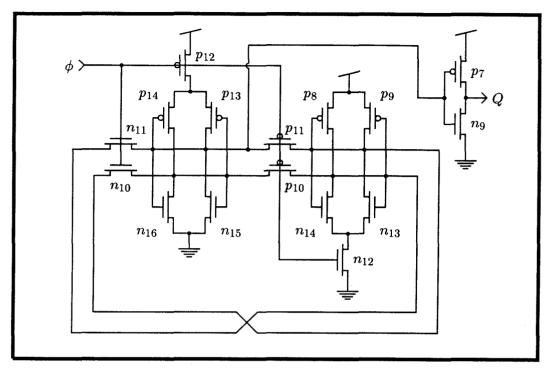

| 6.13 | A toggle flip-flop cell using the single-clock CSRL discipline          | 173 |

| 6.14 | Two-bit binary counter implemented with toggle flip-flop cells          | 174 |

| 6.15 | Nonrestored clock applied to toggle flip-flop cell                      | 175 |

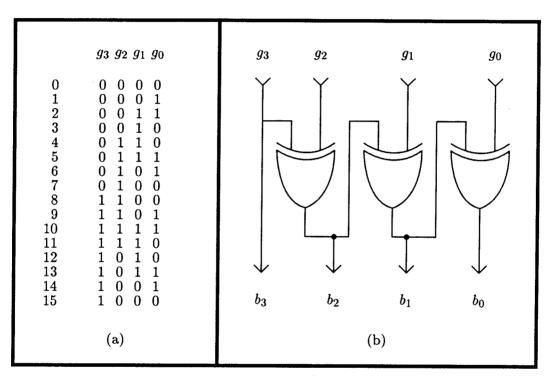

| 6.16 | The Gray code                                                           | 177 |

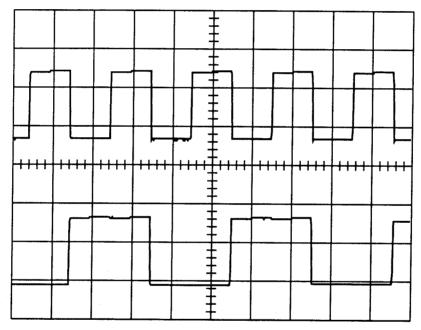

| 6.17 | A scalable Gray-code counter                                            | 178 |

| 6.18 | Sample output from a Gray-code counter                                  | 179 |

| 6.19 | Synthesis of an up-down counter from two up-counters                    | 181 |

| 6.20 | State-transition diagram for up-down counter                            | 182 |

| 6.21 | Huffman flow table for up-down counter                        | 183 |

|------|---------------------------------------------------------------|-----|

| 6.22 | Simplified Huffman flow-table for up-down counter             | 183 |

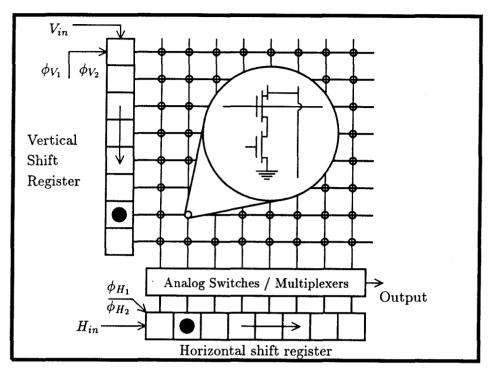

| 6.23 | First-generation retina design frame.                         | 186 |

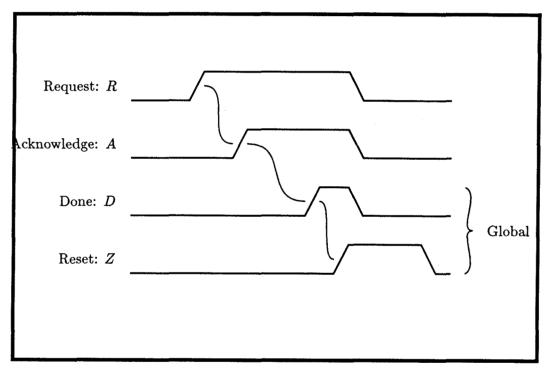

| 6.24 | The self-timed retina asynchronous communication protocol     | 188 |

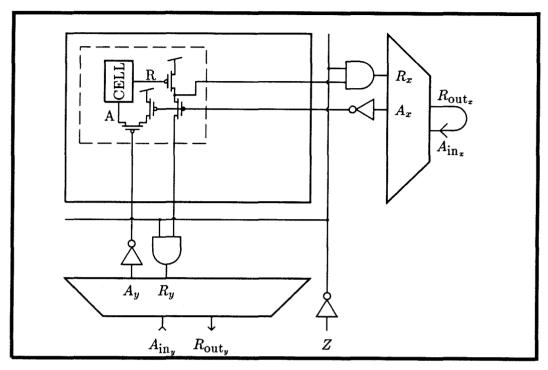

| 6.25 | Self-timed retina design frame                                | 189 |

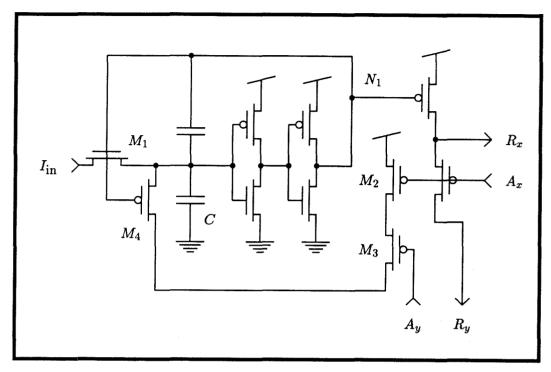

| 6.26 | Delta-modulation cell                                         | 190 |

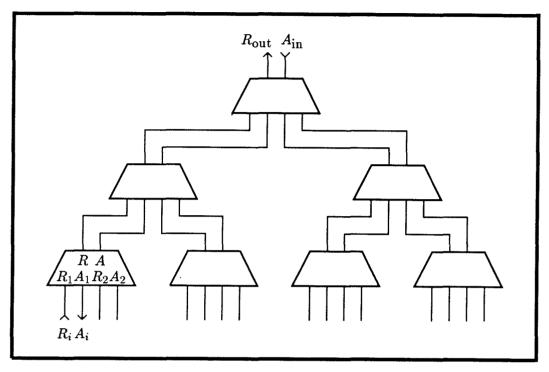

| 6.27 | Binary tree of 2-input arbiters                               | 191 |

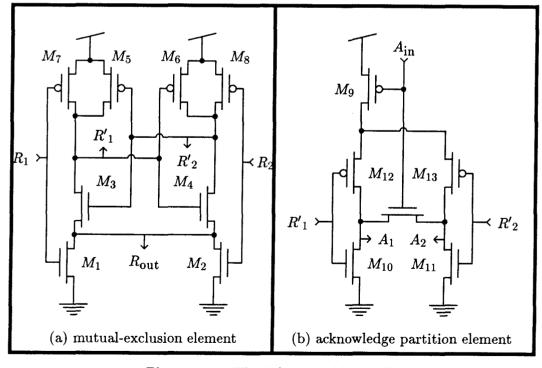

| 6.28 | The 2-input arbiter cell                                      | 191 |

| 6.29 | Equivalent circuit for arbiter in metastable state            | 192 |

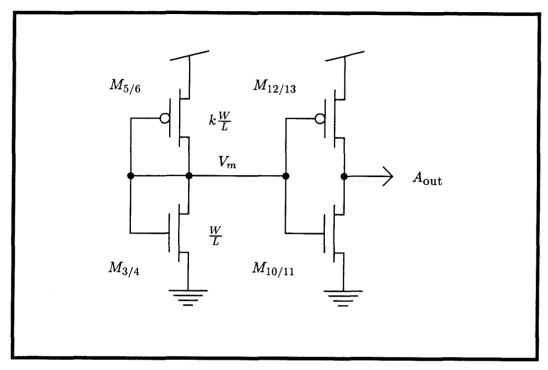

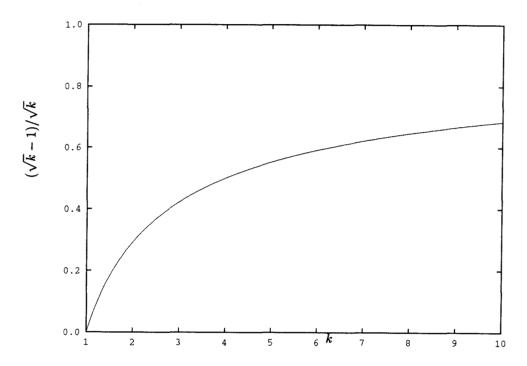

| 6.30 | Guaranteeing safe operation of arbiter by scaling transistors | 194 |

## List of Tables

| 2.1 | $T_{ij}$ update operation | 22  |

|-----|---------------------------|-----|

| 5.1 | NETCMP Performance        | 122 |

| 5.2 | Greedy algorithm model    | 146 |

## Chapter 1

#### Introduction

The inexorable demands for greater functionality, higher performance, reduced silicon area, and lower power consumption are constantly driving advanced VLSI designs toward more aggressive technologies. Analog networks hold great promise, as their explicit parallelism is an obvious match for VLSI circuits. A clear advantage of such networks is a natural scalability intrinsic in their computational structure. Another advantage is that analog systems are often in a better position to exploit innovations in devices, processes and structures, because: (1) analog circuits rely on the rich physical behavior of their components to attain their compactness and great breadth of computational functionality, and (2) analog circuit designers are accustomed to paying great care in interfacing components (great flexibility is possible in the absence of rigid abstraction and composition rules). So-called neural networks are currently an attractive research topic. Their great potential is evidenced by the existence of functional biological systems, able to solve complex tasks necessary to survive in a dynamic, ill-structured, and often hostile environment. From a systems perspective, the chief virtue of neural networks is their departure from a reliance on programming in the conventional algorithmic sense; rather, such networks are commonly taught to

solve a problem, generally by observation of a sequence of input data that has been previously classified by an external teacher. From an implementation perspective, these networks are intrinsically parallel, and typically comprise large numbers of relatively simple individual components; these characteristics make them attractive to VLSI implementation.

Because the connectivity of these networks is often explicitly determined by the neural computation being performed (and the neural training algorithm being applied), a careful consideration of the implications of this connectivity is both appropriate and required at an early point in the design process. Also, as neuromorphic systems continue to increase in sophistication, the necessity for hierarchical processing operating on evolving signal representations will become an increasingly important research issue. In this thesis, we present the design of a system capable of accommodating medium-scale networks by exploiting a hierarchical interconnect strategy; this system provides a prototyping platform for testing such hierarchical networks.

Aggressive designs require sophisticated and reliable design tools. Unfortunately, automated design aids, long considered barely adequate even for traditional digital VLSI applications, are woefully insufficient for large-scale analog systems. In particular, conventional software simulators are too slow, have limited capacities, are inaccurate (the device models are usually for discrete, and not integrated, devices and structures) and inextensible (it is usually difficult to improve the device models, or to add new ones) and, in general, constitute an unfriendly design environment. Consequently, such simulators are inappropriate for testing ideas relating to intermediate-scale systems. For example, analog networks, collective systems, and adaptive control systems all require larger number of components than can be reasonably accommodated in present circuit simulators. Also, large classes of systems exhibit highly data-dependent operation, and require simulation of large numbers of test cases. Even the advent of parallel circuit simulators will not solve the design

bottleneck, as the issues of accurately modeling device behavior over wide ranges, and of modeling circuit parasitics, still remain.

The opportunity thus exists for a high-performance, high-capacity circuit simulator, with precision and flexibility as its principal objectives, and the capability to accommodate novel integrated structures. In this thesis, we propose such a system, built around a field-configurable network that interconnects actual physical devices.

#### 1.1 Reader's road map

The first part of the thesis (Chapters 2, 3, and 4) is a discussion of the connectivity requirement of regular VLSI systems. We begin by describing an early system: the first VLSI implementation of a neural network. In particular, we discuss several implementations of Hopfield-style associative memories, and the consequences of their full interconnect with regard to the absolute size of viable implementations and the scalability of such networks.

We then consider one facet of the general graph embedding problem: by considering the dimensionality of the interconnection medium, we derive wiring limits that determine implementable systems. In particular, we propose a requirement for such systems: the components within the system should be approximately uniformly distributed spatially. From this requirement, we derive a wiring relation that is consistent with a commonly used empirical relation known as Rent's rule. Finally, we approach the wiring problem from the perspective of permissible wire length distributions; we use our wiring model to derive the average wire length for regularly arrayed cells, and relate this length to allowed physical area limits.

The second part of the thesis (Chapters 4 and 5) applies these connectivity constraints to designing an efficient, field-programmable interconnect structure intended for real-time prototyping of medium scale analog systems (a few thousand transis-

tors). Various aspects of the design are discussed, including algorithms for embedding circuit graphs onto the hierarchical interconnect, various tradeoffs in the interconnect technology (e.g., volatility, area density, speed and ease of programming); examples of particular implementations are presented. Test results quantifying the electrical performance of the system are presented.

The opportunity that exists for this system is to provide a fast, versatile environment for developing and testing analog circuits. To this end, in addition to considering the universality and functionality of the hierarchical interconnect network, we describe the software tools that provide utility functions such as netlist specification and manipulation, and provide a methodology for design validation in the form of testing for isomorphism between pairs of circuit graphs. These tools are available as part of the Caltech suite of VLSI CAD tools.

The third part of this thesis (Chapter 6) illustrates particular aspects of analog circuit design by presenting some previously unreported circuits that have become key components in several VLSI systems. Two of these, a single-clock-phase latch and a two-input asynchronous arbiter, are "digital" circuits whose correct operation is guaranteed by careful consideration of their internal analog components. Other circuits include a low-noise differentiator, built using a low clock-feedthrough analog switch, and an isotropic novelty filter that efficiently performs an  $O(N^2)$  computation with only O(N) components. System-level applications are also presented, including various asynchronous counters, and a self-timed retina design frame.

## Chapter 2

# A Novel Associative Memory Implemented Using Collective Computation<sup>1</sup>

Nullumst iam dictum quod non dictum sit prius.

Terrence (c. 190-159 B.C.), Eunuchus. Prolog. 41

<sup>&</sup>lt;sup>1</sup>Portions of this chapter have been previously published. See [SEM85] [SEM86] [Siv86a].

#### 2.1 Introduction

In nature, there exist many examples of systems consisting of large numbers of individually simple elements, which interact in simple ways, yet collectively yield highly complex behaviors. For example, soap molecules interact via local van der Waals forces, yet on a global scale produce strikingly robust bubbles, which minimize rather sophisticated energy functions due to surface tension. In biology, although neurons are not simple (and neither are the mechanisms of excitation/inhibition at synapses) a similar observation is made: the formidable macroscopic computing capability of a human brain must result from the highly interconnected nature of the neurons. In general, specific high-level functions cannot be attributed to a specific neuron, and furthermore it has been shown that the wiring "map" varies considerably between individuals of the same species [KS81].

Collective systems such as these generally display a number of intriguing properties. First, since no single element encapsulates the function of the system as a whole, they are very robust against the failure of a subset of elements. For example, in the human brain, about 0.1% of all cells die each year, and are not replaced (that's some 3 million per day); yet the functionality of the brain is not noticeably impaired. This fault tolerance is in direct contrast with our conventional design techniques for computers, where every element has a clear function, and failure of that element is, in general, catastrophic. For this reason, and for the obvious ability of collective systems to solve problems (e.g. vision, audition) that are difficult for conventional computational paradigms, the understanding of collective computations is desirable.

If computation is defined as the processing of information, there are two aspects which must be investigated: (1) the storage of information, with the associated issue of representation, and (2) retrieval of information, which may be considered a transformation between representations. We will describe a specific example of a collective

computation, that addresses both of these aspects.

#### 2.2 The Content-Addressable Memory

One of the simplest, and best understood, behaviors of collective systems is that of content-addressable memory (CAM), or associative memory. The model we use for this association is that of viewing the computation as an evolution in state space. The association consists of establishing an initial condition, then evolving to a final, stable state, which we call a *memory*. In some sense, this property can be considered *error correction*, as the initial partial information is increased until the state of the system (which represents some encoding of some piece of information) is fully determined.

A physical system can be used as a CAM if a specific set of states can be made to be stable, and if the dynamics of the system guarantee evolution into one of these states. As we shall see, an energy formulation shall prove useful to understanding the behavior of the system.

Conventional digital associative memories [Hay78] [Par73] [Wee82] have two characteristic shortcomings: (1) the association occurs on an a priori defined key, which must be supplied exactly, (2) resolution of multiple matches often demands an additional serial polling algorithm (slow). In addition, they only work on digital (restored) data, and thus are useless for recognition of patterns with grey scale. We have designed and tested a radically new genre of associative memory. In the ASSOCMEM, association takes place on the word as a whole; the result is the word stored in memory that is closest to the supplied word. There is no distinction made between key and data. The convergence of the association process is guaranteed by theory. The length of time required to perform the association depends, in some sense, on the distance between the input and the result.

This novel behavior is obtained through the use of analog circuit techniques to

perform a "collective computation" [Hop82a]. Each bit of the word is represented by the state of an active element (amplifier). These elements are interconnected in a way to make the desired memory contents stable states of the network. An association consists of setting the initial conditions of the network to a neutral state, then letting the network evolve to a fixed-point.

#### 2.3 The Hopfield Model for Collective Systems

These concepts were formalized in Hopfield's fundamental work [Hop82b] [Hop84]. He proposed an algorithm to model a collective system, and derived the dynamics of this model. His first model [Hop82b] provided for the stochastic update of binary processing elements, called "neurons" after the model of McCulloch and Pitts [MP43]. An extension to the model [Hop84] allows continuous analog neurons, and generalizes to permit communication via "action potentials."

The stochastic model postulates N neurons; each neuron has 2 possible output states  $(V_i = -1 \text{ ("off") and } V_i = +1 \text{ ("on")})$ . The state of the system is characterized by  $\vec{V} = (V_1, V_2, ..., V_N)$ . The output of each neuron is fed back to the inputs of other neurons. The strength of coupling between the output of neuron j and the input of neuron i is given by  $T_{ij}$  – the matrix T is called the interconnect matrix.

The input to a neuron i is given by

$$v_i = \sum_j T_{ij} V_j.$$

The state change in the stochastic model is determined by the following algorithm: at random points in time, each neuron i compares its input with a threshold  $U_i$

(usually taken to be zero, by the symmetry of the scheme), and updates its output:

$$\begin{cases} V_i \to +1 \\ V_i \to -1 \end{cases} \quad \text{if} \quad \begin{cases} v_i > U_i \\ v_i < U_i \end{cases}$$

The justification for this algorithm becomes clear once the construction of the  $T_{ij}$  matrix is considered. A self-reinforcement argument leads to the outer product form [Coo73]

$$T_{ij} = \sum_{s} V_i^s V_j^s$$

, where  $\{V^s, s = 1..M\}$  = set of memories to be stored

but with  $T_{ii} = 0$ . Hence,

$$\sum_{j} T_{ij} V_j = \sum_{s} V_i^s \left[ \sum_{j} V_j V_j^s \right]$$

(2.1)

By statistical orthogonality between random states (a natural consequence of optimal encodings), the mean value of the bracketed term in Equation 2.1 is 0, unless V is near  $V^s$ , in which case this term asymptotically approaches N, as  $V \to V^s$ . Thus, for a state near a memory  $\sum_j T_{ij} V_j \approx N V_i^s$ , which drives  $V_i$  toward  $V_i^s$ .

The stability of the system can be investigated by defining a function:

$$E = -\frac{1}{2} \sum_{i} \sum_{j} T_{ij} V_i V_j$$

For symmetric T  $(T_{ij} = T_{ji})$ , the  $\Delta E$  due to  $\Delta V_i$  is:

$$\Delta E = -\Delta V_i \sum_j T_{ij} V_j$$

Since, by the update algorithm,  $\Delta V_i$  and  $\sum T_{ij}V_j$  have the same sign, E is a

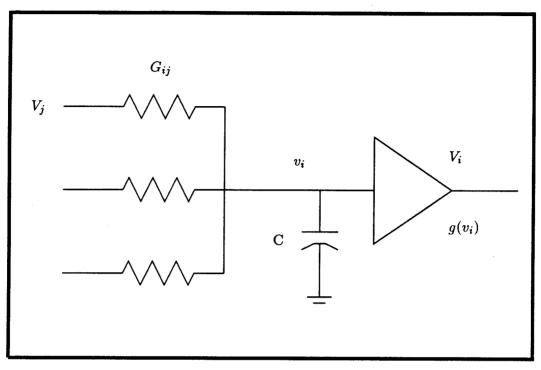

Figure 2.1: Hopfield's neural network model: interconnection of active elements (neurons).

monotonically decreasing function, the local minima of which constitute the memory states. By analogy with the Ising spin model, E is an energy function for the system where  $T_{ij}$  is the exchange coupling. Symmetric  $T_{ij}$ 's hence give rise to *spin glasses* [KS78], which are known to display many stable configurations.

#### 2.3.1 A Continuous Model

Replacing the binary neurons with elements displaying graded transfer functions, and substituting continuous time constants for the asynchronous update schedule, yields a continuous system that displays similar properties [Hop84]. Its analysis is facilitated by considering an electrical circuit model (Figure 2.1).

Application of Kirchoff's Current Law at each input node yields the dynamic

equation:

$$C_i \frac{\partial v_i}{\partial t} = \sum_j G_{ij} (V_j - v_i)$$

(2.2)

where  $V_i = g(v_i)$ . The interconnection conductance  $G_{ij}$  plays the role of  $T_{ij}$ . A Liapunov energy function exists for the system:

$$E = -\frac{1}{2} \sum_{i} \sum_{j} T_{ij} V_{i} V_{j} + \sum_{i} \frac{1}{R_{i}} \int_{0}^{V_{i}} g_{i}^{-1}(V) dV$$

(2.3)

where  $R_i$  is the input impedance seen by the input of amplifier i ( $\frac{1}{R_i} = \sum_j G_{ij}$ ). The time derivative of Equation 2.3 is (for symmetric T):

$$\frac{\partial E}{\partial t} = -\sum_{i} \frac{\partial V_{i}}{\partial t} \left( \sum_{j} T_{ij} V_{j} - \frac{v_{i}}{R_{i}} \right)$$

Substituting Equation 2.2 for the parenthesized expression gives

$$\frac{\partial E}{\partial t} = -\sum_{i} C_{i} \frac{\partial V_{i}}{\partial t} \frac{\partial v_{i}}{\partial t} = -\sum_{i} C_{i} \left. \frac{\partial g^{-1}(V)}{\partial V} \right|_{V_{i}} \left( \frac{\partial V_{i}}{\partial t} \right)^{2}$$

If  $g^{-1}(V)$  is monotonic and increasing,

$$\frac{\partial E}{\partial t} \le 0$$

and  $\frac{\partial E}{\partial t} = 0 \Rightarrow \frac{\partial V_i}{\partial t} = 0, \forall i$

Thus, the continuous model also describes a system which evolves towards stable states, corresponding to local minima of an energy function.

Such associative memories have several appealing features. First, it is possible to indicate *confidence* on a bit-by-bit basis, by setting the initial conditions appropriately, that is, by making certain bits weigh more heavily, if desired. This property allows the ASSOCMEM to accept analog inputs, thus permitting it to process image or sound data. Secondly, all the bits are treated uniformly, in that the network does

not require the distinction of a search key from a data field in either the source or target words. The device may be thought of as an error-correcting machine, where randomly-occurring bit errors are corrected. Thirdly, the actual memories are stored in the interconnect in a highly redundant fashion, making this architecture naturally fault tolerant. Simulation results have indicated that 10% to 20% of all connections may be destroyed with practically no loss of functionality. If a small number of amplifiers are nonfunctional, they can still be "out-voted" by the rest of the network, and errors limited to those bits only.

#### 2.4 VLSI Considerations

Since collective systems exhibit interesting global properties as a consequence of having large numbers of individually simple elements, implementation with very large scale integration (VLSI) circuit technology appears very suitable. There are, however, a number of technology-dependent limitations that are introduced by such a choice.

#### 2.4.1 Cost

The principal cost measure in VLSI is area. Even with the use of die-stitching techniques, there exists a physical limit on the maximum area a circuit can occupy. Also, the off-chip environment is quite different from the internal circuit, for electrical reasons. This fact, coupled with the fundamental restriction on I/O pads, makes it desirable to integrate an entire system on a single chip.

Analog electronics, by exploiting the intrinsic physics of native devices, generally occupy less area per function than an implementation using a digital abstraction. For example, an analog differential-input multiplier may require as few as 8 transistors

to perform the relatively complex calculation  $(y = k(x_{1+} - x_{1-})(x_{2+} - x_{2-}))$ . Furthermore, there is none of the overhead associated with mapping what is essentially a continuous problem into a discrete-time (sampled digital) system.

#### 2.4.2 Power

A common complaint about analog computing elements is that their power consumption is high, due to a desire for maximum linearity at high operating speeds, and because discrete (off-chip) components present relatively highly capacitive loads. In a VLSI context, power dissipation must be limited to a few Watts (for conventional packaging technologies). However, collective circuits implemented entirely on one die have no requirements to drive external loads, do not have to be particularly fast, and value symmetry much more highly than linearity.

It is important to note that the Hopfield circuit model exhibits nonzero power dissipation even after convergence is reached, and the computation is nominally terminated. For systems of several hundred amplifiers, it is not possible to build interconnect matrices of tens of thousands of resistors without explicitly limiting the power consumption of the amplifiers. A commonly suggested alternative, computation by current summing, is even more impractical, as the number of (power dissipating) current injectors that must be controlled scales with the number of synapses.

The approach we have taken to permit the implementation of large arrays is to limit the current consumption of the amplifiers, guaranteed by keeping most of the MOS devices in a subthreshold regime of operation [MM86]. For sufficiently low gate voltages (less than the so-called "threshold voltage," below which the digital abstraction of transistor operation classifies the transistor as "off"), the drain current is exponential in the gate voltage. This behavior is exactly the same (and indeed, the physics are identical) as bipolar transistors exhibit throughout their operating range,

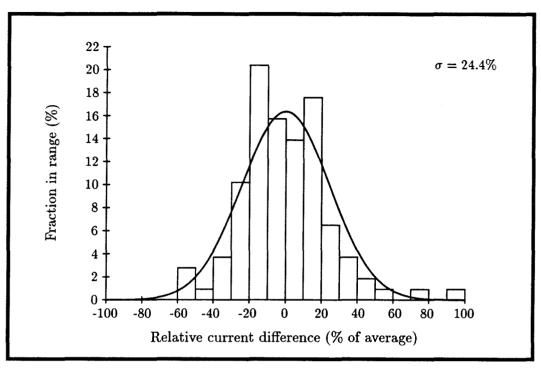

Figure 2.2: Full-wafer current variation in 3x3 micron MOS transistors.

with the additional benefit that MOS transistors draw no gate current.

#### 2.4.3 Parameter Variation

An additional complication is introduced in the case of very small devices, where statistical or systematic doping variations can affect their transfer characteristics by significant amounts. These variations are particularly evident in the case of fabrication lines intended for digital chips (which are relatively insensitive to such variation). If an analog design methodology is used that requires currents to be precisely matched or subtracted, it is unlikely that sufficient accuracy can be obtained with single small transistors. The degree of variation to be expected is illustrated in Figure 2.2 [Tan86], which shows the drain currents of identically biased MOS transistors from a typical MOSIS [CL81] digital process. When differences between adjacent transistor currents

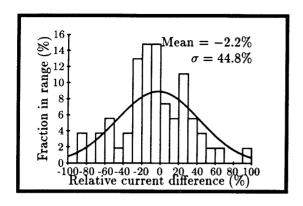

Figure 2.3: Drain current variation in adjacent  $3x3\mu$  MOS transistors.

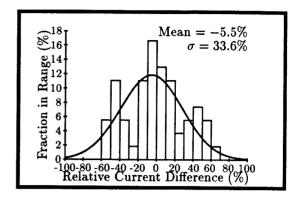

Figure 2.4: Drain current variation in adjacent  $24x24\mu$  MOS transistors.

are taken (Figure 2.3), the variation in relative current differences is substantial, and indicates (in this case) a fairly random process, as opposed to some longer-range (die-scale) systematic variation. These variations can be minimized by using larger transistors (Figure 2.4), or by relying on statistical numbers of transistors to participate in a computation.

Furthermore, it is clear that a computational scheme must be designed that is robust against such variation, and that displays a high tolerance to noise. Such claims are commonly made of collective systems; they must be carefully examined, however, in light of the actual implementation.

## 2.5 Design and Fabrication of a VLSI Implementation

The first version of the ASSOCMEM was designed in  $4\mu$ m nMOS technology, and has a dynamically programmable full interconnect. Consequently, every amplifier must be connectable to every other amplifier, dictating a mesh topology with the amplifiers on the diagonal, and their input and output lines running orthogonal to

Figure 2.5: ASSOCMEM architecture, and reinforcement of stable state with interconnect matrix generated by outer product technique (guaranteeing the symmetry property  $T_{ij} = T_{ji}$ ).

each other. At each off-diagonal node, an interconnection "conductance,"  $G_{ij}$ , is located. This topology (used in Figure 2.5) produces a two-dimensional embedding of the interconnect graph implied by Figure 2.1.

#### 2.5.1 Design of the Active Elements

In order to achieve a general computation, both positive and negative signals and interconnect values must be representable. It is not possible to fabricate negative resistances, as would be implied by a negative matrix element. The solution was to design the amplifiers to take differential inputs and generate complementary outputs. These inputs may be thought of as excitatory and inhibitory (i.e., noninverting and inverting). This duality allows us to represent "negative"  $V_j$ 's while using only positive

Figure 2.6: Dual-rail signal representation.

signals. Also, it guarantees symmetry between "positive" and "negative"  $V_j$ 's, since they are in fact the same voltage, merely on different lines (Figure 2.6). The matched parameters of VLSI devices ensure a high CMRR for this configuration.

This dual-rail voltage representation on both input and output to the active elements greatly simplifies their design. The only constraint on the transfer function  $g(v_j)$  is monotonicity (to guarantee convergence, by the energy theorem), and that the gain be sufficiently large. A loop gain of greater than 1 is required to create distinct stable states; a high gain guarantees that all outputs will be driven to the rails. We chose to implement the amplifiers with the simplest circuit element possible: an nMOS depletion-load inverter (Figure 2.7). Two inverters are required for each amplifier: one between the noninverting input and the complemented output, and one between the inverting input and the uncomplemented output. Note that feedback through the matrix is required to ensure that the amplifier outputs are indeed com-

Figure 2.7: ASSOCMEM neuron element, with variable feedback in  $T_{ii}$ .

Figure 2.8:  $T_{ii}$  element schematic.

plementary. If the two inverters are replaced by a pair of cross-coupled NOR gates (i.e., a simple SR flip-flop), this complementarity can be enforced at each diagonal  $(T_{ii})$  element.

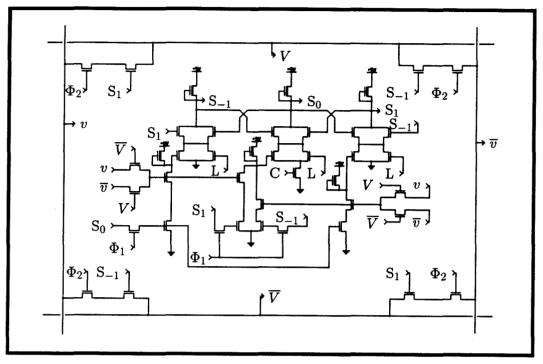

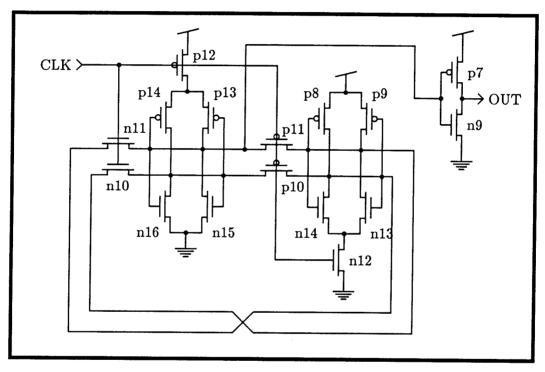

The design that was implemented allowed for both modes of operation to be tested, by providing a variable strength cross-connection (CROSS\_COUPLE) between the two inverters. The circuit diagram for the  $T_{ii}$  element is shown in Figure 2.8. Two pass transistors, gated on  $\Phi_1$ , allow the inputs of the amplifier to be latched. This capability is required for programming the interconnection matrix, and is desirable to halt the operation of the memory, for test purposes.

Figure 2.9: Resistive interconnect.

#### 2.5.2 Resistive Interconnect

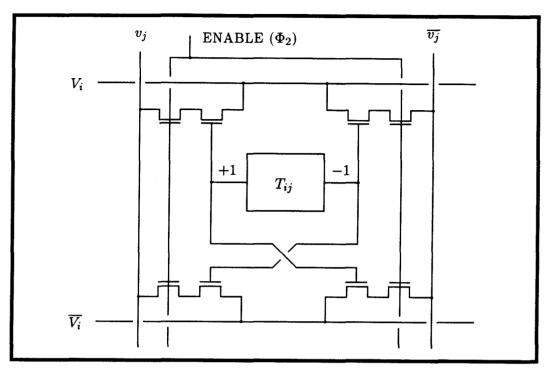

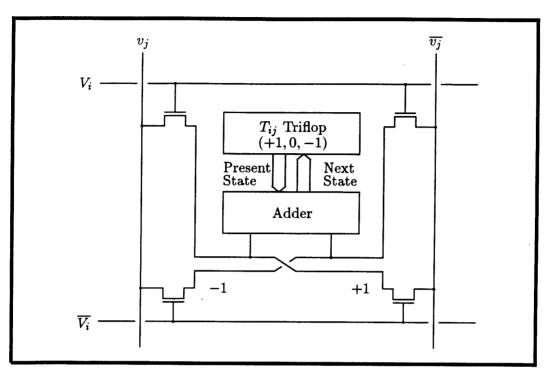

The resistive coupling, representing the  $G_{ij}$  matrix, is provided by pass transistors, which constitute the functional part of the " $G_{ij}$  Element" (Figure 2.9), located at every off-diagonal location of the chip. These pass transistors are controlled by the tri-flop  $T_{ij}$  cell, which provides three interconnection strengths (+1, 0, -1). When  $T_{ij} = +1$ , the + output of amplifier j is connected to the + input of amplifier i (excitation), and the - output is connected to the - input of the respective amplifiers (negative inhibition  $\Rightarrow$  excitation); the opposite is true for  $T_{ij} = -1$ . If  $T_{ij} = 0$ , all transistors are disconnected, and amplifier j has no direct influence on amplifier i. Each pass transistor is in series with an ENABLE transistor that allows the matrix to be selectively disengaged, providing a "single-step" operation.

### 2.5.3 Programming the $T_{ij}$ Elements

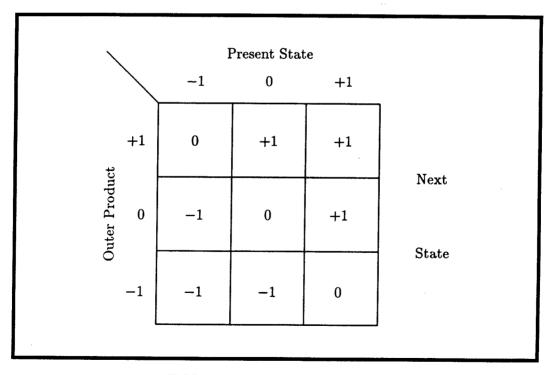

The associative memory can be programmed to have a particular vector as a stable state by adding the outer product of that vector with itself to the existing T matrix. In the ASSOCMEM, this operation is a primitive of the hardware, and has been generalized to allow taking outer products of any two vectors. The components of the outer product are produced in place at the  $T_{ij}$  element where they are required, by placing one vector on the horizontal signal lines, and the other on the vertical lines. This calculation requires only a 1-bit by 1-bit multiplication (for vectors containing +1 and -1 exclusively), which can be implemented by an AND structure (Figure 2.10). The result of the correlation is added to the present contents of the  $T_{ij}$  cell, and the result is stored in the tri-flop  $T_{ij}$  latch.

The addition operation is truncated, and the behavior is described in Table 2.1. It should be noted that this operation is *not* associative (the final matrix depends on the order in which the memories were added); however, the symmetry of the final matrix is guaranteed (since all intermediate sums comprised symmetric matrices, in the case of outer products taken of a vector with itself).

The effect of truncating the matrix in this fashion was one aspect of the theory we were interested in investigating. Software simulation of this scheme indicated that little functionality would be lost, in the case of uncorrelated memories (memories sufficiently far apart in Hamming space, so that no small number of bits become crucial in differentiating between them).

The complete schematic of the  $T_{ij}$  element, and the interconnection "resistors," is shown in Figure 2.11. It should be pointed out that all but four of the transistors are required just to implement the *programmability* of the ASSOCMEM. In many applications, the interconnect matrix could be determined a priori, and the chip fabricated to this specification. We estimate that 100 times as many active elements

Figure 2.10: Programming the  $T_{ij}$  matrix.

Table 2.1:  $T_{ij}$  update operation.

Figure 2.11: Schematic of  $T_{ij}$  element.  $S_1$ ,  $S_0$ , and  $S_{-1}$  are the three state-holding nodes, C is the CLEAR line, and L is the LOAD line.

could be fabricated within the same die size, for a predetermined function.

# 2.6 Fabrication History

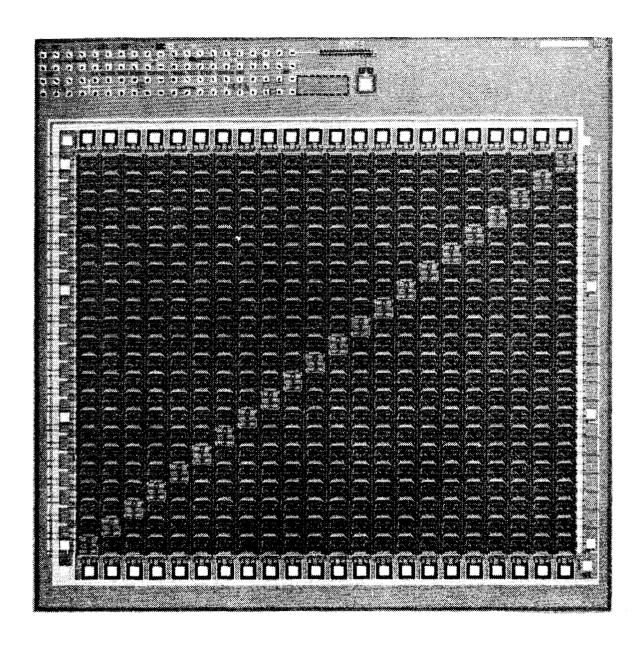

The first version of this chip was fabricated by MOSIS, the ARPA chip broker, on run M41U, in December 1983. It consisted of a 22 × 22 matrix, measuring  $6700\mu m$  ×  $5700\mu m$ , and containing over 20,000 transistors (Figure 2.12). The ASSOCMEM required 53 pads, as both inputs of each amplifier were brought out to pads. This redundancy was incorporated to increase flexibility in testing the chip. Only one input per amplifier is required, as the complement could be generated on-chip.

A second version of the chip was fabricated in May 1984, correcting some defects that made sections of the first chip nonfunctional and nonobservable. This redesign

yielded testable chips; however, the chips were returned unbonded, and only a few could be bonded locally and tested. The yield was low, and no single project was fully functional.

The desire for a larger sample size of chips prompted a third re-submission, which incorporated a set of minor modifications making it possible for MOSIS to package and bond the ASSOCMEM. This set of chips was returned in November 1984, and was subsequently tested.

# 2.7 Experimental Results

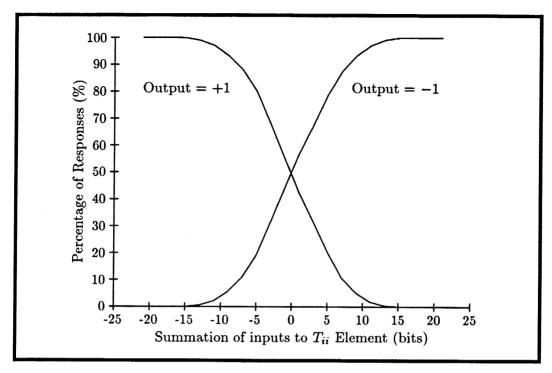

The ASSOCMEM was tested on a dedicated, workstation-based functional tester. The first sets of experiments were designed to measure the input-output characteristics of the active elements. The input of a single  $T_{ii}$  element was connected, (via  $T_{ij}$  elements) to the outputs of the other amplifiers. The output of this element was monitored for 220,000 randomly chosen input vectors (this operation corresponds to taking the inner product of the random input vector with a vector that is all 1s). The resulting output was plotted as a function of the arithmetic sum of the input bits (i.e., the number of +1's in the input vector minus the number of -1's), as shown in Figure 2.13. The symmetry of the graph demonstrates that the output is unbiased and the input sum to the active element is balanced for an input vector containing equal numbers of +1's and -1's.

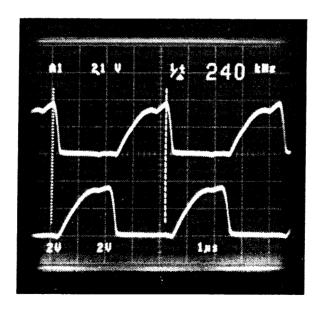

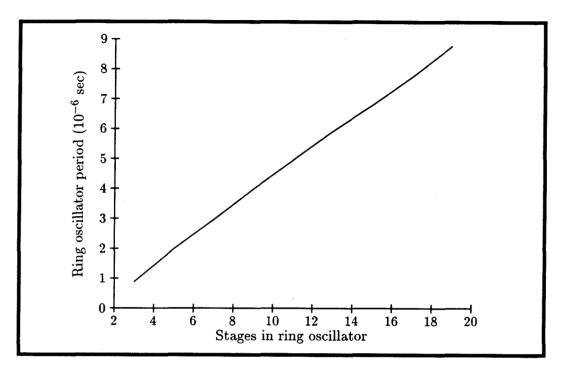

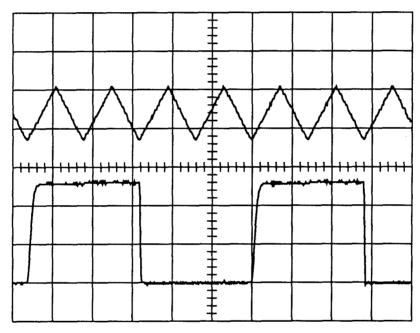

The ability to arbitrarily set a single  $T_{ij}$  element confirmed the functionality of the adder elements and tri-flops within each  $T_{ij}$  element. Several ring oscillators were programmed into the matrix, ranging from 3 stages to 19 stages. A typical waveform is shown in Figure 2.14. The results in Figure 2.15 indicate a characteristic propagation delay of 510ns per stage. The ring oscillators required an asymmetric connection matrix, as oscillatory behavior is excluded for symmetric matrices.

Figure 2.12: The ASSOCMEM.

Figure 2.13:  $T_{ii}$  transfer characteristic.

Figure 2.14: Ring oscillator.

Figure 2.15: Ring oscillator periods.

The next experiment was to perform an actual association. Two random memories were programmed into the matrix, via the on-chip outer product and adder mechanisms, and were observed to be, in fact, fixed points of the network. Due to the fast  $T_{ii}$  elements, the convergence of the network, including the driving of the output pads, was generally completed within a few microseconds.

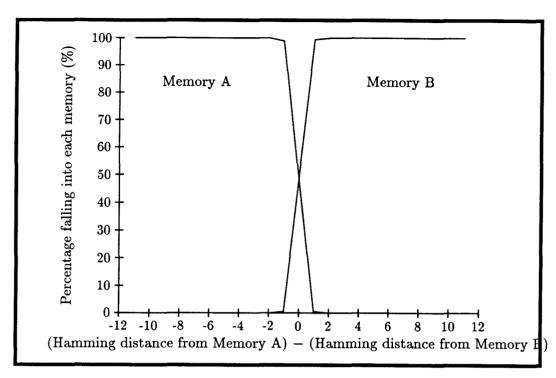

If the function of the ASSOCMEM is considered to be that of an error-correcting code, it is useful to consider the final stable state as a function of the bit-errors in the initial state. Typical experimental results demonstrating the distinct regions of convergence for a two memory system are shown in Figure 2.16. Effectively, this system always converges to the memory nearest in Hamming space to the initial condition.

By using  $\Phi_1$  and  $\Phi_2$  as nonoverlapping "clocks" to successively engage and disengage the connection matrix and  $T_{ii}$  elements, it is possible to "single-step" through

Figure 2.16: ASSOCMEM convergence properties.

the convergence operation. Each step corresponds to the network synchronously performing an inner product calculation to obtain the next state from the present state. It can be proven that a network which converges in synchronous-update mode will also do so asynchronously (i.e.,  $\Phi_1$  and  $\Phi_2$  ON simultaneously), although the converse is *not* true. For networks that do converge in single-step mode, it is interesting to observe the process in action (see Figure 2.17). In this illustration, note that the intermediate results are restored approximations to the analog voltages within the ASSOCMEM, and that although two iterations appear identical, the convergence is not yet complete.

Simulation results [Hop82b] have suggested an empirical limit on the number of uncorrelated memories that can be programmed into a Hopfield network to be approximately 15% of the number of active elements. Beyond this, spurious stable states begin to appear, often displacing desired memories. Since the network is based

on mutual inhibition and reinforcement, any correlation between memories causes some bits to be weighted more heavily than others. Statistical orthogonality between memories minimizes this effect.

A second limitation on the number of stable states arises due to the clipped nature of the  $T_{ij}$  matrix. Hopfield and Feinstein [FH85] showed that the "attraction" of stable states decays exponentially with the number of memories subsequently added to the matrix.

For the ASSOCMEM, it was found that up to three stable states could be reliably programmed, along with their complements (which appear due to the symmetry of the system). At all stages of the experimentation, consistency with simulation results was observed.

Of the ten chips returned by MOSIS, all were found to be functional to the extent of permitting at least two stable states. A CIF defect made a particular  $T_{ij}$  element malfunction in all chips. On some chips, sizable numbers of  $T_{ij}$  elements were inoperative. A sample map, from a particularly bad chip, is shown in Figure 2.18 ("\*" represent good  $T_{ij}$  elements). Since care was taken to keep the CLEAR circuit simple, and the matrices on all chips were observed to clear correctly (and totally), it is postulated that the primary failure mode was  $T_{ij}$  stuck-at-zero faults. Since null  $T_{ij}$ 's do not contribute detrimentally to the operation of the network, even the ASSOCMEM of Figure 2.18 was capable of memorizing two stable states, and associating to them.

# 2.8 High-Density Preprogrammed

# **Associative Memories**

In order to explore the behavior of large associative memories, we undertook the design and fabrication of a series of chips incorporating fixed (i.e., mask-programmable)

X

X

\*X\*\*\*\*\*\*\*\*

### \*\*\*\* X \*\*\*\*X X \*\*\*\*\* X X X X \*\*\*\*\*\*\*\*\* Incremental Association: X \*\*\*\*\*\*\*\*\*\*\*X (stable states (hex): OFOFOF, OOOFFF) X (vector written (hex): 00000F) \*\*\*\*\*\*\*\*\*\*\*\*X\* \*\*\*\* \*\*\*\*\*\*\*\*\*\*\*\*\* \*\*\*\* Iteration 0: V = 000000000000000001111\*\*\*\*\*X\*\*\*\* Iteration 1: V = 000000000111100001111 \*\*\*\*\* X\*\*\* Iteration 2: V = 000000000111100001111 \*\*\*\*\*\*\*\*\*\*\*\*\*\* \*X\*\* Iteration 3: V = 0001010000111100001111 \*\*\*\*\*\*\*\*\*\*\*\*\* \*\*X\*

Figure 2.17: Single-step association.

Iteration 4: V = 0011110000111100001111

Figure 2.18:  $T_{ij}$  yield map.

\*\*\*\*\*\*\*\*\*\*\*\*\*\*

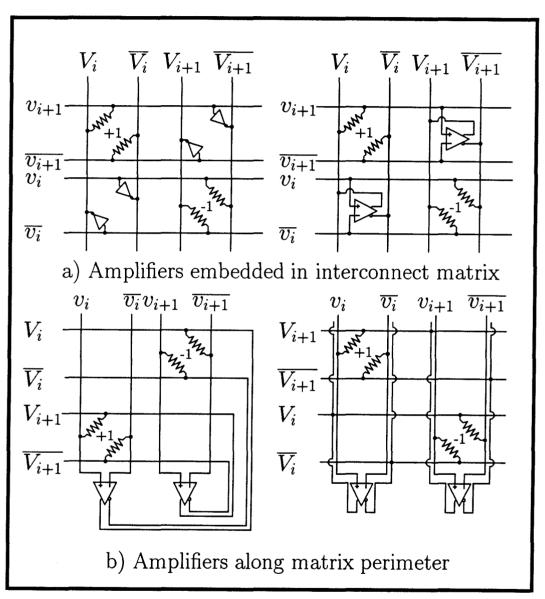

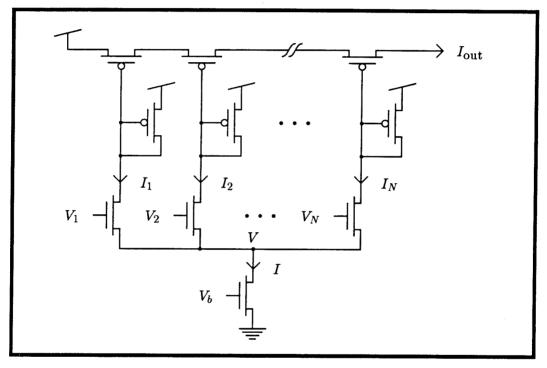

interconnect matrices. These  $T_{ij}$  elements were considerably smaller than the programmable  $T_{ij}$  element described in Section 2.5.2. Because of pitch-matching difficulties between the interconnect conductances and the active amplifiers, a different topology was employed (see Figure 2.19(b)); arranging the amplifiers along two sides of the array also facilitated I/O (the states of the neurons were read/loaded by means of a serial shift register).

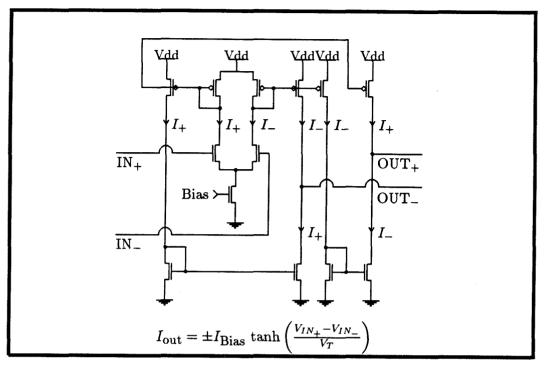

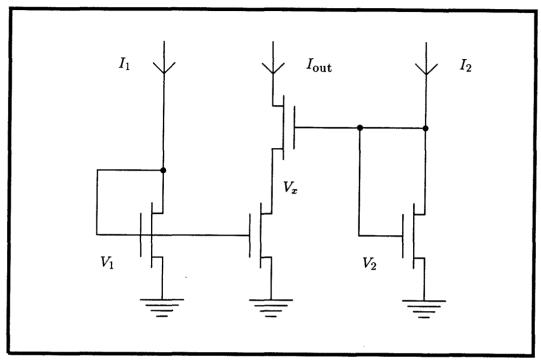

At this time, a redesign in a  $3\mu$  CMOS technology was undertaken. The amplifiers, which had been implemented with inverters in nMOS, were dual-output transconductance amplifiers, with true differential inputs (see Figure 2.20). The interconnect conductances measured  $16 \times 18\lambda$ , and could be mask-programmed to the values (-2, -1, 0, +1, +2). The entire chip contained 290 neurons (and 167620 possible transistors in the interconnect matrix). Twenty memories were stored, corresponding to bit-patterns for a schematized alphanumeric character set sampled at  $17 \times 17$  resolution.

The chip was fabricated on MOSIS run M65N in May, 1986. Upon testing, we found that all 20 memories were stable, and that the performance-limiting step was the serial readout of the results. Nonetheless, 50,000 associations per second were attainable. Of course, if a higher data rate were required, word-parallel inputs to the shift register would accelerate the data transfer.

# 2.9 Summary

Collective systems exhibit many appealing properties, including robustness and fault-tolerance, an ability to deal with ill-posed problems and noisy data, which conventional digital architectures do not. The ASSOCMEM represents a novel computational structure for VLSI. By implementing a well-understood system, such as associative memories, with collective circuit design, we have produced a functional

Figure 2.19: Fully-connected associative memory layout strategies.

Figure 2.20: Subthreshold CMOS active element.

component demonstrating these properties. Collective circuits are ideally suited to VLSI, as they require very large numbers of individually simple elements.

However, the model, as presented in this chapter, scales very poorly with available silicon area. The main difficulty is due to the full interconnect of the general Hopfield model; every neuron has to connect to every other neuron. Thus, the number of neurons, which determines the length of the codewords stored in the memory, increases proportionately to the *square root* of the die area. A secondary difficulty arises in the practical implementation of the different components: the architectures we have discussed require pitch-matching of the "neuron" and "synapse" components. In the 22-neuron ASSOCMEM, the programmable synapses were much more complicated than the active gain elements; in the preprogrammed associative memory, the synapses consisted of merely two transistors, while the CMOS amplifiers were much more complex.

Nonetheless, as feature sizes continue to shrink to the submicron range, the design of associative memories containing 1000 fully-connected neurons is feasible. Because of their ability to reach crisp decisions in the face of noisy or incomplete data, we expect that such networks will find application in the analysis of "fuzzy" sensory data, an application at which biological processes excel, while conventional computer architectures fail miserably.

# Chapter 3

# A Theoretical Model for Estimation of Circuit Wiring Density

Get your facts first, then you can distort them as you please.

Mark Twain (1835–1910)

## 3.1 Introduction

The need to consider complexity of wiring as an essential component of any algorithm has been a key contribution to computer science from VLSI design. Whereas in digital VLSI, wiring considerations give rise to an area-time tradeoff, in analog VLSI (in

the absence of time multiplexing) wiring complexity determines the scalability of an architecture or algorithm. This constraint is amply illustrated by the full interconnect of the Hopfield associative memory presented in Chapter 2. A fully-connected architecture requires  $O(N^2)$  area, where N is the number of neurons in the collective system.

Much of VLSI complexity theory has concentrated on efficient embeddings of particular computational graphs, under particular models for interconnect [Tho80] [Ull84]. The basic procedure is to select a class of graphs, and derive an information-theoretic lower bound for a separator (or partitioning) operator. This separator is then combined with a simple synchronous model for data communication to determine a minimum  $AT^2$  constraint on the computation.

In this section, we take a different approach: we ignore the time cost of communication (we assume that our analog networks use dedicated wires for all signals), and consider only the connectivity of graphs that can be generated when we define a set of layout parameters that specify acceptable component placements. This procedure will define a necessary (but not *sufficient*) constraint on the connectivity of a circuit graph, in contrast to traditional approaches, which generate the worst-case solution for a class of graphs, not the best-case for a specific graph (i.e., solutions which are "not universally optimal, but existentially optimal" [BL84]).

Under a connectivity model based on the intrinsic dimensionality of the interconnect technology, we will derive a wire partition function to bound the number of wires that can cross a closed perimeter. We will show how this function is consistent with a common empirical wiring relation known as Rent's rule. Finally, we will consider acceptable *distributions* of wire lengths within regular layouts, and derive a physical constraint on the average wire length predicted by the model.

### 3.2 Rent's Rule

A circuit may be considered as a graph, the vertices of which represent elements, linked by arcs corresponding to wires. Rent's rule [LR71] is an empirical relationship that relates the number of wires crossing an arbitrary boundary containing a group of elements:

$$P = P_0 N^b \tag{3.1}$$

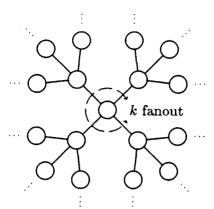

where P is the number of wires that need to cross the border, N is the number of elements (each of which has  $P_0$  pins) contained within the border, and b is an assumed constant. Analysis of several large designs has indicated that typical values lie in the range  $b \in [0.5, 0.75]$  [LR71].

# 3.3 An Operational Definition of Optimal Design

In this section, we introduce an aesthetic evaluation metric by which we can measure the quality of a design's implementation. Unlike the information-theoretic lower bounds developed by classical VLSI complexity theory [Tho80] [Ull84], we are less interested in bounds on classes of graphs than in considering the optimality of the layout of a specific instance within the class. In particular, we are interested in specifying minimum acceptance levels, below which a layout is considered too inefficient, and hence not economically viable. Finally, we will show how our constraint conforms to an empirical wiring relation known as Rent's rule.

We begin with a key observation regarding manufactured systems. We consider such systems to be examples of "optimal systems"—they have successfully satisfied the constraints imposed by the end-application (e.g., cost, size, power, weight, reliability, manufacturability).

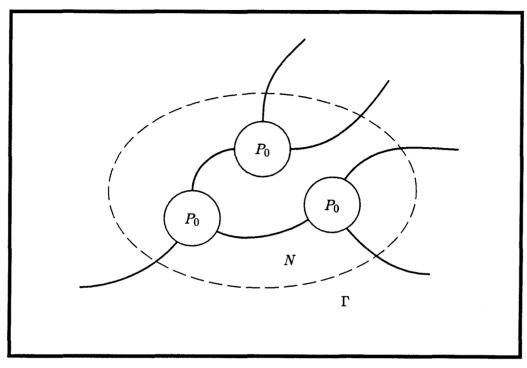

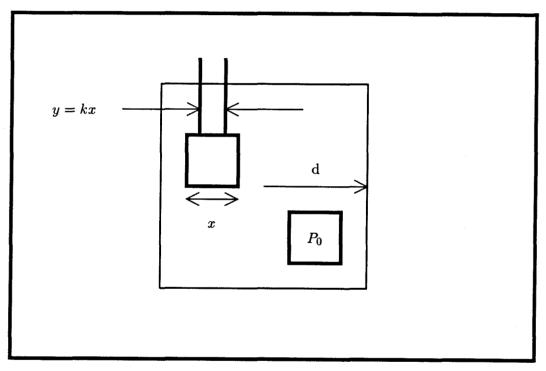

Figure 3.1: Estimating the number of wires crossing the perimeter.

Observation 3.1 In any system consisting of a collection of components, these components are distributed spatially in an approximately uniform manner.

The phrasing of this observation is intentionally general; we intend for the results of this section to be applicable to many different systems, ranging from integrated circuits to printed-circuit boards to entire racks and boxes. In this section, we combine this observation with the physical dimensionality of interconnect wiring to obtain an upper bound partition function. This function bounds the number of wires crossing a manifold containing a number of components of the system in question (see Figure 3.1). We will derive a particular function for systems that are intrinsically two-dimensional (e.g., integrated circuits and printed-circuit boards) and repeat the derivation for three-dimensional systems (e.g., computer back-planes and other aggressive interconnect technologies).

We begin by quantifying Observation 3.1: In a two-dimensional space, assume the density of components is uniform and equal to  $\rho$  components per unit area. Furthermore, assume that a fraction  $\gamma$  of the total area of the system is consumed by components. If we model the components as identical and square, of dimension  $x \times x$ , we have

$$x^2 = \frac{\gamma}{\rho}$$

**Proof:** Consider an area A of the system. By definition, the number of components within this area is  $\rho A$ , and the fraction of area occupied by these components is  $\gamma A$ . The average area per component is then  $\gamma/\rho$ , and, because the components measure x by x, the result  $x^2 = \gamma/\rho$  follows directly.  $\square$

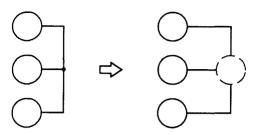

We now apply this result to the system in Figure 3.2: a square area of dimensions  $2d \times 2d$ . We wish to compute the number of wiring tracks crossing the perimeter as a function of the number of components within the boundary. We begin by parameterizing the space occupied by these wiring tracks (i.e., the wiring pitch) in terms of the single dimension of the model: x, the size of the components.

Let the average wire spacing y = kx. In the two-dimensional model, k is a scalar, because x and y are simple linear dimensions.

The component count within the boundary is then

$$N = 4d^2\rho \tag{3.2}$$

The maximum pin count *per element* is limited by the number of wiring channels that can abut the perimeter of a single component:

$$P_0 = \frac{4x}{y} = \frac{4}{k} \tag{3.3}$$

Figure 3.2: A model for circuit connectivity. The area in question measures 2d by 2d, and has perimeter 8d.

# 3.4 A Model for Circuit Connectivity

Estimating the number of wiring channels that cross the perimeter of the region is somewhat more subtle. The analysis is complicated by the need to model the routing capacity through the perimeter  $\Gamma$  in regions where  $\Gamma$  lies within a components. We make the (rather pessimistic) assumption that no routing can occupy the same physical location as the components. This restriction is appropriate for integrated circuits, where programmable logic devices (PLDs), gate arrays, and standard-cell designs tend to have preallocated wiring channels between rows of cells, with severely limited (if any) routing capability through these cells. In particular, this restriction is appropriate for the architecture in Chapter 4. It is less appropriate for technologies such as multi-layer PCBs; however, as we shall see, this approximation only affects certain multiplicative constants—it does not affect the general form of our results.

For randomly placed components, the probability that any given point on the perimeter lies within a component is  $\gamma$ ; consequently, the amount of perimeter available to wiring tracks is  $8d(1-\gamma)$ . The maximum number of wiring tracks is then

$$P = \frac{8d(1-\gamma)}{kx} \tag{3.4}$$

Combining Equations 3.2, 3.3, and 3.4, and recalling  $x^2 = \gamma/\rho$ , we obtain the partition function

$$P = \frac{1 - \gamma}{\gamma^{1/2}} P_0 N^{1/2} \tag{3.5}$$

As a self-consistency check, we can compare this expression with the conventional statement of Rent's rule (Equation 3.1):  $P = P_0 N^b$ . Setting b = 1/2, and solving  $\frac{1-\gamma}{\gamma^{1/2}} = 1$ , we obtain equivalence between the two forms for  $\gamma = 0.38$ . This result corresponds to an area utilization of approximately 40 percent, a typical value for semiautomated VLSI designs (gate arrays, standard-cells, etc.).

We are now in a position to reconsider our assumption that area dedicated to components was unavailable to routing tracks. If all of the perimeter is available for routing, Equation 3.5 becomes  $P = \gamma^{-1/2} P_0 N^{1/2}$ , which would allow  $\gamma$  to reach values near 1. Of course, such high utilization of board area is precisely what we see for typical multi-layer printed-circuit boards.

Now let us consider a higher dimensionality system. In three dimensions, we set  $y = kx^2$  (i.e., wires now have finite cross-sectional area), and observe that  $x^3 = \gamma/\rho$ .

The number of components within the volume is

$$N = \rho(2d)^3 \tag{3.6}$$

The maximum number of wires connecting each component is

$$P_0 = \frac{6x^2}{y} = \frac{6}{k} \tag{3.7}$$

The maximum number of wires crossing the surface  $\Gamma$  is

$$P = (1 - \gamma) \frac{6(2d)^2}{y} \tag{3.8}$$

Again, combining Equations 3.6, 3.7, and 3.8, we obtain

$$P = \frac{1 - \gamma}{\gamma^{2/3}} P_0 N^{2/3} \tag{3.9}$$

Setting  $\frac{1-\gamma}{\gamma^{2/3}} = 1$  gives  $\gamma = 0.43$ .

In summary, this analysis yields wiring bounds that are consistent with Rent's rule in form, and that suggest that the typically observed values for Rent's rule exponents (typically in the range [0.5, 0.7] [LR71]) are due to dimensional constraints of the implementation technology.

## 3.5 Contact Density

An interesting consequence to the partition function is obtained by considering the number of *contacts* that must be placed in order to satisfy the wiring limit of Equation 3.5. Clearly, not all of the wires that originate within the perimeter of the region in Figure 3.2 can propagate through the boundary. Each of the other wires must terminate at a contact with at least one other internal wire. For the purposes of this analysis, we assume, for simplicity, that precisely two wires meet at a contact (this assumption does not affect the form of the final result).

The total number of wires originating within a region measuring  $L \times L$  (or, d = L/2) is

$$P_{\text{total}} = P_0 L^2 \rho$$

The maximum number that can pass through the region's perimeter is given by Equation 3.4:

$$P = \frac{4L(1-\gamma)}{kx}$$

The number of required contacts is then

$$P_c = \frac{1}{2} \left( P_0 L^2 \rho - \frac{4L(1-\gamma)}{kx} \right)$$

In the large L limit,

$$P_c \to \frac{P_0 \rho L^2}{2}$$

and the average area per contact is

$$A_c = \frac{L^2}{P_c} = \frac{2(1/\rho)}{P_0}$$

We can interpret this expression by observing that  $(1/\rho)$  is the average area per

component, in which  $P_0$  pins originate. Each pin must terminate at a contact—the factor of 2 indicates that each contact has two wires connected to it.

If we compute the area density of contacts as a function of d, we obtain (recall that  $\rho = \gamma/x^2$ , and that  $P_0 = 4/k$ )

$$\Delta P_c = \frac{P_0}{x} \left( \frac{4d\gamma}{x} + \gamma - 1 \right) \Delta d$$

$$\Delta A = 8d\Delta d$$

$$\frac{\partial P_c}{\partial A} = \frac{P_0}{x} \left( \frac{\gamma}{2x} + \frac{\gamma - 1}{8d} \right)$$

(3.10)

Thus, the area density of contacts as a function of position d tends to a uniform limit. This result is consistent with our original assumption that components are uniformly distributed throughout the region.

# 3.6 Limits on Wire Length

Although the results of Section 3.3 place upper bounds on the *number* of available wiring channels, they tell us nothing about the macroscopic properties of the interconnect. In particular, it would be useful to consider the distribution of wire lengths predicted by the model, and to verify that this distribution satisfies the dimensional constraints of the implementation technology.

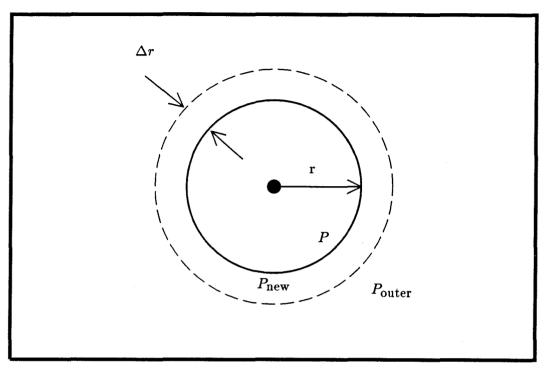

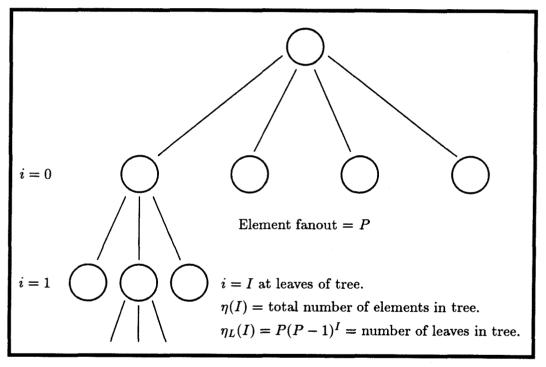

Before we can compute the average wire length, we must consider the rate at which wires from a given cell terminate as a function of distance. Consider the two-dimensional case illustrated in Figure 3.3; a circular partition is drawn a distance r from the cell in question. Applying the general form of Rent's rule, we have

$$P = P_0 N^b$$

$$= P_0 \gamma^b \left(\frac{r}{r_0}\right)^{2b}$$

Figure 3.3: Model for predicting distribution of wire lengths. The system consists of a regular array of identical cells of area  $\pi r_c^2$  each. P wires cross the perimeter at r, while  $P_{\text{outer}}$  cross the perimeter at  $r+\Delta r$ . The number of new pins appearing in the annulus is  $P_{\text{new}}$ .

since

$$N \equiv \frac{\pi r^2 \gamma}{\pi r_0^2}$$

.

If we consider the region between r and  $r + \Delta r$ , we estimate the wires that cross the outer perimeter to be

$$P_{\text{outer}} = P \cdot \left(1 + \frac{2b\Delta r}{r}\right)$$

The new pins that are created within the annulus are

$$P_{\text{new}} = \frac{2\gamma r \Delta r P_0}{r_0^2}$$

**Lemma 3.1** We now compute the number of wires  $P_T$  crossing through the annulus.

$$P_T = \frac{1}{2}(P + P_{\text{outer}} - P_{\text{new}})$$

**Proof:** Let x equal the number of wires that enter the annulus though the inner perimeter and connect to new pins within the annulus. Similarly, let y equal the number of wires that originate on new pins within the annulus, and exit the region through the outer perimeter. Let  $P_T$  equal the number of wires that enter through the inner perimeter and exit through the outer perimeter. The following relations hold:

$$P = x + P_T \tag{3.11}$$

$$P_{\text{outer}} = y + P_T \tag{3.12}$$

$$P_{\text{new}} = x + y \tag{3.13}$$

Adding Equations 3.11 and 3.12, and subtracting Equation 3.13 yields

$$P + P_{\text{outer}} - P_{\text{new}} = 2P_T$$

from which the lemma follows directly.  $\Box$

Substituting the values of P,  $P_{outer}$ , and  $P_{new}$  gives

$$P_T = P + \frac{Pb\Delta r}{r} - \frac{P_0 \gamma r \Delta r}{r_0^2}$$

The fraction of wires crossing though the annulus is then

$$F \equiv \frac{P_T}{P} = 1 + \frac{b\Delta r}{r} - \frac{\gamma^{1-b}r^{1-2b}\Delta r}{r_0^{2-2b}}$$

If  $\eta(r)$  is the number of wires from the central element that are still in existence a distance r from that element, a recurrence relation for  $\eta$  exists: