# Performance Analysis and Optimization of Asynchronous Circuits

Thesis by Steven Morgan Burns

In Partial Fulfillment of the Requirements

for the Degree of

Doctor of Philosophy

California Institute of Technology

Pasadena, California USA

1991

(Defended December 5, 1990)

© 1991

Steven Morgan Burns

All rights reserved

# Acknowledgments

I would first like to thank the members of my thesis defense committee, Chuck Seitz, Mani Chandy, Joel Franklin, Jan van de Snepscheut, and, my thesis advisor, Alain Martin, for the time and effort they expended in reading and criticizing my work. I thankfully acknowledge the funding support of DARPA and IBM.

I had the great pleasure of working with Alain, in an exciting, new field during my years at Caltech. I wish to thank the members of his research group that overlapped with me: Peggy Li, Kevin Van Horn, Blake Lewis, Pieter Hazewindus, Tony Lee, Dražen Borković, Marcel van der Goot, and Jose Tierno. Their constructive criticism of some early ideas greatly improved the quality of this thesis. I wish to thank the entire group, but especially, Marcel, Pieter, and Alain, for the time they spent carefully reading this thesis as well as other manuscripts. I will miss the weekly three-hour group meetings.

My graduate residence at Caltech would not have been as pleasant (although probably shorter) without the close friendship of: Nan and Andy Boden, Steve De-Weerth and Valerie, Emily, and Erik Patterson, Mass Sivilotti and Ruth Erlanson, Mary Ann Maher, Zoya Popović, Michael Emerling and Ruth Ballinger, John, Linda and Melissa Tanner, John and Julia Snyder, Pieter Hazewindus, and Andy Fyfe. "Walleyball", volleyball, basketball, and softball provided an excellent means to vent anger and have fun. I thank the Tanner's and the Snyder's for the time and effort required to organize those activities.

To Phil, Jean, Richard, Nancy, and Cathy, with whom I share a half, and to Helen, Owen, and Gracie, with whom I share a quarter.

## Abstract

Analytical techniques are developed to determine the performance of asynchronous digital circuits. These techniques can be used to guide the designer during the synthesis of such a circuit, leading to a high-performance, efficient implementation. Optimization techniques are also developed that further improve this implementation by determining the optimal sizes of the low-level devices (CMOS transistors) that compose the circuit.

# Contents

| 1 | Introduction |        |                                          | 1  |

|---|--------------|--------|------------------------------------------|----|

|   | 1.1          | Synth  | esis, Analysis, and Optimization         | 4  |

|   | 1.2          | Contr  | ibutions                                 | 6  |

|   | 1.3          | Thesis | s Overview                               | 8  |

| 2 | Eve          | nt-Ru  | le Systems                               | 9  |

|   | 2.1          | Gener  | al Event-Rule Systems                    | 9  |

|   | 2.2          | Repet  | itive Systems                            | 16 |

|   |              | 2.2.1  | Linear Timing Functions                  | 20 |

|   |              | 2.2.2  | Strongly Connected Systems               | 21 |

|   |              | 2.2.3  | The Cycle Period As a Performance Metric | 22 |

|   | 2.3          | Pseud  | orepetitive Systems                      | 24 |

|   |              | 2.3.1  | Definitions                              | 24 |

|   |              | 2.3.2  | Approximating the Timing Simulation      | 26 |

|   | 2.4          | Minin  | num-Period Linear Timing Functions       | 29 |

|   |              | 2.4.1  | Objective Function                       | 32 |

|   |              | 2.4.2  | Cycle Vectors of a Graph                 | 34 |

|   |              | 2.4.3  | Approximating the Timing Simulation      | 39 |

|   | 2.5          | Fast A | Moorithms                                | 49 |

|   |     | 2.5.1  | Graph Transformations                                     | 42 |

|---|-----|--------|-----------------------------------------------------------|----|

|   |     | 2.5.2  | Primal-Dual Method                                        | 44 |

|   | 2.6 | Sumn   | nary and Related Work                                     | 53 |

| 3 | The | e Synt | hesis Method                                              | 57 |

|   | 3.1 | Notat  | ion and Intermediate Forms                                | 57 |

|   |     | 3.1.1  | Communicating Sequential Processes                        | 58 |

|   |     | 3.1.2  | Handshaking Expansions                                    | 59 |

|   |     | 3.1.3  | Production Rules                                          | 60 |

|   |     | 3.1.4  | Quasi-Delay-Insensitive Circuits                          | 61 |

|   | 3.2 | Trans  | formations                                                | 64 |

|   |     | 3.2.1  | Process Decomposition                                     | 64 |

|   |     | 3.2.2  | Reshuffling                                               | 65 |

|   |     | 3.2.3  | Decomposition into Control and Data Parts                 | 65 |

|   |     | 3.2.4  | Multiple-Bit Datapaths and Completion Trees               | 67 |

|   |     | 3.2.5  | Strengthening the Production Rules                        | 70 |

|   |     | 3.2.6  | Introducing State Variables                               | 70 |

|   |     | 3.2.7  | Bubble Shuffling                                          | 70 |

|   |     | 3.2.8  | Decomposition of Large Elements                           | 71 |

|   |     | 3.2.9  | Resetting to the Initial State                            | 71 |

| 4 | Mod | deling | Programs with ER Systems                                  | 72 |

|   | 4.1 | Model  | ing Delays                                                | 73 |

|   | 4.2 | Model  | ing Handshaking Expansions                                | 74 |

|   |     | 4.2.1  | Straight-Line Handshaking Expansions                      | 77 |

|   |     | 4.2.2  | Communication Between Processes                           | 85 |

|   |     | 4.2.3  | Conversion From a General ER System to a Pseudorepetitive |    |

|   |     |        | ER System                                                 | 85 |

|   |      | 4.2.4  | Vacuous Firings                                    | 88  |

|---|------|--------|----------------------------------------------------|-----|

|   |      | 4.2.5  | Other Initial States                               | 89  |

|   |      | 4.2.6  | Multiple Assignments                               | 89  |

|   |      | 4.2.7  | General Parallel Composition Statements            | 90  |

|   |      | 4.2.8  | Conversion to Simple Repetitive Systems            | 90  |

|   | 4.3  | Model  | ing Production Rule Sets                           | 91  |

|   | 4.4  | Data-  | Dependent Computations                             | 96  |

|   | 4.5  | Inhere | ntly Disjunctive Computations                      | 98  |

| 5 | Line | ear Ar | rays of Processes                                  | 102 |

|   | 5.1  | Regula | ar Systems                                         | 102 |

|   |      | 5.1.1  | Linear Timing Function                             | 105 |

|   |      | 5.1.2  | Linear Program                                     | 105 |

|   | 5.2  | Minim  | num-Period/Minimum-Latency Linear Timing Functions | 107 |

|   | 5.3  | Bound  | lary Processes                                     | 119 |

| 6 | Cas  | e Stud | ies                                                | 122 |

|   | 6.1  | FIFO   | Queues                                             | 122 |

|   |      | 6.1.1  | CRT Constraint                                     | 123 |

|   |      | 6.1.2  | Passive/Active Data Constraints                    | 123 |

|   |      | 6.1.3  | Interleavings of Passive/Active Protocols          | 125 |

|   |      | 6.1.4  | Interleavings of Active/Passive Protocols          | 135 |

|   | 6.2  | Microp | processor                                          | 142 |

|   | 6.3  | Other  | Asynchronous Pipeline Circuits                     | 150 |

|   |      | 6.3.1  | Meng                                               | 150 |

|   |      | 6.3.2  | Greenstreet, Williams, and Staunstrup              | 154 |

| 7          | Per                           | forma   | nce Optimization                 | 165 |

|------------|-------------------------------|---------|----------------------------------|-----|

|            | 7.1                           | Tau M   | Iodel                            | 165 |

|            | 7.2 Convex Objective Function |         | ex Objective Function            | 170 |

|            |                               | 7.2.1   | Power Constraint                 | 172 |

|            |                               | 7.2.2   | Minimum Transistor Widths        | 174 |

|            | 7.3                           | Subgra  | adient Algorithm                 | 176 |

|            |                               | 7.3.1   | The Subgradient                  | 176 |

|            |                               | 7.3.2   | Basic Algorithm                  | 176 |

|            |                               | 7.3.3   | Convex Constraints               | 177 |

|            |                               | 7.3.4   | Heuristics and Space Dilation    | 178 |

| 8          | Sun                           | nmary   | and Concluding Remarks           | 183 |

|            | 8.1                           | Loose   | Ends                             | 184 |

| $_{ m Bi}$ | bliog                         | graphy  |                                  | 186 |

| A          | Acc                           | uracy   | of Tau Model                     | 191 |

|            | A.1                           | Tied T  | Transistors in the Pull-up Chain | 198 |

|            | A.2                           | Maxim   | num Approximation                | 199 |

|            | A.3                           | Transi  | stor Models                      | 203 |

| В          | Det                           | ailed E | Example                          | 204 |

# List of Figures

| 1.1  | Execution of fib.asm on $2.0\mu m$ processor                 | 2  |

|------|--------------------------------------------------------------|----|

| 2.1  | Collapsed-constraint graph of Example 2.9                    | 54 |

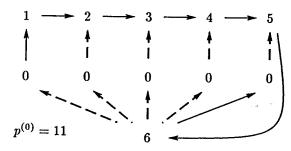

| 2.2  | Complete graph at iteration 0                                | 54 |

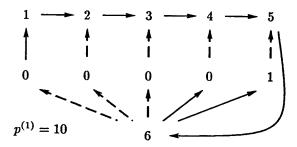

| 2.3  | Critical-arc graph at iteration 0                            | 54 |

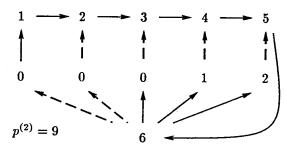

| 2.4  | Complete graph at iteration 1                                | 55 |

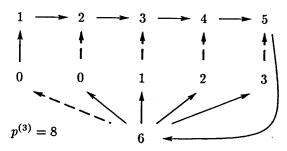

| 2.5  | Critical-arc graph at iteration 1                            | 55 |

| 2.6  | Complete graph at iteration 2                                | 55 |

| 2.7  | Critical-arc graph at iteration 2                            | 55 |

| 2.8  | Complete graph at iteration 3                                | 55 |

| 2.9  | Critical-arc graph at iteration 3                            | 55 |

| 2.10 | Complete graph at iteration 4                                | 55 |

| 2.11 | Cyclic critical-arc graph at iteration 4                     | 55 |

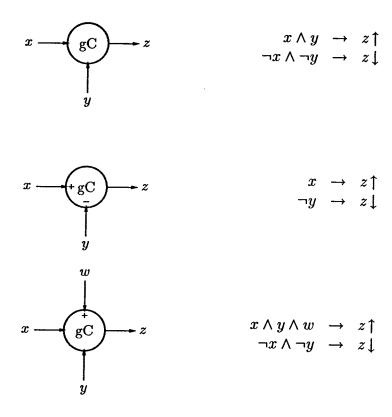

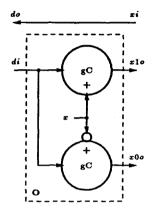

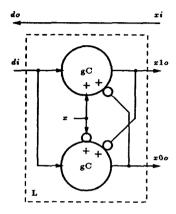

| 3.1  | Schematic symbols for various generalized C-elements         | 63 |

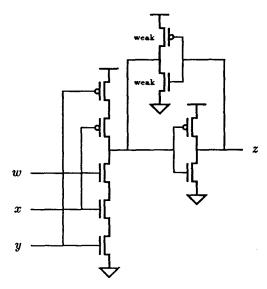

| 3.2  | Weak-feedback CMOS implementation of a generalized C-element | 64 |

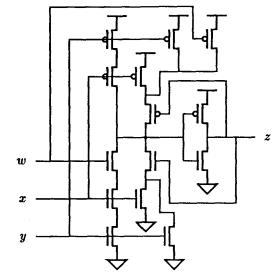

| 3.3  | Fully-static CMOS implementation of a generalized C-element  | 64 |

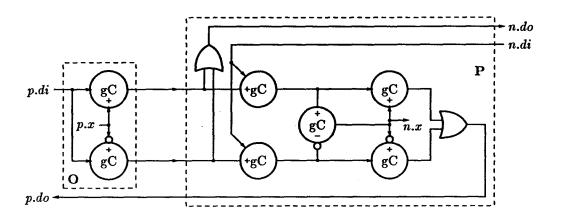

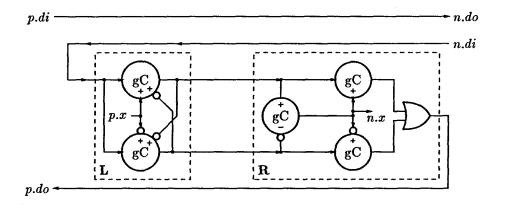

| 3.4  | Implementation of an output unit                             | 68 |

| 3.5  | Alternative implementation of an output unit                 | 68 |

| 3.6  | Implementation of an active-input unit.                      | 68 |

| 3.7  | Implementation of a passive-input unit                                      | 68  |  |

|------|-----------------------------------------------------------------------------|-----|--|

| 3.8  | Standard implementation of a passive-input/active-output data<br>path.      |     |  |

| 3.9  | Alternative implementation of a passive-input/active-output datapath.       | 69  |  |

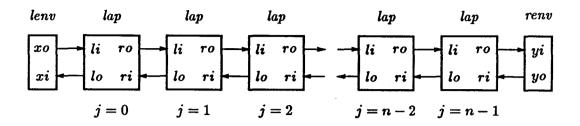

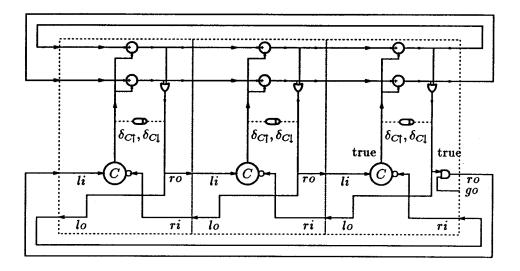

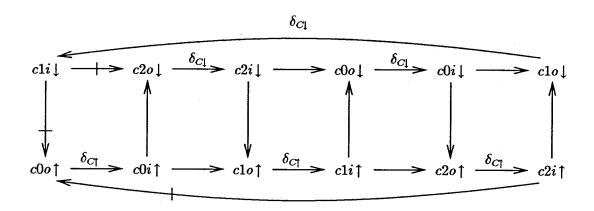

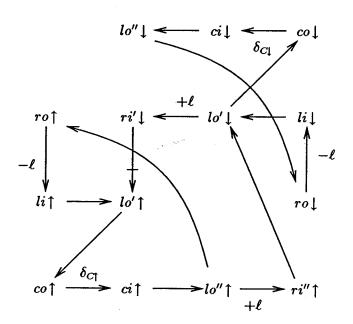

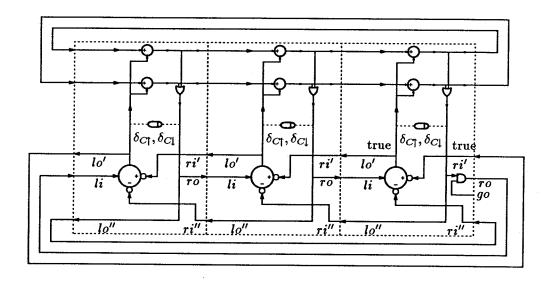

| 5.1  | Regular linear array of $n$ $lap$ processes                                 | 104 |  |

| 5.2  | Latency/period constraint graph for the lazy-active/passive buffer of       |     |  |

|      | Example 5.1                                                                 | 106 |  |

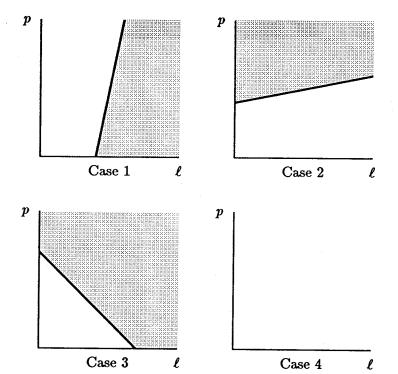

| 5.3  | Four types of constraints imposed by (5.6)                                  | 109 |  |

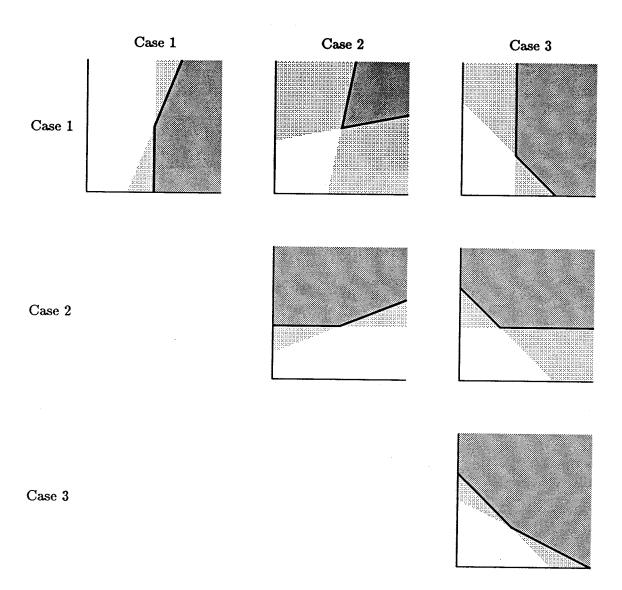

| 5.4  | Six types of constraint intersections imposed by (5.6)                      | 110 |  |

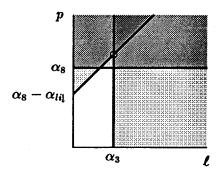

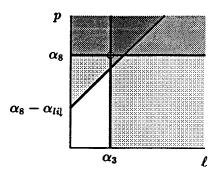

| 5.5  | Graphical depiction of constraints imposed in Example 5.3                   | 111 |  |

| 5.6  | Case 2 critical cycle in three instances of the lazy-active/passive buffer  | 115 |  |

| 5.7  | Intersection of Case 1 and Case 2 critical cycle in the lazy-active/passive |     |  |

|      | buffer                                                                      | 116 |  |

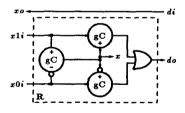

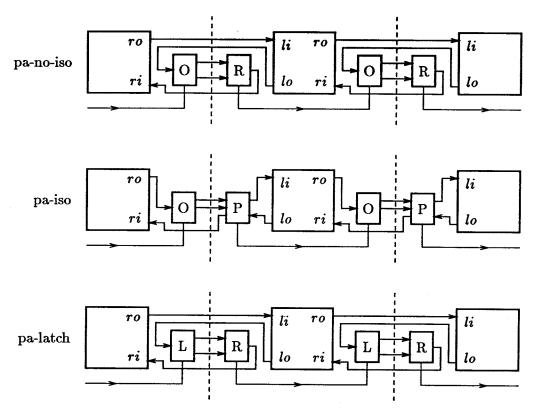

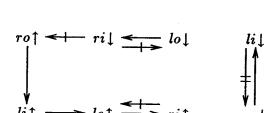

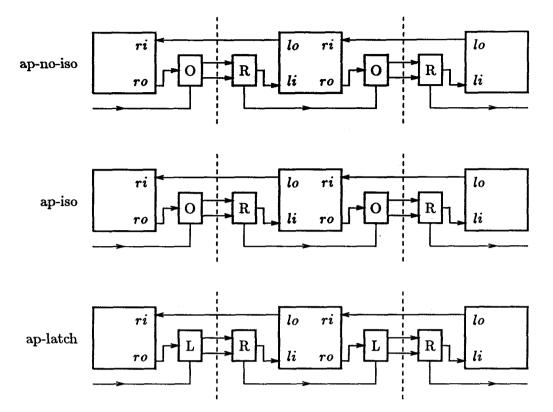

| 6.1  | Possible datapath implementations for a passive/active FIFO                 | 124 |  |

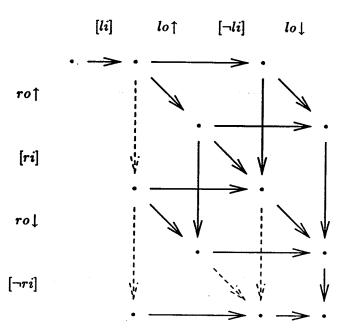

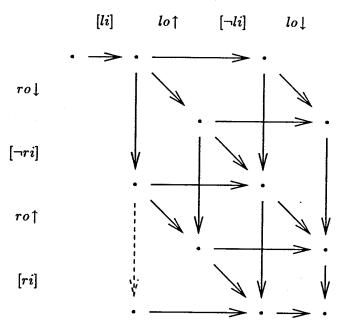

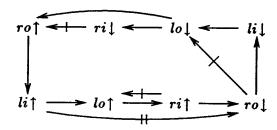

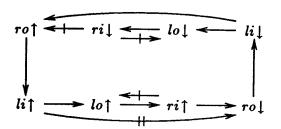

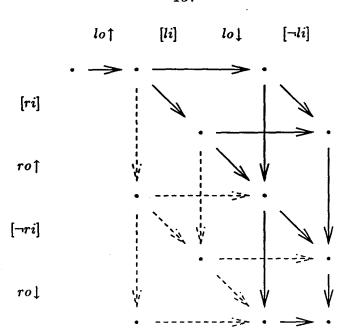

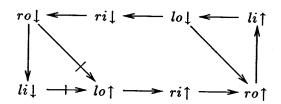

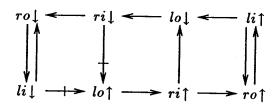

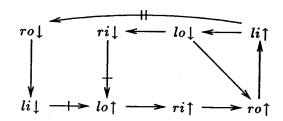

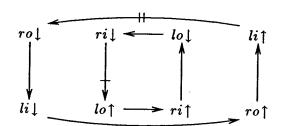

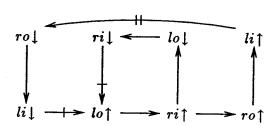

| 6.2  | Diagram to enumerate the passive/active interleavings                       | 125 |  |

| 6.3  | Diagram to enumerate the passive/active interleavings that contain the      |     |  |

|      | vacuous wait $[\neg ri]$                                                    | 126 |  |

| 6.4  | Diagram to enumerate the passive/active interleavings that contain the      |     |  |

|      | vacuous firing $ro\downarrow$                                               | 126 |  |

| 6.5  | Latency/period constraint graph for buffer pa                               | 129 |  |

| 6.6  | Latency/period constraint graph for buffer a1                               | 130 |  |

| 6.7  | Latency/period constraint graph for buffer c8                               | 130 |  |

| 6.8  | Latency/period constraint graph for buffer c9                               | 130 |  |

| 6.9  | Latency/period constraint graph for buffer pla                              | 130 |  |

| 6.10 | Latency/period constraint graph for buffer b1                               | 130 |  |

| 6.11 | Latency/period constraint graph for buffer b2                               | 130 |  |

| 6.12 | Latency/period constraint graph for buffer c3                               | 131 |  |

| 6.13 | Latency/period constraint graph for buffer $c4$                        | 131 |

|------|------------------------------------------------------------------------|-----|

| 6.14 | Latency/period constraint graph for buffer c5                          | 131 |

| 6.15 | Latency/period constraint graph for buffer $c\theta$                   | 131 |

| 6.16 | Latency/period constraint graph for buffer c1                          | 131 |

| 6.17 | Latency/period constraint graph for buffer c2                          | 131 |

| 6.18 | Possible datapath implementations for an active/passive FIFO           | 135 |

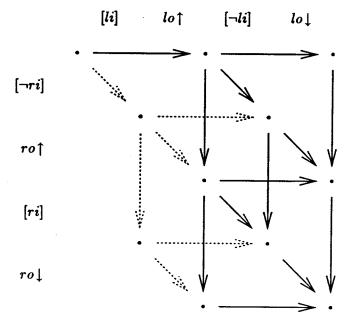

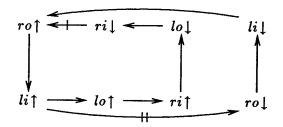

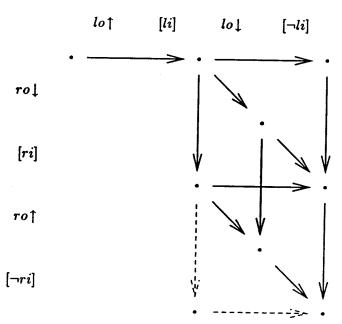

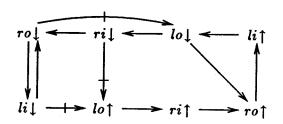

| 6.19 | Diagram to enumerate the active/passive interleavings                  | 137 |

| 6.20 | Diagram to enumerate the active/passive interleavings that contain the |     |

|      | vacuous action $ro\downarrow$                                          | 139 |

| 6.21 | Latency/period constraint graph for buffer ap                          | 140 |

| 6.22 | Latency/period constraint graph for buffer $d1$                        | 140 |

| 6.23 | Latency/period constraint graph for buffer lap                         | 140 |

| 6.24 | Latency/period constraint graph for buffer $d3$                        | 140 |

| 6.25 | Latency/period constraint graph for buffer $d4$                        | 140 |

| 6.26 | Latency/period constraint graph for buffer d5                          | 140 |

| 6.27 | Latency/period constraint graph for buffer $e\theta$                   | 141 |

| 6.28 | Latency/period constraint graph for buffer e1                          | 141 |

| 6.29 | Latency/period constraint graph for buffer e2                          | 141 |

| 6.30 | Latency/period constraint graph for buffer e3                          | 141 |

| 6.31 | Latency/period constraint graph for buffer e4                          | 141 |

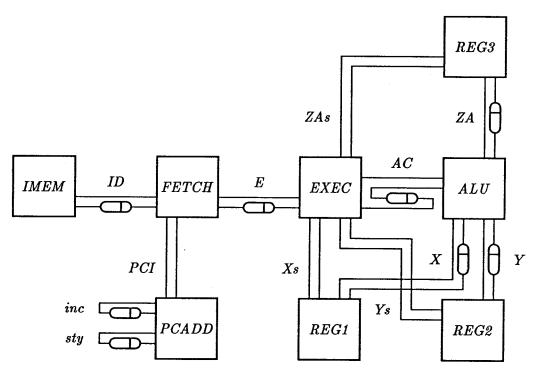

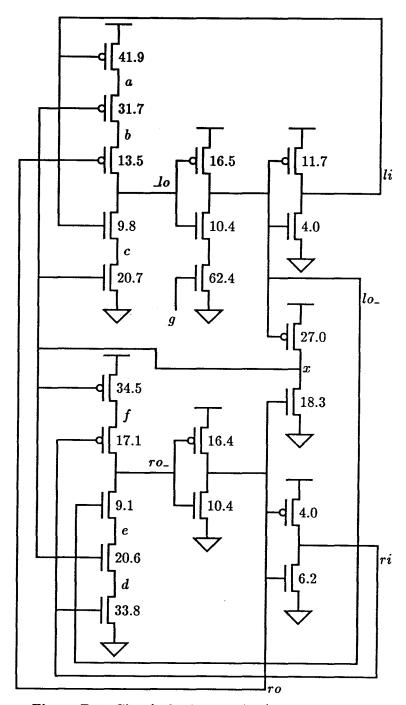

| 6.32 | Interconnections between processes of the $AM$                         | 144 |

| 6.33 | First part of the cycle period graph for $AM$                          | 145 |

| 6.34 | Second part of the cycle period graph for $AM$                         | 146 |

| 6.35 | Simplified cycle-period graph corresponding to Figure 6.34             | 147 |

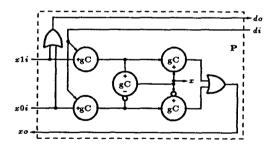

| 6.36 | Meng's FIFO implementation                                             | 150 |

| 6.37 | Latency/period constraint graph corresponding to Meng's FIFO im-       |     |

|      | plementation                                                           | 151 |

|      |                                                                        |     |

| 6.38 | Latency/period constraint graph of the improved implementation        | 153 |

|------|-----------------------------------------------------------------------|-----|

| 6.39 | Implementation of the pipeline stage used by Greenstreet, Williams,   |     |

|      | and Staunstrup                                                        | 155 |

| 6.40 | Latency/period constraint graph of the GWS pipeline stage             | 156 |

| 6.41 | Three GWS pipeline stages connected to form a ring                    | 157 |

| 6.42 | Latency/period constraint graph of three GWS pipeline stages con-     |     |

|      | nected to form a ring                                                 | 158 |

| 6.43 | Latency/period constraint graph for the modified GWS pipeline stage.  | 161 |

| 6.44 | Three modified GWS pipeline stages connected in a ring                | 162 |

| 6.45 | Latency/period constraint graph of three modified GWS pipeline stages |     |

|      | connected in a ring                                                   | 163 |

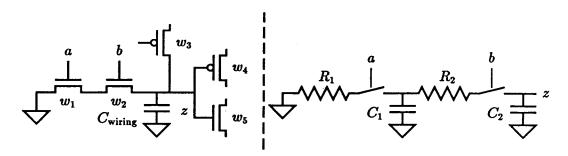

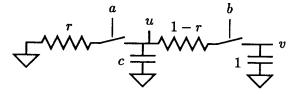

| 7.1  | RC approximation of a CMOS pulldown                                   | 166 |

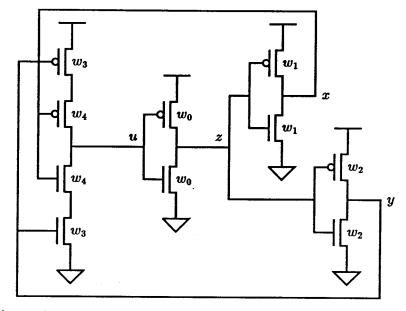

| 7.2  | CMOS circuit for C-element and the trivial environment                | 168 |

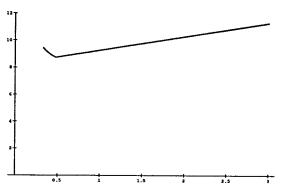

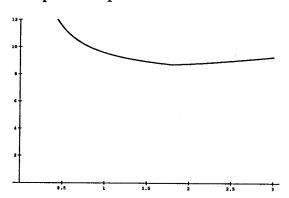

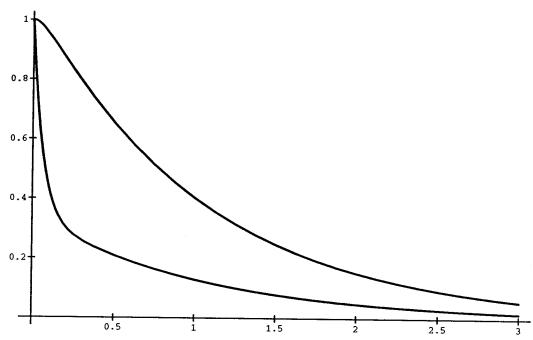

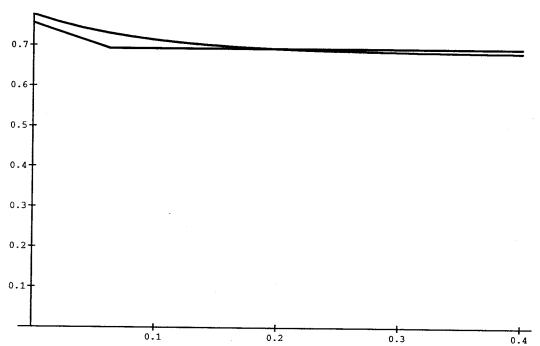

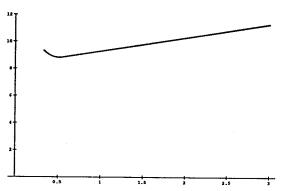

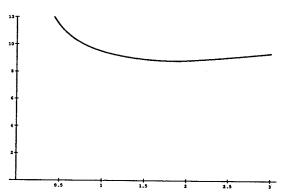

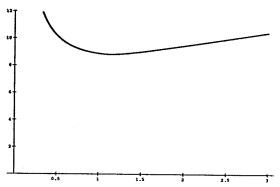

| 7.3  | Cross section of $f$ with respect to $w_1, \ldots, \ldots$            | 171 |

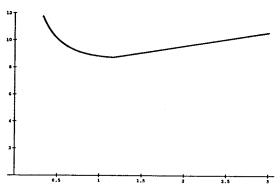

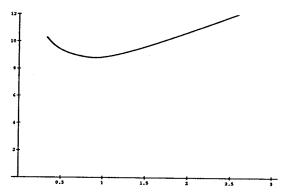

| 7.4  | Cross section of $f$ with respect to $w_2$                            | 171 |

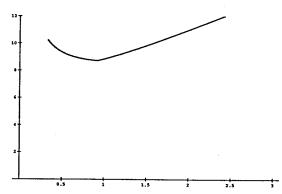

| 7.5  | Cross section of $f$ with respect to $w_3$                            | 171 |

| 7.6  | Cross section of $f$ with respect to $w_4$                            | 171 |

| A.1  | RC pulldown circuit with dimensionless variables                      | 191 |

| A.2  | Time evolution of internal and external node voltages                 | 193 |

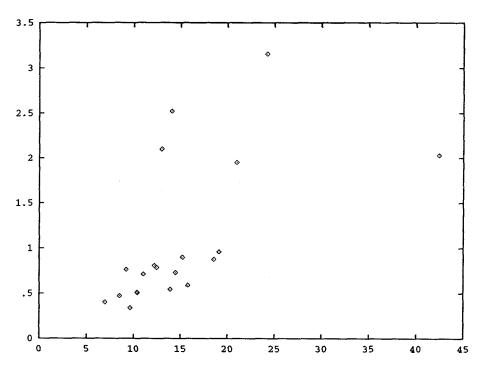

| A.3  | Plot comparing tau-model estimated and actual RC delay                | 200 |

| A.4  | Cross section of smooth $f$ with respect to $w_1$                     | 202 |

| A.5  | Cross section of smooth $f$ with respect to $w_2$                     | 202 |

| A.6  | Cross section of smooth $f$ with respect to $w_3$                     | 202 |

|      | Cross section of smooth $f$ with respect to $w_4$                     | 202 |

| B.1  | Input representation of a single lazy-active/passive buffer           | 205 |

| B.2  | Optimization equations for the lazy-active/passive buffer                                                                                                                                      | 206 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| B.3  | Optimization equations for the lazy-active/passive buffer (cont.)                                                                                                                              | 207 |

| B.4  | Output of optimization tool for the lazy-active/passive buffer                                                                                                                                 | 208 |

| B.5  | Output of optimization tool for the lazy-active/passive buffer (cont.).                                                                                                                        | 209 |

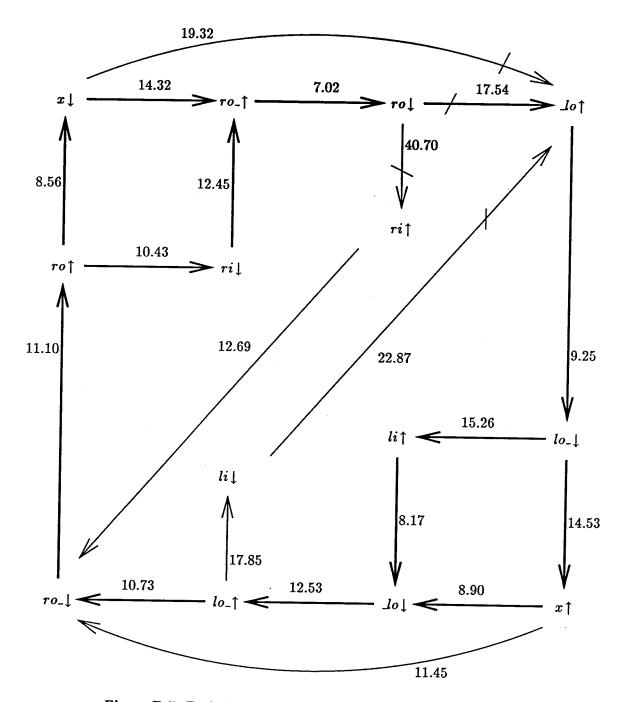

| B.6  | Circuit for lazy-active/passive buffer                                                                                                                                                         | 210 |

| B.7  | Period constraint graph with optimized transistors                                                                                                                                             | 211 |

| B.8  | Period constraint graph with nonoptimized transistors                                                                                                                                          | 212 |

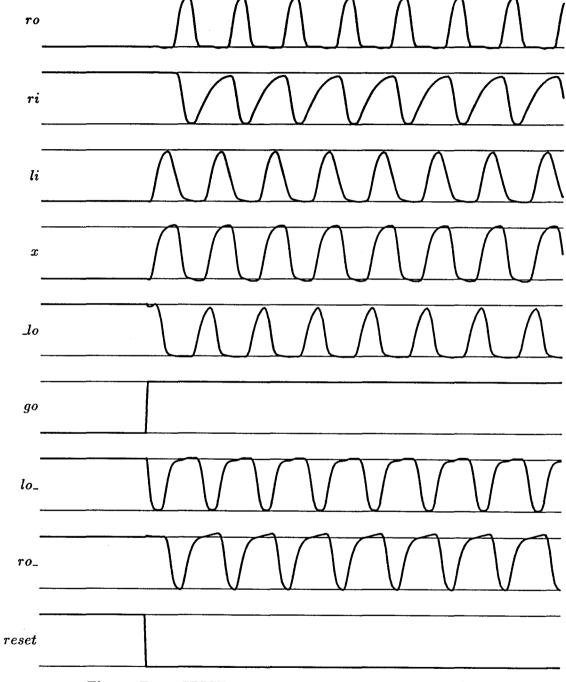

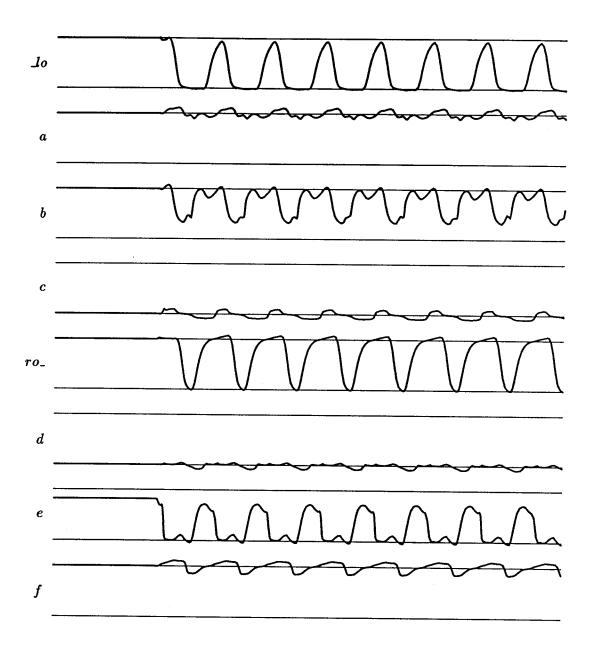

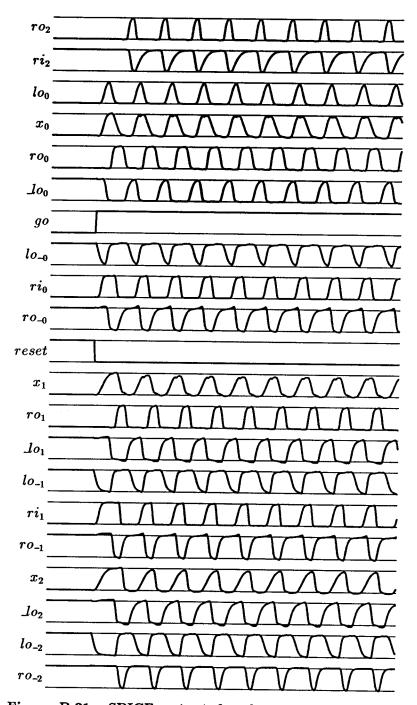

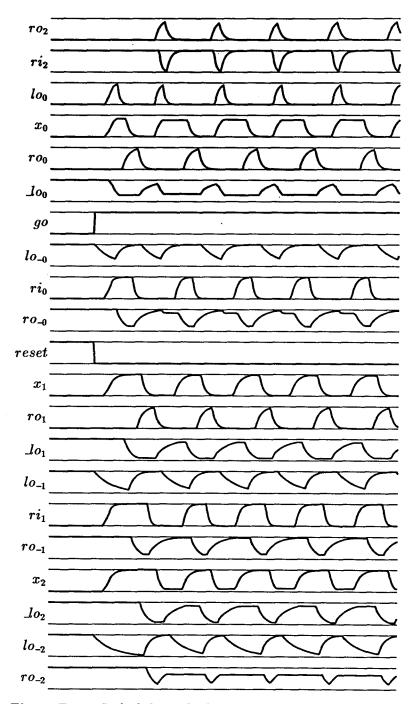

| B.9  | SPICE output of optimized lazy-active/passive buffer                                                                                                                                           | 213 |

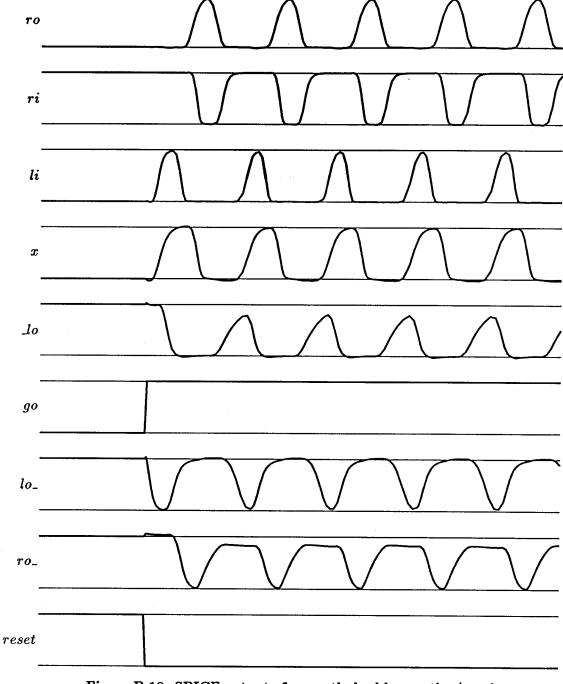

| B.10 | SPICE output of nonoptimized lazy-active/passive buffer                                                                                                                                        | 214 |

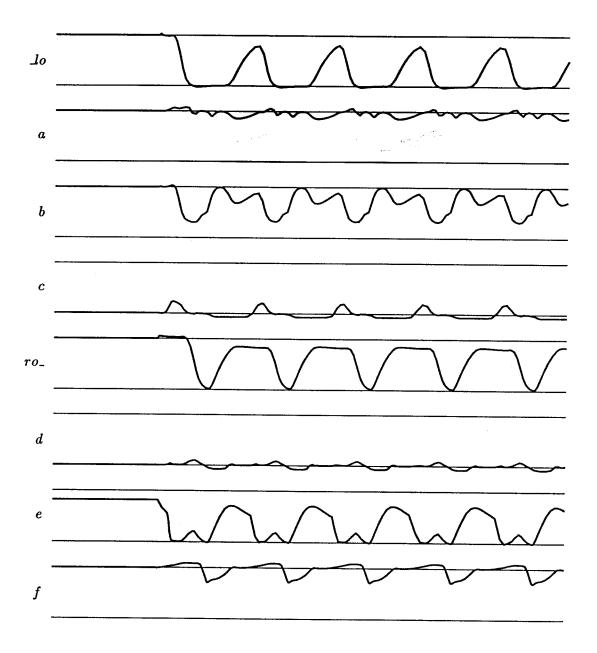

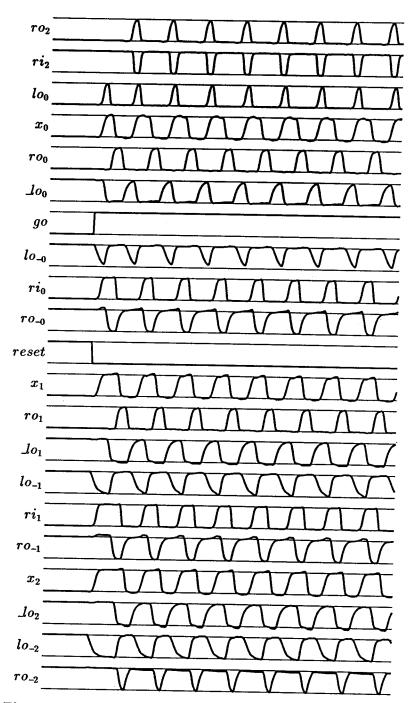

| B.11 | SPICE output of optimized lazy-active/passive buffer using the switch                                                                                                                          |     |

|      | $model.\ \dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots$ | 215 |

| B.12 | SPICE output of nonoptimized lazy-active/passive buffer using the                                                                                                                              |     |

|      | switch model                                                                                                                                                                                   | 216 |

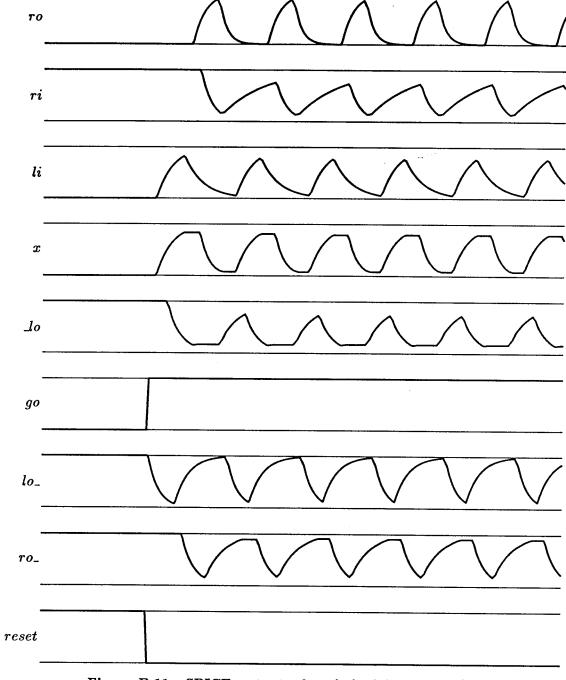

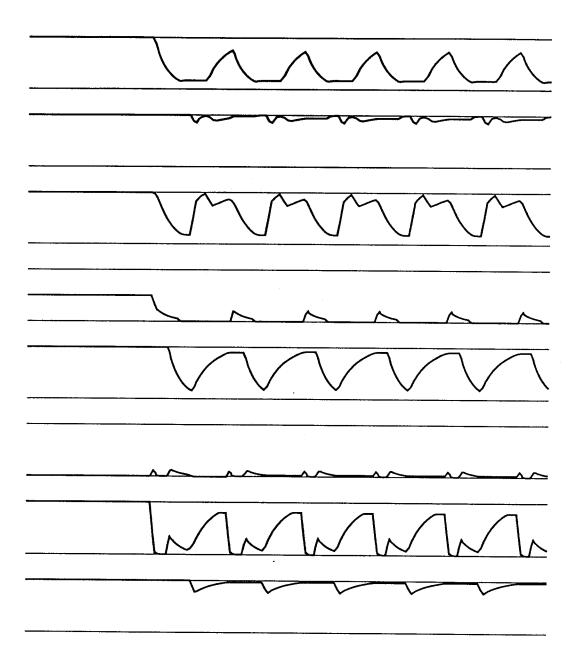

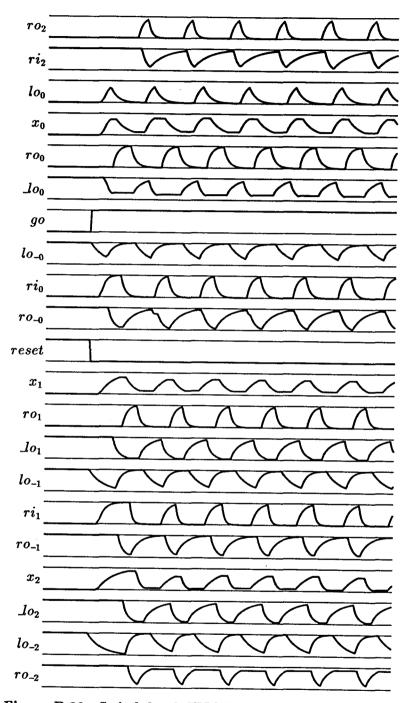

| B.13 | SPICE output of optimized lazy-active/passive buffer                                                                                                                                           | 217 |

| B.14 | SPICE output of nonoptimized lazy-active/passive buffer                                                                                                                                        | 218 |

| B.15 | SPICE output of optimized lazy-active/passive buffer using the switch                                                                                                                          |     |

|      | model                                                                                                                                                                                          | 219 |

| B.16 | SPICE output of nonoptimized lazy-active/passive buffer using the                                                                                                                              |     |

|      | switch model                                                                                                                                                                                   | 220 |

| B.17 | Graph of simulated vs. predicted delays. Transistor simulation. Simple                                                                                                                         |     |

|      | model                                                                                                                                                                                          | 223 |

| B.18 | Graph of simulated vs. predicted delays. Transistor simulation. Simple                                                                                                                         |     |

|      | model                                                                                                                                                                                          | 224 |

| B.19 | Graph of simulated vs. predicted delays. Transistor simulation. Tied                                                                                                                           |     |

|      | model                                                                                                                                                                                          | 227 |

| B.20 | Graph of simulated vs. predicted delays. Switch-level simulation. Tied                                                                                                                         |     |

|      | model                                                                                                                                                                                          | 228 |

| B.21 SPICE output for three-stage optimized lazy-active/passive pipeline 229             |

|------------------------------------------------------------------------------------------|

| B.22 SPICE output for three-stage nonoptimized lazy-active/passive pipeline.230          |

| B.23 Switch-level SPICE output for three-stage optimized lazy-active/passive             |

| pipeline                                                                                 |

| $B.24\ Switch-level\ SPICE\ output\ for\ three-stage\ nonoptimized\ lazy-active/passive$ |

| pipeline                                                                                 |

|                                                                                          |

# List of Tables

| 3.1 | Basic constructs of CSP used to describe processes                     | 58  |

|-----|------------------------------------------------------------------------|-----|

| 3.2 | Syntax of boolean expressions used to guard commands                   | 59  |

| 4.1 | Correspondence between occurrence indices of input and output vari-    |     |

|     | ables                                                                  | 81  |

| 4.2 | Assignment and wait patterns of a <i>SLHE</i> in standard form         | 82  |

| 4.3 | Subsumption of rules under the target-name convention for delays       | 82  |

| 6.1 | Table of external delays in the cycle period and latency of each pas-  |     |

|     | sive/active CRT buffer                                                 | 132 |

| 6.2 | Table of external delays in the cycle period and latency of each pas-  |     |

|     | sive/active CRT buffer                                                 | 138 |

| 7.1 | Performance of optimization tool                                       | 180 |

| B.1 | Table of predicted vs. simulated delays. Transistor simulation. Simple |     |

|     | model                                                                  | 221 |

| B.2 | Table of predicted vs. simulated delays. Switch-level simulation. Sim- |     |

|     | ple model                                                              | 222 |

| B.3 | Table of predicted vs. simulated delays. Transistor simulation. Tied   |     |

|     | model                                                                  | 225 |

### xvii

| B.4 | Table of predicted vs. | simulated delays. | Switch-level simulation. | $\operatorname{Tied}$ |   |

|-----|------------------------|-------------------|--------------------------|-----------------------|---|

|     | model                  |                   |                          | 226                   | ; |

# List of Algorithms

| 2.1 | 1 Transformations that potentially reduce the number of cycles in a co    |     |  |

|-----|---------------------------------------------------------------------------|-----|--|

|     | straint graph                                                             | 43  |  |

| 2.2 | Polynomial-complexity algorithm to find the cycle period                  | 45  |  |

| 4.1 | Algorithm to produce an equivalent set of processes with no repeated      |     |  |

|     | assignments                                                               | 86  |  |

| 5.1 | Algorithm to find the optimal solution to (5.3)                           | 112 |  |

| 7.1 | Subgradient method with space dilation along the gradient                 | 179 |  |

| 7.2 | The r-algorithm, modified to decrease the number of function evaluations. | 181 |  |

# Chapter 1

## Introduction

Fundamental to the traditional techniques used to design digital circuits is the notion of a *global clock*. The computation to be performed by the system is divided into discrete pieces, and each individual piece is performed between ticks of this clock. Such circuits are called *synchronous*.

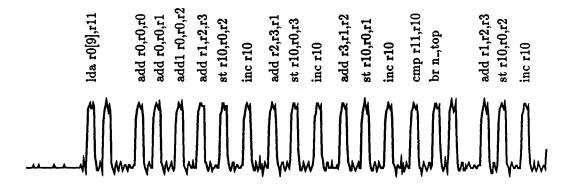

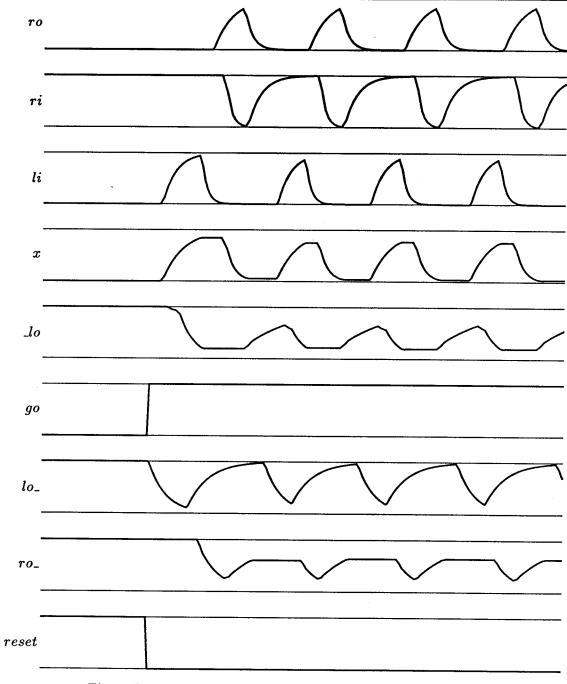

Other types of digital circuits do not use clocks. Instead of a global signal controlling the rhythmic pulsing of the computation, the mechanism that performs a single step of the computation determines when it has completed, and then triggers the next step of the computation to be performed. Figure 1.1 contains measured data from the Asynchronous Microprocessor [23], an example of such an asynchronous digital circuit.

Techniques to design these asynchronous circuits have existed for nearly as long as there have been techniques for their clock-based counterparts. However, for various reasons, the vast majority of the existing digital circuits are synchronous. Probably the most compelling reason for this wide disparity in number is the perceived difficulty of designing asynchronous circuits.

The work described in this thesis is an extension to, and relies heavily on, a

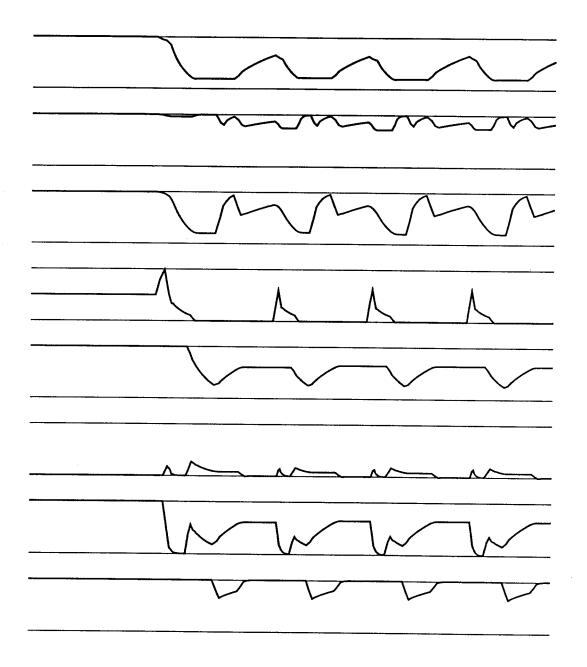

Figure 1.1: Measured data from an execution of a program that computes Fibonacci numbers on the  $2.0\mu m$  AM processor. The oscilloscope trace shown is the request-for-instruction signal generated by the processor. Notice the irregularity of this request.

particular method for synthesizing asynchronous digital circuits. To understand the thesis, it is necessary first to appreciate this synthesis method, especially the reasons why it exists and how it addresses the difficult problems associated with the design of digital circuits.

The synthesis method developed by Alain J. Martin has made the design of asynchronous circuits a simple, methodical activity. This synthesis method is based on a series of semantics-preserving transformations: Computations described in a high-level concurrent programming language are refined, through successively lower-level internal representations, until an asynchronous circuit that performs the original computation has been constructed. Low-level design activities that were once difficult and time-consuming are now automatic. The circuit designer can concentrate on the design at a high level, where most radical improvements in performance can be achieved.

The synthesis method produces circuits that contain no races or hazards; in fact, the circuits have a property known as *quasi-delay-insensitivity* [22]. Such a circuit functions correctly regardless of delays within its elements, except for some necessary assumptions about the relative delays along a few local wires. This view of delays,

except for a trivial difference in the way wires with delays are named, is equivalent to the *speed-independent* delay model [27, 7], originally introduced by David Muller in the 1950s.

These advantages include design modularity, interchangeability of subcomponents, tolerance to variation in power-supply voltages, tolerance to variation in temperatures, lower power consumption, and higher performance. The reader is referred to the literature for a more complete list of these advantages (especially [35, 8, 37, 25]). Here we will concentrate on the possible higher performance of an implementation of a computation as an asynchronous circuit rather than as a synchronous circuit. It is not always the case that an asynchronous circuit will outperform its synchronous counterpart. Which implementation is faster may depend on the relative importance of the many factors that influence the performance of the designs, and can only be determined by comparing actual asynchronous and synchronous implementations. We do not perform this type of analysis here. Instead, we provide techniques to evaluate and improve the performance of an asynchronous implementation.

The most obvious performance advantage is apparent even in the introductory definitions of synchronous and asynchronous given above. Because all steps of a computation performed by a synchronous circuit occur between clock ticks, the clock rate is determined by the slowest step, or worst-case delay. In an asynchronous circuit, the time needed to perform a particular step is determined only locally; thus, the computation proceeds at a rate that corresponds to the actual delay. However, in the asynchronous case, extra circuitry is required to perform the sequencing between two steps, and this extra delay may outweigh the potential speedup. Probably more important to the performance of a circuit are the numerous synchronizations that are necessary in complex concurrent computations. These activities might be synchronized in such a way that the rate at which the computation proceeds might again be

determined by the slowest step in the entire computation.

The traditional technique for determining the effect on performance of the many synchronizations that occur in an asynchronous circuit is (event-driven) simulation. However, simulation has two drawbacks: It is time-consuming (all concurrent events must be executed, even those that are not rate-determining), and it only determines the overall performance. Knowledge of the performance of a particular design is crucial, but it is even more important to know what is limiting the performance of the circuit. Without this information, the designer, when confronted with a variety of design decisions that affect performance, will be unable to make an informed choice. In this thesis we develop techniques that expose the effects on performance of the various interdependencies within large, highly concurrent circuits. We do this without simulating the circuit, but rather by using analytic techniques. The designer can use the results of this performance analysis, which includes not only the performance of the particular design, but also information about what is limiting its performance, to synthesize efficient asynchronous circuits.

### 1.1 Synthesis, Analysis, and Optimization

We espouse a methodology where synthesis, analysis, and optimization work in concert. The synthesis method allows the designer to transform a concurrent program into an asynchronous circuit through various intermediate representations. At any of these levels, the current refinement can be analyzed for performance. Decisions of which transformation to apply can be made at any level by comparing the performance of several competing alternatives. This technique does not necessarily find the optimal circuit, since there is some inevitable error associated with estimating performance at a high level. However, only a few of the best alternatives need be considered at the next synthesis level, thus significantly reducing the vast search space

of the synthesis problem. Instead of exploiting performance information to prune the search space, existing solutions to the synthesis problem [3, 4] seek to use the same sub-circuit template to implement each language construct.

We do not use the term optimization to refer to this searching activity, but instead reserve that term for the final adjustment of low-level parameters, in particular, the sizing of transistors. When designing a computer system, a good designer attempts to optimize some combination of the speed of the system, the size of the system, and the power consumption of the system. In a synchronous system, speed is typically constrained, i.e., the clock frequency is fixed for the entire system, and then changes are made to the system in order to reduce the area and power consumption while still maintaining this speed. This strategy makes less sense for an asynchronous circuit since there is no global clock. Instead, we constrain the area and power consumption, and optimize for speed.

In this thesis, we provide techniques to analyze the performance of an asynchronous circuit constructed using our synthesis method. At each level we can analyze a candidate implementation. The result of the analysis is in the form of a performance metric, an indication of the speed of the circuit. One possible performance metric is the time between the start and the finish of a particular computation (if the computation terminates). Other possibilities include the time between consecutive occurrences of a transition, or the time between identically-numbered occurrences of a transition in adjacent processes. These last two metrics are called the *cycle-period* and the *latency* of a system, and are particularly useful, because, for a large class of systems, they provide simple, accurate measures of a circuit's performance.

Frequently, the analysis to determine the performance metric can be performed without explicit knowledge of the delays of the components that compose the circuit. In such a case, the performance metric is expressed as a function of these individual delays.

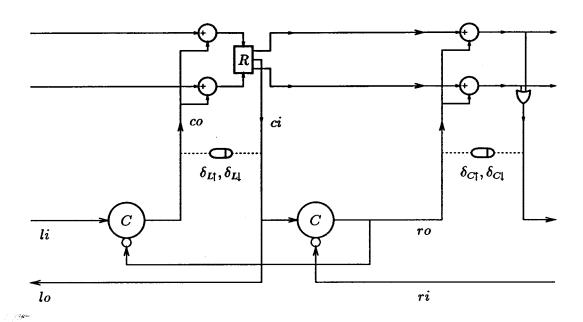

In this thesis, we also provide techniques for the low-level optimization of a performance metric. By using a simple resistance-capacitance (RC) timing model, the component delays can be approximated based on the connectivity of the components and the sizes of the transistors within components. Composing the performance metric in terms of component delays with the delay approximation of the components in terms of transistor sizes, we get an expression for the performance of the system in terms of transistor sizes. This expression is optimized, producing optimal sizes for the transistors.

#### 1.2 Contributions

The contributions made in this thesis are of three types: theory, algorithms and applications.

The theory contribution is a series of definitions, theorems, and elementary proofs that develop precise statements about the rate at which a concurrent computation proceeds. This is done in two parts: A representation of a concurrent program at one of the synthesis levels is transformed into another intermediate representation, called an *event-rule* system, that was designed especially for performance analysis. This intermediate form is then analyzed, producing a performance metric. Simplicity was a major goal in developing the intermediate representation. The transformation to event-rule systems is conceptually simple, but is actually quite involved, if it is to be performed in a mechanical manner. We describe mechanical techniques to perform this transformation for a certain class of computations.

The techniques we use to analyze the performance of an *event-rule* system are similar to techniques advocated by other researchers for other timing analysis problems. One such alternative methodology uses timed Petri nets [31] as the underlying description of the system. While both approaches are based on linear programming,

they are developed differently. Our development, we believe, is more elegant, and is easily extended to include linear arrays of identical processes. We provide new proofs, from basic principles, of the accuracy of the generated performance metrics.

The algorithms contribution includes a new technique to determine efficiently the cycle-period of an event-rule system, and a new tool to size optimally the transistors of an asynchronous circuit. A new low-order polynomial-time algorithm for determining the cycle-period of a computation is developed using the primal—dual technique for solving special-case linear programs. A non-trivial termination proof is provided. As a means to calculate efficiently the objective function, this algorithm has been incorporated into an effective tool for globally optimizing the sizes of the transistors in an asynchronous circuit. This tool implements a general algorithm for minimizing a non-linear, non-differentiable, convex function subject to any number of inequality constraints. For many circuits, a 20–30 percent improvement in performance can be achieved by using this tool.

The applications contribution consists of new analyses of the performance of several asynchronous circuits. It includes a taxonomy of the performance of various implementations of first-in, first-out (FIFO) buffer processes. A large design, the Asynchronous Microprocessor, is briefly described and analyzed. Two designs by other researchers which were thought to be optimal are analyzed and improved.

### 1.3 Thesis Overview

The synthesis and analysis procedures are logically divided as follows:

| Synthesis            | Analysis                  |

|----------------------|---------------------------|

| Concurrent Program   | Concurrent Program        |

|                      | ↓ (Chapter 4)             |

|                      | ${\it Event-Rule}$ System |

| $\psi$ (Chapter 3)   | ↓ (Chapter 2)             |

|                      | Performance Metric        |

|                      | ↓ (Chapter 7)             |

| Asynchronous Circuit | Optimal Transistor Sizes  |

The transformations between the representations are described in the annotated chapters. The synthesis method transforms a concurrent program into an asynchronous circuit. The analysis method transforms a concurrent program, described in any of the representations used during the synthesis process, into an abstract system designed explicitly for performance analysis. This event-rule system is analyzed, resulting in a metric that describes the performance of the original program. This performance metric can then be optimized as a function of transistor sizes.

The two remaining chapters describe the applicability of the synthesis and analysis procedures. Chapter 5 describes methods for analyzing the performance of large concurrent programs that have a regular structure. Chapter 6 is a collection of applications of the various analysis procedures to concrete examples.

## Chapter 2

# **Event-Rule Systems**

The analysis method that we use to determine the timing performance of an asynchronous circuit is based on an abstract notion of events, and constraints between events, called an *event-rule* or *ER* system. Most of the results are developed within this abstract framework without referring in any way to circuits. The purpose of this chapter is to develop these results. Later, in Chapter 4, we show how to transform various high-level representations of an asynchronous circuit into an *ER* system. Together, these techniques form a complete method for determining the performance of asynchronous circuits.

## 2.1 General Event-Rule Systems

A (general) event-rule system is a pair  $\langle E, R \rangle$ , where:

E is a set of events, and

R is a set of rules defining timed constraints between the events. Each  $r \in R$  is written  $e \stackrel{\alpha}{\mapsto} f$ , where

$e \in E$  is the source of r,

$f \in E$  is the target of r, and  $\alpha \in [0, +\infty)$  is the delay of r.

Neither E nor R need be finite. When R is infinite, we require that no event depends on an infinite number of other events. That is, the set of predecessors (immediate or otherwise) of an event must be finite. The set of sources of an event  $f \in E$  is denoted

$$sources(f) = \{e \mid e \stackrel{\alpha}{\mapsto} f \in R\}.$$

Similarly, the set of targets of an event  $e \in E$  is denoted

$$targets(e) = \{ f \mid e \stackrel{\alpha}{\mapsto} f \in R \}.$$

Associated with each  $\langle E, R \rangle$  is a constraint graph G, which is a directed, labeled graph (multiple arcs and self-loops allowed) that contains one node per event and one arc per rule, in which each arc is labeled with the associated delay  $\alpha$ . For a given  $\langle E, R \rangle$ , there is a set of functions T, that satisfies:

T is a subset of the functions from E to  $[0, +\infty)$ ;

$t \in T$  if and only if

$$t(f) \ge t(e) + \alpha \text{ for every } e \xrightarrow{\alpha} f \in R .$$

(2.1)

We call a function t in the set T a timing function of  $\langle E, R \rangle$ . Each t represents a possible or consistent timing specification for the events of the system. If the set T is empty, the constraints (2.1) cannot be satisfied by any such function t. In this case,  $\langle E, R \rangle$  is called *infeasible*; otherwise, it is called *feasible*.

**Example 2.1** Consider  $\langle E, R \rangle$  with

$$E = \{a, b, c\}$$

$$R = \{a \stackrel{\alpha_b}{\mapsto} b, b \stackrel{\alpha_a}{\mapsto} a, b \stackrel{\alpha_c}{\mapsto} c\}.$$

This ER system is feasible if and only if  $\alpha_a = 0$  and  $\alpha_b = 0$ .

The smallest timing function corresponds to the earliest time at which the events of E can execute. We call this smallest timing function the *timing simulation* because it represents the time values that are determined by event-driven simulation of the ER system. The timing simulation represents the most detailed performance metric for an ER system. We now show that such a function exists and is unique in the special case of an acyclic system. We then prove a preliminary lemma and show existence and uniqueness in the general case.

**Lemma 2.1** If the constraint graph G of an event-rule system  $\langle E, R \rangle$  is acyclic, then there exists a unique function  $\hat{t} \in T$  such that for every  $t \in T$ ,

$$\hat{t}(e) \le t(e) \text{ for every } e \in E.$$

(2.2)

We call  $\hat{t}$  the timing simulation of  $\langle E, R \rangle$ .

**Proof:** We propose the following recursive definition for  $\hat{t}$ :

$$\hat{t}(f) = \begin{cases} 0 & \text{if } sources(f) = \emptyset \\ \max\{\hat{t}(e) + \alpha \mid e \stackrel{\alpha}{\mapsto} f \in R\} & \text{otherwise.} \end{cases}$$

(2.3)

Such a function is well-defined because, by hypothesis, there are no cycles in G and thus no circular dependencies between the events in E. This  $\hat{t}$  is by construction a timing function and thus an element of T. We show, by contradiction, that this  $\hat{t}$

satisfies (2.2). Let t be a candidate smaller timing function such that the set F of events e that satisfy  $t(e) < \hat{t}(e)$  is non-empty. Let  $f \in F$  be such that there exists no  $e \stackrel{\alpha}{\mapsto} f \in R$  with  $e \in F$ . Thus the element f is a minimal element of F under the partial order imposed by the rule set R. Either  $sources(f) = \emptyset$  and we have  $0 \le t(f) < \hat{t}(f) = 0$ , or there exists a  $e \stackrel{\alpha}{\mapsto} f \in R$  that achieves the maximum in (2.3) and we have

$$t(f) < \hat{t}(f) = \hat{t}(e) + \alpha \le t(e) + \alpha \le t(f).$$

In both cases we have a contradiction. The inequality  $\hat{t}(e) + \alpha \leq t(e) + \alpha$  follows since  $e \notin F$ . The last inequality holds since  $t \in T$ . Therefore F must be empty, and  $\hat{t}$  satisfies (2.2).

The timing simulation  $\hat{t}$  is unique because if a smallest element of a partially ordered set (in this case, the partially ordered set of timing functions) exists, it is unique.

#### **Example 2.2** The *ER* system defined by the constraint graph:

$$egin{array}{c} e & & & & & \\ & & & & & & \\ \hline a & \stackrel{lpha_{ab}}{\longrightarrow} & b & \stackrel{lpha_{bc}}{\longrightarrow} & c \stackrel{lpha_{cd}}{\longrightarrow} & d \end{array}$$

has the timing simulation:

$$\begin{split} \hat{t}(a) &= 0 \\ \hat{t}(e) &= 0 \\ \hat{t}(b) &= \max(\alpha_{ab}, \alpha_{eb}) \\ \hat{t}(c) &= \max(\alpha_{ab}, \alpha_{eb}) + \alpha_{bc} \\ \hat{t}(d) &= \max(\alpha_{ab}, \alpha_{eb}) + \alpha_{bc} + \alpha_{cd} \; . \end{split}$$

**Lemma 2.2**  $\langle E, R \rangle$  is feasible if and only if  $\alpha = 0$  for all rules in all cycles of G.

Proof: ⇒ Let

$$c = (e_0 \stackrel{\alpha_0}{\mapsto} e_1, e_1 \stackrel{\alpha_1}{\mapsto} e_2, \dots, e_{n-2} \stackrel{\alpha_{n-2}}{\mapsto} e_{n-1}, e_{n-1} \stackrel{\alpha_{n-1}}{\mapsto} e_0)$$

be a cycle in G of length n > 0. For any  $t \in T$ ,

$$t(e_1) \geq t(e_0) + \alpha_0,$$

$$t(e_2) \geq t(e_1) + \alpha_1,$$

$$\vdots \qquad \vdots$$

$$t(e_{n-1}) \geq t(e_{n-2}) + \alpha_{n-2},$$

$$t(e_0) \geq t(e_{n-1}) + \alpha_{n-1}.$$

By summing the inequalities produced by each edge of the cycle, we get,

$$0 \geq \alpha_0 + \alpha_1 + \ldots + \alpha_{n-2} + \alpha_{n-1}$$

and, thus,  $\alpha_i = 0$  for all  $0 \le i < n$ .

$\Leftarrow$  Let SC(f) denote the set of events in the same strongly connected component of G as event f. Let  $\iota$  be an injection of E mapping each event in a strongly connected component to a unique representative. Thus  $\iota(e) = \iota(f)$  for all  $e, f \in E$  such that  $e \in SC(f)$ . Define the new event-rule system  $\langle E_a, R_a \rangle$  as

$$E_a = \{\iota(e) | e \in E\}$$

$$R_a = \{\iota(e) \stackrel{\alpha}{\mapsto} \iota(f) \mid e \stackrel{\alpha}{\mapsto} f \in R \land \iota(e) \neq \iota(f)\}$$

This system is acyclic and, thus, by Lemma 2.1, it is feasible. Let  $t_a$  be a timing function of  $\langle E_a, R_a \rangle$ . It now remains to show that  $t_a(\iota(e))$  is a timing function of  $\langle E, R \rangle$  implying that  $\langle E, R \rangle$  is feasible. By construction,  $t_a(\iota(f)) \geq t_a(\iota(e)) + \alpha$  for all rules  $e \stackrel{\alpha}{\mapsto} f \in R$  such that  $\iota(e) \neq \iota(f)$ . If  $\iota(e) = \iota(f)$ , then both e and f are in the same strongly connected component and, thus,  $e \stackrel{\alpha}{\mapsto} f$  is in a cycle. By hypothesis,  $\alpha = 0$  so

$$t_a(\iota(e)) = t_a(\iota(f)) \ge t_a(\iota(e)) + 0$$

and  $t_a(\iota(e))$  is a timing function of  $\langle E, R \rangle$ .

**Theorem 2.3** If the event-rule system  $\langle E, R \rangle$  is feasible, then there exists a unique smallest timing function  $\hat{t}$ .

**Proof:** By Lemma 2.1, we need only consider cyclic systems. Construct the corresponding acyclic system  $\langle E_a, R_a \rangle$  as shown in the proof of Lemma 2.2. Let  $\iota$  be the unique-representative function that was used to generate  $\langle E_a, R_a \rangle$ . Now, for any timing function t, it is the case that t(e) = t(f) for all e, f such that  $\iota(e) = \iota(f)$ . This follows because if e and f are in the same strongly connected component, then there is a cycle with only zero-delay arcs that contains both e and f.

Let  $\hat{t}_a$  be the timing simulation of  $\langle E_a, R_a \rangle$ . We now propose  $\hat{t}(e) = \hat{t}_a(\iota(e))$  for all  $e \in E$  as the smallest timing function of  $\langle E, R \rangle$ . For proof, suppose that t is a timing function with  $t(\iota(e)) = t(e) < \hat{t}(e) = \hat{t}_a(\iota(e))$  for some  $e \in E$ . But then, t restricted to the domain  $E_a$  is also a timing function of  $\langle E_a, R_a \rangle$ , contradicting the minimality of  $\hat{t}_a$ . Corresponding to the particular rule  $e' \stackrel{\alpha}{\mapsto} f' \in R_a$  is the rule  $e \stackrel{\alpha}{\mapsto} f \in R$  with  $e' = \iota(e)$  and  $f' = \iota(f)$ . Thus,

$$t(f') = t(\iota(f)) = t(f) \ge t(e) + \alpha = t(\iota(e)) + \alpha = t(e') + \alpha$$

and t restricted to  $E_a$  is a timing function of  $\langle E_a, R_a \rangle$ .

The proof of this theorem provides a means to transform any cyclic ER system into an acyclic system, without altering the timing simulations. For the remainder of the thesis, unless explicitly stated, we assume that an ER system is acyclic.

### 2.2 Repetitive Systems

Many ER systems of unbounded size can be generated from bounded structures. Consider the event set E generated from a finite set E' by

$$E = E' \times \mathbb{N} .$$

The elements of E' are called *transitions*. An event  $\langle u,i\rangle\in E$  is the indexed occurrence of the transition  $u\in E'$ . The nonnegative integer i is called the occurrence index.

The rule set R is also generated from a finite set R'. The elements of R' are quadruples

$$r' = \langle u, v, \alpha, \varepsilon \rangle \in R'$$

, where  $R' \subseteq E' \times E' \times [0, +\infty) \times \mathbb{Z}$ ,

which we will write as

$$r' = \langle u, i - \varepsilon \rangle \stackrel{\alpha}{\mapsto} \langle v, i \rangle.$$

The integer  $\varepsilon$  is called the *occurrence-index offset* of r'. The dummy variable i is replaced by a nonnegative integer no less than  $\varepsilon$  when r' is instantiated (an infinite number of times) to form the generated rule set R. We require  $i \geq \max(0, \varepsilon)$  so that the occurrence indices of both the source and the target events of r are both nonnegative and thus in E. We call  $\langle E, R \rangle$  the (general) ER system generated from the repetitive ER system  $\langle E', R' \rangle$ .

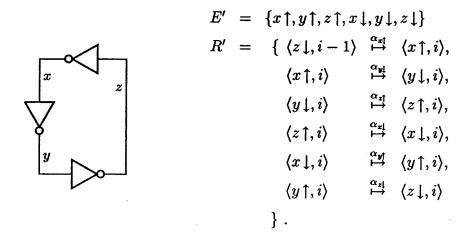

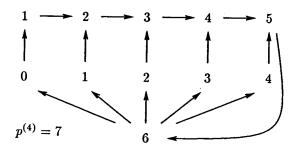

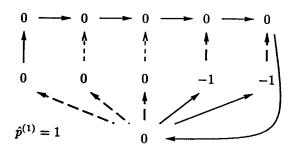

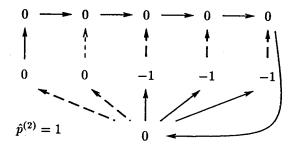

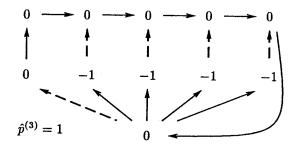

#### Example 2.3 Ring Oscillator

#### Consider the repetitive ER system

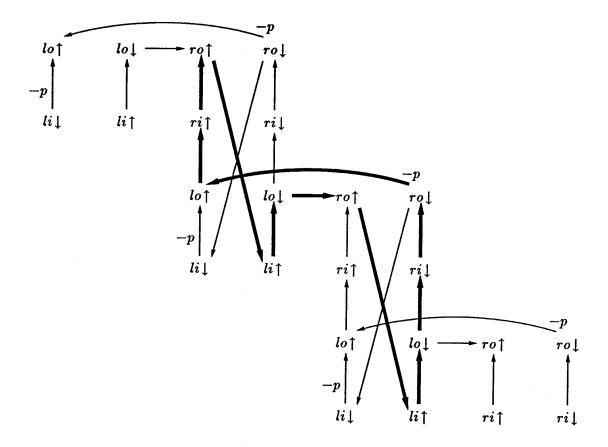

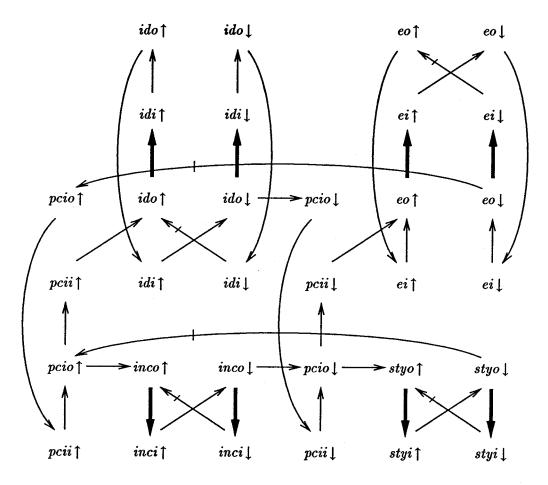

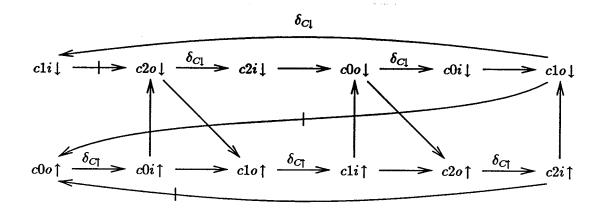

Initially, x and z are false and y is true. The events of the system, those generated from E', represent transitions of circuit variables. Event  $\langle x \uparrow, i \rangle$  represents the  $i^{th}$  occurrence of a transition from x = false to x = true. Similarly,  $\langle x \downarrow, i \rangle$  represents the  $i^{th}$  occurrence of a transition from x = true to x = false. The repeated rules correspond to dependencies introduced by the inverters connecting the circuit variables x and y, y and z, and z and x. We can represent the generated infinite sets E and E graphically.

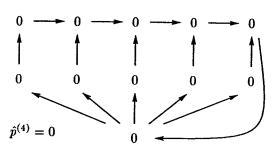

In this diagram, nodes represent elements of E and arcs represent elements of R. Notice that event  $\langle x \uparrow, 0 \rangle$  has no predecessors. In a timing simulation  $\hat{t}(\langle x \uparrow, 0 \rangle)$  is set to 0. The entire timing simulation  $\hat{t}$  can be constructed by inspection. (For ease of notation, we write one-parameter functions of an instantiated repeated event as two-parameter functions of the event and its occurrence index. For example,  $\hat{t}(\langle x \uparrow, 0 \rangle)$  will be written  $\hat{t}(x \uparrow, 0)$ .)

$$\hat{t}(x\uparrow,i) = pi$$

$$\hat{t}(y\downarrow,i) = \alpha_{y\downarrow} + pi$$

$$\hat{t}(z\uparrow,i) = \alpha_{y\downarrow} + \alpha_{z\uparrow} + pi$$

$$\hat{t}(x\downarrow,i) = \alpha_{y\downarrow} + \alpha_{z\uparrow} + \alpha_{x\downarrow} + pi$$

$$\hat{t}(y\uparrow,i) = \alpha_{y\downarrow} + \alpha_{z\uparrow} + \alpha_{x\downarrow} + \alpha_{y\uparrow} + pi$$

$$\hat{t}(z\downarrow,i) = \alpha_{y\downarrow} + \alpha_{z\uparrow} + \alpha_{x\downarrow} + \alpha_{y\uparrow} + \alpha_{z\downarrow} + pi$$

where

$$p = \alpha_{y\downarrow} + \alpha_{z\uparrow} + \alpha_{x\downarrow} + \alpha_{y\uparrow} + \alpha_{z\downarrow} + \alpha_{x\uparrow}$$

.

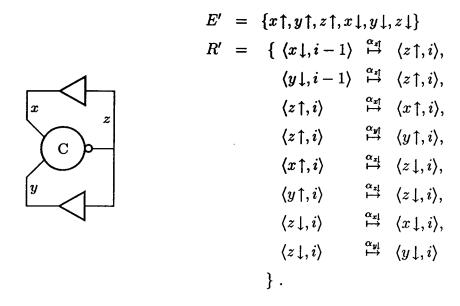

#### Example 2.4 C-element

Consider the repetitive ER system constructed from a circuit containing an inverting

Muller C-element and two noninverting drivers.

Initially x, y and z are false. We can represent the infinite sets E and R graphically as

In this case, the event  $\langle z \uparrow, 0 \rangle$  has no predecessors, and, thus  $\hat{t}(z \uparrow, 0)$  is 0. The entire timing simulation  $\hat{t}$ , constructed by inspection from the constraint graph, is:

$$\begin{array}{lcl} \hat{t}(z\uparrow,i) & = & p\,i \\ \\ \hat{t}(x\uparrow,i) & = & \alpha_{x\uparrow} + p\,i \\ \\ \hat{t}(y\uparrow,i) & = & \alpha_{y\uparrow} + p\,i \\ \\ \hat{t}(z\downarrow,i) & = & \max(\alpha_{x\uparrow},\alpha_{y\uparrow}) + \alpha_{z\downarrow} + p\,i \end{array}$$

$$\hat{t}(x\downarrow,i) = \max(\alpha_{x\uparrow},\alpha_{y\uparrow}) + \alpha_{z\downarrow} + \alpha_{x\downarrow} + pi$$

$$\hat{t}(y\downarrow,i) = \max(\alpha_{x\uparrow},\alpha_{y\uparrow}) + \alpha_{z\downarrow} + \alpha_{y\downarrow} + pi$$

where

$$p = \max(\alpha_{x\uparrow}, \alpha_{y\uparrow}) + \alpha_{z\downarrow} + \max(\alpha_{x\downarrow}, \alpha_{y\downarrow}) + \alpha_{z\uparrow}$$

.

### 2.2.1 Linear Timing Functions

In the previous examples, we saw that the timing simulations of two repetitive ER systems took on a simple form that is linear in the occurrence index i. This is not the case for all repetitive ER systems. However, as we later show (Theorems 2.9 and 2.10), a linear timing function exists whenever the timing simulation exists, and the "best" such function is a very good approximation of the timing simulation.

We call  $\bar{t} \in T$  a linear timing function (of  $\langle E', R' \rangle$ ), if

$$\bar{t}(v,i) = x_v + p_v i \text{ for every } v \in E' \text{ and } i \in \mathbb{N} .$$

(2.4)

Each  $x_v$  and  $p_v$  is independent of *i*. For each  $v \in E'$ ,  $x_v$  and  $p_v$  are called, respectively, the *offset* and *cycle period* of the transition v.

Because of the linear form of  $\bar{t}$ , the timing function constraints (2.1) reduce to linear inequalities in the offsets and cycle periods of the system. All dependence on the occurrence index i can be eliminated. For each rule  $r = \langle u, i - \varepsilon \rangle \stackrel{\alpha}{\mapsto} \langle v, i \rangle \in R'$ , we have the infinite set of constraints

$$\bar{t}(v,i) \geq \bar{t}(u,i-\varepsilon) + \alpha$$

, for each  $i \geq \max(0,\varepsilon)$ .

Replacing  $\bar{t}$  by its definition, we get

$$x_v + p_v i \ge x_u + p_u (i - \varepsilon) + \alpha$$

(2.5)

$$x_v \geq x_u - p_u \varepsilon + \alpha + (p_u - p_v)i. \qquad (2.6)$$

If  $p_u > p_v$  then equation (2.6) can never be satisfied for all i, since i can be arbitrarily large. Thus, the infinite set of constraints generated by r can be replaced by the two inequalities,

$$x_v \geq x_u - p_u \varepsilon + \alpha + (p_u - p_v) \max(0, \varepsilon)$$

, and (2.7)

$$p_v \geq p_u. \tag{2.8}$$

### 2.2.2 Strongly Connected Systems

The collapsed-constraint graph G' of  $\langle E', R' \rangle$  is the directed graph with nodes from E' and arcs from R'. From (2.8) we see that for a linear timing function to exist, a partial ordering between the  $p_v$ 's must be satisfied. If two nodes, u and v, are in the same cycle of the collapsed-constraint graph G', then  $p_u$  must equal  $p_v$ . Thus, all transitions in the same strongly-connected component of G' have the same cycle period. In the following, unless stated otherwise, G' is assumed to be strongly connected, and we use p to denote the cycle period of every element in E'. Thus (2.7) reduces to

$$x_v \geq x_u + \alpha - \varepsilon p. \tag{2.9}$$

Analogously to the constraint graphs of general ER systems, the arcs of the collapsed-constraint graph are labeled so as to specify the timing constraints. Instead of just  $\alpha$ , in this case the label is  $\alpha - \varepsilon p$ .

**Example 2.5** Consider the repetitive ER system of Example 2.3. The labeled collapsed-constraint graph G' is:

$$\begin{array}{cccc} x \uparrow & \xrightarrow{\alpha_{yl}} & y \downarrow & \xrightarrow{\alpha_{z\uparrow}} & z \uparrow \\ & & & & \downarrow \\ \alpha_{z\uparrow} - p \uparrow & & & \downarrow \\ z \downarrow & \xrightarrow{\alpha_{z\downarrow}} & y \uparrow & \xrightarrow{\alpha_{y\uparrow}} & x \downarrow \end{array}$$

Notice the use of  $\alpha_{x\uparrow} - p$  as the label on the arc from  $z \downarrow$  to  $x \uparrow$ . This arc corresponds to the rule

$$\langle z \downarrow, i-1 \rangle \stackrel{\alpha_{x\uparrow}}{\mapsto} \langle x \uparrow, i \rangle$$

which imposes the constraint inequality

$$x_{x\dagger} \geq x_{z\downarrow} + \alpha_{x\uparrow} - p$$

.

### 2.2.3 The Cycle Period As a Performance Metric

A cycle period p found in a linear timing function  $\bar{t}$  is an upper-bound on the asymptotic performance of a repetitive ER system. The time at which occurrence i of a particular transition u fires in an actual execution of the system is  $\hat{t}(u)$ , where  $\hat{t}$  is the timing simulation. Since  $\bar{t}(u,i) \geq \hat{t}(u,i)$  (because  $\hat{t}$  is the smallest timing function), it must be the case that for all i > 0,

$$p \geq \frac{\hat{t}(u,i)}{i} - \frac{x_u}{i}$$

Thus for any u and large enough i, p is not less than a number arbitrarily close to the average time between consecutive occurrences of u. In Sections 2.4 and 2.4.3, we

show that the minimum p is not only not less than, but is actually equal to a number arbitrarily close to the average time between consecutive occurrences of u. Thus, p is a good, single-valued performance metric for the system.

### 2.3 Pseudorepetitive Systems

While repetitive ER systems are simple and easy to analyze, a broader class of systems can be analyzed with a slightly more complex model. In such a model, events are of two types, either initial or repeated. There are only finitely many initial events, and thus after a finite period, only the repeated events occur.

#### 2.3.1 Definitions

Pseudorepetitive ER systems consist of a finite set of initial events, an infinite set of repeated events, a finite set of initial transitions, a finite set of repeated transitions, a finite set of initial rules, and a finite set of repeated rules. In this order, a pseudorepetitive ER system is a six-tuple  $\langle E_0, E_1, E'_0, E'_1, R_0, R'_1 \rangle$ . As in the case of repetitive systems, a pseudorepetitive system generates a general ER system. The corresponding system  $\langle E, R \rangle$  consists of the event set

$$E = E_0 \cup E_1 ,$$

where  $E_0$  is a subset of  $E_0' \times \mathbb{N}$  and  $E_1$  is a subset of  $E_1' \times \mathbb{N}$ .

The elements of the initial rule set  $R_0$  are of the same form as the rules in a general ER system. The source of an initial rule must be an initial event. The elements of the repeated rule set  $R'_1$  are of the same form as the rules in a repetitive ER system. Both the source and the target transitions of a repeated rule must be a repeated transition. Furthermore, the elements of  $R'_1$  are only instantiated for those occurrence indices such that both the source and target events are members of  $E_1$ , the set of repeated events.

**Example 2.6** Consider the pseudorepetitive *ER* system:

$$E'_{0} = \{a,b,c\}$$

$$E'_{1} = \{a,b,c\}$$

$$E_{0} = \{\langle a,0\rangle, \langle b,0\rangle, \langle b,1\rangle, \langle c,0\rangle\}$$

$$E_{1} = \{\langle a,i\rangle \mid i > 0\} \cup \{\langle b,i\rangle \mid i > 1\} \cup \{\langle c,i\rangle \mid i > 0\}$$

$$R_{0} = \{\langle b,0\rangle \stackrel{\alpha_{bc}}{\mapsto} \langle a,0\rangle, \langle a,0\rangle \stackrel{\alpha_{ac}}{\mapsto} \langle c,0\rangle, \langle c,0\rangle \stackrel{\alpha_{cb}}{\mapsto} \langle b,1\rangle, \langle b,1\rangle \stackrel{\alpha_{bd}}{\mapsto} \langle a,1\rangle$$

$$\}$$

$$R'_{1} = \{\langle a,i-1\rangle \stackrel{\alpha_{ab}}{\mapsto} \langle b,i\rangle, \langle c,i-1\rangle \stackrel{\alpha_{cc}}{\mapsto} \langle c,i\rangle, \langle c,i-1\rangle \stackrel{\alpha_{cc}}{\mapsto} \langle a,i\rangle$$

$$\}.$$

The generated general system is the pair  $\langle E, R \rangle$ , where

$$E = E_0 \cup E_1$$

$$R = R_0 \cup \{\langle a, i-1 \rangle \xrightarrow{\alpha_{ab}} \langle b, i \rangle \mid i > 1\}$$

$$\cup \{\langle b, i+1 \rangle \xrightarrow{\alpha_{bc}} \langle c, i \rangle \mid i > 0\}$$

$$\cup \{\langle c, i-1 \rangle \xrightarrow{\alpha_{cd}} \langle a, i \rangle \mid i > 1\}.$$

#### 2.3.2 Approximating the Timing Simulation

While pseudorepetitive systems are more general than repetitive systems, we show now that we can approximate the steady-state timing behavior of a pseudorepetitive system by the timing simulation of a simpler repetitive system.

Theorem 2.4 Let  $P = \langle E_0, E_1, E'_0, E'_1, R_0, R'_1 \rangle$  be a pseudorepetitive ER system. Let S be the general (possibly cyclic) ER system generated from P, and let S' be the general (possibly cyclic) ER system generated from just the repetitive part of P, that is the repetitive ER system  $\langle E'_1, R'_1 \rangle$ . If S is feasible, then S' is feasible, and the timing simulation of S differs by no more than a constant from the timing simulation of S'.

**Proof:** We first show that S' is feasible. Assume S' is not feasible. Then by Lemma 2.2, there exists a cycle of non-zero cost. Let

$$\begin{array}{cccc} \langle u_0,i_0\rangle & \stackrel{\alpha_1}{\mapsto} & \langle u_1,i_1\rangle \\ \\ \langle u_1,i_1\rangle & \stackrel{\alpha_2}{\mapsto} & \langle u_2,i_2\rangle \\ \\ & \vdots \\ \\ \langle u_{\ell-1},i_{\ell-1}\rangle & \stackrel{\alpha_0}{\mapsto} & \langle u_0,i_0\rangle \end{array}$$

be the edges of such a cycle with at least one  $\alpha_j > 0$ . Since S' is repetitive, we can add an arbitrary n to each  $i_j$  in the above rules. For large enough n, each  $\langle u_j, i_j + n \rangle$  is a member of  $E_1$ , the repeated events of the pseudorepetitive system. Thus, there exists a cycle of non-zero cost in the general ER system generated from S. By Lemma 2.2, S is not feasible, contradicting the hypothesis.

We go on to prove the approximation part of the theorem. We start by transforming both S and S' into acyclic ER systems with the technique used in Lemma 2.2. To

avoid cluttered notation, we denote the new acyclic systems with the same names, S and S'. This transformation allows the simpler definition of the timing simulation (2.3) to be used. Consider the timing simulations  $\hat{t}$  of S and  $\hat{t'}$  of S' restricted to the events  $\langle v, i \rangle \in E_1$ , such that  $\langle v, i \rangle$  is the target of a rule with a source in  $E_1$  and not a target of a rule with a source in  $E_0$ . All but a finite number of events are of this type. Since S and S' are both feasible, each excluded event that exist in both S and S' has a finite  $\hat{t}$  and  $\hat{t'}$ , and thus there exists a finite B such that

$$|\hat{t}(v,i) - \hat{t}'(v,i)| \leq B$$

for all excluded  $\langle v,i \rangle$  with  $v \in E'_1$ .

We show that the two timing simulations can differ by no more on a target event than they do on a source event. By the definition of a timing simulation on the restricted set of events, we have

$$\hat{t}(v,i) = \max\{\hat{t}(u,i-\varepsilon) + \alpha \mid \langle u,v,\alpha,\varepsilon \rangle \in R_1'\}$$

$$\hat{t}'(v,i) = \max\{\hat{t}'(u,i-\varepsilon) + \alpha \mid \langle u,v,\alpha,\varepsilon \rangle \in R_1'\}$$

Notice that for each target event the same rules apply for the two timing simulations. We must show that

$$|\hat{t}(v,i) - \hat{t}'(v,i)| \leq \max\{|\hat{t}(u,i-\varepsilon) - \hat{t}'(u,i-\varepsilon)| \mid \langle u,v,\alpha,\varepsilon \rangle \in R_1'\}.$$

Let  $r = \langle u, v, \alpha, \varepsilon \rangle$  be the rule such that  $\hat{t}(v, i) = \hat{t}(u, i - \varepsilon) + \alpha$  and let  $r' = \langle u', v, \alpha', \varepsilon' \rangle$  be the rule such that  $\hat{t}'(v, i) = \hat{t}'(u', i - \varepsilon') + \alpha'$ . If  $\hat{t}(v, i) \geq \hat{t}'(v, i)$ , then

$$\begin{split} \hat{t}(v,i) - \hat{t}'(v,i) &= \hat{t}(u,i-\varepsilon) + \alpha - \hat{t}'(u',i-\varepsilon') - \alpha' \\ &\leq \hat{t}(u,i-\varepsilon) + \alpha - \hat{t}'(u,i-\varepsilon) - \alpha \end{split}$$

$$= \hat{t}(u,i-\varepsilon) - \hat{t}'(u,i-\varepsilon) .$$

The inequality above follows since, by construction,

$$\hat{t}'(u', i - \varepsilon') + \alpha' \geq \hat{t}'(u, i - \varepsilon) + \alpha$$

.

Similarly, if  $\hat{t'}(v, i) \ge \hat{t}(v, i)$ , then

$$\hat{t}'(v,i) - \hat{t}(v,i) \leq \hat{t}'(u',i-\varepsilon') - \hat{t}(u',i-\varepsilon') .$$

Since the absolute difference between  $\hat{t}'(v,i)$  and  $\hat{t}(v,i)$  is no larger for each subsequent event,

$$|\hat{t}'(v,i) - \hat{t}(v,i)| \le B \text{ for all } \langle v,i \rangle \in E_1' \times \mathbb{N} . \quad \blacksquare$$

# 2.4 Minimum-Period Linear Timing Functions

Among the possible linear timing functions, there are those that minimize the cycle period p. The techniques of *linear programming* [13, 29] can be used to find such a minimum-period linear timing function (MPLTF). To fit our needs, we will use linear programs in *standard* form:

$$Ax \ge b, x \ge 0, z = \min c^T x , \qquad (2.10)$$

where A is an m-by-n matrix and x, b and c are column vectors of lengths n, m and n, respectively. The program has a feasible solution x when both vector constraints can be satisfied. The program has an optimal solution x when x is feasible and when for all other feasible x',  $c^Tx \leq c^Tx'$ .

A fundamental result from linear programming relates the primal program (2.10) to the dual program

$$y^T A \le c^T, y \ge 0, w = \max y^T b$$

(2.11)

Theorem 2.5 (Duality Theorem) Exactly one the these four cases occurs:

- 1. Both the primal and the dual have optimal solutions, and z = w.

- 2. The primal has no feasible solution, but the dual has feasible solutions y with  $y^Tb = +\infty$ .

- 3. The dual has no feasible solution, but the primal has feasible solutions x with  $c^T x = -\infty$ .

- 4. Neither the primal nor the dual has a feasible solution.

**Proof:** See [13]. ■

The constraints of a linear timing function (2.9) are simple linear inequalities in the offsets  $x_v$  and cycle period p. By ordering the sets E' and R' of a repetitive ER system, we can construct a linear program in matrix form.

$$\min\left(\begin{array}{cc} c_0^T & c_1^T \end{array}\right) \left(\begin{array}{c} x \\ p \end{array}\right) = z \tag{2.12}$$

$$\left(\begin{array}{cc} A' & \varepsilon \end{array}\right) \left(\begin{array}{c} x \\ p \end{array}\right) \geq \alpha \tag{2.13}$$

$$x, p \geq 0 \tag{2.14}$$

We will discuss the coefficients of the objective function,  $c_0$  and  $c_1$ , later. The elements of the vector x correspond to the offsets (from the linear timing function) of the transitions that make up the set E'. The matrix A' is the arc-node incidence matrix of the collapsed-constraint graph G'. If row j of A' represents the constraint  $r_j \in R'$  and column k of A' represents the transition  $u_k \in E'$ , then

$$a'_{jk} = \begin{cases} -1 & \text{if } u_k \text{ is the source transition of } r_j \\ 1 & \text{if } u_k \text{ is the target transition of } r_j \\ 0 & \text{otherwise} \end{cases}$$

(2.15)

The  $j^{\text{th}}$  elements of the column vectors  $\varepsilon$  and  $\alpha$  are the occurrence-index offset and the delay of the constraint  $r_j$ , respectively.

The dual of (2.13) is

$$\max y^T \alpha = w \tag{2.16}$$

$$y^{T} \left( A' \quad \varepsilon \right) \leq \left( c_{0}^{T} \quad c_{1}^{T} \right) \tag{2.17}$$

$$y \geq 0 . (2.18)$$

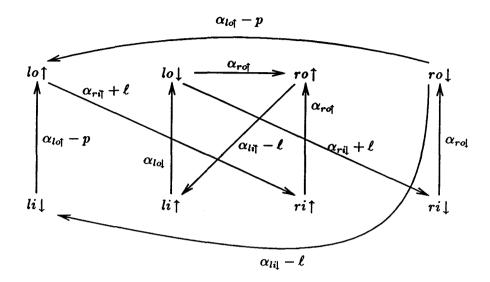

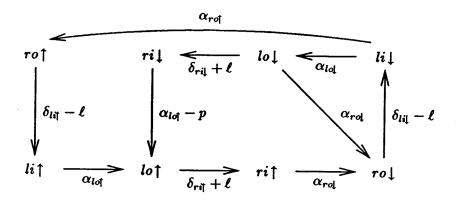

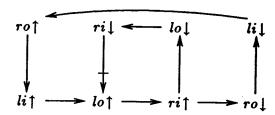

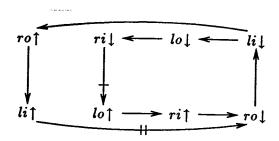

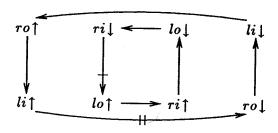

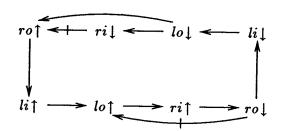

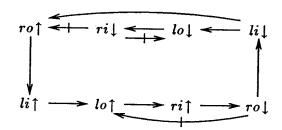

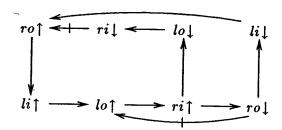

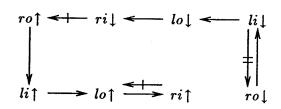

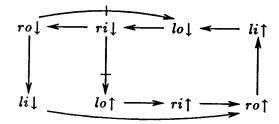

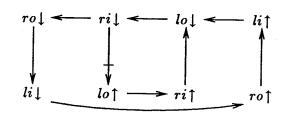

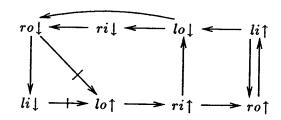

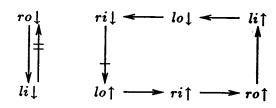

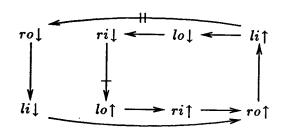

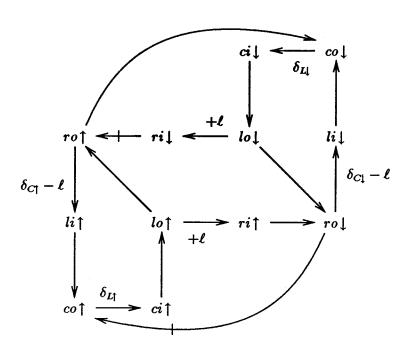

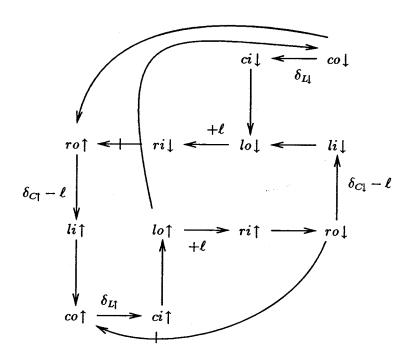

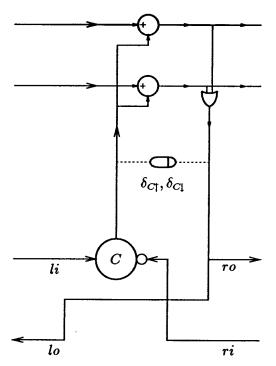

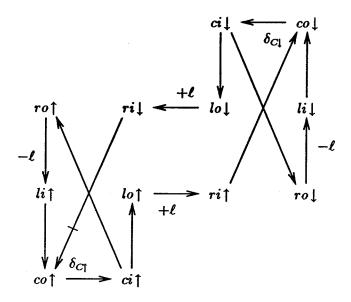

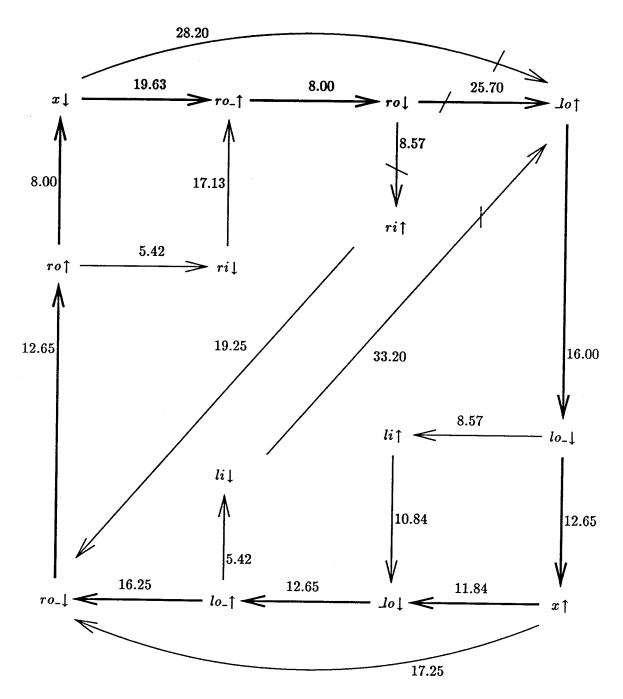

Example 2.7 Lazy-Active/Passive Buffer

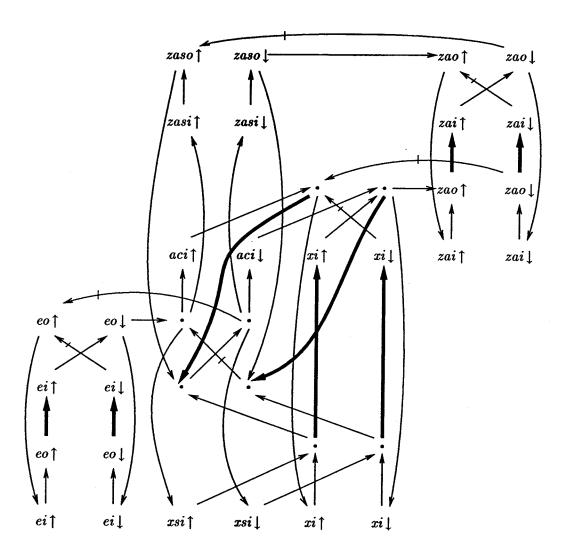

Consider the repetitive ER system

$$E' = \{lo\uparrow, li\uparrow, ro\uparrow, ri\uparrow, lo\downarrow, li\downarrow, ro\downarrow, ri\downarrow\}$$

$$R' = \{\langle li\downarrow, i-1 \rangle \xrightarrow{\alpha_{lof}} \langle lo\uparrow, i \rangle, \langle ro\downarrow, i-1 \rangle \xrightarrow{\alpha_{lof}} \langle lo\uparrow, i \rangle, \langle li\uparrow, i \rangle \xrightarrow{\alpha_{lof}} \langle lo\downarrow, i \rangle, \langle li\uparrow, i \rangle \xrightarrow{\alpha_{rof}} \langle ro\uparrow, i \rangle, \langle ri\uparrow, i \rangle \xrightarrow{\alpha_{rof}} \langle ro\uparrow, i \rangle, \langle ri\downarrow, i \rangle \xrightarrow{\alpha_{rof}} \langle ro\downarrow, i \rangle, \langle lo\uparrow, i \rangle \xrightarrow{\alpha_{rof}} \langle li\uparrow, i \rangle, \langle lo\downarrow, i \rangle \xrightarrow{\alpha_{lof}} \langle li\uparrow, i \rangle, \langle ro\downarrow, i \rangle \xrightarrow{\alpha_{rof}} \langle ri\uparrow, i \rangle, \langle ro\uparrow, i \rangle \xrightarrow{\alpha_{rof}} \langle ri\uparrow, i \rangle, \langle ro\uparrow, i \rangle \xrightarrow{\alpha_{rof}} \langle ri\uparrow, i \rangle, \langle ro\uparrow, i \rangle \xrightarrow{\alpha_{rof}} \langle ri\downarrow, i \rangle$$

$$\}.$$

The corresponding primal program is:

#### **Objective Function** 2.4.1

So far we have left the objective coefficients,  $c_0$  and  $c_1$ , unspecified. Our goal is to find the minimum cycle time, so one choice for the objective function, in the case of a connected system, is min  $z = 0^T x + 1p$ . Thus, for a connected repetitive ER system we have the simplified linear program:

$$z = \min p \tag{2.19}$$

$$A'x + \varepsilon p \geq \alpha \tag{2.20}$$

$$x, p \geq 0 , \qquad (2.21)$$

and corresponding dual

$$w = \max y^T \alpha \tag{2.22}$$

$$y^T A' \leq 0 \tag{2.23}$$

$$y^T \varepsilon \leq 1 \tag{2.24}$$

$$y \geq 0 . (2.25)$$

The above linear program can be further simplified since A' is an incidence matrix. For each row, there is exactly one column with entry -1 and exactly one column with entry 1. Thus A' 1 = 0. In order to satisfy (2.23), we claim that  $y^T A' = 0$ . This follows since  $0 = y^T (A' 1) = (y^T A') 1$  and each element of  $y^T A'$  is non-positive. The dual then becomes

simplifying the primal to

$$z = \min p$$

$$A'x + \varepsilon p \ge \alpha$$

$$x \quad \text{is unconstrained}$$

$$p \ge 0$$

$$(2.27)$$

While the linear programming formulation shows that x need not be constrained in order to find the minimum period, each element of x must be non-negative if it is to be used as an offset in a linear timing function. To form an offset vector, after an optimal solution x,p is found, we subtract from each element of x the smallest

element of x.

### 2.4.2 Cycle Vectors of a Graph

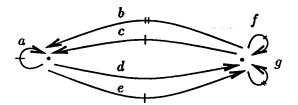

A cycle c of length  $\ell$  in a directed (multi-)graph  $G = \langle \mathcal{N}, \mathcal{A} \rangle$  is an ordered subset  $(a_0, a_1, \ldots, a_{\ell-1})$  of the arcs  $\mathcal{A}$  such that  $target(a_{k-1}) = source(a_k)$  for all  $0 < k < \ell$  and  $target(a_{\ell-1}) = source(a_0)$ . The cycle c can be represented by a cycle vector u, a  $\{0,1\}$ -vector of length  $|\mathcal{A}|$  where  $u_j = 1$  if and only if the  $j^{th}$  arc of  $\mathcal{A}$  is in the set c. For each cycle vector u,  $u^T A' = 0$ , where A' is the arc-node incidence matrix of the graph G. An interesting fact is that any  $y \geq 0$  which satisfies  $y^T A' = 0$  can be formed by the non-negative linear combination of the cycle vectors of G.

**Lemma 2.6** If  $y \ge 0$  is such that  $y^T A' = 0$ , then there exists  $\theta_i \ge 0$  and cycle vectors  $U_i$  such that

$$y = \theta_0 U_0 + \theta_1 U_1 + \ldots + \theta_{q-1} U_{q-1} . \tag{2.28}$$

**Proof:** By induction on the number of cycles in the graph  $G = \langle \mathcal{N}, \mathcal{A} \rangle$ .

Base Case: G is acyclic. By Lemma 2.7 (following), y must be identically zero.

General Case: If G is cyclic, let  $\mathcal{A}' = \{r_j \in \mathcal{A} \mid y_j > 0\}$ . Form the graph  $G' = \langle \mathcal{N}, \mathcal{A}' \rangle$ . Any cycle in the graph G' is also a cycle in G since arcs are removed, but never added, to form G'. If G' has no arcs, then by definition of  $\mathcal{A}'$ , y must be identically zero. Otherwise, a scalar multiple of any cycle vector of G' can be subtracted from y, resulting in a  $y^*$  with more zero elements than y; that is for any cycle c of G' with corresponding cycle vector u,

$$y^* = y - \theta u$$

where  $\theta = \min\{y_j \mid r_j \in c\} > 0$ . Now let  $\mathcal{A}'' = \{r_j \in \mathcal{A} | y_j^* > 0\}$ . Also form the vector y'' of length  $|\mathcal{A}''|$  from  $y^*$  by removing the zero elements. The

graph  $G'' = \langle \mathcal{N}, \mathcal{A}'' \rangle$  has strictly fewer cycles than G' (and G) since the cycle corresponding to u cannot be a member of G''. By the induction hypothesis applied to G'' and y'', we get

$$y'' = \sum_{k=0}^{q''-1} \theta_k'' U_k''$$

where each  $\theta_k'' \geq 0$  and each  $U_k''$  is a cycle vector of G''. Now each  $U_k''$  can be expanded to a vector  $U_k$  of length  $\mathcal{A}$  by filling in zeroes for the removed arcs. Similarly, u can be expanded to U. Thus,

$$y = \theta U + \sum_{k=0}^{q''-1} \theta_k'' U_k$$

which is the required form for y.

**Lemma 2.7** Let G be an acyclic graph with non-empty arc set. If  $y \ge 0 \land y^T A' = 0$  then y = 0.

**Proof:** By induction on the number of arcs.

Base case: If G consists of a single arc, then the single row of A' contains two non-zero entries, one -1 and one 1. For  $y^TA' = 0$ , y = 0.

General case: If G has more than one arc, pick a single arc  $r_j$  with source e such that  $targets(e) = \emptyset$ . Now  $y_j$  must be 0. By the induction hypothesis applied to the graph formed from G by removing  $r_j$  from the arc set, the rest of y is identically 0.

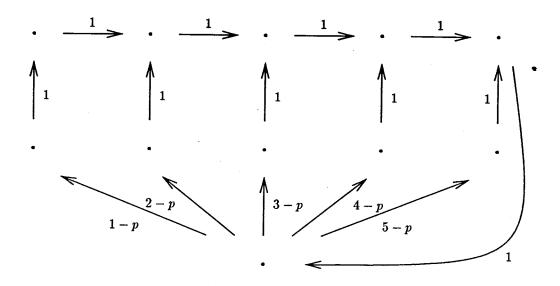

These lemmas provide a straightforward means of determining the minimum cycle period p. By enumerating every cycle in the collapsed constraint graph of a repetitive ER system, and by computing the sum of the delays and the sum of the occurrence-index offsets around each cycle, we can find the minimum cycle period p.

**Theorem 2.8** The minimum cycle period p, that is the optimal value z of the primal program (2.27) is