## Interval Modulation: A New Paradigm for the Design of High Speed Communication Systems

Thesis by

Saleem Mukhtar

In Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

California Institute of Technology Pasadena, California

2004

(Submitted July 7, 2004)

© 2004 Saleem Mukhtar All Rights Reserved

## Acknowledgements

I am deeply indebted to many people who made by Caltech years enlightening, rewarding and a memorable experience. First and foremost, I must extend by gratitude to Prof. Ali Hajimiri, Prof. Jehoshua Bruck and Prof. Paul Sternberg for granting me the honor of being members of their research group. I have benefited vastly from their technical expertise and insights and their high standards in research, teaching and publication. The financial support received from them, as well as the Department of Defense is greatly appreciated.

Second, I must thank my colleagues, former and current members of the Paradise and Chic Lab for years of friendship. These include Mike Gibson, Matthew Cook, Suleyman Gokyigit, Marc Reidel, Kevin Foltz, Massimo Franceschetti, Anxiao (Andrew) Jiang, Yuval Cassuto, Hossein Hashemi, Roberto Aparicio, Xiang Guan, Chris White, Behnam Analui, Ehsan Afshari, Arun Natarajan, Jim Buckwalter, Abbas Komijani, Sam Mandegaran and Aydin Babakhani. Special thanks must be extended to Behnam Analui and Xiaofeng Li who taught me how to design a chip, use the design tools and taught me how to use the measurement equipment. Also I must thank Anne Shen and Niklas Wadefalk for help with soldering and wirebonding. I must also thank my CNS classmates for six wonderful years here at Caltech and one fun trip to Israel. These include Daniella Meeker, Ania Mitros, Adam Hayes, Ofer Mazor, Bjorn Christianson, Javier Perez-Orive and Jason Davis. Also I must thank my closest friends Kashif Alvi, Pururav Thoutireddy and Arella Karspeck for some extraordinary times.

Most of all I must thank my family – my parents, Parveen and Khalid, my younger brother Salman, my Aunt Farzana and my Uncle Tariq, my cousins Farzana and Nafees, Shabana and Mansoor and my nieces, Zoya and Zenab for their love, support and encouragement. They always inspired me to follow the path of my heart as opposed to the path of convenience. I am specially indebted to my parents for the extraordinary sacrifices they made to make not only my education at Caltech, but also my undergraduate education at Carnegie Mellon University possible. I am extremely grateful to them for their love, support and encouragement. This dissertation is dedicated to them as a token of my gratitude.

## Contents

| A              | Acknowledgements |                                                                     |    |  |  |

|----------------|------------------|---------------------------------------------------------------------|----|--|--|

| A              | bstra            | act                                                                 | x  |  |  |

| 1 Introduction |                  |                                                                     |    |  |  |

| 2              | Mo               | dulation Formats                                                    | 8  |  |  |

|                | 2.1              | Analog Modulation Formats                                           | 8  |  |  |

|                | 2.2              | Digital Modulation Formats                                          | 12 |  |  |

|                | 2.3              | Interval Modulation                                                 | 14 |  |  |

| 3              | Pre              | fix Free Coding                                                     | 17 |  |  |

|                | 3.1              | Prefix Free Codes                                                   | 17 |  |  |

|                | 3.2              | Classification of Prefix Free Codes                                 | 19 |  |  |

|                | 3.3              | Results on Prefix Free Coding                                       | 20 |  |  |

| 4              | Inte             | erval Modulation Codes                                              | 22 |  |  |

|                | 4.1              | Review and Examples                                                 | 22 |  |  |

|                | 4.2              | Problem Formulation and Code Construction Using Integer Linear Pro- |    |  |  |

|                |                  | gramming                                                            | 23 |  |  |

|                | 4.3              | Linear Programming Relaxation                                       | 30 |  |  |

|                | 4.4              | Generalized Fibonacci Polyhedra and their Properties                | 30 |  |  |

|                |                  | 4.4.1 The 0-1 Principle                                             | 33 |  |  |

|                |                  | 4.4.2 The Decomposition Principle                                   | 38 |  |  |

|    | 4.5                                                           | Algorithm for Maximizing Linear Functions Over a Generalized Fi-    |     |  |  |

|----|---------------------------------------------------------------|---------------------------------------------------------------------|-----|--|--|

|    |                                                               | bonacci Polyhedra                                                   | 42  |  |  |

|    | 4.6                                                           | Algorithm for Maximizing a Linear Function Over the Intersection of |     |  |  |

|    |                                                               | a Generalized Fibonacci Polyhedra and a Hyperplane                  | 44  |  |  |

|    | 4.7                                                           | Applications and Examples                                           | 47  |  |  |

|    | 4.8                                                           | Open Problems and Future Work                                       | 55  |  |  |

| 5  | Ger                                                           | neralized Fibonacci Numbers and their Sums                          | 57  |  |  |

| 6  | A 20Gbs Integrated Optical Transceiver in IBM BiCMOS 7HP Pro- |                                                                     |     |  |  |

|    | cess                                                          | s Technology                                                        | 66  |  |  |

|    | 6.1                                                           | Transmitter and Receiver Architecture                               | 66  |  |  |

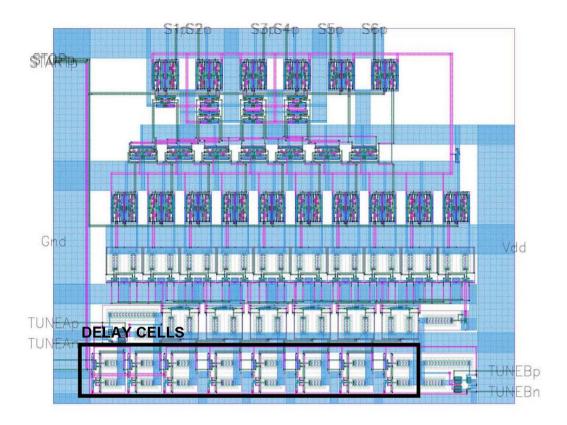

|    | 6.2                                                           | Delay Elements and Phase Interpolation Circuits                     | 71  |  |  |

|    | 6.3                                                           | Pseudo Random Data Sources                                          | 78  |  |  |

|    | 6.4                                                           | Error Unit for Symbol Error Rate Measurement                        | 83  |  |  |

|    | 6.5                                                           | Experimental Results                                                | 85  |  |  |

|    | 6.6                                                           | Summary                                                             | 98  |  |  |

| 7  | Cor                                                           | nclusions and Open Problems                                         | 100 |  |  |

| Bi | bliog                                                         | graphy                                                              | 103 |  |  |

## List of Figures

| 1.1  | General System Level Architecture of a High Speed Optical Receiver .   | 5          |

|------|------------------------------------------------------------------------|------------|

| 2.1  | Heirarchical Categorization of Analog and Digital Modulation Formats   | Ć          |

| 2.2  | Analog Signal Represented Using Different Modulation Formats           | 11         |

| 2.3  | Digital Signal Represented Using Different Modulation Formats          | 15         |

| 3.1  | An Optimum Huffman Code for (E,29), (I,5), (N,7), (P,12), (S,4), (T,8) | 20         |

| 4.1  | A Simple Interval Modulation Code Implemented Using Prefix Trees .     | 26         |

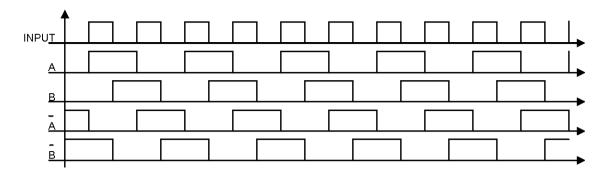

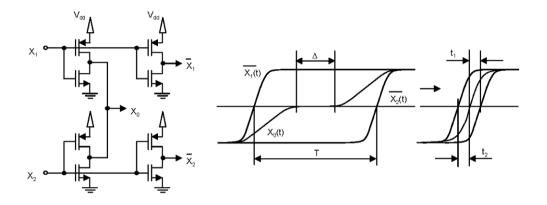

| 6.1  | System Level Architecture of Asynchronous Transmitter                  | 67         |

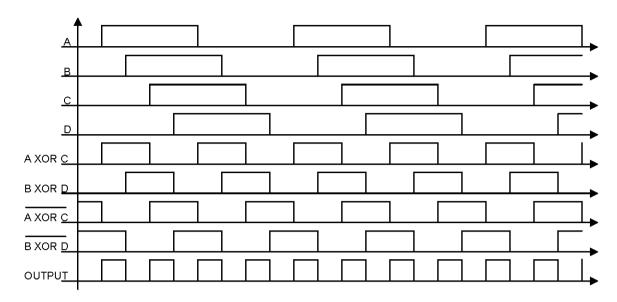

| 6.2  | Transmitter Waveforms                                                  | 68         |

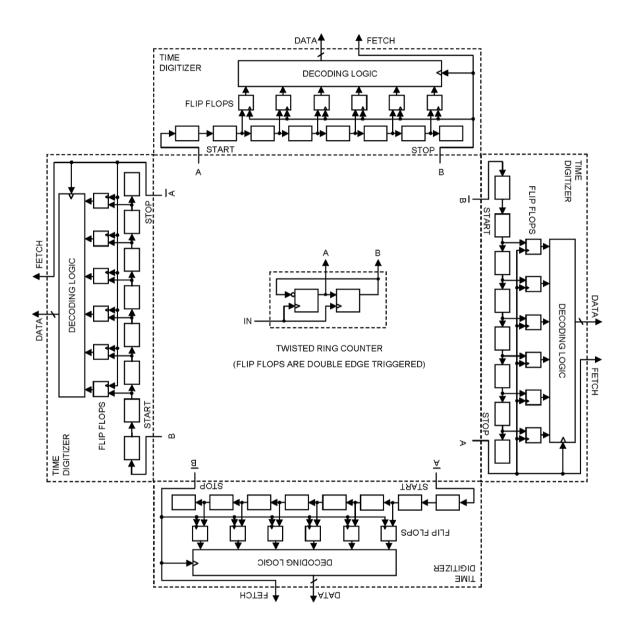

| 6.3  | System Level Architecture of Asynchronous Receiver                     | 70         |

| 6.4  | Receiver Waveforms                                                     | 71         |

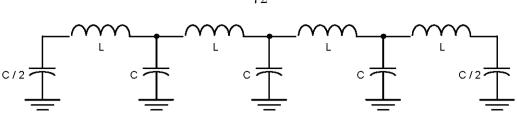

| 6.5  | Constant-K LC Ladder Structure with 4 Stages (Termination Resistors    |            |

|      | are Not Shown)                                                         | 72         |

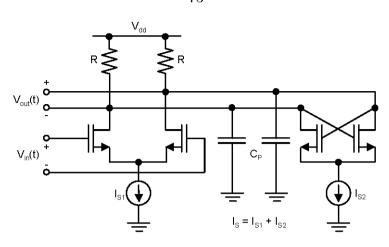

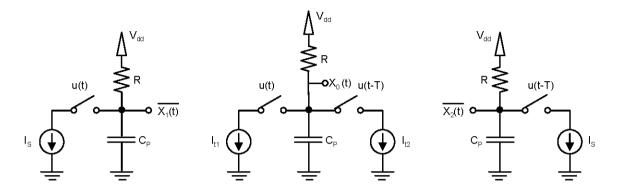

| 6.6  | Differential Tunable Delay                                             | 73         |

| 6.7  | Simple Model of Tunable Delay                                          | 73         |

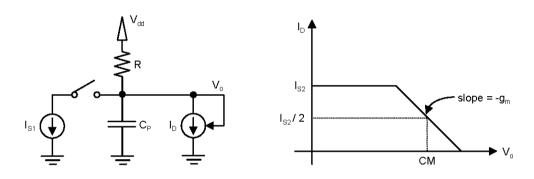

| 6.8  | Effect of Changing Tail Currents on Tunable Delay                      | <b>7</b> 4 |

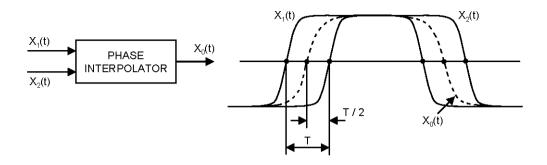

| 6.9  | Phase Interpolation Concept                                            | 75         |

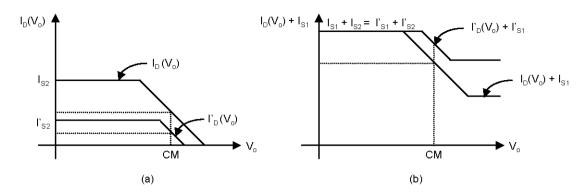

| 6.10 | Static CMOS Phase Interpolator                                         | 75         |

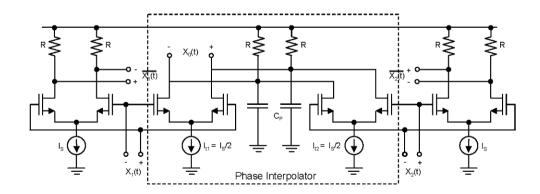

| 6.11 | A Differential Current-Mode Phase Interpolator                         | 75         |

| 6.12 | Simplified Model of Phase Interpolator                                 | 76         |

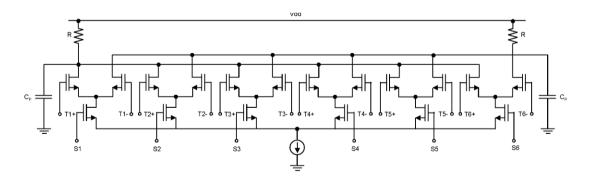

| 6.13 | A Differential 6-1 Multiplexer and Phase Interpolator                  | 76         |

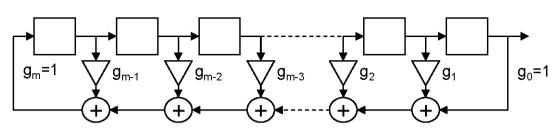

| 6.14 | Fibonacci Implementation of a Linear Shift Register                    | 79         |

| Galois Implementation of a Linear Shift Register                          | 79                                                                                                                    |

|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

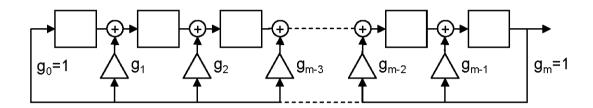

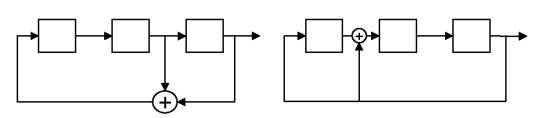

| Fibonacci and Galois Implementation of Linear Shift Registers Corre-      |                                                                                                                       |

| sponding to the Generating<br>Polynomial $X^3+X+1$                        | 81                                                                                                                    |

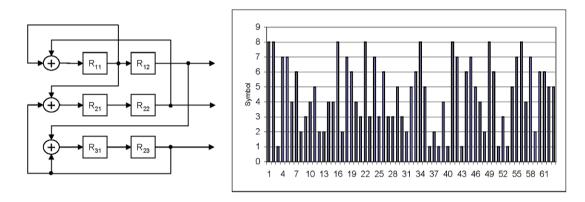

| A Cross Coupled Two Dimensional Linear Shift Register and the Cor-        |                                                                                                                       |

| responding $m$ -sequence                                                  | 81                                                                                                                    |

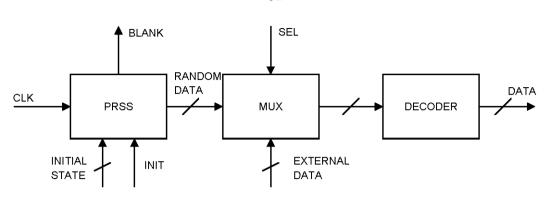

| System Level Schematic of On Chip Datasource                              | 82                                                                                                                    |

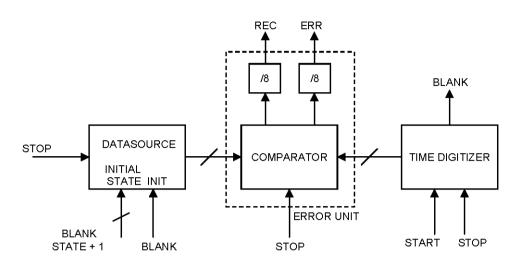

| Error Unit Integrated with Data Source and Time Digitizer Circuit $$ . $$ | 84                                                                                                                    |

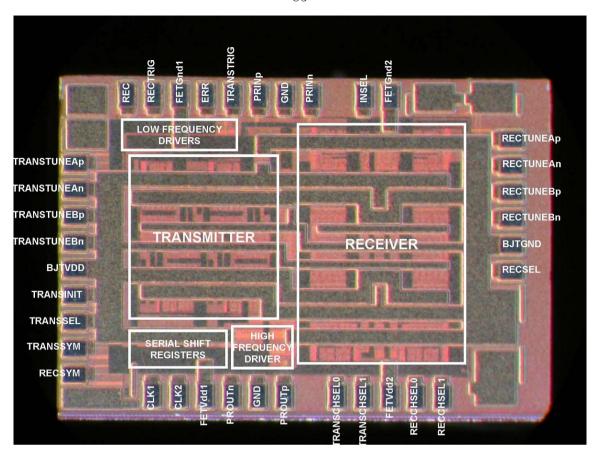

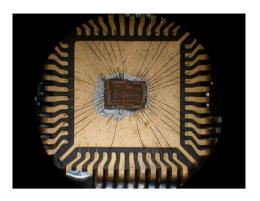

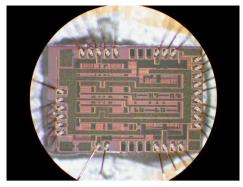

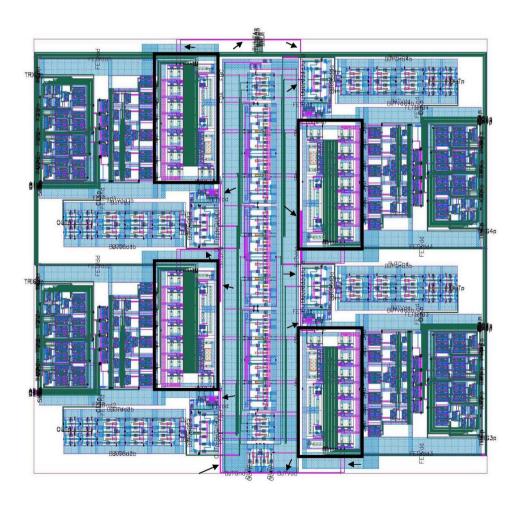

| Die Micrograph of Experimental Prototype Fabricated in $0.18\mu m$ IBM    |                                                                                                                       |

| BiCMOS 7HP Technology                                                     | 85                                                                                                                    |

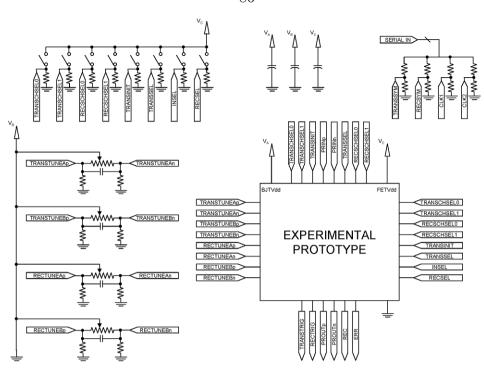

| Control Circuit Schematic                                                 | 86                                                                                                                    |

| Experimental Prototype Wirebonded to Chip Carrier Package                 | 87                                                                                                                    |

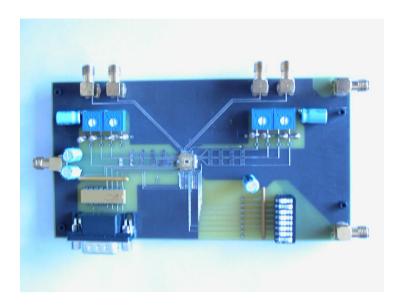

| Printed Circuit Board with Control Circuitry, Chip Carrier and Exper-     |                                                                                                                       |

| imental Prototype                                                         | 88                                                                                                                    |

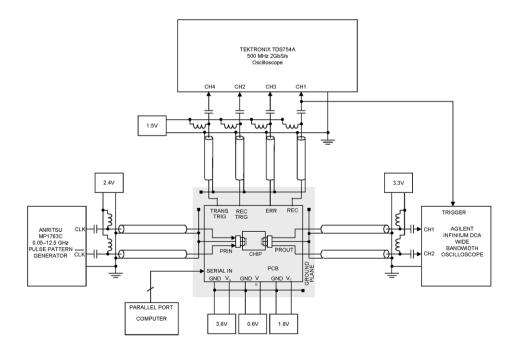

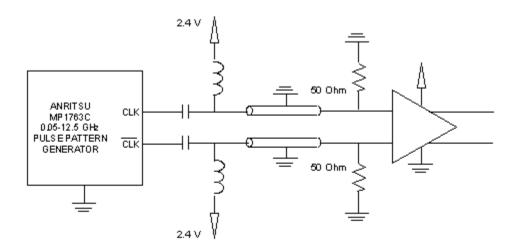

| Measurement Setup                                                         | 88                                                                                                                    |

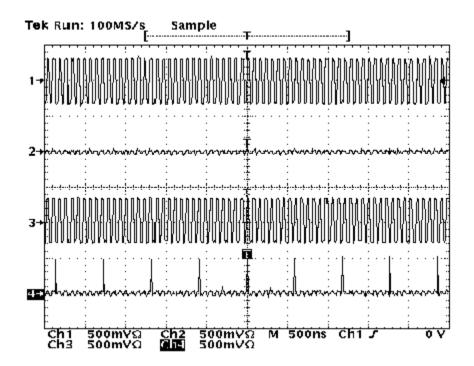

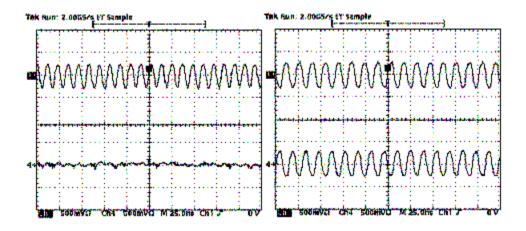

| Low Frequency Transmitter Measurements                                    | 90                                                                                                                    |

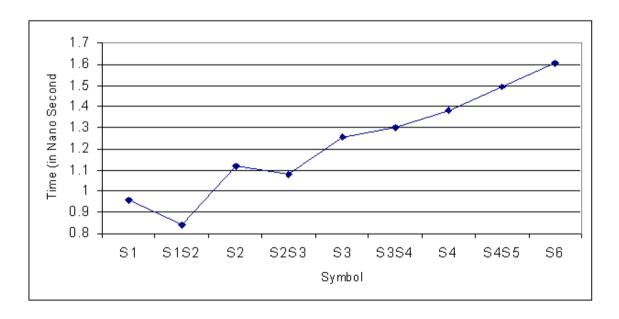

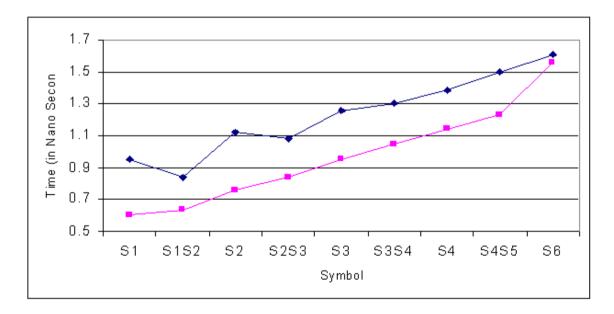

| Delay Lines Characterized Using Low Frequency Measurements                | 90                                                                                                                    |

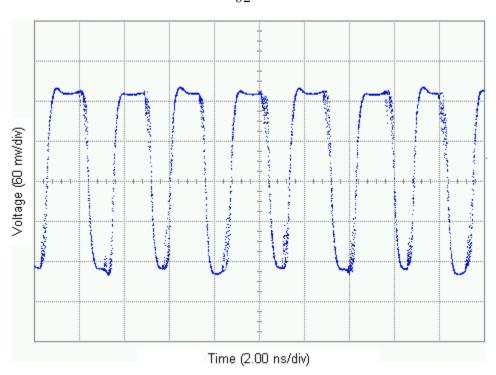

| High Frequency Transmitter Measurements                                   | 92                                                                                                                    |

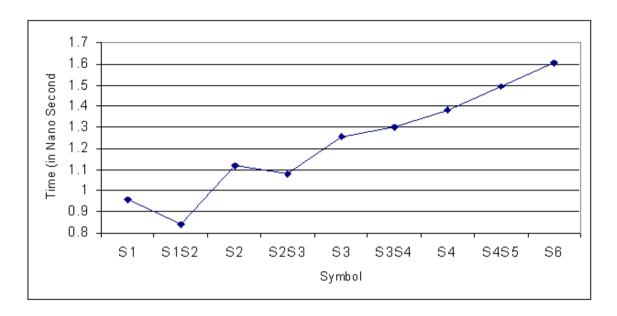

| Delay Lines Characterized Using High Frequency Measurements               | 93                                                                                                                    |

| Comparison of Simulated Delays with Estimated Parasitics and High         |                                                                                                                       |

| Frequency Measurements                                                    | 93                                                                                                                    |

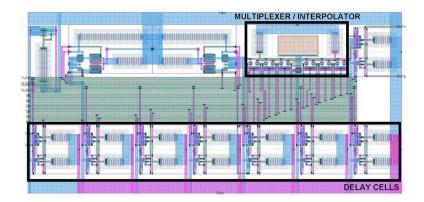

| Layout of Reconfigurable Delay Lines                                      | 95                                                                                                                    |

| Transmitter Layout                                                        | 95                                                                                                                    |

| Layout of Time Digitizers                                                 | 97                                                                                                                    |

| Circuit for Supplying an External Input to the Receiver                   | 97                                                                                                                    |

| Low Frequency Receiver Measurements                                       | 99                                                                                                                    |

|                                                                           | Fibonacci and Galois Implementation of Linear Shift Registers Corresponding to the GeneratingPolynomial $X^3 + X + 1$ |

## List of Tables

| 3.1 | Examples of Distinct, Uniquely Decodable and Prefix Free Codes                   | 18  |

|-----|----------------------------------------------------------------------------------|-----|

| 3.2 | Examples of Prefix Free Codes Belonging to Different Classes                     | 19  |

| 4.1 | Code with $S = \{1.00, 1.13, 1.27, 1.42, 1.60, 1.80, 2.03, 2.28, 2.57, 2.89\}$ . | 24  |

| 4.2 | Code with $S = \{2.00, 2.29, 2.61, 2.99, 3.41, 3.90, 4.46, 5.09, 5.82, 6.65\}$   | 2.5 |

### Abstract

In this thesis we propose a new, biologically inspired, paradigm for the design of high speed communication systems. The paradigm consists of a new modulation format referred to as Interval Modulation (IM). In order to transmit data in an efficient manner using this format, new coding techniques are needed. In this thesis we propose a coding technique based on variable length to variable length prefix trees and code construction algorithms are outlined. These codes are referred to as Interval Modulation Codes (IMC). Furthermore, data encoded with this modulation format cannot be transmitted or received using conventional synchronous CDR based receivers. In this thesis we outline a new asynchronous circuit architecture for both the transmitter and receiver. The architecture is based on active delay lines and eliminates the need for clock recovery.

## Chapter 1

## Introduction

In this thesis we propose a biologically inspired paradigm for the design of high speed digital communication systems for fiber optic communication. The transmission of information in neural systems has been extensively studied. Neural systems are largely asynchronous in nature. The transmission of information from one neuron to another, happens by means of a spike train, or a sequence of action potentials. These action potentials are all or none events. Once a neuron spikes, it enters a refractory period, during which it cannot generate another action potential. The reasons underlying this phenomenon are related to the biophysics of action potential generation. This is the only constraint on the time difference between two adjacent spikes or action potentials. How information is encoded in spike trains is an area of active study and debate, and there are reasons to believe information is encoded differently in different neurons based on function. Two leading hypothesis are rate codes, in which information is encoded in the frequency of action potentials or spikes and temporal codes in which information is encoded in the time difference between two consecutive action potentials.

Communication systems have a wide array of applications, and the theory underlying them has also received much attention. Where as communication systems, can refer to systems that are used to transmit analog or digital information, in this thesis we will mainly discuss communication systems for the transmission of digital information. Unlike neural systems, most communication systems, and in general digital systems are synchronous in nature. Furthermore, unlike neural systems, gen-

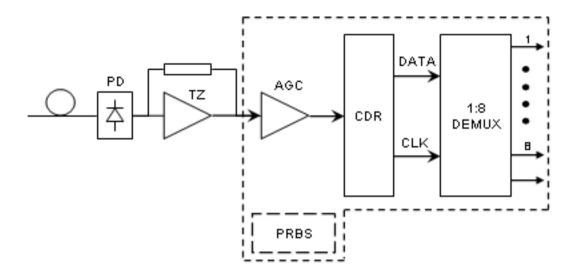

erally information in digital systems is encoded in the amplitude of the signal, a high represents a 1, a low represents a 0. This simple modulation format is known as Non Return to Zero (NRZ) modulation and it is the modulation format of choice in most communication systems. In spite of the simplicity of the modulation format, sending data across a link requires more than just stuffing bits in one end and having them show up at the other. The bits arriving at the receiver must be sampled with a clock to return them to the digital domain. With slower serial interfaces, such as analog spectrum telecommunication modems, this clocking may often be done through an asynchronous over sampling of the received bit stream. At the faster data rates in the optical communication domain, this over sampling becomes impractical. At faster transfer rates the sample clock must operate at the same rate as the bits in the data stream. While the sample clock could be delivered on a separate link, this is generally poor practice. The time skew between the data and the clock is difficult to manage, and the cost of the second links makes this prohibitive. Since no sample clock is delivered to the receiver along with the data, a clock must be extracted from the data stream. This is accomplished through the use of a high performance PLL (Phase Locked Loop) that detects the transitions in the serial stream as illustrated in Figure 1.1. Numerous 10-Gb/s fiber optic receivers based on the paradigm described above have been implemented [4], [8], [42], [43], [44], [45], [73], [88] and [101]. Unfortunately, an NRZ data stream may contain few if any transitions, especially when sending data of mostly one or zero bits. To send data of this type, the data must be modified to force additional transitions into the data stream. Thus there is a need for coding. Numerous methods exist to force additional transitions into a data stream. These can be broken down into two categories, scrambling and run length limited coding.

Scrambling modifies a data stream by merging it with one or more randomizer polynomials. Scrambling, used in telecommunications interfaces such as SONET [89] and ATM [6], is 100% efficient. For every bit in the source data stream, a single bit is sent across the interface. While this would at first appear as the perfect solution, scrambling does have its drawbacks. The characteristics of a scrambler are such that the scrambler can be zeroed out by specific data patterns. In other words, scrambling

Figure 1.1: General System Level Architecture of a High Speed Optical Receiver

cannot guarantee transitions on the data stream, it can only make them more likely. For rogue bit sequences, there will be no data transitions. A scrambled interface is also somewhat limited in how link control information is moved across a link. Because the link efficiency is perfect, all combinations of bits are used to represent data. This requires all link information to be sent as combinations of data characters.

The other method of forcing transitions involves run length limited coding. In a coded interface, the source data is modified by mapping the source data into alternate bit combinations called symbols. These symbols are constructed with extra bits that guarantee a minimum transition density. This problem has been extensively studied in literature and numerous solutions are available [1], [30], [31], [49], [53], [65], [67], [68], [69] and [102]. Encoded interfaces generally have link efficiencies ranging from 50-95%. One of the most popular encodings is known as 8B/10B [102]. This encoding is used by popular high speed serial interfaces such as Fibre Channel [112], ATM [6], ESCON<sup>TM</sup>, Gigabit Ethernet [34] and DVB-ASI. The 8B/10B code maps an 8-bit data character into a 10-bit symbol known as a transmission character. This code limits the maximum number of consecutive ones or zeros that can occur in the transmitted serial bit stream to five. The efficiency of the link is 80%. This code is optimized for transmission across optical media. In addition to guaranteeing transition density,

the code is DC balanced. Thus it limits the low frequency content in the data stream which in turn allows the use of low-cost AC-coupled optical modules. In addition since some of the bit sequences are unused, these can be included in the data stream as special control characters (such as start of frame, end of frame, etc.).

We will describe an alternate paradigm for the design of digital communication systems which is inspired by temporal codes that are used in the nervous system. The primary advantage of the proposed paradigm over conventional designs is a substantial improvement in data rate. The combination of amplitude modulation and run length limited coding can be thought of as interval modulation. In the 8B/10B code, there can be at most 5 consecutive zeros or ones. If B is the bit period, the time between voltage transitions is either 1B, 2B, 3B, 4B, or 5B. Note that since the circuits used are synchronous, the time between voltage transitions are always a multiple of the bit period. The data rate is 0.8/B (compared to a data rate of 1/Bif scrambling were used). The fundamental draw back of this scheme is also that the time intervals between voltage transitions must be multiples of a clock period. Consider what would happen if the time between voltage transitions were to be restricted to just two possibilities 1B, 1.2B. And data were transmitted using a very simple coding scheme where a pulse of duration 1B would be transmitted for every zero in the data stream and a pulse of 1.2B were transmitted for every one in the data stream. Even in the worst case (sequence of all ones), the data rate achieved by this simpler coding would be 1/1.2B which is greater than 0.8/B. In addition to a higher data rate, the coding scheme is much simpler than the 8B/10B code and thus simpler to implement. The code also provides better error propagation properties. It must be noted that this simple scheme for coding is not optimal. Another scheme would first take a binary sequence of fixed length, and map it to a balanced binary sequence. Simple coding techniques for doing this exist and the number of extra bits is only logarithmic in the number of bits in the original sequence [61]. Thus if the original sequence is long enough, there is no loss in terms of data rate. Now the balanced code can be transmitted using the technique described above. Since the coded sequence contains an equal number of zeros and ones, the data rate would be 1/1.1B. Also the code has the interesting property that all binary sequences can be transmitted in the same amount of time. However, there is a loss in terms of error propagation properties. The above arguments illustrate, that if we drop the constraint that the time between voltage transitions must be a multiple of the bit period, then improvements in terms of data rate, DC balance and other properties are realizable. In the example above, we had restricted the time between voltage transitions to belong to one of two possibilities. This requirement is arbitrary. For example the time between voltage transitions could be restricted to belong to 1.0B, 1.2B, 1.4B, 1.6B, or 1.8B. It is possible to show that in this case, the data rate can exceed even that achieved by scrambling. Furthermore, the time between voltage transitions does not have to be restricted to multiples of the clock period B or some other constant but can be a set of any arbitrary values, even though in the cases considered, the time between voltage transitions are multiple of 0.2B. It must be noted that in the optical domain, data rates are very high and as mentioned the clock due to limitations in chip processes can operate at a frequency of at most 1/2B (this corresponds to a bit period of B). Given this limitation, it is not possible to implement a receiver which samples the amplitude using a clock with a frequency of 1/0.2B. An alternate architecture is needed, a transceiver architecture which operates directly by measuring time between voltage transitions. Notice that if we were to sample the amplitude, we would need to sample it at a frequency of 1/0.2B. However, if we are to measure time differences between adjacent transitions, the smallest measurable time interval only needs to be a bit period. And the maximum sampling frequency needs to be 1/2B. The resolution of the time measurement circuit needs to be sub-bit period. Variants of Run Length Limited Codes can still be used to do the encoding in the case where time between transitions is a multiple of some number smaller than the bit period B, but since the architecture of the transceiver is different, conventional Run Length Limited Codes which are designed to be used with conventional synchronous transceivers, lose some of their desirable properties, like limiting the effects of error propagation. Formulating a new circuit architecture, will give rise to new coding constraints that must be satisfied by desirable codes. In this thesis will be address two fundamental questions – one how is binary data to be encoded in a signal where time between transitions can take on arbitrary values. And second what circuit architecture can be used for transmission and reception of data using such a modulation format at high data rates.

We next review the organization of this thesis. In Chapter 2 we will discuss the two basic problem of transmission of analog and digital information through an optical channel. Next we will describe the modulation formats used for analog and digital transmission of information. We will then compare the proposed modulation format to the different modulation formats concluding with a hierarchical categorization of different modulation formats. In order to transmit data using the proposed modulation format one needs new and novel coding techniques. In this thesis we propose a coding technique based on variable length to variable length prefix free codes. In Chapter 3, we will introduce the concept of a prefix free code, and illustrate its primary advantage, instantaneous decodability without the need for look ahead. We will classify prefix free codes into four major categories and discuss and summarize the theoretical problems associated with prefix free coding that have been studied in literature. In Chapter 4 of this thesis we will propose the use of variable length to variable length prefix free codes for interval modulation and refer to these as interval modulation codes. Next we will formulate the problem of code construction. This problem will then we reduced to a large scale integer optimization problem which is well structured. We study the properties of the polyhedra defined by this structured system of inequalities. These properties lead to efficient algorithms for determining if the linear programming relaxation of the code construction problem is feasible and an efficient algorithm for solving the linear programming relaxation. In Chapter 5, we study a generalization of the Fibonacci numbers that arises in the context of rate analysis as well as code construction. In Chapter 6, we outline a novel asynchronous circuit architecture for high speed digital transceiver design. The transmitter is based on the concept of a reconfigurable ring oscillator whereas the receiver is based on the concept of multiplexed picosecond time digitizers. The proposed architecture does away with the need for clock recovery circuits. A prototype based on the ideas discussed in this chapter was fabricated and measurement results are discussed. In Chapter 7 we briefly summarize the contributions of this thesis and outline exciting areas for future research.

## Chapter 2

## **Modulation Formats**

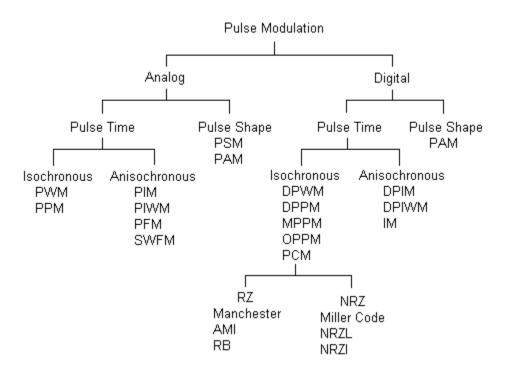

In this chapter we review different modulation formats that are commonly used for data transmission through fiber. Modulation formats can be classified into two categories, analog and digital, based on whether they are designed for analog or digital data transmission. The hierarchical classification of modulation formats used for analog and digital data transmission is presented in Figure 2.1.

#### 2.1 Analog Modulation Formats

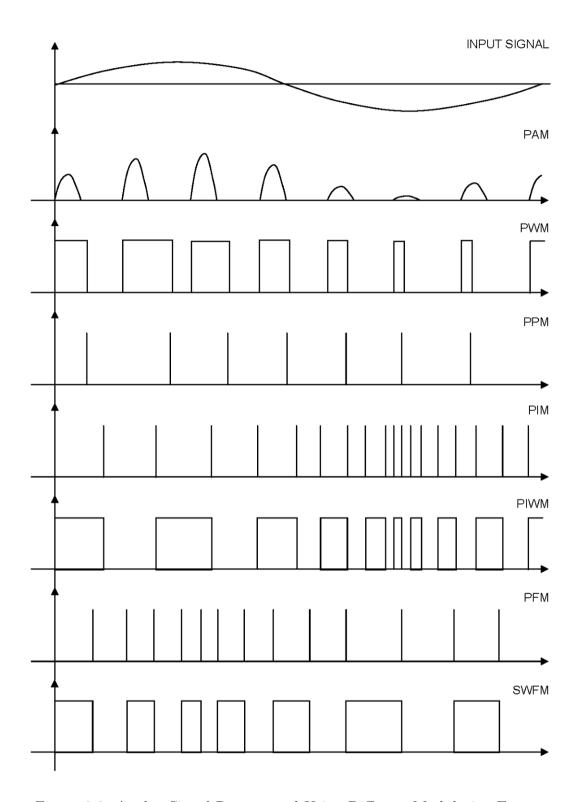

Modulation formats for analog data transmission can be grouped into two categories, Pulse Shape Modulation (PSM) Formats and Pulse Time Modulation (PTM) Formats. The simplest example of a PSM modulation format is Pulse Amplitude Modulation (PAM). In PAM the amplitude of individual, regularly spaced pulses in a pulse train is varied in accordance with the amplitude of the modulating signal. Such a scheme is both simple and bandwidth efficient but cannot deliver the signal to noise ratio. In addition PAM suffers to an extent from nonlinearity of the optical channel, the photodiode, the photodetector and associated circuitry, severely limiting the quality of information transmitted. Due to these reasons, real communication systems are based on alternate modulation formats discussed below.

The basic framework for research into PTM techniques was laid down around 50 years ago and reported in the late 1940s [23], [29], [54] and [64] but it is only recently that a revival of interest has been experienced with the development of fiber

Figure 2.1: Hierarchical Categorization of Analog and Digital Modulation Formats

transmission systems [111]. In all PTM methods, one of a range of time-dependent features of a pulsed carrier is used to convey information in preference to the carrier amplitude. The fundamental advantages of these schemes are that modulation is simple, the signal is not quantized thus there is no need for digital coding, and the pulse format renders the scheme immune to device and channel nonlinearity. Furthermore, the signal can be routed through logic circuits and switching nodes in a network. PTM techniques can be further grouped into two categories – Isochronous PTM techniques and Anisochronous PTM techniques.

Isochronous PTM techniques are fixed rate schemes that require a fixed amount of time to transmit a sample of the modulating signal. Two common examples under this category are Pulse Width Modulation (PWM), sometimes also referred to as Pulse Duration Modulation (PDM) and Pulse Position Modulation (PPM). In PWM, the width of the pulsed carrier within a predetermined timeframe is changed according to the sampled value of the modulating signal. PPM can be considered as differentiated

PWM, and carries information by virtue of the continuously variable position of a narrow pulse within a fixed timeframe. Anisochronous PTM techniques variable rate schemes in which the time required to transmit a sample of the modulating signal varies and generally depends on the sampled value itself. This group consists of four different modulation formats, Pulse Interval Modulation (PIM), Pulse Interval and Width Modulation (PIWM), Pulse Frequency Modulation (PFM) and Square Wave Frequency Modulation (SWFM). As the name suggests in PIM, the variable intervals between adjacent narrow pulses is determined by the amplitude of the input signal. PIWM is derived directly from PIM to produce a waveform is which both mark and space convey information in alternating sequence. In both PIM and PIWM each successive timeframe commences immediately after the previous pulse unlike in PWM and PPM. In PFM, the instantaneous frequency of a train of narrow pulses is determined by the amplitude of the modulating signal. SWFM is closely related to PFM, consisting essentially of a series of square wave edge transitions occurring at the pulse positions of PFM.

The primary advantage of Isochronous PTM techniques over Anisochronous PTM techniques, is that Isochronous PTM techniques are far easier to multiplex in the time domain because of their fixed frame timing intervals and require only a simple demultiplexer at the receiving end. The primary advantage of Anisochronous PTM techniques over Isochronous PTM techniques is that Anisochronous PTM techniques essentially can transmit more samples in a given amount of time. PWM and PPM have been widely adapted for use in fiber optic applications [10], [11], [86], [96], [104], [105] and [106]. PFM has been used extensively for optical fiber transmission of video and broadcast quality TV signals [46], [47], [48], [50], [55] and [76] with SWFM being employed for the transmission of HDTV and other wideband instrumentation signals [66], [79], [82], [107], [109] and [108]. PIM and PIWM have found fewer wideband fiber optic applications [76], [77], [83], [84] and [110].

Figure 2.2: Analog Signal Represented Using Different Modulation Formats

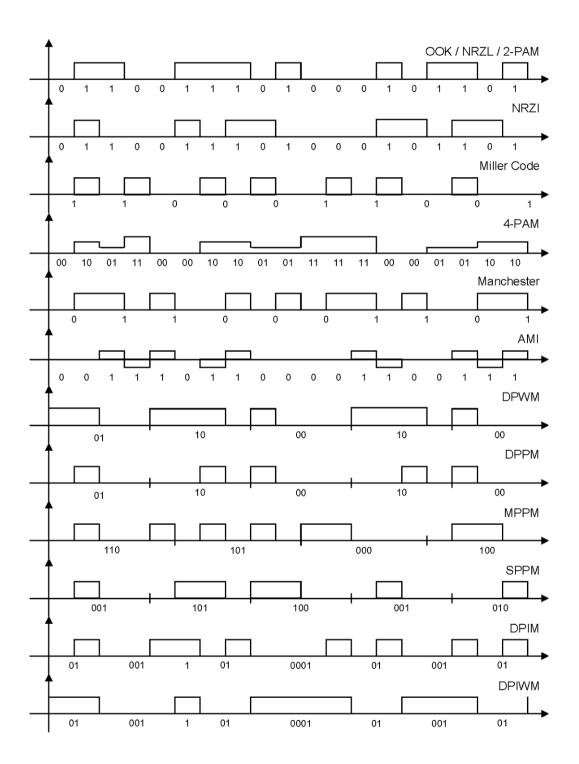

#### 2.2 Digital Modulation Formats

There are several modulation and encoding schemes that are suitable for optical communication systems. The simplest approach is based on intensity modulation with direct detection and is referred to as on-off keying (OOK). In this scheme a zero is represented by zero intensity and a one by positive intensity. The primary disadvantage of this scheme is the low power efficiency. Higher average power efficiency can be achieved by employing Pulse Time Modulation (PTM) schemes which will be discussed later. In these schemes a range of time dependent features of a pulse carrier can be used to convey information. OOK is also referred to as 2-PAM since there are two intensity levels, one corresponding to a logical 0 and the other corresponding to a logical 1. In an n-PAM modulation format, n distinct intensity levels are used, each of these can represent a unique binary combination of  $\lfloor \log_2(n) \rfloor$  bits. In practical systems the number of intensity levels used is 2 or 4. The advantage of 4-PAM systems over 2-PAM systems is higher data rate, but 4-PAM systems suffer from the same limitations as PAM systems used for analog transmission. Namely, nonlinearities in the channel, photodiode and photodetector and associated circuits affect the threshold levels that must be used in the receiver. Furthermore, 4-PAM signals cannot be passed through digital logic and more complex processing circuitry is required.

As in analog modulation formats, an alternate is to use PTM techniques which can be grouped into two classes, Isochronous PTM techniques and Anisochronous PTM techniques. Isochronous PTM techniques, are fixed data rate techniques in which the time required to transmit a bit of information is constant, or equivalently, the number of bits transmitted in a constant amount of time is constant. Anisochronous PTM techniques are variable data rate techniques in which the time required to transmit a given number of bits varies depending on the bit sequence. The common Isochronous PTM techniques are Digital Pulse Width Modulation (DPWM) or Digital Pulse Duration Modulation (DPDM), Digital Pulse Position Modulation (DPPM), Multiple Pulse Position Modulation (MPPM), Overlapping Pulse Position Modulation Modulation (MPPM),

tion (OPPM) and Pulse Code Modulation (PCM). The common Anisochronous PTM techniques are Digital Pulse Interval Modulation (DPIM) and Digital Pulse Interval Width Modulation (DPIWM).

DPWM is comparable to PWM for analog transmission. In this modulation format the width of a pulsed carrier within a predetermined timeframe is changed according to the value of binary combination represented by that time frame. DPPM is a differentiated version of DPWM. In this modulation format, the position of a single pulse within a time frame encodes the binary combination represented by that time frame. MPPM is a generalization of DPPM. In this format the position of multiple, but a fixed number, of pulses within a time frame encodes the binary sequence represented by that time frame. OPPM is a modification of MPPM. In this modulation format, an added constraint is placed on the position of the multiple pulses within a time frame. The added constraint is that the multiple pulses occupy adjacent slots. PCM techniques can be further classified into two groups, Return to Zero (RZ) techniques and Non Return to Zeros (NRZ) techniques. Common RZ modulation techniques are RB Modulation, Alternate Mark Inversion Modulation (AMI) and Manchester Modulation. Common NRZ techniques are Non Return to Zero Level (NRZL) modulation, Non Return to Zero Inverted (NRZI) modulation and Miller Code Modulation. AMI modulation format is a pseudo ternary modulation format in which successive ones are represented by alternately positive and negative polarity and the absolute values of their amplitudes are normally equal and zeros are represented by zero amplitude. In Manchester Modulation, a zero is represented by a 0-1 transition whereas 1-0 transition encodes a 1. NRZL modulation is equivalent to OOK and 2-PAM modulation. A positive intensity level is used to encode a logical 1 and a zero intensity level is used to encode a 0. In NRZI modulation there is a change in amplitude level from one level to another, when a one is transmitted. The amplitude level remains unchanged when a zero is transmitted. This kind of encoding is also called differential encoding. In Miller Code Modulation, a logical one is encoded as a 01 and a zero is encoded as 10 if the preceding bit was a zero, and 00 if the preceding bit was a 1.

As mentioned the Anisochronous Modulation Techniques are DPIM and DPIWM.

In DPIM the time between two consecutive pulses encodes the binary sequence. Thus two binary sequences containing the same number of bits will be represented by different intervals. In DPIWM, the binary sequence is encoded in the width of pulses of alternating polarity.

#### 2.3 Interval Modulation

Interval Modulation (IM) is an anisochronous modulation format for digital data transmission. Interval Modulation is similar to DPIWM in that the binary sequence in encoded in the width of pulses of alternating polarity. The fundamental difference between DPIWM and IM is that in DPIWM the widths of the pulses are constrained to be integer multiples of the bit period. In IM the widths must belong to set of arbitrary values which need not be integer multiples. It must be noted that the data rate achieved by NRZ, OOK and 2-PAM is 1. The data rate achieved by 4-PAM is 2. All other schemes achieve a data rate of less than 1. The disadvantages of 4-PAM have already been discussed. The threshold level used for thresholding intensity levels at the receiver becomes sensitive to nonlinearities of the channel, photodiode and photodetector and associated circuitry. Furthermore, 4-PAM signals are not compatible with conventional two state digital circuits. Like 4-PAM, IM can achieve a data rate in excess of 1. The primary advantages over 4-PAM are that the signal is binary, that is it uses only two intensity levels making it compatible with conventional digital circuitry and making it insensitive to nonlinearities in both the channel and other devices. The disadvantage of IM over 4-PAM are additional complexity since rate efficient coding of binary data is non trivial. Furthermore, since IM is Anisochronous whereas PAM is Isochronous some schemes must be deployed to mitigate the effects of error propagation. It must be noted that all Anisochronous schemes can be impacted by error propagation. So this disadvantage is not restricted to IM alone. Also since the pulse widths need not be multiples of the bit period but can take on arbitrary values, the transceiver design cannot be based on conventional clocked synchronous circuitry. In this thesis we will outline present a coding technique

Figure 2.3: Digital Signal Represented Using Different Modulation Formats

based on variable length to variable length prefix-free codes and an asynchronous transceiver architecture.

## Chapter 3

## **Prefix Free Coding**

#### 3.1 Prefix Free Codes

**Definition 1** A code is a mapping of source messages, words from the source alphabet, into codewords, words from the code alphabet.

Consider the simple code shown in Figure 1 A. The source alphabet is  $\{a, b, c, d\}$  and the code alphabet is  $\{0, 1\}$ . The code itself is a mapping of source messages or words from the source alphabet,  $\{a, b, c, d\}$  to words from the code alphabet,  $\{00, 01, 10, 11\}$ . Thus the string cabd would be represented as 10 00 01 11. The source messages are the basic units into which the string to be represented is partitioned. These basic units may be single symbols of the source alphabet, as in the preceding example, or they may be strings of symbols from the source alphabet. When source messages of variable length are allowed, the question of how a message ensemble (sequence of messages) is parsed during encoding, into individual messages arises. Similarly, if variable length codewords are permitted, the question of how a code ensemble (sequence of codewords) is to be parsed into codewords during the decoding process arises.

**Definition 2** A code is distinct if each codeword is distinguishable from every other, that is the mapping from source messages to code words is one to one.

**Definition 3** A distinct code is uniquely decodable if every codeword is identifiable when immersed in a sequence of codewords.

Note that both the codes in Table 3.1 (A-D) are all distinct. The codes in Table 3.1 (A,C,D) are all uniquely decodable but the code in Table 3.1 (B) is not. If the code in Table 3.1 (B) were to be used 10 could be parsed as the codeword 10 or codeword 1 followed by codeword 0. Thus any message transmitted using this code cannot be uniquely decoded even though the code is distinct.

| Message | Code | Message | Code | Message        | Code   | N             | Aessage                 | Code |

|---------|------|---------|------|----------------|--------|---------------|-------------------------|------|

| a       | 00   | a       | 0    | a              | 1      | a             | ,                       | 0    |

| b       | 01   | b       | 1    | b              | 100000 | $\mid b \mid$ |                         | 10   |

| c       | 10   | c       | 10   | c              | 00     | c             |                         | 110  |

| d       | 11   | d       | 11   |                |        | $\mid d$      | !                       | 111  |

| A       |      | В       |      | $\overline{C}$ | ;      |               | $\overline{\mathbf{D}}$ |      |

Table 3.1: Examples of Distinct, Uniquely Decodable and Prefix Free Codes

**Definition 4** A uniquely decodable code is a prefix-free code if no codeword is prefix of any other codeword.

Note that the codes in Table 3.1 (A,D) are prefix free. Prefix codes have the desirable property that they are instantaneously decodable. That is the code message can be parsed into codewords without the need for look ahead. If the source messages are also prefix free then the code is both instantaneously encodeable and decodable. There is no need for look ahead in either the coding or decoding process. However, the prefix property is not needed to ensure that a code be uniquely decodable. The code in Table 3.1 (C) is uniquely decodable but it is not prefix free. In order to decode a message encoded using the codeword set  $\{1,100000,00\}$  look ahead is required. Note that the first codeword of the message 1000000001 is 1 but this cannot be determined until all ten symbols have been read. The algorithm for determining whether a 1 corresponds to the codeword 1 or the codeword 100000 is based on determining the parity of the number of zeros that follow the 1. Even though this code is not prefix free, it is uniquely decodable. However, decoding requires look ahead.

| $aa \leftrightarrow 00$ | $aa \leftrightarrow 0$   | $a \leftrightarrow 00$   | $a \leftrightarrow 0$     |

|-------------------------|--------------------------|--------------------------|---------------------------|

| $ab \leftrightarrow 01$ | $ab \leftrightarrow 10$  | $ba \leftrightarrow 01$  | $ba \leftrightarrow 10$   |

| $ba \leftrightarrow 10$ | $ba \leftrightarrow 110$ | $bba \leftrightarrow 10$ | $bba \leftrightarrow 110$ |

| $bb \leftrightarrow 11$ | $bb \leftrightarrow 111$ | $bbb \leftrightarrow 11$ | $bbb \leftrightarrow 111$ |

| A                       | В                        | С                        | D                         |

Table 3.2: Examples of Prefix Free Codes Belonging to Different Classes

#### 3.2 Classification of Prefix Free Codes

Prefix free codes can be classified into four classes depending on the number of source alphabets in the source strings and the number of code alphabets in the code strings [63]. The first class consists of prefix free codes in which both the number of source alphabets in the source strings and the number of code alphabets in the code strings is fixed. These codes are referred to as the block to block prefix free codes. A common example is the ASCII representation of the alphanumeric characters. Another example is shown in Table 3.2 (A). Codes in which the number of source alphabets is fixed but the number of code alphabets is allowed to vary are referred to as block to variable length prefix free codes. A common example is Huffman codes [87, 27, 51], discussed later in this chapter. Another example is illustrated in Table 3.2 (B). Note that all the source messages have 2 symbols but the number of code alphabets in the codewords varies from one to three. Codes in which the number of source alphabets is allowed to vary but the number of code alphabets is fixed are referred to as variable length to block codes. An example is shown in Table 3.2 (C). Note that the number of source alphabets in the source messages varies from one to three but the number of code alphabets in the codewords is fixed to two. The most general class of codes consists of prefix free codes in which both the number of source and code alphabets is allowed to vary. A variable length to variable length prefix free code is shown in Table 3.2 (D).

Numerous variants of prefix free code construction problems can be defined. Generally, we are given the source and code alphabets. All source alphabets may have the same probability or the probabilities may differ. Furthermore, the code alphabets may have the same transmission times or the transmission times may differ.

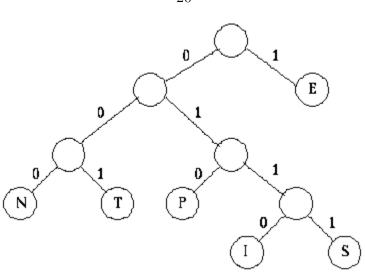

Figure 3.1: An Optimum Huffman Code for (E,29), (I,5), (N,7), (P,12), (S,4), (T,8)

Given the source and code alphabets, the probability of the source alphabets and the transmission times of the code alphabets, the problem is design a general code construction algorithm that minimizes or maximizes a given objective function. The objective function is generally the expected transmission time. Other variants of the code construction problem have been studied. In these variants in addition to the above, the code strings must satisfy some constraint, for example, all code strings must end in a given code alphabet.

#### 3.3 Results on Prefix Free Coding

Prefix free codes that have been most extensively studied in literature are block to variable length prefix free codes. The problem where the probabilities of the source alphabet are different but the transmission costs of the code alphabet are the same was first studied in 1948 by Shannon [87] and in 1949 by Fano [27] who developed essentially identical methods for constructing near optimum codes. In 1952 Huffman [51] used an elegant combinatorial technique to obtain a strictly optimum solution to the problem. These codes are referred to as Huffman codes and an example is discussed next. Let the source alphabet be  $\{E, I, N, P, S, T\}$  and the frequency of

occurrence be (E, 29), (I, 5), (N, 7), (P, 12), (S, 4) and (T, 8). The optimum Huffman Code is shown in Figure 3.1. In 1954 Blachman [12] generalized the Shannon-Fano approximation technique to treat the situation where both the probabilities of the source alphabet and the transmission costs of the code alphabet differ. In 1957 Marcus [70] improved on the Blachman technique by combining it further with the combinatorial results of Huffman. The algorithms of both Blachman and Marcus are approximate in nature and give near optimum solutions. Karp [57] developed an optimum algebraic solution by reducing the problem of code construction to an integer linear program which was solved using Gomory's integer programming algorithm [39, 40, 41]. Other approximation techniques have been developed by Krause [62], Cot [25, 26], Mehlhorn [72], Altenkamp and Mehlhorn [2] and Gilbert [35]. A dynamic programming algorithm for an exact solution has been developed by Golin and Rote [37] is  $O(n^{C+2})$  where n is the number of source words and the transmission cost of the code alphabet belongs to integers from 1 to C. No polynomial time algorithm for arbitrary transmission costs is known. The special case of constructing block to variable length prefix free codes where probabilities of source messages is fixed but transmission costs of the code alphabets is allowed to vary was first studied by Varn [99] in 1971 and is also referred to as Varn coding. Exact solutions have also been proposed by Perl et.al. [78], Choy and Wong [21], Cot [24], Stanfel [93], Kapoor and Reingold [56] and Golin and Young [36]. In 1990 Berger and Yeung [9] introduced a new class of prefix free codes having the property that each codeword ends with a one. A useful application of 1-ended prefix codes is considered by Capocelli et. al. [18, 20], where is it shown how to construct from a given 1-ended prefix code a self synchronizing prefix code having the same codeword lengths. The alphabetic version of 1-ended prefix codes has been studied by Browning and Thomas [16] and Capocelli, et. al. [19]. Synchronizing codes deal with limiting error propagation when variable length prefix free codes are used. Work on variable length to block prefix free codes was pioneered by Tunstall [98]. Compared to block to variable length prefix-free codes and variable length to block prefix free codes, variable length to variable length prefix free codes have received very little attention in literature.

## Chapter 4

## **Interval Modulation Codes**

#### 4.1 Review and Examples

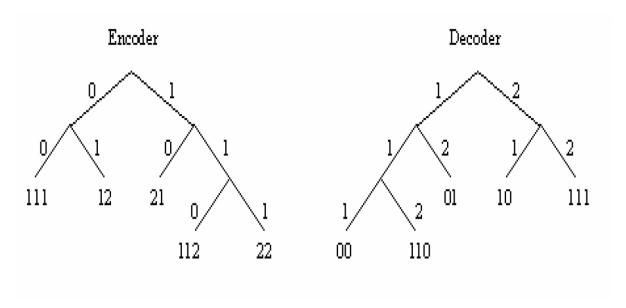

Generally, prefix free codes are used for source coding. However, in our case we would like to use them for channel coding. The data stream to be transmitted consists of binary data, 0s and 1s. These are our source alphabets. Furthermore, the modulated signal can be represented by a sequence of code alphabets which have different transmission times. An Interval Modulation Code is a variable length to variable length prefix free code defined by the source alphabet, 0 and 1, and the code alphabet which consists of a finite set of symbols with different transmission times. In this thesis, we will formulate an algorithm to construct interval modulation codes to maximize worst case data transmission rate. That is minimize the time required to transmit the worst binary data stream. We define S to be the set of permissible time intervals. For expository purposes assume S is  $\{1,2\}$ . A simple encoding strategy would be to map every binary 0 to a 1 and every binary 1 to a 2. This only achieves a worst case rate of 0.5 since a sequence of T 1s would require 2T time units to transmit. An alternate strategy would be to map  $00 \rightarrow 111, \ 01 \rightarrow 12, \ 10 \rightarrow 21, \ 110 \rightarrow 112$ and  $111 \rightarrow 22$ . Note that the sets  $\{00, 01, 10, 110, 111\}$  and  $\{111, 12, 21, 112, 22\}$  are both prefix-free. In the worst case this scheme would achieve a rate of 0.66 since a sequence of 2T 0s would require 3T time units to transmit. Since neither the number of bits nor the number of symbols is fixed, this is a variable length to variable length prefix-free code. Notice that the maximum number of bits that the encoder might have to examine before it can encode part of the binary sequence is 3 (corresponding to 110 or 111). This is the delay associated with the encoder and is referred to as  $T_E$ . Similarly the decoder might have to wait up to 4 units of time before it can map part of the received symbol sequence back to bits (corresponding to 112 or 22). This is the delay associated with the decoder and is referred to as  $T_D$ . More complex variable length to variable length prefix-free codes are shown in Table 4.1 and Table 4.2.

# 4.2 Problem Formulation and Code Construction Using Integer Linear Programming

We have already defined the set of permissible time intervals or symbols to be S. We assume that all elements in S are positive integers<sup>1</sup>. Furthermore, we assume that S has at least 2 elements. Let m be the largest element in S. For  $i \in \{1, 2, ..., m-1, m\}$ , let

$$K_i = \begin{cases} 1 & i \in S \\ 0 & i \notin S \end{cases} \tag{4.1}$$

We define  $N_K(T)$  to be the number of sequences of length T whose elements are in S.

$$N_K(T) = \begin{cases} \sum_{i=1}^m K_i N_K(T-i) & T > m \\ K_T + \sum_{i=1}^{T-1} K_i N_K(T-i) & 2 \le T \le m \\ K_1 & T = 1 \end{cases}$$

(4.2)

It is easy to show that  $N_K(T)$  can be computed using the recurrence above. When  $T=1, N_K(T)$  is 1 if  $K_1=1$   $(1 \in S)$  and 0 if  $K_1=0$   $(0 \notin S)$ . Hence, when  $T=1, N_K(T)=K_1$ . Now consider the case when  $2 \leq T \leq m$ . The number of sequences of length T that end in T is  $K_T$  (1 if  $T \in S$ , 0 if  $T \notin S$ ). The number of sequences of length T that end in i is  $K_iN_K(T-i)$   $(N_K(T-i)$  if  $T \in S$ , 0 if  $T \notin S$ ). Hence,

<sup>&</sup>lt;sup>1</sup>If the symbols are not integers, they must be suitably scaled and truncated or rounded.

| $T_E = 5$                       | $T_E = 6$                        | $T_E = 7$                          |

|---------------------------------|----------------------------------|------------------------------------|

| $T_D = 2.73$                    | $T_D = 3.16$                     | $T_D = 3.63$                       |

| R = 1.83                        | R = 1.87                         | R = 1.92                           |

| $00 \leftrightarrow S_1$        | $00 \leftrightarrow S_1$         | $00 \leftrightarrow S_1$           |

| $010 \leftrightarrow S_3$       | $010 \leftrightarrow S_3$        | $010 \leftrightarrow S_4$          |

| $011 \leftrightarrow S_4$       | $011 \leftrightarrow S_4$        | $0110 \leftrightarrow S_6$         |

| $100 \leftrightarrow S_5$       | $100 \leftrightarrow S_5$        | $0111 \leftrightarrow S_7$         |

| $1010 \leftrightarrow S_6$      | $1010 \leftrightarrow S_6$       | $10000 \leftrightarrow S_2S_1$     |

| $1011 \leftrightarrow S_7$      | $1011 \leftrightarrow S_7$       | $10001 \leftrightarrow S_2S_2$     |

| $1100 \leftrightarrow S_2 S_1$  | $1100 \leftrightarrow S_2 S_1$   | $10010 \leftrightarrow S_3S_1$     |

| $11010 \leftrightarrow S_2S_2$  | $11010 \leftrightarrow S_2S_2$   | $10011 \leftrightarrow S_8$        |

| $11011 \leftrightarrow S_8$     | $11011 \leftrightarrow S_8$      | $10100 \leftrightarrow S_2S_3$     |

| $11100 \leftrightarrow S_2S_3$  | $11100 \leftrightarrow S_2S_3$   | $10101 \leftrightarrow S_3 S_2$    |

| $11101 \leftrightarrow S_2S_4$  | $11101 \leftrightarrow S_2S_4$   | $10110 \leftrightarrow S_3S_3$     |

| $11110 \leftrightarrow S_9$     | $11110 \leftrightarrow S_9$      | $10111 \leftrightarrow S_2S_4$     |

| $111111 \leftrightarrow S_2S_5$ | $1111110 \leftrightarrow S_2S_5$ | $11000 \leftrightarrow S_9$        |

|                                 | $1111111 \leftrightarrow S_2S_7$ | $11001 \leftrightarrow S_5 S_1$    |

|                                 |                                  | $110100 \leftrightarrow S_3 S_4$   |

|                                 |                                  | $110101 \leftrightarrow S_2S_5$    |

|                                 |                                  | $110110 \leftrightarrow S_5 S_2$   |

|                                 |                                  | $1101111 \leftrightarrow S_3S_5$   |

|                                 |                                  | $111000 \leftrightarrow S_5 S_3$   |

|                                 |                                  | $111001 \leftrightarrow S_{10}$    |

|                                 |                                  | $111010 \leftrightarrow S_2 S_6$   |

|                                 |                                  | $111011 \leftrightarrow S_5 S_4$   |

|                                 |                                  | $1111100 \leftrightarrow S_3 S_6$  |

|                                 |                                  | $1111010 \leftrightarrow S_2 S_7$  |

|                                 |                                  | $1111011 \leftrightarrow S_5 S_5$  |

|                                 |                                  | $11111100 \leftrightarrow S_3 S_7$ |

|                                 |                                  | $11111101 \leftrightarrow S_5 S_6$ |

|                                 |                                  | $11111110 \leftrightarrow S_3 S_8$ |

|                                 |                                  | $11111111 \leftrightarrow S_5 S_7$ |

Table 4.1: Code with  $S = \{1.00, 1.13, 1.27, 1.42, 1.60, 1.80, 2.03, 2.28, 2.57, 2.89\}$

| $T_E = 4$                  | $T_E = 6$                                                                                         | $T_E = 7$                                                                                                       |

|----------------------------|---------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| $T_D = 4.46$               | $T_D = 6.75$                                                                                      | $T_D = 7.70$                                                                                                    |

| R = 0.87                   | R = 0.89                                                                                          | R = 0.91                                                                                                        |

| $00 \leftrightarrow S_1$   | $00 \leftrightarrow S_1$                                                                          | $000 \leftrightarrow S_4$                                                                                       |

| $01 \leftrightarrow S_2$   | $010 \leftrightarrow S_4$                                                                         | $0010 \leftrightarrow S_6$                                                                                      |

| $100 \leftrightarrow S_3$  | $0110 \leftrightarrow S_6$                                                                        | $0011 \leftrightarrow S_1S_1$                                                                                   |

| $101 \leftrightarrow S_4$  | $0111 \leftrightarrow S_2 S_1$                                                                    | $0100 \leftrightarrow S_1 S_2$                                                                                  |

| $110 \leftrightarrow S_5$  | $1000 \leftrightarrow S_7$                                                                        | $0101 \leftrightarrow S_2 S_1$                                                                                  |

| $1110 \leftrightarrow S_6$ | $10010 \leftrightarrow S_2S_2$                                                                    | $01100 \leftrightarrow S_1S_3$                                                                                  |

| $1111 \leftrightarrow S_7$ | $10011 \leftrightarrow S_3S_1$                                                                    | $01101 \leftrightarrow S_3S_1$                                                                                  |

|                            | $10100 \leftrightarrow S_2S_3$                                                                    | $01110 \leftrightarrow S_2S_3$                                                                                  |

|                            | $10101 \leftrightarrow S_3S_2$                                                                    | $01111 \leftrightarrow S_3S_2$                                                                                  |

|                            | $10110 \leftrightarrow S_8$                                                                       | $10000 \leftrightarrow S_1 S_4$                                                                                 |

|                            | $10111 \leftrightarrow S_3S_3$                                                                    | $10001 \leftrightarrow S_8$                                                                                     |

|                            | $11000 \leftrightarrow S_2S_4$                                                                    | $10010 \leftrightarrow S_3S_3$                                                                                  |

|                            | $11001 \leftrightarrow S_5 S_1$                                                                   | $10011 \leftrightarrow S_2S_4$                                                                                  |

|                            | $11010 \leftrightarrow S_3 S_4$                                                                   | $10100 \leftrightarrow S_1 S_5$                                                                                 |

|                            | $110110 \leftrightarrow S_2S_5$                                                                   | $10101 \leftrightarrow S_5 S_1$                                                                                 |

|                            | $1101111 \leftrightarrow S_5 S_2$                                                                 | $101100 \leftrightarrow S_3 S_4$                                                                                |

|                            | $111000 \leftrightarrow S_9$                                                                      | $101101 \leftrightarrow S_2S_5$                                                                                 |

|                            | $111001 \leftrightarrow S_3S_5$                                                                   | $101110 \leftrightarrow S_5 S_2$                                                                                |

|                            | $\begin{array}{c} 111010 \leftrightarrow S_5 S_3 \\ 111011 & G.G. \end{array}$                    | $1011111 \leftrightarrow S_9$                                                                                   |

|                            | $\begin{array}{c} 111011 \leftrightarrow S_2S_6 \\ 111100 & G.G. \end{array}$                     | $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                          |

|                            | $\begin{array}{c} 1111100 \leftrightarrow S_5 S_4 \\ 1111101 \leftrightarrow S_5 S_4 \end{array}$ | $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                          |

|                            | $\begin{array}{c} 1111101 \leftrightarrow S_3S_6 \\ 1111110 \leftrightarrow S_3S_6 \end{array}$   | $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                          |

|                            | $\begin{array}{c} 1111110 \leftrightarrow S_{10} \\ 1111111 \leftrightarrow S_{10} \end{array}$   | $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                          |

|                            | $1111111 \leftrightarrow S_2S_7$                                                                  | $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                          |

|                            |                                                                                                   | $\begin{array}{ c c c c c }\hline 110101 \leftrightarrow S_1 S_7 \\ 110110 \leftrightarrow S_7 S_1 \end{array}$ |

|                            |                                                                                                   | $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                          |

|                            |                                                                                                   | $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                          |

|                            |                                                                                                   | $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                          |

|                            |                                                                                                   | $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                          |

|                            |                                                                                                   | $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                          |

|                            |                                                                                                   | $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                          |

|                            |                                                                                                   | $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                          |

|                            |                                                                                                   | $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                          |

|                            |                                                                                                   | $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                          |

|                            |                                                                                                   | $1111001 \leftrightarrow S_1 S_8$                                                                               |

|                            |                                                                                                   | $1111010 \leftrightarrow S_2 S_2 S_3$                                                                           |

|                            |                                                                                                   | $1111011 \leftrightarrow S_5 S_6$                                                                               |

|                            |                                                                                                   | $11111100 \leftrightarrow S_2S_8$                                                                               |

|                            |                                                                                                   | $11111101 \leftrightarrow S_7 S_4$                                                                              |

|                            |                                                                                                   | $11111110 \leftrightarrow S_2 S_2 S_4$                                                                          |

|                            |                                                                                                   | $11111111 \leftrightarrow S_3 S_8$                                                                              |

Table 4.2: Code with  $S = \{2.00, 2.29, 2.61, 2.99, 3.41, 3.90, 4.46, 5.09, 5.82, 6.65\}$

Figure 4.1: A Simple Interval Modulation Code Implemented Using Prefix Trees

$N_K(T) = K_T + \sum_{i=1}^{T-1} K_i N_K(T-i)$ . The proof for when T > m is similar and left as an exercise for the reader. It is easy to show that  $N_K$  is a generalization of the Fibonacci Numbers.

**Example 5** First consider the case when  $S = \{1, 2, 3\}$ . In this case m = 3 and  $K_1 = 1$ ,  $K_2 = 1$  and  $K_3 = 1$ . Using the recurrence above, we find  $N_K(5) = 13$ . The 13 sequences of length 5 are  $\{11111, 1112, 1121, 1211, 2111, 122, 212, 221, 113, 131, 311, 23, 32\}$ . Now consider the case when  $S = \{2, 3, 5\}$ . In this case m = 5 and  $K_1 = 0$ ,  $K_2 = 1$ ,  $K_3 = 1$ ,  $K_4 = 0$  and  $K_5 = 1$ . Using the recurrence above we find  $N_K(9) = 8$ . The 8 sequences of length 9 are  $\{2223, 2232, 2322, 3222, 333, 225, 252, 522\}$ .

Note that variable length to variable length prefix-free codes can be implemented using prefix trees. The coding technique outlined in the previous section for  $S = \{1, 2\}$  is implemented using prefix trees in Figure 4.1.

**Definition 6** For each leaf node x of the encoder tree T, let  $d_e(x)$  denote the length of the path from the root to x, called the "encoder delay" of x. Also, let  $d_d(x) =$

$x_1 + ... + x_n$ , where  $x_1, ..., x_n$  is in  $S^n$  is the label of x, called the "decoder delay" of x.

Let  $\max_x d_e(x)$  and let  $\max_x d_d(x)$  be called the "maximum encoder" and "maximum decoder" delays, respectively, taken over all leaf nodes x of the tree T. We will refer to these as  $T_E$  and  $T_D$  respectively. Also define the "rate" to be  $R = \min_x d_e(x)/d_d(x)$ .

Before we define the code construction problem and present a reduction to integer linear programming, we would like to prove a theorem.

**Notation 7**  $\Sigma_S^+$  is the set of non-null strings over S

For all  $s \in \Sigma_S^+$ , ||s|| is the sum of the elements in s

$$\Pi_{S}^{l} = \{ s | s \in \Sigma_{S}^{+} \text{ and } ||s|| = l \}$$

Assume  $p \in \Sigma_S^+$  and  $l \ge ||p||$ . We define  $P_A(p, l) = \{s | s \in \Sigma_S^+ \text{ and } ||s|| = l \text{ and } p$  is a prefix of  $s\}$

**Theorem 8** We are given  $M_S \subseteq \Sigma_S^+$  such that  $M_S$  is a prefix-free set. For all i let  $y_i = |\{s|s \in M_S \text{ and } ||s|| = i\}|.$

For all

$$n, y_n \le N_K(n) - \sum_{l=1}^{n-1} N_K(n-l)y_l$$

Furthermore, if we are given  $y_i$  such that they satisfy the constraints above, we can find  $M_S \subseteq \Sigma_S^+$  such that  $M_S$  is a prefix-free set and  $|\{s|s \in M_S \text{ and } ||s|| = i\}| = y_i$ .

**Proof.** We are given n. Define  $\bar{M}_S(n) = \{s | s \in M_S \text{ and } ||s|| < n \}$  and  $\bar{R}_S(n) = \{s | s \in M_S \text{ and } ||s|| = n \}$ .

Note that,

$$\bar{R}_S(n) \cup \bigcup_{s \in \bar{M}_S(n)} P_S(s, n) \subseteq \Pi_S^n$$

Hence,

$$\left| \bar{R}_S(n) \cup \bigcup_{s \in \bar{M}_S(n)} P_S(s, n) \right| \leq |\Pi_S^n|$$

It is easy to show that  $\bar{R}_S(n) \cap \bigcup_{s \in \bar{M}_S(n)} P_S(s,n) = \phi$  and since  $\bar{M}_S(n)$  is a prefix-free set for all  $s_1, s_2 \in \bar{M}_S(n), P_S(s_1,n) \cap P_S(s_2,n) = \phi$ .

Hence,

$$|\bar{R}_{S}(n)| + \sum_{s \in \bar{M}_{S}(n)} |P_{S}(s, n)| \leq |\Pi_{S}^{n}|$$

Hence,

$$y_n \le N_K(n) - \sum_{l=1}^{n-1} N_K(n-l)y_l$$

The proof of the converse is constructive. Note that  $y_1 \leq N_K(1) = K_1$ . If  $K_1 = 0$ , let  $M_S = \{\}$  and if  $K_1 = 1$ , let  $M_S = \{1\}$ . Now we will assume that we have constructed a prefix-free set such that for  $i \in \{1, ..., n-1\}$ ,  $|\{s|s \in M_S \text{ and } ||s|| = i\}| = y_i$ .

Note that,

$$y_n \leq N_K(n) - \sum_{l=1}^{n-1} N_K(n-l)y_l$$

Now let

$$U = \prod_{S=0}^{n} - \bigcup_{s \in M_S} P_S(s, n)$$

Hence,

$$|U| = \left| \prod_{S=M_S}^n P_S(s, n) \right|$$

First note that  $\bigcup_{s \in M_S} P_S(s, n) \subseteq \Pi_S^n$ . Also note that since  $M_S(n)$  is a prefix-free set for all  $s_1, s_2 \in M_S(n), P_S(s_1, n) \cap P_S(s_2, n) = \phi$ .

Hence,

$$|U| = N_K(n) - \sum_{l=1}^{n-1} N_K(n-l)y_l$$

Hence,  $y_n \leq |U|$ . It suffices to pick  $y_n$  elements from U and add them to  $M_S$ .

**Problem 9** Given numbers  $T_E$ ,  $T_D$ , and R, and a set of positive integers S, find a tree T with the fewest possible leaves such that the maximum encoder delay is  $T_E$ , the maximum decoder delay is  $T_D$ , the rate is at least R, and the labels of the leaves form a prefix-free set over S.

For  $l \in \{1, 2, ..., T_D\}$  and  $d \in \{1, 2, ..., T_E\}$ , let  $x_d^l$  be the number of leafs (non negative integer) in the encoder tree at depth d which have a label of length l. Also, we define  $x^l$  to be the number of labels of length l and we define  $x_d$  to be the number of leafs in the encoder at depth d. Formally,

$$x^{l} = \sum_{i=1}^{T_{E}} x_{i}^{l} \text{ and } x_{d} = \sum_{i=1}^{T_{D}} x_{d}^{i}$$

(4.3)

The problem is to design the smallest encoder decoder pair. So we would like to,

$$\min \sum_{i=1}^{T_D} \sum_{j=1}^{T_E} x_j^i \tag{4.4}$$

Firstly, since the encoder tree is a full prefix tree, the Kraft Inequality for full trees, tells us that

$$\sum_{i=1}^{T_E} 2^{(T_E - i)} x_i = 2^{T_E} \tag{4.5}$$

Furthermore the labels attached to the leaf nodes of the encoder tree must form a prefix-free set over S. Equivalently, the decoder must be a prefix tree. From Theorem 8 we know that,

For

$$1 \le L \le T_D$$

,  $x^L + \sum_{l=1}^{L-1} N_K(L-l)x^l \le N_K(L)$  (4.6)

Also the encoder and decoder must achieve a rate of R. Hence,

$$j/i < R \Longrightarrow x_i^i = 0 \tag{4.7}$$

It is easy to verify that equations (4.5,4.6,4.7) are also sufficient. If we are given  $x_j^i$  which satisfy these constraints we can construct a code which achieves the desired rate and has the specified delays. Since equation (4.5) is satisfied, the Kraft inequality for full binary trees tells us that we can construct a full binary tree such that the number of leafs at depth i is  $x_i$ . Since equation (4.6) is satisfied, Theorem 8 tells us

that we can find a prefix-free set  $M_S$  over S such that the number of labels in  $M_S$  of length l is  $x^l$ . We can now arbitrarily assign  $x_j^i$  labels of length i from the set  $M_S$  to leaf nodes of the encoder tree at depth j in a one on one manner.

#### 4.3 Linear Programming Relaxation

Equations (4.4,4.5,4.6,4.7) represent an integer linear program. Equations (4.4,4.5,4.6,4.7) without the integrality constraint are the linear programming relaxation of the integer linear program. Although the solution to the linear programming relaxation does not provide a code, it does provide a lower bound on the size of the optimal code. In this chapter we will present a polynomial time<sup>2</sup> algorithm for finding an optimal solution to the linear programming relaxation, if one exists. We next formulate a necessary and sufficient condition for the linear programming relaxation to have a solution.