## Analog Models for Early Vision

Thesis by

John G. Harris

California Institute of Technology

Pasadena, California

1991

(Defended May 30, 1991)

©1991

John G. Harris

All rights reserved

# Acknowledgments

- Thanks to Christof for many things, especially for his rapid-fire ideas and the constant enthusiasm he exudes. Thanks also to the rest of Koch Lab for help and comfort over the years. Research in the Koch lab is funded by a National Science Foundation grant IST-8700064, DDF-II funds from the Jet Propulsion Laboratory at the California Institute of Technology, Office of Naval Research Young Investigator and National Science Foundation Presidential Young Investigator Awards, the James S. McDonnell Foundation, Rockwell International Science Center and the Hughes Aircraft Artificial Intelligence Center. Thanks also to the Hughes AI Center for supporting me with a fellowship during my years at Caltech.

- Of course, none of this would have been possible without Carver for laying the framework upon which this research has been built. He serves as a model for us all to follow. Thanks also to everyone in Carver's lab for their help during my years at Caltech. Hewlett-Packard provided computing support. All chips were fabricated through MOSIS with DARPA's support.

- My thesis committee (Christof, Carver, Al Barr, David Van Essen, and Rod Goodman) provided valuable criticism. Candi Hochenedel and Andy Moore graciously read earlier drafts of this thesis. Jin Luo helped with the fuse chip and especially for built the hardware for scanning data on and off the chip. Thanks to Massimo Sivilotti for writing many of the Latex macros which were used in formatting this thesis. Mass

also wrote WoL, the VLSI layout editor that was used to design all the chips in this thesis. Thanks to Shih-Chii Liu, Bimal Mathur, and John Wyatt for many collaborations during this work. John Wyatt pointed out the theorems dealing with stability and uniqueness of nonlinear resistive networks.

- Thanks to my mother and father for their constant love and encouragement. They have taught me and my brothers the value of education.

- Finally, I thank Anita for bringing so much happiness to my life.

## Abstract

Analog models provide a novel framework for understanding and developing algorithms for computer vision. This thesis introduces several extensions to well-known resistive network techniques for solving early vision problems. First, constraint boxes are developed as a general methodology for mapping regularization-based algorithms onto stable analog hardware. These multiterminal resistor systems solve low-level vision problems by minimizing a global Lyapunov energy. Second, a circuit element called the resistive fuse is introduced to extend these networks for discontinuity detection. This is the first hardware circuit that explicitly implements line-process discontinuities. Since resistive fuse networks must minimize a non-convex energy function that may contain local minima, complex annealing or continuation methods are necessary for adequate solutions of the problem. Third, the tiny-tanh network is proposed as a new mechanism for discontinuity detection that is not plagued by problems with local minima. A piece-wise constant segmentation is performed through minimization of a convex Lyapunov energy.

# Contents

|   | Ack  | nowledgments                            | iii |

|---|------|-----------------------------------------|-----|

|   | Abs  | stract                                  | v   |

| 1 | Intr | roduction                               | 1   |

|   | 1.1  | Analog Models                           | 3   |

|   | 1.2  | Regularization Theory                   | 4   |

|   | 1.3  | Resistive Networks                      | 6   |

|   | 1.4  | Stability                               | 8   |

|   | 1.5  | Uniqueness                              | 10  |

| 2 | Cor  | nstraint Boxes                          | 12  |

|   | 2.1  | Single Constraint Boxes                 | 13  |

|   | 2.2  | Networks of Constraint Boxes            | 14  |

|   | 2.3  | Examples of Constraint boxes            | 16  |

|   |      | 2.3.1 The Resistor                      | 16  |

|   |      | 2.3.2 The Subtraction Constraint Box    | 17  |

|   |      | 2.3.3 The Multiplication Constraint Box | 19  |

|   | 2.4  | Exact Constraint Boxes                  | 22  |

| 3 | Cou  | pled Depth/Slope Network                | 24  |

|   | 3.1  | Coupled Depth/Slope                     | 24  |

|   | 3.2            | Hardware Implementation                      | 27         |  |  |

|---|----------------|----------------------------------------------|------------|--|--|

|   | 3.3            | Constrained Optimization Approach            | 31         |  |  |

| 4 | Resistive Fuse |                                              |            |  |  |

|   | 4.1            | Line Processes                               | 33         |  |  |

|   | 4.2            | Resistive Fuse Theory                        | <b>3</b> 6 |  |  |

|   | 4.3            | Hardware Implementation                      | 39         |  |  |

|   | 4.4            | Segmentation Performance                     | 47         |  |  |

|   | 4.5            | Annealing Schedules and Continuation Methods | 49         |  |  |

|   | 4.6            | Alternate Hardware Implementations           | 59         |  |  |

|   | 4.7            | Constraint Fuses                             | 62         |  |  |

|   | 4.8            | Time Fuse                                    | 67         |  |  |

| 5 | The            | e Tiny Tanh Network                          | 73         |  |  |

|   | 5.1            | Convex Energy for Segmentation               | 73         |  |  |

|   | 5.2            | Simulation                                   | <b>7</b> 6 |  |  |

|   | 5.3            | An Application to Stereo                     | 81         |  |  |

|   | 5.4            | Step Response                                | 82         |  |  |

|   | 5.5            | Hardware Implementation                      | 86         |  |  |

|   | 5.6            | Segmentation Results                         | 90         |  |  |

|   | 5.7            | Piece-wise Linear Segmentation               | 92         |  |  |

| 6 | Conclusions 9- |                                              |            |  |  |

|   | 6.1            | Why Analog Models?                           | 95         |  |  |

|   | 6.2            | Future Directions                            | 97         |  |  |

| R | efere          | nces                                         | 99         |  |  |

## Chapter 1

## Introduction

This thesis studies analog models for early vision. These analog models are an active research topic for two reasons. First, we want to build artificial vision systems for use in robotics, factory automation, parts inspection, and other industrial applications. These analog models are useful because they lead toward fast, low-power analog VLSI hardware. Second, we study these models in order to understand the information processing tasks necessary for artificial and biological vision systems.

Analog models provide a novel framework for understanding and developing algorithms for computer vision. This thesis describes examples of analog networks for several early vision problems such as image and depth segmentation. Many real-world applications become feasible because of the speed, size, cost, and power consumption of these networks. Besides these advantages, however, experimentation with continuous-time nonlinear circuits has led to some fundamental insights relevant to computer vision. Powerful analog algorithms thus developed may prove useful even if a computer vision researcher is limited to simulating the analog hardware on a digital computer.

The outline of this thesis is as follows:

- Chapter 1 introduces regularization theory and resistive networks.

- Chapter 2 develops constraint boxes as a general methodology for mapping regulari-

zation based algorithms to stable analog hardware. These systems find a solution by minimizing a global convex Lyapunov energy. Convexity implies that there are no other stable points in the energy surface other than a single global minimum.

- Chapter 3 describes an experimental analog VLSI chip for smooth surface interpolation from sparse depth data. Subtraction constraint boxes are used to enforce a second-order or "thin-plate" smoothness constraint on the data. This algorithm, as well as most regularization-based approaches, oversmoothes discontinuities.

- Chapter 4 describes the resistive fuse, the first hardware circuit that explicitly implements line process discontinuities. A two-dimensional fuse circuit successfully segments data which is scanned into the chip. However, resistive fuse networks must minimize a non-convex energy function that may contain local minima. As in computer vision, complex annealing or continuation methods are necessary for adequate solutions of the problem.

- Chapter 5 discusses an entirely new way of dealing with discontinuities that is not

plagued by problems with local minima. The tiny-tanh network smoothes and segments data by minimizing a convex energy functional. The tiny-tanh approach is

demonstrated in analog hardware.

- Chapter 6 speculates on some future directions of this work and summarizes the thesis.

Several subthreshold CMOS circuits are shown and described in this thesis. Rather than provide an exhaustive tutorial on this subject, the reader is strongly recommended to review Mead's excellent textbook on analog VLSI and neural systems [Mead, 1989]. (See also [Vittoz, 1985]). Furthermore, since the emphasis of this thesis has been the development of new algorithms, much can be learned by readers totally unfamiliar with analog VLSI. The ideas developed here have utility independent of any particular implementation technology.

#### 1.1 Analog Models

Analog computation is not a new concept. In the 1950s, electronic analog computers were widely used to solve many types of mathematical problems, especially ordinary differential equations and boundary-value problems (for example, see [Karplus, 1958] or [Levine, 1964]). These analog systems provided a faster and cheaper solution to these problems than the crude digital systems of the day. Digital computers were required whenever greater accuracy was needed than the accuracy analog computers could provide.

The idea of using analog circuits for solving vision problems was explicitly stated by Horn, when he proposed the use of a grid of resistors to find the inverse of the discrete approximation to the thresholded Laplacian [Horn, 1974]. Later, Knight built an analog network for convolving an image with a Difference-of-Gaussian filter. Gaussian convolution was implemented using a resistor-capacitor network [Knight, 1983]. As charge diffused according to the diffusion equation, the diffusion time determined the width of the Gaussian.

Knight also proposed a MOS switching network that alternately opened switches to share charge in the horizontal and vertical directions [Knight, 1983]. This network implemented a binomial approximation to a Gaussian. A similar idea was implemented by Sage in a CCD process [Sage, 1984] [Sage and Lattes, 1987]. After an image was acquired by an on-chip imager, it was shifted to a convolver portion of the chip. Charge would then be alternately shared in the x and y directions until the correct amount of smoothing was performed. Yang implemented the same binomial approximation by efficiently performing these charge sharing operations as the image was being shifted out [Yang, 1990].

Poggio and Koch [1985] show how standard regularization algorithms map onto resistive networks. Exploiting Kirchhoff's and Ohm's law, they proved that the minimum of the regularized, quadratic cost functional is equivalent to the state of least power dissipation in an appropriate linear resistive network, where the data are given by injecting current into certain nodes and the solution by the stationary voltage distribution. For an overview of the use of analog circuits for early vision, see [Koch, 1989] and [Horn, 1988].

The work in this thesis relies upon the pioneering development of subthreshold, analog CMOS VLSI circuits for various sensory tasks by Carver Mead [Mead, 1989]. Mead is interested in understanding biological systems, and he and coworkers have developed numerous silicon models including the retina [Mead and Mahowald, 1988] [Mead, 1989], the cochlea [Lyon and Mead, 1988], and a circuit for auditory localization [Lazzaro and Mead, 1989]. Since analog VLSI circuits operate under many of the same power and communication restrictions imposed upon their biological counterparts, it is hoped that the silicon models will provide insights into these biological information processing systems.

#### 1.2 Regularization Theory

Numerous problems in early vision are ill-posed [Poggio et al., 1985]. A problem is well-posed if its solution

- 1. exists,

- 2. is unique, and

- 3. depends continuously on the data.

A problem is ill-posed if it fails at least one of the above criteria. For example, many edge detection techniques amount to thresholding the magnitude of some sort of derivative of intensity data. Since derivatives amplify noise in the signal, edge detection is ill-posed because the result does not depend continuously on the data.

Consider

$$d = Au \tag{1.1}$$

where A is a known operator. We must solve the inverse problem of finding u from the measured data d which is typically ill-posed. Of course, the forward problem of finding d from u is straightforward and well-posed since A is known. The idea behind regularization is to use a priori information to constrain the problem in such a way that there is only one

unique solution that depends continuously on the data. Typically, an energy functional is created that consists of two terms. The data term forces the solution to be close to the data and the stabilizing term imposes constraints (such as smoothness) upon the solution. The solution u is the function that minimizes

$$||Au - d||^2 + \lambda ||Pu||^2 \tag{1.2}$$

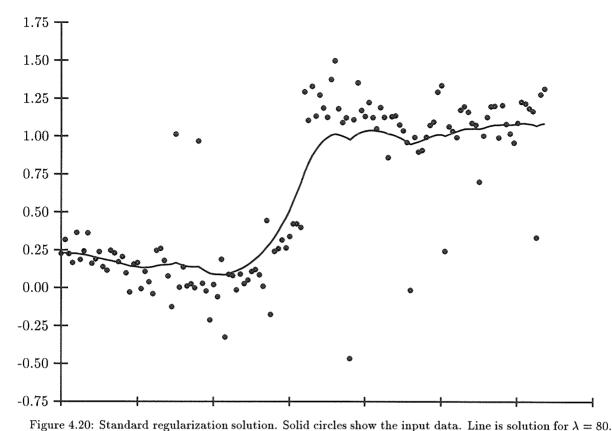

where the norms are usually quadratic and the stabilizing functional ||Pu|| is typically a smoothness assumption. The regularization parameter  $\lambda$  controls the tradeoff between closeness of the solution to the data versus the degree of regularization. Many early vision algorithms can be described as examples of regularization even though most of these algorithms were developed before the unifying theory of regularization was applied to vision. Examples exist in stereo [Marr and Poggio, 1976], surface interpolation [Grimson, 1981] [Terzopoulos, 1983], optical flow [Horn and Schunck, 1981] [Hildreth, 1984], shape from shading [Ikeuchi and Horn, 1981], and edge detection [Poggio et al., 1986].

We will use surface interpolation as a problem to study regularization theory and analog networks. Reconstructing a surface from sparse sensory data is a well-known problem in computer vision. Early vision modules typically supply sparse depth, orientation, and discontinuity information. The surface reconstruction module incorporates these sparse and possibly conflicting measurements of a surface into a consistent, dense depth map. Suppose sparse and noisy data  $d_i$  are sampled randomly from a surface u. Since there are infinitely many surfaces u that could have led to these depth measurements, the problem is ill-posed. The usual regularizing method is to pick a stabilizing functional that enforces smoothness. If we use quadratic norms in Equation 1.2, we must minimize the following energy functional E(u) with respect to all possible functions u:

$$E(u) = \int G(x) (d(x) - u(x))^2 dx + \lambda \int (u')^2 dx$$

(1.3)

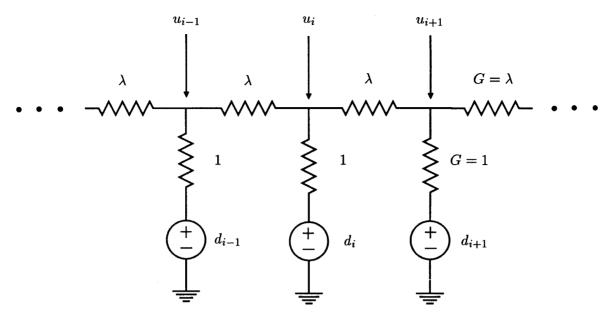

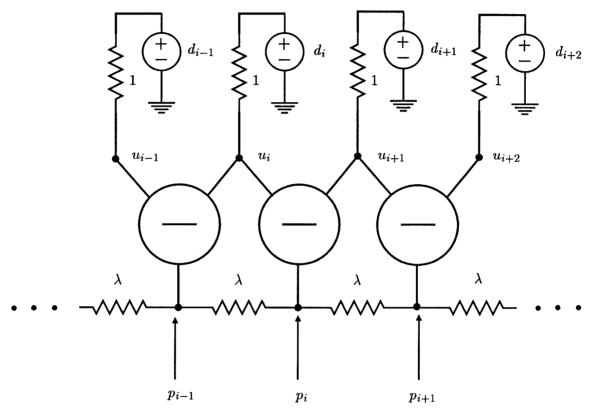

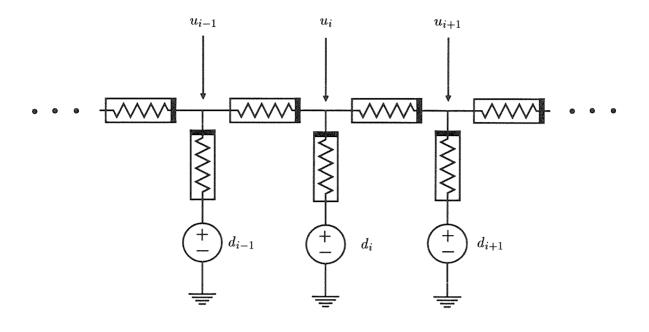

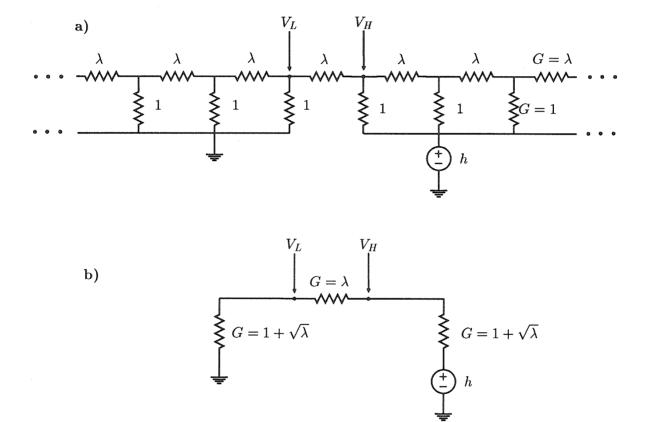

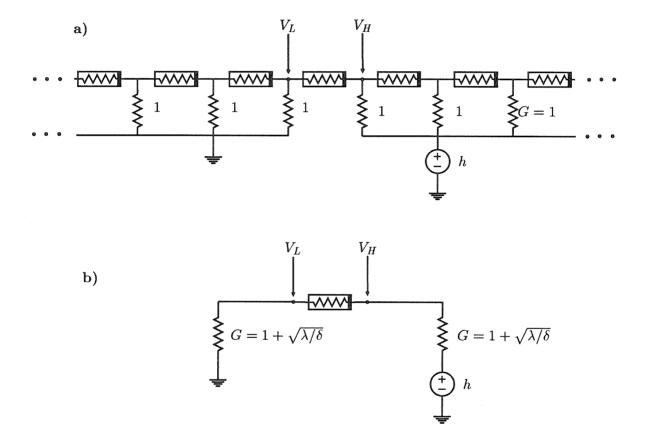

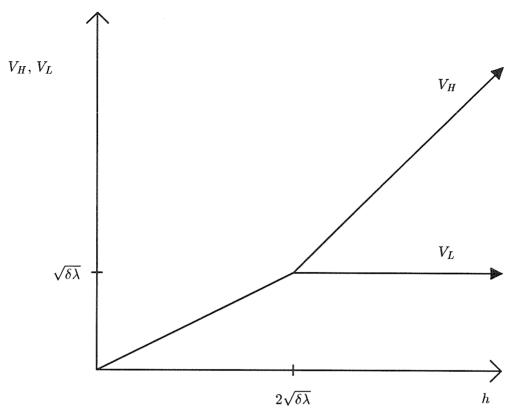

Figure 1.1: Resistive network for smoothing or interpolation. Data values  $d_i$  are supplied by voltage sources connected to the network with unity conductance resistors. Resistors with conductance  $\lambda$  implement the smoothness assumption. The stationary voltage values  $u_i$  are the smoothed outputs of the network.

It is assumed throughout this thesis that G(x) = 1. In discrete form, this equation turns into

$$E(u) = \sum_{i} (d_i - u_i)^2 + \lambda \sum_{i} (u_{i+1} - u_i)^2$$

(1.4)

The first term ensures that the solution will be close to the data while the second term implements the smoothness constraint. Minimizing this term forces neighboring  $u_i$  to be similar. The typical approach in computer vision is to discretize time and repeatedly descend the gradient of the energy until a solution is found. This procedure is time-consuming even on the most powerful parallel computers. The next section describes an analog circuit that provides a continuous-time solution to this problem.

#### 1.3 Resistive Networks

Consider the circuit shown in Figure 1.1. Noisy input data are provided as voltages  $d_i$  and the smoothed output values given by the voltages  $u_i$ . Resistors with conductance  $\lambda$  connect each  $u_i$  value with its neighbors. The total power dissipated by these resistors in the network

is equal to  $\lambda \sum (u_{i+1} - u_i)^2$ , which is identical to the second term of Equation 1.4. Unity conductance resistors couple  $u_i$  to  $d_i$  and the power dissipated by these resistors is identical to the first term in Equation 1.4. Therefore, the network dissipates exactly the power given by Equation 1.4. According to Maxwell's minimum heat theorem [Maxwell, 1891], the stationary voltage distribution is the solution to the minimization problem. Since all the resistors are linear, the node voltages are guaranteed to converge to a single unique set of values that minimize the total power dissipation of the circuit.

Resistor networks of this sort have a long history. Kirchoff [1845] describes what was probably the first conductive sheet system using a thin sheet of copper [Karplus, 1958]. Later, Kayan built an electrical model of thermal conducting systems using conducting paper [Kayan, 1945]. These metallic sheet simulations were hampered by the difficulty of obtaining uniform resistivity throughout the sheet. Evidently, it was difficult to reduce mismatches to below 10%. Karplus describes systems that use high-grade paper which reduced variations to below 2%. Numerous systems have been constructed using various materials such as metallic screens, conductive fabrics, conductive paint on glass, graphite and wax models, and even conductive liquids. Later researchers used lumped circuit elements to approximate the continuous field properties of conductive sheets. Depack [1947] and Redshaw [1948] present some of the first published reports of successful solutions of Laplace's and Poisson's equation using this technique.

A hexagonal extension of the 1-D network shown in Figure 1.1 has been built in analog VLSI [Koch et al., 1990b] [Luo et al., 1989]. This 48x48 pixel network successfully performs interpolation and smoothing of noisy and possibly sparse data. This network used Mead's saturating resistor as its resistor element. This device is often called HRES (Horizontal RESistor) since it was originally designed to model the horizontal cells in the mammalian retina [Mead, 1989]. The I-V curve of this resistor is linear for small voltage drops and

<sup>&</sup>lt;sup>1</sup>Interestingly, because of the high resistivity of paper compared to graphite, equipotential regions could be specified by drawing pencil lines on the paper.

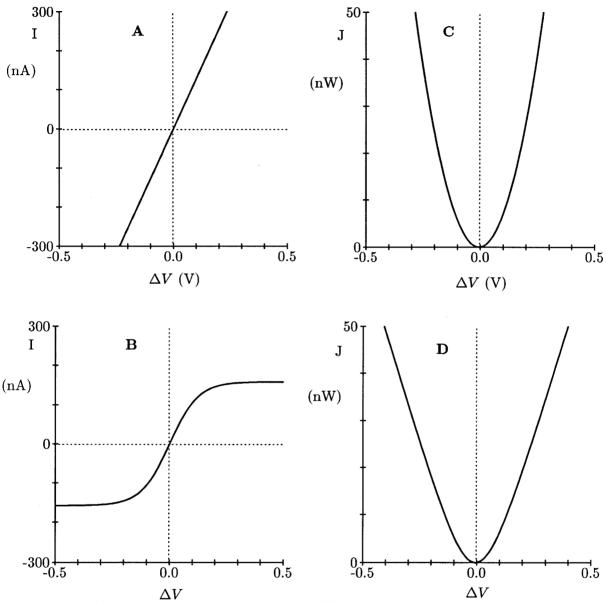

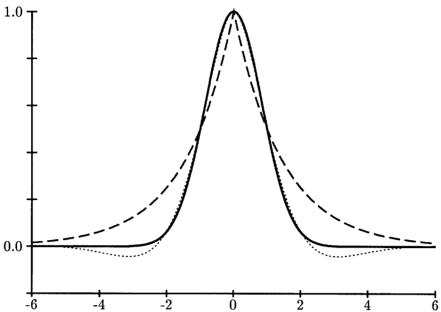

saturates for large voltage drops. The slope of the linear region, i.e., the conductance for small voltage drops, can be varied over five orders of magnitude. The measured I-V curve has the form of a hyperbolic tangent as shown in Figure 1.2B. The next section discusses the implications of using nonlinear resistors, such as Mead's saturating resistor, on network stability and uniqueness.

### 1.4 Stability

Stability is an important issue to address in these analog models. Wyatt and Standley show how oscillations may occur when stable elements are coupled together with a resistive network [Wyatt et al., 1989]. They give criteria for guaranteeing the stable design of such systems. Since we are constructing devices out of highly nonlinear transistor building blocks, stability and uniqueness are pertinent issues.

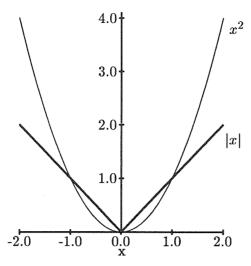

As pointed out by Poggio and Koch [Poggio and Koch, 1984], the notion of minimizing power in linear networks implementing quadratic "regularized" algorithms must be replaced by the more general notion of minimizing the total resistor co-content [Millar, 1951] for nonlinear networks. For a voltage-controlled resistor characterized by I = f(V), the co-content is defined as

$$J(V) = \int_0^V f(V')dV'$$

(1.5)

For a linear resistor, I = GV, the co-content is given by  $\frac{1}{2}GV^2$ , which is just half the dissipated power  $P = GV^2$ . The co-content for linear and saturating resistors is plotted in Figure 1.2.

If the *internal* dynamics of the incrementally active resistor circuit are neglected (that is, if we neglect the fact that our circuits consist of transistors with their own, relatively fast, temporal behavior), for any voltage input and any initial condition a purely passive resistive network will *not* oscillate indefinitely but must eventually settle to *some* stationary state (for more general stability results, see [Wyatt et al., 1989]). Purely passive means

Figure 1.2: Theoretical I-V curves for a linear resistor (A) and a measured I-V curve for Mead's saturating resistor (B). Integrating numerically over these curves gives the co-content of the linear resistor (C) and the saturating resistor (D). Co-content is defined by Equation 1.5 and represents generalized power for nonlinear systems. The co-content for the linear resistor is equivalent to half the dissipated power, and thus a quadratic function in  $\Delta V$ , while the co-content for the saturating resistor becomes a linear function of  $\Delta V$  as  $|\Delta V| \to \infty$ .

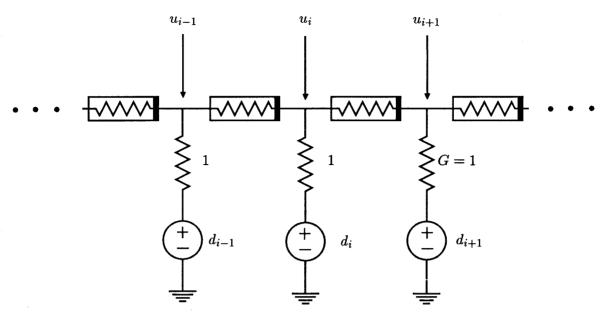

Figure 1.3: Nonlinear resistive network for smoothing or interpolation. The smoothing resistors in Figure 1.1 have been replaced by nonlinear resistors.

that each resistor's I-V curve only passes through the first and third quadrants as well as the origin. In other words, all resistive elements must dissipate power and no energy can be created. This conclusion holds even if parasitic (nonlinear but positive) capacitors are distributed arbitrarily throughout the network, provided there are no inductors. The total co-content of all resistors will act as a Lyapunov function [Harris et al., 1989].

### 1.5 Uniqueness

Given that nonlinear resistive networks can be shown to converge to a stable state under certain conditions, what can be said about the uniqueness of this stable state for arbitrary nonlinear resistive networks? It can be shown that a network of arbitrary topology consisting of strictly incrementally passive resistors (i.e., where dI/dV > 0 for all V) and ideal voltage and current sources has at most one solution, given by the unique minimum of the co-content [Harris et al., 1989]. This theorem first appeared in [Duffin, 1947]; see also [Birkhoff and Diaz, 1956]. found Α more recent treatment can be in [Hasler and Neirynck, 1986] or [Chua et al., 1987].

In the network shown in Figure 1.3, each node is connected to exactly two nonlinear resistors and one linear resistor. Suppose the nonlinear resistors are described by an arbitrary nonlinear function I = f(V). The co-content of the system is given by

$$J(u) = \frac{1}{2} \sum_{i} (u_i - d_i)^2 + \sum_{i} \int_0^{u_{i+1} - u_i} f(V) dV$$

(1.6)

For a network consisting of passive nonlinear resistive elements, a sufficient condition to guarantee a unique stationary network solution is

$$\frac{\partial^2 J}{\partial u_i^2} > 0 \tag{1.7}$$

for all  $u_i$ . This implies:

$$1 + f'(u_i - u_{i+1}) + f'(u_i - u_{i-1}) > 0 (1.8)$$

In the worst case, this condition is satisfied if f'(V) > -1/2 for all values of V. For the 2D Cartesian case f'(V) > -1/4 for all values of  $\Delta v$ . For sparse data, or an arbitrarily connected nonlinear resistive network, this condition reduces to requiring the sign of the derivative of the I-V characteristic to be strictly positive. Because the I-V curve of Mead's saturating resistor has the form  $I = I_0 \tanh(V/V_0)$  [Mead, 1989], its derivative is always positive. Thus, replacing ideal linear resistors with Mead's saturating resistors will not cause additional solutions to appear. This treatment again neglects the possible effect of the internal dynamics of the saturating resistor on the stability of the network.

We have shown how resistive elements implement the smoothness constraint required for regularizing ill-posed problems in early vision. The next chapter discusses constraint boxes that are analog models for implementing more powerful constraints.

## Chapter 2

## Constraint Boxes

This chapter introduces constraint boxes—a useful mechanism for solving computational problems that also provides a direct mapping to stable analog VLSI circuits.<sup>1</sup> This chapter introduces a theory of constraint boxes that can be used to implement powerful constraints that are useful in early vision.

Analog networks that solve most regularizable early vision problems can be designed with networks consisting solely of linear resistances and batteries [Poggio and Koch, 1985]. Unfortunately, many times these networks contain negative resistances that are troublesome to implement in analog hardware. Also, battery values may be complex functions (i.e., products or quotients) of measurable image quantities. This chapter proposes a new way of implementing the resulting analog networks using a theory of least-squares constraint boxes. Using constraint boxes, all nominal resistance values are data-independent and input voltages are relevant image quantities.

These least-square constraint boxes are contrasted with the "exact" constraint methods used in constrained optimization problems [Platt, 1990] [Arrow et al., 1958].

<sup>&</sup>lt;sup>1</sup>Portions of this chapter have already been published [Harris, 1988] [Harris, 1989].

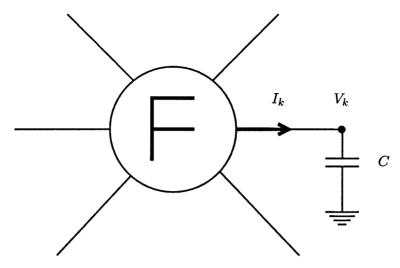

Figure 2.1: A generic constraint box enforces a constraint F on its voltage terminals. For the kth voltage terminal, a current  $I_k$  is generated that tends to push the voltage  $V_k$  in the direction which best satisfies the constraint F. The capacitor is added to provide dynamics to the system.

### 2.1 Single Constraint Boxes

A constraint box such as the one shown in Figure 2.1 imposes a constraint on the voltages of its terminals. A general constraint is given by

$$F(V_1, V_2, ...V_i ....V_n) = 0 (2.1)$$

$V_i$  represents the voltage at the *i*th terminal. Intuitively, the constraint box senses the voltages at its terminals and feeds back currents that drive the voltages in the right directions to satisfy the constraint. The current supplied by the constraint box to the *i*th voltage terminal is

$$I_i = C \frac{dV_i}{dt} = -\frac{\partial F}{\partial V_i} FG \tag{2.2}$$

where G is an arbitrary constant that reflects the "conductance" of the constraint box. C is the capacitance at each node. We will assume C=1 without loss of generality. It will be shown that for this choice of currents given by Equation 2.2 the constraint box minimizes an energy of

$$E = \frac{1}{2}GF^2 \tag{2.3}$$

which is the square error in the constraint equation scaled by the conductance G.

To prove this, take the time derivative of the energy and show that it is always decreasing:

$$\frac{dE}{dt} = \frac{1}{2}G\frac{d}{dt}F^2 \tag{2.4}$$

$$= GF\frac{dF}{dt} \tag{2.5}$$

By using the chain rule,

$$\frac{dE}{dt} = GF \sum_{i} \frac{\partial F}{\partial V_i} \frac{dV_i}{dt}$$

(2.6)

$$= -\sum_{i} \left(\frac{dV_i}{dt}\right)^2 \tag{2.7}$$

since  $dV_i/dt = -(\partial F/\partial V_i)FG$  from Equation 2.2. Thus dE/dt is always negative (or zero) and therefore E is always decreasing (or stationary). If G is always positive, the energy  $E \geq 0$  and therefore is bounded. G and the capacitance at each node determine the speed of convergence of a single constraint box. We can force a constraint box to obey Kirchhoff's current laws by constraining all of the currents into the constraint box to sum to zero, i.e.,  $\sum I_i = 0$ . This may require adding an extra terminal to the constraint box.<sup>2</sup>

### 2.2 Networks of Constraint Boxes

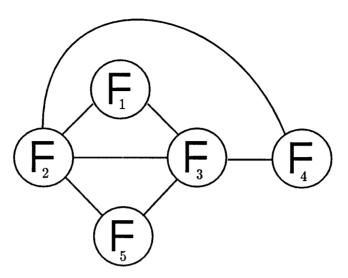

Imagine the arbitrary network of constraint boxes shown in Figure 2.2. The constraint enforced by the *j*th constraint can be written as

$$F_j(V_1, V_2, ...V_i ....V_n) = 0 (2.8)$$

$V_i$  represents the voltage at the *i*th terminal of the *j*th constraint box. The constraint box current equation gives the current to the *i*th voltage terminal from the *j*th constraint box

<sup>&</sup>lt;sup>2</sup>Actual constraint box implementations in CMOS will generally require additional connections to power and ground.

Figure 2.2: Arbitrary network of constraint boxes. It is shown in the text that any arbitrary collection of constraint boxes minimizes the sum of the squares of the errors in all of the constraints.

as

$$I_{ij} = -\frac{\partial F_j}{\partial V_i} F_j G_j \tag{2.9}$$

The constant  $G_j$  is the conductance of the jth constraint box. By Kirchhoff's current law, the total current supplied to node j equals the sum of all the currents supplied by the constraint boxes, so

$$C\frac{dV_i}{dt} = I_i = \sum_j I_{ij}$$

$$= -\sum_j \frac{\partial F_j}{\partial V_i} F_j G_j \qquad (2.10)$$

The total energy minimized will be the weighted sum of the squares of all of the constraint equations. Therefore,

$$E = \frac{1}{2} \sum_{j} G_j F_j^2 \tag{2.11}$$

Taking the time derivative of this energy yields

$$\frac{dE}{dt} = \frac{1}{2} \sum_{j} G_j \frac{d}{dt} (F_j)^2 \tag{2.12}$$

$$= \sum_{j} G_j F_j \frac{dF_j}{dt} \tag{2.13}$$

$$= \sum_{i} G_{j} F_{j} \sum_{i} \frac{\partial F_{j}}{\partial V_{i}} \frac{dV_{i}}{dt}$$

(2.14)

because of the chain rule. Substituting in Equation 2.10 (assuming C=1) and rearranging gives

$$\frac{dE}{dt} = \sum_{i} \frac{dV_{i}}{dt} \sum_{j} G_{j} F_{j} \frac{\partial F_{j}}{\partial V_{i}}$$

$$= -\sum_{i} (\frac{dV_{i}}{dt})^{2} \tag{2.15}$$

which is always negative or zero. Therefore, a network of constraint boxes minimizes the weighted sum of the squares of all of the constraint equations utilizing simple gradient descent.

### 2.3 Examples of Constraint boxes

#### 2.3.1 The Resistor

One of the simplest constraints to enforce is A = B, where A and B are the voltages of two nodes in a network. Of course, a simple method for enforcing this constraint exactly is to hook a wire from A to B, but this method does not generalize for more complicated constraints and does not degrade gracefully with conflicting constraints. The constraint we wish to enforce can be rewritten as

$$F(A,B) = A - B = 0 (2.16)$$

Applying the constraint box current rule gives

$$I_A = -GF \frac{\partial F}{\partial A} = -G(A - B)$$

$I_B = -GF \frac{\partial F}{\partial B} = G(A - B)$  (2.17)

Notice that these currents are exactly those that would be supplied by a resistor with conductance G connecting A to B. Therefore, the resistive networks discussed in Chapter 1 are a special case of these constraint box networks.

#### 2.3.2 The Subtraction Constraint Box

The next chapter discusses a surface interpolation scheme that requires an element that enforces the constraint that A - B = C - D, which leads to the following error equation:

$$F(A, B, C, D) = (A - B) - (C - D) = 0 (2.18)$$

Assuming that G = 1 and applying constraint box theory yields

$$I_{A} = -F\frac{\partial F}{\partial A} = -(A - B) + (C - D)$$

$$I_{B} = -F\frac{\partial F}{\partial B} = (A - B) - (C - D)$$

$$I_{C} = -F\frac{\partial F}{\partial C} = -(A - B) + (C - D)$$

$$I_{D} = -F\frac{\partial F}{\partial D} = (A - B) - (C - D)$$

where  $I_A$ ,  $I_B$ ,  $I_C$  and  $I_D$  represent feedback currents that must be generated by the device.

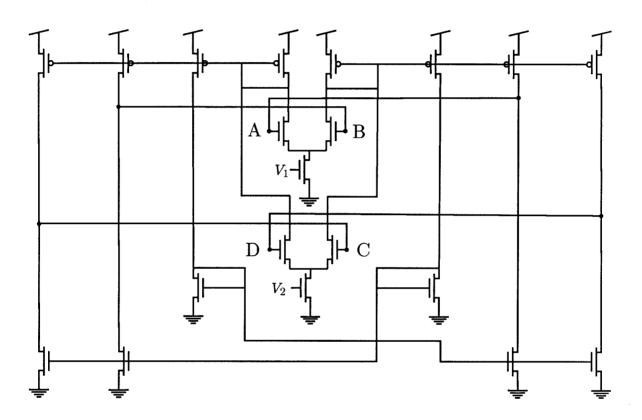

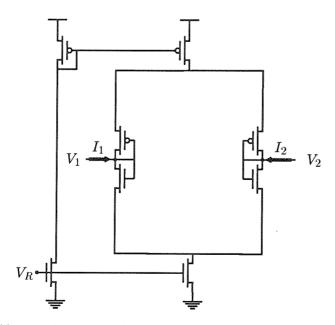

Figure 2.3 shows a transistor realization of the above equations. As long as the differences |A - B| and |C - D| are small, we can assume that the differential pairs are working in their linear region. In subthreshold operation, the following constraint is implemented:

$$e^{V_1/(kT/q)}(A-B) = e^{V_2/(kT/q)}(C-D)$$

(2.19)

Figure 2.3: CMOS implementation of the subtraction constraint circuit. This device implements the constraint that A - B = C - D.  $V_1$  and  $V_2$  are bias voltages which control the relative weighting of A - B vs C - D.

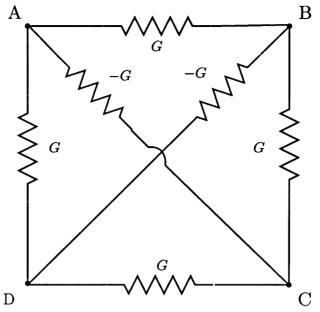

Figure 2.4: This resistor network also implements the constraint A-B=C-D at the expense of constructing negative resistors.

The bias voltages  $V_1$  and  $V_2$  allow either side of the equation to be scaled arbitrarily. This circuit has been implemented in a standard CMOS process and successfully tested. It is used as a building block for the spline interpolation circuit discussed in Chapter 3.

An alternative implementation using resistors is shown in Figure 2.4. This circuit also minimizes the same constraint  $F^2$  given above. Note, however, that negative resistors are required. Negative resistors are notoriously difficult to build and control stably.

#### 2.3.3 The Multiplication Constraint Box

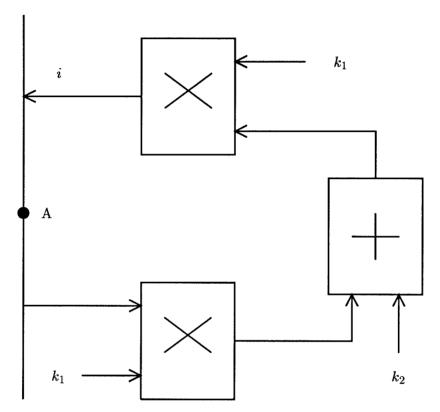

Many times a multiplication constraint is necessary. For example, the Tanner motion chip enforces a multiplication constraint to compute the uniform velocity of an image [Tanner, 1986] [Tanner and Mead, 1986]. In 1D, the basic constraint necessary is  $k_1A = k_2$ , where  $k_1$  and  $k_2$  are arbitrary fixed constants. The constraint equation is

$$F(A) = k_1 A - k_2 (2.20)$$

Figure 2.5: The Tanner-like multiplication constraint box implements the constraint that  $k_1A=k_2$  where  $k_1$  and  $k_2$  are input voltages and A is the output voltage.

Figure 2.6: This resistor network also implements the constraint  $k_1A = k_2$  where  $k_1$  and  $k_2$  are input voltages and A is the output voltage. Although the resistor value is non-negative, the resistor and the voltage values are nontrivial functions of  $k_1$  and  $k_2$ .

Now the current equation is

$$I_A = -F\frac{\partial F}{\partial A} = -k_1(k_1 A - k_2) \tag{2.21}$$

Figure 2.5 depicts a multiplication constraint box very similar to that used by Tanner.

Various strategies for implementing Figure 2.5 have been investigated. Building a compact four-quadrant multiplier in analog VLSI that is quantitatively accurate is a difficult task because of transistor mismatches. An alternative circuit using resistors is depicted in Figure 2.6. The resistor required is data-dependent but always positive. However, a voltage source is needed whose value is the four-quadrant quotient of two voltages. This design would also have to contend transistor mismatches.

Hutchinson et al. have proposed a analog network for computing optical flow from two images [Hutchinson et al., 1988]. The constraint-box methodology has been used to simplify this proposal to one in which all resistors are positive and data-independent [Harris et al., 1990b]. Furthermore, all voltage source values are relevant image quantities. Dennis studied the use of analog networks to solve optimization problems. He used diodes to enforce inequality constraints [Dennis, 1959]. More recently, Chua has extended the approach of Dennis and actually built optimization circuits using discrete op amps [Chua and Lin, 1984]. In both of these approaches, negative resistors are still necessary.

#### 2.4 Exact Constraint Boxes

Least squares constraint boxes are related to ideas from constrained optimization. It is rare in early vision processing to require constraints to be satisfied exactly. Omnipresent noise and inaccuracies present in the inputs and processing circuitry make it unlikely that constraints should be enforced exactly. Suppose, however, that there are hard and soft constraints in a particular problem. The hard constraints  $(\hat{F}_i)$  must be satisfied exactly while soft constraints  $(F_j)$  can be approximately fulfilled. In other words we must, minimize the following energy functional:

$$E = \frac{1}{2} \sum_{j} G_{j} F_{j}^{2} \tag{2.22}$$

while satisfying  $\hat{F}_i = 0$  for all values of i. One solution would be to implement  $\hat{F}_i$  as a set of constraint boxes, each with conductance  $\hat{G}$ . This would lead to the following augmented energy function:

$$E = \frac{1}{2} \sum_{i} \hat{G} \hat{F}_{i}^{2} + \frac{1}{2} \sum_{i} G_{j} F_{j}^{2}$$

(2.23)

The conductance factor  $\hat{G}$  can be increased to obtain arbitrary accuracy in the constraints  $\hat{F}_i$ , provided that the constraints do not conflict.  $\hat{F}_i$  will be identically equal to zero in the limit as  $\hat{G} \to \infty$ . This technique is called the penalty method in the constrained optimization literature [Platt, 1990] [Gill et al., 1981]. The penalty method requires solving a very stiff set of differential equations causing instability problems for both numerical differential equation solvers and analog hardware [Platt, 1990].

Another method for satisfying constraints exactly is to minimize an absolute-value con-

straint energy instead of the more familiar quadratic. This would result in

$$E = \frac{1}{2} \sum_{i} \hat{G}|\hat{F}_{i}| + \frac{1}{2} \sum_{j} G_{j} F_{j}^{2}$$

(2.24)

For values of  $\hat{G}$  above a certain finite value,  $\hat{F}_i$  will be satisfied exactly [Platt, 1990] [Gill et al., 1981]. This method will be discussed in more detail in Chapter 3 and actually used in working hardware in Chapter 5.

Another way to enforce the constraints  $\hat{F}_i$  exactly is to use Lagrange multipliers. Under this formulation, the following energy would be minimized:

$$E = \sum_{i} \lambda_{i} \hat{F}_{i} + \frac{1}{2} \sum_{i} \hat{G} \hat{F}_{i}^{2} + \frac{1}{2} \sum_{j} G_{j} F_{j}^{2}$$

(2.25)

If gradient ascent is performed on  $\lambda$ , a small value of  $\hat{G}$  solves the problem [Platt, 1990] [Arrow et al., 1958] [Bertsekas, 1976]. The  $\frac{1}{2}\sum_{i}\hat{G}\hat{F}_{i}^{2}$  term is needed to guarantee stability.

## Chapter 3

# Coupled Depth/Slope Network

This chapter discusses a biharmonic surface interpolation chip using constraint boxes.

The coupled/depth slope network minimizes a second-order or "thin-plate" energy of the surface.<sup>1</sup>

### 3.1 Coupled Depth/Slope

Reconstructing a surface from sparse sensory data is a well-known problem in computer vision. Early vision modules typically supply sparse depth, orientation, and discontinuity information. The surface reconstruction module incorporates these sparse and possibly conflicting measurements of a surface into a consistent, dense depth map.

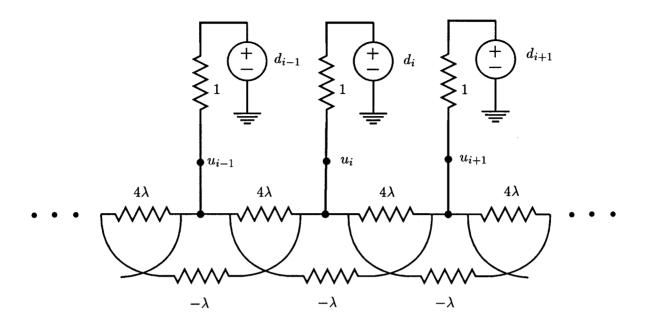

The coupled depth/slope model provides a novel solution to the surface reconstruction problem [Harris, 1987]. Figure 3.1 depicts a high-level schematic of the circuit. The  $d_i$  voltages represent noisy and possibly sparse input data, the  $u_i$ s are the smooth output values, and the  $p_i$ s are the explicitly computed slopes. The vertical data resistors (with unity conductance) control the confidence in the input data. In the absence of data these resistors are open circuits. The horizontal chain of smoothness resistors (each with conductance  $\lambda$ ) forces the derivative of the data to be smooth. This model is called the coupled depth/slope

<sup>&</sup>lt;sup>1</sup>Portions of this chapter have already been published [Harris, 1986] [Harris, 1987] [Harris, 1989].

Figure 3.1: The coupled depth/slope model. The data  $d_i$  are supplied to the network through unity conductance resistors. The subtract constraint boxes compute an explicit representation of the derivatives  $p_i$  which are smoothed by resistors with conductance  $\lambda$ . The stationary voltage values  $u_i$  are the final smooth outputs.

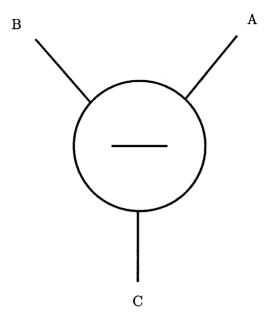

Figure 3.2: Single subtract constraint box. This device enforces the constraint that A - B = C.

model because of the coupling between the depth and slope representations provided by the subtraction elements. The subtractors explicitly calculate a slope representation of the surface. Any depth or slope node can be made into a constraint by fixing a voltage source to the proper location in the network. Intuitively, any sudden change in slope is smoothed out with the resistor mesh.

The tri-directional subtractor device (developed in the last chapter) is responsible for the coupling between the depth and slope representations. The subtract constraint box is shown schematically in Figure 3.2. If nodes A and B are set with ideal voltage sources, then node C will be forced to A-B by the device. This circuit element is unusual in that all of its terminals can act as inputs or outputs. If nodes B and C are held constant with voltage sources, then the A terminal is fixed to B+C. If A and C are input, then B becomes A-C. This element can be constructed with the A-B=C-D constraint box (shown in Figure 2.3) by setting the D terminal to a constant reference voltage that defines "zero" slope. C can now be positive or negative with respect to the reference voltage. When further constraints are added, this device minimizes an energy proportional to  $(A-B-C)^2$ . The energy minimized by the constraint box is different, in general, from the actual power

dissipated by its transistor implementation. In the limiting case of a continuous network, the total energy is

$$E = \int (u - d)^2 + G \left(\frac{du}{dx} - p\right)^2 + \lambda \left(\frac{dp}{dx}\right)^2 dx$$

(3.1)

The three terms arise from the power dissipated in the subtractors and in the two different types of resistors. Energy minimization techniques and standard calculus of variations have been used to formally show that the reconstructed surfaces, u, satisfy the 1D biharmonic equation between input data points [Harris, 1987]. In the two-dimensional formulation, u is a solution of

$$\nabla^2 \nabla^2 u = 0 \tag{3.2}$$

This interpolant, therefore, provides the same results as minimizing the energy of a thin plate, which has been commonly used in surface reconstruction algorithms on digital computers [Grimson, 1981] [Terzopoulos, 1983].

In discrete terms, this energy becomes

$$E(u) = \sum_{i} (u_i - d_i)^2 + G(u_{i+1} - u_i - p_i)^2 + \lambda (p_i - p_{i+1})^2$$

(3.3)

The variable G is a measure of the conductance of the constraint box. As the value of G increases, the constraint box accuracy becomes more exact. This is an implementation of the penalty method in constrained optimization [Gill et al., 1981].

### 3.2 Hardware Implementation

An eight-node 1D network of the form shown in Figure 3.1 was designed and fabricated in  $3\mu$ m CMOS. Three important components of the model must be mapped to analog VLSI: the two different types of resistors and the subtractors. The vertical confidence resistors are built with simple transconductance amplifiers (transamps) connected as followers. The

Figure 3.3: A negative-resistor solution to the 1D biharmonic equation. This circuit is equivalent to the network in Figure 3.1 in the limit as the conductance of the constraint boxes (G) goes to infinity.

bias voltage of the transamp follower determines its conductance and therefore signifies the certainty of the data. If there are no data for a given location, the corresponding transamp follower is turned off. The horizontal smoothness resistors are implemented with Mead's saturating resistor [Mead, 1989]. Since conventional CMOS processes lack adequate resistive elements, we are forced to build resistors out of transistor elements. The bias voltage for Mead's resistor allows the effective conductance of these circuit elements to vary over many orders of magnitude.

The circuit shown in Figure 3.3 computes the same solutions as the coupled depth/slope network in the limit as  $G \to \infty$ . Interestingly, a 2-D implementation of this idea was implemented in the 1960s using inductors and capacitors. Proper choice of the frequency of alternating current allowed the circuit elements to act as pure positive and negative impedances. Unfortunately, negative resistances are troublesome to implement, especially

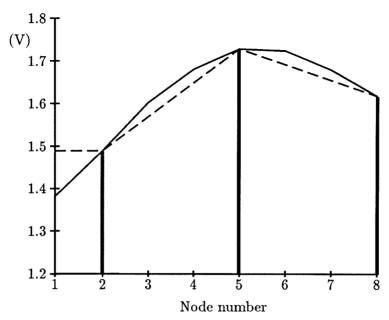

Figure 3.4: Measured data from the second-order chip (solid line) and simulated first-order result (dashed line). The second-order interpolant is smoother and also extrapolates beyond the data points.

in analog VLSI. Recently, a 2D approximation of this network was constructed in analog VLSI [White and Abidi, 1989] [Kobayashi et al., 1991]. Their chip dissipates over 2 Watts of power; presumably much of this is necessary for the negative resistor elements. One of the big advantages of using constraint boxes to implement early vision algorithms is that the resulting networks do not require negative resistances.

Figure 3.4 shows a sample output of the circuit. Data (indicated by vertical dashed lines) were supplied at nodes 2, 5, and 8. As expected, the chip finds a smooth solution (solid line) that extrapolates beyond the known data points. As discussed in Chapter 1, a single resistive grid minimizes the first-order or membrane energy of a surface. A disadvantage of the coupled depth/slope implementation is its sensitivity to transistor offsets due to the nature of the derivative operation. The first-order resistive network implementation using Mead's saturating resistor is guaranteed to have zero voltage offset.

Figure 3.4 also shows the simulated performance of a first-order energy or membrane energy minimization. Data points are again supplied at nodes 2, 5, and 8. In contrast to the second-order chip results, the solution (dashed line) is much more jagged and does not

Figure 3.5: Graphical comparison of 1D analytic Green's functions for first-order (dashed line), second-order (dotted line) and Gaussian (solid line).

extrapolate outside of the known data points (for example, see node 1). Interestingly, psychophysics experiments support the smoother interpolant used by the second-order coupled depth/slope chip [Grimson, 1981]. Unlike the second-order network, the first-order network is not rigid enough to incorporate either orientation constraints or orientation discontinuities [Terzopoulos, 1983].

Image smoothing is a special case of surface interpolation where the data are given on a dense grid. The first-order network is a poor smoothing operator. A comparison of the analytic Green's functions of the first- and second-order networks is shown in Figure 3.5 (the first-order shown with a dashed line and the second-order with a solid line). Note that the analytic Green's function of the second-order network (solid line) and that of standard Gaussian convolution (dotted line) are nearly identical. This fact was pointed out by Poggio, Voorhees, and Yuille [1986], when they suggested the use of the second-order energy to regularize the edge detection problem. Gaussian convolution has been claimed by many authors to be the "optimal" smoothing operator and is commonly used as the first stage of edge detection [Marr and Hildreth, 1980] [Poggio et al., 1986]. Though the

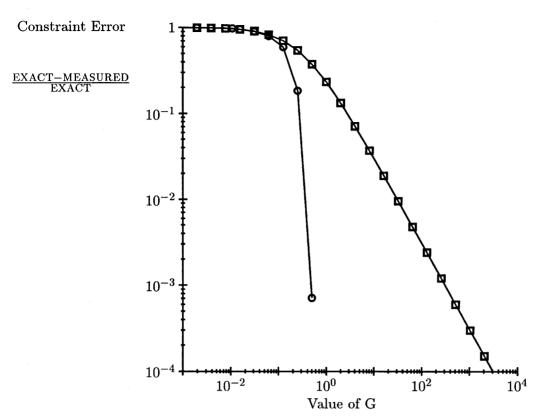

Figure 3.6: Inaccuracy of the constraint box versus G for simulation of the coupled depth/slope network. The penalty method (Equation 3.4) is shown with squares and the absolute value penalty method (Equation 3.5) shown with circles.

second-order network can be used to smooth images, Gaussian convolution cannot be used to solve the more difficult problem of interpolation between sparse data points.

## 3.3 Constrained Optimization Approach

The hardware described in this chapter minimizes the following energy functional when all the devices are operating in the linear range:

$$E(u) = \sum_{i} (u_i - d_i)^2 + G(u_{i+1} - u_i - p_i)^2 + \lambda (p_i - p_{i+1})^2$$

(3.4)

The variable G is the measure of the conductance of the constraint box. As the value of G increases, the constraint box computation becomes more exact. An infinite value of G is necessary for the constraint to be satisfied exactly. An alternative is to use the absolute

value constraint. This energy becomes

$$E(u) = \sum_{i} (u_i - d_i)^2 + G|u_{i+1} - u_i - p_i| + \lambda(p_i - p_{i+1})^2$$

(3.5)

As discussed in Chapter 1, a small finite value of G will suffice to ensure that the constraint is fulfilled exactly. Both the quadratic and the absolute value methods were simulated. Figure 3.6 compares the accuracy of the two methods for various values of G. As expected, the absolute value method reduces the error in the constraint equation to within machine precision even for small values of G.

The coupled depth/slope network has a natural generalization that enforces smoothness constraints to any arbitrary level of derivative of the data. Furthermore, discontinuities of any order can be detected with resistive fuses on each level of derivative. For example, discontinuities in the first-derivative, i.e., creases, can be detected. Higher-order smoothing and discontinuity detection has been demonstrated for edge detection, image segmentation, and surface interpolation [Liu and Harris, 1989]. Recently, Suter has studied the higher-order smoothness problem [Suter, 1990a]. His approach uses the exact constraint boxes proposed by Platt instead of the penalty method [Suter, 1990b].

# Chapter 4

# Resistive Fuse

This chapter describes the resistive fuse circuit—the first hardware circuit that explicitly implements either analog or binary line processes in a controlled fashion. We have successfully designed and tested an analog CMOS VLSI circuit that contains a 20x20 network of resistive fuses implementing piece-wise smooth surface interpolation. The segmentation ability of this network is demonstrated for various 2-D inputs. Finally extensions of these ideas are discussed for the detection of outliers and for segmentation of temporal signals.<sup>1</sup>

#### 4.1 Line Processes

Standard regularization theory provides a basis for solving most early vision problems but algorithms that depend solely on a smoothness assumption perform badly at discontinuities. In surface reconstruction, for example, an inflexible surface smoothness constraint either blurs discontinuities or else causes unrealistic overshoot effects wherever there are breaks in the surface. Resistors and constraint boxes can map most regularization theory algorithms onto stable analog hardware, but they must be extended to deal with discontinuities.

Many recent approaches combine discontinuity detection with surface reconstruction by

<sup>&</sup>lt;sup>1</sup>Portions of this chapter have already been published [Harris et al., 1989] [Harris and Koch, 1989] [Harris et al., 1990a].

defining an energy function of the surface as a nonconvex energy function that includes binary line processes. Line processes provide a systematic method of selectively "breaking" the smoothness constraints imposed by standard regularization theory. Geman and Geman worked with binary line processes on a Markov field lattice in reconstructing surfaces from noisy images [Geman and Geman, 1984]. They also used simulated annealing to minimize the resulting nonconvex energy. Marroquin used two coupled Markov random fields to solve the surface reconstruction problem—one for analog depth values and the other for binary line processes [Marroquin, 1987].

Rather than use time-consuming stochastic annealing methods, Koch, Marroquin and Yuille later showed how the reconstruction problem can be solved using analog networks where the discontinuities are allowed to vary continuously between 0 and 1 [Koch et al., 1987]. The energy function of this network is minimized using similar updating equations from Hopfield's work [Hopfield, 1984]. Koch et al. used a first-order energy model (membrane) for reconstructing the surface between sparse depth points of simple synthetic images. Blake and Zisserman used similar energy functions to locate discontinuities in natural images using the membrane model [Blake and Zisserman, 1987]. They also extended their work using a plate model to locate discontinuities in synthetic images. They obtain the minimum of the energy function by an approach they called the GNC (gradient non-convexity) method. A convex approximation to the problem is first constructed and then the energy landscape is continuously transformed into its true form.

A number of authors have used deterministic methods to find the (local) minima of non-convex variational functionals, with next-to-optimal results (e.g., [Koch et al., 1987] [Terzopoulos, 1986] [Chou and Brown, 1986]). Line processes were extended and modified to account for discontinuities in depth, texture, optical flow and color [Marroquin, 1987] [Marroquin et al., 1987] [Hutchinson et al., 1988] [Poggio et al., 1988] [Zhou and Chellappa, 1988]. The principal drawback of all of these methods is the computational expense involved in minimizing the associated non-quadratic cost functionals, in

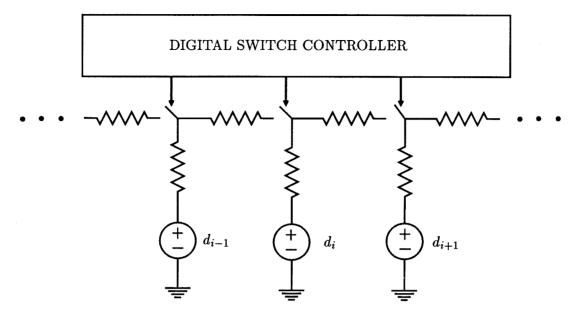

Figure 4.1: Resistor network with digital switching network, similar to proposal in [Koch et al., 1987].

particular when numerous constraints are incorporated.

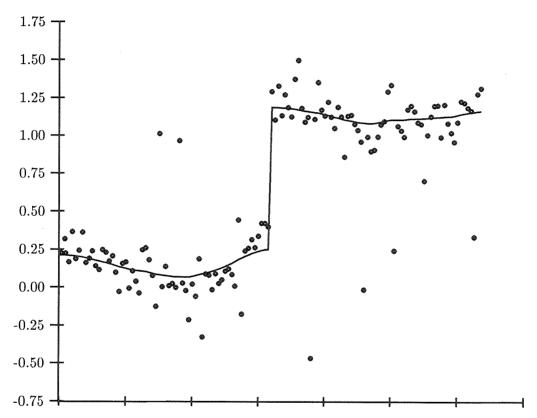

Including binary line processes  $\ell$  into the functional of Equation 1.4 leads to

$$E(u) = \sum_{i} (d_i - u_i)^2 + \lambda \sum_{i} (u_{i+1} - u_i)^2 (1 - \ell_i) + \sum_{i} \alpha \ell_i$$

(4.1)

where  $\alpha$  is an additional free parameter. The second term in this functional has been modified to implement the constraint that surfaces should vary smoothly for small values of the surface gradient. If all variables, with the exception of  $u_i$ ,  $u_{i+1}$ , and  $\ell_i$ , in Equation 4.1 were held fixed and  $\lambda(u_{i+1}-u_i)^2 < \alpha$ , it would be "cheaper" to pay the price  $\lambda(u_{i+1}-u_i)^2$  and set  $\ell_i = 0$  than to pay the larger price  $\alpha$ . However, if the difference becomes too steep, the line process is switched on, i.e.  $\ell_i = 1$ , and the "price"  $\alpha$  is paid. The functional of Equation 4.1 is non-convex and a large number of both stochastic and deterministic methods have been designed to find optimal or nearly optimal solutions for this and similar functionals [Geman and Geman, 1984] [Marroquin et al., 1987] [Koch et al., 1987] [Blake and Zisserman, 1987] [Terzopoulos, 1983] [Terzopoulos, 1986].

One straightforward manner to implement line discontinuities is via binary switches, breaking the resistive connections among neighboring nodes. Figure 4.1 depicts a pro-

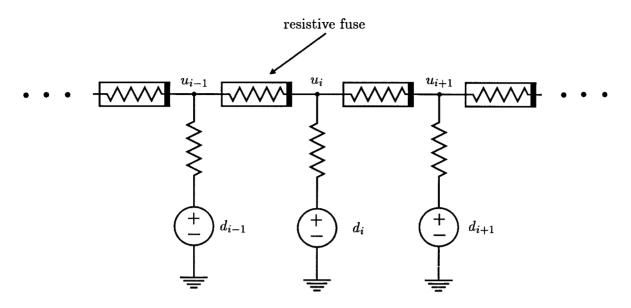

Figure 4.2: 1D fuse network.

posal for implementing these line processes in hardware, i.e., see [Koch et al., 1987] and [Hutchinson et al., 1988]. Switches are added to the resistive network of Figure 1.1. Each switch has an associated digital processor that controls the opening and closing of the switch in either a deterministic or in a stochastic fashion, depending on the value of the voltage across the switch as well as on the states of neighboring switches. Such an analog-digital implementation is quite difficult to implement within conventional two-dimensional silicon circuits, due to the high amount of connectivity among nodes and the complexity of integrating the analog and digital processes. This mixed analog-digital circuit can be replaced by a single analog non-linear resistor, the "resistive fuse" as shown in Figure 4.2.

# 4.2 Resistive Fuse Theory

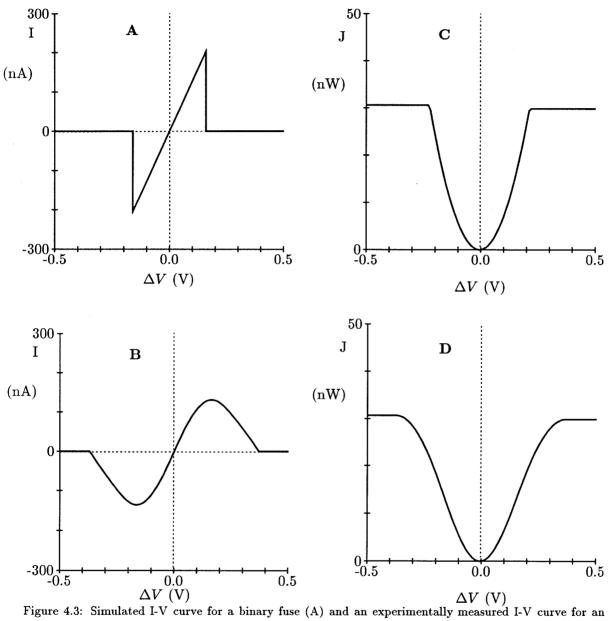

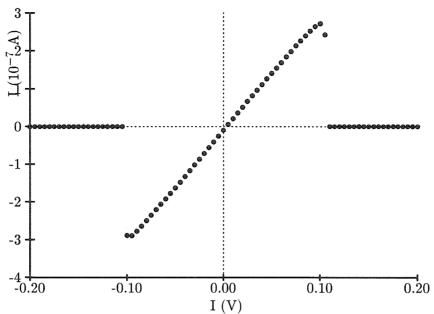

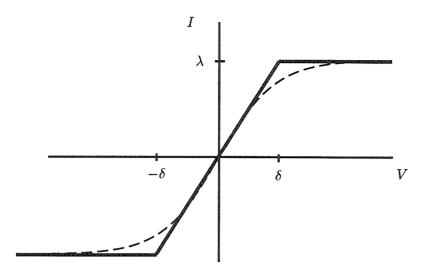

The appropriate current-voltage relationship of a binary resistive fuse is illustrated in Figure 4.3a. As long as the voltage drop across this device is below a threshold, the current through the nonlinear resistor is linearly related to the voltage across it. Once past the voltage threshold, the fuse open-circuits (hence the name "fuse"), and the current is zero. Unlike conventional electrical fuses, however, the resistive fuse can "reconnect" after open-

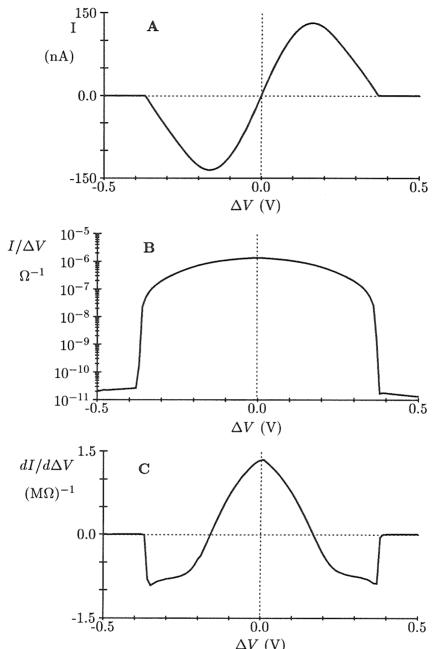

Figure 4.3: Simulated I-V curve for a binary fuse (A) and an experimentally measured I-V curve for an analog resistive fuse (B). Integrating numerically over these curves gives the co-content J for the binary (C) and the analog fuse (D).

circuiting as long as the voltage across the fuse drops again below the threshold. This two-terminal device therefore implements the high-level constraint that surfaces should be smooth unless their neighboring values differ by more than  $\sqrt{\alpha/\lambda}$ , at which point the surface will break. Figure 4.3c can be interpreted as a plot of the co-content  $(J(u, \ell))$  as a function of the depth at locations  $u_i$  and  $u_{i+1}$  and as a function of the discontinuity  $\ell_i$ . The values of the surface and of the line discontinuities are assumed to be fixed at all other locations. As long as  $\lambda(u_{i+1} - u_i)^2 \leq \alpha$ , the function J is quadratic in the gradient. However, once  $|u_i - u_{i+1}|$  exceeds the gradient limit  $\sqrt{\alpha/\lambda}$ , J remains flat at  $J = \alpha$ , independent of the magnitude of  $u_i - u_{i+1}$  [Blake and Zisserman, 1987].

The measured I-V relationship of the analog fuse is shown in Figure 4.3b. The most salient difference from the binary fuse is the smooth flanks, where the current decreases smoothly to zero for increasing values of the voltage gradient (in contrast with the discontinuity in the I-V relationship for the binary fuse). In this region, the slope conductance dI/dV will be negative (Figure 4.15). The measured I-V curve can be related directly to the concept of analog line discontinuities of Koch et al. [1987]. The key idea is that, following Hopfield and Tank [1985] in their neural network implementation of the Traveling Salesman Problem , binary discontinuities are mapped onto continuous "neurons," whose output is constrained to lie between 0 and 1. The input-output relationship of these "discontinuity neurons" is governed by the sigmoidal function V = g(U), where g(U) is a strictly monotonic function, usually taken to be

$$g(U) = \frac{1}{1 + e^{-2\eta U}} \tag{4.2}$$

with the "gain"  $\eta > 0$ . The network converges to a stationary solution using a steepest-descent rule. It is straightforward to derive an analog version of resistive fuses with the following I-V relationship

$$I = f(V) = \left[1 - g(V^2 - \alpha)\right]V \tag{4.3}$$

Our measured I-V curve for the fuse (Figure 4.3b) implements a similar function. For

$\eta \to \infty$ , the function g becomes binary and f(V) of Equation 4.3 approaches the form of the binary fuse (Figure 4.3a).

The analytical form of the I-V relationship of the resistive fuse element we used in our simulations (see below) can be rigorously derived using a deterministic Mean Field Approximation to the underlying stochastic Markov Random Field model of piecewise smooth surface interpolation [Geiger and Girosi, 1989]. In this approximation, common to statistical mechanics [Huang, 1963], the interaction among neighboring values of u and  $\ell$  is replaced by the interaction among neighboring mean values of u and  $\ell$ . If we re-interpret the results of Geiger and Girosi within our electrical circuit framework, we arrive at the constitutive relationship of the analog resistive fuse given in Equation 4.3.

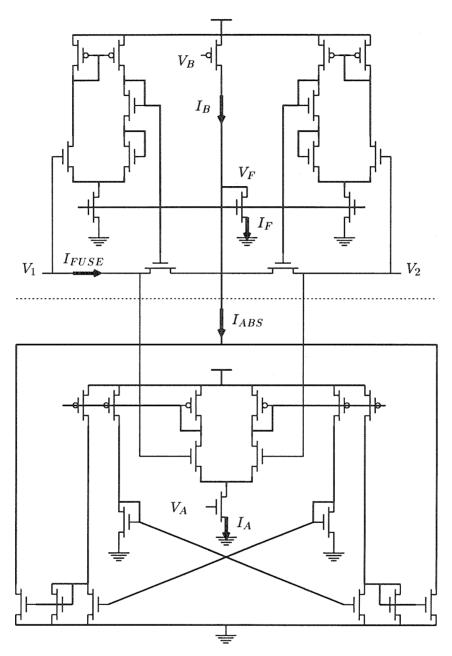

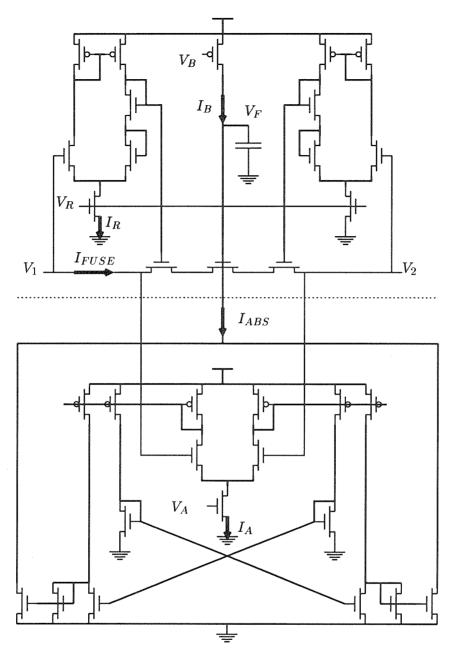

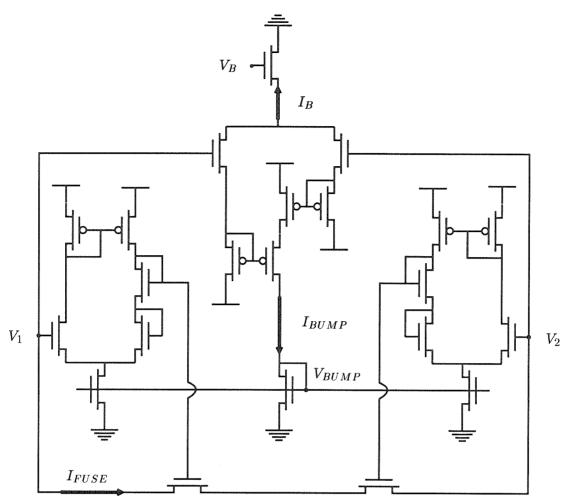

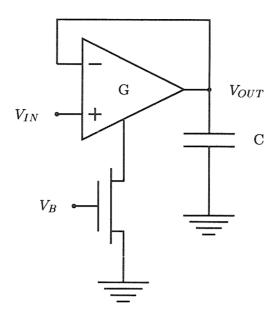

#### 4.3 Hardware Implementation

The circuit schematic for the original analog resistive fuse is shown in Figure 4.4. The circuitry above the dotted line in the figure is Mead's saturating resistor with a p-type pullup transistor that sets the nominal resistance of the fuse. In subthreshold operation, the current through a transistor varies exponentially with the gate-to-source voltage. Thus, the voltage  $V_B$  produces a current  $I_B$  equal to:

$$I_B = I_0 e^{\kappa (V_{DD} - V_B)} \tag{4.4}$$

All voltages are assumed to be normalized by kT/q. The variable  $\kappa$  is a process-dependent parameter that reflects the inability of the gate to be 100% effective in reducing the barrier potential [Mead, 1989].  $I_0$  is a constant that includes the width and length of the transistor as well as process-dependent fabrication parameters. Letting  $I_F = I_B$ , the I-V relation of the resistor can be derived as:

$$I_{FUSE} = \frac{I_F}{2} \tanh\left(\frac{\Delta V}{2}\right) \tag{4.5}$$

Figure 4.4: Schematic of the analog fuse circuit. The nonlinear, voltage-controlled resistance is seen across the  $V_1$  and  $V_2$  terminals. The circuitry above the dotted line is a saturating resistor [Mead, 1989] with  $V_B$  controlling the nominal amount of resistance. The circuit below the dotted line is a saturating absolute-value circuit that turns off the resistor for large  $|V_1 - V_2|$ .  $V_A$  determines the magnitude of the current drawn by the absolute-value circuit.

where  $\Delta V = V_1 - V_2$ . For small  $\Delta V$  this portion of the circuit operates as a linear resistor with a resistance of

$$R = \frac{4kT/q}{I_F} \tag{4.6}$$

Because we are working in the subthreshold region,  $I_F$ , and thus the resistance, can be varied over five orders of magnitude. For large  $\Delta V$  the resistor saturates and provides a constant current of  $I_F/2$ . A measured I-V curve for this circuit was shown in Figure 1.2B.

The circuit below the dotted line in the figure performs a saturating absolute-value operation. This portion of the circuit is enabled by the voltage  $V_A$ , which creates a current  $I_A$  equal to:

$$I_A = I_0 e^{\kappa V_A} \tag{4.7}$$

The positive parts of the outputs of a dual-output wide-range transconductance amplifier are combined to create a current of:

$$I_{ABS} = I_A \tanh\left(\frac{\kappa|\Delta V|}{2}\right)$$

(4.8)

By Kirchhoff's current law, the current  $I_F$  is:

$$I_F = \lfloor I_B - I_{ABS} \rfloor \tag{4.9}$$

where the symbols | | are defined as

Substituting Equation 4.8 and Equation 4.9 into Equation 4.5, gives

$$I_{FUSE} = \frac{1}{2} \left[ I_B - I_A \tanh\left(\frac{\kappa |\Delta V|}{2}\right) \right] \tanh\left(\frac{\Delta V}{2}\right)$$

(4.10)

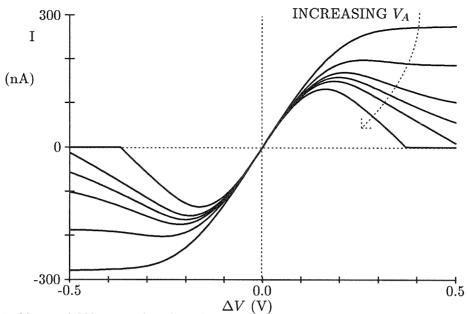

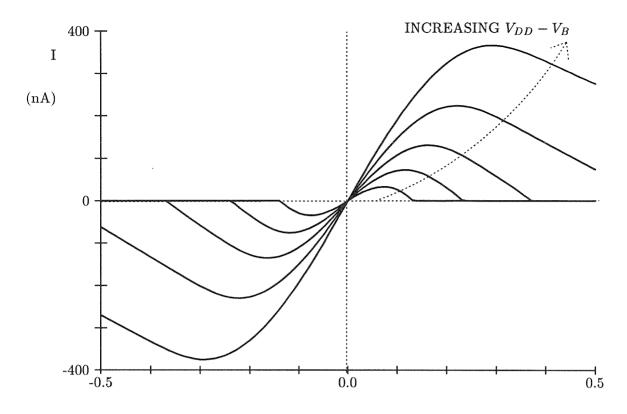

Figure 4.5: Measured I-V curves that show the effect of continuously varying from the saturating characteristic to that of the fuse curve.  $V_B$  was set to 4V and  $V_A$  was varied from 0V to 2V. When  $V_A = 0$ , the resulting I-V curve is identical to that of Mead's saturating resistor.

When  $|\Delta V|$  is small, the fuse acts as a linear resistor whose nominal resistance is set by  $I_B$ . When  $|\Delta V|$  is large,  $I_A$  increases above the current supplied by the p-type pull-up, and  $V_F$  is pulled to ground, shutting off the resistor. In between these extremes, the fuse exhibits a gradual transition.

Figure 4.5 shows a family of curves measured by varying  $V_A$  while keeping  $V_B$  constant. By varying  $V_A$  in this way, the circuit's I-V characteristic can be continuously and smoothly changed from that of a saturating resistor to the fuse I-V curve. Setting  $V_A = 0$  gives  $I_A = 0$ , disabling the absolute-value circuit, and giving the fuse a saturating I-V relationship (Figure 1.2B).

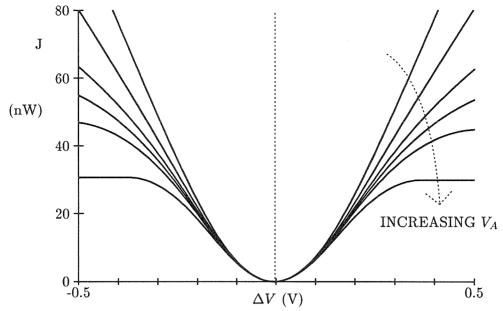

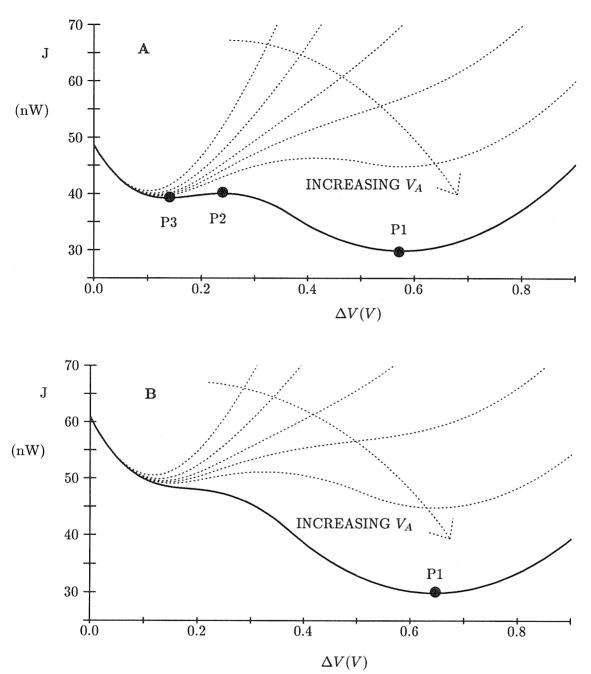

Integration of the I-V curves in Figure 4.5 gives the family of co-content curves shown in Figure 4.6. For small  $\Delta V$  the co-content is quadratic and for large  $\Delta V$  the co-content saturates at a constant value. Instead of saturating for large voltage differences, the co-content of the saturating resistor increases linearly with voltage. From Chapter 1 it is known that networks of resistors with positively sloped I-V curves are guaranteed to converge to a unique minimum value of the co-content. By changing the control voltage, we are warping

Figure 4.6: Co-content functions: each curve was numerically integrated from the family of curves in Figure 4.5. Continuously varying the co-content curves in this way performs a useful computation that is explored further in Figure 4.16 and Figure 4.17.

the energy landscape in a continuous fashion ("continuation method") from one containing a unique global minimum to one containing many local minima.

The fuse provides a mechanism for changing the threshold value. If we assume that the circuit is operating in the linear region of the two hyperbolic tangents,  $I_{FUSE}$  becomes twin parabolas of the form:

$$I_{FUSE} = \left\lfloor \frac{I_B}{4} - \kappa \frac{I_A}{8} |\Delta V| \right\rfloor \Delta V \tag{4.11}$$

This linear analysis indicates that the measured curve in Figure 4.3b consists of a parabola in each of the first and third quadrants. This current in Equation 4.11 is cut to zero for:

$$|\Delta V| \ge 2\frac{I_B}{I_A} \frac{kT}{q\kappa} \tag{4.12}$$

$I_{FUSE}$  reaches its extrema points at:

$$|\Delta V| = \frac{I_B}{I_A} \frac{kT}{q\kappa} \tag{4.13}$$

$\Delta V$  (V) Figure 4.7: Measured I-V curves illustrating different line process penalties.  $V_A$  was kept constant at 2V and  $V_B$  was varied from 3.9V to 4.1V.

The extrema points can be set by the ratio of  $I_B$  to  $I_A$ . In subthreshold operation, the width of the saturating tanh curves is about 100mV. The extrema points can then only be varied from 0 to about  $\pm 100$ mV. For gate voltages above the threshold of the bias transistors, the width of the linear region of the hyperbolic tangent function increases by  $V_{GS} - V_T$ , where  $V_{GS}$  is the gate-to-source voltage and  $V_T$  is the threshold voltage of the bias transistors. Thus, by going slightly above threshold, the extremum point can be varied from 0 to about  $\pm 500$ mV. Figure 4.7 shows a family of I-V curves measured by varying  $V_B$  and holding  $V_A$  constant.

A binary fuse has been built and tested. The measured I-V curve of the binary fuse (shown in Figure 4.9) has a small incrementally active region. The schematic (shown in (Figure 4.8) is a minor modification of the analog fuse circuit. Instead of feeding the absolute-value current back to the resistor bias circuits, current is fed back to a pass gate

Figure 4.8: Modification of the fuse to obtain a binary characteristic. As before, a saturating resistor and an absolute-value circuit are combined to create a fuse. However, different from the circuit of Figure 4.4, the absolute-value circuit discharges the gate of a pass transistor that has been added in the resistance path. This pass gate acts as a binary switch that is opened or closed depending on whether or not the absolute-value current is greater than the threshold current provided by  $V_B$ .  $V_B$  provides independent control of the resistance of the fuse when the binary switch is closed. The parasitic capacitor at the high-gain node has been added to illustrate that the fuse has non-zero switching times.

Figure 4.9: Measured I-V curve for the binary fuse circuit. Currents were measured with voltage steps of 5 mV.

that acts as a binary switch in the current path. When  $I_B > I_{ABS}$  the voltage  $(V_F)$  on the gate of the binary switch is charged to  $V_{DD}$ . On the other hand, when  $I_B < I_{ABS}$ ,  $V_F$ is pulled to ground, effectively open-circuiting the resistor. The resistance of the resistor is controlled by  $V_R$ , which sets the bias current  $I_R$ . Notice that the current that controls the line process penalty is decoupled from the current that sets the resistance of the fuse. Assuming high-gain elements, the I-V equation for the high-gain fuse is given by:

$$I_{FUSE} = \frac{I_R}{2} \tanh\left(\frac{\Delta V}{2}\right) \quad \text{if} \quad I_A \tanh\left(\frac{\kappa |\Delta V|}{2}\right) < I_B$$

$$I_{FUSE} = 0 \quad \text{if} \quad I_A \tanh\left(\frac{\kappa |\Delta V|}{2}\right) \ge I_B$$

(4.14)

$$I_{FUSE} = 0 \quad \text{if} \quad I_A \tanh\left(\frac{\kappa|\Delta V|}{2}\right) \ge I_B$$

(4.15)

This implementation of the binary fuse shares an advantage with Mead's saturating resistor layout, because only one biasing circuit is needed for each node. This saves many transistors, especially in 2-D layouts. The low-gain fuse requires 33 transistors per connection, while the high-gain fuse requires only 21 transistors per connection plus 6 transistors per node. For a hexagonal mesh, each basic cell needs to contain one node plus half of the six

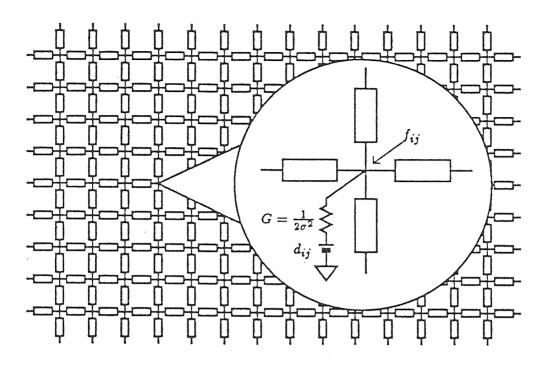

Figure 4.10: Schematic diagram of the 20 by 20 resistive fuse chip. The chip consists of a rectangular mesh of analog resistive fuse elements (shown in Figure 4.4). The data are given as battery values  $d_{ij}$  with the conductance G connecting the battery to the grid. If no data are available, G = 0. The output is the voltage  $u_{ij}$  at each node. Parasitic capacitances (not shown) provide the dynamics. A zero-slope boundary condition is assumed along the boundary. Data are read in/out via additional scanning circuitry (not shown).

neighboring connections, requiring a total of 69 transistors per cell for the high-gain fuse and 99 transistors per cell for the low-gain version.

### 4.4 Segmentation Performance

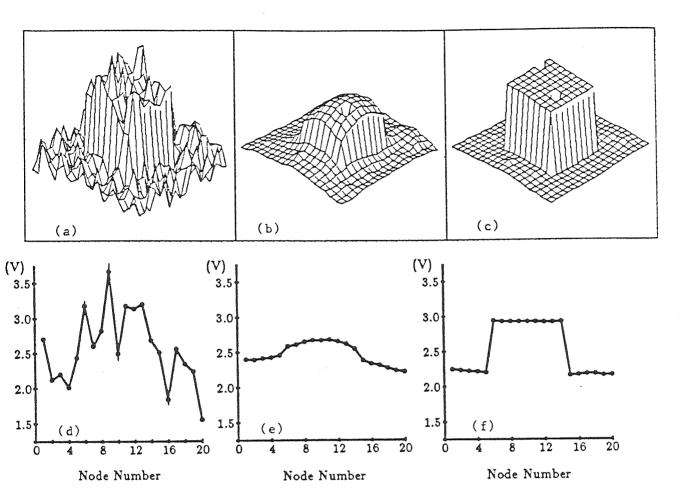

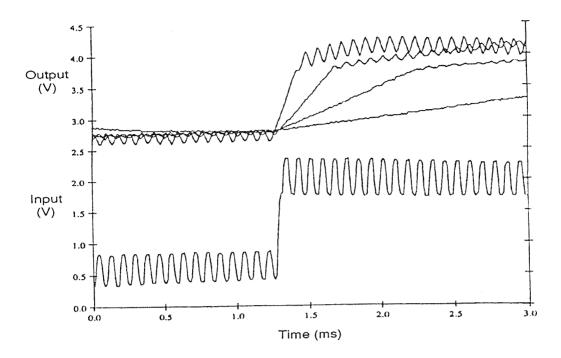

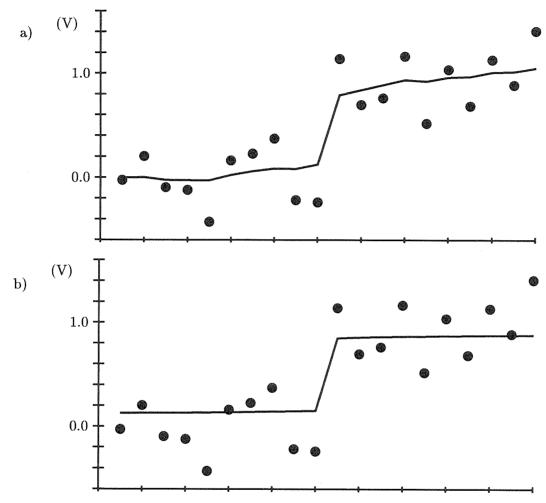

A 20 by 20 resistive fuse chip has been fabricated and tested. The analog fuse (shown in Figure 4.4) was used. Figure 4.11 shows experimental data from this chip. The input array which was scanned into the chip corresponds to a central tower on a flat plane corrupted by Gaussian noise (Figure 4.11a,d). The middle plots illustrate the resultant voltage distribution if the "fuses" are set to act as saturating resistors. The tower merges into the

Figure 4.11: Experimental data from the chip. The scanned input data was a tower (corresponding to  $d_{ij} = 3.0 \ V$ ) rising from a plane (corresponding to 2.0 V) with superimposed Gaussian noise. (a) shows the input with the variance of the noise set to 0.2 V, (b) the voltage output using the fuse configured as a saturating resistance, and (c) the output when the I-V curve of the fuse has been varied from the saturating resistance to that of the analog fuse (following the arrow in Figure 4.5) as well as increasing the conductance  $\lambda$ . (d), (e) and (f) illustrate the same behavior along a horizontal slice across the chip for  $\sigma^2 = 0.4 \ V$ . The smoothing and segmentation abilities of the fuses are obvious. Notice that the amplitude of the noise in the last case (40% of the amplitude of the voltage step) is so large that a single filtering step on the input (d) will fail to detect the tower. Cooperativity and hysteresis are required for optimal performance. Notice the "bad" pixel in the middle of the tower (in c) which was due to a chip fabrication error. Its effect is localized to a single element.

plane, since no discontinuities prevent smoothing from occurring. The resistors around the perimeter of the tower are saturating but do not provide enough of a segmentation effect to filter the noise and preserve the step.<sup>2</sup> Figure 4.11c,f show that changing the I-V curve from that of a saturating resistor to that of an analog fuse enables the network to clearly segment the tower from the background. Numerical analysis as well as our empirical studies have shown that the smoothing abilities of resistive networks are robust to variations (caused by process variations) in the value of the resistances across the chip. Furthermore, point defects, such as the one shown in Figure 4.11c, induce line processes to break, thereby preventing the error from propagating.

The I-V curves of the fuses in this example have been set to the form shown in Figure 4.3b. In this configuration, the network exhibits a hysteresis property in which two stable final states are possible. The two stable states correspond to segmenting or smoothing the step edge. The segmented stable state is shown as the solid line in Figure 4.16b. The smoothed stable state becomes essentially a flat horizontal line. The final state depends on the temporal history of the network. To ensure that the proper stable state is reached in a deterministic fashion,  $V_A$  is initially set to 0 V and then gradually moved to its final value.

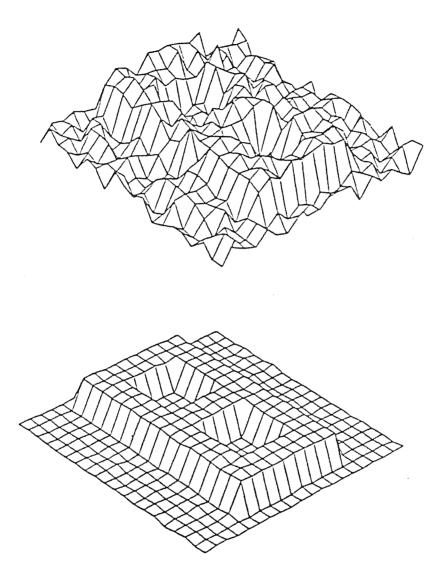

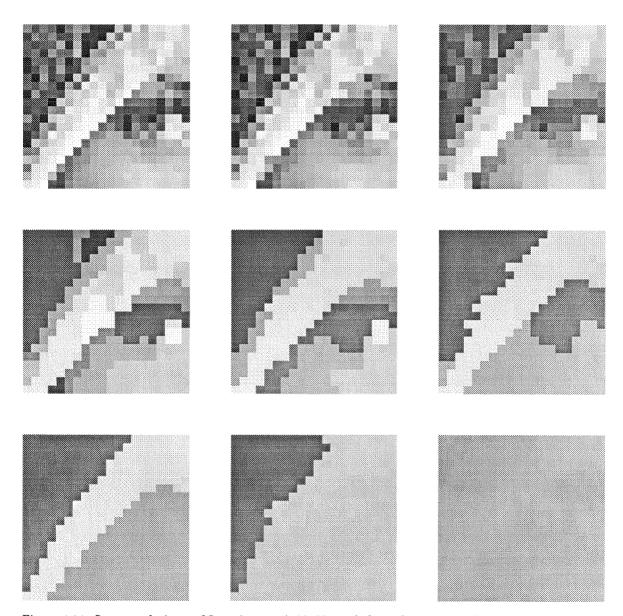

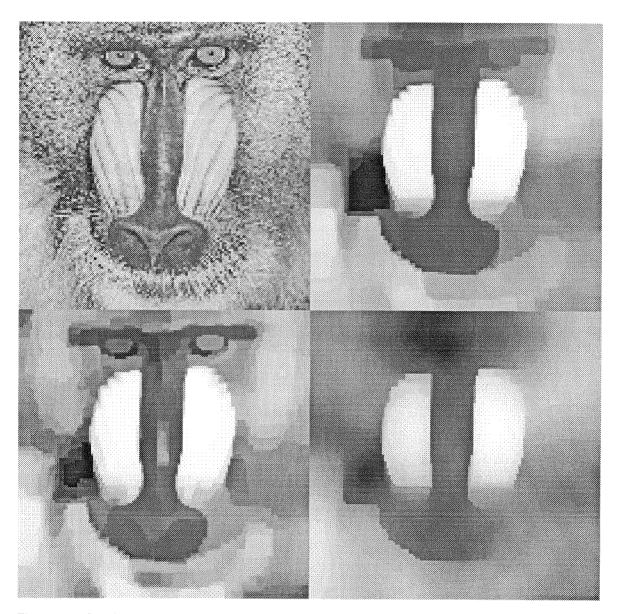

Figure 4.12a shows a figure-eight pattern that was scanned into the chip. The height of the signal was 0.5V with evenly distributed additive noise of  $\pm 0.25$ V. Figure 4.12b shows the measured voltage values that were scanned off the chip. Finally, a 20x20 piece of the Lena image (shown in Figure 4.13) was scanned into the fuse chip and processed.<sup>3</sup> These results are shown in Figure 4.14. Various levels of segmentation behavior were obtained from many edges (top left) to no edges (bottom right).

# 4.5 Annealing Schedules and Continuation Methods

Though the chord resistance (i.e., V/I) of the fuse circuit is always positive, its incre-

<sup>&</sup>lt;sup>2</sup>Chapter 5 describes a modification of the saturating resistor that enhances its segmentation ability.

<sup>&</sup>lt;sup>3</sup>As this image has historically been used in vision research, we include it here for comparison.

Figure 4.12: a) shows a figure-eight pattern that was scanned into the 20x20 resistive fuse chip. The height of the signal was 0.5V with evenly-distributed additive noise of  $\pm 0.25V$ . b) shows the measured voltage values that were scanned off the chip.

Figure 4.13: 128x128 pixel Lena image.

Figure 4.14: Segmented pieces of Lena image. A 20x20 patch from the image in Figure 4.13 was scanned into the resistive fuse chip. Various levels of segmentation behavior were obtained from many edges (top left) to no edges (bottom right).

Figure 4.15: The I-V curve of the fuse measured in 10mV increments is shown in (A). (B) shows the numerically computed chord conductance, which is defined as  $I/\Delta V$ . Incremental conductance is defined to be  $dI/d\Delta V$ , which is the derivative of the I-V curve. (C) shows the incremental conductance computed using a two-point derivative approximation. Note the two regions of negative incremental conductance in (C).

mentally negative resistance regions (see Figure 4.15) raise doubts about the stability of networks of resistive fuse elements. However, as was discussed in Chapter 1, as long as the nonlinear resistors are externally passive (i.e., their I-V curves lie in the 1st and 3rd quadrants of the I-V plane) and if we can neglect the internal dynamics of the incrementally active resistor circuit, then for any voltage input and any initial condition, the network will not oscillate indefinitely but must eventually settle to some stationary state. This conclusion holds even if parasitic (positive) capacitances are distributed arbitrarily throughout the network, provided there are no inductors. This is a rather surprising result in view of the well-known instability problems with negative incremental resistance circuits.

As was noted in Chapter 1, the notion of minimizing the dissipated power in linear resistive networks must be replaced by the notion of minimizing the co-content (Equation 1.5) in nonlinear resistive networks. With incrementally active resistors, i.e., with regions of negative slope such as in the fuse, there will, in general, exist a number of stationary network solutions for a given input image, and uniqueness is no longer guaranteed.

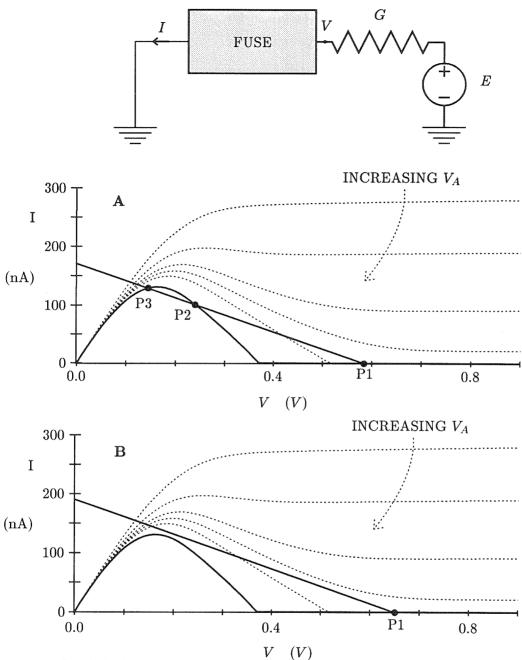

The hysteresis properties of the network can be better understood through a load-line analysis of a much simplified circuit (Figure 4.16). The current through the fuse is plotted as a function of the voltage across the fuse. The simulated voltage source/resistor is also illustrated as a solid line, with the negative slope of this line given by the conductance G and the x-intercept given by the value of the voltage source E. A stability analysis reveals that the system possesses up to three equilibria. In the case illustrated in Figure 4.16A, the middle equilibrium is unstable and the voltage will tend toward the two stable solutions P1 and P2. Point P1 corresponds to segmentation, and P3 corresponds to smoothing. By increasing the value of the voltage source E (Figure 4.16B), only a single stable equilibrium point remains, corresponding to segmentation. Of course, stability cannot be guaranteed for negative values of G. The dotted-line curves show the effect of changing  $V_A$ .

Figure 4.17 shows the computed total co-content from the I-V curves shown in Figure 4.16. For Figure 4.17A, P1 is the global and P3 is only a local minimum, while P2

Figure 4.16: Simple load-line analysis shows that there can be up to three equilibrium points for the fuse/resistor circuit given above. The I-V curves for the measured fuse and the simulated voltage source/resistor are shown as solid lines. For plot A, points P1 and P3 are stable, and P2 is unstable. Voltages in the neighborhood of P2 will be driven to either P1 or P3. By increasing the value of the voltage source E, a single stable equilibrium point P1 remains (plot B). The dotted-line curves show the effect of changing  $V_A$ .

Figure 4.17: Computed total co-content J from the I-V curves shown in Figure 4.16. In plot A, P1 and P3 correspond to stable minima while P2 is an unstable maximum. In contrast, Plot B contains a single equilibrium point P1 that corresponds to a discontinuity. The dotted lines show the effect of increasing  $V_A$ .

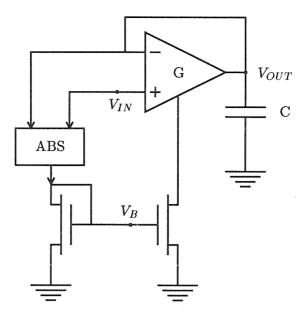

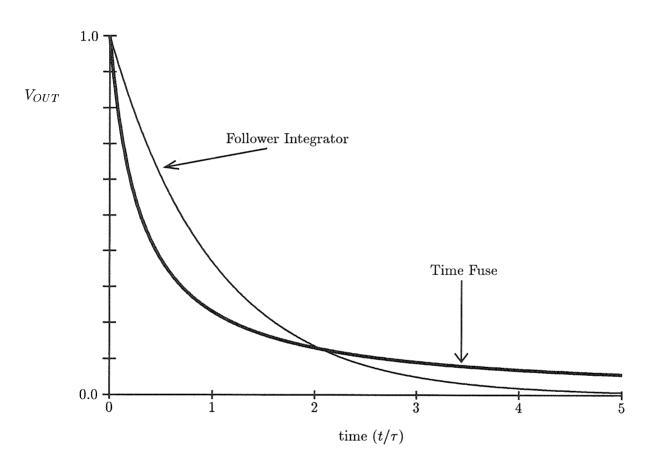

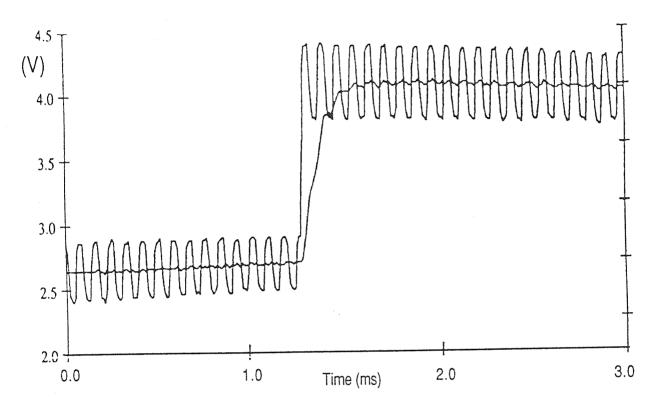

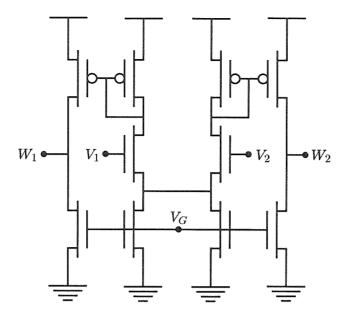

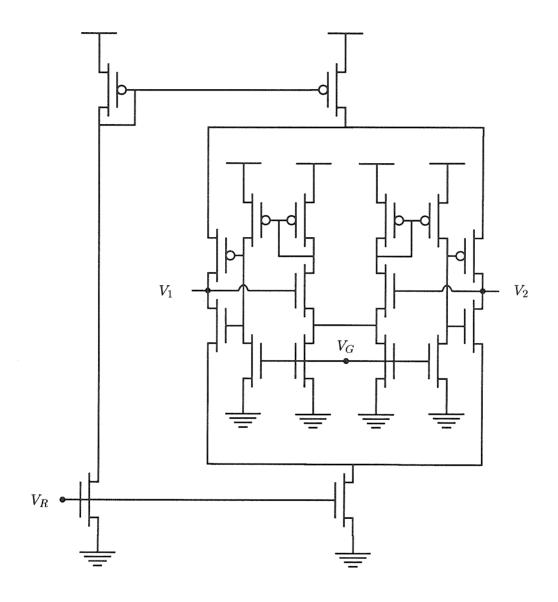

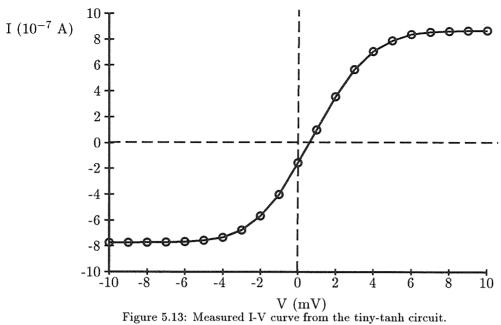

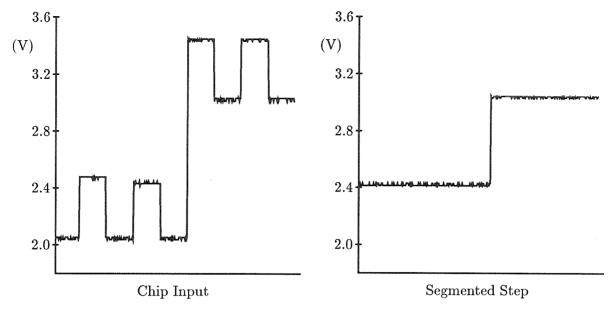

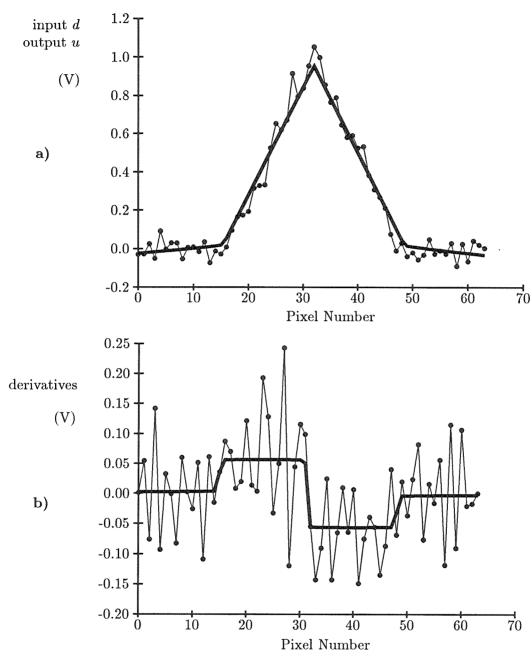

corresponds to an unstable local maximum. In contrast, Figure 4.17B contains a single equilibrium point, P1, which corresponds to a discontinuity. The dotted lines show the effect of increasing  $V_A$ , deforming the energy surface from one with a single equilibrium point to one with two local minima. By using a continuation method in this fashion, discontinuities are deterministically located. Reasonable performance may be obtained by using a single setting of the fuse control voltages and keeping the voltages constant over time. This static approximation of the continuation method will still smooth small step edges while preserving large steps. However, medium steps, such as those simulated in Figure 4.16, can be either smoothed or segmented depending upon the temporal history of the network. This load-line analysis is a simplified version of the true dynamics of networks of fuse elements, but serves to illustrate the complexity of even a single fuse element circuit.