# Control Art of Switching Converters

Thesis by

Keyue Ma Smedley

In Partial Fulfillment of the Requirements

for the Degree of

Doctor of Philosophy

California Institute of Technology

Pasadena, California

1991

(Submitted June 21, 1990)

© 1991

Keyue Ma Smedley

All Rights Reserved

Dedicated to My Mother Wanhua Ma

iv

# Acknowledgements

I wish to thank my advisor, Professor Slobodan Ćuk and Professor R. D. Middlebrook, for accepting me as the first woman graduate student in the Caltech Power Electronics Group, and for their guidance, support and encouragement.

I gratefully acknowledge the financial support of Caltech, in the form of a Graduate Teaching Assistantship, Research Assistantship, and Powell Fellowship.

I would like to thank my colleagues in the Power Electronics Group and my friends at Caltech. Their friendship and support made my stay at Caltech an enjoyable and memorable experience. Special thanks go to Milivojo Brković and Narayana Sateesh Pillai for their generous help with the buck converter experimental circuits.

Credit is also due my former university adviser, Professor Shipeng Huang of Zhejiang University China, for accepting me as the first woman graduate student in the field of Power Electronics in China.

I am deeply grateful to my mother, Wanhua Ma. Without her love and encouragement, study at Caltech would never have been possible.

Finally and most importantly, I would like to thank my husband, Dr. Greg Smedley, for his love, understanding, and support. I greatly appreciate his valuable help in drawing figures, writing data-transfer programs, and editing the thesis.

#### Abstract

# Switching Flow-Graph Model

The Switching Flow-Graph is a unified graphical model of large-signal, small-signal and steady-state behavior of pulse-width-modulated (PWM) switching converters. Switching branches are introduced into the flow-graph to represent the switches of the PWM switching converters. The Switching Flow-Graph model is easy to derive, and it provides a visual physical understanding of switching converter systems. The small-signal Switching Flow-Graph generates analytical transfer functions and the large-signal Switching Flow-Graph is compatible with the TUTSIM simulation program. The Switching Flow-Graphs of PWM switching converters reveal a regular pattern, and they predict right-half-plane (RHP) zeros, caused by the imbalanced effects of the duty-ratio control signal on the output of the switching converters. Criteria are found for the design of damping circuits that are capable of eliminating RHP zeros. General models are derived for current-mode controlled switching converters. In addition, the large-signal model and the small-signal model are verified by experiments.

### One-Cycle Control Technique

The One-Cycle Control technique is conceived to control the duty-ratio d of the switch in real time such that in each cycle the average of the chopped waveform at the switch output is exactly equal to the control reference. Implementation circuits are found for any type of switch, constant frequency, constant ON-time, constant OFF-time, and

variable. One-Cycle Control fully rejects the input signal, and linearly all passes the control signal. This technique turns a nonlinear switch into a linear one. Experiments were conducted using the One-Cycle Control technique on the buck converter and the Ćuk converter. One-Cycle Control was found to reject input perturbations and input filter dynamics. The diode voltage of One-Cycle Controlled converters follows the control reference instantaneously in one cycle. One-Cycle Control takes advantage of the pulsed and nonlinear nature of switching converters to achieve instantaneous control of the average value of the diode voltage. This technique is suitable for large-signal control of PWM switching converters and quasi-resonant converters.

# Contents

| A | Acknowledgements |                                                    | v   |

|---|------------------|----------------------------------------------------|-----|

| A | bstra            | act                                                | vii |

| 1 | Int              | roduction                                          | 1   |

|   | 1.1              | Object                                             | 1   |

|   | 1.2              | Background                                         | 3   |

|   | 1.3              | Outline of the Thesis                              | 6   |

|   |                  |                                                    |     |

| Ι | Sw               | itching Flow-Graph Model                           | 11  |

| 2 | Swi              | tching Flow-Graph Modelling Technique              | 13  |

|   | 2.1              | Flow-Graph Background                              | 13  |

|   | 2.2              | Switching Flow-Graph                               | 16  |

|   | 2.3              | Switches                                           | 21  |

|   | 2.4              | Large-Signal Model of Switching Converters         | 24  |

|   | 2.5              | Steady-State Model                                 | 28  |

|   | 2.6              | Small-Signal Model                                 | 30  |

|   | 2.7              | Extra-Element Theory of the Flow-Graph             | 34  |

|   | 2.8              | Summary                                            | 36  |

| 3 | Мо               | delling Pulse-Width-Modulated Switching Converters | 39  |

|    | 3.1 | Modelling Second-Order PWM Switching Converters           | 39 |

|----|-----|-----------------------------------------------------------|----|

|    | 3.2 | Modelling Fourth-Order PWM Converters                     | 44 |

|    | 3.3 | Simplification of the Small-Signal Switching Flow-Graphs  | 49 |

|    | 3.4 | Experimental Verification                                 | 54 |

|    | 3.5 | Summary                                                   | 65 |

| 4  | Rig | ht-Half-Plane Zero Study                                  | 37 |

|    | 4.1 | The Physical Interpretation of Right-Half-Plane Zeros     | 37 |

|    | 4.2 | Detection of the Right-Half-Plane Zeros                   | 71 |

|    | 4.3 | Damping Technique to Eliminate the Right-Half-Plane Zeros | 77 |

|    | 4.4 | Summary                                                   | 32 |

| 5  | Ger | neral Model for Converters with Current-Mode Control 8    | 33 |

|    | 5.1 | Switching Converter Power-Stage 8                         | 33 |

|    | 5.2 | Current-Mode Control Loop                                 | 34 |

|    | 5.3 | General Model of Current-Mode Control                     | 37 |

|    | 5.4 | Current-Mode Control of Converters with RHP Zeros         | 95 |

|    | 5.5 | Summary                                                   | )3 |

| II | 0   | ne-Cycle Control Technique 10                             | 15 |

| 6  | One | e-Cycle Control Technique                                 | 7  |

|    | 6.1 | General Concept of One-Cycle Control                      | )8 |

|    | 6.2 | One-Cycle Controlled Switches                             | 10 |

|    | 6.3 | One-Cycle Control Operating Process                       | 18 |

|    | 6.4 | Summary                                                   | 21 |

| 7                      | One  | e-Cycle Control of Pulse-Width-Modulated Switching Converters   | 123 |

|------------------------|------|-----------------------------------------------------------------|-----|

|                        | 7.1  | Task of Control Loops                                           | 124 |

|                        | 7.2  | One-Cycle Control                                               | 125 |

|                        | 7.3  | The Effect of the Input Low-Pass Filter                         | 134 |

|                        | 7.4  | The Effect of the Output Low-Pass Filter                        | 138 |

|                        | 7.5  | Comparison with Pulse-Width-Modulation and Current-Mode Control | 140 |

|                        | 7.6  | Experiments of One-Cycle Controlled Buck Converter              | 146 |

|                        | 7.7  | Summary                                                         | 158 |

| 8                      | Stal | pility of One-Cycle Controlled Pulse-Width-Modulated Converters | 161 |

| •                      | 8.1  | One-Cycle Controlled Switch in Converters                       | 161 |

|                        | 8.2  | Global Stability of the One-Cycle Controlled Ćuk Converter      | 163 |

|                        | 8.3  | Local Dynamic Behavior                                          | 167 |

|                        | 8.4  | Experiments                                                     | 171 |

|                        | 8.5  | Summary                                                         | 179 |

| 9                      | One  | -Cycle Control Circuit Design                                   | 181 |

|                        | 9.1  | Limitation of the Switching Duty-Ratio                          | 181 |

|                        | 9.2  | Condition of Discontinuous Conduction                           | 186 |

|                        | 9.3  | Integrator Design                                               | 187 |

|                        | 9.4  | Summary                                                         | 191 |

| 10                     | Con  | clusion                                                         | 193 |

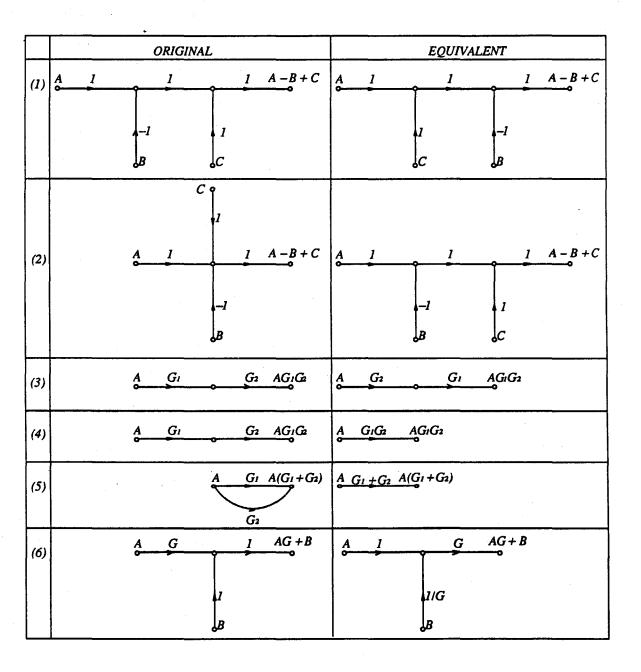

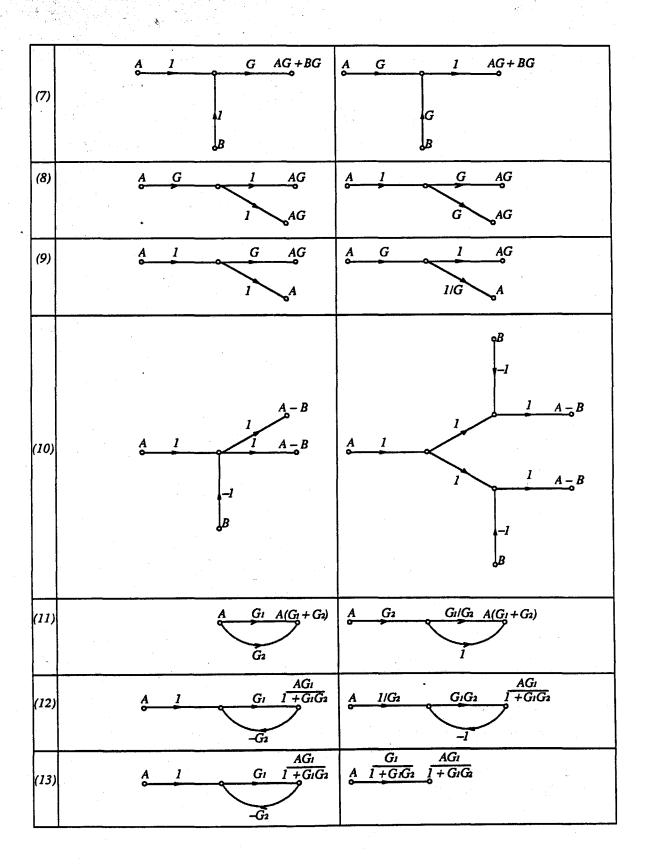

| A                      | The  | Algebraic Rules of the Flow-Graph                               | 197 |

| $\mathbf{R}\mathbf{e}$ | fere | nces                                                            | 199 |

# List of Figures

| 1.1  | Switching Converter                                            | . 1 |

|------|----------------------------------------------------------------|-----|

| 1.2  | Sliding-Mode Control Concept                                   | 5   |

| 1.3  | Constant Frequency Sliding-Mode Control                        | 5   |

|      |                                                                |     |

| 2.1  | The RC Circuit                                                 | 14  |

| 2.2  | Flow-Graph of the RC Circuit.                                  | 15  |

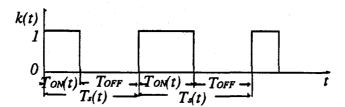

| 2.3  | Switching Functions                                            | 17  |

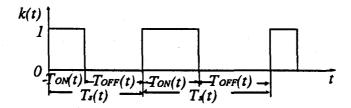

| 2.4  | The Switching Branches: $k$ and $\overline{k}$                 | 18  |

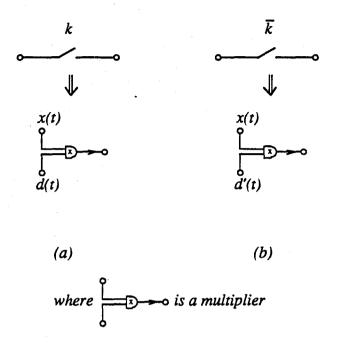

| 2.5  | The Buckboost Converter and its Subcircuits                    | 19  |

| 2.6  | The Switching Flow-Graph of the Buckboost Converter            | 20  |

| 2.7  | The Simplified Switching Flow-Graph of the Buckboost Converter | 21  |

| 2.8  | The Constant Frequency Switch                                  | 22  |

| 2.9  | The Constant ON-Time Switch                                    | 22  |

| 2.10 | The Constant OFF-Time Switch                                   | 23  |

| 2.11 | The Variable Switch                                            | 23  |

| 2.12 | The Signal Flow of the Switching Branches                      | 24  |

| 2.13 | The Large-Signal Models of the Switching Branches              | 26  |

| 2.14 | The Large-signal Model of the Buckboost Converter              | 27  |

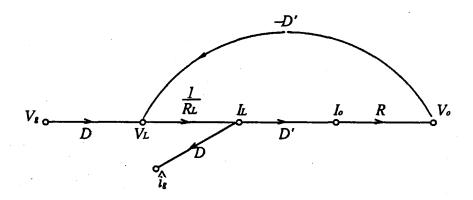

| 2.15 | The Steady-State Models of the Switching Branches              | 29  |

| 2.16 | The Steady-State Model of the Buckboost Converter              | 29  |

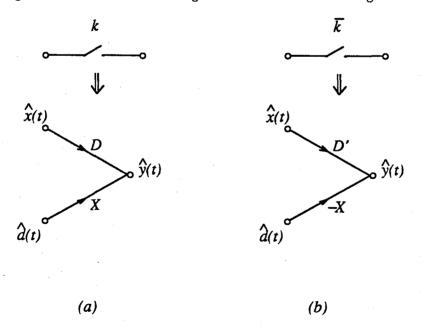

| 2.17 | The Small-Signal Models of the Switching Branches              | 31  |

| 2.18 | The Small-Signal Model of the Buckboost Converter                                | 32 |

|------|----------------------------------------------------------------------------------|----|

| 2.19 | The Simplified Small-Signal Model of the Buckboost Converter                     | 32 |

| 2.20 | The Parallel Extra-Element                                                       | 34 |

| 2.21 | The Series Extra-Element                                                         | 36 |

| 3.1  | The Basic Second-Order PWM Converter                                             | 40 |

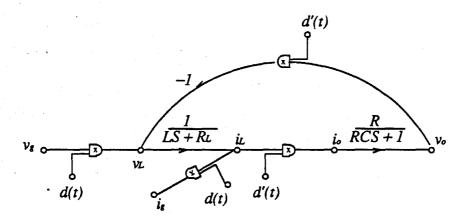

| 3.2  | The Switching Flow-Graphs of the Second-Order PWM Converters                     | 41 |

| 3.3  | The Large-Signal Models of the Second-Order PWM Converters                       | 42 |

| 3.4  | The Small-Signal Models of the Second-Order PWM Converters                       | 43 |

| 3.5  | The Fourth-Order PWM Converters                                                  | 45 |

| 3.6  | The Switching Flow-Graphs of the Fourth-Order PWM Converters                     | 46 |

| 3.7  | The Large-Signal Models of the Fourth-Order PWM Converters                       | 47 |

| 3.8  | The Small-signal Models of the Fourth-Order PWM Converters                       | 48 |

| 3.9  | Reduce the Switching Flow-Graph of the Buck Converter with Input Filter          | 51 |

| 3.10 | The Small-Signal Transfer Functions of the Second-Order PWM Converters           | 52 |

| 3.11 | The Small-Signal Transfer Functions of the Fourth-Order PWM Converters           | 53 |

| 3.12 | The Experimental Buck Converter with an Input Filter                             | 56 |

| 3.13 | The Large-Signal Model of the Buck Converter with an Input Filter                | 56 |

| 3.14 | The Input Format of The TUTSIM Program                                           | 57 |

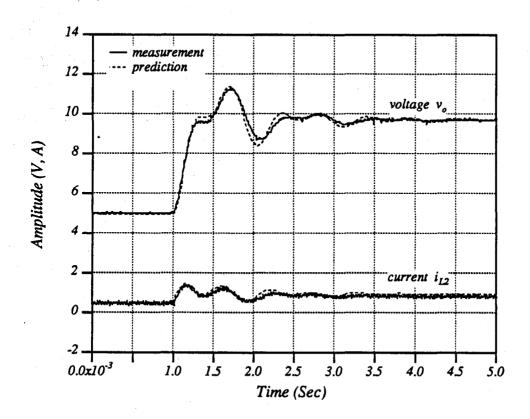

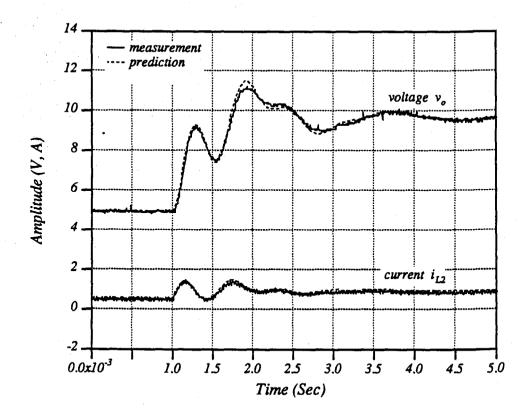

| 3.15 | The Predicted and Measured Large-Signal Step Response                            | 58 |

| 3.16 | The Predicted and Measured Large-Signal Step Response                            | 59 |

| 3.17 | The Predicted and Measured Large-Signal Step Response                            | 60 |

| 3.18 | The Small-Signal Model of the Buck Converter with an Input Filter                | 62 |

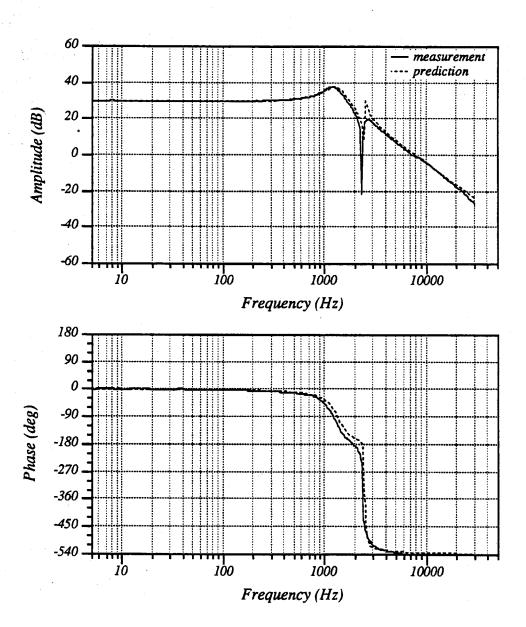

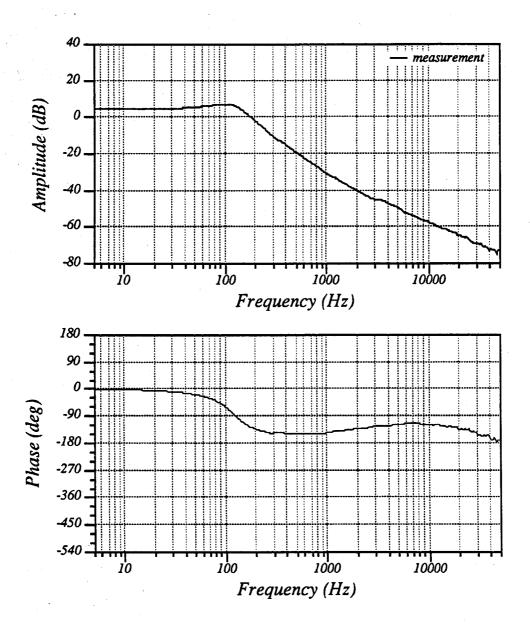

| 3.19 | The Predicted and Measured Frequency Response of $\frac{\hat{v}_o}{\hat{d}}$     | 63 |

|      | The Predicted and Measured Frequency Response of $\frac{\hat{i}_{t_2}}{\hat{d}}$ |    |

| 4.1  | The Boost Converter and its Small-Signal Model                                   | 69 |

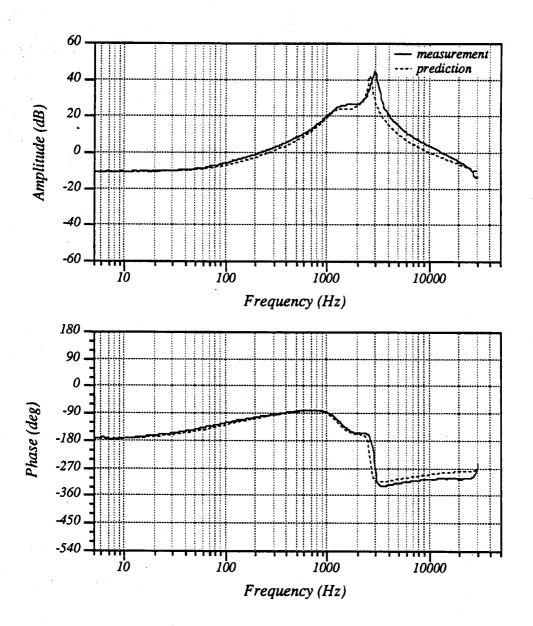

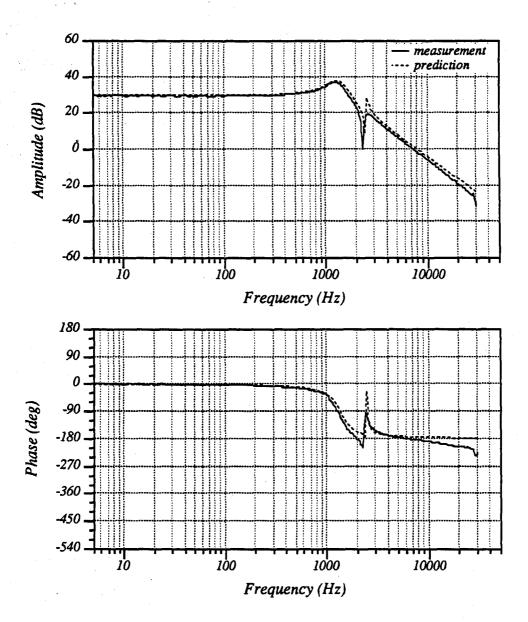

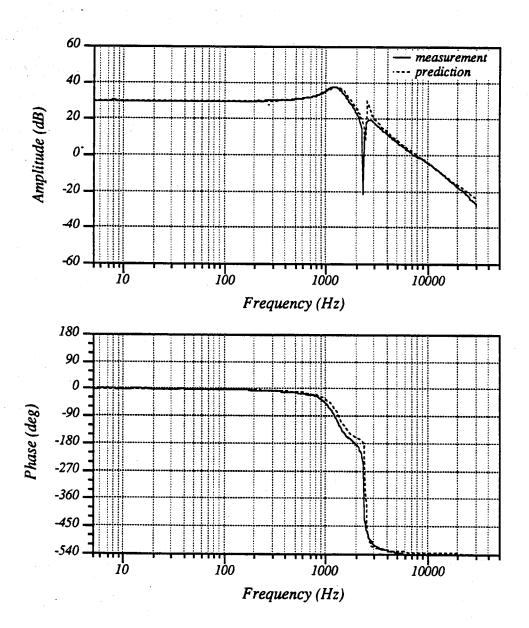

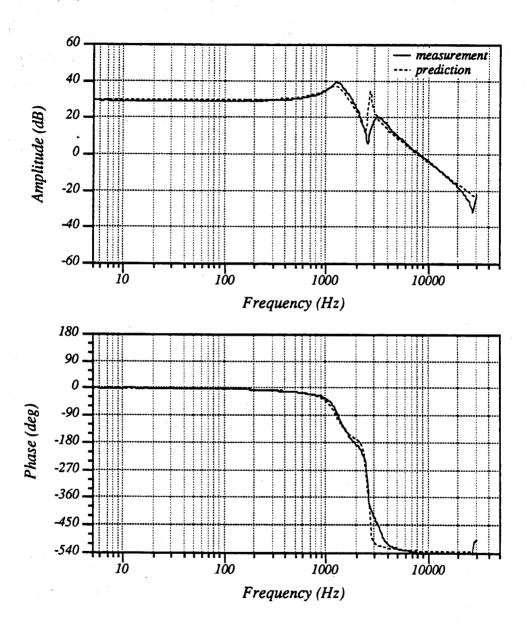

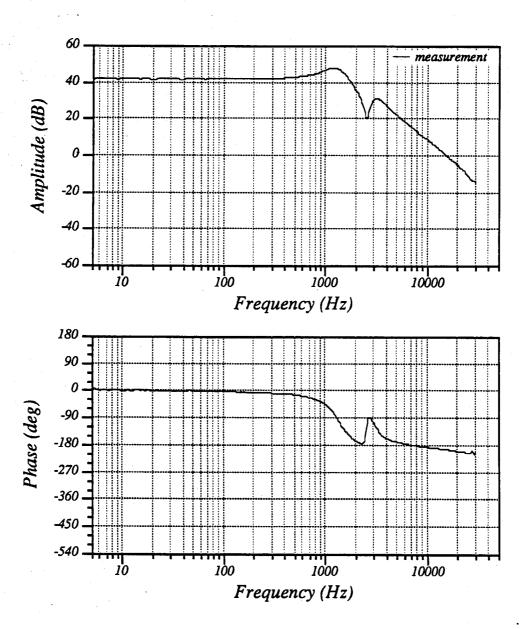

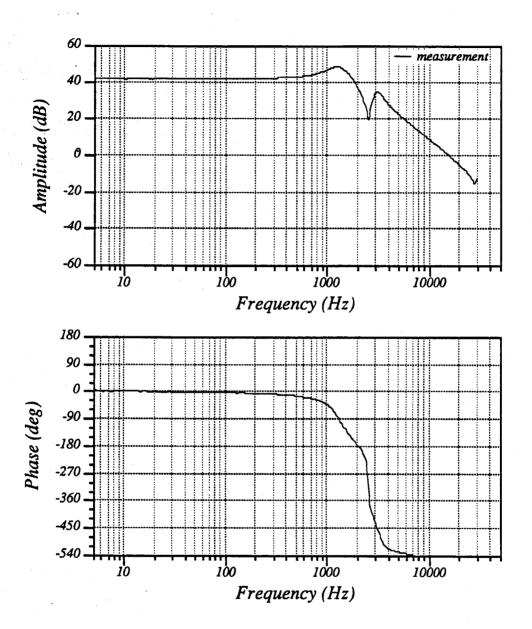

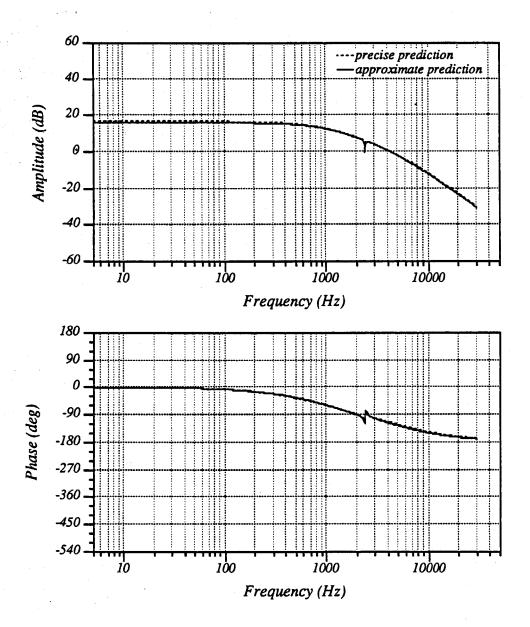

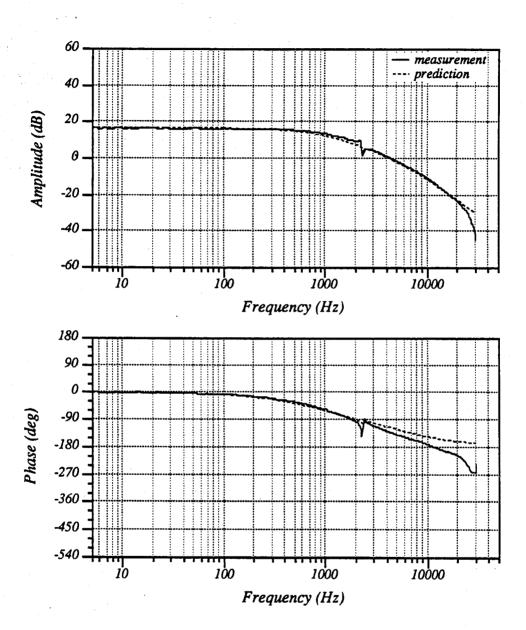

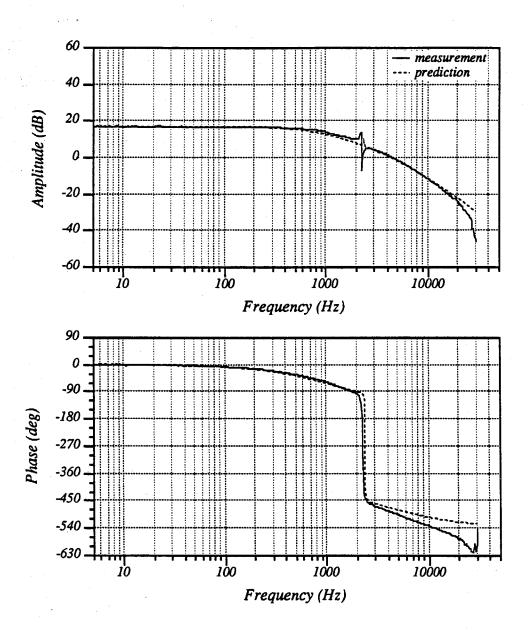

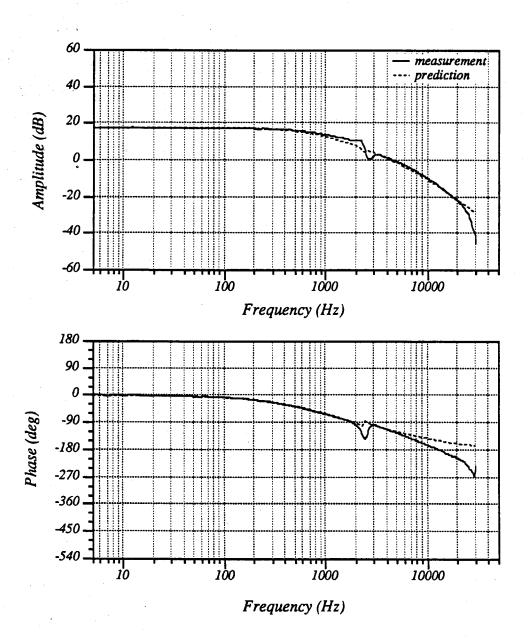

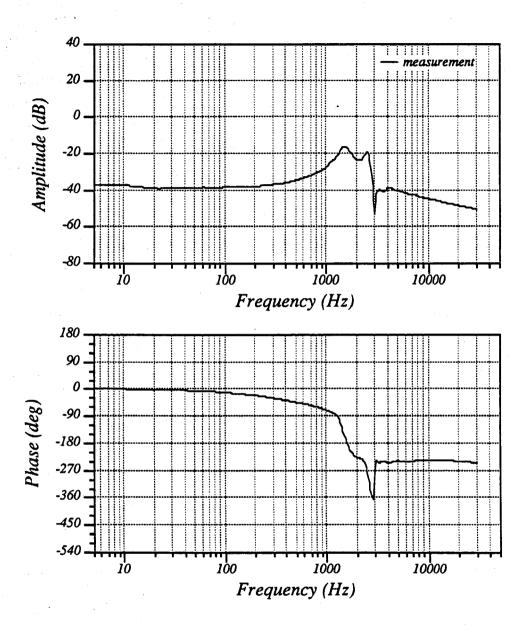

| 4.2  | The Predicted and Measured Frequency Response when D=0.2              | 73  |

|------|-----------------------------------------------------------------------|-----|

| 4.3  | The Predicted and Measured Frequency Response when D=0.23             | 74  |

| 4.4  | The Predicted and Measured Frequency Response when D=0.27             | 75  |

| 4.5  | The Predicted and Measured Frequency Response when D=0.4              | 76  |

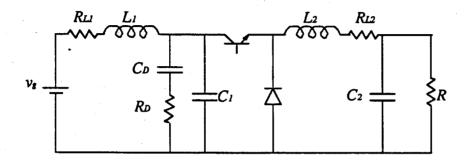

| 4.6  | The Damping Circuit for the Buck Converter                            | 78  |

| 4.7  | The Measured Frequency Response when the Damping Condition is Sat-    |     |

|      | isfied                                                                | 80  |

| 4.8  | The Measured Frequency Response when the Damping Condition is not     |     |

|      | Satisfied                                                             | 81  |

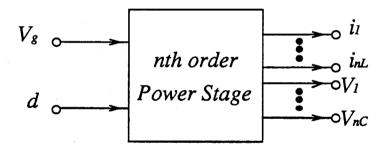

| 5.1  | The nth-Order Power Stage                                             | 84  |

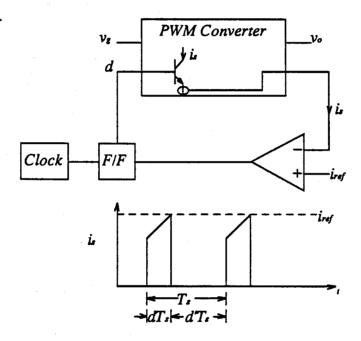

| 5.2  | Block Diagram of Current-Mode Control                                 | 85  |

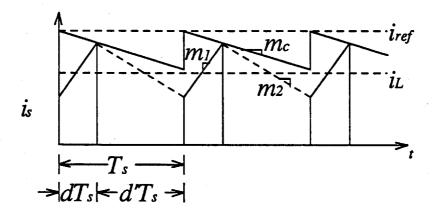

| 5.3  | The Geometric Function of Current-Mode Control                        | 86  |

| 5.4  | The Converter System                                                  | 88  |

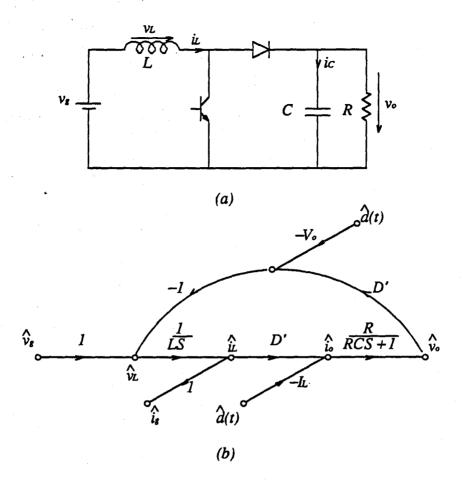

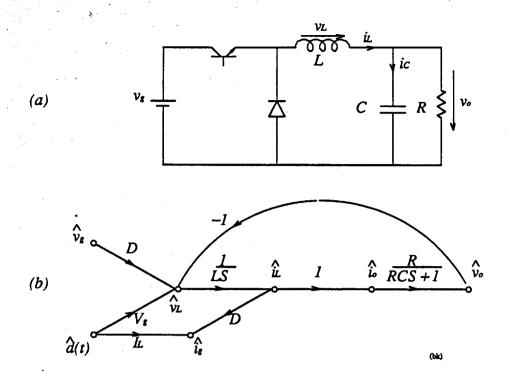

| 5.5  | The Buck Converter and its Small-Signal Model                         | 93  |

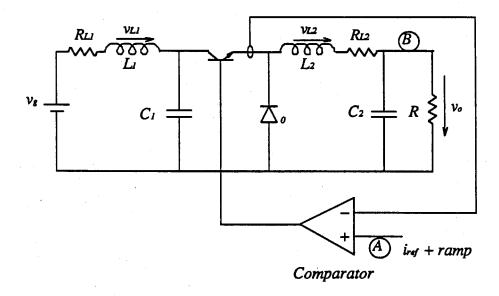

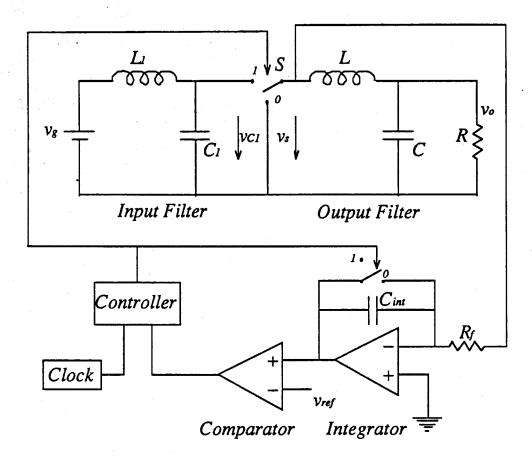

| 5.6  | The Current-Mode-Controlled Buck Converter with Input Filter          | 95  |

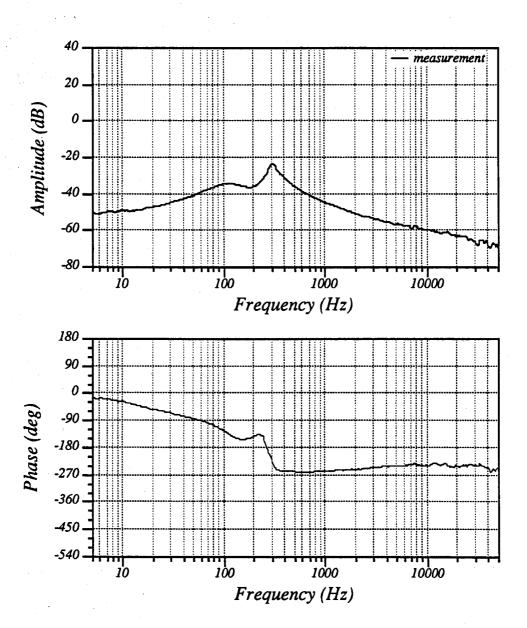

| 5.7  | Frequency Response of the Current-Mode-Controlled Buck Converter with |     |

|      | Input Filter                                                          | 98  |

| 5.8  | The Frequency Response of the Current-Mode-Controlled Buck Converter  |     |

|      | with Input Filter                                                     | 100 |

| 5.9  | The Frequency Response of the Current-Mode Controlled Buck Converter  |     |

|      | with Input Filter                                                     | 101 |

| 5.10 | The Frequency Response of the Current-Mode Controlled Buck Converter  |     |

|      | with Input Filter                                                     | 102 |

| 6.1  | The Switch                                                            | 108 |

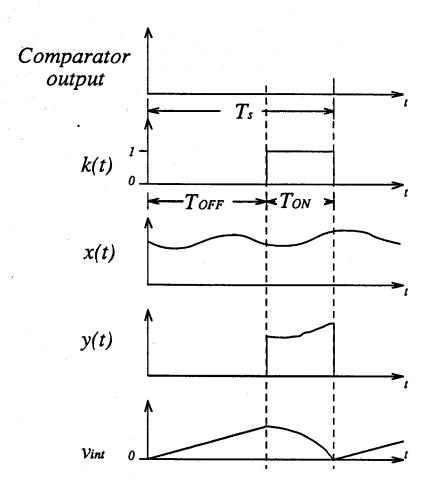

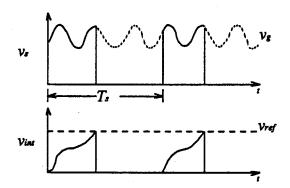

| 6.2  | The One-Cycle Controlled Constant Frequency Switches                  | 111 |

| 6.3  | The Waveform of One-Cycle Controlled Constant Frequency Switches 112          |

|------|-------------------------------------------------------------------------------|

| 6.4  | The One-Cycle Controlled Constant ON-Time Switches                            |

| 6.5  | The Waveform of One-Cycle Controlled Constant ON-Time Switches 114            |

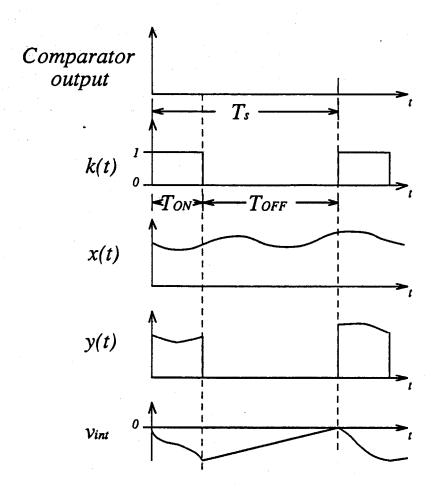

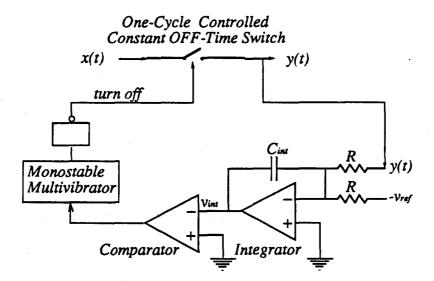

| 6.6  | The One-Cycle Controlled Constant OFF-Time Switches                           |

| 6.7  | The Waveform of One-Cycle Controlled Constant OFF-Time Switches 116           |

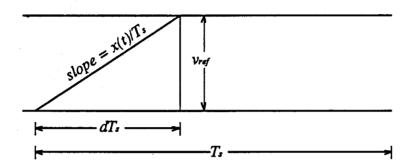

| 6.8  | The Triangle Rule of Constant Frequency One-Cycle Control                     |

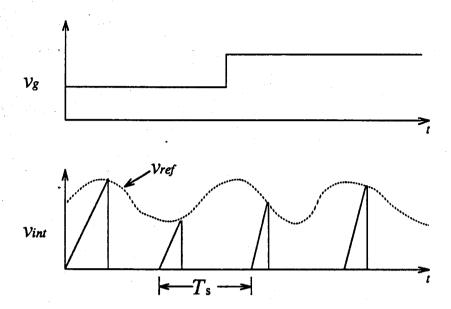

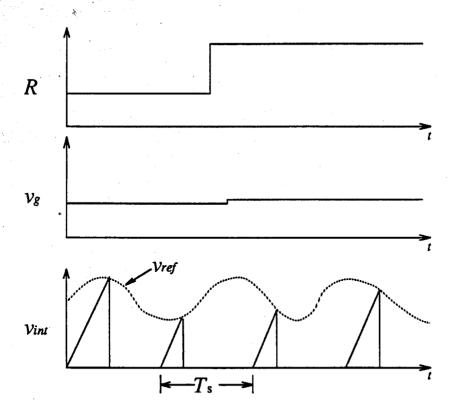

| 6.9  | Input Signal Perturbation is Rejected by One-Cycle Control                    |

| 6.10 | Follow the Control Signal in One Cycle                                        |

| 6.11 | Follow the Control Signal and Reject the Input Signal Perturbation 120        |

| 7.1  | The Buck Converter                                                            |

| 1.1  | The Buck Converter                                                            |

| 7.2  | The Working Waveforms of the Buck Converter                                   |

| 7.3  | One-Cycle Control of Buck Converter                                           |

| 7.4  | Diode-Voltage Waveform of the Buck Converter                                  |

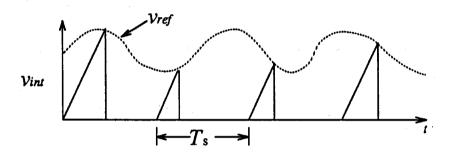

| 7.5  | Rejection of Input-Voltage Perturbations                                      |

| 7.6  | High Frequency Input-Perturbation Rejection                                   |

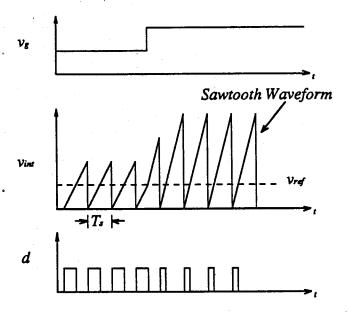

| 7.7  | Integrated Input Voltage Feedforward Control of Buck Converter 131            |

| 7.8  | The Saw-Tooth of Feedforward Buck Converter                                   |

| 7.9  | Following the Control Signal in One Cycle                                     |

| 7.10 | Following the Control Signal and Rejecting the Input Voltage Perturbation 134 |

| 7.11 | Following the Control Signal and Rejecting the Load Disturbance 135           |

| 7.12 | Buck Converter with Input Filter                                              |

| 7.13 | The Working Waveform of the Buck Converter with Input Filter 136              |

| 7.14 | One-Cycle Control of the Buck Converter with Input Low-Pass Filter 137        |

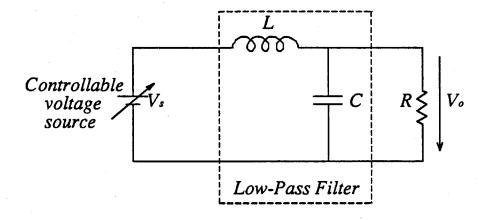

| 7.15 | The Equivalent Circuit for Buck Converter with One-Cycle Control 138          |

| 7.16 | Second-Order System Responses                                                 |

| 7.17 | Feedback Control of The Buck Converter                                       |

|------|------------------------------------------------------------------------------|

| 7.18 | Transient Response Caused by Input-Voltage Perturbation                      |

| 7.19 | Current-Mode Control of the Buck Converter                                   |

| 7.20 | Current-Mode Control Function                                                |

| 7.21 | The Response of Current-Mode Control to the Input Perturbation 144           |

| 7.22 | Current-Mode Control of Buck Converter with Artificial Ramp 146              |

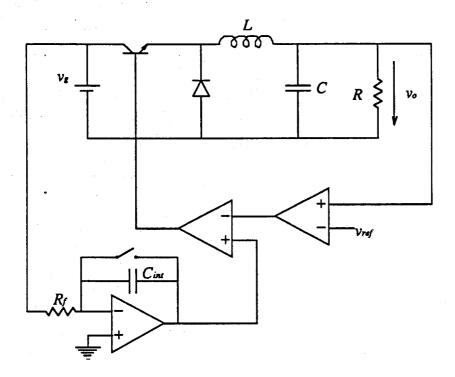

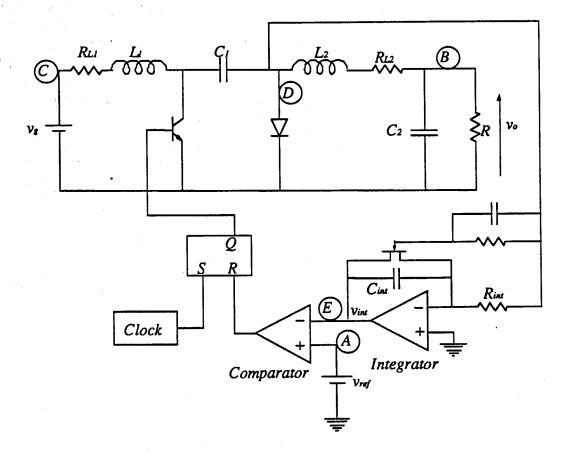

| 7.23 | The Experimental Buck Converter with One-Cycle Control 147                   |

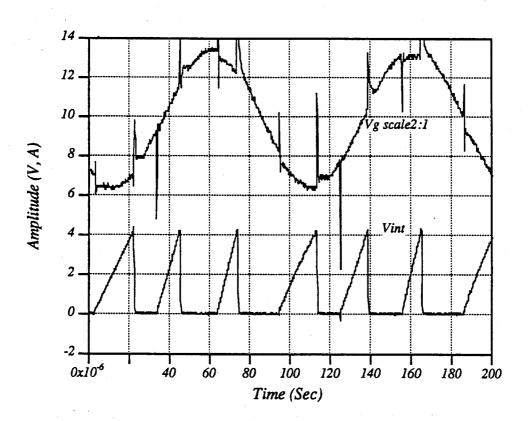

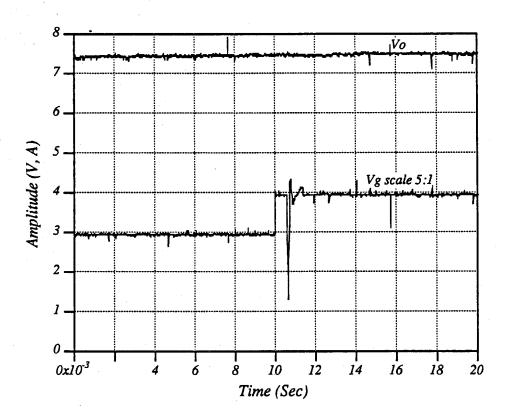

| 7.24 | The Response of the Buck Converter to a Step-Up of the Control Reference 149 |

| 7.25 | Buck Converter Rejects a Step-Up in the Input Voltage                        |

| 7.26 | Buck Converter Rejects a Sinusoid Change in the Input Voltage 151            |

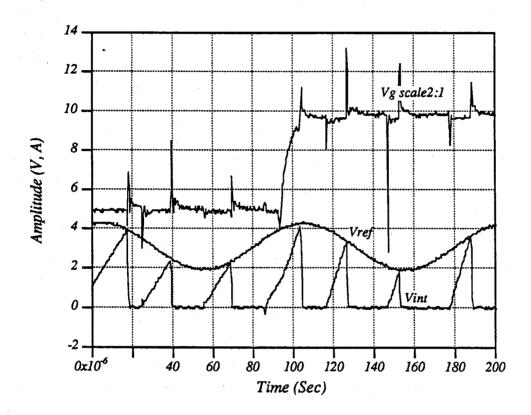

| 7.27 | Buck Converter Response to a Step-Up in the Input Voltage and a Sinusoid     |

|      | Change in the Control Reference                                              |

| 7.28 | The Response of the Buck Converter to a Sinusoid Change in the Input         |

|      | Voltage and a Step-up in the Load Resistance                                 |

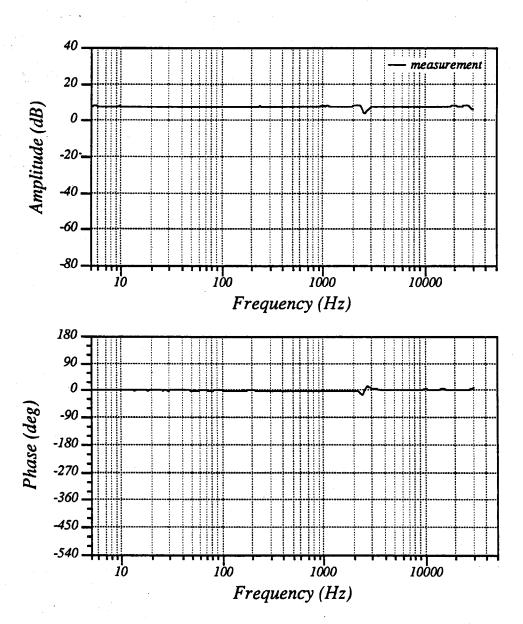

| 7.29 | Control-to-Diode-Voltage Frequency Response of Buck Converter with In-       |

|      | put Filter                                                                   |

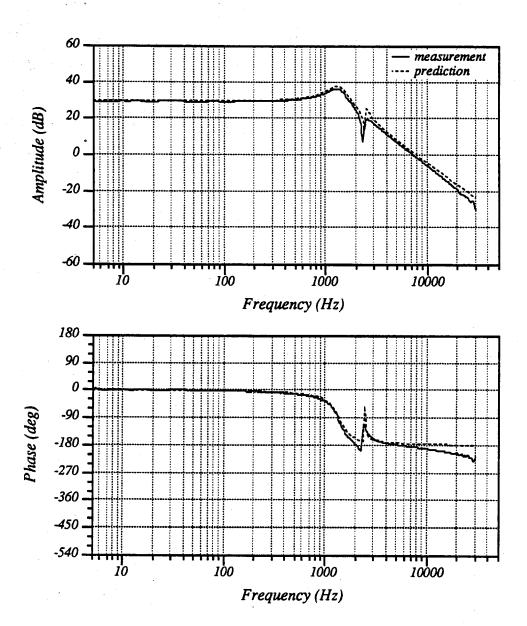

| 7.30 | Control-to-Output Frequency Response of Buck Converter with Input Filter 156 |

| 7.31 | Input-to-Output Frequency Response of Buck Converter with Input Filter 157   |

| 8.1  | Diode-Voltage One-Cycle Control                                              |

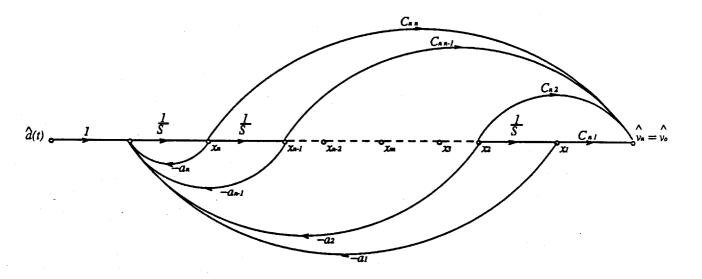

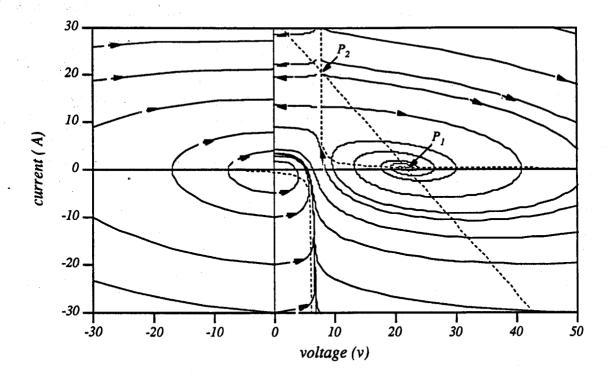

| 8.2  | The Large-Signal Model of the One-Cycle Controlled Ćuk converter 164         |

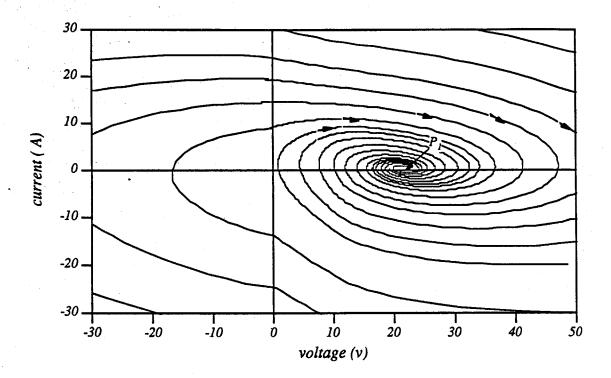

| 8.3  | The Global Dynamic Behavior of the One-Cycle Controlled Ćuk Converter 165    |

| 8.4  | The Global Dynamic Behavior with Duty-Ratio Limitation 166                   |

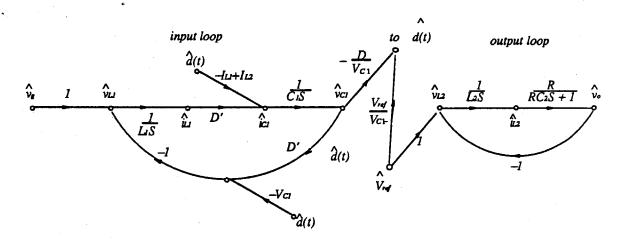

| 8.5  | The Small-Signal Model of One-Cycle Controlled Ćuk Converter 168             |

| 8.6  | The Loop-Gain of the One-Cycle Controlled Ćuk Converter 169                  |

| 8.7  | Take Advantage of the Pulsed and Nonlinear Nature                            |

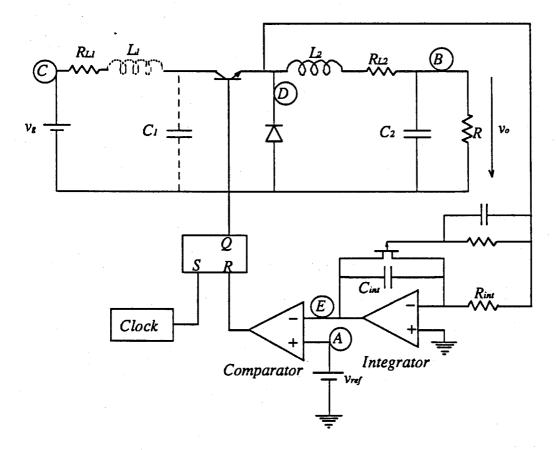

| 8.8  | The Experimental Cuk Converter with One-Cycle Control 172                |

|------|--------------------------------------------------------------------------|

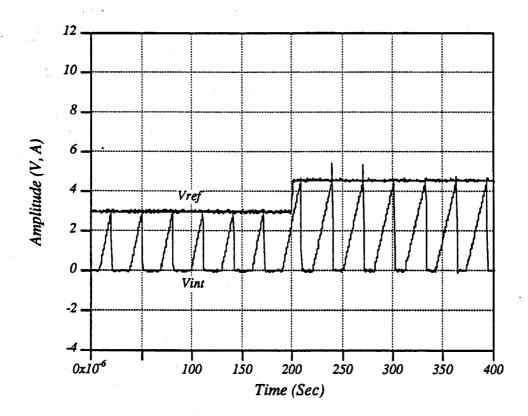

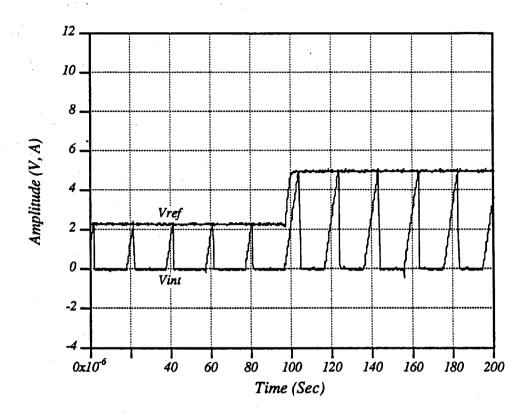

| 8.9  | Ćuk Converter Follows Step-up of the Control Reference 173               |

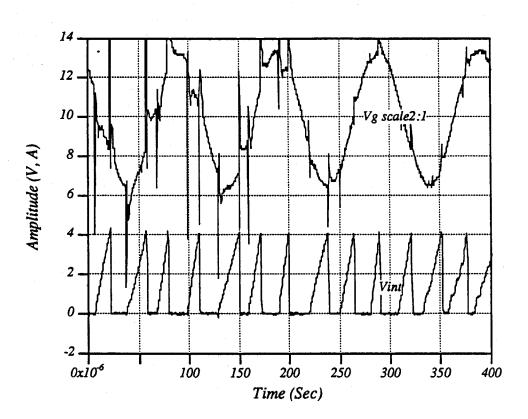

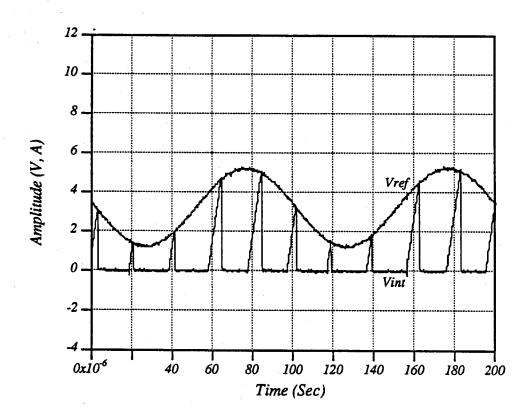

| 8.10 | Ćuk Converter Follows Sinusoid Change of Control Reference 174           |

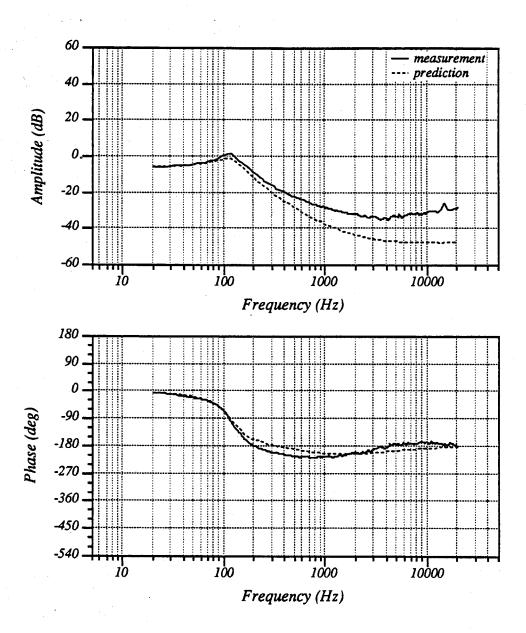

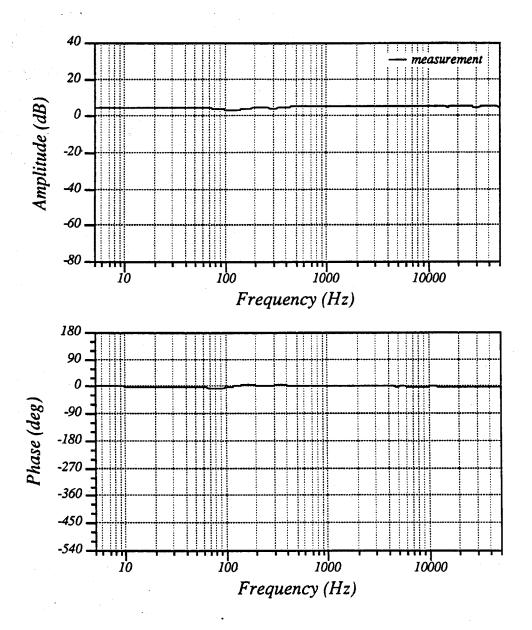

| 8.11 | The Control-to-Diode-Voltage Frequency Response of the One-Cycle Con-    |

|      | trolled Ćuk Converter                                                    |

| 8.12 | The Control-to-Output Frequency Response of the One-Cycle Controlled     |

|      | Ćuk Converter                                                            |

| 8.13 | The Input-to-Output Frequency Response of the One-Cycle Controlled       |

|      | Ćuk Converter                                                            |

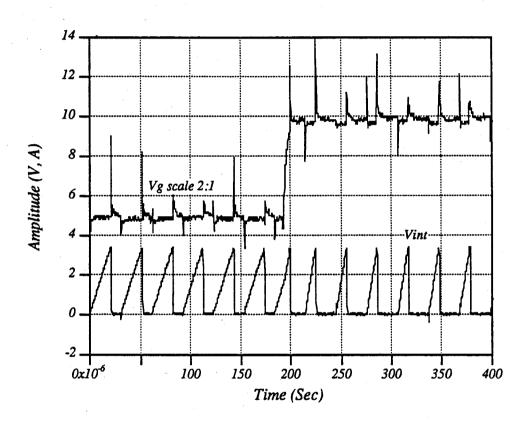

| 8.14 | The Input-to-Output Step Up Response of the One-Cycle Controlled Ćuk     |

|      | Converter                                                                |

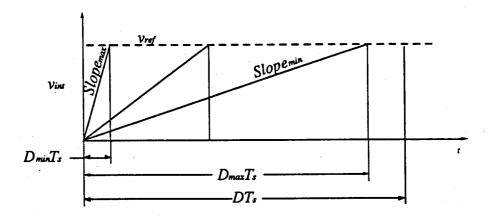

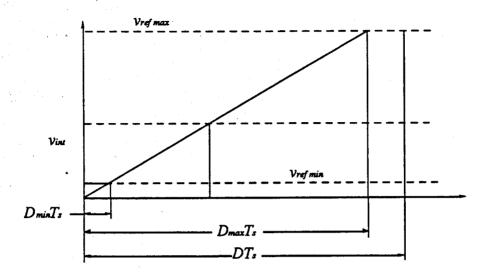

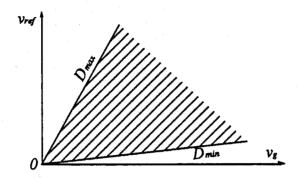

| 9.1  | The Allowable Operating Range of the Input Voltage of Buck Converter 182 |

| 9.2  | The Allowable Range of the Control Reference of Buck Converter 183       |

| 9.3  | One-Cycle Control Operation Region of Buck Converter                     |

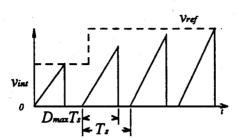

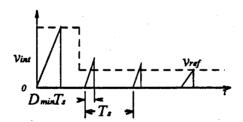

| 9.4  | One-Cycle Controlled Ćuk Converter Operates under the Maximum Duty-      |

|      | Ratio                                                                    |

| 9.5  | One-Cycle Controlled Ćuk Converter Operates under the Minimum Duty-      |

|      | Ratio                                                                    |

| 9.6  | One-Cycle Control of Buck Converter at Discontinuous Conducting Con-     |

|      | dition                                                                   |

| 9.7  | The Real-Time Integrator                                                 |

| 9.8  | Integration Error due to Finite DC Gain                                  |

| 9.9  | Integration Error due to Finite Bandwidth                                |

## Chapter 1

# Introduction

### 1.1 Object

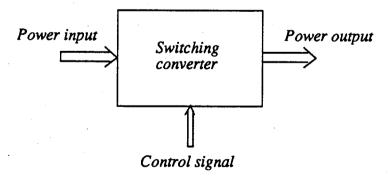

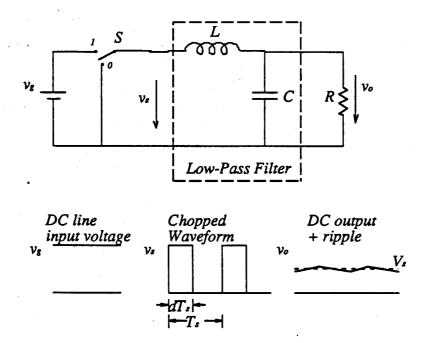

Switching converters, as shown in Fig. 1.1, are power processing units that utilize lossless components, switches, inductors, and capacitors to convert input power to output power with 100 percent efficiency in the ideal case. The input power is generally AC or DC, whereas the output power can be AC, DC, or any desired function. The conversion capability for a particular application is established by the topology of the converter, while the function and quality of the output waveform depends on the control-loop design.

Figure 1.1: Switching Converter. It is a power processing unit. The input power may be AC or DC, the output power may be AC, DC or any desired functions.

In recent years power electronics has been a very active discipline. Many new switching converter topologies have been and are being discovered in both the pulse-width-

modulation (PWM) converter family and the quasi-resonant converter family [1]. The circuits are becoming more complicated; therefore, the modelling tools and the control techniques are confronting new challenges.

Switching converters are pulsed and nonlinear dynamic systems. There has been no standard way to model and control nonlinear systems. People usually avoid the pulsed and nonlinear nature by linearizing the governing equations to obtain small-signal models. Linear feedback control structures are used to control nonlinear systems. If a system is very simple, a satisfactory control loop may be obtained through the use of a small-signal model, a linear control scheme, some previous design experience and a lot of trial and error. However, if the circuit is more complicated, this approach may never achieve a workable solution. First of all, a small-signal model provides only the local dynamic information around the operating point; if the system is perturbed, enough to leave the operating point, the system may not converge. On the other hand, since switching converters are pulsed and nonlinear in nature, their capability is greatly restricted if linear feedback control is applied.

The work in this thesis takes advantage of the pulsed and nonlinear nature of switching converter systems rather than avoiding it. The goal here is to find a suitable way to achieve switching nonlinear control. The motivation is that a switching system under pulsed nature nonlinear control should be more robust, have faster dynamic response and better input perturbation rejection than the same system under linear control.

In Part I, a new unified nonlinear modelling tool, the Switching Flow-Graph technique, is developed and used to reveal the global and local dynamic properties of switching converters. In Part II, a new pulsed nature nonlinear control technique, One-Cycle Control, is conceived based on the understanding gained from the model. The One-Cycle Control technique provides fast dynamic response and good input perturbation rejection.

It can be used to control PWM converters and quasi-resonant converters. A buck converter and a Cuk converter were built to test both the One-Cycle Control technique and the Switching Flow-Graph model.

#### 1.2 Background

A brief review of the previous work on modelling and control techniques of switching converters is given below for comparison to the present work.

#### Small-Signal Modeling Techniques

The state-space averaging method [2] is widely used in industry. This method averages and linearizes the pulsed and nonlinear trajectories in state space. This model provides small-signal predictions with very good accuracy when the signal frequency is lower than half the switching frequency.

The sampled-data modelling method [3] is another small-signal modelling tool that provides better accuracy at high frequency. However, the mathematics are much more complicated than for the state-space averaging method.

The small-signal frequency response theory [4] provides an exact solution to the frequency response problem of DC-to-DC converter systems; however, it is valid only in the small-signal limit.

The small-signal models are linear and hence easily applied to most practical design problems. However, because of the small-signal assumption, these models do not describe the behavior of the switching converter during large transients.

### Large-Signal Modelling Techniques

Robert Erickson developed a large-signal model for state-feedback switching regulators [5]. The model is provided in two forms, a discrete-time equation for use in computer simulations and an analytical matrix expression to enhance physical understanding. However, the model does not provide a general form for large-signal, small-signal, and steady-state analysis.

#### Control Techniques

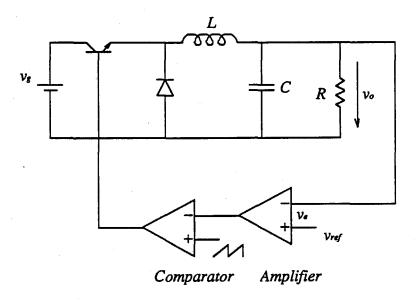

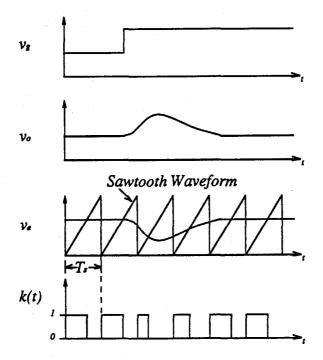

PWM feedback control is a linear error control technique. The output voltage of the switching converter is compared with a control reference. The error between the control reference and the output voltage is amplified and compared with a saw-tooth waveform to adjust the duty-ratio in the direction required to reduce the error. In order to obtain good input perturbation rejection and fast dynamic response to the control reference, the loop-gain must be very high. Unfortunately, high loop-gain may cause circuit instability.

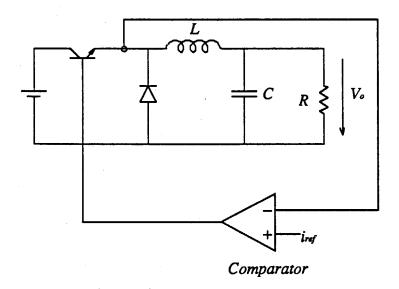

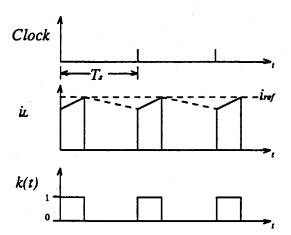

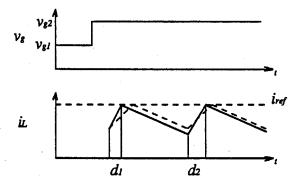

The current-mode control technique, [6][7], includes some pulsed nature control concepts. The switch current is sensed and compared with a control reference. The transistor is turned ON at clock pulses and is turned OFF when the switch current reaches the control reference. This method is equivalent to state-feedback control. A stabilizing ramp is necessary when the system operates at a duty-ratio larger than 0.5. If the slope of the ramp is equal to the falling slope of the inductor currents which flow through the transistor when it is ON, this control technique will reject input perturbations. However, only the buck converters with constant output voltage satisfy this condition.

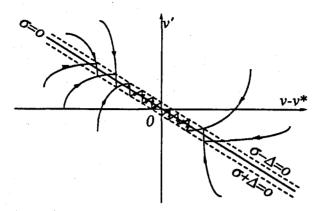

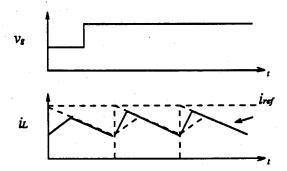

Sliding-mode control [8][9] is based on pulsed and nonlinear nature. A sliding line is defined through the operating point. The switch is turned ON when the trajectories reach the lower limit, and is turned OFF when the trajectories reach the upper limit. The system motion is restricted along the sliding line and within the hysteresis,  $\Delta < \sigma < \Delta$ , as shown in Fig. 1.2. Therefore, the system order is reduced by one. However, the switch operates at a variable frequency.

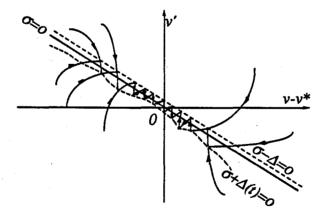

If a variable hysteresis is used to envelope the system motion, as shown in Fig. 1.3,

Figure 1.2: Sliding-Mode Control Concept. A sliding line is defined through the operating point. The switch is turned ON when the trajectories reach the lower limit, and is turned OFF when the trajectories reach the upper limit. Therefore, the system motion is restricted along the sliding line and within the hysteresis,  $\Delta < \sigma < \Delta$ .

Figure 1.3: Constant Frequency Sliding-Mode Control. A variable hysteresis is used to envelope the system motion. The switch is turned ON by the clock pulse, and turned OFF when the trajectories reach the upper limit.

the switching frequency is fixed [10]. In this case, the switch is turned ON by the clock pulse, and turned OFF when the trajectories reach the upper limit. This control function is similar to the one used for current-mode control.

Sliding-mode control is possible only when both the reaching condition and the converging condition are satisfied. When the system order is higher than two, a sliding surface is very hard to find that satisfies both the reaching condition and the converging condition.

#### 1.3 Outline of the Thesis

This thesis contains two parts. The Switching Flow-Graph model is discussed in Part I and the One-Cycle Control technique is presented in Part II. Each Part of the thesis includes both theory and experiments.

#### Part I. Switching Flow-Graph Model

The Switching Flow-Graph technique provides a unified graphical representation of the large-signal nonlinear model, the small-signal model and the steady-state model for any PWM switching converter.

This technique utilizes some concepts from state-space averaging, and is an extension of linear circuit flow-graph theory. Though a switching converter is a nonlinear system, it is equivalent to a linear circuit, the ON-circuit, when the switch is in the ON state, and it is equivalent to another linear circuit, the OFF-circuit, when the switch is in the OFF state. The On-circuit and the OFF-circuit can be described by their respective flow-graphs. The Switching Flow-Graph is obtained by combining the flow-graphs of the ON-circuit and the OFF-circuit through the use of switching branches. The switching branches are the only nonlinear components in the Switching Flow-Graph; therefore,

the modelling work is reduced to the switching branches. Large-signal, small-signal and steady-state representations of the switching branches are given. The Switching Flow-Graph model is very easy to obtain, and it provides a visual means for the physical understanding of switching converter systems. It can predict the large-signal, the small-signal, and the steady-state behavior of switching converter systems. The details are described in Chapter 2.

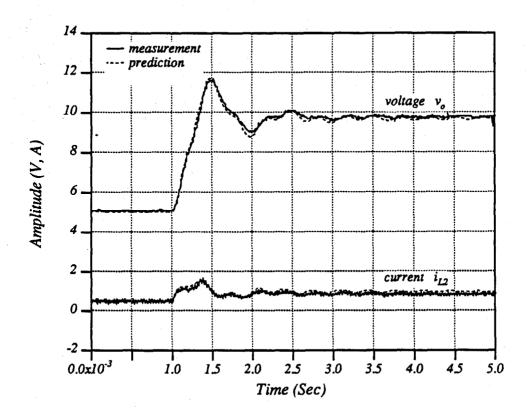

In Chapter 3, the Switching Flow-Graph modelling technique is used to model the most commonly used PWM switching converters in the second-order and fourth-order families. The Switching Flow-Graphs reveal a regular pattern, and generate deeper physical insight into the function of switching converters. The large-signal model is compatible with the TUTSIM simulation program [11]. Users enter the branch transmittances, the node connections, the initial conditions, and the simulation step size. The small-signal model gives visual graphs and analytical transfer functions. The Switching Flow-Graph technique is used to predict the global and local dynamic behavior of switching converters. Experiments were conducted to verify the large-signal model and the small-signal model. The measured and the predicted dynamic response are very close.

In Chapter 4, the Switching Flow-Graph model is used to develop a physical explanation of right-half-plane (RHP) zero problems. The duty-ratio control reference has imbalanced effects on the output of the switching converters, which causes the RHP zeros. Design criteria are found, for the damping circuit, to eliminate the RHP zeros. The model can analytically predict the conditions under which the RHP zeros will appear and therefore reveals how to eliminate them. Experiments were conducted to generate and remove the RHP zeros. The experimental results verified the theoretical predictions.

The general model for current-mode controlled switching converters is derived, in Chapter 5, using the Switching Flow-Graph technique. The current-mode control-loop does not affect the zeros in the transfer function of the switching converters, while it rearranges the system poles, which is, however, not fully controllable, since the state-feedback coefficients are restricted by the current-mode control function. Current-mode control may convert RHP zeros into RHP poles; therefore, the loop may oscillate. Experiments verified the predictions.

#### Part II. One-Cycle Control Technique

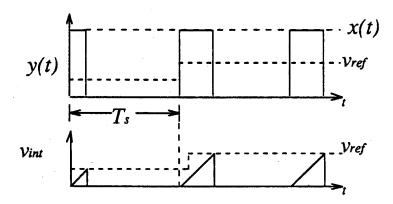

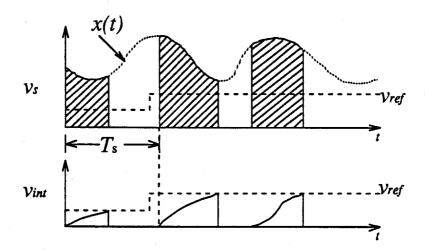

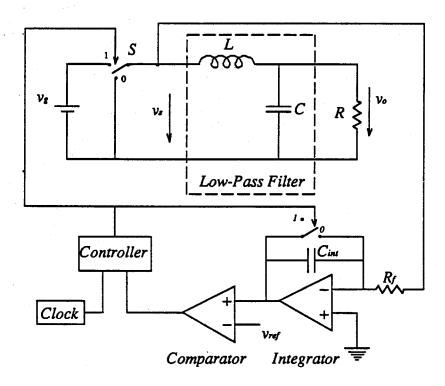

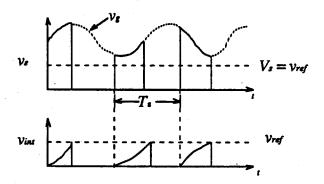

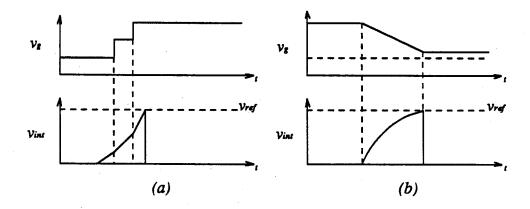

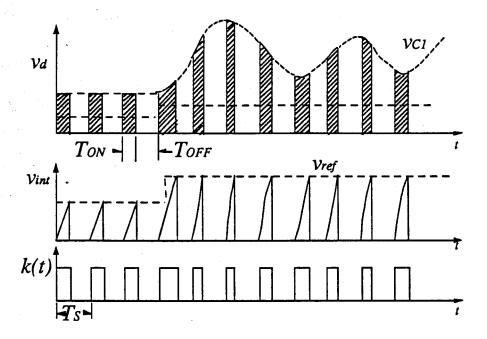

The One-Cycle Control technique is conceived to control the duty-ratio d of the switch in real time such that in each cycle the average of the chopped waveform at the switch output is exactly equal to the control reference. With One-Cycle Control, a switching converter can rejects the effects of the input voltage, and follows the control reference quickly. This technique is suitable for large-signal control of PWM switching converters and quasi-resonant converters.

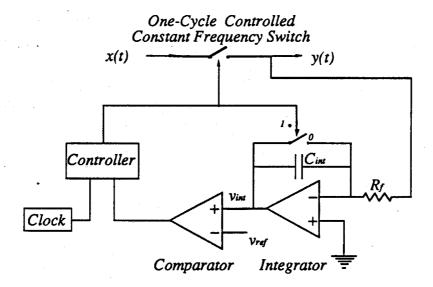

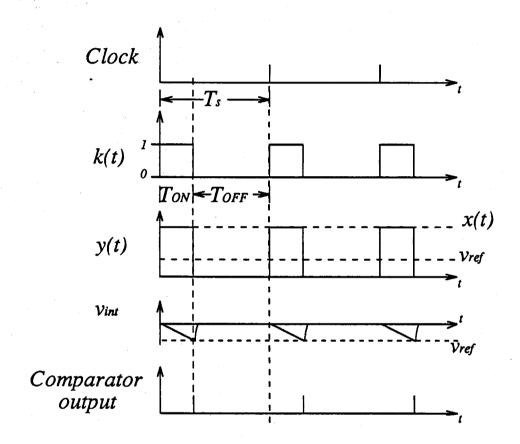

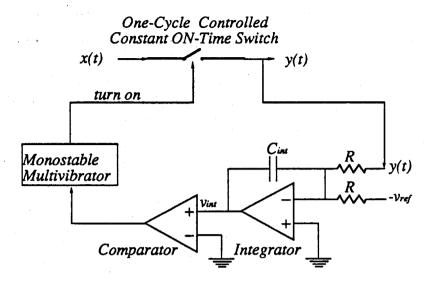

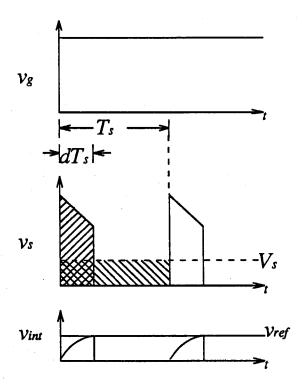

The general concept of One-Cycle Control can be summarized as follows: The effective value of the chopped waveform at the switch output is its average when the signal frequency is lower than half of the switching frequency. A real-time integrator is employed to integrate the chopped waveform. If the integrated value of the chopped waveform in one cycle is exactly equal to the integrated value of the control reference in one cycle, then the average of the chopped waveform is exactly equal to the control reference in one cycle. The implementation circuits are found for any type of switch, constant frequency, constant ON-time, constant OFF-time, and variable. The key component of One-Cycle Control is the real-time integrator. For a constant-frequency switch example, the real-time integrator starts integrating at the instant when the switch is turned on, and when the integrated value reaches the control reference, the controller shuts OFF the switch. Therefore, the output signal of the switch is exactly equal to the control signal. The details of the One-Cycle Control theory and its implementation are

described in Chapter 6.

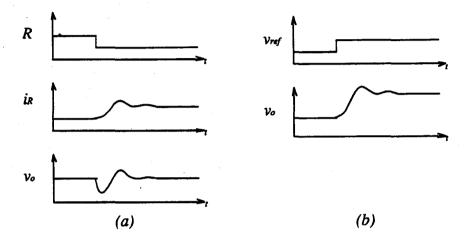

In Chapter 7, the One-Cycle Control technique is used to control the PWM buck converter. The control processes are analyzed to see exactly how the circuit rejects the input voltage and the load current perturbations, and how it follows the control reference. When the converter has an input filter, the dynamics of the input filter do not affect the dynamic response of the output. The One-Cycle Controlled buck converter with input filter behaves like a second-order system. This control scheme is compared with the PWM feedback control technique and the current-mode control technique. Experiments were conducted to verify the theory.

In Chapter 8, the dynamic behavior of the One-Cycle Controlled system is investigated, with the Ćuk converter as an example. The diode voltage of the Ćuk converter is instantaneously controlled by the control reference; therefore, one would assume that the control-loop has infinite loop-gain. The Switching Flow-Graph model is employed to study the large-signal stability and small-signal behavior of the One-Cycle Controlled system. The One-Cycle Controlled Ćuk converter is not globally stable. However, the limitation of the switching duty-ratio may prevent the system from operating in the unstable region. It is also found that the One-Cycle Control loop-gain is below 0db! The system dynamics must obey physical laws; therefore, the transients of the capacitor voltage and the inductor current are not instantaneously controlled. One-Cycle Control takes advantage of the pulsed and nonlinear nature of the system to achieve instantaneous control over the average value of diode voltage.

The physical limitations, the discontinuous current operating condition, and the design of the real-time integrator are discussed in Chapter 9.

The conclusions and some further discussion are given in Chapter 10.

# Part I

Switching Flow-Graph Model

# Chapter 2

# Switching Flow-Graph Modelling Technique

A new modelling tool for switching converters, the Switching Flow-Graph Modelling Technique, is introduced in this chapter. This technique is developed based on experience with the state-space averaging method and the linear circuit flow-graph method. This new technique can be utilized to create the large-signal nonlinear model, the small-signal linear model, and the steady-state model.

A brief background of flow-graph is reviewed in Section 2.1. The Switching Flow-Graph is introduced in Section 2.2. The switching functions, constant frequency, constant ON-time, constant OFF-time, and variable, are discussed for the switching branches in Section 2.3. The large-signal, steady-state, and small-signal representations of the Switching Flow-Graph are obtained in Section 2.4, Section 2.5, and Section 2.6, respectively. The linear circuit extra-element theory is extended to the use in flow-graphs and Switching Flow-Graphs in Section 2.7.

# 2.1 Flow-Graph Background

Flow-graph [18] is a symbolic language for the description of dynamic systems that provides a graphic representation of the signal flow within the system. The flow-graph construction breaks a system into virtually all of its basic components, and thereby clearly illustrates the effects of input and/or parameter changes upon its signals at all points in the system. Flow-graphs may be reduced, using standard procedures, to obtain

transfer characteristics between arbitrary points in the system. Once the basic concepts of this technique are understood, the flow-graph can be easily constructed from the system equations or directly from the electrical circuit.

The signals are represented by nodes, which are schematically represented by small circles in the diagrams. The nodes are connected by branches, line segments with arrows. The signals flow only in the direction of the arrow on each branch. Each branch has a transmittance or gain indicated next to it and the signals passing along that branch are multiplied by the branch transmittance. The signal at a node is the sum of all signals entering the node. Source nodes, nodes with outputs only, represent independent variables. Sink nodes, nodes with inputs only, always represent dependent variables. A mixed node has both inputs and outputs.

The procedure for constructing the flow-graph of a system is straightforward. First each variable of interest is assigned a node on the flow-graph. Next the nodes are interconnected as required by the specific system configuration. Once all of the nodes are properly connected, the flow-graph is complete.

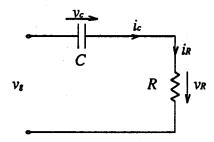

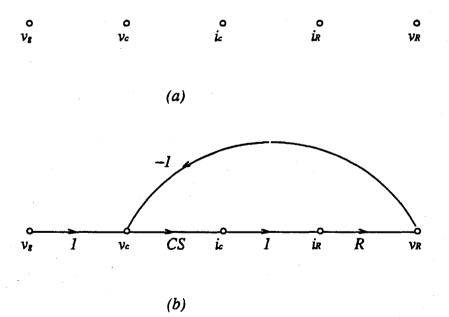

Figure 2.1: The RC Circuit.  $v_g$  is the input voltage,  $v_C$  is the voltage cross the capacitor,  $i_C$  is the capacitor current,  $i_R$  is the resistor current and  $v_R$  is the output voltage.

Consider a simple RC circuit as an example. Fig. 2.1 depicts an RC circuit, where  $v_g$  is the input voltage,  $v_C$  is the voltage across the capacitor,  $i_C$  is the capacitor current,  $i_R$  is the resistor current, and  $v_R$  is the output voltage. To create the flow-graph for this

RC circuit, first assign five nodes from left to right to denote  $v_g$ ,  $v_C$ ,  $i_C$ ,  $i_R$ , and  $v_R$ , respectively, as shown in Fig. 2.2 (a). From Kerchhoff's law, it is found that:

$$v_C = v_q - v_R \tag{2.1}$$

$$i_C = CSv_C \tag{2.2}$$

$$i_R = i_C \tag{2.3}$$

$$v_R = Ri_R \tag{2.4}$$

where C is the capacitance, R is the resistance, and S is the Laplace complex number  $S = \sigma + j\omega$ . These relations are used to connect the nodes in Fig. 2.2 (a), to produce the flow-graph shown in Fig. 2.2 (b). The node that represents the input voltage  $v_g$  is

Figure 2.2: Flow-Graph of the RC Circuit. (a) Five nodes are assigned to the circuit variables:  $v_g$ ,  $v_C$ ,  $i_C$ ,  $i_R$ , and  $v_R$ . (b) The nodes are connected according to the circuit equations (2.1), (2.2), (2.3) and (2.4).

a source node, while the other nodes are mixed nodes. From the flow-graph, it is very

easy to obtain the transfer function for the circuit.

$$v_o = v_R \tag{2.5}$$

$$= \frac{RCS}{1 + RCS} v_g \tag{2.6}$$

#### 2.2 Switching Flow-Graph

Flow-graph is a very useful tool for the design and analysis of linear circuits. This tool is extended to study the dynamic behavior of switching converters.

Switching converters are nonlinear dynamic systems; however, deeper insight reveals that switching converters are systems with variable structure. A switching converter, in continuous mode, contains two linear subcircuits. The subcircuits share common elements, such as inductors, capacitors and resistors, connected in different topologies. The switch of the converter operates at a frequency, either constant or variable, and alters the system between the two linear subcircuits. This conceptual view provoked the motivation to model these two linear subcircuits using flow-graphs, then to relate the flow-graphs to each other using switching branches.

Suppose a switching converter operates at a frequency  $f_s(t) = \frac{1}{T_s(t)}$ . When  $0 < t < T_{ON}$  the switch S is ON, and when  $T_{ON} < t < T_s$ , the switch S is OFF. For the two positions of the switch S, in the switching converter, the two switched subcircuits are obtained. It is clear that a change in the topological structure occurs within each period as the circuit configuration is periodically changed from the ON-circuit to the OFF-circuit. Both switched subcircuits are linear by themselves, while the converter itself is a nonlinear circuit due to the periodic structure change. The fact that both subcircuits are linear enables them to be modelled using the flow-graph technique.

During the time when the switch S is in the ON position,  $0 < t < T_{ON}$ , the converter is switched to the ON-circuit. Nodes are assigned to each variable, according to the

ON-circuit configuration, and are connected to form a flow-graph  $\mathcal{G}_{ON}$ . During the time when the switch S is in the OFF position,  $T_{ON} < t < T_s$ , the converter is switched to the OFF-circuit. The OFF-circuit contains the same circuit elements as those in the ON-circuit; therefore, it preserves the same variables. The same nodes, which were used for the ON-circuit, are used to represent the OFF-circuit variables. However, the nodes are connected according to the OFF-circuit configuration to form a flow-graph  $\mathcal{G}_{OFF}$ .

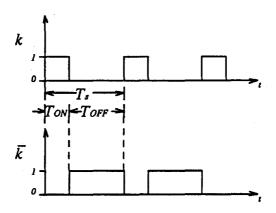

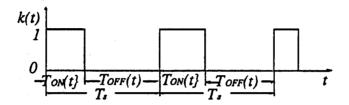

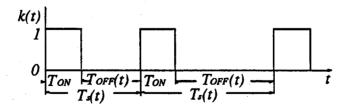

Figure 2.3: Switching Functions. The k function has a value of "1," when  $0 < t < T_{ON}$ , and has a value "0," when  $T_{ON} < t < T_s$ . The  $\overline{k}$  function has a value of 1 - k.

The two flow-graphs,  $\mathcal{G}_{ON}$  and  $\mathcal{G}_{OFF}$ , have exactly the same nodes. However, some connections that exist in  $\mathcal{G}_{ON}$  may not exist in  $\mathcal{G}_{OFF}$ , and some branches that exist in  $\mathcal{G}_{OFF}$  may not exist in  $\mathcal{G}_{ON}$ . Consider the switching functions k and  $\overline{k}$  as shown in Fig. 2.3. The k function has a value "1," when  $0 < t < T_{ON}$ , and has a value zero, when  $T_{ON} < t < T_s$ . The  $\overline{k}$  function has a value of 1 - k. With these two switching functions, the two flow-graphs  $\mathcal{G}_{ON}$  and  $\mathcal{G}_{OFF}$  can be topologically merged by the following equation:

$$\mathcal{G} = k\mathcal{G}_{ON} + \overline{k}\mathcal{G}_{OFF} \tag{2.7}$$

Two switching branches, the k-branch and its complementary  $\overline{k}$ -branch, are thus

Figure 2.4: The Switching Branches: k and  $\overline{k}$ . During the time  $0 < t < T_{ON}$ , the k-branch has a transmittance of "1," and the  $\overline{k}$ -branch has a transmittance of "0." During the time  $T_{ON} < t < T_S$ , the k branch has a transmittance of "0," and the  $\overline{k}$ -branch has a transmittance of "1."

introduced, as shown in Fig. 2.4. The transmittances of the two branches are time dependent. During the time  $0 < t < T_{ON}$ , the k-branch has a transmittance of "1," and the  $\overline{k}$ -branch has a transmittance of "0." During the time  $T_{ON} < t < T_S$ , the k branch has a transmittance of "0," and the  $\overline{k}$ -branch has a transmittance of "1." These switching branches physically unite the two flow-graphs,  $\mathcal{G}_{ON}$  and  $\mathcal{G}_{OFF}$ , into one flow-graph  $\mathcal{G}$ .  $\mathcal{G}$  is the graphical representation of the switching converter. The flow-graph  $\mathcal{G}$  contains switching branches, the k-branch and the  $\overline{k}$ -branch, therefore, it is defined as a Switching Flow-Graph. The switching control signals are injected into the converter through these switching branches.

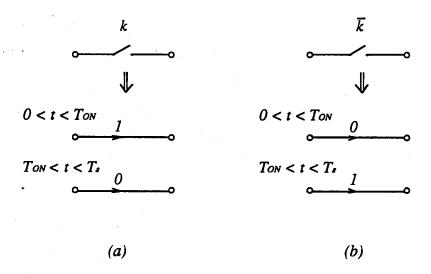

Consider the buckboost converter, shown in Fig. 2.5 (a), as an example, where  $v_g$  is the input voltage, L is the inductor, C is the capacitor, R is the load,  $R_L$  is the parasitic resistance of the inductor, and S is the switch. Define  $v_L$ ,  $v_{R_L}$ , and  $v_o$  as the inductor voltage, the parasitic-resistor voltage, and the output voltage respectively.

Figure 2.5: The Buckboost Converter and its Subcircuits. (a) The buckboost converter.

(b) The two subcircuits: ON-circuit and OFF-circuit.

Define  $i_g$ ,  $i_L$ , and  $i_o$  as the input current, the inductor current, and the output current flowing in the same direction as  $v_g$ ,  $v_L$ , and  $v_o$  respectively. The quantity  $i_o$  is the sum of the load current and the capacitor current  $i_C$ . The two subcircuits, the ON-circuit and the OFF-circuit, are shown in Fig. 2.5 (b). When the switch is ON, the buckboost converter is equivalent to its ON-circuit, and when the switch is OFF, it is equivalent to its OFF-circuit.

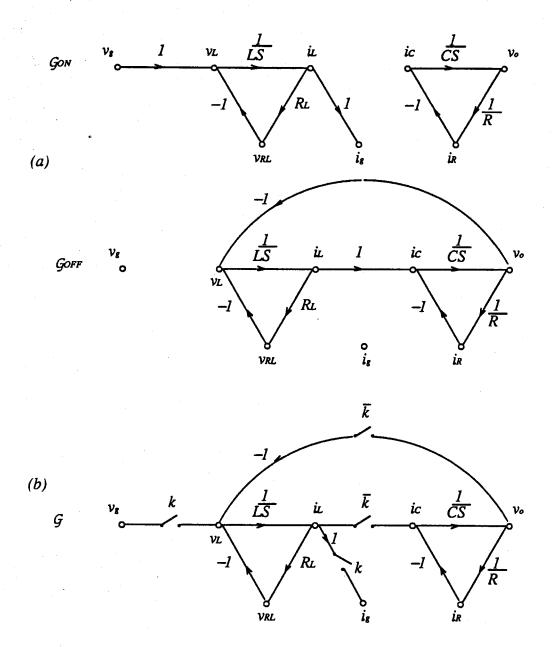

The two subcircuits can be described by their flow-graphs,  $\mathcal{G}_{ON}$  and  $\mathcal{G}_{OFF}$ , shown in Fig. 2.6 (a). These two flow-graphs share the same nodes and share some of the same branches. By overlapping  $\mathcal{G}_{ON}$  and  $\mathcal{G}_{OFF}$ , it is easily seen that some branches exist in both  $\mathcal{G}_{ON}$  and  $\mathcal{G}_{OFF}$ , while other branches exist only in one of them. The branches that exist in  $\mathcal{G}_{ON}$  but not in  $\mathcal{G}_{OFF}$  are replaced by k-branches, and the branches that

Figure 2.6: The Switching Flow-Graph of the Buckboost Converter. (a) The flow-graph  $\mathcal{G}_{ON}$  for the buckboost ON-circuit and the flow-graph  $\mathcal{G}_{OFF}$  for the buckboost converter OFF-circuit. (b) The Switching Flow-Graph  $\mathcal{G}$  for the buckboost converter.

Figure 2.7: The Simplified Switching Flow-Graph of the Buckboost Converter.

exist in  $\mathcal{G}_{OFF}$  but not in  $\mathcal{G}_{ON}$  are replaced by  $\overline{k}$ -branches. Therefore,  $\mathcal{G}_{ON}$  and  $\mathcal{G}_{OFF}$  are combined to form one Switching Flow-Graph  $\mathcal{G}$ , shown in Fig. 2.6 (b). In addition, the Switching Flow-Graph  $\mathcal{G}$  of the buckboost converter can be simplified, as shown in Fig. 2.7, using the algebraic rules in Appendix A.

#### 2.3 Switches

The Switching Flow-Graph  $\mathcal{G}$  is linear except for the switching branches. The switching branches are the signal-flow representations of the real switches. The real switches in the switching converter have very different behavior depending on their voltage, current, and load conditions. Therefore, it is very difficult to make a general model for the real switches. However, when switching converters are transferred into Switching Flow-Graphs, the switches are transferred into generalized switching branches: k-branches and  $\overline{k}$ -branches. The k-branches represent the active switches, whereas the  $\overline{k}$ -branches represent the passive switches. The active switching branch and the passive switching branch are complementary.

Switches are classified, according to their operating function, as constant frequency switches, constant ON-time switches, constant OFF-time switches, and variable switches.

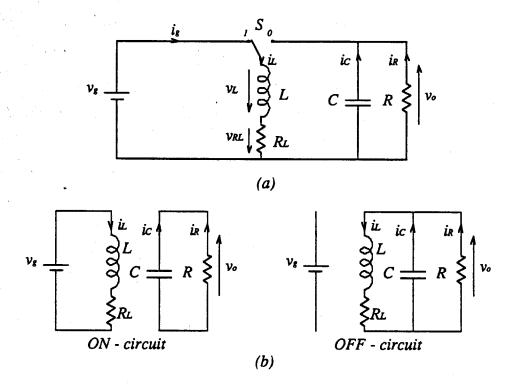

The constant frequency switch operates at a switching frequency  $f_s = \frac{1}{T_s}$ . The switch remains in the ON state for a variable time duration  $T_{ON}(t)$  and remains in the OFF state for a variable time duration  $T_{OFF}(t)$ , where  $T_{ON}(t) + T_{OFF}(t) = T_s$ , as shown in Fig. 2.8.

Figure 2.8: The Constant Frequency Switch. The constant frequency switch operates at a switching frequency  $f_s = \frac{1}{T_s}$ .

The constant ON-time switch operates at a variable switching frequency  $f_s(t) = \frac{1}{T_s(t)}$ . The switch remains in the ON state for a constant period  $T_{ON}$  and remains in the OFF state for a variable time duration  $T_{OFF}(t)$ , where  $T_{ON} + T_{OFF}(t) = T_s(t)$ , as shown in Fig. 2.9.

Figure 2.9: The Constant ON-Time Switch. The constant ON-time switch operates at a variable switching frequency  $f_s(t) = \frac{1}{T_s(t)}$ . The switch remains in the ON state for a constant duration  $T_{ON}$  and remains in the OFF state for a variable time duration  $T_{OFF}(t)$ .

The constant OFF-time switch operates at a variable switching frequency  $f_s(t)$  =

$\frac{1}{T_{\bullet}(t)}$ . The switch remains in the ON state for a variable time duration  $T_{ON}(t)$  and remains in the OFF state for a constant time duration  $T_{OFF}$  as shown in Fig. 2.10.

Figure 2.10: The Constant OFF-Time Switch. The constant OFF-time switch operates at a variable switching frequency  $f_s(t) = \frac{1}{T_s(t)}$ . The switch remains in the ON state for a variable time duration  $T_{ON}(t)$  and remains in the OFF state for a constant time duration  $T_{OFF}$ .

The variable switch operates at a variable switching frequency  $f_s(t) = \frac{1}{T_s(t)}$ . The switch remains in the ON state for a variable time duration  $T_{ON}(t)$  and remains in the OFF state for a variable time duration  $T_{OFF}(t)$  as shown in Fig. 2.11.

Figure 2.11: The Variable Switch. The variable switch operates at a variable switching frequency  $f_s(t) = \frac{1}{T_s(t)}$ . The switch remains in the ON state for a variable time duration  $T_{OFF}(t)$  and remains in the OFF state for a variable time duration  $T_{OFF}(t)$ .

# 2.4 Large-Signal Model of Switching Converters

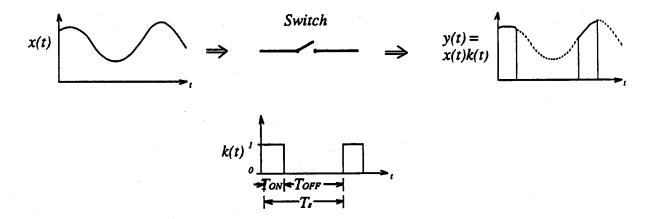

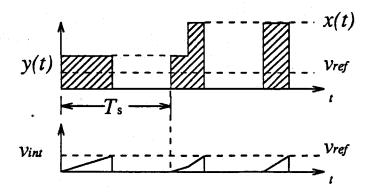

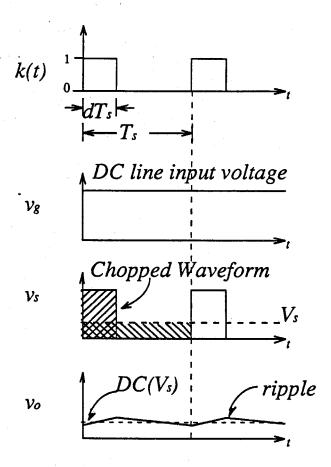

Suppose that the signal entering the k-branch is x(t), and that the the output signal of the switching branch is y(t). The input signal x(t) is chopped by the switch function, as shown in Fig. 2.12. The output signal y(t) of the switching branch is a chopped waveform with an envelope equal to the input signal x(t), a pulse frequency equal to the switch frequency  $f_s$ , and a pulse width equal to  $T_{ON}$ .

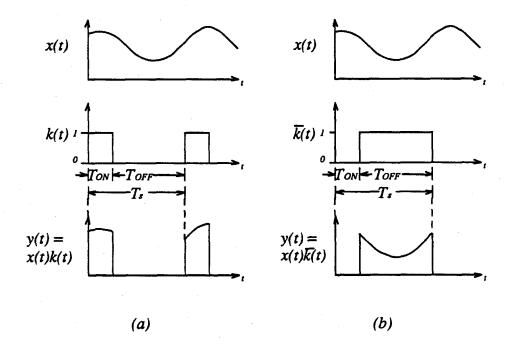

Figure 2.12: The Signal Flow of the Switching Branches. The input signal x(t) is chopped by the switch function k(t) and  $\overline{k}(t)$ . The effective signal carried in the output signal is y(t). (a) The signal flow of the k-branch. (b) The signal flow of the  $\overline{k}$ -branch.

Assume that the small ripple condition is satisfied; therefore, the switch frequency is attenuated in the circuit. Also, assume that the signal frequency is much lower than the switch frequency. The effective signal carried at the k-branch output is equal to its

average value over a switch cycle:

$$y(t) = \frac{1}{T_s(t)} \int_0^{T_{ON}(t)} x(t) dt \qquad (2.8)$$

$$\approx x(t) \frac{1}{T_s(t)} \int_0^{T_{ON}(t)} dt \tag{2.9}$$

$$= x(t) \frac{T_{ON}(t)}{T_s(t)} \tag{2.10}$$

$$= x(t)d(t) (2.11)$$

Similarly for the  $\overline{k}$ -branch, the input signal x(t), and output signal y(t) have the relation:

$$y(t) = \frac{1}{T_s(t)} \int_{T_{ON}(t)}^{T_S(t)} x(t) dt$$

(2.12)

$$\approx x(t) \frac{1}{T_s(t)} \int_{T_{ON}(t)}^{T_s(t)} dt \qquad (2.13)$$

$$= x(t) \frac{T_{OFF}(t)}{T_s(t)} \tag{2.14}$$

$$= x(t)d'(t) (2.15)$$

where d(t) and d'(t) are the averages of the switch functions k(t) and  $\overline{k}(t)$  respectively, and they represent the duty-ratio of the switch.

$$d(t) = \frac{T_{ON}(t)}{T_s(t)} \tag{2.16}$$

$$d'(t) = \frac{T_{OFF}(t)}{T_s(t)} \tag{2.17}$$

$$d'(t) = 1 - d(t) (2.18)$$

Switches are controlled by their duty-ratio function d(t). The duty-ratio functions are found for the constant frequency switches, the constant ON-time switches, the constant OFF-time switches, and the variable switches:

$$d(t) = T_{ON}(t)f_s$$

for the constant frequency switches (2.19)

$$d(t) = T_{ON} f_s(t)$$

for the constant ON-time switches (2.20)

$$d(t) = 1 - T_{OFF} f_s(t)$$

for the constant OFF-time switches (2.21)

$$d(t) = T_{ON}(t)f_s(t)$$

for the variable switches (2.22)

Figure 2.13: The large-signal Models of the Switching Branches. (a) The Large-signal model of the k-branch. (b) The Large-signal model of the  $\overline{k}$ -branch.

Equations (2.11) and (2.15) indicate that the output signal y(t) from the switching branches is the product of the input signal x(t) and the duty-ratio control signal d(t) or d'(t), thus it is directly affected by the input signal x(t) and controlled by the duty-ratio d(t) or d'(t). Therefore, the large-signal models of the switching branches are represented by a single multiplier, as shown in Fig. 2.13. The large-signal model of a switching converter is obtained by replacing the switching branches with the large-signal models of the switching branches in the Switching Flow-Graph  $\mathcal{G}$ .

Large-signal models are necessary for studying the global dynamic behavior of the switching converter systems. Global knowledge makes it possible to design a switching converter system that operates in the desirable converging region of state space. Inside this desired converging region, the small-signal model can be employed to investigate the

Figure 2.14: The Large-Signal Model of the Buckboost Converter. The large-signal model of the buckboost converter is obtained by replacing the switching branches with the large-signal models of the switching branches in the Switching Flow-Graph  $\mathcal{G}$ .

local frequency response for small-signals.

The large-signal model is shown in Fig. 2.14 for the same buckboost converter discussed in the previous section. The input to output large-signal response can be obtained by injecting a signal into node  $v_g$ , and observing the output at the node  $v_o$ . In addition, the input impedance can be determined by detecting the signal at node  $i_g$ . Injecting a signal into node d(t) and detecting the output at node  $v_o$  generates the control to output large-signal-response. Injecting a signal into the node  $v_o$ , one can detect the signal at node  $i_o$  to get the output impedance.

It is very easy to obtain the global view of the dynamic behavior of the system by entering the model into a computer simulation program. From the study of the large-signal dynamic behavior, a desired stable operating region is found. Inside this region, the system can be linearized in the neighborhood of the operating point to obtain the small-signal frequency response.

### 2.5 Steady-State Model

The large-signal models of the k-branch and the  $\overline{k}$ -branch, derived in the previous section, can be modified to generate a steady-state model of the switching branches. Assume that the input signals and the duty-ratio control signals, x(t), d(t), and d'(t), entering the switching branches are constant. That is:

$$x(t) = X (2.23)$$

$$d(t) = D (2.24)$$

$$d'(t) = D' (2.25)$$

Then the output signal y(t) of the switch is also constant:

$$y(t) = Y \tag{2.26}$$

Therefore, the switching branches degenerate to standard branches, as shown in Fig. 2.15. In the steady-state, the k-branch has only one input signal, X; the transmittance of the branch is D and the output signal is Y. Similarly, for the  $\overline{k}$ -branch, the input signal is X, the transmittance of the branch is D' and the output signal is Y.

Substitution of these steady-state models into the Switching Flow-Graph  $\mathcal{G}$  of the switching converter for the switching branches and assuming  $S \to 0$ , immediately yields the steady-state model of the switching converter. The steady-state model of the buckboost converter is shown in Fig. 2.16.

Relations between state variables, such as the input-to-output gain, the DC relations between the state variables, and the efficiency, etc., can be read directly off the steady-state flow-graph model.

$$\frac{V_o}{V_g} = \frac{D/D'}{1 + \frac{R_L}{RD'^2}} \tag{2.27}$$

Figure 2.15: The Steady-State Models of the Switching Branches. (a) The steady-state model of the k-branch. (b) The steady-state model of the  $\overline{k}$ -branch.

Figure 2.16: The Steady-State Model of the Buckboost Converter. Substitution of the steady-state models into the Switching Flow-Graph  $\mathcal G$  of the buckboost converter for the switching branches and assuming  $S \to 0$ , immediately yields the steady-state model of the buckboost converter.

$$\frac{I_L}{V_g} = \frac{D}{R_L + D^{\prime 2}R} \tag{2.28}$$

$$\frac{I_C}{V_a} = \frac{DD'}{R_L + D'^2 R} \tag{2.29}$$

$$\eta = \frac{1}{1 + \frac{R_L}{D^{2}R}} \tag{2.30}$$

### 2.6 Small-Signal Model

For the k-branch and the  $\overline{k}$ -branch, in the large-signal environment, the input and output signals have the relationships:

$$y(t) = x(t)d(t)$$

for the k-branch (2.31)

$$y(t) = x(t)d'(t)$$

for the  $\overline{k}$ -branch (2.32)

Define the operating point by X, D and Y, and the associated small-signal perturbations by  $\hat{x}(t)$ ,  $\hat{d}(t)$ , and  $\hat{y}(t)$ , where:

$$d(t) = D + \hat{d}(t) \tag{2.33}$$

$$d'(t) = D' - \hat{d}(t) \tag{2.34}$$

$$1 = D + D' (2.35)$$

$$x(t) = X + \hat{x}(t) \tag{2.36}$$

$$y(t) = Y + \hat{y}(t) \tag{2.37}$$

Inserting Equations (2.33), (2.34), (2.36) and (2.37) into the large-signal switching branch relations (2.31) and (2.32), yields the equations for the small-signal perturbations.

$$Y + \hat{y}(t) = (X + \hat{x}(t))(D + \hat{d}(t))$$

$$= XD + D\hat{x}(t) + X\hat{d}(t) + \hat{x}(t)\hat{d}(t)$$

(2.38)

for the k-branch and

$$Y + \hat{y}(t) = (X + \hat{x}(t))(D' - \hat{d}(t))$$

$$= XD' + D'\hat{x}(t) - X\hat{d}(t) - \hat{x}(t)\hat{d}(t)$$

(2.39)

for the  $\overline{k}$ -branch.

At the operating point, the k-branch and the  $\overline{k}$ -branch satisfy:

$$Y = XD$$

for the k-branch (2.40)

$$Y = XD'$$

for the  $\overline{k}$ -branch (2.41)

Neglecting the second-order perturbations, yields the small-signal switching branch equations:

$$\hat{y}(t) = D\hat{x}(t) + X\hat{d}(t)$$

for the k-branch (2.42)

$$\hat{y}(t) = D'\hat{x}(t) - X\hat{d}(t)$$

for the  $\overline{k}$ -branch (2.43)

The small-signal models of the switching branches are shown in Fig. 2.17. Substitution

Figure 2.17: The Small-Signal Models of the Switching Branches. (a) The small-signal model of the k-branch. (b) The small-signal model of the  $\overline{k}$ -branch.

of the small-signal models for the switching branches in the Switching Flow-Graph immediately generates the small-signal model.

The small-signal dynamic model is shown in Fig. 2.18 for the same buckboost converter discussed in the last section. The small-signal model of the buckboost converter,

Figure 2.18: The Small-Signal Model of the Buckboost Converter. Substitution of the small-signal models for the switching branches in the Switching Flow-Graph of the buckboost converter, immediately generates the small-signal model.

shown in Fig. 2.18, can be further simplified to Fig. 2.19 using the flow-graph algebraic rules in Appendix A. The analytic forms of the transfer functions for the buckboost converter are easily obtained from Fig. 2.19.

Figure 2.19: The Simplified Small-Signal Model of the Buckboost Converter. The small-signal model of the buckboost converter can be simplified using the flow-graph algebraic rules in Appendix A.

$$\frac{\hat{v}_o}{\hat{d}} = \frac{V_g + V_o - \frac{LS + R_L}{D'} I_L}{D'((1 + \frac{R_L/R}{D'^2}) + \frac{R_LC + L/R}{D'^2} S + \frac{LC}{D'^2} S^2)}$$

(2.44)

$$\frac{\hat{v}_o}{\hat{v}_g} = \frac{\frac{D}{D'}}{(1 + \frac{R_L/R}{D'^2}) + \frac{R_LC + L/R}{D'^2}S + \frac{LC}{D'^2}S^2}$$

(2.45)

The transfer function, shown in Equation (2.44), which represents the relationship between the small-signal control  $\hat{d}(t)$  and the output  $\hat{v}_o$ , can be simplified using the steady-state relations of Equation (2.27) and (2.28).

$$\frac{\hat{v}_o}{\hat{d}} = \frac{V_g \left(1 + \frac{D(RD' - R_L/D')}{R_L + RD'^2} - \frac{LD/D'}{R_L + RD'^2}S\right)}{D' \left(\left(1 + \frac{R_L/R}{D'^2}\right) + \frac{R_LC + L/R}{D'^2}S + \frac{LC}{D'^2}S^2\right)}$$

(2.46)

The small-signal transfer functions, obtained using the Switching Flow-Graph technique, are the same as those obtained using the state-space averaging technique; however, the Switching Flow-Graph technique provides a more visible and faster way to obtain the small-signal models for switching converters. The Switching Flow-Graph models generate a more physical understanding of the signal processing in switching converters. For example, it is evident from Fig. 2.7 that a right-half-plane (RHP) zero exists in the control-to-output frequency response. The physical insight necessary to make this observation of the RHP zero is further discussed in Chapter. 4.

In addition, the Switching Flow-Graph facilitates the determination of the input and output impedances:

$$\hat{z}_{in} = \frac{\hat{v}_g}{\hat{i}_g}

= \frac{R \frac{D'^2}{D^2} ((1 + \frac{R_L/R}{D'^2}) + \frac{R_LC + L/R}{D'^2} S + \frac{LC}{D'^2} S^2)}{1 + RCS}

\hat{z}_{out} = \frac{\hat{v}_o}{\hat{i}_R|_{v_g=0}}

= \frac{R_L (1 + \frac{L}{R_L} S)}{D'^2 ((1 + \frac{R_L/R}{D'^2}) + \frac{R_LC + L/R}{D'^2} S + \frac{LC}{D'^2} S^2)}$$

(2.47)

### 2.7 Extra-Element Theory of the Flow-Graph

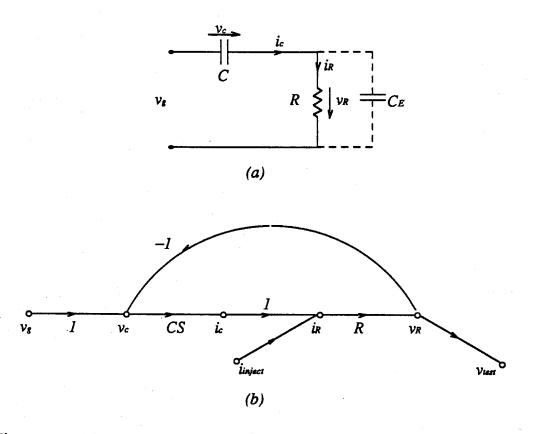

The extra-element theory [12] can be applied to the flow-graph and the Switching Flow-Graph. Suppose  $\mathcal{B}_i$  is *i*-th branch of the Switching Flow-Graph  $\mathcal{G}$ . The branch  $\mathcal{B}_i$  represents an electrical element  $Z_i$  of the original circuit. If an extra-element  $Z_E$  is to be inserted into the original circuit in parallel with the element  $Z_B$ , as shown in Fig. 2.20, then the extra-element  $Z_E = 1/C_E S$  shares the current with the original element  $Z_B$ . Therefore,  $Z_d$  and  $Z_n$  can be determined by injecting a current signal into the current node of branch  $\mathcal{B}_i$  and detecting the voltage at the voltage node of branch  $\mathcal{B}_i$ , as shown in Fig. 2.20. Let  $v_g = 0$ ,  $v_o = v_R$ ,

Figure 2.20: The Parallel Extra-Element.  $Z_d$  and  $Z_n$  can be determined by injecting a current signal into the current node of branch  $\mathcal{B}_i$  and detecting the voltage at the voltage node of branch  $\mathcal{B}_i$ .

$$Z_d = \frac{v_{test}}{i_{inject}} |_{v_g = 0} \tag{2.49}$$

$$= \frac{R}{1 + RCS}. (2.50)$$

Adjust  $i_{inject}$  such that  $v_o = 0$ ,

$$Z_n = \frac{v_{test}}{i_{inject}}|_{v_0=0} \tag{2.51}$$

$$= 0. (2.52)$$

The gain  $\frac{v_o}{v_g}$  with the extra-element  $Z_E$  is:

$$\frac{v_o}{v_g}|_{Z_E} = \frac{v_o}{v_g}|_{Z_E = \infty} \frac{1 + \frac{Z_n}{Z_E}}{1 + \frac{Z_d}{Z_E}}$$

(2.53)

$$= \frac{RCS}{1 + R(C + C_E)S}. (2.54)$$

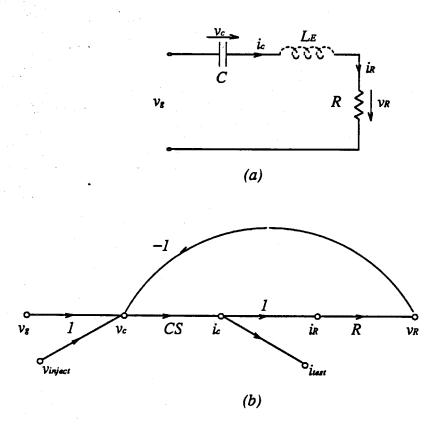

If an extra-element  $Z_E$  is inserted into the circuit in series with the element  $Z_B$ , as shown in Fig. 2.21, then the extra element  $Z_E = L_E S$  shares the voltage with the original element  $Z_B$ . Therefore,  $Z_d$  and  $Z_n$  can be determined by injecting a voltage signal in to the current node of branch  $\mathcal{B}_i$ , and detecting the current at the current node of branch  $\mathcal{B}_i$ , as shown in Fig. 2.21. Let  $v_g = 0$  and  $v_o = v_R$ ,

$$Z_d = \frac{v_{inject}}{i_{test}} \Big|_{v_g=0}$$

(2.55)

$$= \frac{1 + RCS}{CS}. \tag{2.56}$$

Adjust  $i_{inject}$  such that  $v_o = 0$ ,

$$Z_n = \frac{v_{inject}}{i_{test}} |_{v_0=0}$$

(2.57)

$$= \infty. \tag{2.58}$$

The gain  $\frac{v_o}{v_g}$  with the extra-element  $Z_E$  is:

$$\frac{v_o}{v_g} |_{Z_E} = \frac{v_o}{v_g} |_{Z_E=0} \frac{1 + \frac{Z_E}{Z_n}}{1 + \frac{Z_E}{Z_d}}$$

(2.59)

$$= \frac{RCS}{1 + RCS + L_E CS^2}. (2.60)$$

Figure 2.21: The Series Extra-Element.  $Z_d$  and  $Z_n$  can be determined by injecting a voltage signal into the voltage node of branch  $\mathcal{B}_i$ , and detecting the current at the current node of branch  $\mathcal{B}_i$ .

For simple circuits such as those shown in Fig. 2.20 and Fig. 2.21, there is not much advantage in using the extra-element theory. However, the extra-element theory is of tremendous help when the circuit is very complicated.

# 2.8 Summary

The Switching Flow-Graph technique is an easily implemented graphic modelling tool for switching converter design and analysis. This technique provides a large-signal model, a small-signal model, and a steady-state model. The large-signal model gives a global view of the switching converter, thus it can be used to find the convergent operating

region and to design a converter that operates in a desired region. The steady-state model yields the steady-state relations, which are useful in determining the efficiency and other steady-state properties of switching converters. The small-signal model gives the transfer functions from one arbitrary state variable to another arbitrary state variable, such as the input-to-output gain, the control-to-output gain, the input and output impedances, etc. The Switching Flow-Graph is a graphic realization of the circuit that contains all the information about the circuit, provides physical insight into the operation of the circuit and is very easy to obtain.

# Chapter 3

# Modelling Pulse-Width-Modulated Switching

## Converters

The Switching Flow-Graph technique is applied to model the most commonly used pulsed-width-modulated (PWM) converters in the second-order family in Section 3.1 and the fourth-order family in Section 3.2. The algebraic rules, outlined in Appendix A, are employed to simplify the small-signal Switching Flow-Graphs in Section 3.3. Experiments, described in Section 3.4, were conducted to verify both the large-signal and the small-signal models.

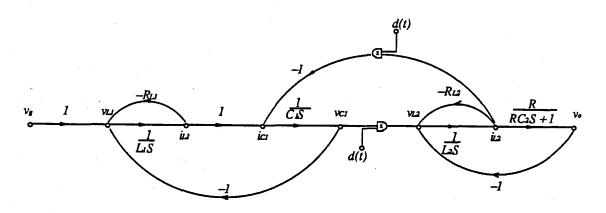

# 3.1 Modelling Second-Order PWM Switching Converters

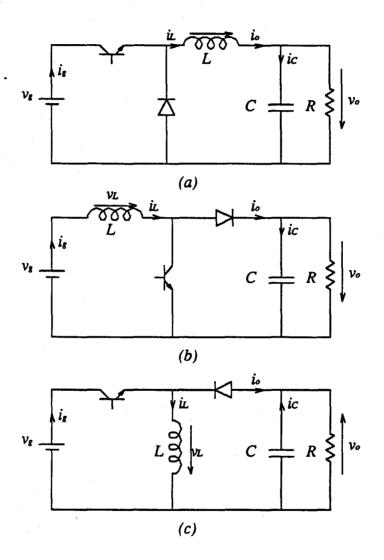

The Switching Flow-Graph technique is used to study the dynamic behavior of standard second-order PWM converters, such as the buck converter, the boost converter, and the buckboost converter, shown in Fig. 3.1. L is the inductor, C is the capacitor, and R is the load resistor. A transistor and a diode are employed to implement the switch S. When the transistor is ON the diode is OFF and when the transistor is OFF the diode is ON. Define  $v_g$ ,  $v_L$ ,  $v_o$  as the input voltage, the inductor voltage, and the output voltage, respectively. Assume that the input current  $i_g$ , the inductor current  $i_L$ , and the output current  $i_O = i_C + i_R$  are in the same direction as  $v_g$ ,  $v_L$ , and  $v_o$ .

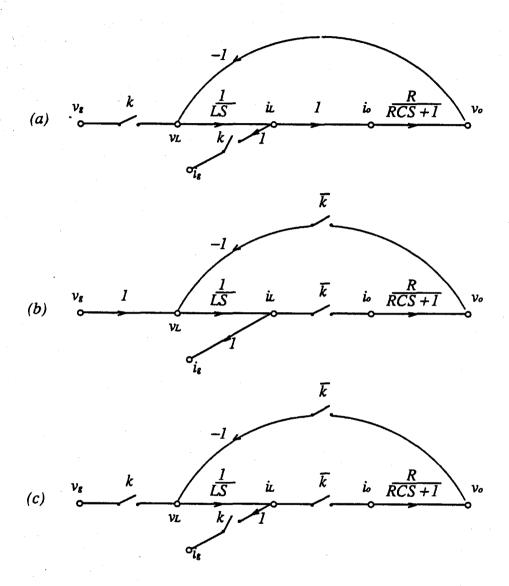

The Switching Flow-Graphs, shown in Fig. 3.2, for the buck converter, the boost

Figure 3.1: The Basic Second-Order PWM Converter. (a) The buck converter. (b)

The boost converter. (c) The buckboost converter.

Figure 3.2: The Switching Flow-Graphs of the Second-Order PWM Converters.

The Switching Flow-Graph for the buck converter (a), the boost converter (b), and the buckboost converter (c).

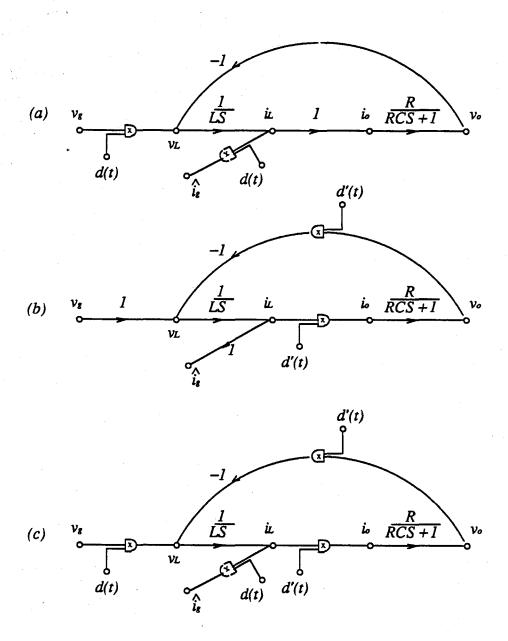

Figure 3.3: The Large-Signal Models of the Second-Order PWM Converters. The large-signal model for the buck converter (a), the boost converter (b), and the buckboost converter (c).

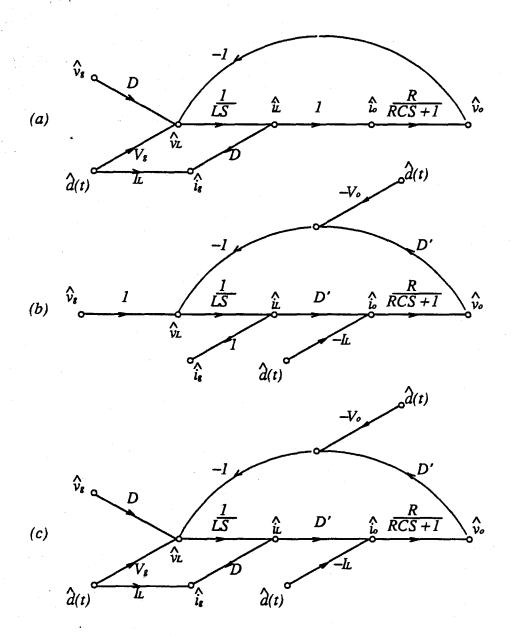

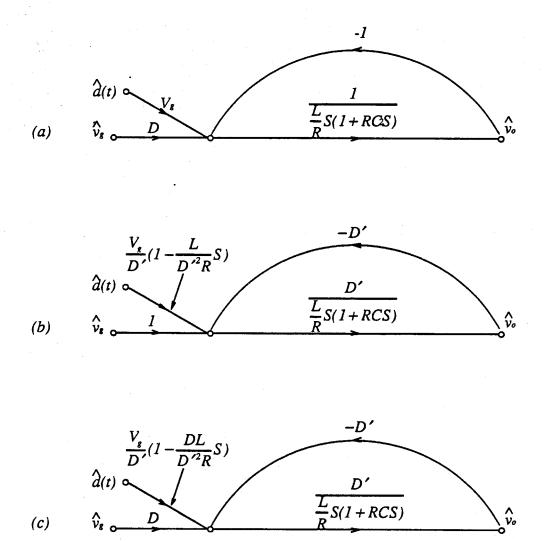

Figure 3.4: The Small-Signal Models of the Second-Order PWM Converters. The small-signal model for the buck converter (a), the boost converter (b), and the buckboost converter (c).

converter, and the buckboost converter are very similar. The Switching Flow-Graphs exhibit an interesting regularity. The k-branches appear in pairs and the  $\overline{k}$ -branches appear in pairs. In all cases, one switching branch of a given pair is in the voltage path, while the other is in the current path. The buck converter has only one pair of k-branches, the boost converter has only one pair of  $\overline{k}$ -branches, and the buckboost converter has both a k-branch pair and a  $\overline{k}$ -branch pair.

The large-signal models are shown in Fig. 3.3. Relations between the various state variables are obtained by simulation. The small-signal models are shown in Fig. 3.4. Small-signal transfer functions between state variables are read directly from the small-signal Switching Flow-Graph. Fig. 3.4 also indicates that the duty-ratio signal  $\hat{d}$  injected into the current path has a negative effect on the output voltage  $\hat{v}_o$ . This negative effect raises the problem of right-half-plane (RHP) zeros that is discussed in Chapter 4.

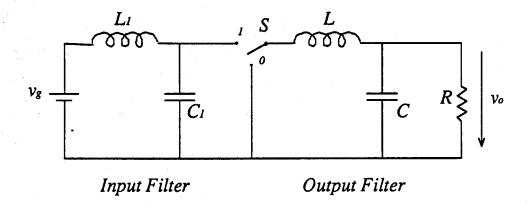

### 3.2 Modelling Fourth-Order PWM Converters

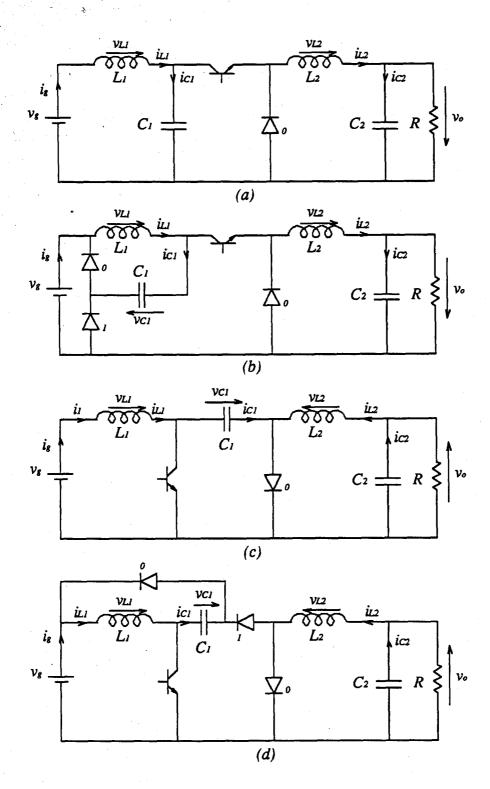

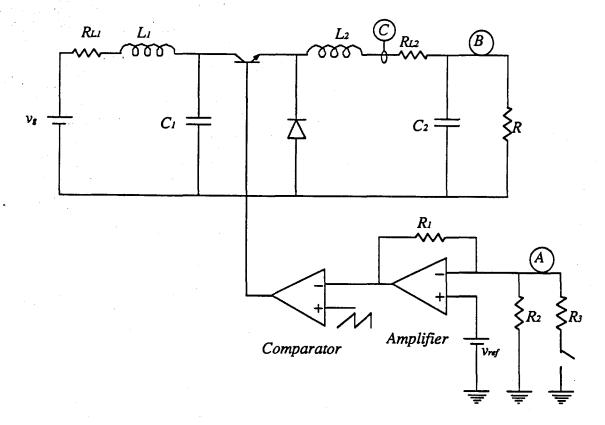

The Switching Flow-Graph technique is also well suited for the study of the dynamic behavior of fourth-order systems, such as the buck converter with input filter, the  $d^2$  converter, the Ćuk converter, and the Lambda converter, as shown in Fig. 3.5.  $L_1$  and  $L_2$  are the input and output inductors,  $C_1$  and  $C_2$  are the input and output capacitors, and R is the load resistor. In each circuit, a transistor and one or more diode(s) are used to implement the switch S. When the transistor is ON, diode "1"s are ON and diode "0"s are OFF. When the transistor is OFF, diode "1"s are OFF and diode "0"s are ON. Define  $v_g$  as the input voltage,  $v_{L1}$  and  $v_{L2}$  as the voltages across  $L_1$  and  $L_2$ ,  $v_{C1}$  as the voltage across  $C_1$ , and  $v_o$  as the output voltage. Define  $i_g$  as the input current,  $i_{L1}$  and  $i_{L2}$  as the currents through  $L_1$  and  $L_2$ ,  $i_{C1}$  as the current through  $C_1$ , and  $i_o = i_{L2} = i_R + i_{C2}$  as the output current. All currents flow in the same direction as

Figure 3.5: The Fourth-Order PWM Converters. (a) The buck converter with input filter. (b) The  $d^2$  converter. (c) The Cuk converter. (d) The Lambda converter.

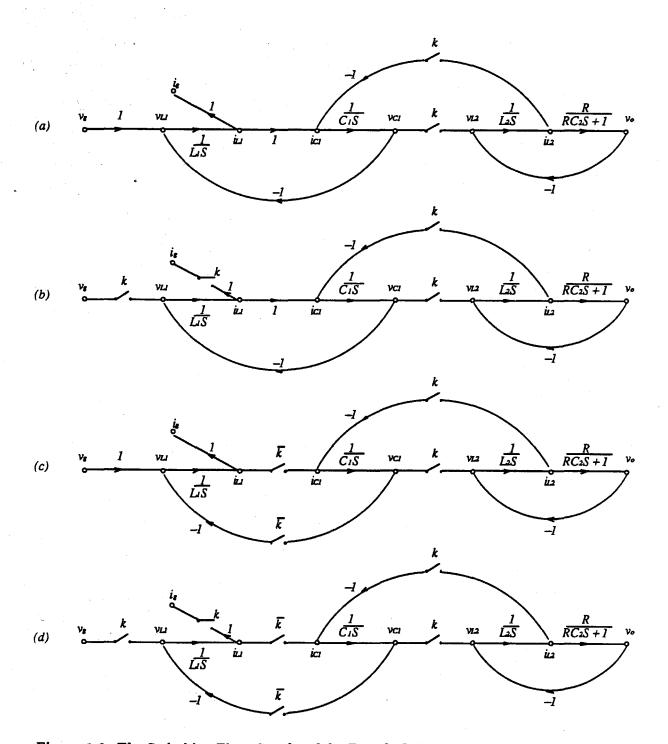

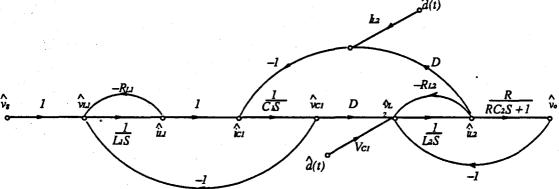

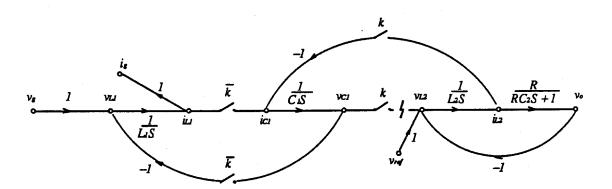

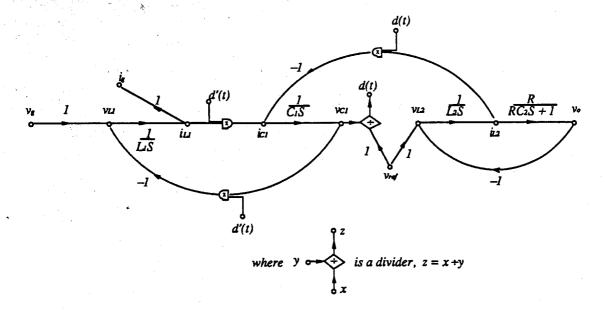

Figure 3.6: The Switching Flow-Graphs of the Fourth-Order PWM Converters. The Switching Flow-Graph for the buck converter with input filter (a), the  $d^2$  converter (b), the Ćuk converter (c), and the Lambda converter (d).

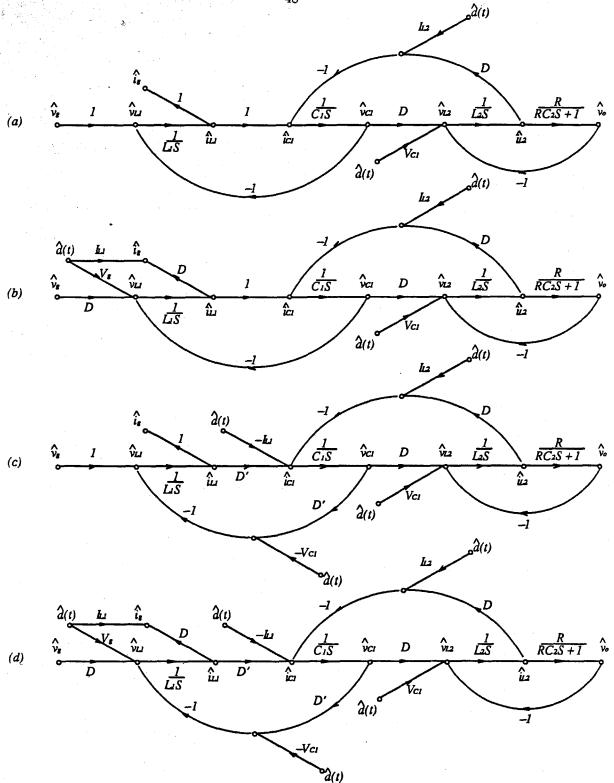

Figure 3.7: The Large-Signal Models of the Fourth-Order PWM Converters. The large-signal model for the buck converter with input filter (a), the  $d^2$  converter (b), the Ćuk converter (c), and the Lambda converter (d).

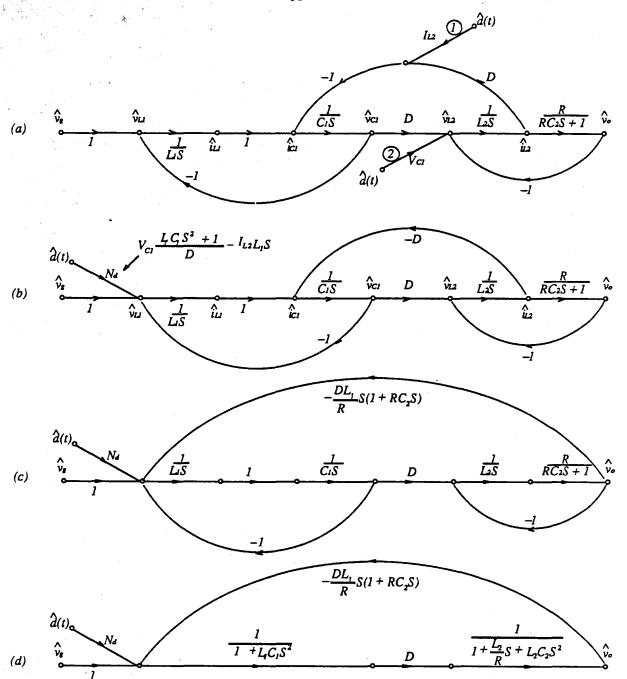

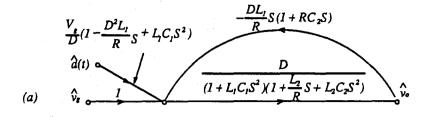

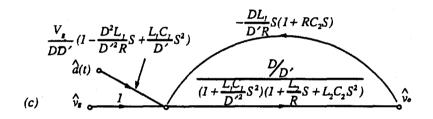

Figure 3.8: The Small-Signal Models of the Fourth-Order PWM Converters. The small-signal model for the buck converter with input filter (a), the  $d^2$  converter (b), the Cuk converter (c), and the Lambda converter (d).

their associated voltages.

The Switching Flow-Graphs obtained for the fourth-order converters are shown in Fig. 3.6. The Switching Flow-Graphs illustrate the same regular pattern as seen in the second-order converters. The k-branches appear in pairs, and the  $\overline{k}$ -branches appear in pairs. In all cases, one switching branch of a given pair is in the voltage path and the other is in the current path. A loop contains at most one type of switching branch. If a loop has switching branches, it always has two, one in the forward path and the other in the feedback path. If two adjacent loops both have switching branches, they have different types. Converters with DC gain  $\frac{D^m}{D^m}$  have m pairs of k-branches and n pairs of  $\overline{k}$ -branches in their Switching Flow-Graphs.

The large-signal models in Fig. 3.7 and the small-signal models in Fig. 3.8 are given to demonstrate the ease with which this Switching Flow-Graph technique can be applied to generate deeper insight into the operation of PWM converters.

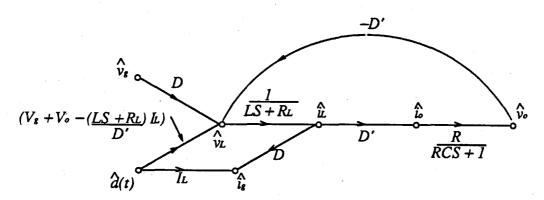

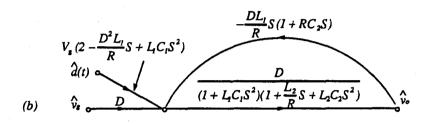

## 3.3 Simplification of the Small-Signal Switching Flow-Graphs

The Switching Flow-Graph small-signal models are linear. Hence all the linear flow-graph reducing techniques are applicable, such as the Flow-Graph algebraic rules, shown in Appendix A, the Mason Formula, etc. The algebraic rules are visual; therefore, they are more straightforward. The algebraic rules are used here to simplify the Switching Flow-Graph small-signal models, shown in Fig. 3.4 and Fig. 3.8 to obtain the input-to-output, the control-to-output transfer functions.

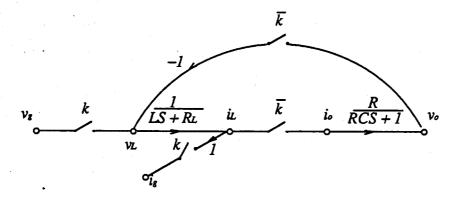

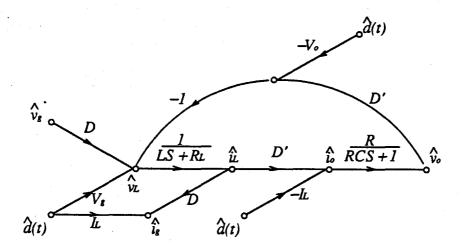

To demonstrate the procedure, the buck converter with input filter in the fourthorder family, as shown in Fig. 3.8(a), is used as an example. First, label all the  $\hat{d}(t)$ control branches, as shown in Fig. 3.9(a). Second, move all the  $\hat{d}(t)$  control branches to one node, for example the  $\hat{v}_{L1}$  node. Branch #1 must be moved forward to node  $\hat{i}_{C1}$  and then backward along the Switching Flow-Graph path from node  $\hat{i}_{C1}$  to node  $\hat{v}_{L1}$ ; therefore, the transmittance of Branch #1 is changed after the move. According to the algebraic rules, a factor of  $-\frac{1}{L_1S}$ , which is the total gain of the path to be crossed, must be divided into the original transmittance. The transmittance of Branch #1 becomes  $-I_{L2}L_1S$ . In order to move Branch #2 to node  $V_{L1}$ , it must cross a local loop that has a gain  $\frac{D}{1+C_1L_1S^2}$ . Therefore the transmittance of Branch #2 becomes  $V_{C1}\frac{1+C_1L_1S^2}{D}$ . By superposition, Branch #1 and #2 can be combined into one branch with a transmittance  $N_d$ , as shown in fig. 3.9(b).

$$N_d = V_{C1} \frac{1 + C_1 L_1 S^2}{D} - I_{L2} L_1 S \tag{3.1}$$

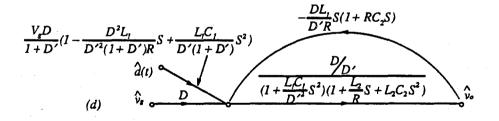

The third step in the simplification involves reshaping of the  $\hat{i}_{L2}$  feedback branch. Move the feedback point from node  $\hat{i}_{L2}$  to node  $\hat{v}_o$ , and move the injection point from node  $\hat{i}_{C1}$  to node  $\hat{v}_{L1}$ , that yields a feedback transmittance of  $-\frac{DL_1}{R}S(1+RC_2S)$ , as shown in Fig. 3.9(c). Last, reshape the two local feedback loops. The left loop is reduced to a branch with transmittance  $\frac{1}{1+C_1L_1S^2}$ , and the right loop is reduced to a branch with transmittance  $\frac{1}{1+\frac{L_2}{R}S+L_2C_2S^2}$ , as shown in Fig. 3.9(d).

The input-to-output transfer function and the control-to-output transfer function of the buck converter with input filter are read from Fig. 3.9(d).

$$\frac{\hat{v}_o}{\hat{v}_g} \approx \frac{D}{(1 + \frac{D^2 L_1}{R} S + \frac{1}{L_0 C_0} S^2)(1 + \frac{L_2}{R} S + \frac{1}{L_0 C_0} S^2)}$$

(3.2)

$$= \frac{K_g}{(1 + \frac{1}{Q_1\omega_1}S + \frac{1}{\omega_1^2}S^2)(1 + \frac{1}{Q_2\omega_2}S + \frac{1}{\omega_2^2}S^2)}$$

(3.3)

$$\frac{\hat{v}_o}{\hat{d}} \approx \frac{V_g (1 - \frac{D^2 L_1}{R} S + L_1 C_1 S^2)}{(1 + \frac{D^2 L_1}{R} S + \frac{1}{L_1 C_1} S^2)(1 + \frac{L_2}{R} S + \frac{1}{L_2 C_2} S^2)}$$

(3.4)

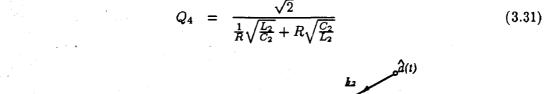

$$= \frac{K_d(1 + \frac{1}{Q_0\omega_0}S + \frac{1}{\omega_0^2}S^2)}{(1 + \frac{1}{Q_1\omega_1}S + \frac{1}{\omega^2}S^2)(1 + \frac{1}{Q_2\omega_2}S + \frac{1}{\omega_0^2}S^2)}$$

(3.5)

where

$$K_g = D (3.6)$$

Figure 3.9: Reduce the Switching Flow-Graph of the Buck Converter with Input Filter. (a) The original Switching Flow-Graph of the Buck Converter with Input Filter. (b) Move all d(t) control branch to one node. (c) Reshape the  $i_{L2}$  feedback branch. (d) Reduce two local feedback loops.

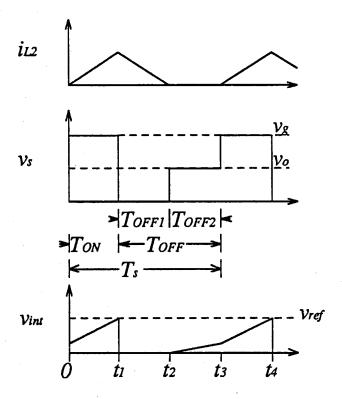

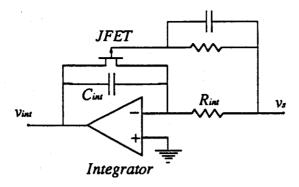

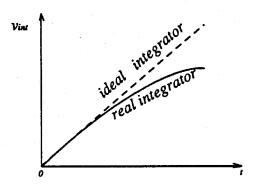

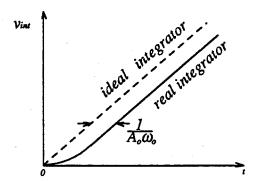

Figure 3.10: The Small-Signal Transfer Functions of the Second-Order PWM Converters. The small-signal transfer function for the buck converter (a), the boost converter (b), and the buckboost converter (c).