# Investigation of Novel Semiconductor Heterostructure Systems:

## I: Cerium Oxide/Silicon Heterostructures

## II: 6.1 Å Semiconductor-Based Avalanche Photodiodes

Thesis by

Edward J. Preisler

In Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

California Institute of Technology Pasadena, California

2003 (Submitted March 25, 2003)

© 2003 Edward J. Preisler All Rights Reserved To Cori

## Acknowledgements

The largest share of my gratitude will always be with my wife. Being a spouse of a scientist is just as difficult as being a scientist yourself and Cori managed to perfect this art form flawlessly. If it hadn't been for her, the Caltech experience would have made me a stranger and more maladjusted person (and I guess that's saying something).

When I sit and think about the effect my advisor, Tom McGill, has had on me, I come up with two things. First, the best and worst thing he has ever done for me as a student is convincing me that I am doing good work and that I am a legitimate researcher. I don't know if it's true, but having Tom's endorsement is the next best thing to believing it myself. Second, Tom runs a group in which we have to learn to do *everything*. It seems like a pain, but after five years, you find you've received an extremely broad education in performing research.

I benefited in very real ways from interactions with all of my contemporaries in the group. Firstly I need to thank Tim Harris for insulating all of us from the financial side of science and letting us just worry about research. Bob Beach is the only guy in the world who, if you told him you wanted to build a synchrotron out of spare parts in the lab, not only would tell you it was a good idea, but could also probably find most of the parts. Cory Hill taught me everything I ever wanted to know but was afraid to ask about MBE, plus he forced me to keep my short game healthy. Xavier Cartoixà always had reasonable (and correct) explanations of every solid-state physics question I ever had. Plus he calculated the band structure of every possible permutation of binary 6.1 Å semiconductor superlattices for me in about an hour (literally). Justin Brooke gave all of my projects a real shot in the arm, plus, while he was here I didn't have to be the only muck-raking liberal around. And he makes a mean mojitos (not that there's anything wrong with that). I want to thank Neal Oldham for his courage and enthusiasm when it comes to all things UHV. What would a vent be without

Neal around? I seem to have a knack for finding the "don't cares" in our computers' truth tables, so I have to thank Steve Ichiriu for cleaning up those messes. He'll have a lot more time on his hands to do research when I'm gone. Lastly, I've got to thank Rob Strittmatter for being the most dependable source of knowledge and insight I've come across (most people probably wonder if this is the same Rob). I guess I always got more of his yin than his yang or vice versa, but there are several parts of this thesis I couldn't have done without his help.

I have also had the help of several group associates in my research. I had nothing but positive experiences with the late Jim McCaldin who was one of the few great academics who didn't talk down to you even though it was probably his right to. Gerry Picus forced me to always make sure I knew what I was talking about and when I did (which was rare) he'd trust me. Ogden Marsh has an idea for how to measure anything and everything. He is by far the best person to talk to when things seem completely hopeless.

Finally I'd like to thank my family. In addition to the usual love and support stuff, my mom made certain that I never smoothed any data, my dad is the most rapt and competent audience in the world for talking about science, and my sister, going through an undergrad physics program at the same time as I went through Caltech, constantly exposed how little I actually understood about physics and forced me to relearn things.

Thanks to all these people, I think I finally know enough to take some measurements. Oh well.

## Abstract

The work presented in this thesis concerns the development of two different semiconductor heterostructure technologies.

Part I describes research in the  $CeO_2/silicon$  heterostructure system. Details are presented concerning the growth of  $CeO_2$  on silicon and the reactions that take place at the  $CeO_2/silicon$  interface. The evolution of this interface as a function of annealing temperature and annealing ambient are studied via *in situ* x-ray photoelectron spectroscopy (XPS). Studies of metal-CeO<sub>2</sub>-silicon capacitors are also presented which help to determine the usefulness of this oxide as an alternative gate dielectric for silicon-based device applications.

Part II involves research into the fabrication of avalanche photodiodes (APD's) utilizing the 6.1 Å semiconductor system. Certain alloys of  $Al_xGa_{1-x}Sb$  are shown to greatly favor hole multiplication which is beneficial for both noise characteristics and gain-bandwidth product. Further, details are presented on the current investigation into using 6.1 Å superlattices to acheive even more desirable detector performance.

# Contents

| Α            | Acknowledgements |                                                                                                             |    |  |

|--------------|------------------|-------------------------------------------------------------------------------------------------------------|----|--|

| $\mathbf{A}$ | bstra            | act                                                                                                         | vi |  |

| 1            | Inti             | roduction                                                                                                   | 1  |  |

|              | 1.1              | Thesis Overview                                                                                             | 1  |  |

|              | 1.2              | Motivation                                                                                                  | 2  |  |

|              |                  | 1.2.1 CeO <sub>2</sub> /Silicon Heterostructures                                                            | 2  |  |

|              |                  | 1.2.2 6.1 Å Avalanche Photodiodes                                                                           | 9  |  |

|              | 1.3              | Summary of Results                                                                                          | 20 |  |

|              |                  | 1.3.1 CeO <sub>2</sub> /Silicon Heterostructures                                                            | 20 |  |

|              |                  | 1.3.2 6.1 Å Avalanche Photodiodes $\dots \dots \dots$ | 21 |  |

|              | Bibl             | liogrpahy                                                                                                   | 23 |  |

|              |                  |                                                                                                             |    |  |

| Ι            | Ce               | ${ m eO}_2/{ m Silicon~Heterostructures}$                                                                   | 27 |  |

| <b>2</b>     | Ce(              | $\mathbf{D}_2 \; \mathbf{Growth}$                                                                           | 28 |  |

|              | 2.1              | Overview                                                                                                    | 28 |  |

|              | 2.2              | Background of $CeO_2$ Growth on Silicon                                                                     | 28 |  |

|              | 2.3              | Silicon Preparation                                                                                         | 29 |  |

|              | 2.4              | E-Beam Deposition                                                                                           | 30 |  |

|              | 2.5              | Pulsed Laser Deposition                                                                                     | 30 |  |

|              |                  | 2.5.1 PLD Growth Rates                                                                                      | 39 |  |

|              | 2.6              | Conclusion                                                                                                  | 42 |  |

|              | Bibl             | liogrpahy                                                                                                   | 44 |  |

| 3  | XPS  | S Studies of the $CeO_2/Silicon$ Interface     | 46  |

|----|------|------------------------------------------------|-----|

|    | 3.1  | Overview                                       | 46  |

|    | 3.2  | Introduction                                   | 46  |

|    | 3.3  | Experiment                                     | 47  |

|    | 3.4  | Analysis Techniques and Fitting of Core Levels | 48  |

|    |      | 3.4.1 Silicon 2p Core Level                    | 51  |

|    |      | 3.4.2 Cerium 3d Core Level                     | 53  |

|    |      | 3.4.3 Oxygen 1s Core Level                     | 57  |

|    |      | 3.4.4 Valence Band                             | 59  |

|    | 3.5  | Results                                        | 61  |

|    | 3.6  | Conclusion                                     | 72  |

|    | Bibl | iogrpahy                                       | 73  |

| 4  | Met  | $tal-CeO_2$ -Silicon Capacitors                | 76  |

|    | 4.1  | Overview                                       | 76  |

|    | 4.2  | Introduction                                   | 76  |

|    | 4.3  | Experiment                                     | 77  |

|    | 4.4  | Theory                                         | 78  |

|    | 4.5  | Results                                        | 87  |

|    |      | 4.5.1 Capacitance-Voltage Analysis             | 87  |

|    |      | 4.5.2 Interface Trap State Density             | 92  |

|    | 4.6  | Conclusion                                     | 95  |

|    | Bibl | iogrpahy                                       | 99  |

| 5  | Par  | t I Conclusion                                 | 100 |

| II | 6.   | .1 Å Semiconductor-Based Avalanche Photodiodes | 102 |

| 6  | The  | Physics of Avalanche Photodiodes               | 103 |

|    | 6.1  | Overview                                       | 103 |

|    | 6.2  | Introduction                                   | 103 |

|              | 6.0             |                                                                       | 104  |

|--------------|-----------------|-----------------------------------------------------------------------|------|

|              | 6.3             | Threshold Energy and Impact Ionization Coefficient                    | 104  |

|              | 6.4             | Noise Considerations                                                  | 106  |

|              | 6.5             | Materials Considerations                                              | 109  |

|              | 6.6             | Choosing Materials for Study in This Work                             | 113  |

|              | Bibl            | iogrpahy                                                              | 116  |

| 7            | $\mathbf{Al}_x$ | $Ga_{1-x}Sb \ APD's$                                                  | 117  |

|              | 7.1             | Overview                                                              | 117  |

|              | 7.2             | Introduction                                                          | 117  |

|              | 7.3             | MBE Growth                                                            | 120  |

|              |                 | 7.3.1 Doping                                                          | 121  |

|              | 7.4             | Device Processing                                                     | 124  |

|              | 7.5             | Electrical Characterization                                           | 127  |

|              | 7.6             | Photoresponse                                                         | 132  |

|              | 7.7             | Conclusion                                                            | 141  |

|              | Bibl            | iogrpahy                                                              | 143  |

| 8            | 6.1             | Å Superlattice APD's                                                  | 145  |

|              | 8.1             | Overview                                                              | 145  |

|              | 8.2             | Introduction                                                          | 145  |

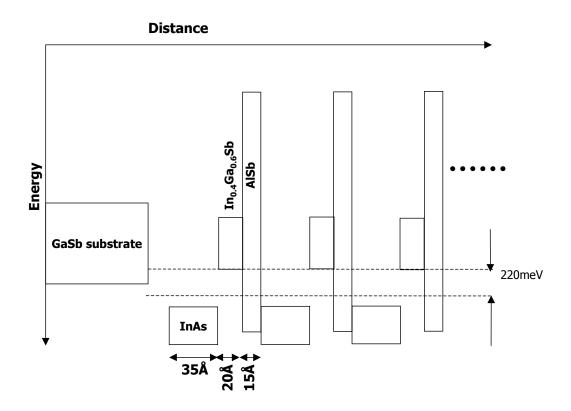

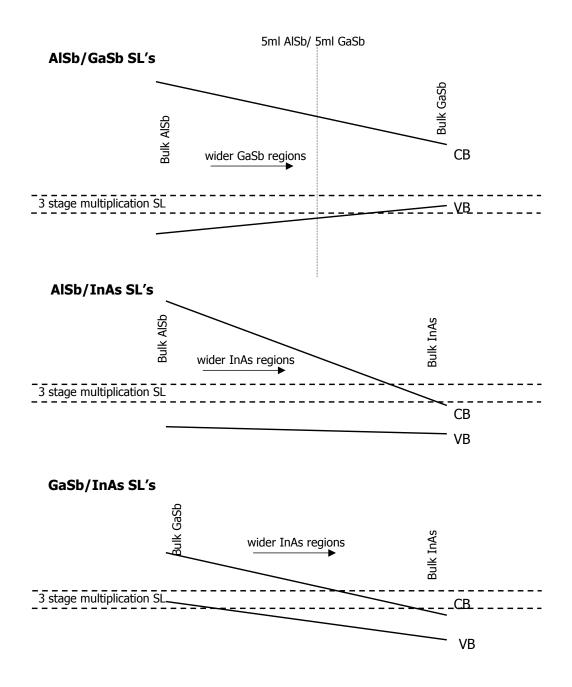

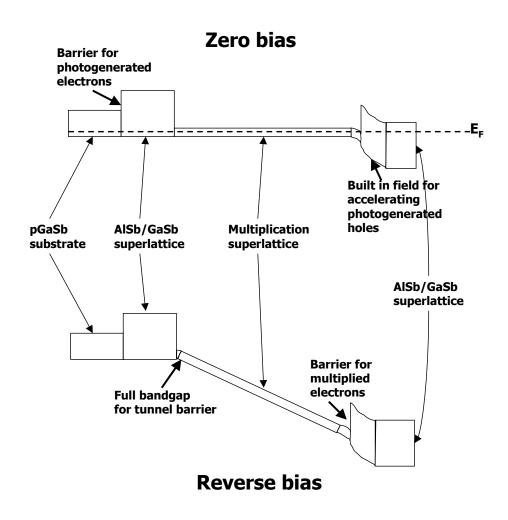

|              | 8.3             | Description of Three-Stage Multiplication Superlattice                | 146  |

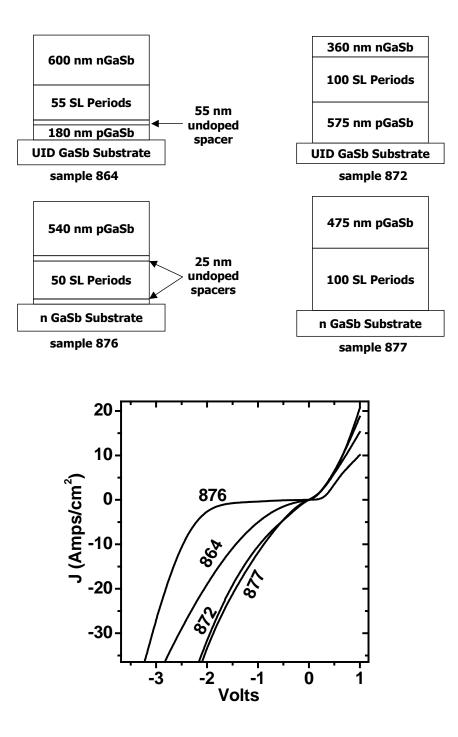

|              | 8.4             | Electrical Characteristics of Superlattice APD's                      | 149  |

|              | 8.5             | New Superlattice Device Designs                                       | 151  |

|              | 8.6             | Conclusion                                                            | 153  |

|              | Bibl            | iogrpahy                                                              | 157  |

| 9            | Par             | t II Conclusion                                                       | 158  |

| $\mathbf{A}$ | Der             | ivation of Interface State Density Formulae                           | 160  |

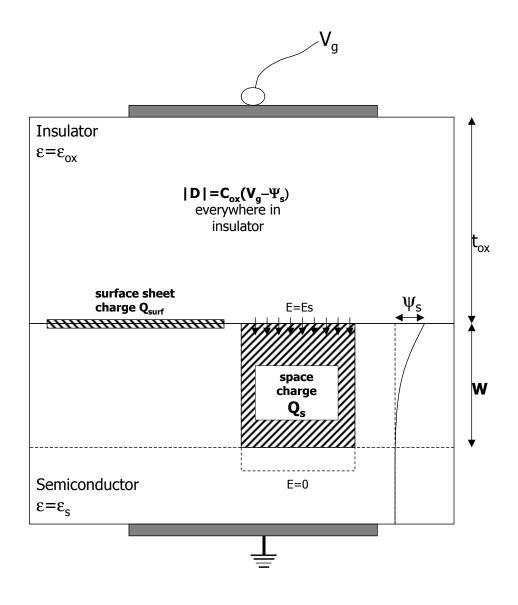

|              | A.1             | Charge-Potential Relationship at Insulator- Semiconductor Interface . | 160  |

|              | A.2             | Simple Equivalent Circuit for MOS Capacitor with Interface Trap Level | s161 |

|              | A.3             | Adjusting Measured Quantities for Bulk Series Resistance              | 163  |

B Derivation of Energy and Momentum Relations for Impact Ionization Events 165

# List of Figures

| 1.1  | Band alignments for the 6.1 Å semiconductor system $\ldots \ldots \ldots$            | 11 |

|------|--------------------------------------------------------------------------------------|----|

| 1.2  | Various applications of the infrared spectrum                                        | 14 |

| 1.3  | Noise equivalent power for an APD with different dark currents and                   |    |

|      | different excess noise factors                                                       | 19 |

| 2.1  | TEM images of $CeO_2$ grown on silicon via e-beam deposition                         | 31 |

| 2.2  | Schematic of PLD setup                                                               | 33 |

| 2.3  | RHEED images of $CeO_2$ grown on silicon via PLD                                     | 34 |

| 2.4  | XPS spectra of PLD-grown ${\rm CeO}_2$ grown under various oxygen ambients           | 36 |

| 2.5  | XRD scan of a stoichiometric thin film of single-crystalline $CeO_2$ on              |    |

|      | silicon (111)                                                                        | 38 |

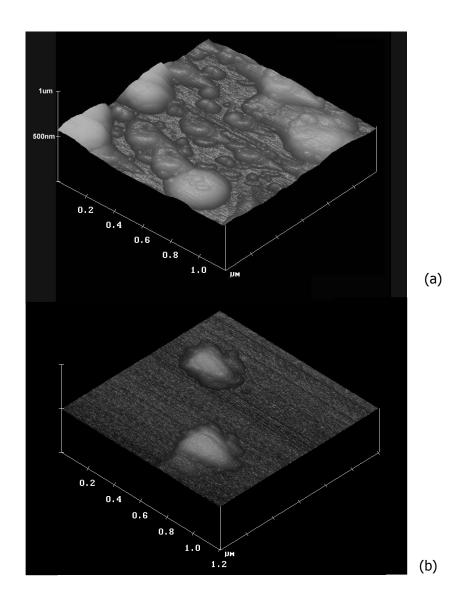

| 2.6  | AFM image of $CeO_2$ films grown by PLD with two different wavelengths               | 40 |

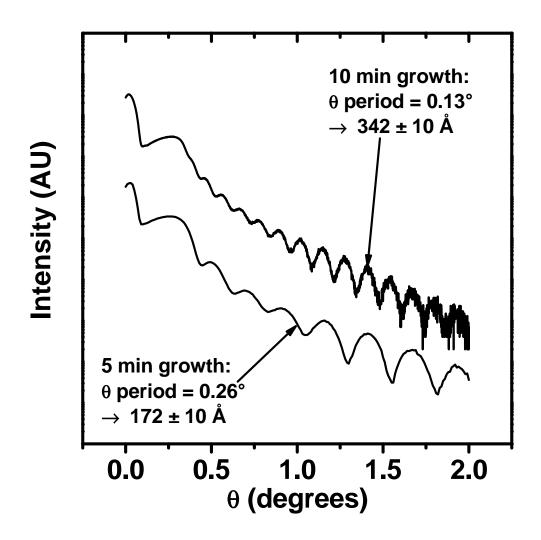

| 2.7  | X-Ray reflectivity for two $CeO_2$ samples of different thicknesses $\ldots$         | 41 |

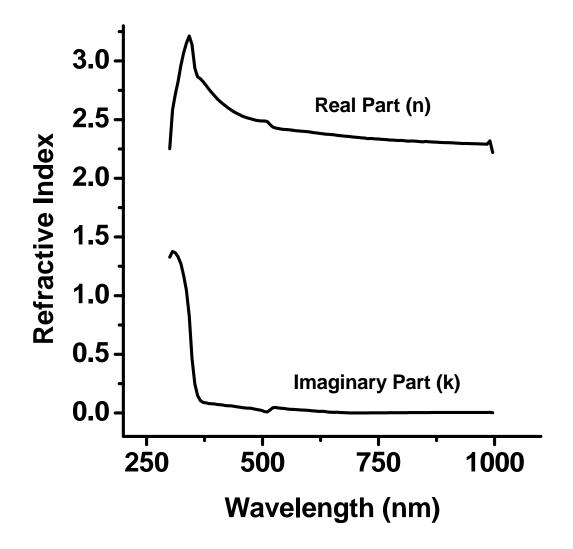

| 2.8  | Optical constants for PLD-grown $CeO_2$ films                                        | 43 |

| 3.1  | Schematic of sample used for XPS experiments                                         | 49 |

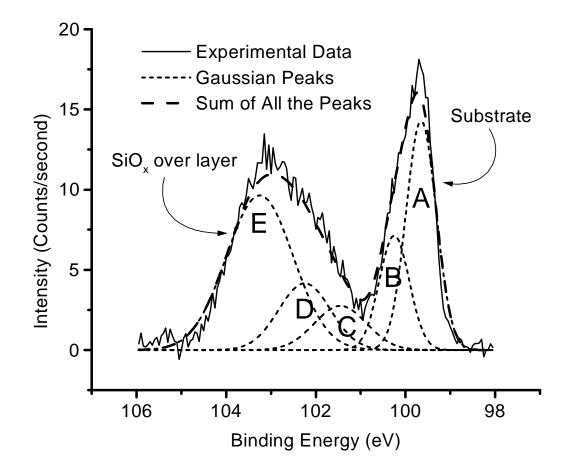

| 3.2  | Example of Si 2p spectrum                                                            | 54 |

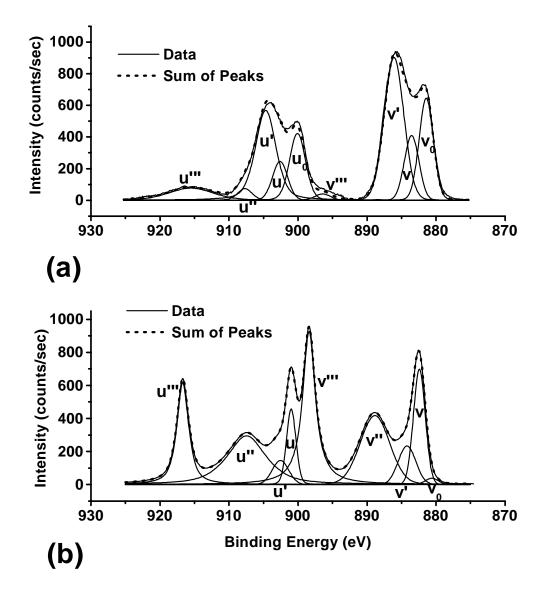

| 3.3  | Example of Ce 3d spectrum                                                            | 56 |

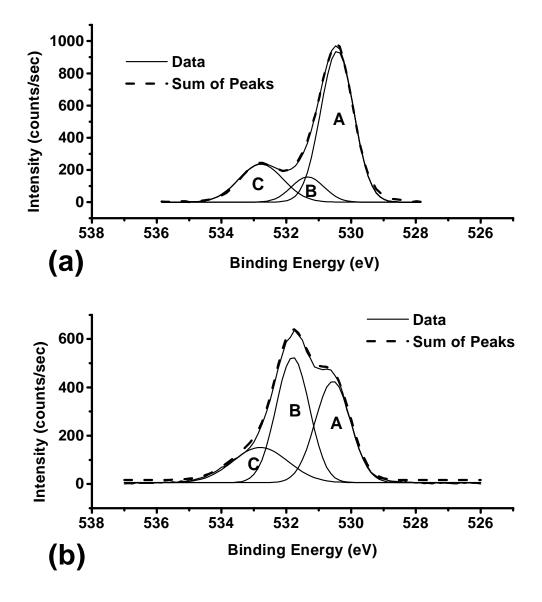

| 3.4  | Example of O 1s spectrum                                                             | 60 |

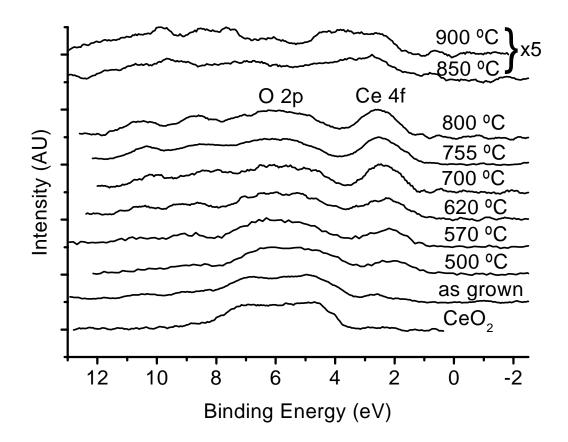

| 3.5  | Valence band spectra                                                                 | 62 |

| 3.6  | $SiO_{2-x}$ thickness versus anneal temperature $\ldots \ldots \ldots \ldots \ldots$ | 63 |

| 3.7  | $SiO_{2-x}$ oxidation state versus anneal temperature $\ldots \ldots \ldots \ldots$  | 64 |

| 3.8  | Cerium oxidation state as calculated from the Ce 3d spectrum $\ . \ . \ .$           | 67 |

| 3.9  | Cerium oxidation state as calculated from the O 1s spectrum                          | 69 |

| 3.10 | Model of the $CeO_x$ /silicon interface                                              | 71 |

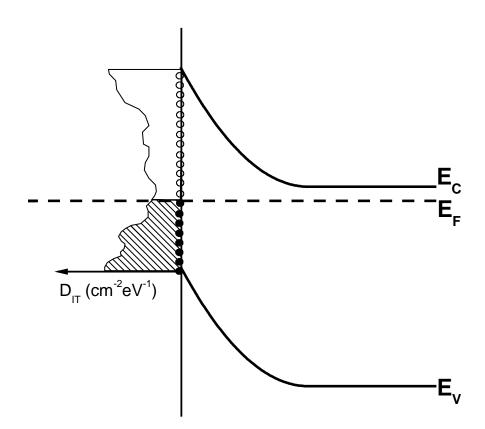

| 4.1  | Schematic of an insulator-semiconductor interface with interface states              | 80 |

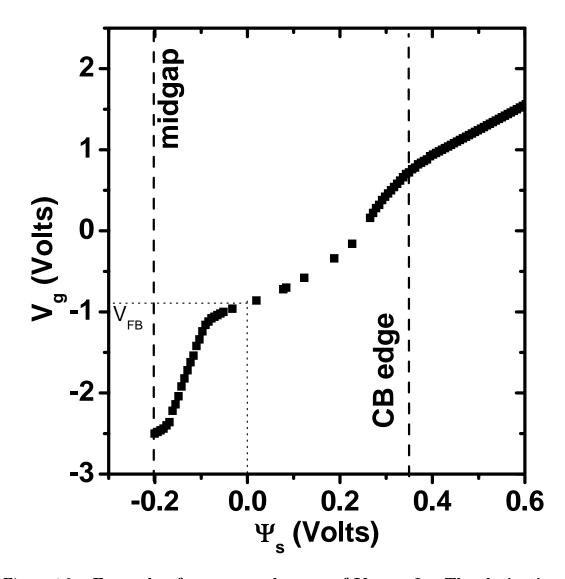

| 4.2  | Example of a measured curve of $V_g$ vs. $\Psi_s$                                                       | 82   |

|------|---------------------------------------------------------------------------------------------------------|------|

| 4.3  | Equivalent circuit models for a MOS capacitor with interface traps                                      | 85   |

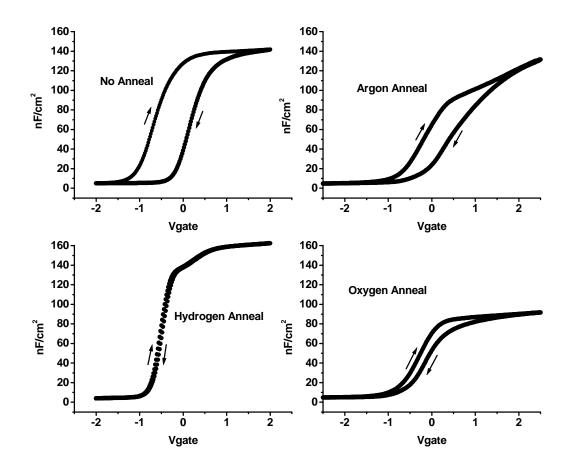

| 4.4  | C-V of $CeO_2$ MOS capacitors annealed under various conditions                                         | 88   |

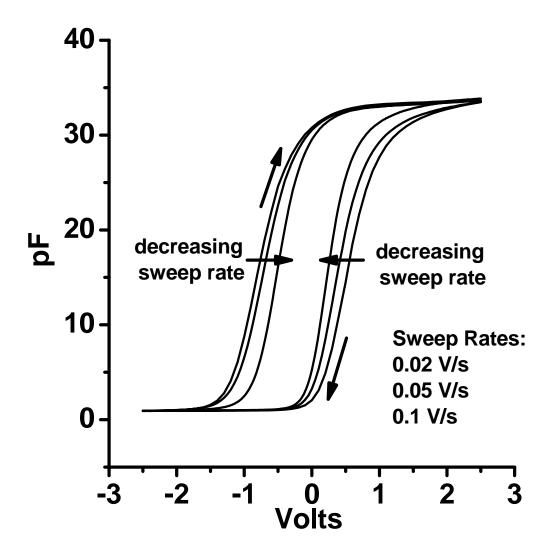

| 4.5  | Dependence of hysteresis on sweep rate                                                                  | 90   |

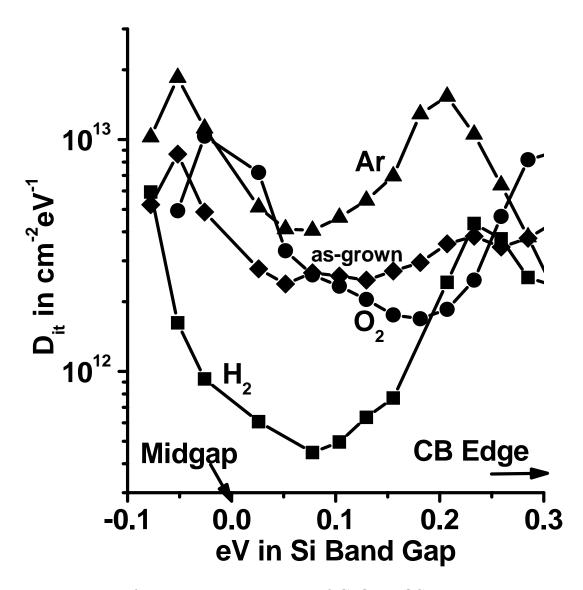

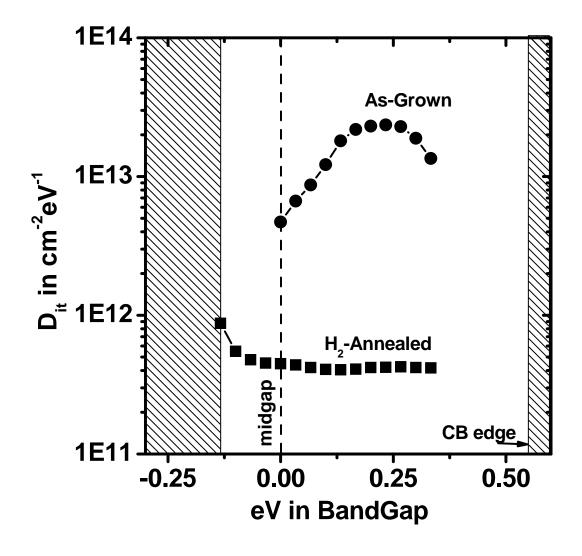

| 4.6  | Interface trap state density of $CeO_2$ MOS capacitors annealed under                                   |      |

|      | various conditions                                                                                      | 94   |

| 4.7  | Interface trap state density of $CeO_2$ MOS capacitors as measured by                                   |      |

|      | the conductance method                                                                                  | 96   |

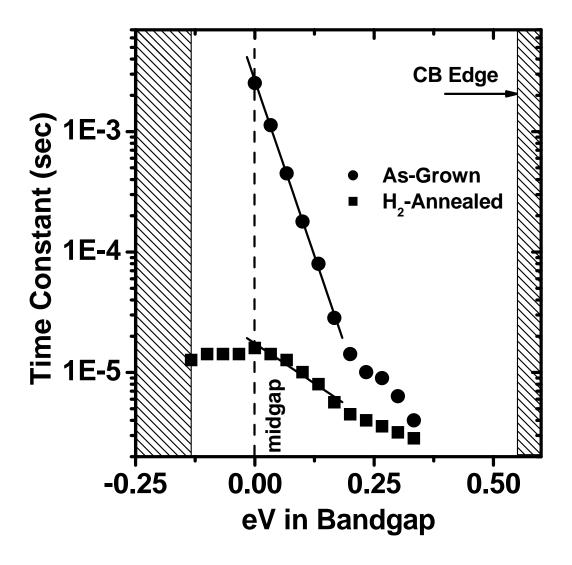

| 4.8  | Measured time constants of the distribution of interface traps $\ldots$ .                               | 97   |

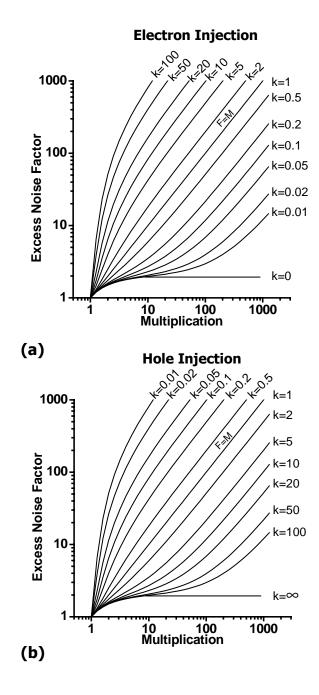

| 6.1  | Excess noise factor as a function of gain                                                               | 108  |

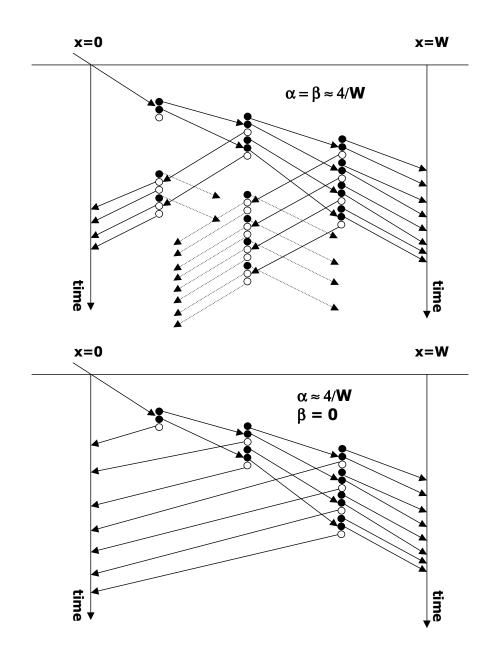

| 6.2  | Diagram of avalanche multiplication for $\alpha = \beta$ and $\alpha \gg \beta$                         | 110  |

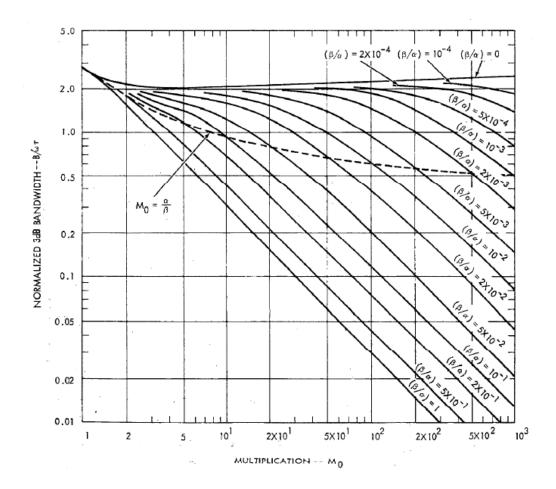

| 6.3  | 3 dB bandwidth for APD's with various values of $k$ $\hdots$                                            | 111  |

| 6.4  | Schematic of an impact ionization process for a semiconductor with                                      |      |

|      | three parabolic bands                                                                                   | 114  |

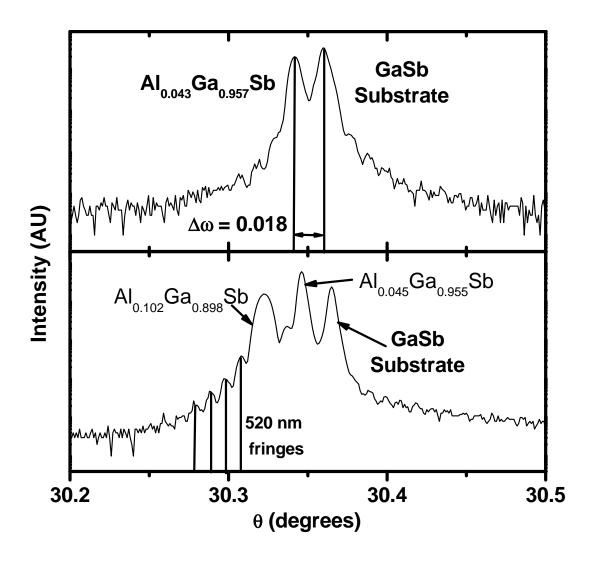

| 7.1  | $\theta/2\theta$ scans of Al <sub>x</sub> Ga <sub>1-x</sub> Sb on GaSb                                  | 122  |

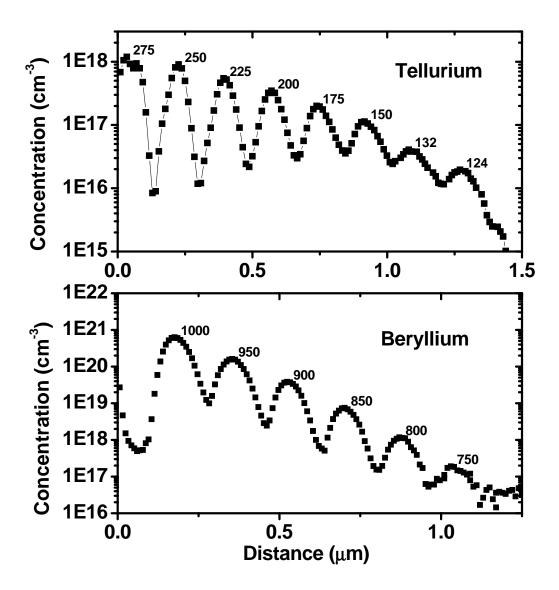

| 7.2  | SIMS Profiles of Te and Be doping in MBE growths                                                        | 123  |

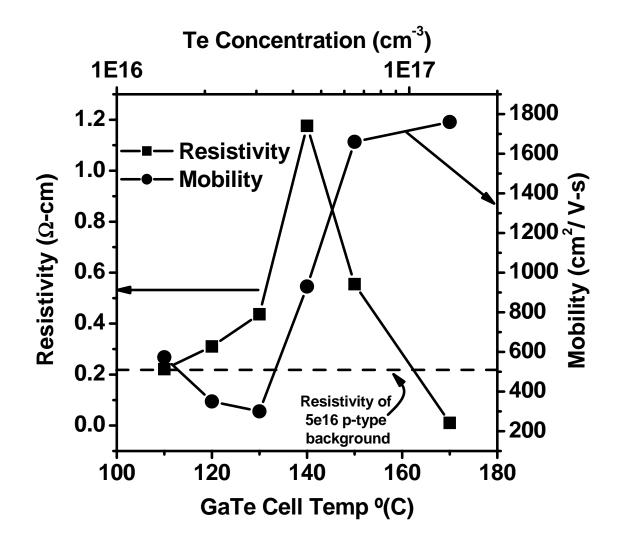

| 7.3  | Resistivity and mobility of counterdoped $\mathrm{Al}_{0.05}\mathrm{Ga}_{0.95}\mathrm{Sb}$ layers $\ .$ | 125  |

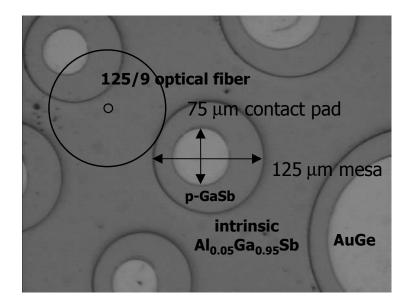

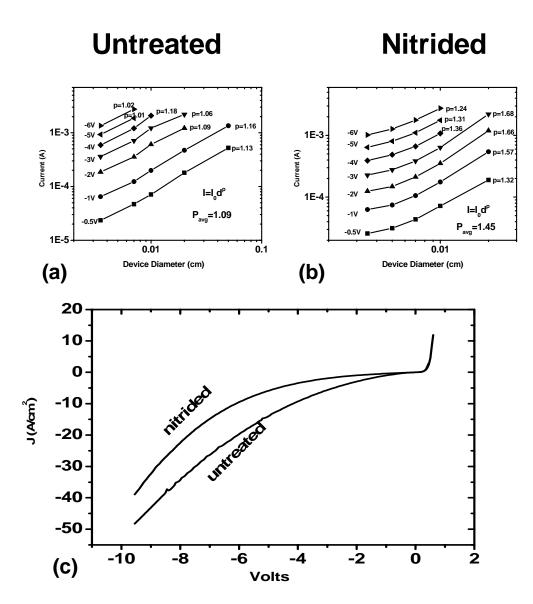

| 7.4  | Image of processed p-i-n mesa APD's and schematic cross section of                                      |      |

|      | mesas                                                                                                   | 126  |

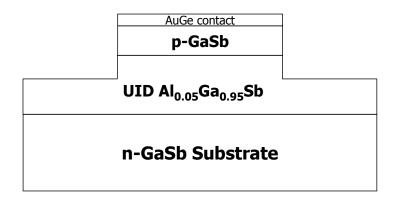

| 7.5  | I-V and C-V plots for counterdoped and non-counterdoped samples .                                       | 128  |

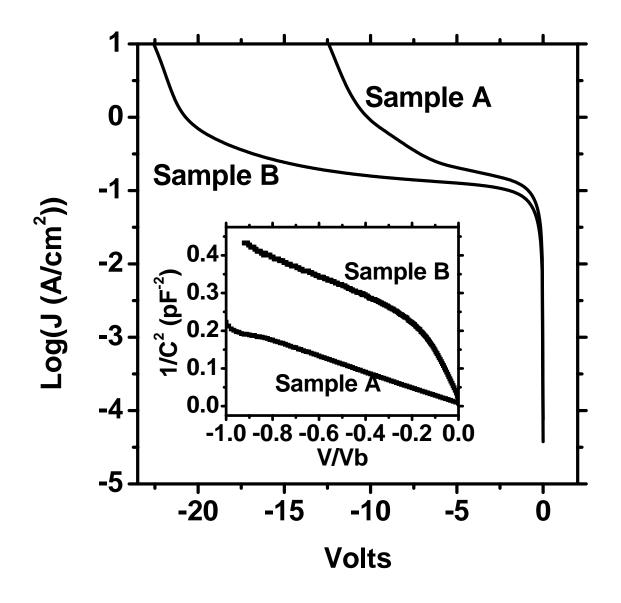

| 7.6  | Comparison of untreated and nitrogen plasma treated p-i-n mesa diode                                    | s130 |

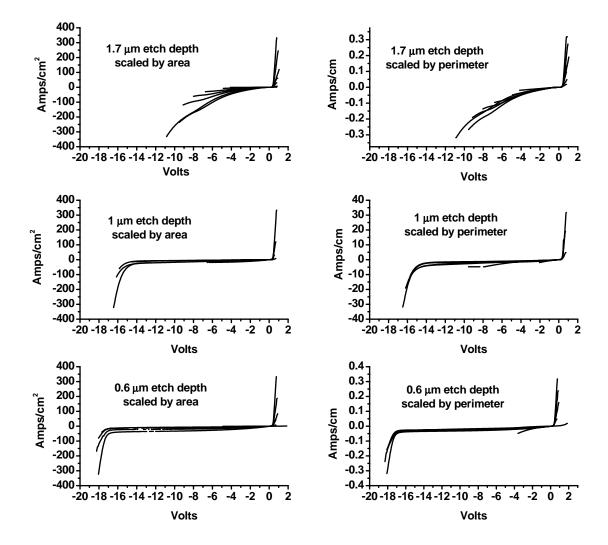

| 7.7  | I-V curves of p-i-n mesa diodes etched to different depths                                              | 131  |

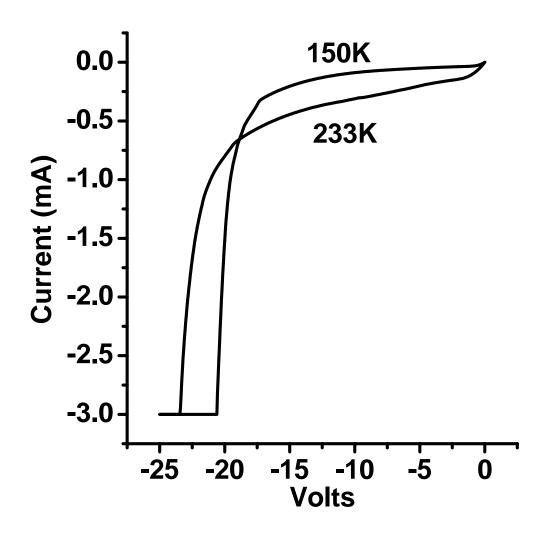

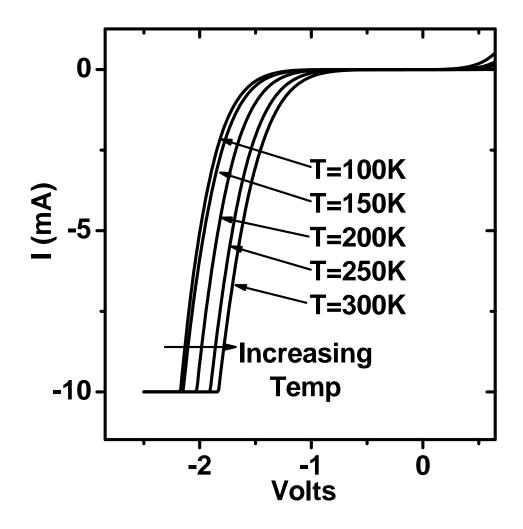

| 7.8  | Temperature-dependent I-V curves of p-i-n mesa diodes                                                   | 133  |

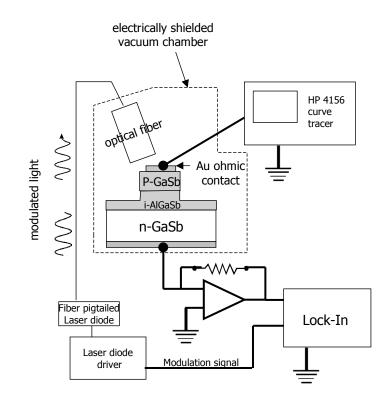

| 7.9  | Schematic of setup for photoresponse measurements                                                       | 134  |

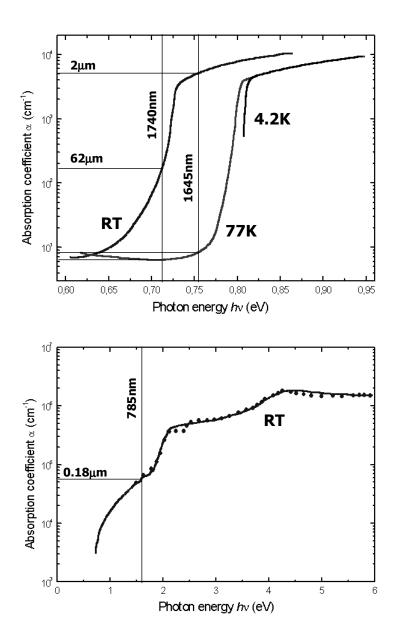

| 7.10 | Absorption spectrum of GaSb                                                                             | 135  |

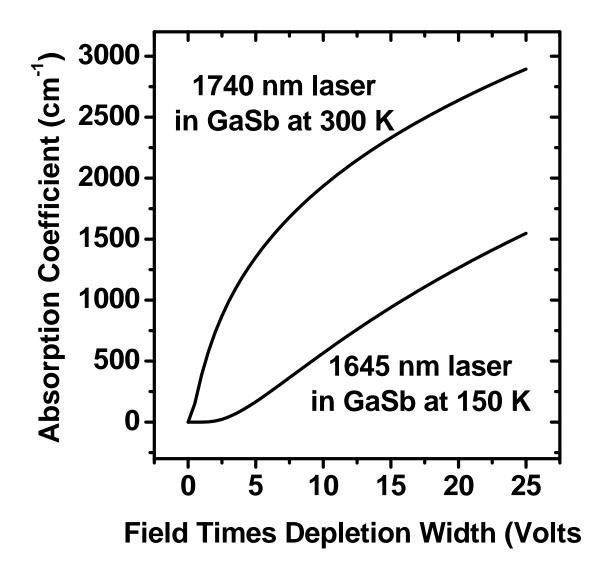

| 7.11 | Absorption coefficient as a function of applied bias in GaSb                                            | 138  |

| 7.12 | Room temperature photoresponse and I-V for an $\rm Al_{0.05}Ga_{0.95}Sb$ APD                            |      |

|      | illuminated by three different laser wavelengths                                                        | 140  |

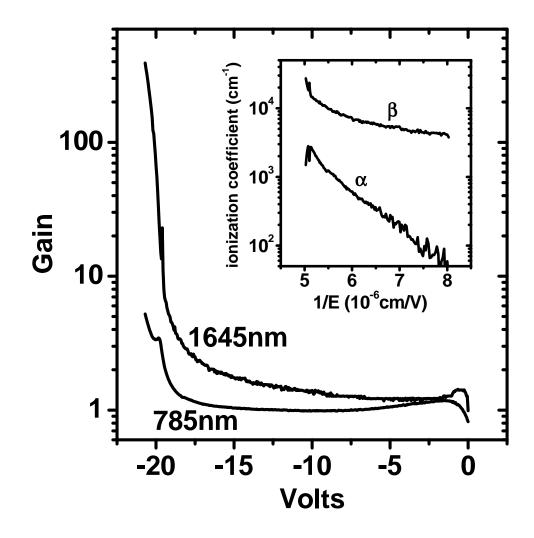

| 7.13 | Photoresponse and impact ionization coefficients at 150 K for an $Al_{0.05}Ga$      | $_{0.95}\mathrm{Sb}$ |

|------|-------------------------------------------------------------------------------------|----------------------|

|      | APD illuminated by two different laser wavelengths $\ldots \ldots \ldots$           | 142                  |

| 8.1  | Schematic of the three-stage multiplication superlattice                            | 147                  |

| 8.2  | Diagram of four superlattice APD samples along with typical I-V char-               |                      |

|      | acteristics                                                                         | 148                  |

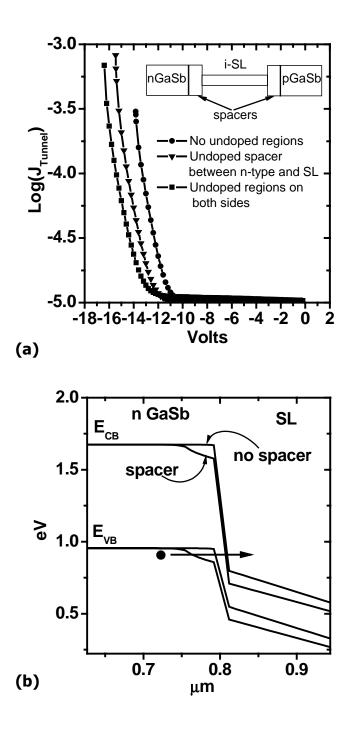

| 8.3  | Computer simulations of p-sl-n diodes with or without undoped spacer                |                      |

|      | layers                                                                              | 150                  |

| 8.4  | Temperature-dependent reverse bias I-V curves of a p-sl-n APD $\ . \ . \ .$         | 152                  |

| 8.5  | Schematic diagram of 6.1 Å binary superlattices $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 154                  |

| 8.6  | Band diagram of a theoretical APD using superlattices for both the                  |                      |

|      | multiplication region and the n and p-type contacts $\ . \ . \ . \ . \ .$           | 155                  |

| A.1  | Schematic of the important charges, fields and potentials at the insu-              |                      |

|      | lator semiconductor interface                                                       | 162                  |

# List of Tables

| 1.1 | Properties of alternative gate dielectric candidate materials                                | 6   |

|-----|----------------------------------------------------------------------------------------------|-----|

| 1.2 | Properties of silicon heterostructure candidate materials                                    | 8   |

| 1.3 | Mobilities of 6.1 Å semiconductors $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 12  |

| 1.4 | Sources of light for night vision                                                            | 15  |

| 3.1 | Electron inelastic mean free paths                                                           | 52  |

| 3.2 | Assignment of Si 2p peak labels                                                              | 55  |

| 3.3 | Assignment of Ce 3d peak labels                                                              | 58  |

| 4.1 | Summary of bulk charges in metal-CeO <sub>2</sub> -silicon capacitors $\ldots \ldots$        | 89  |

| 6.1 | Values of k and $E_G$ for some common semiconductors $\ldots \ldots \ldots$                  | 115 |

## Chapter 1 Introduction

### 1.1 Thesis Overview

This thesis is a report on two different semiconductor heterostructure systems. Part I is a general study of aspects of the cerium oxide/silicon heterostructure system. Cerium oxide has become the subject of considerable attention in the field of silicon electronics because of its excellent lattice match with silicon, its insulating properties and its chemical stability. However, certain aspects of this materials system are as of yet poorly understood and need extensive further examination to bring the system to the level of maturity needed for commercial devices.

In particular, the following areas are of critical importance. First, the behavior of the semiconductor-insulator interface formed between silicon and cerium oxide needs to be quantified. Among the most important pieces of information are a precise knowledge of the species formed at the interface, the interface trap state density and the conduction band offset with silicon. These are all critical parameters in determining cerium oxide's usefulness for metal-oxide-semiconductor (MOS) applications. Second, more exact knowledge of the nature of cerium oxide in thin film form will need to be ascertained in order to predict its applicability as a tunnel barrier in a silicon-based resonant tunneling device.

In order to clarify the issues addressed above, the work presented in Part I details a host of different types of analysis. These include, but are not limited to, x-ray photoelectron spectroscopy (XPS) to determine interface properties and the nature of chemical bonding in the oxide thin films, and capacitance and conductance profiling of MOS capacitor devices to examine the electrical behavior of films.

In the end, it is the aim of this project to expand the level of understanding of the cerium oxide/silicon heterojunction system from its current state of perhaps only scientific interest to the point where it is known whether or not it has the properties necessary to be used in practical devices. Along the way it becomes clear that much about the nature of oxide thin films and semiconductor-insulator junctions in general is exemplified by this system.

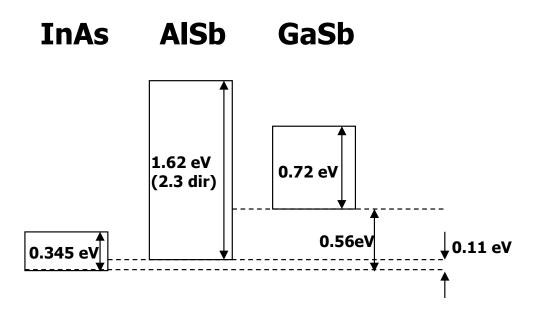

Part II concerns research on the 6.1 Å family of semiconductors. The three semiconductors, InAs, AlSb and GaSb, known as the 6.1 Å family because they share roughly that lattice constant, are gaining importance in the fields of optoelectronics and high speed electronic devices. They have bandgaps that span from the visible to the near infrared and exhibit type I, type II-staggered and type II-broken gap band offsets with respect to one another. These properties, combined with the ability to grow all three materials epitaxially on one another, enable the creation of an incredibly rich and diverse range of superlattices that can extend the usefulness of the system.

The work presented in Part II is a study of the application of this system to a specific kind of optoelectronic device known as an avalanche photodiode (APD). The work concerns adapting an alloy of  $Al_xGa_{1-x}Sb$  for use as a multiplication region in an APD as well as progress towards the use of various 6.1 Å superlattices in APD's. Aspects of growth, materials characterization, device fabrication and finally device characterization are discussed.

The purpose of this project is to advance the technology of 6.1 Å APD's to the point where they have properties that are comparable or superior to competitive infrared APD material systems such as  $Hg_xCd_{1-x}$ Te and  $In_xGa_{1-x}$ As.

### 1.2 Motivation

#### 1.2.1 $CeO_2/Silicon$ Heterostructures

#### The Future of Silicon Electronics

As semiconductor devices continue to scale down in size and up in speed, several fundamental physical limits begin to loom. For metal-oxide-silicon field effect transistor (MOSFET) technology, for instance, these limits include the minimum gate oxide thickness that can still prevent gate leakage and the maximum saturation velocity of carriers in silicon that ultimately determines the operation frequency. Although alternative semiconductors provide some answers (such as III-V's for high speed devices) for a path to circumvent these problems, there also may be some ways to extend the life of silicon itself. Two such paths are indicated below: alternative gate dielectrics and silicon-based heterostructures, both of which can be facilitated by the introduction of cerium oxide materials into traditional silicon-based electronic device structures.

#### Alternative Gate Dielectrics

The ability to "scale" down the size of MOSFET's while maintaining roughly the same electrical behavior is the reason that microprocessor technology has been able to increase in speed and exponentially increase in device density over time (Moore's law).

The basic MOSFET scaling argument is as follows (see, for instance, reference [1]). The main parameter that shrinks with each successive generation of transistor is the gate width. Smaller gate widths allow more transistors to be packed into a smaller area and reduce the transit times for carriers going from source to drain. However, in order to keep the transistor normally off, as is required for complementary MOS (CMOS) logic, the semiconductor region under the gate cannot be fully depleted at zero bias. This leads to the need for higher doping in the gate region so that the source and drain depletion widths will not extend to the point where they meet each other (punch-through). The higher doping requirement in turn leads to higher charge density at the semiconductor-insulator interface. Thus, in order to invert the channel and thus turn on the device, a higher gate voltage will be necessary. Finally, in order to keep the same threshold voltages to turn on the device, a higher gate capacitance is needed. A higher gate capacitance also improves the subthreshold voltage current swing and the on-state drive current. Traditionally the gate capacitance is increased by simply thinning the gate oxide.

Theoretically the gate capacitance diverges as the oxide thickness goes to zero but

of course in reality, other effects take over as the thickness approaches the "quantum" limit (roughly the de Broglie wavelength of an electron). Most importantly quantum tunneling from the gate electrode to the semiconductor becomes significant, especially under an applied bias. This translates to a "leakage" current which consumes excess power and reduces transistor gain and noise margins. Also, the uniformity of devices across a large wafer becomes more and more sensitive to fluctuations in the actual oxide thickness. For instance, for a 20Å thick gate oxide, a deviation of even one atomic layer of silicon atoms (about 2Å) would create a 10% fluctuation in thickness and hence about a 10% fluctuation in threshold voltage which would greatly affect the consistency of device performance across the chip. In fact, Intel researchers came to the conclusion that for their purposes the most pressing physical limit standing in the way of future device scaling is the gate oxide thickness [2, 3].

Alternative gate dielectrics have been vigorously sought after as a way to avoid the gate oxide thickness problem. That is, gate insulators made out of materials with a higher dielectric constant than that of  $SiO_2$  can be made thicker while maintaining the same device performance (same gate capacitance per unit area) in order to prevent gate leakage.

There are several candidates for possible materials to replace SiO<sub>2</sub>. Buchanan [4] gives an excellent overview of the use of silicon oxynitrides as gate dielectrics and recently Yeo et al. [5] have successfully made silicon nitride MOS devices with promising characteristics. However, it is not clear how much can be gained from using nitrided oxides or pure silicon nitride because their bandgap and band offsets with silicon are always going to be less than those of SiO<sub>2</sub> without gaining much in dielectric constant ( $\kappa$ =7.5 for Si<sub>3</sub>N<sub>4</sub> as compared to  $\kappa$ =3.9 for SiO<sub>2</sub>). Also, while there is some knowledge about the interface state density [6], little is known about how the stoichiometry of silicon nitride and deposition conditions can affect the device.

Many other metal oxides have also been proposed. Most notable are zirconium oxide [7] or yttria stabilized zirconium oxide (YSZ) [8], tantalum oxide [9], hafnium oxide [10], and titanium oxide [11]. A comparison of the pertinent parameters for gate dielectrics of these and various other dielectrics along with those of cerium oxide are shown in Table 1.1.

As one can see from the table, each dielectric has its own advantages and disadvantages. For instance, while  $SrTiO_3$  has a huge dielectric constant and relatively good interface properties, it has almost no conduction band offset to silicon and grows in a perovskite structure that can be very difficult to control. Or for the case of  $Si_3N_4$ , while it has a large (2.4 eV) band offset to silicon, it has a relatively low dielectric constant and poor interface qualities.

Comparatively little research has been done on the application of the cerium oxides as gate dielectrics. The values for the bandgap and the interface state density vary widely in the literature [20, 21, 22]. Also, even though Hubbard and Schlom have calculated CeO<sub>2</sub> to be thermodynamically unstable on silicon at 1000K [14], it has been shown that it can be grown epitaxially on silicon anyway with no amorphous SiO<sub>2-x</sub> layer at the interface through the use of pulsed laser deposition (PLD) at very low temperatures [23]. Even if the CeO<sub>2</sub> reacts with the silicon, it will reduce to Ce<sub>2</sub>O<sub>3</sub> (see chapter 3), which is thermodynamically stable on silicon even at high temperatures and still acts as an insulator. In other words an ultrathin suboxide layer between the semiconductor and the CeO<sub>2</sub> will barely affect most device properties.

Another potentially critical advantage of  $CeO_2$  over some of the other materials listed in Table 1.1 is the ability to grow  $CeO_2$  epitaxially on silicon. The mobility of carriers in the channel of a MOSFET is almost exclusively governed by scattering at the silicon-insulator interface either via coulomb interactions or interactions with a mechanically rough interface. For a true epitaxially grown insulator, the carriers in the channel would have mobilities much closer to their bulk values since there are no dangling bonds or drastic breaks in symmetry at a heteroepitaxial interface. In this case the channel would be a true two-dimensional electron or hole gas as is used for the channel in a heterojunction field effect transistor (HFET).

All in all, the cerium oxides have properties that are comparable to all of the other materials listed and yet have been studied far less than all the others in terms of their use as a gate dielectric.

|                                | Dielectric  | Band         | CB Offset             | Interface Trap                       | Crystalline | Thermo-       |

|--------------------------------|-------------|--------------|-----------------------|--------------------------------------|-------------|---------------|

| Material                       | Constant    | Gap (eV)     | w.r.t                 | State Density                        | Growth      | dynamically   |

|                                |             |              | Si (eV)               | $(\mathrm{cm}^{-2}\mathrm{eV}^{-1})$ | on Si?      | Stable on Si? |

| $\mathrm{SiO}_2$               | 3.9         | 9            | 3.5                   | $\leq$ 1×10 <sup>10</sup>            | No          | NA            |

| $\mathrm{Si}_3\mathrm{N}_4$    | 7.5         | 5.3 [12]     | 2.4 [12]              | $5 \times 10^{11}$ [6]               | No          | NA            |

| $\mathrm{SiO}_x \mathrm{N}_y$  | 3.9-7.5     | 5.3-9        | 2.4-3.5               | ?                                    | No          | NA            |

| YSZ                            | 25-29.7 [8] | $\sim_{5.8}$ | $\sim_{1.4}$          | $2 \times 10^{11}$ [8]               | Yes         | Yes? [8]      |

| $\rm ZrO_2$                    | 20-25 [13]  | 5.8 [12]     | 1.4 [12]              | $3 \times 10^{11}$ [13]              | No          | Yes [14]      |

| HfO <sub>2</sub>               | 30 [10]     | 6 [12]       | 1.5 [12]              | $1 \times 10^{11}$ [10]              | No          | Yes [14]      |

| $\mathrm{TiO}_2$               | 40-86 [11]  | 3-3.5 [11]   | 1 [11]                | $1 \times 10^{11}$ [15]              | No          | No [14]       |

| $Ta_2O_5$                      | 25 [9]      | 4.4 [12]     | 0.3 [12] (theory)     | $2 \times 10^{11}$ [16]              | Yes         | No [14]       |

|                                |             |              | $0.77 \ [17] \ (exp)$ |                                      |             |               |

| SrTiO <sub>3</sub>             | 150 [11]    | 3.3 [12]     | -0.1 [12]             | $6.4 \times 10^{10}$ [18]            | Yes         | No [14]       |

| ${\rm CeO}_2$                  | 20-26       | 5.5 [19]     | ?                     | $2 \times 10^{11}$ (see note)        | Yes         | No [14]       |

| Ce <sub>2</sub> O <sub>3</sub> | ?           | 3 [19]       | ?                     | ?                                    | ?           | Yes [14]      |

Table 1.1: Comparison of the important properties of various candidates for alternative gate dielectrics for silicon MOSFET's. The interface trap state density for  $CeO_2$  is taken from the data in Chapter 4. Since all of the other numbers in this table were taken on Si (100) substrates, the number has been divided by two to reflect that it is taken for growth on a (111) substrate which has a higher dangling bond density than (100).

#### Silicon-Based Heterostructures

Different device paradigms and changes in the traditional structure of silicon devices have also been proposed as ways to further the development of silicon-based electronics. Devices that use quantum confinement such as resonant tunneling diodes have been suggested as a way to enable higher speeds and multi-state logic [24]. Stacking of layers of nanoelectronics has also been proposed as a way to increase device density for a given area of wafer. Finally, use of silicon-on-insulator (SOI) layers instead of bulk silicon has been shown to improve both the speed and power consumption of CMOS circuits [25]. To enable any of these techniques one must search for a material that can be grown on silicon and then have single-crystal silicon grown back on it. As of yet, nobody has created a true silicon heterostructure akin to those created in III-V semiconductor systems. While SiGe alloys provide somewhat of a solution, the maximum conduction band offset achievable is very low ( $\sim 0.1 \text{eV}$  [26]) which makes using this heterojunction for quantum confinement almost impossible at room temperature. An epitaxial insulator with a wide bandgap would effectively enable this technology as well as provide a true insulating substrate for growing single-crystal silicon for SOI. Table 1.2 gives a summary of some potential silicon heteromaterials and their properties.

Again it is clear that  $\text{CeO}_2$  has properties that are comparable to those of the other materials in the table in terms of qualities for forming a silicon heterostructure.  $\text{Ce}_2\text{O}_3$  is also shown to emphasize that it too can be made to be commensurate with the silicon lattice because of its convenient match to the hexagonal symmetry (111) face of Si. The experiments carried out by Kirk et al. on ZnS [33] and  $\text{BeSe}_x\text{Te}_{1-x}$  [34] have shown that fairly good epitaxial silicon can be grown on these materials. They also have shown the  $\text{BeSe}_x\text{Te}_{1-x}$  system to have reasonable band offsets and electrical qualities. The example of  $\text{Pr}_2\text{O}_3$  is shown above as an example of a materials system very similar to that of the cerium oxides, in which relatively precise interfaces have been created and silicon overgrowth achieved [30]. However,  $\text{Pr}_2\text{O}_3$  has a hexagonal crystal structure and thus only can be grown epitaxially on Si (111).  $(\text{La}_x\text{Y}_{1-x})_2\text{O}_3$

|                                                 | Crystal        | Lattice Constant           | Bandgap      | Conduction          |

|-------------------------------------------------|----------------|----------------------------|--------------|---------------------|

| Material                                        | Structure      | in Å                       | in eV        | Band                |

|                                                 |                | (mismatch to Si)           |              | Offset (eV)         |

| Silicon                                         | Diamond        | 5.43 (0)                   | 1.12         | NA                  |

| $\mathrm{Si}_x\mathrm{Ge}_y$                    | Diamond        | 5.43-5.65 (0-4%)           | 0.66-1.12    | 0-0.1 [26]          |

| ZnS                                             | Zinc Blende    | 5.42~(0.2%)                | 3.7          | 1.7 on (111) [27]   |

|                                                 |                |                            |              | 1.0  on  (100) [28] |

| $\operatorname{BeSe}_x\operatorname{Te}_{1-x}$  | Zinc Blende    | 5.63-5.15 (0-5.2%)         | 2.7 - 4.5    | 1.3 [29]            |

| $Pr_2O_3$                                       | Hexagonal [30] | (0.5%) (111) only [30]     | 2.5-3.9 [31] | 0.5 - 1.5 [31]      |

| $(\mathrm{La}_x\mathrm{Y}_{1-x})_2\mathrm{O}_3$ | Variable [32]  | (0-2.4%) [32]              | ?            | ?                   |

| ${\rm CeO}_2$                                   | Fluorite       | 5.41(0.4%)                 | 5.5 [19]     | ?                   |

| $\rm Ce_2O_3$                                   | Hexagonal      | a=3.89(1.2%  on(111)) [19] | 3 [19]       | ?                   |

Table 1.2: Comparison of the important properties of various candidates for silicon heterostructure materials.

represents another oxide that has been used for successful regrowth of epitaxial silicon, also on (111), but may potentially be grown on (100) in the future because it can be made to form in a cubic crystal structure [32]. CeO<sub>2</sub> always grows in the cubic CaF<sub>2</sub> structure so it is theoretically possible to grow CeO<sub>2</sub> on any face of silicon.

All of these materials show promise as silicon heterojunction materials and it is probably only limited time and resources that have prevented these technologies from maturing further. The excellent lattice match and commensurate cubic crystal structure of  $CeO_2$  make it an excellent candidate for a silicon heterostructure material. Combined with its favorable properties as an alternative gate dielectric, it is clear that there should be significant experimental effort put forth in determining the usefulness of applying  $CeO_2$  to silicon-based electronics.

#### 1.2.2 6.1 Å Avalanche Photodiodes

#### Overview of the 6.1 Å Semiconductor Materials

Over the last two decades or so, compound semiconductors such as GaAs have been studied nearly as much as silicon. However, the application of compound semiconductor devices lags far behind the now omnipresent silicon-based device industry. There are several reasons for this, most notably the failure to create a viable III-V MOS device. However, in the field of optoelectronics, which can loosely be defined as electronics applied to the creation of or detection of light, compound semiconductors dominate. This can be attributed mostly to two factors. Firstly, many compound semiconductors (most notably GaAs) have direct bandgaps that allow light to be emitted or absorbed efficiently. Secondly, the ability to "engineer" the bandgap of materials by creating alloys and heterostructures makes compound semiconductors far more flexible than silicon.

In Part II of this thesis, a relatively new compound semiconductor system is examined for its suitability in creating optoelectronic devices.

The three semiconductors InAs, AlSb and GaSb are known as the 6.1 Å family because they share roughly that lattice constant. They already have been successfully employed in making infrared light detectors [35] and infrared lasers [36]. Although not discussed any further herein, they also have been applied to high-speed electronic devices [37, 38].

All three materials grow in the Zinc Blende crystal structure and the excellent lattice match between the three materials allows all three to be grown epitaxially on one another, as can many mixed III or mixed V alloys [39]. Their bandgaps span the range from the near infrared to the visible and between the three of them, they exhibit type I, type II-staggered gap and type II-broken gap band offsets [40] (see Fig. 1.1). InAs and GaSb are direct gap materials while AlSb is indirect.

Superlattices can be grown that take advantage of these properties and move the useful optical spectrum of the system out into the mid infrared [35]. In fact, because of the type II-broken gap band offset between InAs and GaSb, there is no theoretical lower limit to the effective bandgap that can be engineered within this system.

Even for use in optoelectronic devices, the electronic properties of the system will be important in creating practical devices. Table 1.3 shows the mobilities for these materials as compared to GaAs. InAs has an extremely high electron mobility and GaSb has a higher hole mobility than most of the other III-V's. Also, n-type InAs forms a negative Schottky barrier with most metals so ohmic contacts easily can be made to any n-type 6.1 Å material.

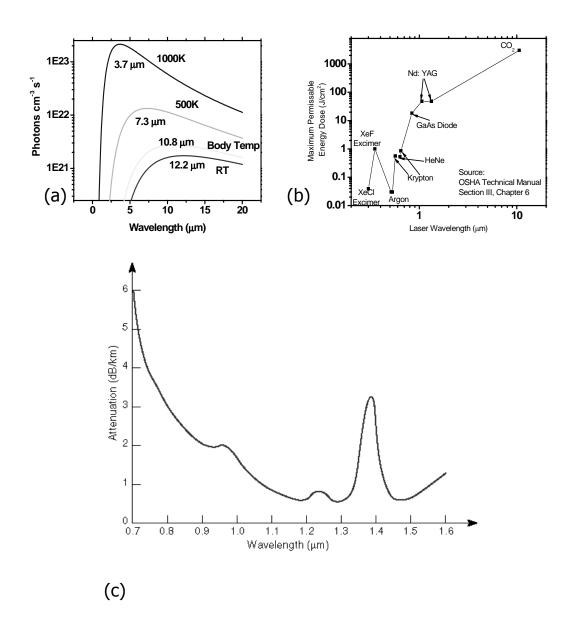

#### Uses of the Infrared Spectrum

The information contained in the infrared light spectrum is useful in several practical applications. One example is thermal imaging where one seeks to identify an object by detecting its blackbody radiation against a background of different temperature. Figure 1.2 (a) illustrates the fact that objects that are at practical temperatures on Earth emit most strongly in the mid to far infrared (greater than about  $5\mu$ m). A second example is active imaging such as 3-D LIDAR where a reflected laser beam is used for detecting objects and determining their distance from the detector analogous to RADAR. In these applications it would be advantageous to have a high power laser that is still "eye-safe." Figure 1.2 (b) shows the maximum permissible energy dose

Figure 1.1: Band alignments for the 6.1 Å semiconductor system.

| Material | J                                        | Hole Mobility |  |

|----------|------------------------------------------|---------------|--|

|          | $({\rm cm}^2 {\rm V}^{-1} {\rm s}^{-1})$ |               |  |

| GaAs     | 9200                                     | 400           |  |

| InAs     | 33000                                    | 450           |  |

| GaSb     | 3759                                     | 680           |  |

| AlSb     | 200                                      | 400           |  |

Table 1.3: Mobilities of 6.1 Å semiconductors compared with GaAs. Datataken from reference [41]

(according to OSHA) absorbed by the human eye for lasers of various wavelengths. One can see that far more energy is permitted as the wavelength is increased, indicating that the infrared spectrum is most suitable for this application. A third example is fiber optic communications. Figure 1.2 (c) shows the well-established minimum at about 1.5  $\mu$ m in the attenuation spectrum of a silica optical fiber. Detectors that operate at this wavelength are needed to process information that has been sent along the fiber. Finally, night vision is a field that benefits greatly from the use of the infrared spectrum. Table 1.4 summarizes the sources of light available for imaging at night. The bands are atmospheric transmission bands centered at the wavelength indicated in the table. On a night where moonlight is weak, the only light available comes from stars or the night airglow which originates from optical transitions of molecules in the atmosphere. One can see from the table that the strongest signal of these remaining light sources comes from the night airglow in the near infrared.

As mentioned above, the 6.1 Å semiconductors are poised to be of great benefit for infrared detection because of the ability to create materials with almost arbitrarily small bandgaps, and hence extremely long wavelength detection capabilities.

#### Application of 6.1 Å Materials to Infrared Avalanche Photodiodes

It is clear that for all of the applications of infrared light detection discussed above, desirable detector qualities will include sensitivity and high-speed performance. Avalanche photodiodes (APD's) can provide a substantial advantage with respect to both the signal-to-noise and gain-bandwidth product metrics of traditional semiconductor photodetectors [43]. While silicon APD's have excellent properties and are readily available commercially, they are limited in their detection wavelength by the bandgap of about 1.1 eV (about 1100 nm). Once again, the 6.1 Å materials can be made to absorb much further into the infrared than any of the other traditional semiconductor systems perhaps with the exception of  $Hg_xCd_{1-x}Te$ .

In most semiconductor photodetectors light is converted into an electrical signal by the absorption of photons with energies greater than the bandgap of the semiconductor material, leading to the creation of electron-hole pairs. The signal then

Figure 1.2: Various applications of the infrared spectrum. Figure (a) shows the blackbody radiation spectrum at various temperatures, Fig. (b) shows the permissible energies for "eye-safe" lasers of different wavelengths and Fig. (c) shows the attenuation spectrum of a silica optical fiber taken from www.newport.com.

| Band | Wavelength       | Moon                  | Stars                   | Night AirGlow            |

|------|------------------|-----------------------|-------------------------|--------------------------|

|      | $\mu \mathrm{m}$ | I                     | photons cm <sup>-</sup> | $^{-2}  \mathrm{s}^{-1}$ |

| 1    | 0.58             | $5.83 \times 10^{11}$ | $1.21 \times 10^{9}$    | $4.2 \times 10^{7}$      |

| 2    | 1                | $1.83 \times 10^{11}$ | $1.24 \times 10^{8}$    |                          |

| 3    | 1.24             | $2.09 \times 10^{11}$ | $1.15 \times 10^{8}$    |                          |

| 4    | 1.59             | $1.99 \times 10^{11}$ | $8.67 \times 10^{7}$    | $4.5 \times 10^{10}$     |

| 5    | 2.1              | $1.37 \times 10^{11}$ | $6.02 \times 10^{7}$    | $2.2 \times 10^{10}$     |

Table 1.4: Sources of light for night vision. Data taken from reference [42]. The data is listed in bands since these wavelengths represent minima in the absorption spectrum of our atmosphere.

is measured by converting these newly created carriers into a current. This is done by using an electric field to accelerate the carriers and thus create a current. This electric field either can be applied externally or can be intrinsic to the device as in a p-n junction or Schottky barrier photodiode. In an ideal case, each photon creates one electron-hole pair and each electron and hole are collected at one terminal of the device or the other and measured as a current. Of course, in reality, this is never the case. Many photons are absorbed by other processes and many carriers are created by processes other than direct bandgap absorption. Thus detection of a small number of photons becomes difficult because of both a finite quantum efficiency (not all photons are converted to electron hole pairs) and a noise floor (some of the current comes from carriers not created by the light).

All photocurrent devices such as the ones discussed above must subsequently pass their signal into a transimpedance amplifier to convert the current signal to a voltage for measurement. At its most basic, a transimpedance amplifier is simply a resistor. The action of current passing through a resistor leads to both shot noise and thermal noise. So while the signal is being amplified by an amount proportional to the value of the resistor, noise is being added to the signal such that there is only an advantage in signal to noise ratio for a finite range of amplification.

It is this added noise coming from the subsequent amplification stage that avalanche photodiodes (APD's) seek to obviate. In an APD, there is already an intrinsic gain mechanism built into the photodetector itself, reducing or even eliminating the need for subsequent amplification. Basically, an APD is a photodiode that absorbs light by creating electron-hole pairs in the same way as the conventional detectors discussed above, but then the carriers enter a gain medium. In this gain medium the number of carriers is multiplied by creating several more electron-hole pairs for each initial carrier. Then the photocurrent that one would measure is the true photocurrent as in a conventional photodetector times this multiplication factor. This is the solid-state analog to a photomultiplier tube.

The intrinsic gain mechanism in APD's comes from the process of impact ionization where a carrier in an electric field in a semiconductor achieves sufficient energy to excite or "ionize" a valence electron into the conduction band. This electric field usually is created by applying a large reverse bias to a p-n junction so that a large field exists in the depletion region. The result of the impact ionization event is two newly created carriers (the excited electron and the hole it left behind in the valence band) plus the initiating carrier, be it a hole or an electron. If this impact ionization event takes place in a region with high enough electric field, the three final carriers in turn can be accelerated and initiate new impact ionization events. Thus after two levels of events, there can be as many as nine carriers directly attributable to the one initial carrier. In certain situations this process can continue indefinitely, reaching a state known as "avalanche breakdown," hence the name of the device. When a device is operated in this regime, it is known as a Geiger-mode device. In carefully controlled situations, devices operated in this mode can detect single photons [44, 45, 46]. More typically, however, devices are operated in a regime where the gain is on the order of 10 to 1000.

However, this added gain does not come without a cost. In order for the APD structure to be advantageous compared to conventional photodetectors, certain criteria must be met by both the materials system and the device design. To illustrate this point, the signal-to-noise ratio of an APD will be examined. The mean squared signal current for a modulated input signal in an APD is given by,

$$\langle I_0^2 \rangle = \frac{1}{2} \left( \frac{q \eta \lambda P_0 M}{hc} \right)^2, \tag{1.1}$$

where  $P_0$  is the power of the optical signal,  $\eta$  is the quantum efficiency,  $\lambda$  is the wavelength of the optical signal and M is the multiplication of the APD. There are two noise sources in the APD and readout circuit: the shot noise coming from all the various currents in the circuit and the thermal noise from all the resistances in the circuit. Thus the mean squared noise current is given by

$$< I_{noise}^2 >= 2qFM^2B[I_0 + I_b + I_d] + 4kTB/R_{eq},$$

(1.2)

where  $I_0$  is the signal current,  $I_b$  is the photoelectric current from background light sources that are not part of the signal,  $I_d$  is the dark current,  $R_{eq}$  is the parallel sum of all the resistances in the circuit and F is called the excess noise factor which is an artifact of the avalanche multiplication process and will be discussed in detail in Chapter 6. Dividing Equation 1.1 by 1.2 gives the mean squared signal to noise ratio. An often cited figure of merit is the noise equivalent power (NEP) defined as the minimum signal power required to give a signal to noise ratio of one. Setting the signal to noise ratio equal to one and solving for  $P_0$  gives

$$NEP = \frac{2hcBF}{\lambda\eta} \left[ 1 + \sqrt{1 + \frac{I_d + I_b + \frac{2kT}{qM^2R_{eq}}}{qBF^2}} \right].$$

(1.3)

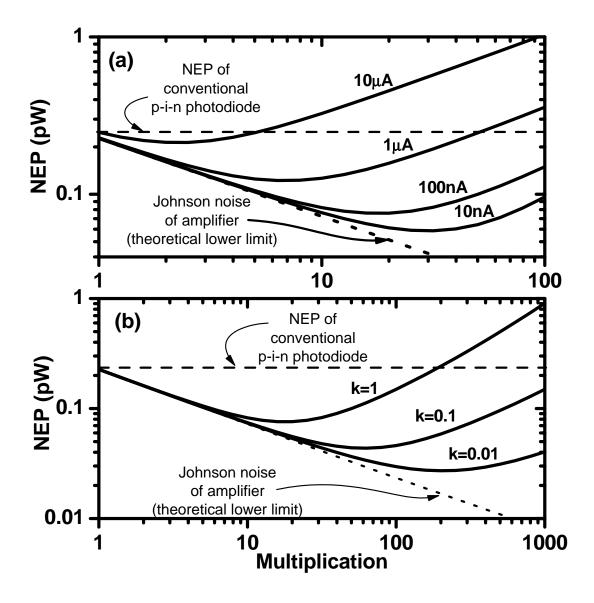

Figure 1.3(a) shows a plot of Equation 1.3 for various values of dark current. It is clear that it is vital to reduce the dark current (current not derived from photogenerated carriers) to improve the noise behavior of APD's.

The excess noise factor is an artifact of the avalanche multiplication process that does not exist in conventional photodetectors. Hence, it must be minimized in order to reap the benefits of the multiplication. As will be shown in Chapter 6, the excess noise factor is a function of multiplication with the worst-case scenario being F=M. It has been shown that APD's made from materials exhibiting a strong preference for impact ionization of one carrier type over the other (e.g., electrons over holes) have the lowest values of the excess noise factor and the highest gain-bandwidth product [47, 48] (this is discussed in much greater detail in Chapter 6). Figure 1.3 (b) shows the NEP for an APD with 100nA of dark current and varying values of "k," which is defined as the ratio of the hole impact ionization coefficient to the electron impact ionization coefficient. It is clear that the value of k also has a profound effect on the noise characteristics.

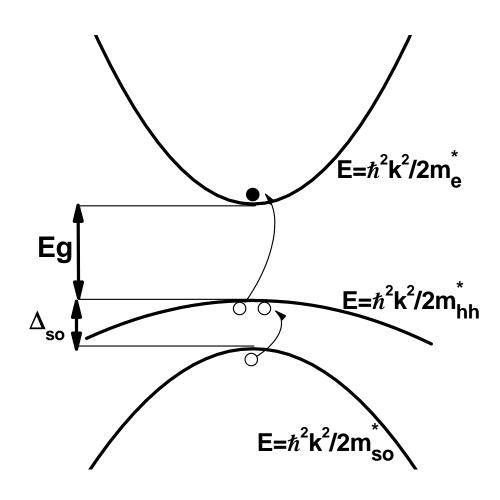

Gallium rich alloys of  $Al_x Ga_{1-x}Sb$  have been shown to greatly favor hole ionization over electron ionization because of a resonance in the energy spacings of the bandgap,  $E_g$  and the split-off band energy,  $\Delta_{so}$  as demonstrated by Hildebrand et al. [49, 50]

Figure 1.3: Noise equivalent power at a bandwidth of 1 GHz for an APD with different dark currents and different values of  $k=\beta/\alpha$ , where  $\beta$  is the hole impact ionization coefficient and  $\alpha$  is the electron impact ionization coefficient. Figure (a) shows the NEP as a function of multiplication for an APD with various dark currents and k=1. Figure (b) shows the NEP as a function of dark current and various values of k. The dashed line is the NEP for a photodiode with no gain. The dotted line represents the noise floor of the external interaction circuit (last term in Equation 1.2).

Thus there may be significant advantages in employing the 6.1 Å system to make APD's, not just in detection wavelength but in the actual performance of the devices as well.

Further, the ability to grow heterostructures of almost arbitrary bandgap and band offset discussed above leads to the possibility of many more improvements in APD design [51]. These improvements include the use of separate absorption and multiplication regions so that one layer of material can be designed so as to have optimum impact ionization characteristics while another layer can be tailored to absorb light of a precise wavelength. Also, by engineering the band offsets between absorption and multiplication regions, one can select either electrons or holes to carry the majority of the signal, enhancing device performance (see Chapter 6).

### **1.3 Summary of Results**

### 1.3.1 CeO<sub>2</sub>/Silicon Heterostructures

In Part I, the nature of thin films of  $CeO_2$  on silicon is studied. First, the growth of  $CeO_2$  on silicon is examined. It is found that single-crystal layers of  $CeO_2$  can be deposited by electron beam evaporation, but only at elevated temperatures which has repercussions as discussed in the next paragraph. It is found that single-crystal layers of cerium oxide can be grown by pulsed laser ablation at much lower temperatures but require a significant additional background oxygen supply. These layers have extremely poor surface topology due to formation of particulates during the laser ablation process. The topology can be improved drastically by choosing a lower laser wavelength for growth, but only with a sacrifice in the crystal quality.

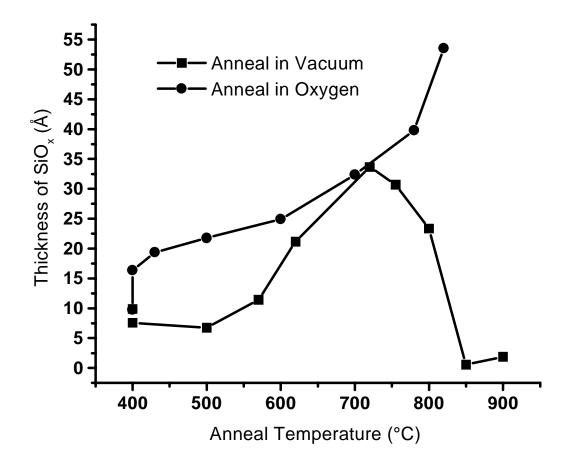

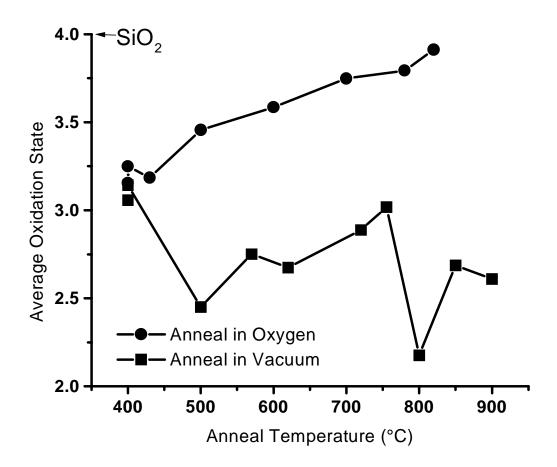

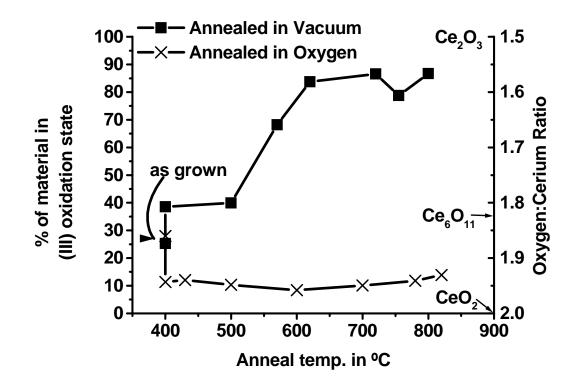

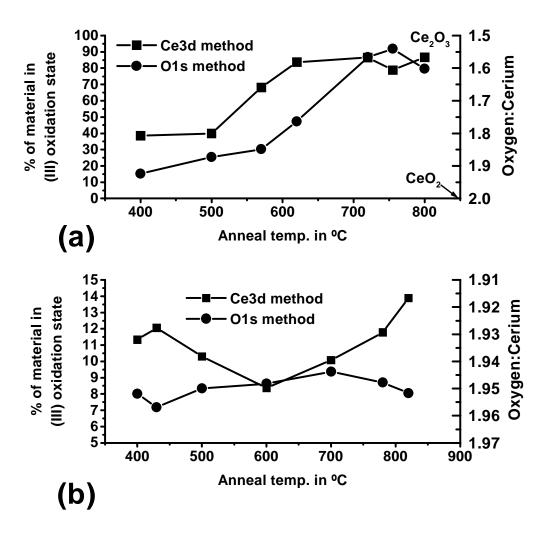

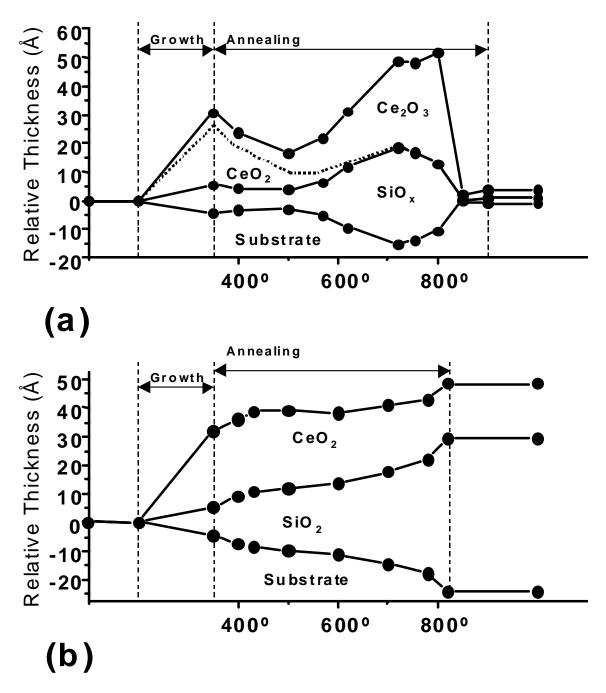

Next, the reactions that take place at the  $\text{CeO}_2/\text{silicon}$  interface are studied by XPS. It is shown that the interface is extremely reactive at elevated temperatures and that it may be difficult or even impossible to bring a stoichiometric layer of  $\text{CeO}_2$  in contact with a silicon surface. It is found that when annealed in vacuum, the  $\text{CeO}_2$  is reduced to  $\text{Ce}_2\text{O}_3$  at the expense of a growing layer of  $\text{SiO}_{2-x}$  between the cerium

oxide and the silicon. It is found that when annealed in an oxygen-rich ambient, the  $CeO_2$  remains stoichiometric but a thick layer of  $SiO_2$  forms between the cerium oxide and the silicon.

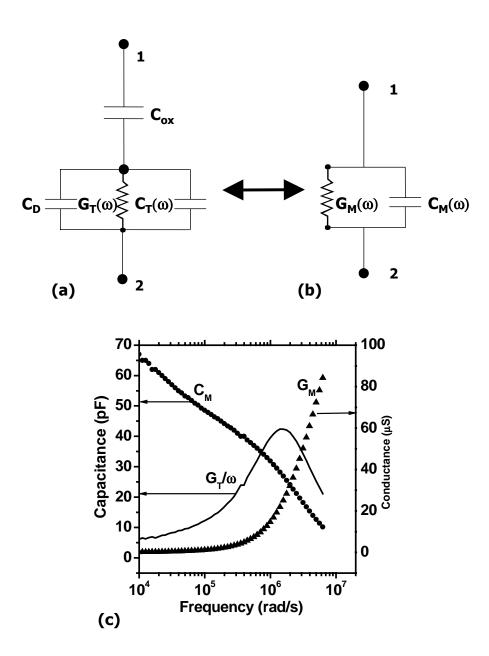

In the next section, electrical characterization of metal-CeO<sub>2</sub>-silicon capacitors is performed. The capacitance-voltage (C-V) characteristics elucidate the dielectric constant, trapped charge in the CeO<sub>2</sub> layer, and the interface trap state density at the CeO<sub>2</sub>/silicon interface. Further, the effect of various annealing procedures on these parameters is discussed. It is shown that the effective dielectric constant of singlecrystalline layers of stoichiometric CeO<sub>2</sub> is on the order of 10 but changes significantly with annealing. There is excessive trapped charge, but annealing seems to eliminate some of it including charges that lead to hysteresis in the C-V curves. The interface trap state density of the as-grown layers is on the order of  $2 \times 10^{12}$  cm<sup>-2</sup>eV<sup>-1</sup> but can be reduced as low as  $4 \times 10^{11}$  cm<sup>-2</sup>eV<sup>-1</sup> by annealing in hydrogen.

#### 1.3.2 6.1 Å Avalanche Photodiodes

In Part II, the results of an investigation of avalanche photodiodes made from 6.1 Å semiconductor materials are discussed. P-i-n avalanche photodiodes using  $Al_{0.05}Ga_{0.95}Sb$  as the intrinsic multiplication layer have been fabricated. Several unique techniques are used in order to create diodes with good electrical and photoresponse behavior. It is found that the treatment of the surfaces of mesa diodes is extremely important for obtaining good reverse bias leakage current behavior. It is also found that counterdoping of the intrinsic layers in p-i-n diodes is highly effective in enhancing both the electrical characteristics and the quality of the photoresponse of the diodes.

It is observed that these devices do indeed show a preference for hole multiplication as predicted. The ratio of the impact ionization coefficients,  $k=\beta/\alpha$  is measured to be about five at high electric fields and much higher as the field is reduced. Avalanche gains of as high as 300 are achieved for devices operating at -20 volts at 150K. All of this data shows great promise for use of this material as a multiplication layer for infrared APD's. Progress also has been made towards fabricating superlattice APD's with 6.1 Å materials. Devices have been fabricated using a superlattice designed specifically for enhanced hole impact ionization. However, it is found that the leakage current of these devices in unacceptably high. Thus the design of new device structures which should show much better leakage properties is discussed. These new structures not only should reduce the leakage current but also actively select the carrier type to be multiplied in the gain region, improving both noise and bandwidth characteristics.

## Bibliography

- D. J. Frank, R. H. Dennard, E. Nowak, P. M. Solomon, Y. Taur, and H. S. P. Wong, Proc. IEEE 89, 259 (2001).

- [2] S. Thompson, P. Packan, and M. Bohr, Intel Technology Journal Q3, 1 (1998).

- [3] B. Doyle, R. Arghavani, D. Barlage, S. Datta, M. Doczy, J. Kavalieros, A. Murthy, and R. Chau, Intel Technology Journal 6, 42 (2002).

- [4] D. A. Buchanan, IBM J. Res. Develop. 43, 245 (1999).

- [5] Y. C. Yeo, Q. Lu, P. Ranade, H. Takeuchi, K. J. Yang, I. Polishchuk, T. J. King, C. Hu, S. C. Song, H. F. Luan, and D. L. Kwong, IEEE Electron Device Lett. 22, 227 (2001).

- [6] J. Schmidt, F. M. Schuurmans, W. C. Sinke, S. W. Glunz, and A. G. Aberle, Appl. Phys. Lett. 71, 252 (1997).

- [7] M. Copel, M. Gribelyuk, and E. Gusev, Appl. Phys. Lett. 76, 436 (2000).

- [8] S. J. Wang, C. K. Ong, S. Y. Xu, P. Chen, W. C. Tjiu, A. Huan, W. J. Yoo, J. S. Lim, W. Feng, and W. K. Choi, Semicond. Sci. Tech. 16, L13 (2001).

- [9] D. Park, Y. King, Q. Lu, T. J. King, C. M. Hu, A. Kalnitsky, S. P. Tay, and C. C. Cheng, IEEE Electron Device Lett. 19, 441 (1998).

- [10] L. Kang, B. H. Lee, W. J. Qi, Y. Jeon, R. Nieh, S. Gopalan, K. Onishi, and J. C. Lee, IEEE Electron Device Lett. 21, 181 (2000).

- [11] S. A. Campbell, H. S. Kim, D. C. Gilmer, B. He, T. Ma, and W. L. Gladfelter, IBM J. Res. Dev. 43, 383 (1999).

- [12] J. Robertson, J. Vac. Sci. Technol. B 18, 1785 (2000).

- [13] C. M. Perkins, B. B. Triplett, P. C. McIntyre, K. C. Saraswat, S. Haukka, and M. Tuominen, Appl. Phys. Lett. 78, 2357 (2001).

- [14] K. J. Hubbard and D. G. Schlom, J. Mater. Res. 11, 2757 (1996).

- [15] H. Fukuda, S. Namioka, M. Miura, Y. Ishikawa, M. Yoshino, and S. Nomura, Jpn. J. Appl. Phys. 38, 6034 (1999).

- [16] B. Lai, N. H. Kung, and J. Lee, J. Appl. Phys. 85, 4087 (1999).

- [17] B. C. Lai, J. C. Yu, and J. Lee, IEEE Electron Device Lett. 22, 221 (2001).

- [18] R. Droopad, Z. Y. Yu, J. Ramdani, L. Hilt, J. Curless, C. Overgaard, J. L. Edwards, J. Finder, K. Eisenbeiser, J. Wang, V. Kaushik, B. Y. Ngyuen, and B. Ooms, J. Crystal Growth 227, 936 (2001).

- [19] N. V. Skorodumova, R. Ahuja, S. I. Simak, I. A. Abrikosov, B. Johansson, and B. I. Lundqvist, Phys. Rev. B 64, 115108 (2001).

- [20] L. Tye, N. A. Elmasry, T. Chikyow, P. Mclarty, and S. M. Bedair, Appl. Phys. Lett. 65, 3081 (1994).

- [21] T. Nakazawa, T. Inoue, M. Satoh, and Y. Yamamoto, Jpn. J. Appl. Phys. 34, 548 (1995).

- [22] Y. Nishikawa, T. Yamaguchi, M. Yoshiki, H. Satake, and N. Fukushima, Appl. Phys. Lett. 81, 4386 (2002).

- [23] M. Yoshimoto, K. Shimozono, T. Maeda, T. Ohnishi, M. Kumagai, T. Chikyow, O. Ishiyama, M. Shinohara, and H. Koinuma, Jpn. J. Appl. Phys. 34, L688 (1995).

- [24] J. P. Sun, G. I. Haddad, P. Mazumder, and J. N. Schulman, Proc. IEEE 86, 641 (1998).

- [25] G. G. Shahidi, IBM J. Res. Dev. 46, 121 (2002).

- [26] E. T. Yu, E. T. Croke, T. C. Mcgill, and R. H. Miles, Appl. Phys. Lett. 56, 569 (1990).

- [27] C. Maierhofer, S. Kulkarni, M. Alonso, T. Reich, and K. Horn, J. Vac. Sci. Technol. B 9, 2238 (1991).

- [28] B. Brar, R. Steinhoff, A. Seabaugh, X. Zhou, S. Jiang, and W. P. Kirk, Compound Semiconductors 1997 156, 167 (1998).

- [29] W. P. Kirk, K. Clark, E. Maldonado, N. Basit, R. T. Bate, and G. F. Spencer, Superlattices And Microstructures 28, 377 (2000).

- [30] H. J. Osten, J. P. Liu, E. Bugiel, H. J. Mussig, and P. Zaumseil, Mater. Sci. Engineering B 87, 297 (2001).

- [31] H. J. Osten, J. P. Liu, and H. J. Mussig, Appl. Phys. Lett. 80, 297 (2002).

- [32] S. Guha, N. A. Bojarczuk, and V. Narayanan, Appl. Phys. Lett. 80, 766 (2002).

- [33] X. C. Zhou, S. Jiang, and W. P. Kirk, J. Appl. Phys. 82, 2251 (1997).

- [34] S. Jiang, P. Barrios, R. T. Bate, and W. P. Kirk, Nanotechnology 10, 187 (1999).

- [35] H. Xie, J. Piao, J. Katz, and W. I. Wang, J. Appl. Phys. 70, 3152 (1991).

- [36] T. C. Hasenberg, D. H. Chow, A. R. Kost, R. H. Miles, and L. West, Electron. Lett. 31, 275 (1995).

- [37] K. Segawa, H. Miki, M. Otsubo, K. Shirahata, and K. Fujibayashi, Jpn. J. Appl. Phys. 16, 103 (1977).

- [38] E. R. Brown, J. R. Soderstrom, C. D. Parker, L. J. Mahoney, K. M. Molvar, and T. C. Mcgill, Appl. Phys. Lett. 58, 2291 (1991).

- [39] T. H. Chiu and W. T. Tsang, J. Appl. Phys. 57, 4572 (1985).

- [40] E. T. Yu, J. O. Mccaldin, and T. C. Mcgill, Solid State Physics: Advances In Research And Applications, Vol 46 46, 1 (1992).

- [41] Semiconductors Basic Data, edited by O. Madelung (Springer, Berlin, Germany, 1994).

- [42] X. C. Cheng, Ph.D. thesis, California Institute of Technology, 1999.

- [43] G. E. Stillman and C. M. Wolfe, in *Semiconductors and Semimetals*, edited by R. K. Willardson and A. C. Beers (Academic Press, New York, New York, 1977), Vol. 12, pp. 291–392.

- [44] H. Dautet, P. Deschamps, B. Dion, A. D. Macgregor, D. Macsween, R. J. Mcintyre, C. Trottier, and P. P. Webb, Appl. Opt. 32, 3894 (1993).

- [45] W. J. Kindt, N. H. Shahrjerdy, and H. W. vanZeijl, Sensors And Actuators A 60, 98 (1997).

- [46] W. J. Kindt and H. W. van Zeijl, IEEE Trans. Nucl. Sci. 45, 715 (1998).

- [47] R. J. Mcintyre, IEEE Trans. Electron Devices Ed19, 703 (1972).

- [48] R. J. Mcintyre, IEEE Trans. Electron Devices Ed13, 164 (1966).

- [49] O. Hildebrand, W. Kuebart, J. Lutz, and M. Pilkuhn, IEEE Trans. Electron Devices 27, 2188 (1980).

- [50] O. Hildebrand, W. Kuebart, K. W. Benz, and M. H. Pilkuhn, IEEE J. Quantum Electron. 17, 284 (1981).

- [51] K. F. Brennan and J. Haralson, Superlattices And Microstructures 28, 77 (2000).

# Part I

# $CeO_2/Silicon$ Heterostructures

## Chapter 2 $CeO_2$ Growth

#### 2.1 Overview

In this chapter, aspects of the epitaxial growth of  $CeO_2$  on silicon are discussed. First, a brief comparison of the various growth techniques that have been shown to be successful in producing single-crystal layers of  $CeO_2$  on silicon is given. Then a summary of the attempts to grow high quality  $CeO_2$  layers in our research group is presented. Finally, an assessment of the optimum procedures for growing high-quality, defect-free thin films of  $CeO_2$  on silicon with the best possible interface characteristics is given.

#### 2.2 Background of CeO<sub>2</sub> Growth on Silicon

The original motivation for growing CeO<sub>2</sub> on silicon was to integrate the growth of high temperature superconducting materials with silicon. In particular, YBa<sub>2</sub>Cu<sub>3</sub>O<sub>7-x</sub> is well lattice-matched to CeO<sub>2</sub>. Most of the early work was focused in this direction. It was shown that high-quality, insulating CeO<sub>2</sub> could be grown on Si (111) wafers [1]. Since then, most of the work has focused on improving the quality of this growth. Considerable strides have been made in this area including room temperature growth of CeO<sub>2</sub> on Si (111) [2] and growth on Si (100) substrates [3].

Some of the methods most commonly used for deposition of  $\text{CeO}_2$  on silicon include e-beam evaporation [1], pulsed laser deposition (PLD) [4], sputtering [5] and dual ion beam deposition [6]. In the case of both e-beam deposition and sputtering, high substrate temperatures during growth or high temperature post-growth annealing are necessary in order to create highly crystalline layers on silicon. In the case of PLD, however, it has been shown that single-crystalline material can be grown even as cold as room temperature [2]. The role of temperature on the nature of the CeO<sub>2</sub>/silicon interface is discussed in great detail in Chapter 3. It is shown that a low-temperature growth method is preferred.

While growth of CeO<sub>2</sub> is theoretically possible on any silicon surface, it has been found that there are issues that complicate growth on all but the (111) surface. It has been shown that it is the oxygen atoms in CeO<sub>2</sub> interacting with dangling bonds on silicon atoms that tend to dictate the growth direction [7]. It turns out that even though CeO<sub>2</sub> forms a cubic crystal structure as does silicon, single-crystal growth is only intrinsically possible on (111) substrates because of this effect. On (001) substrates, two different orientations of  $\{110\}$  CeO<sub>2</sub> are energetically equivalent and favorable to any  $\{001\}$  orientation. Thus considerably more effort is required to grow single-crystal CeO<sub>2</sub> on Si (001) substrates. Nevertheless, Nagata et al. [3] showed that it is possible to achieve single-crystalline growth of CeO<sub>2</sub> on Si (001) substrates miscut slightly towards (110). However, the rest of the discussion in this chapter is focused on growth on Si (111).

#### 2.3 Silicon Preparation

All of the growths used for this section of the thesis were done on 3" Si (111) wafers with various types of doping. The wafers first were degreased in acetone, isopropyl alcohol, and deionized water. The wafers then were etched with buffered oxide etchant ( $NH_4F_2$  and HF in water) until the surface was completely hydrophobic, indicating that the native oxide was removed. This process left the surface hydrogen terminated after which the wafers were introduced quickly into vacuum to prevent reoxidation of the surface.

In order to create a repeatable starting surface for  $\text{CeO}_2$  growth, a thin buffer layer of epitaxial silicon was grown. This was accomplished by first heating the substrates to 800°C in vacuum to desorb the hydrogen and residual oxygen contamination. Then silicon from an e-beam evaporation source was slowly deposited on the wafer until a strong (7×7) reconstruction could be observed by reflection high-energy electron diffraction (RHEED). The temperature then was lowered to about 600°C while the rate of silicon deposition was slowly increased. A total of between 100Å and 500Å was grown and always resulted in a strong (7×7) surface reconstruction that was stable down to room temperature. This process created a very reproducible starting surface for CeO<sub>2</sub> growth.

#### 2.4 E-Beam Deposition

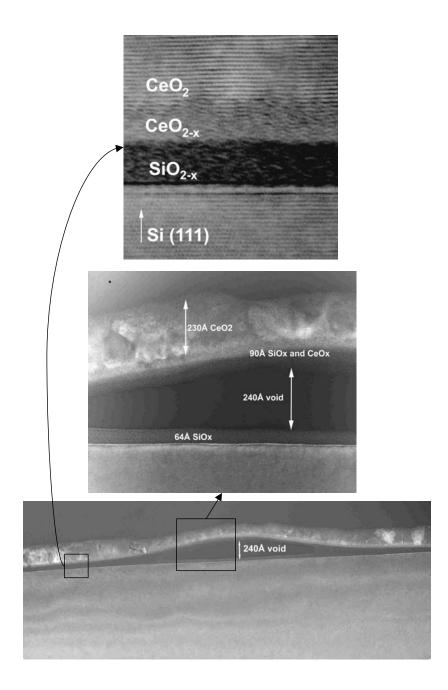

The existing silicon molecular beam epitaxy (MBE) machine in our laboratory contains dual e-beam sources so very little effort was required to modify the chamber for CeO<sub>2</sub> deposition. By evaporating cerium oxide from a CeO<sub>2</sub> target and bleeding in molecular oxygen through a variable fine-leak valve, stoichiometric thin films of polycrystalline CeO<sub>2</sub> (as determined by *in situ* RHEED) routinely could be grown on Si (111) substrates. However, temperatures in excess of 700°C were required to obtain single-crystal films. At these elevated temperatures the growth morphology was extremely poor and relatively thick layers of both SiO<sub>2-x</sub> and CeO<sub>x</sub> were formed between the silicon and the crystalline CeO<sub>2</sub> as shown in Fig. 2.1. It is clear from these images that under the growth conditions in our system, device-quality singlecrystalline CeO<sub>2</sub> thin films could not be grown on silicon via e-beam evaporation. Nevertheless, the lower temperature polycrystalline growths were useful for examining interface reactions (see Chapter 3).

#### 2.5 Pulsed Laser Deposition

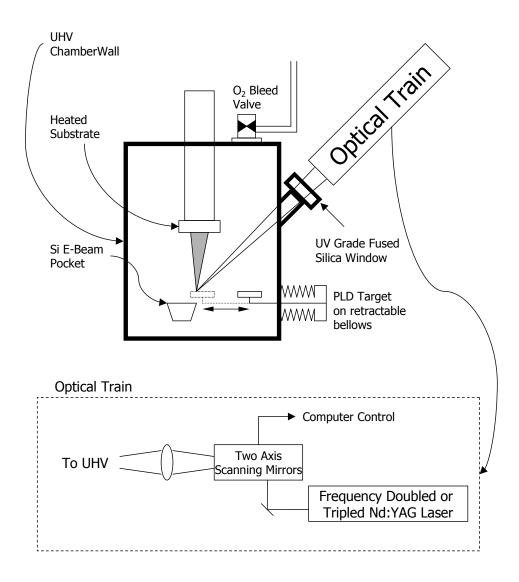

The failure to grow consistent high quality crystalline  $CeO_2$  thin films via e-beam MBE led to an investigation of pulsed laser deposition of  $CeO_2$ . Figure 2.2 shows a schematic of the setup for using PLD to grow  $CeO_2$  on silicon.

Pulsed laser deposition works by impinging high-intensity laser light on a material held in vacuum, which causes the material to ablate off and then redeposit elsewhere in the vacuum chamber. There are several mechanisms that cause the ablation which are outlined in great detail by Chrisey and Hubler [8]. The main advantage of PLD

Figure 2.1: Transmission Electron Microscopy (TEM) images of  $CeO_2$  grown on silicon via e-beam deposition. The detailed sections show the various layers at the interface including what appear to be voids.

over traditional thermal evaporation is the high energy of the expelled particles. Thermally evaporated particles will have energies only on the order of  $k_B T$ , or a few tenths of an eV, whereas laser ablated species can have energies as high as 100 eV [9], partially due to the interaction of the laser with the plume. For our purposes, the advantage of this extra energy is that the substrate will not need to be heated as much to obtain the amount of surface diffusion necessary for high quality epitaxial growth. Another advantage of PLD is that the growth can proceed just as easily in any ambient, so the introduction of molecular or atomic oxygen will not hamper the growth process. Almost all other ultra-high vacuum (UHV) deposition techniques involve filaments which easily can be damaged by operating in an excess of oxygen.

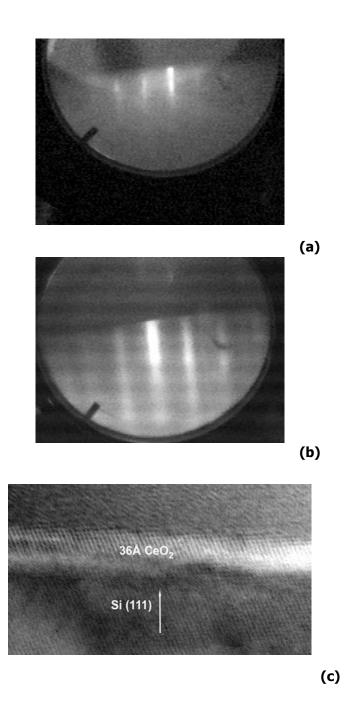

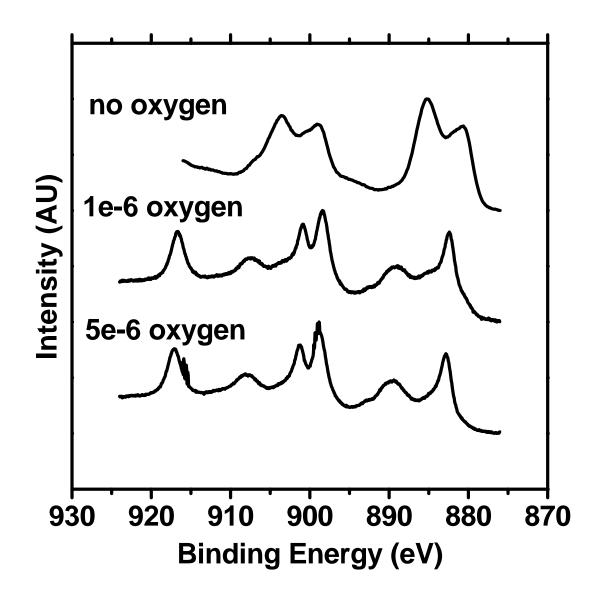

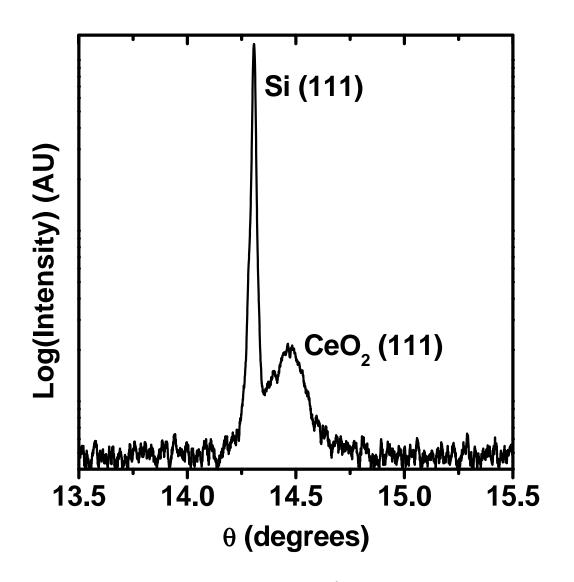

In the first experiments, the second harmonic of a Nd:YAG laser (532 nm light) was used to ablate cerium oxide from a stoichiometric  $CeO_2$  target. As can be seen in Fig. 2.3 (a), this produced a streaky RHEED pattern when ablated onto Si (111). The spacing of the lines was commensurate with the spacing of the underlying silicon lines and the pattern repeated itself every 60 degrees of substrate rotation as required for the 6-fold symmetry of a  $\{111\}$  plane. Figure 2.3(c) shows a transmission electron microscopy (TEM) image of a  $CeO_2$ /silicon interface grown as described without any extra oxygen. Comparison with Fig. 2.1 shows that this technique is a considerable improvement over e-beam MBE as far as the formation of interfacial layers are concerned. However, by examining in situ x-ray photoelectron spectroscopy (XPS) spectra of the films ablated in vacuum (see Fig. 2.4) it was discovered that the layers were underoxidized, almost to the point where they were closer to  $Ce_2O_3$  than  $CeO_2$ . While  $Ce_2O_3$  has hexagonal symmetry instead of cubic like  $CeO_2$  and silicon, a rough lattice match between  $Ce_2O_3$  and silicon can be found on the hexagonal symmetry Si (111) face with about a 1% mismatch. There is also evidence that  $CeO_2$ will remain in its cubic state even when a significant amount of oxygen vacancies are created [10]. Either of these scenarios would explain the fact that single-crystalline growth is possible for underoxidized cerium oxide species on silicon.

By bleeding in oxygen through a variable leak value, the oxidation state easily could be brought back to that of  $CeO_2$ . Figure 2.4 shows that full  $CeO_2$  stoichiometry

Figure 2.2: Schematic of the setup used for PLD growth of  $CeO_2$  on silicon.

Figure 2.3: Figure (a) shows the RHEED pattern of PLD-grown CeO<sub>2</sub> on silicon grown in vacuum. The pattern repeats itself every 60 degrees of substrate rotation indicative of 6-fold symmetry. Figure (b) shows the RHEED pattern of PLD-grown CeO<sub>2</sub> on silicon grown in  $5 \times 10^{-6}$  torr of O<sub>2</sub>. The lines are much broader indicating that some charging is occuring and the lines do not change with substrate rotation. Figure (c) shows a TEM image of a thin film grown by PLD in vacuum.