# Exploiting Parallel Memory Hierarchies for Ray Casting Volumes

Thesis by

Michael E. Palmer

In Partial Fulfillment of the Requirements

for the Degree of

Doctor of Philosophy

California Institute of Technology Pasadena, California

1997

(Submitted April 4, 1997)

© 1997 Michael E. Palmer All Rights Reserved

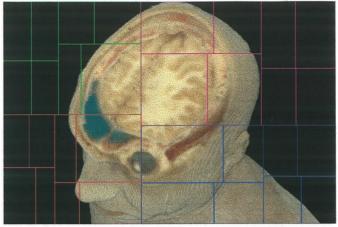

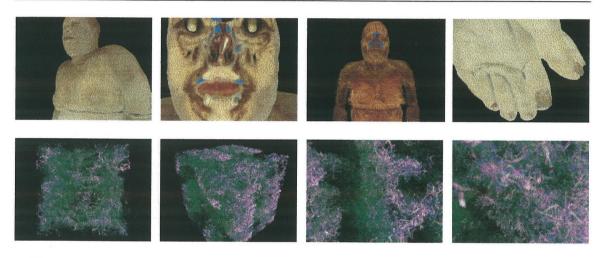

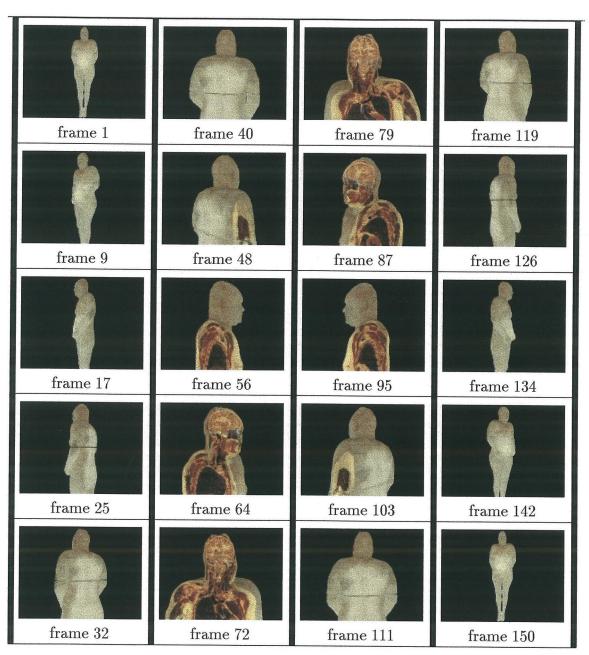

The Visible Male dataset (357 MB). Squares in this image partition correspond to individual processors. Colors correspond to separate nodes of a Power Challenge Array.

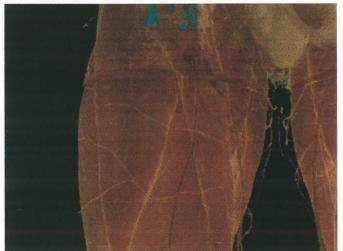

Manipulation of the mapping between voxel values and opacity reveals the internal musculature and vasculature of the leg of the Visible Male.

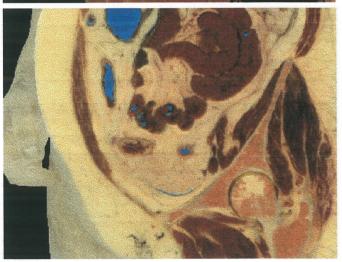

A view of the hip joint of the Visible Female dataset. In this work, we render the Visible Female at full spatial resolution: 1610x894x5192voxels, for a total of 7.1 GB, the largest volume dataset ever rendered.

# Acknowledgements

This thesis would not have been possible without the help of many people. First of all, I would like to thank my family and my fiancée, Jessica Liu, for their unconditional love and support.

I would like to thank my advisor, Stephen Taylor, for all his advice and support over the past six years. Steve is truly a man of integrity and generosity. He combined a respect for letting me follow my own path, with just enough gentle nagging to make sure I would submit my work for publication on a periodic basis.

Thanks to Brian Totty, who contributed a great deal to this thesis. He promoted my work within Silicon Graphics, and collaborated with me on several papers. Brian is also responsible for most of the performance-tuning optimizations to the ray casting kernel. Brian also contributed the tongue-in-cheek name for my experimental ray casting code: RendAsunder

I would like to thank Paul Woodward, Steve Anderson, and the rest of the Laboratory for Computational Science and Engineering (LCSE) at the University of Minnesota. The work I did there in the summer of 1994 was the genesis of *RendAsunder*, my experimental ray casting code. The LCSE also provided the vorticity dataset used in many of my experiments. Steve Anderson has been a good friend to me, gave me much technical advice when I was just beginning on the Silicon Graphics platform, and contributed to early versions of *RendAsunder*. Some of his code is still running in the current version.

I would like to thank Silicon Graphics for the opportunity to participate in Supercomputing '94 and '95. Silicon Graphics also gave me the opportunity to present RendAsunder at two other conferences. Specifically, thanks to John Brown of Silicon Graphics for taking an interest in RendAsunder, promoting its development, and spoiling me with ample machine time on a Power Challenge Array.

Further machine time, in particular for the experiments in chapter 6 and for the

rendering of the largest volume dataset ever, the 7.1 GB Visible Female dataset, was provided by the National Center for Supercomputing Applications (NCSA) at the University of Illinois, Urbana-Champaign. The excellent operations staff at NCSA were very helpful.

Jerrell Watts' SCPlib message passing library allowed me to achieve high performance on the NCSA machines. Jerrell went above and beyond the call of duty several times with late night emergency sessions of performance tuning.

Thanks to John Thornley for discussions of my thesis and journal paper, and for advice on how to handle the whole process of putting together a Ph.D. thesis.

Thanks to H. Ross Harvey for contributing the Power Challenge "cache bashing" benchmark in Chapter 5.

Thanks to Peter Schröder for giving me access to the machines in his lab to finish up many odds and ends.

Thanks to Al Barr and Cindy Ball of the Graphics Group at Caltech for access to, and much help with, video equipment, respectively.

Thanks to Michael Ackerman of the Visible Human Project at the National Library of Medicine for providing the Visible Male and Visible Female datasets.

This research was sponsored by the Defense Advanced Research Projects Agency (DARPA) under contract number DABT63-95-C-0116, and AASERT award number N0014-93-1-0843.

# **Abstract**

Previous work in single-processor ray casting methods for volume rendering has concentrated on algorithmic optimizations to reduce computational work. This approach leaves untapped the performance gains which are possible through efficient exploitation of the memory hierarchy.

Previous work in parallel volume rendering has concentrated on parallel partitioning, with the goals of maximizing load balance and minimizing communication between distributed nodes. This implies a simplified view of the memory hierarchy of a parallel machine, ignoring the relationship between parallel partitioning and memory hierarchy effects at all but the top level.

In this thesis, we progressively develop methods to optimize memory hierarchy performance for ray casting: 1) on a uniprocessor, using algorithmic modifications to isolate cache miss costs, specialized hardware to monitor cache misses on the bus, and a software cache simulator; 2) on the a shared-memory Power Challenge multiprocessor, examining the fundamental dependence of algorithmic design decisions regarding parallel partitioning upon memory hierarchy effects at several levels; and 3) on a distributed array of interconnected Power Challenge multiprocessors, on which we implement a logical global address space for volume blocks, and investigate the tradeoff between replication (caching) and communication of data.

The methods we develop permit us to exploit the coherence found in volume rendering to increase memory locality, and thereby increase memory system performance. This focus on the optimal exploitation of the entire memory hierarchy, from the processor cache, to the interconnection network between distributed nodes, yields faster frame rates for large (357 MB to 1 GB) datasets than have been previously cited in the literature, and allows us to efficiently render a 7.1 GB dataset, the largest ever rendered.

Our results have implications for the parallel solution of other problems which, like

ray casting, require a global gather operation, use an associative operator to combine partial results, and contain coherence. We discuss implications for the design of a parallel architecture suited to solving this class of problems, specifically, that these algorithms are best served by a deep memory hierarchy.

# Contents

| A | Acknowledgements |                                          | iv                                                             |    |  |

|---|------------------|------------------------------------------|----------------------------------------------------------------|----|--|

| A | f Abstract       |                                          |                                                                | vi |  |

| 1 | Introduction     |                                          |                                                                | 1  |  |

|   | 1.1              | Motiv                                    | ration                                                         | 1  |  |

|   | 1.2              | Contr                                    | ibutions of this thesis                                        | 2  |  |

| 2 | Bac              | kgrou                                    | nd Material and Terminology                                    | 5  |  |

|   | 2.1              | Volun                                    | ne rendering                                                   | 5  |  |

|   |                  | 2.1.1                                    | Coordinate systems for computer graphics                       | 5  |  |

|   |                  | 2.1.2                                    | Representing three-dimensional data                            | 7  |  |

|   |                  | 2.1.3                                    | Physical models for volume datasets                            | 9  |  |

|   |                  | 2.1.4                                    | Algorithms for direct volume rendering                         | 12 |  |

|   |                  | 2.1.5                                    | Algorithmic optimizations to ray casting                       | 17 |  |

|   | 2.2              | Parall                                   | el architectures for ray casting                               | 21 |  |

|   | 2.3              | .3 Parallel partitioning for ray casting |                                                                |    |  |

|   |                  | 2.3.1                                    | The two goals of parallel partitioning                         | 22 |  |

|   |                  | 2.3.2                                    | Algorithms for parallel partitioning and load balance          | 22 |  |

|   | 2.4              | Memo                                     | ory hierarchies and exploiting locality of memory access       | 25 |  |

|   |                  | 2.4.1                                    | Uniprocessor cache architecture                                | 25 |  |

|   |                  | 2.4.2                                    | Shared memory                                                  | 27 |  |

|   |                  | 2.4.3                                    | Distributed memory                                             | 28 |  |

|   |                  | 2.4.4                                    | A hybrid architecture: the Power Challenge Array               | 29 |  |

|   | 2.5              | The r                                    | elationship between parallel partitioning and memory hierarchy |    |  |

|   |                  | perfor                                   | mance                                                          | 29 |  |

| 3 | Exp | erimental Goals, Methodology, and Tools                             | 32   |

|---|-----|---------------------------------------------------------------------|------|

|   | 3.1 | Experimental goals                                                  | 32   |

|   | 3.2 | Experimental methodology                                            | 33   |

|   | 3.3 | Hardware platform: the Silicon Graphics Power Challenge Array       | 34   |

|   | 3.4 | Experimental software platform: RendAsunder                         | 35   |

|   |     | 3.4.1 General features of RendAsunder                               | 35   |

|   |     | 3.4.2 RendAsunder as an experimental tool                           | 36   |

|   |     | 3.4.3 The high performance of RendAsunder                           | 37   |

|   |     | 3.4.4 RendAsunder as a demonstration vehicle for interactive volume |      |

|   |     | rendering                                                           | 38   |

|   |     | 3.4.5 Summary of features of RendAsunder                            | . 39 |

| 4 | One | Processor                                                           | 42   |

|   | 4.1 | Ray casting cost analysis                                           | 42   |

|   | 4.2 | Datasets                                                            | 44   |

|   | 4.3 | The axisorbit test suite                                            | 45   |

|   | 4.4 | Experimental procedure                                              | 47   |

|   | 4.5 | View direction dependence of time per ray-voxel intersection        | 47   |

|   | 4.6 | Isolation of time due to cache effects                              | 51   |

|   | 4.7 | Hardware bus-snooping board                                         | 55   |

|   | 4.8 | Cache simulator                                                     | 57   |

|   | 4.9 | Conclusions                                                         | 63   |

| 5 | One | Shared-Memory Node, Multiple Processors                             | 65   |

|   | 5.1 | Load balancing for ray casting on a shared-memory machine           | 65   |

|   |     | 5.1.1 Image partition                                               | 66   |

|   |     | 5.1.2 Object partition                                              | 66   |

|   | 5.2 | The shared bus of the Power Challenge                               | 67   |

|   | 5.3 | Experimental procedure                                              | 68   |

|   | 5.4 | Parallel speedup                                                    | 69   |

|   |     |                                                                     |      |

69

|   | 5.6             | Comp               | parison of partitioning methods                            | 74  |

|---|-----------------|--------------------|------------------------------------------------------------|-----|

|   | 5.7             | Maxir              | num frame rates                                            | 75  |

|   | 5.8             | Concl              | usions                                                     | 78  |

| 6 | Mu              | ltiple [           | Distributed Shared-Memory Nodes                            | 80  |

|   | 6.1             | Volun              | ne rendering requires a global gather operation            | 81  |

|   |                 | 6.1.1              | Transferring 2D subimages versus 3D subvolumes             | 82  |

|   |                 | 6.1.2              | The tradeoff between replication of data and communication |     |

|   |                 |                    | expense                                                    | 84  |

|   | 6.2             | A soft             | tware block caching system for the Power Challenge Array   | 86  |

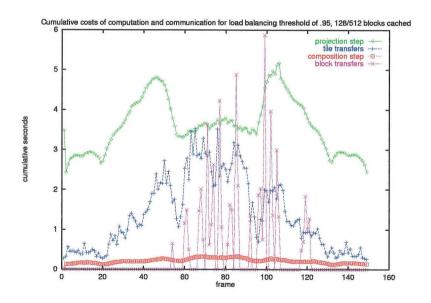

|   | 6.3             | Datas              | ets and the typicalview test suite                         | 89  |

|   | 6.4             | Exper              | rimental results                                           | 92  |

|   |                 | 6.4.1              | Experimental procedures                                    | 92  |

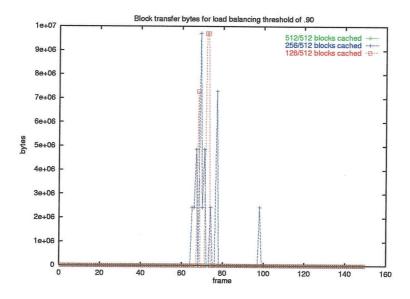

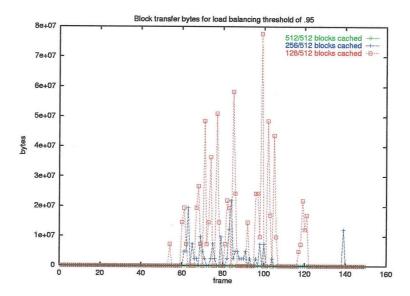

|   |                 | 6.4.2              | Communication due to block transfers                       | 94  |

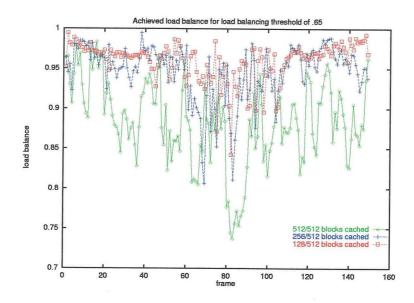

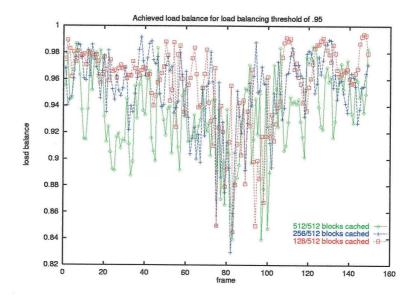

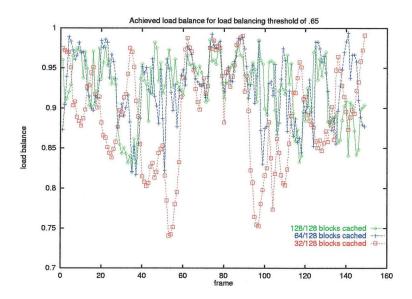

|   |                 | 6.4.3              | Load balance                                               | 98  |

|   |                 | 6.4.4              | Communication due to tile transfers                        | 104 |

|   |                 | 6.4.5              | Frame times                                                | 109 |

|   |                 | 6.4.6              | Parallel speedup                                           | 111 |

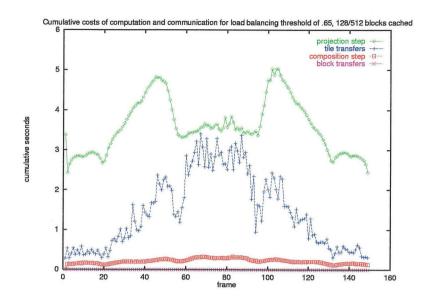

|   |                 | 6.4.7              | Relative costs of computation and communication            | 112 |

|   |                 | 6.4.8              | Performance on a very large dataset                        | 113 |

|   | 6.5             | Concl              | usions                                                     | 113 |

| 7 | $\mathbb{R}$ el | ated ${\mathbb V}$ | Vork                                                       | 117 |

|   | 7.1             | Closel             | y related papers                                           | 117 |

|   |                 | 7.1.1              | Lower levels of the memory hierarchy                       | 117 |

|   |                 | 7.1.2              | Higher levels of the memory hierarchy                      | 118 |

|   | 7.2             | Perfor             | rmance comparison                                          | 119 |

| 8 | Con             | clusio             | ns                                                         | 121 |

|   | 8.1             | Result             | ts and implications for ray casting volume rendering       | 121 |

|   | 8.2             | Implie             | cations for other parallel algorithms                      | 124 |

|              | 8.3    | Implications for parallel architecture design      | 125 |

|--------------|--------|----------------------------------------------------|-----|

| $\mathbf{A}$ | A fi   | ne-grained MIMD implementation with no replication | 127 |

| B            | ibliog | graphy                                             | 131 |

# List of Figures

| 1.1        | Example ray casting output, male dataset                                                      | 1              |

|------------|-----------------------------------------------------------------------------------------------|----------------|

| 2.1        | Coordinate systems in Volume Rendering                                                        | 6              |

| 2.2        | Cubes in orthogonal projection and perspective projection                                     | 7              |

| 2.3        | Transmission, reflection, and refraction in ray tracing                                       | 11             |

| 2.4        | Transmission and emission in ray casting                                                      | 12             |

| 2.5        | Rendering by ray casting or "image order" rendering                                           | 13             |

| 2.6        | Rendering by projection or "object order" rendering                                           | 16             |

| 2.7        | Dynamic resolution refinement for higher frame rate                                           | 20             |

| 2.8        | A typical memory hierarchy for a single-processor architecture                                | 26             |

| 2.9        | A typical memory hierarchy for a shared-memory architecture                                   | 27             |

| 2.10       | A typical memory hierarchy for a distributed-memory architecture                              | 28             |

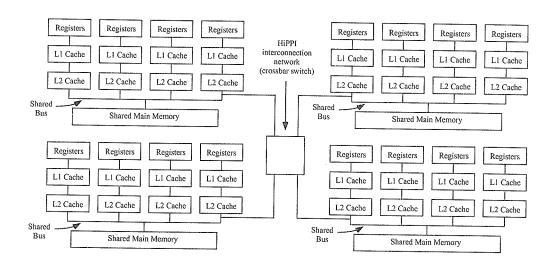

| 2.11       | A hybrid distributed/shared memory hierarchy, the Power Challenge                             |                |

|            | Array                                                                                         | 30             |

| 3.1        | Sample performance points for RendAsunder                                                     | 37             |

| 3.2        | Hardware configuration at Supercomputing '95                                                  | 38             |

| 4.1        | A typical memory hierarchy for a single-processor architecture                                | 42             |

| 4.2        | Sizes of experimental datasets                                                                | 45             |

| 4.3        |                                                                                               |                |

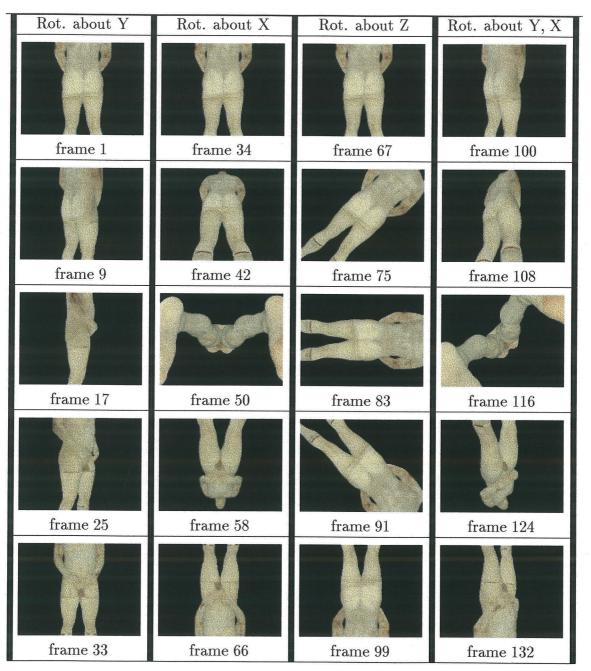

| 4.4        | Example images of the female (top) and vorticity (bottom) datasets .                          | 45             |

| 4.4        | Example images of the female (top) and vorticity (bottom) datasets.  The axisorbit test suite | 45<br>46       |

| 4.4        |                                                                                               |                |

|            | The axisorbit test suite                                                                      | 46             |

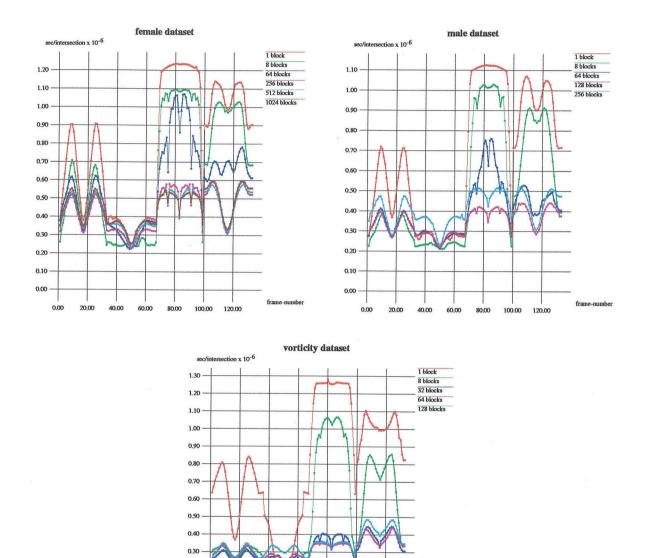

| 4.5        | The axisorbit test suite                                                                      | 46<br>48<br>52 |

| 4.5<br>4.6 | The axisorbit test suite                                                                      | 46<br>48<br>52 |

| 4.9                                                           | Left: bus-snoop L2 misses/intersection. Right: "mem-only" and "bus-        |                                                                                        |

|---------------------------------------------------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

|                                                               | snoop L2" time/intersection                                                | 56                                                                                     |

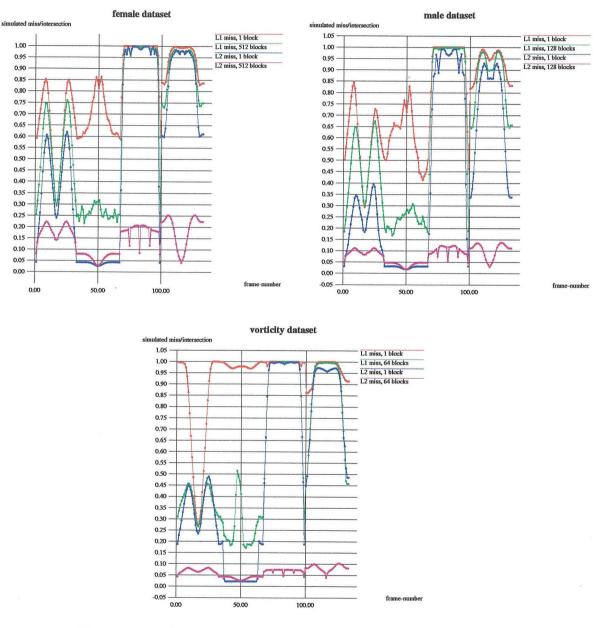

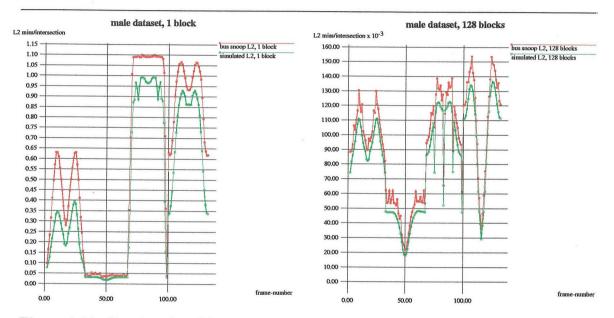

| 4.10                                                          | Simulation of L1 and L2 cache misses/intersection                          | 58                                                                                     |

|                                                               | Simulated and bus-snooping board L2 misses/intersection, male dataset      | 60                                                                                     |

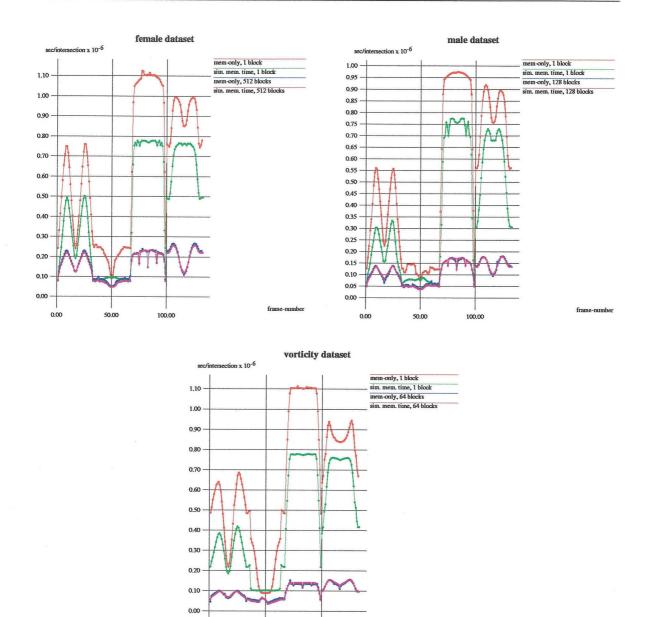

|                                                               | Simulated and "mem-only" memory hierarchy time/intersection                | 62                                                                                     |

| 5.1                                                           | A typical memory hierarchy for a shared-memory architecture                | 65                                                                                     |

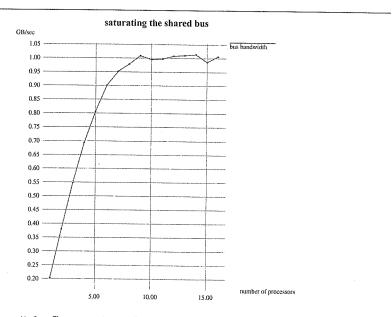

| 5.2                                                           | Saturating the shared bus                                                  | 67                                                                                     |

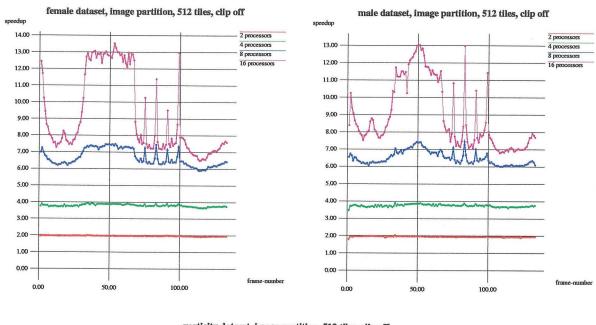

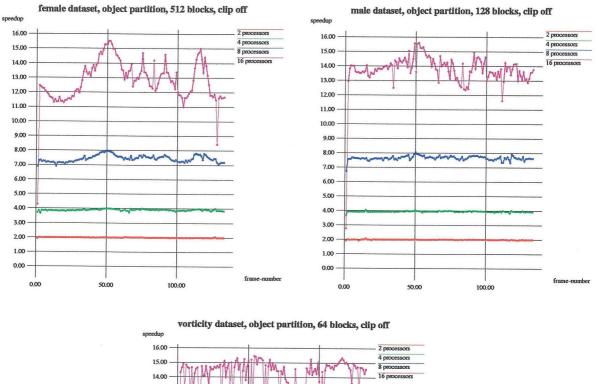

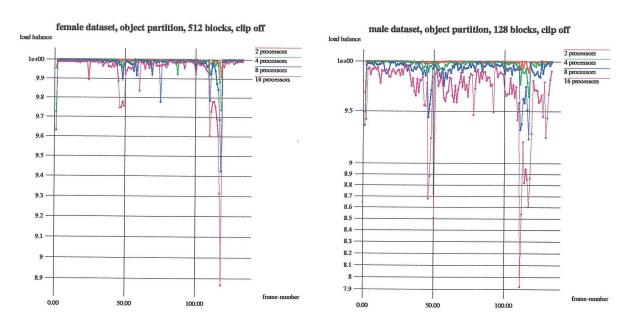

| 5.3                                                           | Parallel speedup, image partition, clipping off                            | 70                                                                                     |

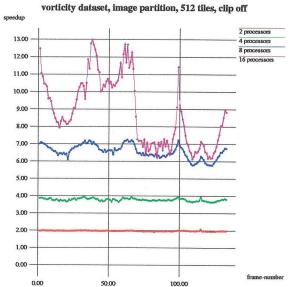

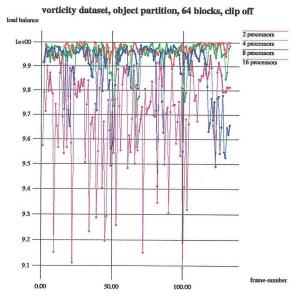

| 5.4                                                           | Parallel speedup, object partition, clipping off                           | 71                                                                                     |

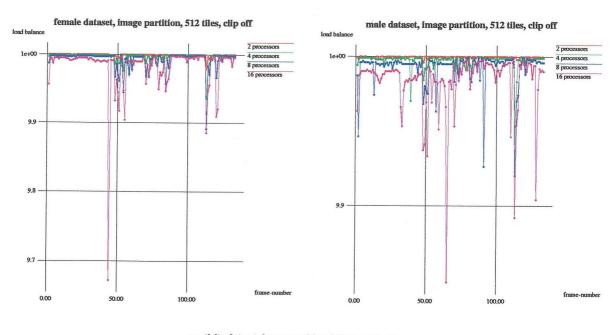

| 5.5                                                           | Load balance, image partition, clipping off                                | 72                                                                                     |

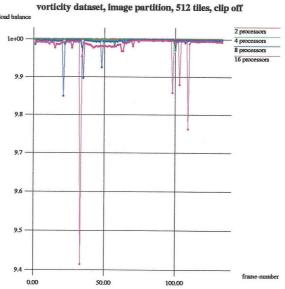

| 5.6                                                           | Load balance, object partition, clipping off                               | 73                                                                                     |

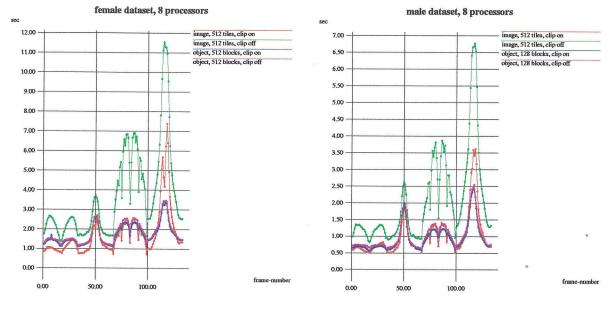

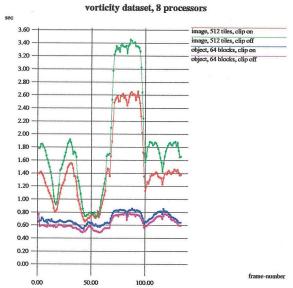

| 5.7                                                           | Time per frame, eight processors                                           | 76                                                                                     |

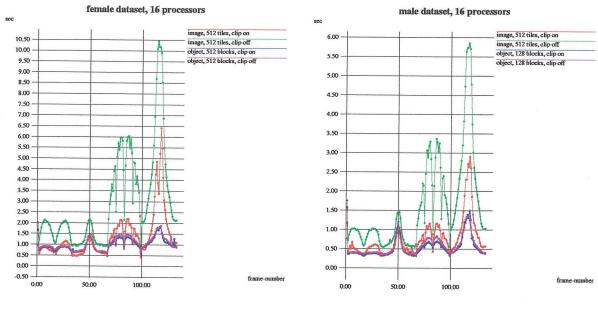

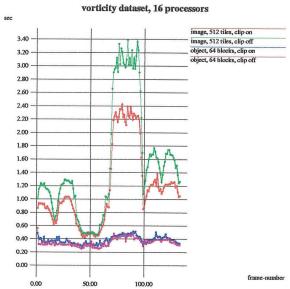

| 5.8                                                           | Time per frame, sixteen processors                                         | 77                                                                                     |

| 6.1                                                           | A hybrid distributed/shared memory hierarchy, the Power Challenge          |                                                                                        |

|                                                               |                                                                            |                                                                                        |

|                                                               | Array                                                                      | 80                                                                                     |

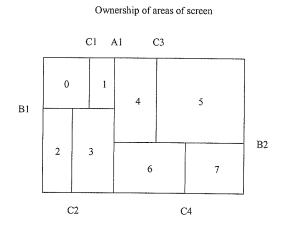

| 6.2                                                           | Array                                                                      | 80<br>85                                                                               |

| 6.2<br>6.3                                                    |                                                                            |                                                                                        |

|                                                               | An image partition based on binary subdivision                             | 85                                                                                     |

| 6.3                                                           | An image partition based on binary subdivision                             | 85<br>90                                                                               |

| 6.3<br>6.4                                                    | An image partition based on binary subdivision                             | 85<br>90<br>91                                                                         |

| 6.3<br>6.4<br>6.5                                             | An image partition based on binary subdivision                             | 85<br>90<br>91                                                                         |

| 6.3<br>6.4<br>6.5                                             | An image partition based on binary subdivision                             | 85<br>90<br>91<br>94                                                                   |

| 6.3<br>6.4<br>6.5<br>6.6                                      | An image partition based on binary subdivision                             | <ul><li>85</li><li>90</li><li>91</li><li>94</li><li>96</li></ul>                       |

| 6.3<br>6.4<br>6.5<br>6.6                                      | An image partition based on binary subdivision                             | <ul><li>85</li><li>90</li><li>91</li><li>94</li><li>96</li></ul>                       |

| 6.3<br>6.4<br>6.5<br>6.6                                      | An image partition based on binary subdivision                             | 85<br>90<br>91<br>94<br>96<br>97                                                       |

| 6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8                        | An image partition based on binary subdivision                             | <ul><li>85</li><li>90</li><li>91</li><li>94</li><li>96</li><li>97</li><li>98</li></ul> |

| 6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>6.9<br>6.10         | An image partition based on binary subdivision                             | 85<br>90<br>91<br>94<br>96<br>97                                                       |

| 6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>6.9<br>6.10<br>6.11 | An image partition based on binary subdivision  The typicalview test suite | 85<br>90<br>91<br>94<br>96<br>97<br>98<br>99                                           |

| 6.14 | Average tile transfer bytes per frame on four nodes of eight processors | 105 |

|------|-------------------------------------------------------------------------|-----|

| 6.15 | Tile transfer bytes per frame on four nodes of eight processors, female |     |

|      | dataset                                                                 | 106 |

| 6.16 | Average tile transfer bytes per frame on two nodes of eight processors  | 107 |

| 6.17 | Average tile transfer bytes per frame on eight virtual nodes of four    |     |

|      | processors                                                              | 107 |

| 6.18 | Assignments of blocks to nodes for projection, for replication factors  |     |

|      | of one (left) and four (right) $\hdots$                                 | 108 |

| 6.19 | Average frame times on four nodes of eight processors (sec)             | 109 |

| 6.20 | Average frame times on two nodes of eight processors (sec)              | 110 |

| 6.21 | Average frame times on eight virtual nodes of four processors (sec)     | 111 |

| 6.22 | Parallel speedup over single node (percentage of number of nodes)       | 112 |

| 6.23 | Relative costs of computation and communication on four nodes, fe-      |     |

|      | male dataset (sec)                                                      | 114 |

| 8.1  | The impact of ray divergence                                            | 123 |

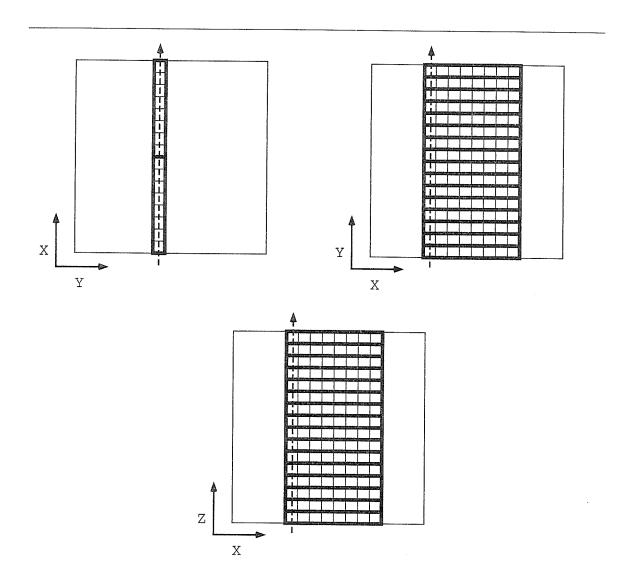

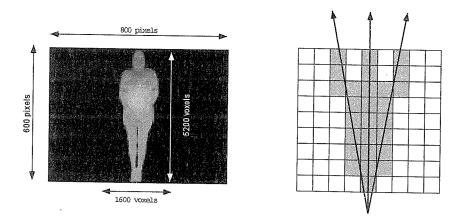

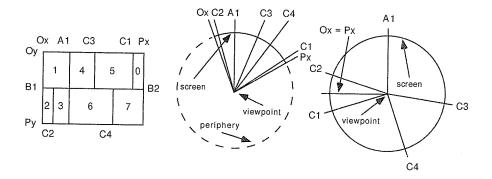

| A.1  | Three views of a set of partitioning lines                              | 128 |

| A 2  | Three views of the lines after a head rotation                          | 199 |

# Chapter 1 Introduction

# 1.1 Motivation

As the data sets generated by computational simulations and medical imaging grow larger, scientists are swamped by their large (multi-gigabyte) three-dimensional datasets. The most intuitive way for a scientist to understand these vast volumes of data is to explore them interactively through high-performance volume rendering. Interactivity requires certain minimum frame rates (e.g., 10 frames per second). This level of performance for rendering very large datasets is not possible on contemporary single-processor machines. Parallelism offers the promise of rendering large datasets at interactive frame rates. However, the leap to parallelism introduces a host of new algorithmic design considerations. One of the most important is the consideration of the interaction between parallel partitioning and efficient exploitation of the memory hierarchy at all levels.

Figure 1.1: Example ray casting output, male dataset

Figure 1.1 shows example images generated by the ray casting volume rendering implementations described in this thesis using the Silicon Graphics Power Challenge.

Manipulation of the mapping between voxel value and opacity, and use of a front clipping plane, yield views of the interior muscle and bone structure of this human body dataset [Ackerman95].

# 1.2 Contributions of this thesis

Early research in uniprocessor ray casting volume rendering focused on algorithmic optimizations to improve performance; for example, by reducing the total number of rays that must be cast, or the number of intersections between rays and data voxels that must be calculated. However, previous work has left largely untapped the performance benefits to be gained through optimal exploitation of the memory hierarchy. The primary means to achieve this on a uniprocessor is by increasing locality of memory access through the manipulation of the order of memory accesses.

Past research in parallel volume rendering has concentrated on the partitioning problem, with the specific goals of maximizing load balance and minimizing communication between distributed processors. Past work has not, in general, considered the more complex problem of exploiting the entire memory hierarchy of the parallel machine. The focus on communication between distributed processors, to the exclusion of other levels of the memory hierarchy, implies an oversimplified model of the operation of the entire machine. A parallel computer is a machine dedicated not only to performing operations on data, but also to moving the data efficiently from the memory locations where it is stored, through many levels of a deep memory hierarchy, to the processor registers where it can be operated on. Hardware from the level of the processor cache, to the interconnection network between distributed nodes, plays a role in this task. The performance of each level of this system is extremely sensitive to algorithmic characteristics such as locality of memory access. Consideration of the efficient exploitation of all levels of a deep memory hierarchy must be reflected in algorithmic design, and fundamentally affects design decisions regarding parallel partitioning.

Although poor load balance is commonly the focus of parallel rendering work, we

will show that poor performance at any level of the memory hierarchy can also thwart parallel speedup. Optimal performance at all levels of the memory hierarchy is even harder to achieve than optimal load balance, in part because memory hierarchy effects can be complex and unintuitive.

This thesis focuses on the volume rendering of volumetric data defined on regular cartesian grids by ray casting. Regular grids, because of their simplicity, are the obvious place to begin the characterization of memory hierarchy effects for ray casting. They are used commonly in a range of applications, from magnetic resonance image (MRI) to some computational fluid dynamics (CFD) work.

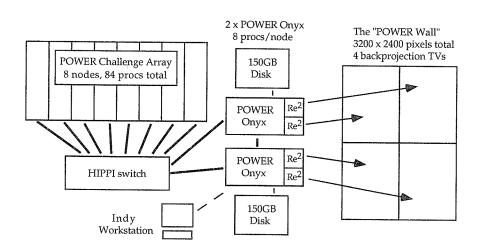

Our primary experimental hardware platform is the Silicon Graphics Power Challenge Array, an example of a hybrid distributed/shared memory architecture, consisting of a distributed array of up to eight Power Challenge shared-memory multiprocessors, each containing up to eighteen MIPS R8000 processors.

In this thesis, we progressively develop techniques to maximally exploit the memory hierarchy on a uniprocessor; within a shared-memory Power Challenge multiprocessor; and finally on a distributed array of interconnected Power Challenge multiprocessors.

On a single processor, we focus on the optimization of the performance of the level one (L1) and level two (L2) caches of the R8000 microprocessor. Our investigative techniques include 1) algorithmic changes to isolate the costs of cache misses; 2) direct observation of L2 cache misses using a limited-edition hardware bus-snooping board; and 3) simulation of both L1 and L2 cache misses with a software cache simulator, which can be configured to mimic the caching behavior of the L1 and L2 caches of the R8000.

On multiple processors within a single shared-memory Power Challenge node, we investigate the relationship between parallel partitioning and cache performance, studying both image-based and object-based parallel partitions. We evaluate these partitioning options in terms of achievable cache hit rates, load balance, parallel speedup, the tendency to saturate the shared bus as the number of processors increases, and the applicability of common algorithmic optimizations to ray casting.

Across multiple distributed Power Challenge Array nodes, we implement in software a system providing a logical global address space for accessing and caching blocks of volume data. We investigate both image-based, and object-based, parallel partitioning algorithms for distributed machines, evaluating them in terms of volume of data communication, attainable load balance, parallel speedup, and their performance under conditions of limited memory resources for use by the distributed block caching system.

This attention to the performance of each level of the deep memory hierarchy yields higher frame rates for large volume datasets than we have previously seen cited in the literature, both for large datasets (357 MB to 1 GB) on a single shared-memory array node, and for very large datasets (up to 7.1 GB) on multiple array nodes, which have not been previously rendered.

Our findings have implications to other parallel algorithms, which share with ray casting volume rendering the characteristics of: 1) they require a global gather operation (i.e., the entire distributed dataset contributes to a solution that will end up stored on a single node), 2) the operator which combines partial results is associative, and 3) they contain some form of coherence which can be exploited to increase memory locality. These algorithms are not scalable, because the communication they require increases with increasing numbers of nodes. However, the coherence they contain can be exploited on a machine with a sufficiently deep memory hierarchy to obtain good parallel speedup on moderate numbers of nodes.

This, in turn, has implications to the design of parallel architectures. The ideal architecture for solving these problems on moderate numbers of processors is not a distributed architecture with a slow but "scalable" interconnection network. Rather, expansion to moderate numbers of parallel processors should be achieved by creating a deeper memory hierarchy. The top level of the memory hierarchy should be implemented by connecting shared-memory multiprocessors with a high performance network that is scalable only to a low number of connected nodes. (This is unlike the "scalable" but relatively low performance HIPPI crossbar network used in the Power Challenge Array.)

# Chapter 2 Background Material and Terminology

In this chapter, we define a number of terms and concepts relevant to parallel volume rendering. Some of these concepts are developed in more detail in other chapters as they become relevant. More detailed discussion of closely related papers is presented in Chapter 7, Related Work.

# 2.1 Volume rendering

Volume rendering is the process of rendering two-dimensional images, from a particular viewpoint, from discretized three-dimensional scalar fields. The data to be rendered consists of space-filling discretized regions called *voxels*.

# 2.1.1 Coordinate systems for computer graphics

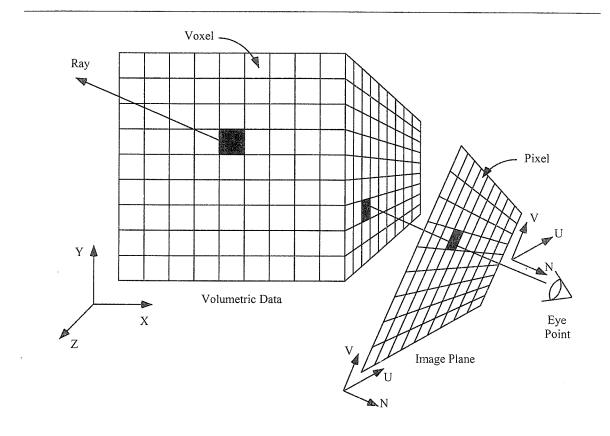

We call the coordinate system of the three-dimensional dataset *object space*. In Figure 2.1, this set of coordinate axes is labeled X, Y, and Z. The coordinate system of the viewer is called *image space*, and is labeled U (to the viewer's right), V (the viewer's "up" direction), and N (opposite to the direction in which the viewer is looking). We call the discrete volume elements making up the dataset *voxels* and the discrete squares making up the image plane *pixels*.

As the viewer peers about the dataset, flying around and through it, the relationship between object space and image space changes. This relationship is specified by a coordinate transformation matrix called the *view matrix*, which maps any point in object space to a point in the viewer's image space.

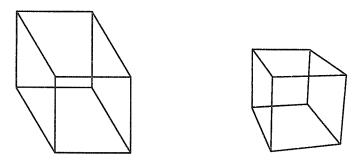

Two methods of projection are commonly used in computer graphics. *Orthogonal* projection assumes that all rays projected from the eye point are parallel, making a

Figure 2.1: Coordinate systems in Volume Rendering

projected cube look like the one on the left of Figure 2.2. The parallel edges of a cube preserve their parallelism in this projection. In our day-to-day experience in viewing the world, we are more familiar with seeing objects in perspective projection. In the perspective projection, rays projected from the eye point diverge from the eye point. This projection makes all parallel edges of objects, such as the cube on the right of Figure 2.2, appear to converge. Since projection of a three-dimensional object onto a two-dimensional surface implies a loss of information, the perspective projection gives important depth cues to a viewer accustomed to perceiving three-dimensional objects in this way. The orthogonal projection allows certain algorithmic optimizations which increase performance, but it has become less popular in contemporary volume rendering because of the unusual appearance it lends to objects.

Figure 2.2: Cubes in orthogonal projection and perspective projection

Rendering using the perspective projection requires, in addition to the view matrix, a value specifying the severity of the perspective transformation. This is specified as the *field of view*, the angle that the full width of the image subtends from the eye point. This specifies the angle of divergence between a ray at one edge of the screen and a ray at the other edge.

# 2.1.2 Representing three-dimensional data

A continuous three-dimensional scalar field must be discretized for storage on a digital computer. A convenient means is *spatial discretization*. We can approximately represent the scalar field with a finite collection of small volume elements, giving each

element a single value corresponding to the average value of the continuous scalar field within that volume element. Alternatively, we could approximate the field by storing its value at a finite set of points in space.

Instead of discretizing in space, we could alternatively take a fourier transform of the scalar field, and represent the resulting frequencies in discrete form. There are countless other possible representations. A band-limited function can be exactly represented by a finite set of discrete samples. If the input function is not band-limited, each type of representation yields characteristic deviations, or errors, compared to the original input.

We primarily consider spatial discretization in this work. A variety of geometries can be used in spatial discretization, including regular cartesian grids, rectilinear and curvilinear grids, unstructured grids (e.g., irregular tetrahedra), hierarchical grids (e.g., octrees), and multiresolution grids (i.e., regular blocks of varying resolution, which may or may not overlap).

Regular grids, for instance grids consisting of identical cubes (or other identical solids, like regular tetrahedra), are the simplest form of grid. The entire grid can be uniquely specified by a small number of parameters. For instance, a regular cubical grid can be specified by the dimensions of the grid and the size of one cubical element. There exist very efficient algorithms to find the path of a ray traversing a regular cubical grid.

Slightly more complicated are rectilinear grids. These grids are formed by stretching one or more of the axes of a regular grid. These grids can be completely specified with the same information necessary to specify a regular grid, plus information about the stretching function along each axis. Curvilinear grids are more complex in that the grid lines may curve; however, each data element still has the same number of neighbors (e.g., six in the case of cubical grid cells).

Many interesting scalar fields contain large regions in which the value of the field does not change greatly, and other regions where rapid change is concentrated. Such scalar fields can be stored relatively compactly by multiresolution methods. For example, octree subdivision consists of a hierarchy of cubes recursively divided into

eight subcubes. In relatively constant regions of the scalar field, a large cube can serve to represent the entire region. If the scalar field is not constant within the region of a cube, then the cube is divided again. Another means to achieve a multiresolution subdivision of space is to define regions or blocks which each contain grids of a different resolution.

In contrast to the small number of parameters that are required to specify a regular grid, irregular grids generally require that each grid point be specified explicitly, since each grid point is placed without adherence to an overall regular structure. Such grids are commonly constructed of irregular tetrahedra. They can become quite complex in that grid cells may not all have the same number of neighbors. These grids could be constructed of elements with varying numbers of sides, although this is uncommon. Tetrahedral grids are often useful in computational fluid dynamics, since the faces of the tetrahedra can be aligned with the faces of solid surfaces impeding the flow of the fluid, reducing the error in the representation of such surfaces. It is relatively expensive to compute the path of a ray through an irregular grid; however, a small total number of properly placed irregular tetrahedra can often yield less approximation error than a much larger number of regular cubes.

In this thesis, we are primarily concerned with volume data represented on regular cartesian grids. These grids are commonplace, ray casting on them is efficient, and their simplicity makes them the obvious first subject of an investigation into the importance of memory hierarchy effects in ray casting volume rendering.

# 2.1.3 Physical models for volume datasets

Given an approximation of a three-dimensional scalar field in a computer's memory, there is not a single best representation of the data which will bestow maximum understanding upon a human observer. In an extreme example, the volume dataset could be dumped onto the screen as a long sequence of 0's and 1's. More usefully, we might extract some statistics from the dataset that summarize it in a table; for instance, in a fluid flow simulation, we might calculate the average velocity, maximum

velocity, and the variance in the velocities of the fluid particles. However, in order to promote deeper understanding of complex three-dimensional data by scientists, we may exploit the human visual system by making an analogy to the physical world. We can model our three-dimensional dataset as a three-dimensional object with certain visual characteristics. We will choose a location in three space for the viewpoint, choose a view direction, and generate two-dimensional images of this object that properly obey the rules of perspective.

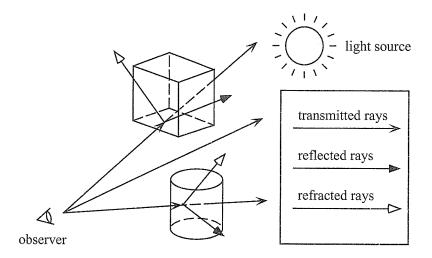

Much research in ray tracing [Kajiya84] has attempted to realistically model the physics of the transmission, reflection, and refraction of light, as shown in Figure 2.3. Ray tracing can reproduce an impressive array of visual and optical effects, including motion blur, depth of field, penumbras, translucency, and glossy reflections [Cook84]. However, the goal of scientific visualization is to allow scientists to understand their datasets, not to accurately model the physics of the transport of light. Complex reflective effects, for example, could cause features to appear to be where they are not present in the data. Therefore, most scientific volume visualization follows a simpler and more practically oriented physical model. Volume rendering for this purpose generally includes features that aid in the visual interpretation of the images as three-dimensional objects, and eschews others in exchange for clarity of interpretation, simplicity of implementation, and higher performance.

There are two common types of physical models for three-dimensional datasets:

1) isosurface extraction [Lorensen87] models, which reduce the volume data to a set of discretized surfaces approximating those at which the scalar field assumes a constant value, and 2) direct volume rendering models [Upson88, Sabella88, Drebin88], which treat the scalar field as a cloud of translucent material of varying opacity and color.

Isosurface extraction models reduce the volume data to a set of polygons defining surfaces at which the discretized scalar field assumes a constant value. These sets of polygons are commonly generated by an algorithm called "marching cubes" [Lorensen87]. The polygons are then typically illuminated by a light source and rendered as opaque or translucent objects, which may or may not cast shadows on each other. Self-shadowing is not generally required, since directional shading (shading

Figure 2.3: Transmission, reflection, and refraction in ray tracing

based on the surface normal of the polygons, and the direction of the light from the light source) provides sufficient visual cues. The human visual system does not effectively identify the "missing" self-shadowing. True self-shadowing is much more expensive computationally than directional-based shading.

The set of polyhedra representing the isosurface typically has much smaller storage requirements than the original dataset, and polygons can be rendered economically and quickly by specialized graphics hardware. The disadvantage of this approach is that the entire dataset is not represented in the resulting images, and that aliasing artifacts are common. For example, one may wish to extract from an MRI dataset the set of polygons lying on the surface of the bones. However, a single signal intensity does not define the bone surface (the signal varies due to bone density and due to artifacts in the MRI data). A common result is that some bones that are not actually connected may appear to be fused together. Since this method is a reduction of the dataset, information is lost, and such errors can occur.

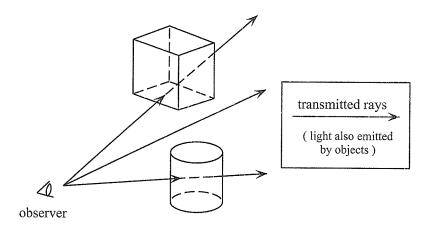

Direct volume rendering algorithms model the data volume as a cloudy material of varying color and opacity. A mapping from the scalar voxel values to a color and opacity is defined. [Blinn82, Kajiya84, Max86] A simplified model of *light emittance* and *light transmission* is commonly used: the cloudy material both emits light and

Figure 2.4: Transmission and emission in ray casting

partially occludes light passing through it [Porter84], as shown in Figure 2.4. Shadows from external light sources are generally omitted: true self-shadowing of the cloudy material is expensive, and no well-defined surface normals exist a priori to be used for inexpensive directional shading. (Surface reflections can be defined, at additional expense, using the gradient of the scalar field [Levoy88].) Scattering and reflection of light are omitted, since these properties can make clear understanding of the resulting images more difficult, and are in addition expensive.

# 2.1.4 Algorithms for direct volume rendering

There are several algorithms which can be used for direct volume rendering, i.e., used to produce results that accord with the physical model of a cloudy material of varying opacity and color. These include ray casting [Sabella88, Nieh92]; projection methods [Westover90, Shirley90, Laur91, Wilhelms91] in which individual volume elements are projected on to the image plane and composited together; and shear-warp methods, which decompose the view matrix into a series of shears and/or warps [Drebin88, Schröder91, Wittenbrink94, Lacroute94] and process slabs of the entire volume at once.

#### Ray casting

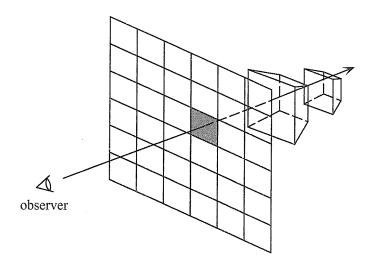

Figure 2.5 illustrates an algorithm known as ray casting. A ray originating at the eye strikes an image pixel on the display screen, and passes through objects in the data volume. The ray accumulates color and opacity depending on the voxels that it intersects. This is reverse of the direction that a light ray in our physical model would travel, but can be made to yield equivalent pixel values.

Figure 2.5: Rendering by ray casting or "image order" rendering

Models developed for the realistic simulation of light transport [Blinn82, Kajiya84, Max86] were discretized [Sabella88], simplified, and combined with the concept of the opacity channel [Porter84], to yield discrete equations for the accumulation of color and opacity by a ray passing through voxels of varying color and opacity.

Each ray has an associated four-vector of red, green, blue, and opacity, which is initialized to the zero vector. A ray intersects an ordered set of voxels  $V_1$  to  $V_n$ ; this set of voxels depends on the manner in which the ray intersects the dataset. As the ray passes through each voxel, it accumulates color and opacity from it, depending on the color and opacity of the voxel, and the length of the intersection between the ray and the voxel. Opacity is accumulated in the following manner:

$$ray_k^{\alpha} = ray_{k-1}^{\alpha} + (1 - ray_{k-1}^{\alpha}) * V_k^{\alpha} * L(V_k)$$

where  $ray_k^{\alpha}$  is the total opacity accumulated for the ray. for voxels 1 through k. The voxels which comprise this path depend on the eye point and the direction of the ray.  $V_k^{\alpha}$  is the opacity of voxel  $V_k$ ; and  $L(V_k)$  is a function of length of the line segment formed by the intersection of the ray with the voxel.

Color is accumulated in a similar way:

$$\begin{split} ray_{k}^{R} &= ray_{k-1}^{R} + (1 - ray_{k-1}^{\alpha}) * V_{k}^{R} * L(V_{k}) \\ ray_{k}^{G} &= ray_{k-1}^{G} + (1 - ray_{k-1}^{\alpha}) * V_{k}^{G} * L(V_{k}) \\ ray_{k}^{B} &= ray_{k-1}^{B} + (1 - ray_{k-1}^{\alpha}) * V_{k}^{B} * L(V_{k}) \end{split}$$

where  $ray_k^R$ ,  $ray_k^G$ , and  $ray_k^B$  are the red, green, and blue color values accumulated for voxels 1 through k; and  $V_k^R$ ,  $V_k^G$ , and  $V_k^B$  are the color values of voxel  $V_k$ .

If we measure opacity on a scale of zero to one, the opacity of the ray asymptotically approaches one (1). As the ray becomes completely opaque, each subsequent voxel makes a smaller contribution to the color and opacity of the ray. After a ray has passed completely through the volume, the effect of a background color may also be accumulated. The final color is assigned to the image pixel associated with the ray.

In vector form, the four equations for *composition* of voxels, above, can be stated as:

$$ray_{k}^{\alpha,R,G,B} = ray_{k-1}^{\alpha,R,G,B} + (1 - ray_{k-1}^{\alpha}) * V_{k}^{\alpha,R,G,B} * L(V_{k})$$

Researchers found that manipulation of the opacity channel could be used to antialias the images, and to delineate complex relationships among surfaces and interior structures. [Upson88, Drebin88]

<sup>&</sup>lt;sup>1</sup>An exponential function of the length is more accurate to the canonical light transport integral, but a linear approximation to this is commonly used for steps of small length.

# Composition is associative but not commutative

We have some flexibility in the order in which we composite the voxels. This is the property that will allow us to manipulate the order of memory accesses to influence access locality. We define the *composition operator*, C, as:

$$ray_k^{\alpha,R,G,B} = C(ray_{k-1}^{\alpha,R,G,B}, V_{k-1}^{\alpha,R,G,B})$$

This operator is used to take the value of the ray at step k, and accumulate the value of the kth voxel upon it. Note that the composition operator is associative but not commutative. That is:

$$C(C(a,b),c) = C(a,C(b,c))$$

but, in general:

$$C(a,b) \neq C(b,a)$$

Therefore, we need not composite an ordered set of voxels  $V_1$  through  $V_n$  strictly in order. We can composite any contiguous subset of voxels without regard to whether neighboring contiguous subsets have yet been completed.<sup>2</sup> The results from these subsets can then be composited together to generate the results for larger contiguous subsets, until ultimately the entire set of voxels  $V_1$  through  $V_n$  has been included.

It is this flexibility in the order of composition that will allow us to manipulate the order of memory accesses, to increase memory locality. This flexibility also makes projection methods possible:

<sup>&</sup>lt;sup>2</sup>An assumption made here is that addition is associative. This is only approximately true in general with digital representations of floating point numbers. However, the color and opacity values remain within a small range of values (generally 0.0 to 1.0), and the error due to this approximation is negligible in practice.

#### Projection methods

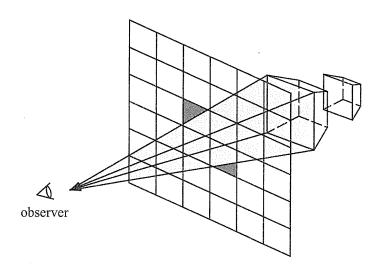

In contrast to ray casting, which considers each pixel and calculates the data voxels it intersects, *projection methods* [Westover90, Shirley90, Laur91, Wilhelms91] consider each data element in turn, and calculate the element's contribution to the image.

Figure 2.6: Rendering by projection or "object order" rendering

These methods are more commonly used with irregular grids, for which it is relatively expensive to do ray traversal. They are also used to render sets of three-dimensional objects that do not fill space. As shown in Figure 2.6, the objects (or irregular voxels) in the dataset are sorted in order of their distance from the eye point. Some projection operator P is applied to each object to determine its projected image on the pixels of the image plane. These two-dimensional projected images are composited together to form the final image. The same composition equations stated in the previous section are used.

Shear-warp methods [Drebin88, Schröder91, Wittenbrink94, Lacroute94] decompose the view matrix into a a sequence of computationally inexpensive shearing and/or warping operations. The operations are applied to an entire slab of data at a time, determining the projected image of the slab onto the image plane. The subimages are then composited together. This type of algorithm can be considered an optimized

projection method.

#### Volume rendering algorithms used in this thesis

In this thesis, we will primarily use ray casting methods. However, for considerations of cache locality and parallel partitioning, we will also divide the regular dataset into blocks. We will treat these blocks semantically as objects to which we apply some projection operator P to determine their projected image, which are then composited together, as in projection methods. At the level of the individual block, the operator P which we use is ray casting. We will exploit the flexibility afforded by the associativity of the composition operator to manipulate the order of memory accesses, thereby increasing memory access locality and memory hierarchy performance.

# 2.1.5 Algorithmic optimizations to ray casting

Since this work focuses on ray casting for direct volume rendering, we discuss some algorithmic optimizations that are commonly made to the ray casting algorithm. Algorithmic optimization seeks to obtain higher performance, while accepting certain rendering artifacts in return.

# Coherence in volume rendering

Many algorithmic optimizations to ray casting take advantage of some form of *coherence* [Sutherland74], for example:

- Object coherence

That objects tend to be connected, bounded bodies.

- Area coherence

That the two-dimensional projection of a three-dimensional body tends to have a connected, bounded range.

- Frame coherence

That one frame of an animated sequence is likely to resemble the previous frame.

(e.g., in the colors assigned to given pixels; in the costs to render given units of work.)

• Coherence (locality) of memory reference

That a memory reference to a given location is likely be temporally close to references to logically neighboring locations.

Many optimizations to ray casting take advantage of some form of coherence:

#### Bounding boxes

Object coherence is often exploited by placing bounding boxes around the non-empty regions of the dataset. [Kay86, Glassner84, Levoy90] These "boxes" need not necessarily be rectangular solids. Only rays which intersect non-empty volumes need to be processed. If a ray exits such a volume, it can skip to where it next enters such a volume, ignoring the intermediate voxels. This optimization exploits object coherence and the performance improvement it yields is dataset dependent. This optimization need not result in any rendering artifacts.

Five-dimensional bounding boxes (3D spatial plus a 2D solid angle) are placed around sets of rays originating from nearby points and pointing in the similar directions in [Arvo87].

# Adaptive pixel subsampling

Area coherence can be exploited by casting fewer rays where the image does not contain much fine detail. For example, initially, a sampling of rays distributed randomly around the image are cast. If the final accumulated values of neighboring rays differ by more than a certain threshold, then more rays are cast in their neighborhood; otherwise, a ray is used to color more than a single pixel. A common artifact is for small objects to be missed entirely.

#### Data blocking

A primary focus of this thesis is improving memory hierarchy performance. One means to achieve this on at the level of the processor cache is to subdivide a large dataset into blocks that are stored contiguously in memory. If these blocks are sized appropriately relative to the size of the cache, and are processed serially, then both cache locality, and overall performance, can be greatly increased. [Palmer97a] This is a primary focus of this thesis, and these concepts are discussed in greater depth in section 2.4.

#### Opacity clipping

A ray's accumulated opacity value will asymptotically approach 1 at a rate that depends on the opacity of the intersected data voxels. A common algorithmic optimization known as *opacity clipping* [Levoy90] stops the further advancement of rays that have become nearly opaque. This optimization is quite dataset dependent: it works best on datasets with large opaque areas, and not at all on completely translucent datasets where rays never become completely opaque. A two- to four-fold performance improvement is possible in practice on many interesting datasets.

#### Re-use of information between frames

When the change in viewpoint between frames is small, temporal coherence results. This can be exploited to reduce redundant computation [Badt88]; in this thesis and in [Palmer94a, Palmer94b, Palmer95, Palmer97a, Palmer97b], we rely on this coherence in order to use workload estimates from one frame to predict workloads for the next frame.

# Variable pixel density

In ray casting, there is a near-linear relationship between the number of pixels rendered (i.e., the resolution of the image) and the time to render a frame. <sup>3</sup> By the

<sup>&</sup>lt;sup>3</sup>This relationship is true if we neglect cache effects, which are discussed in detail below.

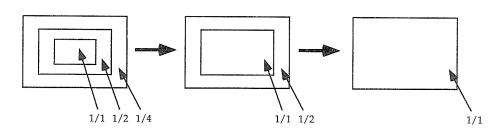

technique of dynamic resolution reduction, it is possible to automatically choose which of these is most important to the user. One pattern of resolution reduction is shown in Figure 2.7. In the center of the screen, we maintain full resolution. Around this central area, we place concentric bands of reduced resolution. When the user stops moving, we refine the image in several steps until the entire screen is at full resolution, as shown from left to right in the figure. With this technique, we obtained [Palmer95] a typical four-fold reduction in total number of rays cast, and a corresponding four-fold frame rate increase, when it is most needed during user movement. This perhaps exploits coherence of user interest: the user will tend to place the region of the data in which they are currently most interested in the center of the screen.

Figure 2.7: Dynamic resolution refinement for higher frame rate

# Dynamic subsampling of the dataset by distance from viewpoint

Due to perspective, data voxels far from the eye appear smaller than those that are very close. At a certain distance, the projected area of a voxel is smaller than a single image pixel. When a ray reaches this distance, a more aggressively band-filtered dataset (which can be represented accurately with a smaller number of discrete samples) may be substituted for the original dataset with little visible effect on the image. [Laur91, Danskin92] As the ray travels further, still lower resolution datasets may be substituted. This has two effects: it decreases the total number of ray-voxel intersections which must be made, and improves cache hit rates if intersections are calculated in an appropriate order. It exploits the coherent and constant divergence of rays in the perspective projection.

#### Types of coherence exploited in this thesis

In some of the experiments described in later chapters, we use the algorithmic optimizations of opacity clipping, which exploits ray coherence; and bounding boxes, which exploits object coherence. For the purposes of load balancing, we exploit frame coherence, using load measurements for one frame to predict the likely load for the next frame. Most importantly, we focus on how to effectively maximize coherence (locality) of memory access, in order to tap significant gains in memory hierarchy performance.

# 2.2 Parallel architectures for ray casting

A notable example is the PixelPlanes architectures [Fuchs89], however, this hardware was never distributed commercially. The first version of this architecture appeared as early as 1981. [Cabral94] used the texture mapping hardware of the Silicon Graphics RealityEngine graphics subsystem to do volume rendering (a task for which it was not explicitly designed). This implementation was quite fast (10Hz) for small volumes, but volumes were limited to the size of the memory in the graphics subsystem (16MB). This thesis is primarily concerned with algorithms that do not require a high fraction of the machine cost to be dedicated to special-purpose graphics hardware.

Volume rendering algorithms have been implemented on a wide variety of general-purpose architectures. Two early implementations on the Connection Machine CM-2 [Schröder91, Schröder92] achieved near-interactive rates for small volumes by sacrificing perspective projection. Both algorithms were specifically designed for the fine-grained SIMD architecture of the CM-2.

Early distributed-memory implementations were [Dippé84, Cleary86, Nemoto86]. [Corrie92] was the first distributed-memory implementation which used caching of volume blocks among the nodes. A large number of other distributed-memory algorithms have been described.

[Challinger91] implemented both ray casting and projection algorithms on the shared-memory BBN TC2000. [Nieh92] was a high-performance implementation on the shared-memory Stanford DASH. [Cox93] took specific advantage of the shared bus with a snooping algorithm to optimize pixel merging.

This thesis will primarily concern itself with MIMD (both shared- and distributed-memory) architectures, rather than SIMD architectures, whose prominence has waned in recent years.

# 2.3 Parallel partitioning for ray casting

# 2.3.1 The two goals of parallel partitioning

Ray casting is replete with parallelism. However, a primary concern in both shared-memory and distributed-memory MIMD implementations is selection of a suitable algorithm for partitioning the work (and, for distributed-memory architectures, the data) on a parallel machine. Parallel partitioning and load balancing algorithms have traditionally been designed to satisfy two often conflicting goals:

- Equal balance of workload among processors

- Minimization of communication among distributed nodes

# 2.3.2 Algorithms for parallel partitioning and load balance

Finding such algorithms suitable for ray casting volume rendering is nontrivial. There exists a wide variety of such algorithms, which can be classified by partition type and by the method used for load balancing.

# Image partitioning versus object partitioning

In ray casting, work units can be created by subdividing the two-dimensional display screen, assigning sets of rays to each processor; or by subdividing the threedimensional volume database, assigning sets of voxels to each processor.

Image partitioning [Challinger91, Nieh92, Corrie92, Whitman93, Palmer94b] methods partition the two-dimensional image plane, and assign subdomains (e.g., scanlines or rectangles) to the processors. The appeal of image partitioning is that the disposition of a pixel can be solely determined by the owning processor, without the composition of contributions from other processors. This allows global opacity clipping, the early termination of rays that become opaque before completely traversing the dataset. This algorithmic optimization yields performance gains which are dataset dependent but sometimes substantial. The primary disadvantage of image partitioning is lack of locality in accessing the three-dimensional volumetric data set. Since the relationship between image space and object space is not fixed, a processor may in general need to access any voxel in the dataset to cast a single ray. This lack of locality can result in cache thrashing in shared-memory systems. In distributedmemory systems, large communication volumes can result, unless the entire dataset is replicated on each distributed node. On fine-grain distributed-memory systems, the cost of either replication or communication can become prohibitive, and the image partition may not be suitable for use. (An exception is [Schröder92], who were able to reduce communication costs by using regular communication patterns on a data-parallel architecture.)

Object partitioning [Dippé84, Nemoto86, Cleary86, Kobayashi87, Priol89], an alternate approach, assigns subdomains of the object space called blocks (e.g., rectangular solid subsets of the data volume) to processors. In the projection step, processors cast rays through each block individually, generating a tile, the volume rendered image of a single block. The tiles are sorted according to their distance from the eye point, and composited together in the composition step to create the final image of the entire data volume.

Most importantly for the goals of this thesis, object partitioning schemes have a natural potential to improve local memory system performance. Blocks are stored contiguously in memory, so by processing an entire block at once, locality of memory access is dramatically increased. For properly sized blocks, orientation-dependent memory system delays all but vanish, offering the potential of reliable, interactive

rendering rates.

One drawback of object partitions is that global opacity clipping is infeasible because blocks are rendered individually. Intra-block opacity clipping can still be done, but it is not as effective, particularly with large numbers of small blocks. In addition, there is overhead associated with the composition phase of the algorithm; this phase is parallelizable (the most straightforward method would use an image partition for the composition step), but has a cost proportional to the total area of the projected tiles (or proportional to the cube root of the number of blocks).

#### Static versus dynamic load balancing

Another important characteristic of parallel partitioning methods is how an equal balance of workload can be assigned among the parallel processors.

Static load balancing algorithms [Cleary86, Kobayashi88] make a fixed assignment of units of work to processors. Static load balance is simpler to implement than dynamic load balancing. These methods rely on a statistical tendency toward equal load balance due to a high granularity of work units, and a low variance in their cost (both among themselves and temporally). If these conditions are met, then a random assignment of work units to processors will tend to yield an equal load balance. For example, one can assign individual scan lines of an image to processors in round-robin fashion. Unfortunately, this yields the side effect of very low locality of memory reference. Increasing locality among assigned work units tends to increase the correlation between their costs, causing poor load balance. Furthermore, the dynamic nature of interactive volume rendering tends to yield a high variance in the cost of work units. For image partitions, regions of the screen may have high cost, or have no cost if we are able to cheaply determine that they do not overlap the projected image of the dataset; for an object partition, subvolumes of the dataset may have a high cost, or may not currently be visible on the screen, and have no cost.

Dynamic load balancing algorithms [Dippé84, Nemoto86, Nieh92] change the assignments of work units to processors when necessary. This may be when load balance falls below a certain threshold, or when the expected improvement in load balance is

worth any communication costs that will be entailed. Dynamic load balancing algorithms often rely on frame coherence, the tendency of one frame (and one set of costs for the units of work) to be similar to the previous frame. Under the constraint of smooth movement of the view point and view direction, the temporal variance in the cost of a given unit of work remains low. This allows continuous adjustment of load balance through a gradual change in load conditions. Setting the required minimum load balance threshold too high can result in load balance thrashing, in which work units are shuttled back and forth among processors, without a payoff in improved load balance.

## 2.4 Memory hierarchies and exploiting locality of memory access

#### 2.4.1 Uniprocessor cache architecture

Fast memory is generally more expensive than slow memory. Fortunately, typical access patterns to memory exhibit the property of locality: A memory reference to a given location will tend to be temporally near references to neighboring locations. Therefore, a hierarchy of increasingly small amounts of increasingly faster types of memory can be constructed, yielding higher cost effectiveness than a single layer of any one kind of memory.

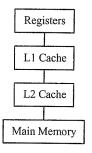

A typical memory hierarchy for a single-processor architecture, shown in Figure 2.8, has one or two layers of fast cache memory between the processor and the main memory, called the level one (L1) and level two (L2) caches. The L1 cache is smaller and faster than the L2 cache. The caches are divided logically into cache lines. When the processor first requests a word from memory, the entire line containing that word is copied into the L2 cache, then into the L1 cache, then into the processor registers. The next time the processor needs a word from that line, the request can be satisfied from fast cache memory without the necessity of going to main memory. Likewise, if the processor needs to write to a word of memory, the write will

Figure 2.8: A typical memory hierarchy for a single-processor architecture

be faster if the cache line containing that word is already in the cache. The cache memory is much smaller than the main memory, so it will eventually become full, and some lines will have to be discarded. A common policy is to discard those which were least recently accessed. When a line is discarded from the cache, its contents are written back to memory if the line is "dirty" — if it has been written to.

Carefully written programs can be made to have increased locality of memory access, yielding better cache performance at each level of the cache; however, the interaction between a given program, other programs, the operating system, and multilevel cache hardware, is often complex. User programs generally do not have control over which blocks are maintained in the cache, since the caching policies are usually built into the hardware. This does not necessarily result in the most efficient use of the cache. There are certainly cases in which the programmer has information about future memory accesses that is not available to the cache hardware.

Copies of a given word of data are replicated vertically in this simple single-processor memory hierarchy. Each copy of the word can be considered to be consuming precious system resources. Algorithm designers are accustomed to conserving operations and program size; efficient use of each copy of a word of data is no less important.

#### 2.4.2 Shared memory

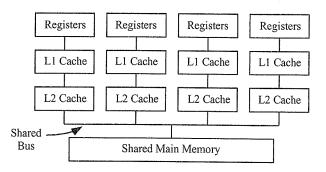

Many algorithms are structured such that more than one processor can simultaneously work contribute to a solution. A shared-memory design is one way to build a parallel machine.

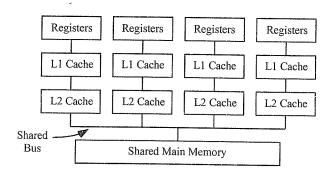

Shared memory systems consist of multiple processors, each with their own registers and caches, connected by a bus to a shared main memory, as in Figure 2.9. A typical example is the Silicon Graphics Power Challenge.

Figure 2.9: A typical memory hierarchy for a shared-memory architecture

In such a system, a given word of memory is replicated not only vertically, but can also be replicated horizontally, across the processors. This introduces the problem of maintaining cache coherence horizontally among the processors. For example, suppose two processors read the value "0" from the same location in memory into their caches, increment that value in their caches, and (when the cache lines are purged) each write the line back to the shared main memory. If special provision were not made to maintain cache coherence, then slight variations in the timing of these operations could result in nondeterministic results - equivalent to a single processor incrementing the value either once or twice. One hardware mechanism for assuring the property of cache coherence is referred to as directory based, in which a central directory of the sharing status of each cache line (whether a copy exists on more than one processor) is maintained; another is bus-snooping, in which each processor watches the bus for transactions involving cache lines of which it currently holds a copy.

The point-to-point bandwidth and latency of the bus shared by the processors is generally much higher than that of the interconnection network connecting processors of a distributed memory machine. However, this design is not scalable to as many processors as a distributed memory design, described below. It is possible to saturate the shared bus with requests so that *bus contention* among the processors limits the bandwidth available to each.

#### 2.4.3 Distributed memory

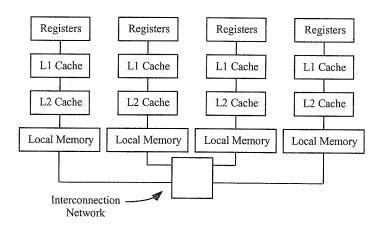

Distributed memory systems consist of multiple processors, each with their own registers, cache, and local main memory; the processors are connected some interconnection network, as in Figure 2.10. A wide variety of interconnection topologies have been used.

Figure 2.10: A typical memory hierarchy for a distributed-memory architecture

Many commercial distributed memory machines do not allow the programmer to access the entire memory of the machine as a single global address space. Each processor is able to read its own local memory; access to data stored in other processors' local memories must be transferred by the explicit passing of messages. On such machines, the programmer has complete control over how data moves between distributed nodes and over how what data, if any, is replicated.

On machines that do not provide a global shared address space, the programmer

can implement one logically in software. This allows the use of information not available to an automatic caching hardware to optimize cache performance. We examine such a system, complete with provision for caching, in this thesis.

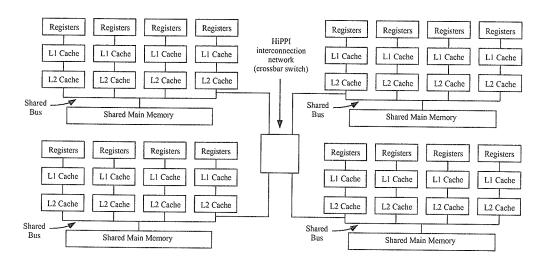

#### 2.4.4 A hybrid architecture: the Power Challenge Array

The memory hierarchy of the Power Challenge Array is a hybrid: it consists of multiple shared-memory Power Challenge nodes connected by a HIPPI crossbar network, as shown in Figure 2.11. For certain problems, such non-uniform memory access (NUMA) architectures allow efficient scaling to greater numbers of parallel processors than either shared-memory machines (with their fast but non-scalable bus) or distributed memory machines (with their "scalable" but relatively slow interconnects). The deep memory hierarchy of such machines allows better use to be made of the coherence in some problems, in order to increase memory locality.

Our use of this architecture in our experimentation allows us to explore shared memory performance considerations, distributed memory considerations, and considerations for a relatively deep memory hierarchy, which requires particular attention to exploiting memory hierarchy to achieve the maximum available performance. It is quite difficult, both algorithmically, and in terms of implementation, to achieve the peak performance on such an architecture. This is one of the goals of this thesis.

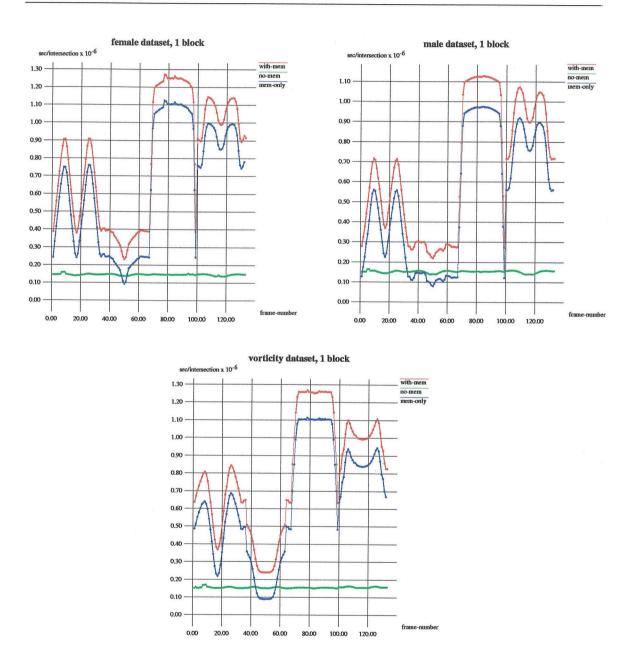

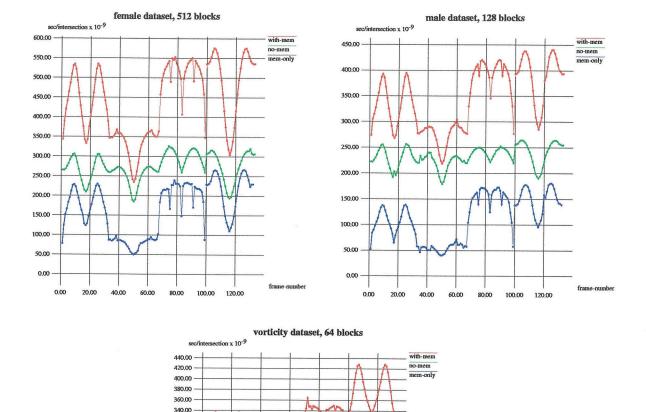

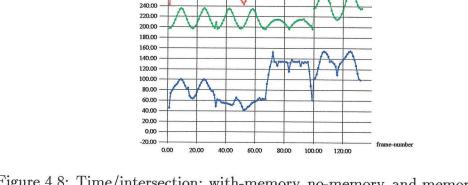

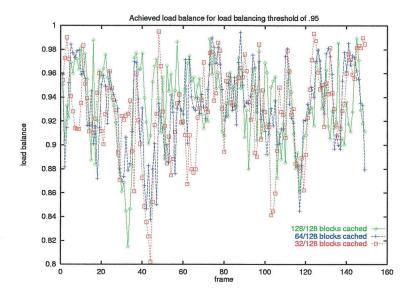

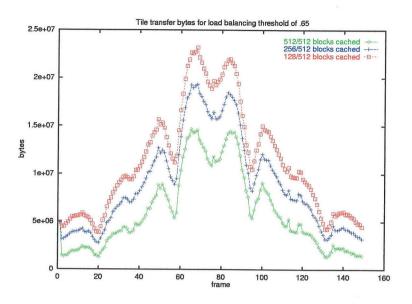

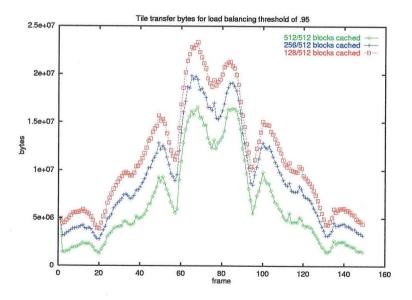

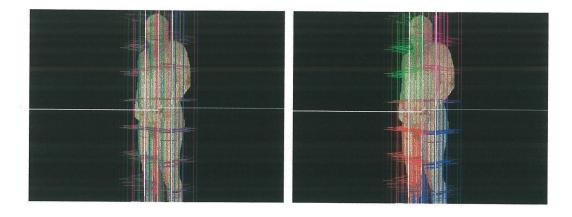

# 2.5 The relationship between parallel partitioning and memory hierarchy performance