# **Analysis of Single Phase Rectifier Circuits**

Thesis by

James Frederick Lazar

In Partial Fulfillment of the Requirements

for the Degree of

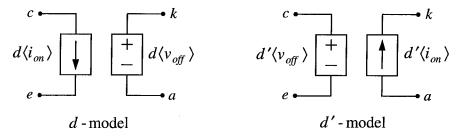

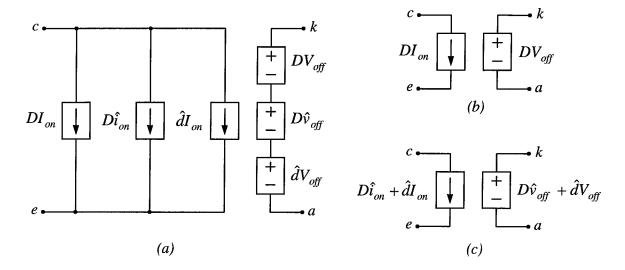

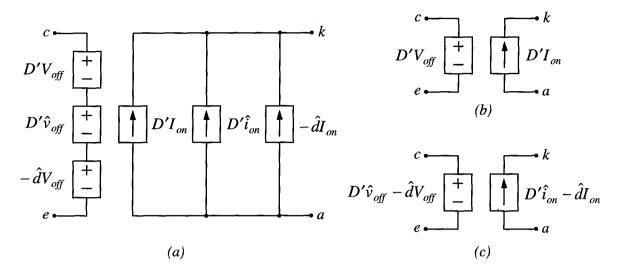

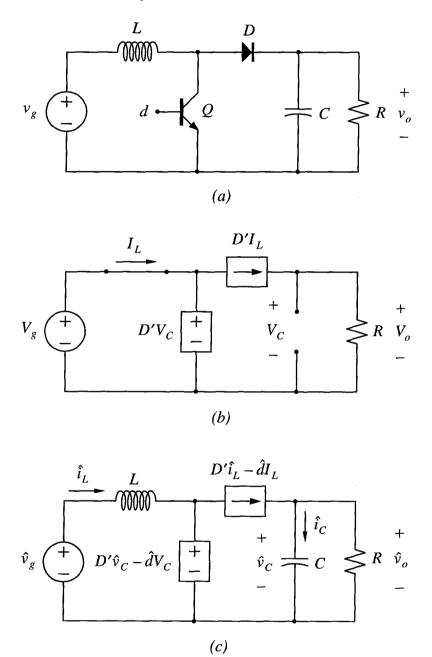

Doctor of Philosophy

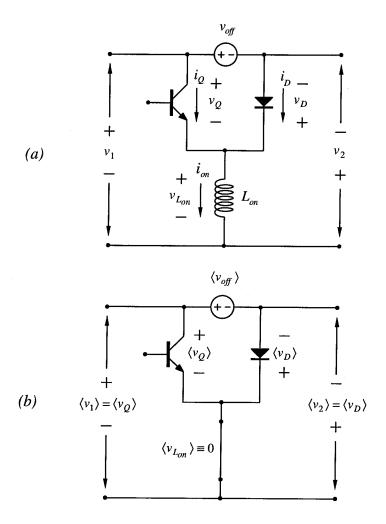

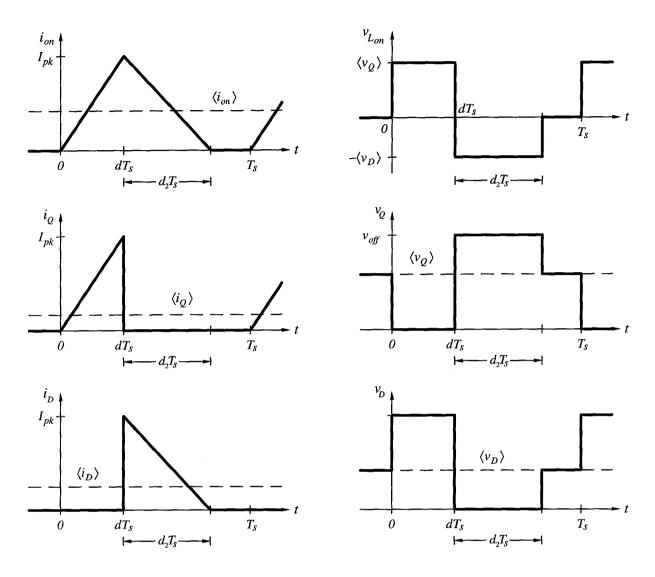

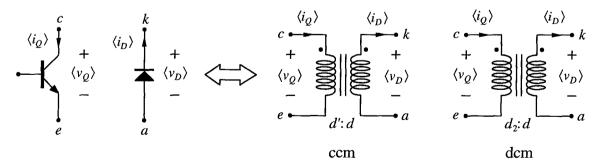

California Institute of Technology

Pasadena, California

1997

(Submitted March 19, 1997)

© 1997 James Frederick Lazar All Rights Reserved to my family

## Acknowledgments

I wish to thank my advisor, Professor Slobodan Cuk, and co-advisor, Professor R.D. Middlebrook, for accepting me into the Power Electronics Group, for their guidance, but most of all for the teacher-student relationship we have shared.

I gratefully acknowledge the financial support of the Sorensen Foundation (graduate research fellowship), of Caltech (graduate teaching and research fellowships), and of the following corporations who supported the Power Electronics Group during my stay: Rockwell International Inc., General Electric Co., Apple Computer Inc., GEC Ferranti Defense Systems Ltd., Southern California Edison Inc., Italtel Inc., Day-Ray Products Inc., Boeing Electronics Inc., and Magnetek Inc..

Every graduate of the Power Electronics Group is indebted to his (her) predecessors, each of whom has sacrificed part of himself (herself) to contribute to the body of knowledge representative of the Power Electronics Group.

## **Abstract**

The preponderant application of rectifier circuits is the powering of dc loads from the ac utility line. Ordinary rectifier circuits present a nonlinear load impedance to the utility line, thereby generating harmonic currents, and contributing to the harmonic current problem. There are many active and passive rectifier circuits offering reduced harmonic currents, and in this work a methodology is developed by which these circuits may be analyzed and compared.

Rectifier circuits can be classified as either active or passive. A passive rectifier circuit contains passive components (inductors, capacitors, saturable reactors, etc.), and passive switches (rectifier diodes) only. Active rectifier circuits use at least one controllable active switch (power transistor), in addition to passive switches and passive components. The performance characteristics of these circuits can be assessed with respect to a fictional device called the ideal rectifier. This assessment allows direct comparison of various approaches, passive or active, using the ideal rectifier as the common reference. Rectifier circuit performance may also be compared against specified requirements.

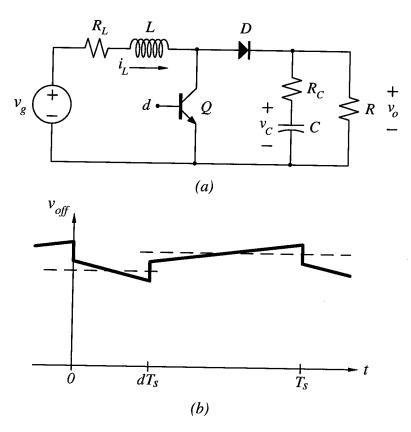

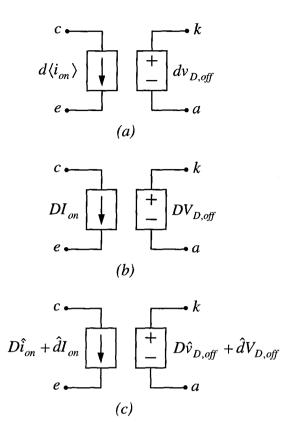

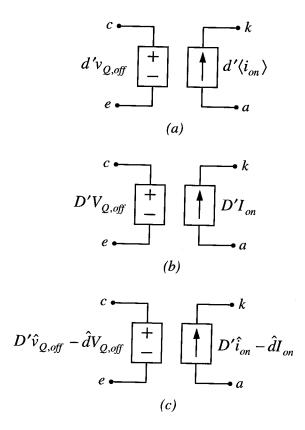

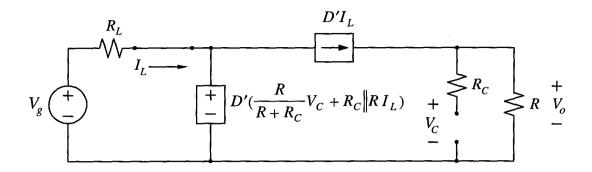

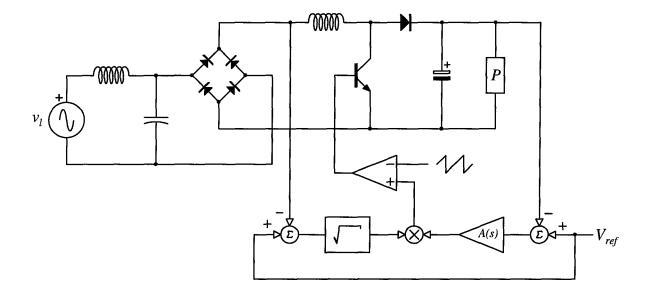

The next topic considered is the analysis of active rectifier circuits employing a pwm (pulse width modulation) converter as a means to control power flow within the rectifier circuit. The pwm converter is modeled using the pwm switch method. A large-signal nonlinear pwm switch model is used for modeling large-signal rectifier circuit behavior, and models are developed for operation in either the continuous or discontinuous conduction mode. Similarly, a small-signal model is developed for small-signal considerations. In addition, for pwm converters operating in the continuous conduction mode, the effect of lossy resistive elements inside the converter are accounted for in the

pwm switch model, and this modeling technique is shown to give results identical to those obtained via the state-space averaging method.

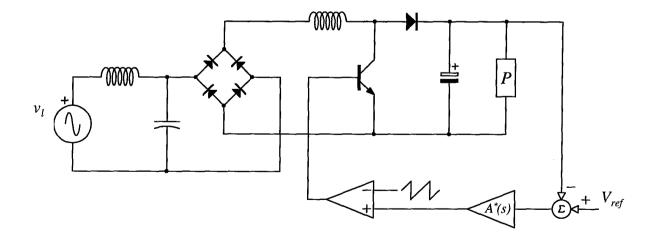

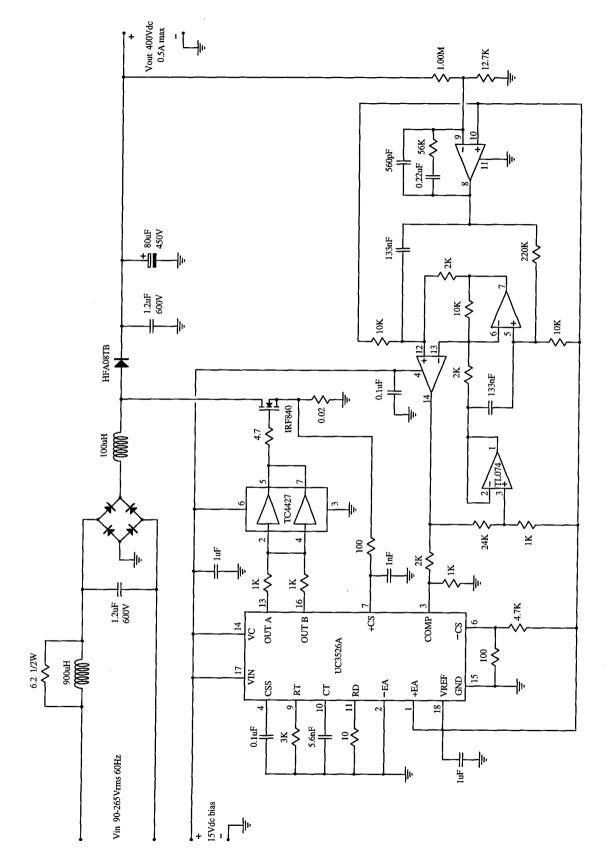

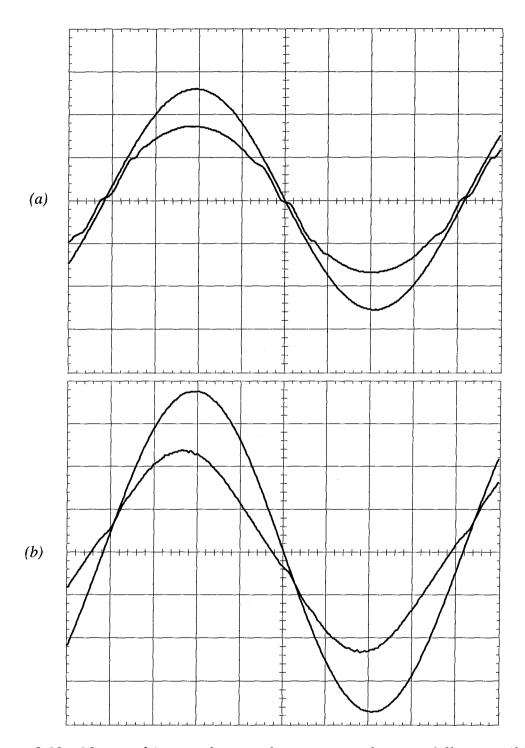

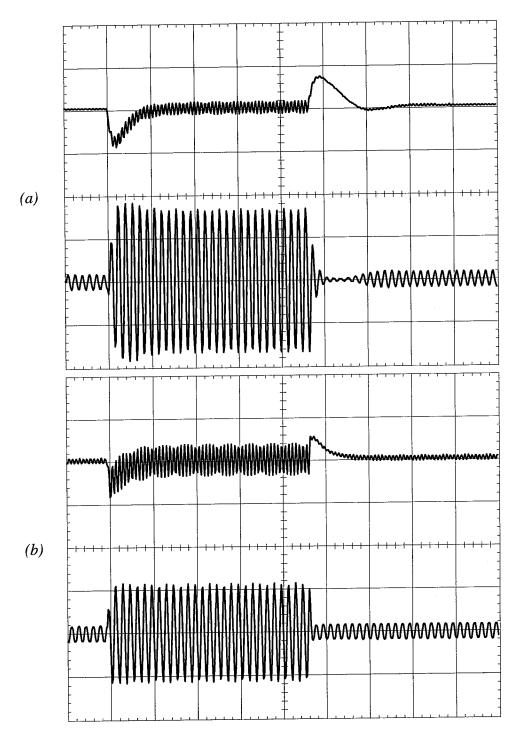

The methods developed are then applied to the analysis of the boost rectifier operating in the discontinuous conduction mode. Three control schemes are compared, each offering a different compromise between circuit complexity and performance. Finally, a design example is given, and experimental results are provided.

# **Contents**

| Acknowledgments |          |                                      |  |  |  |

|-----------------|----------|--------------------------------------|--|--|--|

| Ab              | Abstract |                                      |  |  |  |

| 1               | Int      | roduction 1                          |  |  |  |

| 2               | Pov      | ver Factor and the Ideal Rectifier 5 |  |  |  |

|                 | 2.1      | Power Factor6                        |  |  |  |

|                 | 2.2      | The Ideal Rectifier                  |  |  |  |

|                 | 2.3      | Constant Power Load                  |  |  |  |

| 3               | Pas      | sive Rectifier Circuits 23           |  |  |  |

|                 | 3.1      | Capacitor Filter                     |  |  |  |

|                 | 3.2      | Inductor Filter                      |  |  |  |

|                 | 3.3      | Line-Side Inductor Filter            |  |  |  |

|                 | 3.4      | Load-Side inductor Filter            |  |  |  |

|                 | 3.5      | Resonant Filter                      |  |  |  |

|                 | 3.6      | Discussion                           |  |  |  |

| 4               | Ene      | ergy Storage 75                      |  |  |  |

|                 | 4.1      | Load Balancing76                     |  |  |  |

|                 | 4.2      | Single Element Load Balancing        |  |  |  |

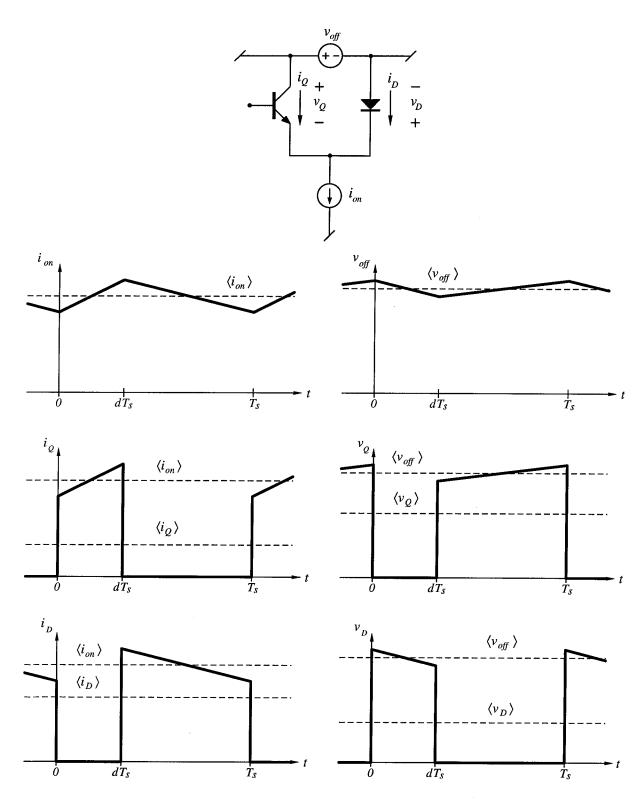

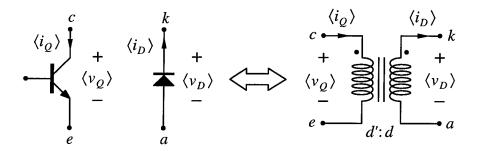

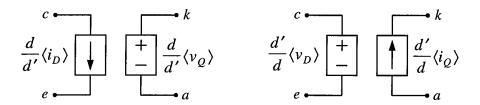

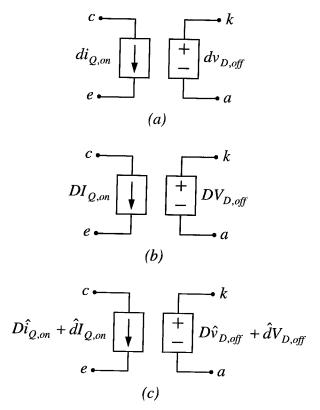

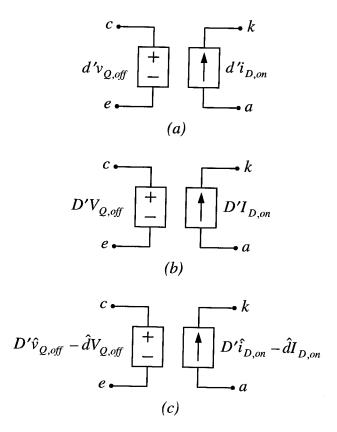

| 5   | Pw                                          | m Switches in Continuous Conduction Mode                       | 81  |

|-----|---------------------------------------------|----------------------------------------------------------------|-----|

|     | 5.1                                         | Definition of an Ideal Pwm Converter                           | 81  |

|     | 5.2                                         | Pwm Switches for Ideal Pwm Converters                          | 83  |

|     | 5.3                                         | Dc and Small-Signal Ac Models for Pwm Switches                 | 87  |

|     | 5.4                                         | Pwm Switches for Converters with Series Resistive Elements     | 92  |

|     | 5.5                                         | Pwm Switches for Converters with Parallel Resistive Elements   | 96  |

|     | 5.6                                         | Application of the Pwm Switch in Ac/Dc Rectifier Circuits      | 100 |

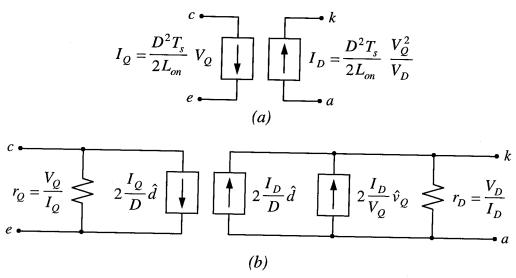

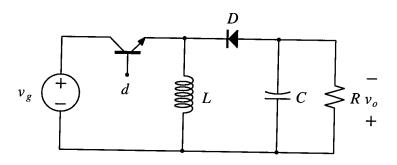

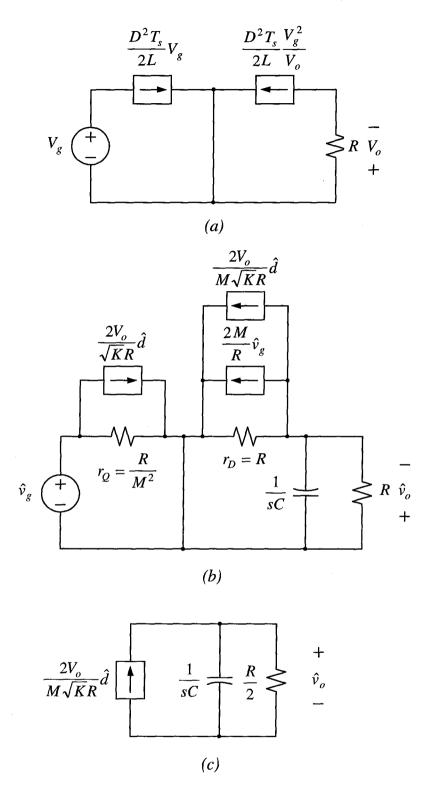

| 6   | Pwi                                         | m Switches in Discontinuous Conduction Mode                    | 107 |

|     | 6.1                                         | Pwm Switches in Discontinuous Conduction Mode                  | 108 |

|     | 6.2                                         | Dc and Small-Signal Ac Models for Pwm Switches in Dcm          | 113 |

|     | 6.3                                         | Application of the Nonlinear Model in Ac/Dc Rectifier Circuits | 117 |

| 7   | Operating Modes in Ac/Dc Rectifier Circuits |                                                                |     |

|     | 7.1                                         | Ac & Dc Circuits                                               | 120 |

|     | 7.2                                         | Equivalent Duty Ratio                                          | 125 |

|     | 7.3                                         | Pwm Converters in Ac/Dc Rectifier Circuits                     | 129 |

| 8   | The                                         | Dcm Boost Rectifier                                            | 135 |

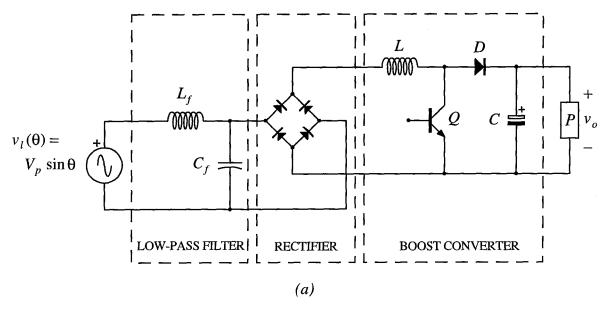

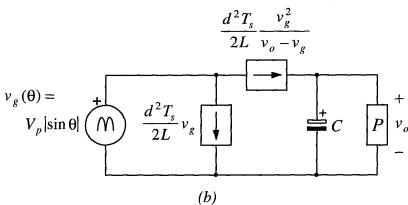

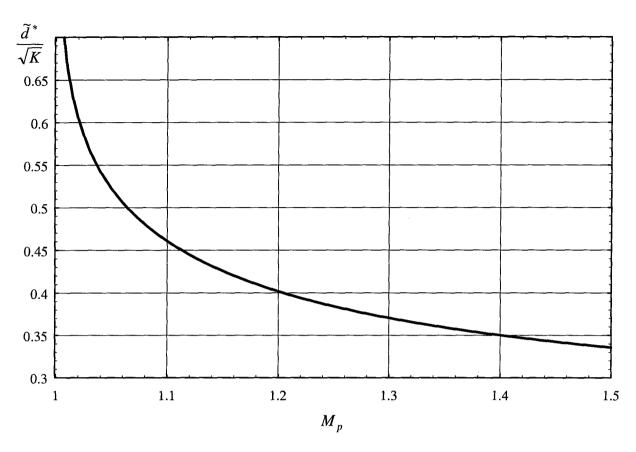

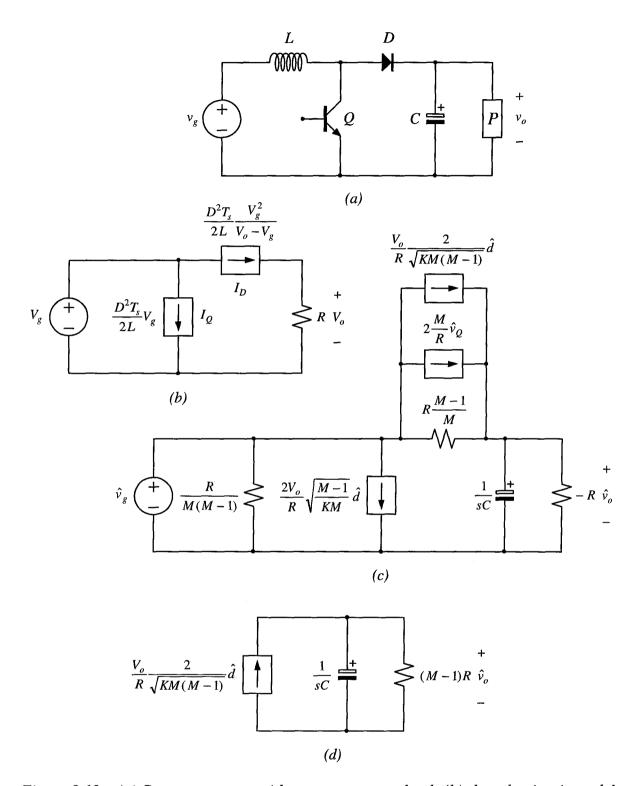

|     | 8.1                                         | Dcm Circuit Model                                              | 136 |

|     | 8.2                                         | Constant Duty Ratio Dcm Boost Rectifier                        | 138 |

|     | 8.3                                         | Unity Power Factor Dcm Boost Rectifier                         | 146 |

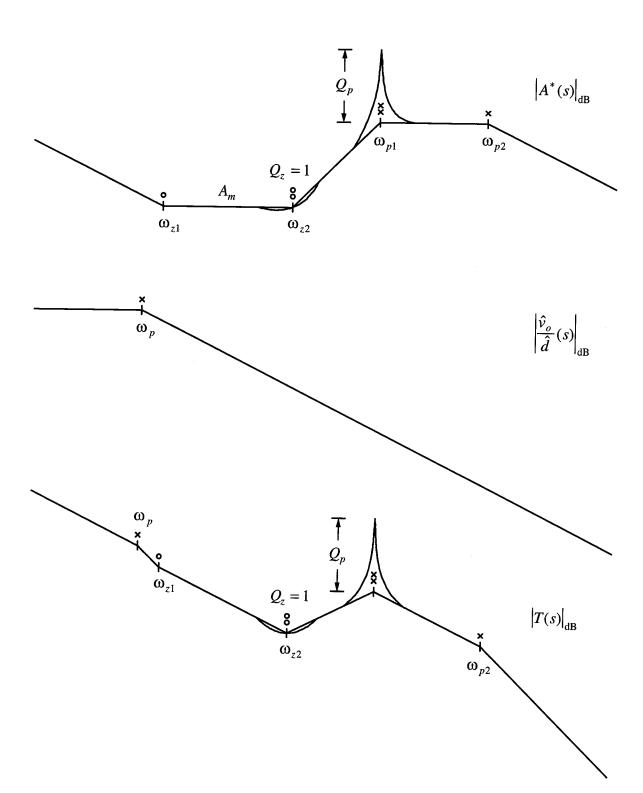

|     | 8.4                                         | Optimal Voltage Feedback Dcm Boost Rectifier                   | 149 |

|     | 8.5                                         | Optimal Voltage Feedback Design Example                        | 162 |

| 9   | Con                                         | clusion                                                        | 177 |

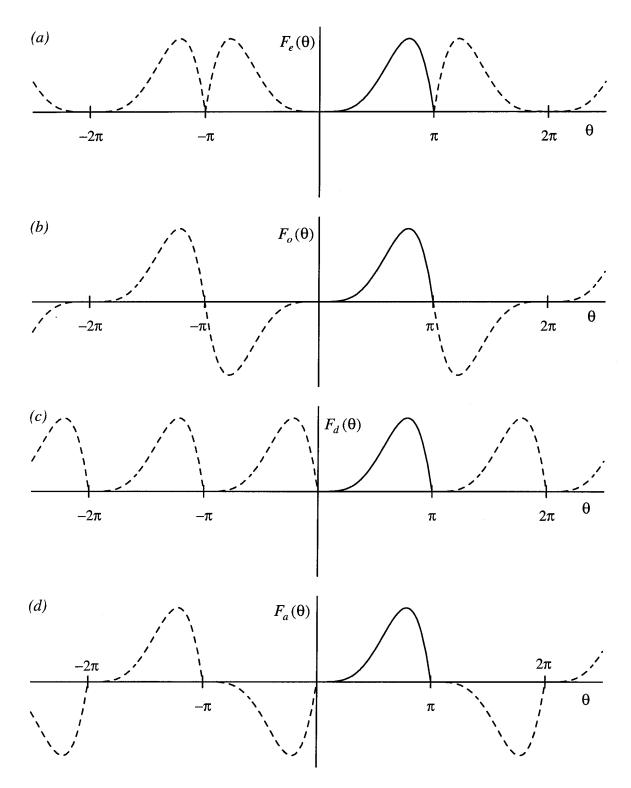

| App | pend                                        | ix A Periodic Extensions                                       | 181 |

|     | <b>A.</b> 1                                 | Even Periodic Extension                                        | 181 |

|     | A.2                                         | Odd Periodic Extension                                         | 184 |

|     | A.3                                         | Direct Periodic Extension                                      | 185 |

| Referen | ces                                          | 191 |

|---------|----------------------------------------------|-----|

| A.5     | Phase-Shifted Alternating Periodic Extension | 188 |

| A.4     | Alternating Periodic Extension               | 187 |

## Chapter 1

## Introduction

Electrical power conversion systems process electric power at the system input into a desired form at the system output. There are two basic types of electrical power, namely ac and dc, which implies that that there are four basic power conversion processes. These processes have been given the names dc/dc conversion, dc/ac inversion, ac/dc rectification, and ac/ac cycloconversion. The systems that perform these processes are similarly named dc/dc converters, dc/ac inverters, ac/dc rectifiers, and ac/ac cycloconverters. This thesis is concerned primarily with the process of ac/dc rectification, specifically as it pertains to single phase ac/dc rectifier circuits. Although the primary focus is on ac/dc rectification, because a dc/dc converter is at the heart of many ac/dc rectifier systems, much attention is given to the analysis of dc/dc converters, and then further extended to the ac/dc rectification problem. The omnipresence of ac power sources and dc loads, and the desire to connect them, makes this study an important one.

Ideally, the electrical utility system provides low frequency ac power to the electric power consumer via a fixed frequency, fixed amplitude, sinusoidal voltage waveform. The electric power consumer then connects loads, some linear, some nonlinear, to the utility line to perform some desired task. However, the connection of nonlinear loads drawing non-sinusoidal current, combined with the non-zero source impedance of the utility line, causes distortion of the line voltage waveform. Further, this distortion is presented not only to the offending load, but to non-offending loads and consumers as well. In addition, the utility provider is asked to provide the non-sinusoidal current, through a utility grid which must be designed to carry the extra burden.

This scenario raises the issue of power quality, which is the primary motivation for studying the ac/dc rectification problem. The subject of power quality is concerned with the degree to which the electrical utility provides stable, reliable, zero distortion and disturbance-free voltage. Because many ac/dc rectifier circuits present a nonlinear load to the utility, they influence power quality by inducing distortion of the utility line voltage, and lower the power delivery system reliability through the circulation of non-sinusoidal current. While the influence of any one load, however small, on the utility line may seem insignificant, it is the net effect of all such loads that causes difficulty. The proliferation of personal computers as part of the information age is a particularly troublesome example.

In chapter 2, a quantitative measure of the effectiveness of electric power transfer, called the circuit power factor, is defined in general. Like most general definitions, however, it is difficult to draw many conclusions and obtain useful results without first making assumptions. To this end, the general case is quickly abandoned for the specific case of ideal sinusoidal utility line voltage. Although the actual voltage measured at the load operating on the utility line will never be an ideal sinusoid, this assumption leads to simple, intuitive results and provides a basis by which various rectifier circuits may be compared. Besides, an ideal sinusoid is certainly a reasonable approximation to what is actually measured at the terminals of a typical wall outlet. The effect of non-sinusoidal voltage components present on the utility line can be considered separately.

Also in chapter 2 is a general discussion of the terminal behavior of the constant power load. The constant power load is used many times throughout this thesis as a simple means of modeling the loading effect of a switching post-regulator as part of a complete ac/dc rectifier system. It is shown that this type of load exhibits the large-signal character of a positive resistance, and the small-signal character of a negative resistance. For this reason, modeling the loading effect of a switching regulator simply as an equivalent resistor can lead to incorrect results.

In chapter 3, the results developed in chapter 2 are applied to the analysis of passive rectifier circuits. In each case, it is assumed that the passive rectifier circuit is to be followed by a switching post-regulator, and the constant power load is therefore used to

emulate its loading effect. Passive rectifier circuits offer the advantages of simplicity and durability over active approaches, but are generally bulky and heavy as compared to their active counterparts. For high frequency input power sources, these disadvantages are less apparent, but for low frequency utility line applications, the size and weight of passive components are often prohibitive. The results contained in this chapter can be applied to make this determination, based on the specific performance requirements. The performance characteristics of each passive rectifier circuit are presented graphically, and can be compared directly against characteristics of other rectifier circuits, and also against the actual performance requirements.

The necessity for a single phase rectifier circuit to store energy is examined in chapter 4. Under the assumptions of unity input power factor and constant output power, the energy stored in the rectifier circuit is determined to within a constant. The minimum stored energy necessary for load balancing is determined, and this places a fundamental limitation on the design of these systems.

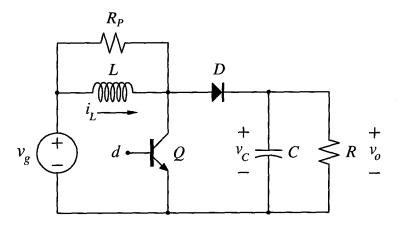

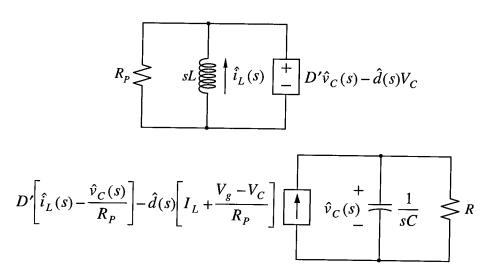

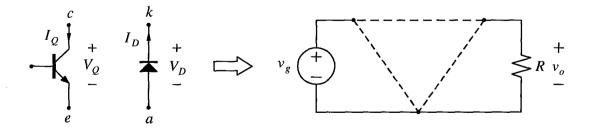

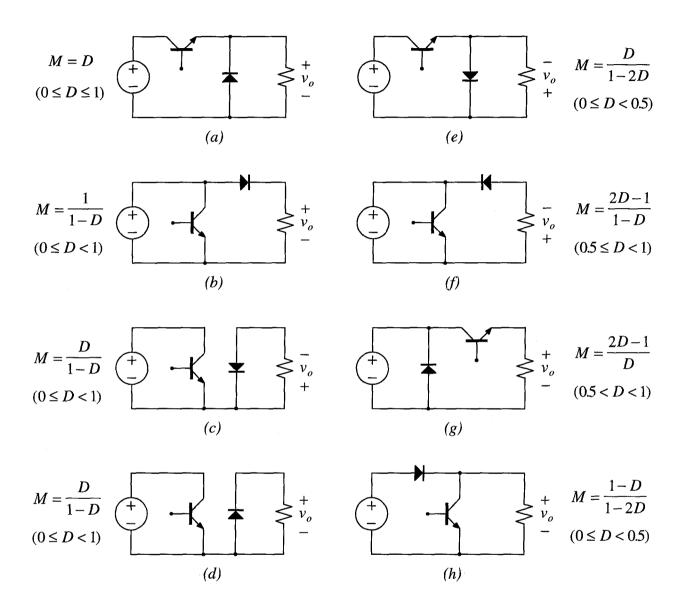

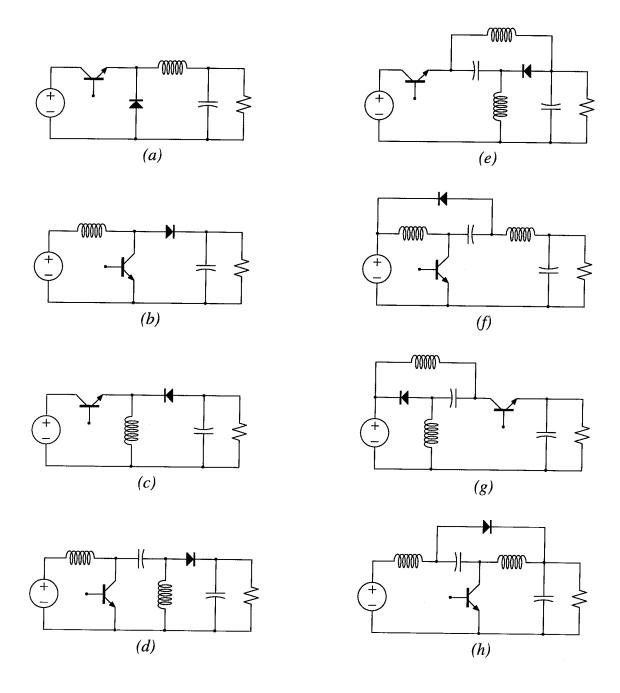

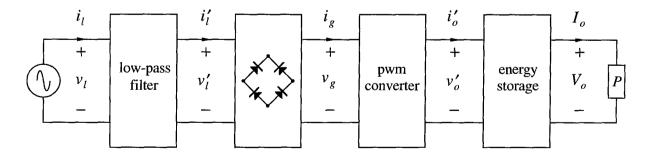

The remainder of this thesis considers ac/dc rectifier circuits incorporating pwm (pulse width modulation) dc/dc converters acting as the power processing interface between the ac input and dc output. To simplify matters, the pwm switch concept is considered in chapters 5 and 6, where several conceptually new pwm switch models are introduced. The pwm switch is a simplified circuit-oriented analysis method which confines the nonlinearity inherent in the switching process to the transistor and diode switches themselves. Pwm switches for converters operating in the continuous conduction mode are taken up in chapter 5, followed by pwm switches for converters in the discontinuous conduction mode in chapter 6. Although pwm switches are derived based on converter operation in a dc/dc system, they can be used for the analysis of ac/dc rectifier circuits under certain conditions.

The determination of the boundary between the continuous and discontinuous conduction modes is considered in chapter 7. In dc/dc converter applications, this boundary is a static one, since the operating point is fixed. In contrast, in ac/dc rectifier applications, the boundary changes continuously since the converter operating point varies throughout the line period. The converter can, however, be designed to maintain

a particular conduction mode over the entire line period, by ensuring that the boundary is not crossed at any point. It is usually desired for the converter in a rectifier circuit to operate exclusively in a single operating mode because the control system designed for operation in one mode may not be suitable for operation in another.

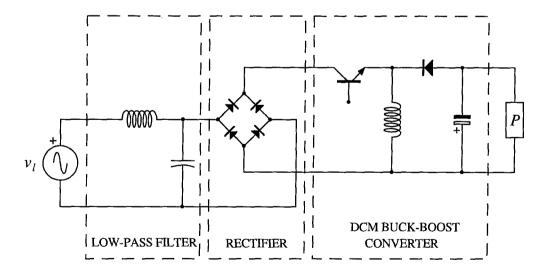

Finally, many of the ideas developed in the previous chapters are put to use in chapter 8, which is devoted entirely to analysis and design of the boost rectifier operating in the discontinuous conduction mode. The boost converter remains the converter of choice in ac/dc rectifier circuits for two main reasons. The first is that it is capable of voltage step-up, and therefore operates down to zero input voltage, through the zero crossings of the utility line. The second is that the boost is a partial power processing converter, where the switches process only part of the total output power. Hence, part of the input power passes directly to the output without being processed, and therefore without the associated power loss. This property makes the boost converter extremely efficient when compared to total power processing converters, such as the buck-boost, or any of the buck-boost type converters (cuk, sepic, zeta, etc.). One drawback of the boost converter which is a consequence this partial power processing property, is that it cannot directly provide galvanic isolation. However, in a complete rectifier system, a secondary post-regulator is usually added to provide precise regulation of the dc output voltage and to provide multiple dc outputs, and this regulator can employ a converter which is easily isolated. A second drawback is that the output voltage of the boost converter must be greater than the input voltage, since it is capable only of voltage step-up (hence, its name). In an ac/dc rectifier application, this requirement implies that the output voltage must be greater than the peak input voltage, which may be higher than desired. However, excellent performance is demonstrated with the peak conversion ratio approaching unity.

## Chapter 2

# Power Factor and the Ideal Rectifier

In this chapter, the basic definitions are set forth which quantify the quality with which a load processes power delivered from an ac power source. Power factor is a concept familiar to most engineers, but is often understood only at a rudimentary level. In section 2.1, the general time-domain definition of power factor is given. Next, the frequency-domain interpretation of power factor is discussed, for the specific case of ideal sinusoidal input voltage. Using a Fourier series expansion of the input current waveform, it is shown that the power factor may be written as the product of two factors, one called the distortion factor, and the other called the displacement factor. The distortion factor is concerned with the current harmonics flowing in the circuit, and the displacement factor with the phase of the fundamental component of the input current relative to the input voltage. The power factor is a compact way of quantifying the effect of both of these factors, although in practice it is often necessary to consider the two factors separately.

In section 2.2, the ideal rectifier circuit is defined. The ideal rectifier, like most idealizations, is unrealizable, but provides a theoretical reference against which real rectifier circuit performance can be assessed. The ideal rectifier is used extensively in this manner throughout this thesis. In section 2.3, the constant power load is discussed. The constant power load is a simple way to model the static and low frequency dynamic behavior of the input to a high performance switching regulator. A high performance switching regulator is often used in a complete ac/dc rectifier system as a secondary regulator, following the high power factor rectifier input stage. In this configuration, the secondary regulator is used to provide fast and precise output voltage regulation, multiple outputs, and also to provide galvanic isolation with respect to the ac input.

#### 2.1 Power Factor

The Power Factor is a measure of the effectiveness with which an ac source transfers power to a load. The power factor ranges between zero and unity, with zero power factor corresponding to completely ineffective power transfer, and unity power factor corresponding to completely effective power transfer. When the power factor is unity, the burden on the power delivery system is minimized, making this mode of operation very desirable.

#### 2.1.1 Definition of Power Factor

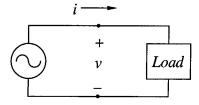

Consider the connection of a load, either linear or nonlinear, to a source of ac power, as in figure 2.1. It is assumed that the system is in steady-state, and that the voltage and current waveforms are periodic with the same period. Under these conditions, the power factor is defined, and is given by the ratio

$$PF \equiv \frac{P}{S} \tag{2.1.1}$$

where P is the average power and S is the apparent power delivered to the load. The average power P is the time-average value of the instantaneous power taken over one period

$$P = \frac{1}{T} \int_{T} v(t)i(t)dt$$

(2.1.2)

and is the quantity which would be read by a suitable wattmeter. The apparent power S is the product of the root-mean-square (rms) values of the voltage and current

$$S = V_{rms}I_{rms} \tag{2.1.3}$$

Figure 2.1: Single-phase ac circuit consisting of an ac power source and a load.

where the rms values of the voltage and current are defined by

$$V_{rms} \equiv \sqrt{\frac{1}{T} \int_{T} v^{2}(t) dt} \quad ; \quad I_{rms} \equiv \sqrt{\frac{1}{T} \int_{T} i^{2}(t) dt}$$

(2.1.4)

It is important to note that the power factor is a quantity which is defined for a *circuit*, and not for a *load*. It is therefore incorrect to say that a load exhibits a particular power factor. If identical loads are connected to two different ac sources, the power factor in each of these circuits may be different. One exception is if the load is a linear resistor. In this case, at any instant, the voltage and current are related by

$$v(t) = i(t)R \tag{2.1.5}$$

Substituting this expression into the definition of power factor, we find that the power factor is unity, regardless of the ac source waveform. Thus, proportional current, in general, yields unity power factor. This explains why high power factor rectifier circuits are sometimes referred to as "resistor emulators."

In the analysis of the power factor in ac/dc rectifier circuits, the goal is to determine the power factor of the circuit formed when the input to the rectifier circuit is connected to the ac utility line. Throughout this thesis, for the sake of simplicity, the utility line is modeled by a zero-impedance voltage source. Since the power factor is a circuit quantity which depends on both the ac power source and the load, in order to compare the power factor and performance of different rectifier circuits, the ac power source should of course be the same. The choice of a standard ac power source is obvious, namely an ideal sinusoidal voltage source, and the implications of this choice on the power factor formulation are the subject of the next section.

## 2.1.2 Frequency-Domain Formulation with an Ideal Sinusoidal Voltage Source

For the purpose of studying the power factor and current harmonics in circuits operating on the ac utility line, it is reasonable to model the utility line as an ideal sinusoidal voltage source. The sinusoidal assumption is invoked because it simplifies the analysis considerably, yielding results which are both accurate and informative. The effect of voltage waveform distortion can be handled separately, and is not considered

here. The purpose here is to develop concepts and methods useful for rectifier circuit design, simple enough that they are easily applied, yet complex enough that the results are accurate. To begin, we define angle  $\theta$  as the normalized time variable

$$\theta \equiv \omega_l t \tag{2.1.6}$$

where  $\omega_l$  is the line frequency. The source voltage is, by assumption, sinusoidal, with zero phase shift. We may therefore write

$$v(\theta) = \sqrt{2} V_{ideal} \sin \theta \tag{2.1.7}$$

where  $V_{ideal}$  is the rms value of the ideal sinusoidal source voltage. The following auxiliary formulas are introduced here because they are useful in the determination of the coefficients in the Fourier series expansion, and also in the derivation of the frequency-domain interpretation of power factor that follows. For any two integers  $n, m \neq 0$ , we have:

$$\int_{-\pi}^{\pi} \cos n\theta \, d\theta = 0$$

$$\int_{-\pi}^{\pi} \sin n\theta \, d\theta = 0$$

$$\int_{-\pi}^{\pi} \cos n\theta \cos m\theta \, d\theta = \begin{cases} \pi \; ; \; n = m \\ 0 \; ; \; n \neq m \end{cases}$$

$$\int_{-\pi}^{\pi} \sin n\theta \sin m\theta \, d\theta = \begin{cases} \pi \; ; \; n = m \\ 0 \; ; \; n \neq m \end{cases}$$

$$\int_{-\pi}^{\pi} \sin n\theta \cos m\theta \, d\theta = 0$$

$$(2.1.8)$$

$$\int_{-\pi}^{\pi} \sin(n\theta + \phi_n) \sin(m\theta + \phi_m) d\theta = \begin{cases} \pi ; & n = m \\ 0 ; & n \neq m \end{cases}$$

Let the periodic current waveform admit a Fourier series expansion of the form

$$i(\theta) = I_0 + \sum_{n=1}^{\infty} a_n \cos n\theta + b_n \sin n\theta$$

(2.1.9)

To determine the Fourier coefficients, first consider the dc term  $I_0$ . Integrating both sides of the Fourier series expansion (2.1.9) from  $-\pi$  to  $\pi$ , and taking the integral inside the summation, we get

$$\int_{-\pi}^{\pi} i(\theta) \ d\theta = \int_{-\pi}^{\pi} I_0 \ d\theta + \sum_{n=1}^{\infty} \left[ a_n \int_{-\pi}^{\pi} \cos n\theta \ d\theta + b_n \int_{-\pi}^{\pi} \sin n\theta \ d\theta \right]$$

(2.1.10)

From the auxiliary formulas (2.1.8), the integrals inside the summation vanish, leaving only

$$\int_{-\pi}^{\pi} i(\theta) \ d\theta = 2\pi I_0 \tag{2.1.11}$$

which is used to compute  $I_0$ . To determine the  $a_n$  coefficients, multiply both sides of the Fourier series expansion (2.1.9) by  $\cos m\theta$ , and then integrate from  $-\pi$  to  $\pi$ :

$$\int_{-\pi}^{\pi} i(\theta) \cos m\theta \ d\theta = I_0 \int_{-\pi}^{\pi} \cos m\theta \ d\theta + \sum_{n=1}^{\infty} \left[ a_n \int_{-\pi}^{\pi} \cos n\theta \cos m\theta \ d\theta + b_n \int_{-\pi}^{\pi} \sin n\theta \cos m\theta \ d\theta \right]$$

(2.1.12)

Referring to the auxiliary formulas (2.1.8), the first integral on the right side vanishes, and the last integral on the right side vanishes as well. The only integral that remains is the one beside  $a_n$ , which is nonzero only when n = m. Thus, we conclude

$$\int_{-\pi}^{\pi} i(\theta) \cos n\theta \, d\theta = a_n \pi \quad ; \quad n = 1, 2, 3, \dots$$

(2.1.13)

which is used to compute  $a_n$ . Similarly, to find a formula for  $b_n$ , multiply both sides of the Fourier series expansion (2.1.9) by  $\sin m\theta$ , and integrate from  $-\pi$  to  $\pi$ . In this case, we find

$$\int_{-\pi}^{\pi} i(\theta) \sin n\theta \ d\theta = b_n \pi \quad ; \quad n = 1, 2, 3, \dots$$

(2.1.14)

In summary, for a periodic function  $i(\theta)$  with period  $2\pi$ , the Fourier coefficients are given by the formulas

$$I_{0} = \frac{1}{2\pi} \int_{-\pi}^{\pi} i(\theta) d\theta$$

$$a_{n} = \frac{1}{\pi} \int_{-\pi}^{\pi} i(\theta) \cos n\theta d\theta$$

$$b_{n} = \frac{1}{\pi} \int_{-\pi}^{\pi} i(\theta) \sin n\theta d\theta$$

$$(2.1.15)$$

To evaluate the power factor, first we find the average power delivered to the load. The average power delivered is the time-average value of the instantaneous power taken over one line period. This gives

$$P = \frac{1}{2\pi} \int_{-\pi}^{\pi} \sqrt{2} V_{ideal} \sin \theta \left[ I_0 + \sum_{n=1}^{\infty} a_n \cos n\theta + b_n \sin n\theta \right] d\theta$$

(2.1.16)

where the current has been replaced by its Fourier series expansion (2.1.9). Bringing the integral inside the summation, we have the somewhat lengthy expression

$$P = \frac{V_{ideal}}{\sqrt{2}\pi} \left\{ I_0 \int_{-\pi}^{\pi} \sin\theta \ d\theta + \sum_{n=1}^{\infty} \left[ a_n \int_{-\pi}^{\pi} \sin\theta \cos n\theta \ d\theta + b_n \int_{-\pi}^{\pi} \sin\theta \sin n\theta \ d\theta \right] \right\}$$

(2.1.17)

However, the first integral vanishes, as does the one beside  $a_n$ . The last integral vanishes for every n except n=1. Hence, only the  $b_1$  term contributes to the average power delivered, which can now be written simply as

$$P = \frac{b_1}{\sqrt{2}} V_{ideal} \tag{2.1.18}$$

The quantity " $b_1/\sqrt{2}$ " has special meaning, and is given the name "ideal current." The reason that this name is chosen will become apparent at the end of this section. The average power delivered can now be written in terms of the ideal current

$$P = I_{ideal} V_{ideal} \tag{2.1.19}$$

and this allows the power factor to be written simply as the ratio

$$PF = \frac{I_{ideal}}{I_{rms}} \tag{2.1.20}$$

Next, we define what is meant by a harmonic. For any positive integer n, the n<sup>th</sup> harmonic is a function of the form

$$i_n(\theta) = \sqrt{2} I_n \sin(n\theta + \phi_n)$$

(2.1.21)

where  $I_n$  is the rms magnitude of the harmonic, and  $\phi_n$  is the phase. The frequency of the  $n^{\text{th}}$  harmonic is n times that of the fundamental (first) harmonic. Using a well-known formula from trigonometry, this harmonic may also be written

$$i_n(\theta) = \sqrt{2} I_n(\cos n\theta \sin \phi_n + \sin n\theta \cos \phi_n)$$

(2.1.22)

Now, by setting

$$a_n = \sqrt{2}I_n \sin \phi_n$$

and  $b_n = \sqrt{2}I_n \cos \phi_n$  (2.1.23)

we find that every harmonic of the form (2.1.21) can also be expressed

$$i_n(\theta) = a_n \cos n\theta + b_n \sin n\theta \tag{2.1.24}$$

Conversely, every function of this form is also a harmonic. To show this, we can solve equations (2.1.22) for  $I_n$  and  $\phi_n$ . The result is

$$I_n = \sqrt{\frac{a_n^2 + b_n^2}{2}}$$

and  $\phi_n = \tan^{-1} \frac{a_n}{b_n}$  (2.1.25)

The Fourier series expansion of the input current, equation (2.1.8), can now be written as the sum of harmonics of the form (2.1.21):

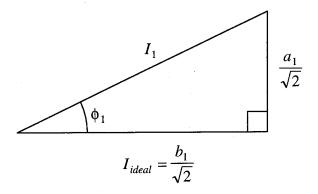

Figure 2.2: Geometric picture of the fundamental input current component.

$$i(\theta) = I_0 + \sum_{n=1}^{\infty} \sqrt{2} I_n \sin(n\theta + \phi_n)$$

(2.1.26)

Consider the fundamental harmonic. Its magnitude and phase angle are given by

$$I_1 = \sqrt{\frac{a_1^2 + b_1^2}{2}}$$

;  $\phi_1 = \tan^{-1} \frac{a_1}{b_1}$  (2.1.27)

These formulas provide the geometric picture of the fundamental component of the current shown in figure 2.2. From the picture, it is clear that

$$I_{ideal} = I_1 \cos \phi_1 \tag{2.1.28}$$

which allows the power factor (2.1.20) to be expressed as the product of two factors

$$PF = \frac{I_1}{I_{rms}} \cos \phi_1 \tag{2.1.29}$$

The first factor,  $I_1/I_{rms}$ , is called the "distortion factor." To see how the distortion factor gets its name, we need a result called Parseval's theorem. We can derive Parseval's theorem as follows: In the definition of rms current, equation (2.1.4), replace the function  $i(\theta)$  by its Fourier series expansion (2.1.8):

$$I_{rms}^{2} = \frac{1}{2\pi} \int_{-\pi}^{\pi} \left[ I_{0} + \sum_{n=1}^{\infty} \sqrt{2} I_{n} \sin(n\theta + \phi_{n}) \right]^{2} d\theta$$

(2.1.30)

If we now expand the square of the quantity in brackets, and then integrate term-byterm, only the integrals of products of like functions remain, while integrals of products of different functions vanish. This equation may therefore be written

$$I_{rms}^{2} = \frac{1}{2\pi} \left\{ \int_{-\pi}^{\pi} I_{0}^{2} d\theta + \sum_{n=1}^{\infty} \int_{-\pi}^{\pi} \left[ \sqrt{2} I_{n} \sin(n\theta + \phi_{n}) \right]^{2} d\theta \right\}$$

(2.1.31)

Using the last of the auxiliary formulas (2.1.8), this reduces to simply

$$I_{rms}^2 = I_0^2 + I_1^2 + I_2^2 + \dots {(2.1.32)}$$

also known as Parseval's theorem. Now consider the usual case when the dc component of the current  $I_0 = 0$ . In this case, the distortion factor,  $I_1/I_{rms}$ , can be expressed

$$DF = \frac{1}{\sqrt{1 + (THD)^2}}$$

(2.1.33)

where *THD* is the total harmonic distortion. It is clear from this result how distortion components present in the circuit act to degrade the power factor.

The second component of the power factor in equation (2.1.29),  $\cos \phi_1$ , accounts for the phase displacement of the fundamental component of the current relative to the voltage, and is therefore given the name "displacement factor." From figure 2.2, it is easily seen that the displacement factor may be expressed

$$\cos \phi_1 = \frac{I_{ideal}}{I_1} \tag{2.1.34}$$

It is clear that this ratio is unity only when the quadrature component of the fundamental current harmonic,  $a_1$ , is zero. It is also clear that this quadrature component is solely responsible for any degradation of the power factor due to phase displacement, and that the phase of all other harmonic components is irrelevant insofar as the power factor is concerned.

Summarizing the results of this section, the power factor, distortion factor, and displacement factor may be written as the ratios of currents

$$PF = \frac{I_{ideal}}{I_{rms}}$$

;  $DF = \frac{I_1}{I_{rms}}$ ;  $\cos \phi_1 = \frac{I_{ideal}}{I_1}$  (2.1.35)

and these expressions will be used to compute these quantities in later chapters. From the results of this section, it is easy to see that the following inequalities must hold

$$I_{rms} \ge I_1 \ge I_{ideal} \tag{2.1.36}$$

with equality only when the power factor is unity. Therefore, when the power factor is unity, we conclude that the current consists of a single component at the fundamental frequency, with no harmonics present, and with no phase displacement of the current relative to the voltage waveform. Thus, when the power factor is unity, the current waveform is determined, as given by

$$i(\theta) = \sqrt{2} I_{ideal} \sin \theta \tag{2.1.37}$$

and this is exactly the ideal current waveform. We stated in the beginning of this chapter that, in general, proportional current yields unity input power factor, as demonstrated by the case of the linear resistor. The present result shows, at least for the case of sinusoidal input voltage, that unity input power factor also implies that the input current is proportional, and that this current waveform is unique. Note that any current waveform for which  $b_1 = \sqrt{2}I_{ideal}$ , regardless of all other coefficients, causes exactly the same average power,  $P = I_{ideal}V_{ideal}$ , to be absorbed by the load. The ideal current waveform is, however, the smallest of all of these waveforms, in the rms sense.

It should be reemphasized that these results are based on the assumption of ideal sinusoidal input voltage, and are not correct in general. For the more general case of a non-sinusoidal periodic input source, the linear resistor example demonstrates that input current which is proportional to the input voltage implies unity input power factor. It can also be shown that the converse is true; i.e., that unity input power factor implies proportional voltage and current [1]. However, proof of this statement beyond the scope of this discussion. Nevertheless, we have proven this result for the specific case of sinusoidal input voltage, and conclude not only that proportional input current implies unity input power factor, but also that unity input power factor implies proportional (i.e., sinusoidal) input current.

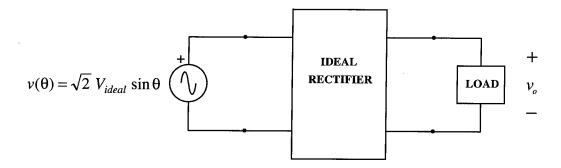

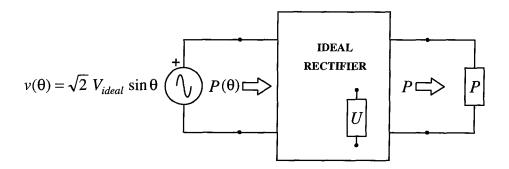

### 2.2 The Ideal Rectifier

The ideal rectifier system represents the goal of a real rectifier system, and therefore provides a basis against which the real system may be compared. The ideal rectifier itself is a two-port network within the ideal rectifier system, as shown in figure 2.2. In this idealization, the ac power source is assumed to be an ideal sinusoidal voltage source, from which the ideal rectifier, by definition, draws power with unity input power factor. Further, the ideal rectifier is assumed to be lossless, and therefore all of the ac power absorbed at the ac input port is converted to dc power at the dc output port. By "dc power," we mean only that both the current and the voltage at the dc output port are unipolar, and nothing is implied about the quality of these waveforms. The quality of the dc output waveforms is handled as a separate issue.

Figure 2.3: The ideal rectifier system consists of an ideal sinusoidal voltage source, the ideal rectifier, and a dc load.

Since the ideal rectifier absorbs power with unity input power factor, the current flowing into the ac port is exactly the ideal current given by equation (2.1.37). The average power absorbed at this port is therefore

$$P = I_{ideal} V_{ideal} (2.2.1)$$

Since the ideal rectifier is lossless, this power represents the output power as well. At any instant, the input current is proportional to the input voltage, and we may therefore write

$$v(\theta) = i(\theta)R_{ideal} \tag{2.2.2}$$

where the constant of proportionality,  $R_{ideal}$ , represents the impedance looking into the ac port of the ideal rectifier. This representation leads to the familiar static relationships for rms quantities

$$V_{ideal} = I_{ideal} R_{ideal} \quad ; \quad P = I_{ideal}^2 R_{ideal} \quad ; \quad P = \frac{V_{ideal}^2}{R_{ideal}}$$

(2.2.3)

In actual rectifier applications, the known quantities are usually the input voltage and the output (load) power. The ideal current and ideal resistance may be written in terms of these quantities as

$$I_{ideal} = \frac{P}{V_{ideal}}$$

;  $R_{ideal} = \frac{V_{ideal}^2}{P}$  (2.2.4)

These relations will prove to be useful in assessing the performance of non-ideal rectifier circuits, since they represent optimum values, and therefore serve as a basis for the normalization of theoretical or measured values. For example, input current harmonics can be normalized according to

$$i_n = \frac{I_n}{I_{ideal}} \tag{2.2.5}$$

Also, in the analysis of passive rectifier circuits, we will find it convenient to normalize the impedance of reactive elements within the rectifier circuit with respect to the ideal resistance  $R_{ideal}$ . Hence, we define

$$\rho = \frac{\left| Z(j\omega_l) \right|}{R_{ideal}} \tag{2.2.6}$$

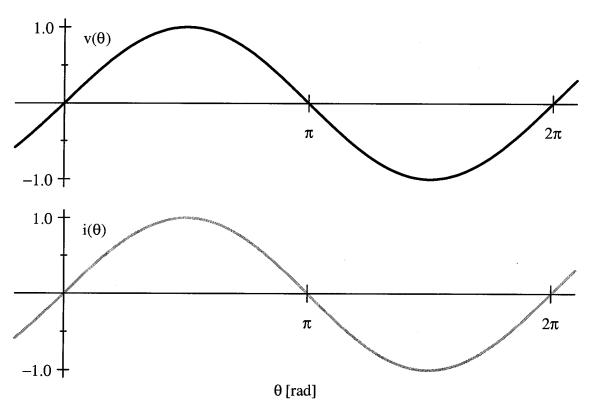

called the normalized impedance. This ratio is a measure of the size of the impedance of the reactive component, evaluated at the line frequency, relative to the input impedance of the ideal rectifier. In chapter 3, we will see how the performance characteristics of the passive rectifier circuits can be assessed as a function of this parameter alone. In addition, the time domain input voltage and input current waveforms can be normalized with respect to their ideal values. That is, the (sinusoidal) input voltage is normalized with respect to its peak value, according to

$$v(\theta) = \frac{v(\theta)}{V_p}$$

;  $V_p = \sqrt{2} V_{ideal}$  (2.2.7)

Similarly, the input current is normalized with respect to the peak value of the ideal current

$$i(\theta) = \frac{i(\theta)}{\sqrt{2}I_{ideal}}$$

(2.2.8)

This choice of normalization yields the picture shown in figure 2.4 for the ideal rectifier, where the normalized voltage and current waveforms are both ideal sinusoids with unity peak amplitude. When evaluating a real rectifier circuit, the quality of the input current waveform can be compared to that of the ideal rectifier, not only qualitatively by visually comparing the waveforms, but also quantitatively by using the ideal waveforms as a basis for the normalization of the non-ideal current waveform and its harmonics.

Figure 2.4: Normalized input voltage (black) and input current (grey) for the ideal rectifier.

### 2.3 Constant Power Load

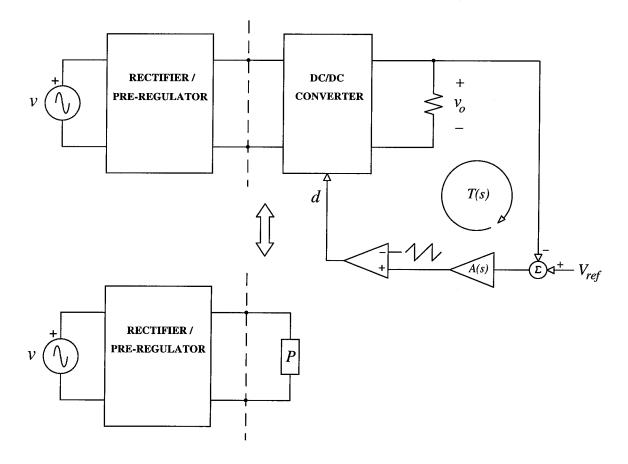

In the analysis of single phase rectifier circuits, we often make use of a two-terminal element called the constant power load. The constant power load is a simple way to model the effect of loading a rectifier/pre-regulator with a high-performance switching post-regulator, as shown in figure 2.5. In this configuration, the feedback loop of the post-regulator acts to fix the output voltage despite changes in voltage at the post-regulator input, thereby fixing not only the output voltage, but the output power as well. If we assume that the post-regulator is completely efficient and stores no energy, then the power flow into the post-regulator is equal to the output power, and thus appears to the rectifier/pre-regulator as a constant power load.

Figure 2.5: The effect of loading the rectifier/pre-regulator with a high performance switching regulator is simply modeled by a constant power load.

In arriving at this conclusion, there are at least three major assumptions necessary. First, it is assumed that the post-regulator feedback loop maintains the output voltage as constant. This assumption is valid at frequencies below the post-regulator loop gain crossover frequency, since crossover marks the frequency at which the feedback is no longer effective. In a well designed post-regulator, this frequency is typically about a decade below the switching frequency. Since, in the design of a rectifier/pre-regulator, we are concerned with circuit operation at the *line* frequency and harmonics thereof, this assumption is normally well justified.

The second assumption is that the post-regulator is completely efficient. This idealization is usually nearly true, with typical post-regulator efficiencies approaching 0.90 or even higher. If it is desired to include the effect of the efficiency, the constant power load is easily adjusted to accommodate this factor, provided the efficiency is independent of the operating point [17]. For the present purpose, we will assume that the post-regulator is completely efficient.

Finally, it is assumed that the post-regulator does not store energy. This, of course, is never justified in any switching regulator containing inductors or capacitors, since these energy storage elements are fundamental to the power conversion process itself. However, in the typical switching post-regulator, these components are sized to process power at the switching frequency, and have little effect on power flow when a small-signal disturbance is introduced at the line frequency, or at low harmonic frequencies thereof. In conclusion, the constant power load can be used to emulate the dc and low frequency loading effect of a high performance switching regulator.

#### 2.3.1 Terminal Characteristics

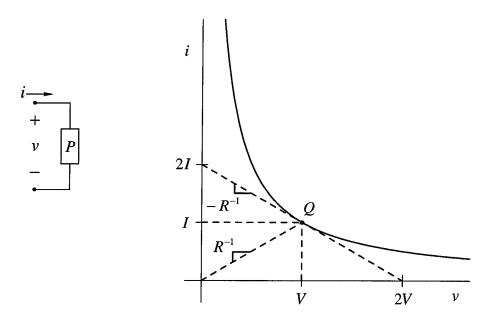

The large-signal and small-signal terminal characteristics of the constant power load are very different. Consider the constant power load shown in figure 2.6. Its terminal characteristics are defined by

$$P = iv (2.3.1)$$

Figure 2.6: The constant power load and its hyperbolic i-v characteristic.

and its i-v characteristic is the constant power hyperbola also shown in figure 2.6. In theory, a constant power load as defined by equation (2.3.1) could also operate in the third quadrant, or even in quadrants two and four as a constant power source, if P is allowed to be negative. However, the purpose here is to emulate the loading effect of the input to a dc/dc switching regulator, which accepts voltage of only one polarity. It is therefore assumed that the constant power load operates in only in the first quadrant. The operating range of a real switching regulator is further limited by its maximum and minimum operating voltages, beyond which it cannot operate. For simplicity however, we will assume that the switching regulator can operate anywhere along the constant power hyperbola in the first quadrant, and that its operating range is not exceeded.

If we denote the ratio of the voltage to the current, evaluated at the operating point, as the large-signal equivalent resistance R, we find

$$R \equiv \frac{V}{I} \bigg|_{Q} = \frac{V^2}{P} \tag{2.3.2}$$

and the small-signal equivalent resistance r can then be expressed

$$r \equiv \frac{dv}{di} \bigg|_{Q} = -R \tag{2.3.3}$$

The constant power load exhibits the large-signal behavior of a positive resistance with value R, and the small-signal behavior of a negative resistance with value -R. The slope of the line tangent to the i-v curve at point Q in figure 2.3 represents the small-signal conductance of the constant power load, which is actually the inverse of this small-signal resistance. These characteristics, both large and small-signal, are good approximations to the low-frequency large and small-signal characteristics of the input to a switching regulator [13]. Hence, for the purpose of studying the low frequency static and dynamic behavior of a rectifier/pre-regulator loaded by a high performance switching post-regulator, the constant power load can be used to emulate the loading effect of the high performance switching post-regulator.

# Chapter 3

# **Passive Rectifier Circuits**

In order to put in perspective the wide variety of known rectifier circuits, including both passive and active rectifier circuits, the performance and limitations of passive circuits need to be studied. Passive rectifier circuits consist of passive filter components and diodes only, and are therefore sometimes referred to simply as "passive filters." They offer the advantages of simplicity, durability, and even perhaps cost over active circuits, but disadvantages include the size and weight of passive filter components, the inability to actively control the output voltage, and the limitation of less than unity power factor. However, for a required level of performance, the advantages of a passive scheme may outweigh the disadvantages, making it a viable alternative in certain applications.

In this chapter, several practical passive rectifier circuits are analyzed to determine their level of performance. In each case, it is assumed that the passive rectifier circuit serves as a pre-regulator only, and is to be followed by a high performance switching post-regulator to form a complete ac/dc rectification system. Since the purpose here is to evaluate the pre-regulator portion of this system, the post-regulator is simply modeled by a constant power load, as described in section 2.3. By including the constant power load in the analysis, some surprising differences from similar analyses based on resistive loads are brought out.

The performance of a rectifier circuit can be quantified in various ways, including power factor, total harmonic distortion, and output voltage regulation. In this chapter, these measures are analyzed in detail, with results presented in graphical form. From these graphs, compliance with a particular performance specification or standard can be determined, and the results are easily compared with other passive or active approaches.

## 3.1 Capacitor Filter

The capacitor filter is actually a problem rather than a solution. Owing to the pulsed nature of the input current to this type of filter, the input current waveform is rich in harmonic content. In the past, the use of these filters was justified in devices that operated in the low power range, say several hundred watts or less, since the number of such devices was not large. In recent years, however, owing to the proliferation of this filter in many different types of electronic equipment, the net effect of having many of these low power devices operating on the same power line simultaneously is significant. Hence, it has become necessary to consider the harmonic content of the input current even for devices operating at low power levels.

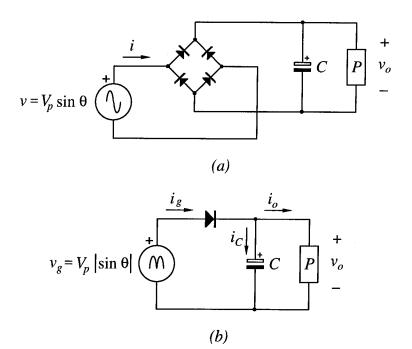

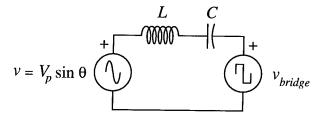

The capacitor filter is shown in figure 3.1(a), with its equivalent circuit in figure 3.1(b). The equivalent circuit is actually the output equivalent circuit, which properly represents the voltages and currents on the output side of the bridge rectifier. The actual input current i is found by "unfolding" the equivalent current waveform  $i_g$  through the bridge rectifier. This unfolding process is defined mathematically in appendix A.

Figure 3.1 Capacitor filter with constant power load; (a) circuit, and (b) equivalent circuit.

The analysis of this apparently simple circuit is complicated by the fact that the diodes are not conducting continuously, and the angles through which they conduct need to be determined. Several assumptions are in order before beginning the analysis. These are: (1) the input is an ideal sinusoidal voltage source; (2) the diodes are ideal, with zero voltage when forward-biased, and zero current when reverse-biased; (3) the capacitor is linear and ideal; and (4) the load is the constant power type described in section 2.3. To begin, consider the equivalent circuit of figure 3.1(b). The input voltage to this circuit is the rectified version of the ideal source voltage, given by

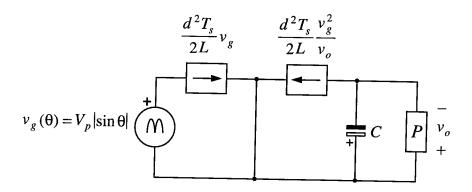

$$v_g(\theta) = V_p |\sin \theta| \tag{3.1.1}$$

where  $V_p$  is the peak value of the input voltage, related to the ideal sinusoidal input voltage (rms value) by

$$V_p = \sqrt{2} V_{ideal} \tag{3.1.2}$$

Since the period of the rectified line voltage is half of the line period, it is sufficient to consider only half of a line cycle to determine the steady-state behavior of the equivalent circuit of figure 3.1(b). Once the input current  $i_g$  is found for the equivalent circuit, the input current to the actual circuit is easily constructed by "unfolding" the current waveform  $i_g$  through the bridge rectifier. The input current to the equivalent circuit is

$$i_g = \begin{cases} i_C + i_o & \text{idiode conducting} \\ 0 & \text{idiode less} \end{cases}$$

(3.1.3)

where the capacitor current and the output current are given by

$$i_C(\theta) = \omega_l C \frac{d}{d\theta} v_C(\theta) \quad ; \quad i_o(\theta) = \frac{P}{v_C(\theta)}$$

(3.1.4)

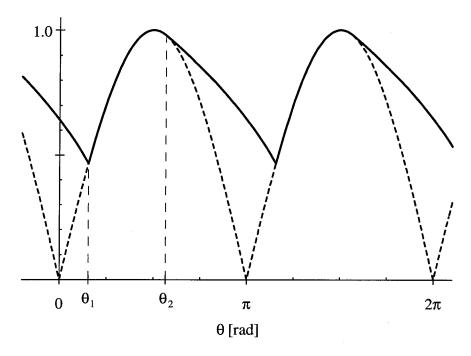

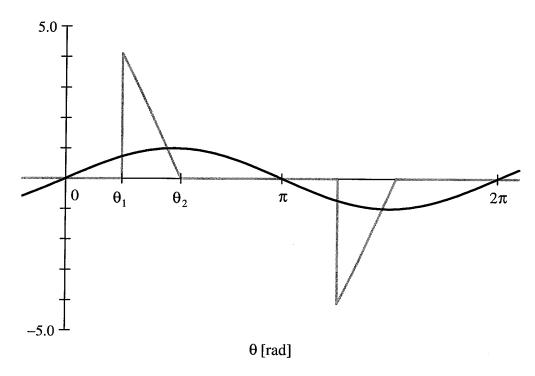

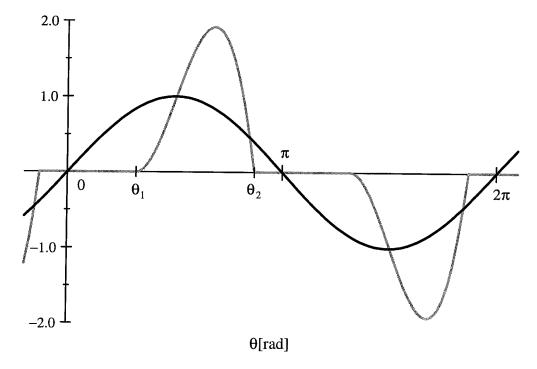

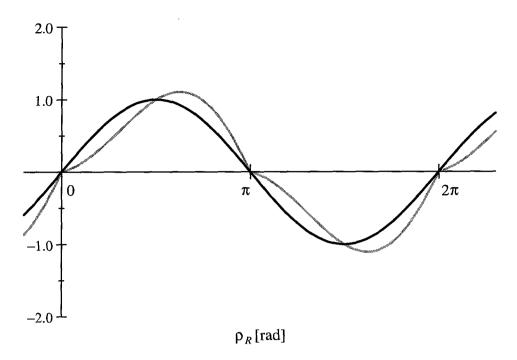

Consider the typical capacitor voltage waveform of figure 3.2. Let  $\theta_1$  be the angle at which diode conduction begins, and let  $\theta_2$  be the angle at which diode conduction terminates. Between these angles, the diode is conducting, and the input voltage and the capacitor voltage are therefore equal. The input current for the equivalent circuit over the entire half cycle  $0 \le \theta \le \pi$  is therefore

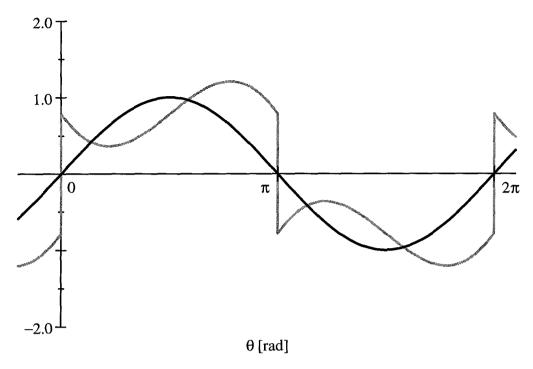

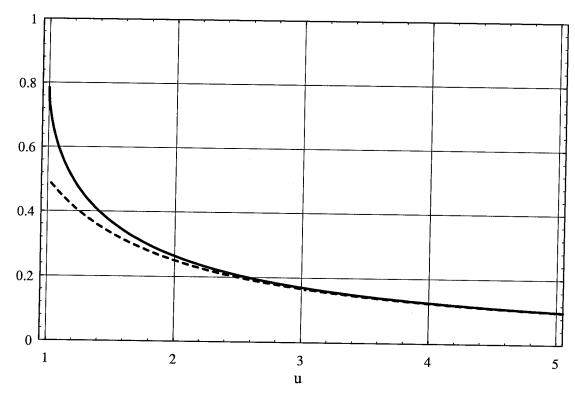

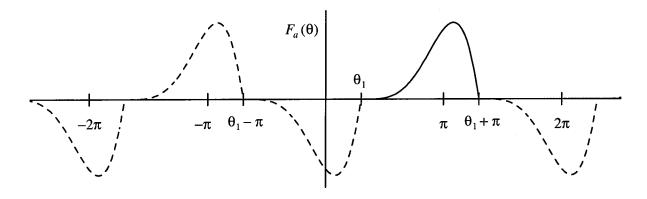

Figure 3.2: Normalized capacitor voltage waveform (solid) and rectified input voltage (dashed) for the capacitor input filter. ( $\rho_C = 0.16$ )

$$i_{g}(\theta) = \begin{cases} 0 & ; \quad 0 \le \theta < \theta_{1} \\ \omega_{l}CV_{p}\cos\theta + \frac{P}{V_{p}\sin\theta} & ; \quad \theta_{1} \le \theta \le \theta_{2} \\ 0 & ; \quad \theta_{2} \le \theta \le \pi \end{cases}$$

(3.1.5)

The current is discontinuous at  $\theta_1$ , when the diode turns on, but continuous at  $\theta_2$ , when the diode opens. Solving equation (3.1.5) for angle  $\theta_2$  gives

$$\sin 2\theta_2 + \rho_C = 0 \tag{3.1.6}$$

where the normalized impedance of the capacitor,  $\rho_C$ , combines the effects of known circuit quantities into one convenient parameter

$$\rho_C = \frac{\left| Z_C(j\omega_l) \right|}{R_{ideal}} = \frac{P}{\omega_l C V_{ideal}^2}$$

(3.1.7)

The solution of equation (3.1.6) is multi-valued and choosing the correct solution for  $\theta_2$  is a little tricky. Examining figure 3.2, the correct solution is the first solution that occurs after  $\theta = \pi/2$ , and is given by

$$\theta_2 = \frac{\pi}{2} + \frac{1}{2} \sin^{-1} \rho_C \tag{3.1.8}$$

where  $\sin^{-1} \rho_C$  denotes the principal value of the inverse sine function.

Next, consider the interval  $\theta_2 \le \theta \le \pi + \theta_1$ . During this interval, the diode is open and the output current is supported entirely by the capacitor. The capacitor voltage is described by the separable type first-order differential equation

$$\omega_l C \frac{dv_C}{d\theta} + \frac{P}{v_C} = 0 \tag{3.1.9}$$

subject to the initial condition at  $\theta = \theta_2$ :

$$v_C(\theta_2) = V_p \sin \theta_2 \tag{3.1.10}$$

Solving, we find the capacitor voltage for the interval  $\theta_2 \le \theta \le \pi + \theta_1$ :

$$v_C(\theta) = V_p \sqrt{\sin^2 \theta_2 - \rho_C(\theta - \theta_2)}$$

(3.1.11)

Angle  $\theta_1$  is still undetermined. Referring to figure 3.2, angle  $\pi + \theta_1$  occurs at the moment when the capacitor voltage waveform intercepts the rectified line voltage waveform. This leads to the transcendental relation

$$\sin^2 \theta_2 - \sin^2 \theta_1 - \rho_C (\pi + \theta_1 - \theta_2) = 0 \tag{3.1.12}$$

which, given angle  $\theta_1$ , is solved to find angle  $\theta_2$ , with  $\theta_1$  in the range  $0 < \theta_1 < \pi/2$ . Note that if  $\theta_1 = 0$  is allowed, the capacitor voltage falls to zero at the instant  $\theta = \theta_1$ . However, the capacitor voltage must not be allowed to fall to zero, because infinite output current will result in order to maintain constant power to the load. It is therefore necessary to restrict  $\theta_1$  to be strictly larger than zero. Hence, the case  $\theta_1 = 0$  defines a critical boundary of circuit operation. The corresponding critical value of  $\theta_2$  is found by solving equations (3.1.6) and (3.1.12) for angle  $\theta_2$  with  $\theta_1 = 0$ . This yields a transcendental equation for  $\theta_{2,crit}$ :

$$\tan \theta_{2,\text{crit}} + 2(\pi - \theta_{2,\text{crit}}) = 0 \implies \theta_{2,\text{crit}} \cong 1.9760 \text{ rad}$$

(3.1.13)

Again using equation (3.1.6), this value of  $\theta_2$  corresponds to a critical value for  $\rho_C$ , beyond which operation with a constant power load is rendered impossible:

$$\rho_{C,\text{crit}} = -\sin 2\theta_{2,\text{crit}} \cong 0.7246 \tag{3.1.14}$$

For values of  $\rho_C$  larger than  $\rho_{C,\text{crit}}$ , the capacitor voltage is allowed to fall to zero during the line cycle, rendering operation of the rectifier circuit with a constant power load impossible. The value  $\rho_C = \rho_{C,\text{crit}}$  thus represents the critical boundary for circuit operation with a constant power load, and in practical circuits,  $\rho_C$  should probably be kept well below this critical value.

It is interesting to note that operation of the capacitor filter with a resistive load exhibits no such critical boundary. With a resistive load, the interval during which the bridge rectifier is open is characterized by exponential decay of the capacitor voltage. This is in contrast to the discharge of the capacitor into a constant power load, described by the square-root relationship in equation (3.1.11). This difference is apparent by examining the capacitor voltage waveform in figure 3.2. The plot shows that with a constant power load, during the interval when the rectifier bridge is open, the capacitor voltage waveform actually curves *downward*, indicative of the increased output current demand necessary to maintain constant output power as the output voltage decreases. During the equivalent interval with a resistive load, the capacitor voltage decays exponentially, and theoretically never reaches zero regardless of the values chosen for the resistor and capacitor. Thus, with a resistive load, there may be large ripple, but there is no critical boundary like that for the constant power load.

#### 3.1.2 Performance Characteristics

In this section, it is shown that the performance characteristics such as ac/dc conversion ratio, ripple ratio, and power factor can be considered functions of a single parameter, namely the normalized impedance  $\rho_C$ . These performance characteristics are then plotted as a function of this parameter alone. Using these results, the applicability of a particular design can easily be assessed.

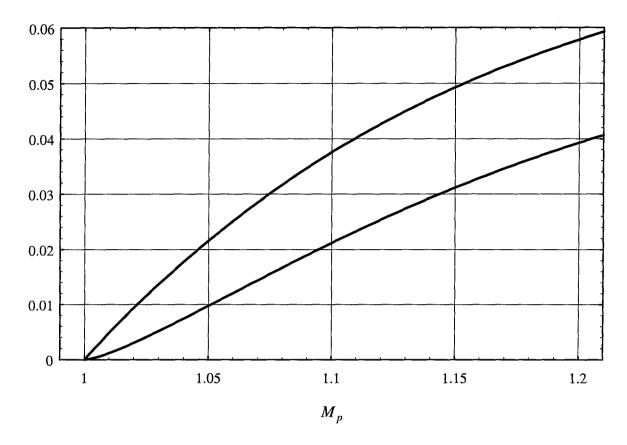

## **Conduction Angle**

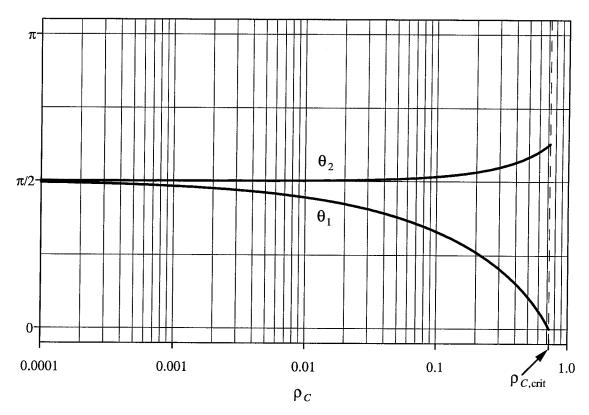

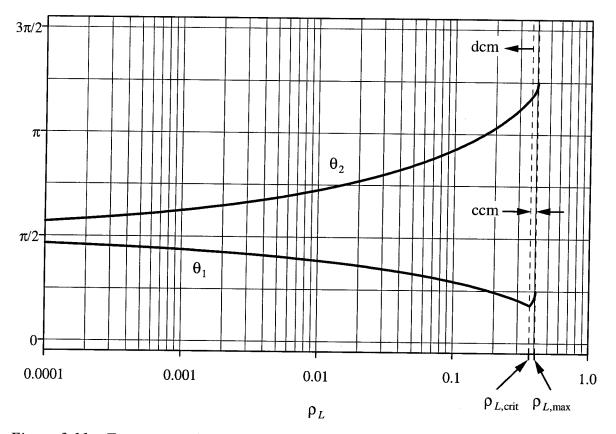

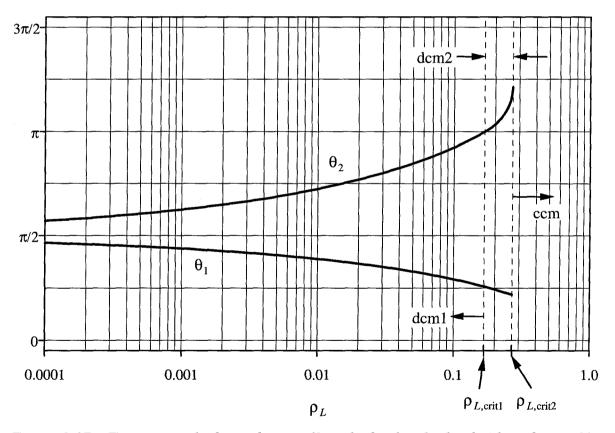

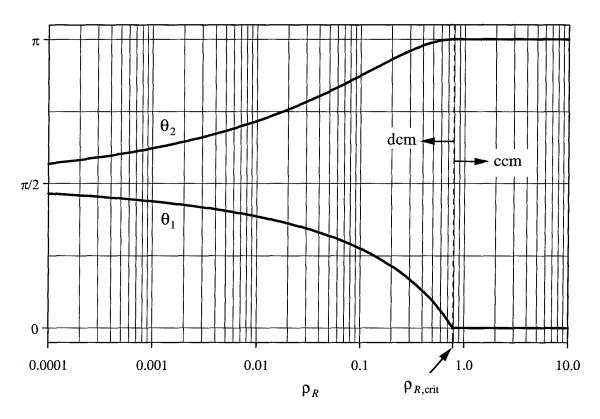

Angle  $\theta_2$  is expressed as an explicit function of the normalized impedance  $\rho_C$  in equation (3.1.8). In addition, angle  $\theta_1$  is related to angle  $\theta_2$  through the transcendental relationship (3.1.12), and thus may also be considered a function of  $\rho_C$ . Using these results, these angles are plotted in figure 3.3 as a function of  $\rho_C$ . Although the conduction angle is largest at the critical boundary, operation near this boundary is not recommended, because the output voltage ripple becomes too large for most practical applications.

# Ac/Dc Conversion Ratio, Ripple Ratio

With the angles  $\theta_1$  and  $\theta_2$  known, the ac/dc conversion ratio and output ripple voltage can be determined. We define the peak ac/dc conversion ratio as the ratio of the average dc output voltage to the peak line voltage

Figure 3.3: Angles  $\theta_1$  and  $\theta_2$  for the capacitor filter as a function of the normalized impedance  $\rho_C$ .

$$M_p \equiv \frac{V_o}{V_p} \tag{3.1.15}$$

The average output voltage is given by the integral

$$V_o = \frac{1}{\pi} \int_{\theta_1}^{\pi + \theta_1} v_C(\theta) d\theta$$

(3.1.16)

Over the interval of integration, the instantaneous capacitor voltage is given by

$$v_C(\theta) = \begin{cases} V_p \sin \theta & ; \quad \theta_1 \le \theta \le \theta_2 \\ V_p \sqrt{\sin^2 \theta_2 - \rho_C(\theta - \theta_2)} & ; \quad \theta_2 \le \theta \le \pi + \theta_1 \end{cases}$$

(3.1.17)

from which the peak ac/dc conversion ratio is found

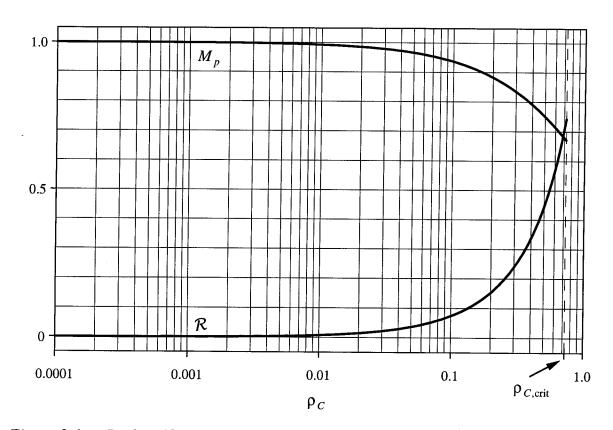

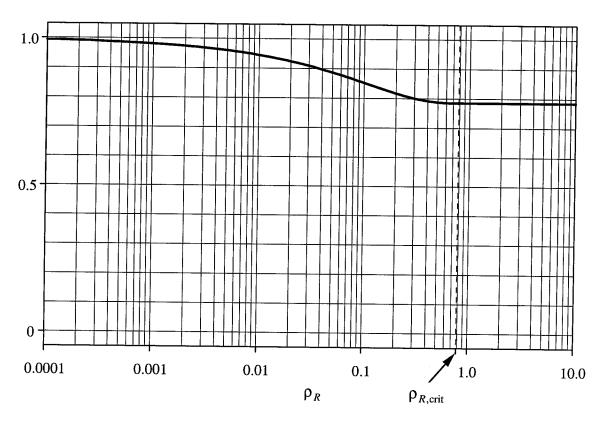

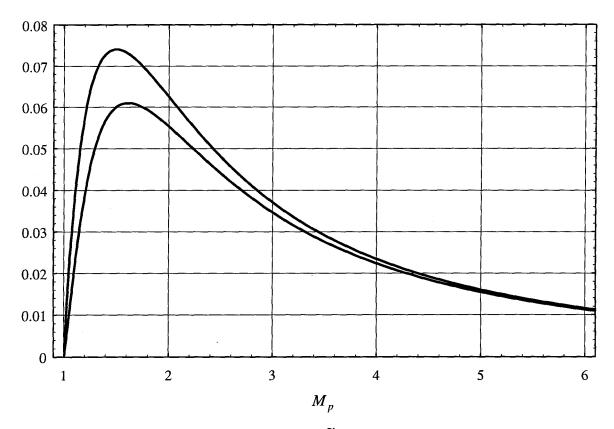

Figure 3.4: Peak ac/dc conversion ratio  $M_p$  and ripple ratio  $\mathcal R$  as a function of the normalized impedance  $\rho_{\mathcal C}$ .

$$M_{p} = \frac{1}{\pi} \left[ \cos \theta_{1} - \cos \theta_{2} + \frac{2}{3\rho_{C}} (\sin^{3} \theta_{1} - \sin^{3} \theta_{2}) \right]$$

(3.1.18)

and is plotted in figure 3.4 as a function of normalized impedance  $\rho_C$ . We define the "ripple ratio"  $\mathcal{R}$  as the ratio of one-half of the peak-to-peak output voltage ripple to the average dc output voltage

$$\mathcal{R} = \frac{v_{o,\text{max}} - v_{o,\text{min}}}{2V_o} \tag{3.1.19}$$

A little algebra gives the ripple ratio for the capacitor filter

$$\mathcal{R} = \frac{1 - \sin \theta_1}{2M_p} \tag{3.1.20}$$

which is also plotted in figure 3.4 as a function of the normalized impedance  $\rho_{\it C}$ .

#### **Power Factor and Harmonics**

In the preceding analysis, normalized impedance  $\rho_C$  was used to collect known circuit quantities into a single parameter, against which the desired circuit performance characteristics could be evaluated. In this section, it is shown that the line current harmonics and power factor can also be expressed as functions of this same parameter. The actual input current to the capacitor filter is the alternating periodic extension (see appendix A) of the input current to the equivalent circuit on the interval  $0 \le \theta \le \pi$ . For the equivalent circuit, the input current is given by equation (3.1.5), and may be written in terms the ideal current as

$$i_{g}(\theta) = \begin{cases} 0 & ; \quad 0 \leq \theta < \theta_{1} \\ I_{ideal} \sqrt{2} \left[ \frac{1}{\rho_{C}} \cos \theta + \frac{1}{2} \csc \theta \right] & ; \quad \theta_{1} \leq \theta \leq \theta_{2} \\ 0 & ; \quad \theta_{2} \leq \theta \leq \pi \end{cases}$$

(3.1.21)

where the ideal current, defined in chapter 2, is given by

$$I_{ideal} = \frac{P}{V_{ideal}} \tag{3.1.22}$$

Figure 3.5: Normalized input voltage (black) and input current (grey) for the capacitor filter. ( $\rho_C = 0.20$ )

Figure 3.5 shows a plot of the normalized input voltage and current for the capacitor filter with  $\rho_C = 0.20$ . This example exemplifies the poor performance of this filter.

The Fourier coefficients of the alternating periodic extension are computed using the results of appendix A. Fundamental coefficients  $a_1$  and  $b_1$  are given by

$$a_{1} = I_{ideal} \frac{\sqrt{2}}{\pi} \left\{ \frac{1}{\rho_{C}} (\theta_{2} - \theta_{1}) + \frac{1}{2\rho_{C}} (\sin 2\theta_{2} - \sin 2\theta_{1}) + \log_{e} \frac{\sin \theta_{2}}{\sin \theta_{1}} \right\}$$

$$b_{1} = I_{ideal} \sqrt{2}$$

(3.1.23)

The rms input current is given by

$$I_{rms} = I_{ideal} \frac{1}{\sqrt{2\pi}} \left[ \cot \theta_1 - \cot \theta_2 + \frac{2}{\rho_C^2} (\theta_2 - \theta_1) + \frac{4}{\rho_C} \log_e \frac{\sin \theta_2}{\sin \theta_1} + \frac{1}{2\rho_C^2} (\cot \theta_2 - \cot \theta_1 + \cos 3\theta_1 \csc \theta_1 - \cos 3\theta_2 \csc \theta_2) \right]^{\frac{1}{2}}$$

(3.1.24)

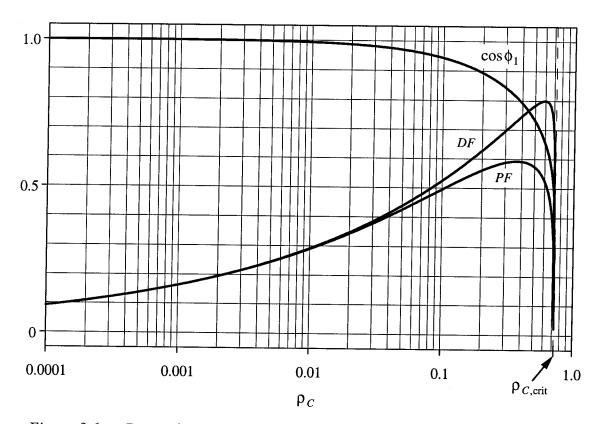

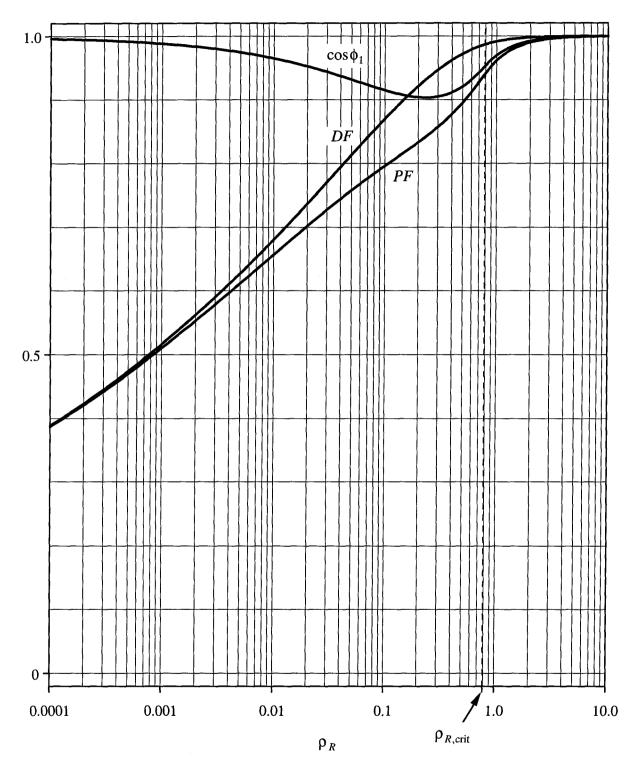

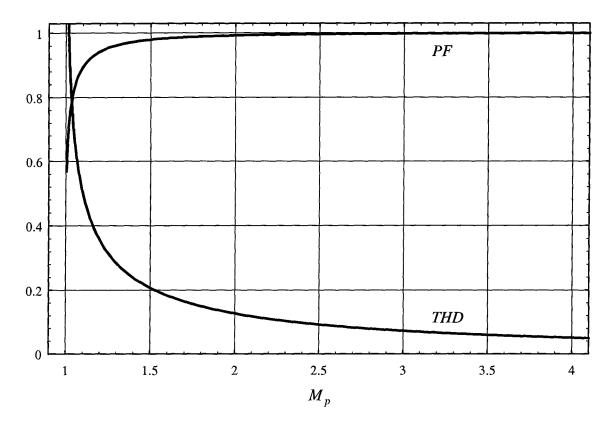

Using these results, the power factor, distortion factor, and displacement factor are computed using the results of chapter 2, and are plotted in figure 3.6 as a function of the normalized impedance  $\rho_C$ .

The normalized current harmonics are defined by the ratio

$$i_n \equiv \frac{I_n}{I_{ideal}} \tag{3.1.25}$$

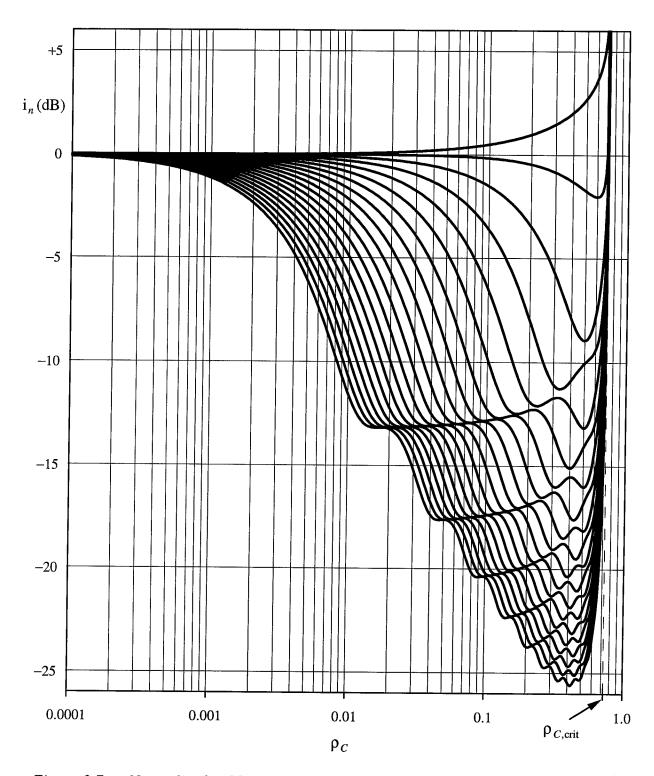

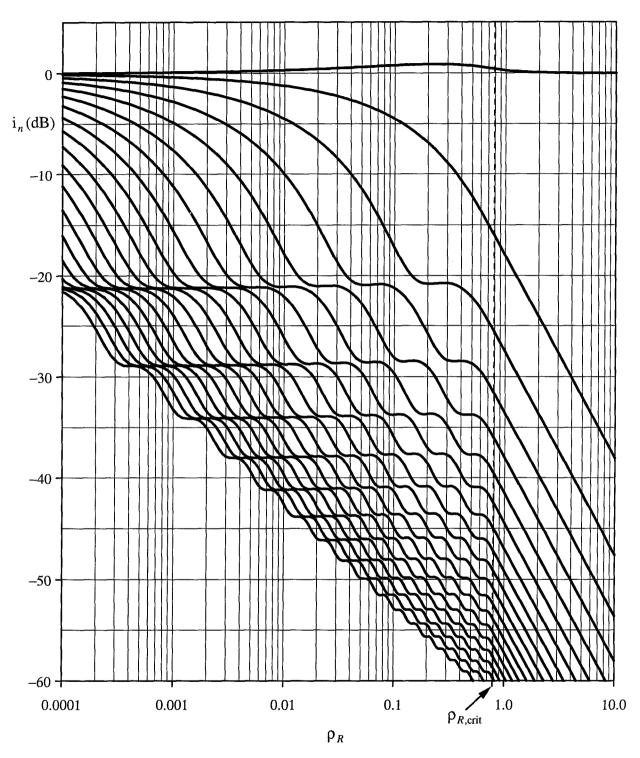

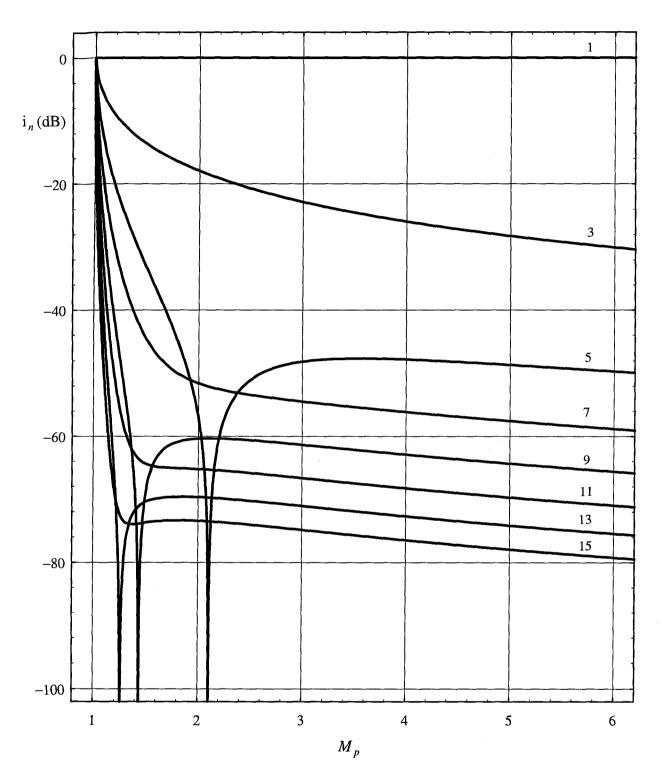

These harmonics are computed by finding the Fourier coefficients of the alternating periodic extension of the current waveform  $i_g$  over the interval  $0 \le \theta \le \pi$ . As shown in appendix A, the alternating periodic extension of a function contains only odd harmonics. Using these results, normalized odd current harmonics 1 through 39 are computed numerically and are plotted in figure 3.7, once again as a function of the normalized impedance  $\rho_C$ .

Figure 3.6: Power factor, distortion factor, and displacement factor as a function of normalized impedance  $\rho_C$  for the capacitor filter. Operation in the region beyond  $\rho_C = \rho_{C,\text{crit}}$  is not possible.

Figure 3.7: Normalized odd current harmonics 1-39 as a function of normalized impedance  $\rho_C$  for the capacitor filter. The topmost curve is the fundamental, and odd harmonics 3-39 progress downward in order.

## 3.2 Inductor Filter

The inductor filter consists of the same elements found in the capacitor filter, plus an inductor. The inductor improves performance by broadening the conduction angle of the bridge rectifier. The inductor filter offers an additional degree of freedom over the capacitor filter, since the inductor can be sized to provide quality ac input current, and the capacitor sized to provide quality dc output voltage. In the present analysis, however, the capacitor is assumed to be large enough that the output voltage may be considered constant, and only the effect of the inductor is considered.

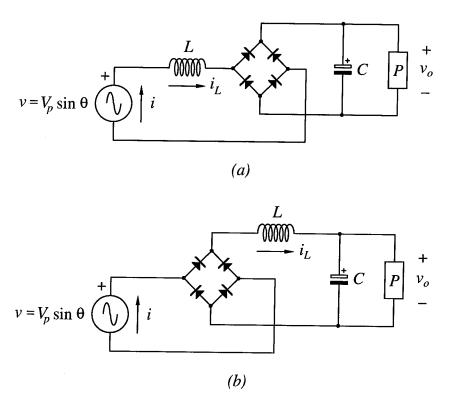

Two different inductor filter configurations are analyzed in the following sections, and are shown in figure 3.12. The behavior of these two configurations can be identical or very different, depending on the operating mode. The load-side inductor filter is frequently analyzed in the literature [1,30]. It is shown here, however, that the line-side inductor filter can offer a performance improvement, by offering reduced input current harmonics over a wider operating range. The simple explanation for this is that the

Figure 3.8: Two different inductor input filter configurations: (a) line-side inductor filter; and (b) load-side inductor filter.

inductor in the line-side inductor filter is connected adjacent to the input, thereby promoting continuity of the input current, and reducing the current harmonics.

The line-side filter does, however, suffer from one serious drawback which may explain why it is not often used. Consider a device employing a line-side inductor filter which is suddenly removed from the ac power source (i.e., unplugged). The inductor current path is suddenly interrupted, leaving no path for the inductor current to flow. In actual designs, however, a capacitor can be connected across the input both to correct the lagging phase angle, and to provide a path for the inductor current as well. The load-side filter, on the other hand, suffers from no such drawback, since the bridge rectifier provides the necessary path for the inductor current. However, even for the load-side inductor filter, it may be desirable to include the additional capacitor across the input, to correct the lagging phase angle thereby improving the circuit power factor.

Analysis of the inductor filters proceeds in much the same way as the capacitor filter. The assumptions here are: (1) the output capacitor is assumed sufficiently large so that the output voltage may be considered constant; (2) the input is an ideal sinusoidal voltage source; (3) the diodes are ideal, with zero voltage when forward-biased, and zero current when reverse-biased; (4) the inductor is ideal; and (5) the load is the constant power type of section 2.3.

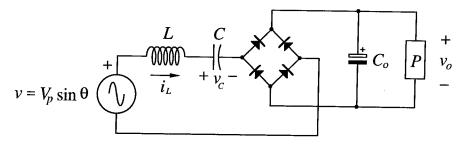

## 3.3 Line-Side Inductor Filter

The behavior of this filter depends on the operating mode. The line-side inductor filter possesses two distinct operating modes, one called the continuous conduction mode (ccm), and the other called the discontinuous conduction mode (dcm). In ccm, there is no finite interval within the line period over which the inductor current is zero. The inductor current in ccm is zero only at the distinct instants of the zero-crossings. In dcm, however, the inductor current remains zero during finite intervals within the line period.

#### 3.3.1 Discontinuous Conduction Mode

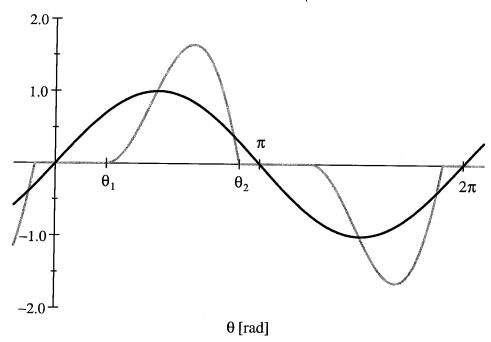

Operation in the discontinuous conduction mode (dcm) is characterized by finite intervals during which the inductor current is zero. Typical normalized input voltage

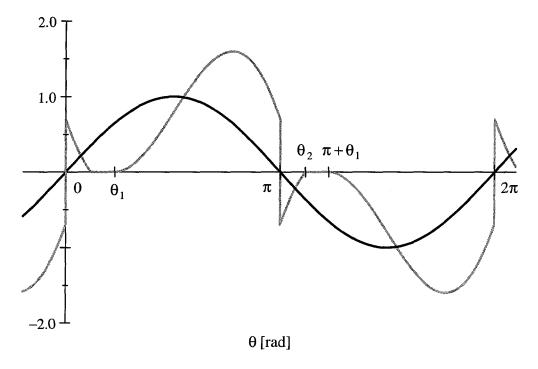

Figure 3.9: Normalized input current (grey) and input voltage (black) for the inductor input filter in discontinuous conduction mode ( $\rho_L = 0.063$ ).

and current waveforms in dcm are shown in figure 3.9. Assume that the circuit is operating in steady-state with constant dc output voltage  $V_o$ . Turn-on angle  $\theta_1$  occurs at the moment when the ac input voltage overtakes the dc output voltage. This gives

$$V_p \sin \theta_1 = V_o \tag{3.3.1}$$

where  $V_p$  is the peak value of the sinusoidal input voltage. The peak ac/dc conversion ratio in dcm is then simply

$$M_{p,\text{dcm}} = \sin \theta_1 \tag{3.3.2}$$

The fundamental i-v relationship for an inductor, as a function of the normalized time variable  $\theta$ , is given by

$$v_L(\theta) = \omega_l L \frac{d}{d\theta} i_L(\theta)$$

(3.3.3)

The inductor current on the interval  $\theta_1 \le \theta \le \theta_2$ , found by integrating the inductor voltage with respect to  $\theta$ , is given by

$$i_L(\theta) = \frac{V_p}{\omega_I L} \left[ \cos \theta_1 - \cos \theta - \sin \theta_1 (\theta - \theta_1) \right]$$

(3.3.4)

Substituting  $i_L(\theta_2) = 0$  yields a transcendental relationship between angles  $\theta_2$  and  $\theta_1$  valid in dcm

$$\cos \theta_1 - \cos \theta_2 - \sin \theta_1 (\theta_2 - \theta_1) = 0 \tag{3.3.5}$$

The critical angles for operation at the boundary between dcm and ccm can be found by finding the angle  $\theta_{1,crit}$ , for which angle  $\theta_{2,crit} = \theta_{1,crit} + \pi$ . Substitution in equation (3.3.5) gives

$$\theta_{1,\text{crit}} = \tan^{-1} \frac{2}{\pi} \tag{3.3.6}$$

The actual input current is the alternating periodic extension (see Appendix A) of the inductor current over the half-cycle  $\theta_1 \le \theta \le \pi + \theta_1$ . On this interval, the inductor current may be written in terms of the ideal current as

$$i_{L}(\theta) = \begin{cases} I_{ideal} \frac{\sqrt{2}}{\rho_{L}} \left[ \cos \theta_{1} - \cos \theta - \sin \theta_{1} (\theta - \theta_{1}) \right]; \ \theta_{1} \leq \theta \leq \theta_{2} \\ 0; \ \theta_{2} \leq \theta \leq \pi + \theta_{1} \end{cases}$$

(3.3.7)

where the normalized impedance  $\rho_L$  is given by

$$\rho_L = \frac{\left| Z_L(j\omega_l) \right|}{R_{ideal}} = \frac{\omega_l LP}{V_{ideal}^2}$$

(3.3.8)

Equating the average inductor current over the half cycle with the output current,

$$\frac{1}{\pi} \int_{\theta_1}^{\theta_2} i_L(\theta) d\theta = \frac{P}{V_o}$$

(3.3.9)

establishes a relationship between normalized impedance  $\rho_L$  and angles  $\theta_1$  and  $\theta_2$ :

$$\rho_L = \frac{2}{\pi} \sin \theta_1 \left[ \sin \theta_1 - \sin \theta_2 + (\theta_2 - \theta_1) \cos \theta_1 - \frac{1}{2} (\theta_2 - \theta_1)^2 \sin \theta_1 \right]$$

(3.3.10)

Substituting critical angles  $\theta_{1,crit}$  and  $\theta_{2,crit}$  in this equation gives the critical value of the normalized impedance  $\rho_L$  corresponding to operation at the boundary between dcm and ccm

$$\rho_{L,\text{crit}} = \frac{16}{\pi^3 + 4\pi} \cong 0.3672 \tag{3.3.11}$$

Hence, the filter operates in dcm with normalized impedance  $\rho_{\it L}$  in the range

$$0 < \rho_L < \frac{16}{\pi^3 + 4\pi} \implies \text{dcm}$$

(3.3.12)

and the range for which the filter operates in ccm remains to be determined.

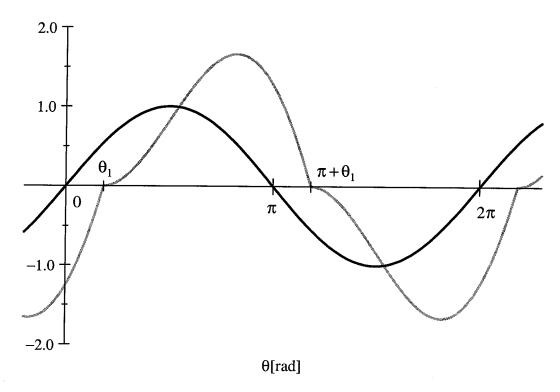

## 3.3.2 Continuous Conduction Mode

The continuous conduction mode (ccm) is characterized by inductor current which is not zero over any finite interval. The input current is zero only at the instants when it crosses zero, and it is at these instants that commutation of the bridge rectifier takes place. Typical normalized voltage and current waveforms in ccm are shown in figure 3.10. The inductor current over the interval  $\theta_1 \le \theta \le \pi + \theta_1$  is again found by integrating the fundamental *i-v* relationship for an inductor, equation (3.3.3), with respect to  $\theta$ :

$$i_L(\theta) = \frac{V_p}{\omega_l L} \int_{\theta_1}^{\theta} (\sin \theta' - M_p) d\theta'$$

(3.3.13)

The condition that the current is zero at  $\theta = \pi + \theta_1$  leads to the following relationship between the peak ac/dc conversion ratio and angle  $\theta_1$ , valid in ccm

$$M_{p,\text{ccm}} = \frac{2}{\pi} \cos \theta_1 \tag{3.3.14}$$

The inductor current over the interval  $\theta_1 \le \theta \le \pi + \theta_1$  can then be written in terms of the ideal current as

$$i_L(\theta) = I_{ideal} \frac{\sqrt{2}}{\rho_L} \left[ \cos \theta_1 - \cos \theta - \frac{2}{\pi} \cos \theta_1 (\theta - \theta_1) \right]$$

(3.3.15)

Figure 3.10: Normalized input current (grey) and input voltage (black) for the line-side inductor input filter operating in ccm ( $\rho_L = 0.38$ ).

Equating the average inductor current over the half cycle with the output current

$$\frac{1}{\pi} \int_{\theta_1}^{\pi + \theta_1} i_L(\theta) \, d\theta = \frac{P}{V_o}$$

(3.3.16)

establishes an explicit relationship between the normalized impedance  $\rho_L$  and angle  $\theta_1$ :

$$\rho_L = \frac{4}{\pi^2} \sin 2\theta_1 \tag{3.3.17}$$

From this result, it is clear that the maximum value of the normalized impedance  $\rho_L$  is

$$\rho_{L,\text{max}} = \frac{4}{\pi^2} \cong 0.4053 \tag{3.3.18}$$

If  $\rho_L$  exceeds this limit, the circuit cannot operate properly. That is, the circuit is rendered incapable of delivering the required constant power P to the load, limited by the large impedance of the inductor in series with the input voltage.

At the boundary between dcm and ccm, we found the lowest value of  $\rho_L$  for which the filter operates in ccm. The upper bound is given by (3.3.18), and the very narrow range of  $\rho_L$  for which the filter operates in ccm is therefore

$$\frac{16}{\pi^3 + 4\pi} \le \rho_L \le \frac{4}{\pi^2} \implies \text{ccm}$$

(3.3.19)

and the filter cannot operate at all for larger values of  $\rho_L$ . Hence, the line-side inductor filter exhibits a phenomenon similar to the one observed for the capacitor filter—a critical value of the normalized impedance beyond which operation is not possible. In both cases, the constant power load is responsible for this behavior, but the cause in each case is different: For the capacitor filter, the output capacitor voltage drooping to zero renders the filter incapable of supplying constant power; For the line-side inductor filter, it is the impedance of the inductor in series with the ac source which effectively limits the available power.

Like the capacitor filter, the line-side inductor filter does not exhibit this behavior if the load is resistive. For resistive loads, the line-side inductor filter continues to operate for any value of load resistor, but is still effectively power limited by the impedance of the inductor in series with the ac source. Hence, the maximum power point with resistive load is achieved by choosing a resistor whose value corresponds to the same large-signal dc operating point as the constant power load, with  $\rho_L = \rho_{L, max}$ . Using the results of this section, it can be shown that this resistor possesses the value

$$R_{\text{max power}} = \omega_l L \tag{3.3.20}$$

which, interestingly, is the identical result obtained by maximizing the ac power delivered to the resistor in a simple series linear L-R circuit driven by a sinusoidal ac voltage source.

### 3.3.3 Performance Characteristics

The performance characteristics of the line-side inductor filter, such as the ac/dc conversion ratio, input power factor, and input current harmonics, are again assessed as a function of the normalized impedance alone, just as was done for capacitor filter.

## **Conduction Angle**

In dcm, transcendental relation (3.3.5) is used to solve for  $\theta_2$  given  $\theta_1$ , with  $\theta_1$  in the range  $\theta_{1,\text{crit}} < \theta_1 < \pi/2$ . Equation (3.3.10) is then used to compute the normalized impedance  $\rho_L$ . In plotting, the process is reversed, and angles  $\theta_1$  and  $\theta_2$  are plotted as a function of normalized impedance  $\rho_L$ . In ccm, angle  $\theta_1$  is found by inverting equation (3.3.17), which gives

$$\theta_1 = \frac{1}{2} \sin^{-1} \left[ \frac{\pi^2}{4} \rho_L \right] \tag{3.3.21}$$

Angle  $\theta_2$  is then simply

$$\theta_2 = \pi + \theta_1 \tag{3.3.22}$$

The results for operation in both dcm and ccm are plotted in figure 3.11.

Figure 3.11 Turn-on angle  $\theta_1$  and turn-off angle  $\theta_2$  as a function of normalized impedance  $\rho_L$  for the line-side inductor filter. Operation in the region beyond  $\rho_L = \rho_{L,max}$  is not possible.

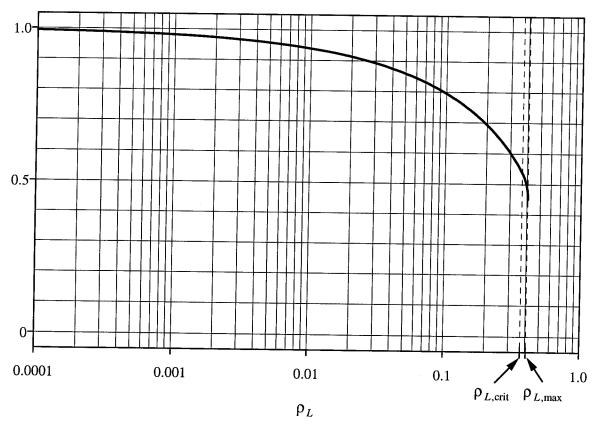

#### Ac/Dc Conversion Ratio

With angle  $\theta_1$  known as a function of the normalized impedance  $\rho_L$ , it is a simple matter to derive the ac/dc conversion ratio. In dcm, equation (3.3.2) gives the peak ac/dc conversion ratio as a function of angle  $\theta_1$ , which can then be plotted as a function of  $\rho_L$ . In ccm, the peak ac/dc conversion ratio is expressed as a function of  $\theta_1$  in equation (3.3.14), and angle  $\theta_1$  is expressed as a function of  $\rho_L$  in equation (3.3.20). Making use of a half-angle relation from trigonometry, the peak ac/dc conversion ratio in ccm can be written explicitly as a function of  $\rho_L$ :

$$M_{p,\text{ccm}} = \frac{\sqrt{2}}{\pi} \sqrt{1 + \sqrt{1 - \left(\frac{\pi^2}{4}\rho_L\right)^2}}$$

(3.3.23)

The results for operation in both dcm and ccm are plotted below in figure 3.12.

Figure 3.12: Peak ac/dc conversion ratio  $M_p$  as a function of normalized impedance  $\rho_L$  for the line-side inductor filter, for operation in both dcm and ccm.

#### **Power Factor and Harmonics**

The power factor and normalized input current harmonics can also be plotted as a function of normalized impedance  $\rho_L$ . First consider operation in dcm. The inductor current over the interval  $\theta_1 \leq \theta \leq \pi + \theta_1$  is given by equation (3.3.7). The input current is the alternating periodic extension of the inductor current on this interval. Using the results of appendix A, the Fourier coefficients of the input current in dcm are, in integral form

$$a_{n,\text{dcm}} = \begin{cases} \frac{2}{\pi} \int_{\theta_1}^{\theta_2} i_L(\theta) \cos n\theta \, d\theta \; ; \; n \text{ odd} \\ 0 \; ; \; n \text{ even} \end{cases}$$

$$b_{n,\text{dcm}} = \begin{cases} \frac{2}{\pi} \int_{\theta_1}^{\theta_2} i_L(\theta) \sin n\theta \, d\theta \; ; \; n \text{ odd} \\ 0 \; ; \; n \text{ even} \end{cases}$$

$$0 \; ; \; n \text{ even}$$

$$(3.3.24)$$

From these integrals, the Fourier coefficients of the fundamental component of the input current are given by

$$a_{1,\text{dcm}} = I_{ideal} \frac{\sqrt{2}}{\pi \rho_L} \left[ (\theta_1 - \theta_2) (1 + 2\sin\theta_1 \sin\theta_2) + \frac{1}{2} (\sin 2\theta_1 - \sin 2\theta_2) + 2\sin(\theta_2 - \theta_1) \right]$$

$$b_{1,\text{dcm}} = I_{ideal} \sqrt{2}$$

(3.3.25)

The rms input current in dcm is

$$I_{rms,dcm} = I_{ideal} \sqrt{\frac{2}{\pi}} \frac{1}{\rho_L} \left[ \frac{1}{3} (\theta_2 - \theta_1)^3 \sin^2 \theta_1 + (\theta_2 - \theta_1) \cos^2 \theta_1 + \frac{1}{2} (\theta_2 - \theta_1) + 2(\theta_2 - \theta_1) \sin \theta_1 \sin \theta_2 + \frac{1}{4} (\sin 2\theta_2 - \sin 2\theta_1) - 2 \sin(\theta_2 - \theta_1) - \frac{1}{2} (\theta_2 - \theta_1)^2 \sin 2\theta_1 \right]^{\frac{1}{2}}$$

$$(3.3.26)$$

Now consider operation in ccm. From appendix A, the Fourier coefficients of the input current are, in integral form

$$a_{n,\text{ccm}} = \begin{cases} \frac{2}{\pi} \int_{\theta_1}^{\pi+\theta_1} i_L(\theta) \cos n\theta \, d\theta \; ; \; n \text{ odd} \\ 0 \; ; \; n \text{ even} \end{cases}$$

$$b_{n,\text{ccm}} = \begin{cases} \frac{2}{\pi} \int_{\theta_1}^{\pi+\theta_1} i_L(\theta) \sin n\theta \, d\theta \; ; \; n \text{ odd} \\ 0 \; ; \; n \text{ even} \end{cases}$$

$$0 \; ; \; n \text{ even}$$

$$(3.3.27)$$

The Fourier coefficients of the fundamental component of the input current are then

$$a_{1,\text{ccm}} = I_{ideal} \frac{\sqrt{2}}{\rho_L} \left[ \frac{8}{\pi^2} \cos^2 \theta_1 - 1 \right]$$

$$b_{1,\text{ccm}} = I_{ideal} \sqrt{2}$$

(3.3.28)

and the rms input current is given by

$$I_{rms,ccm} = I_{ideal} \frac{1}{\rho_L} \sqrt{1 - \left[\frac{16}{\pi^2} - \frac{2}{3}\right] \cos^2 \theta_1}$$

(3.3.29)

where angle  $\theta_1$  is given as an explicit function of  $\rho_L$  in equation (3.3.21).

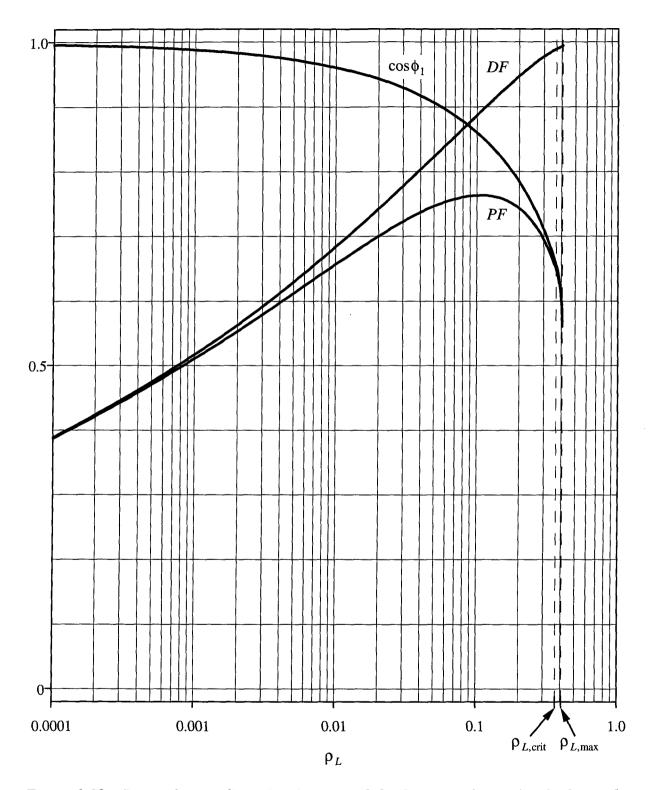

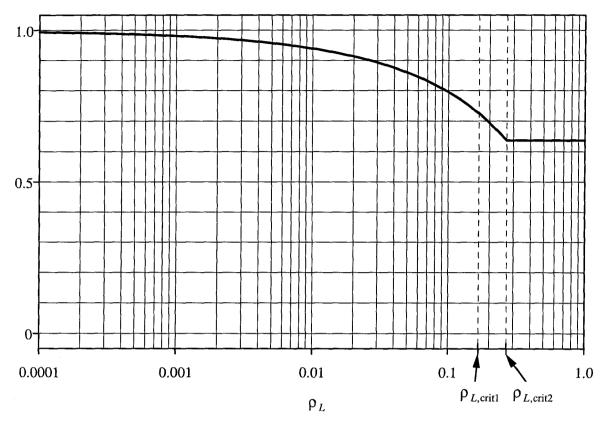

Using these results, the power factor, distortion factor, and displacement factor are computed using the results of chapter 2:

$$PF = \frac{I_{ideal}}{I_{rms}}$$

;  $DF = \frac{I_1}{I_{rms}}$ ;  $\cos \phi_1 = \frac{I_{ideal}}{I_1}$  (3.3.30)

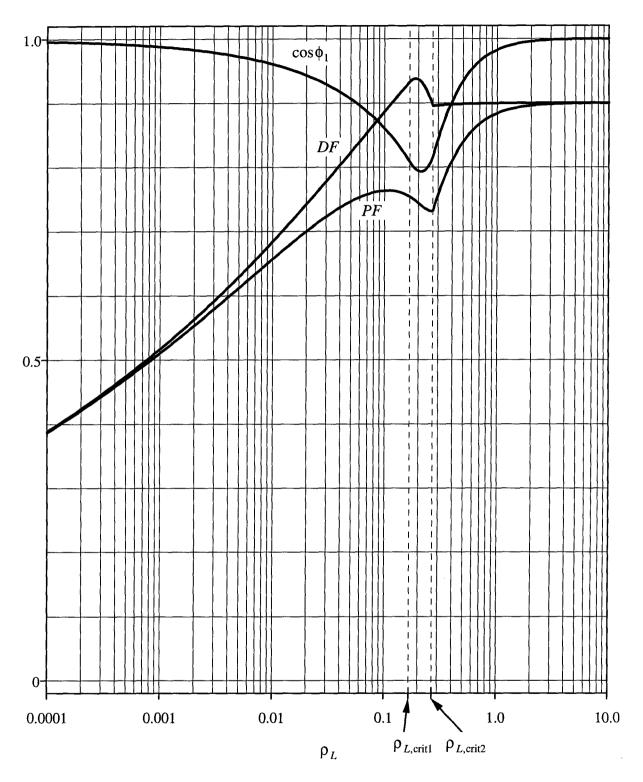

and these results in both operating modes are plotted in figure 3.13.

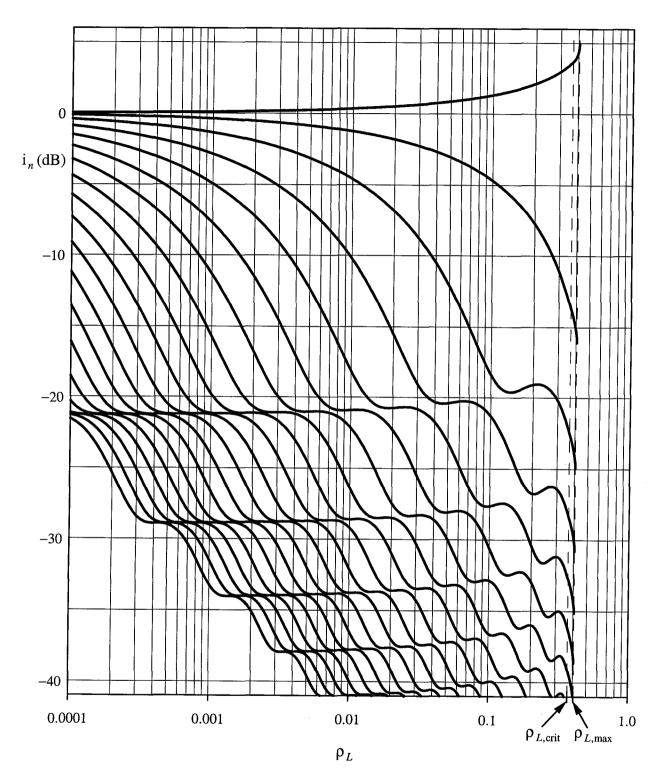

The normalized input current harmonics

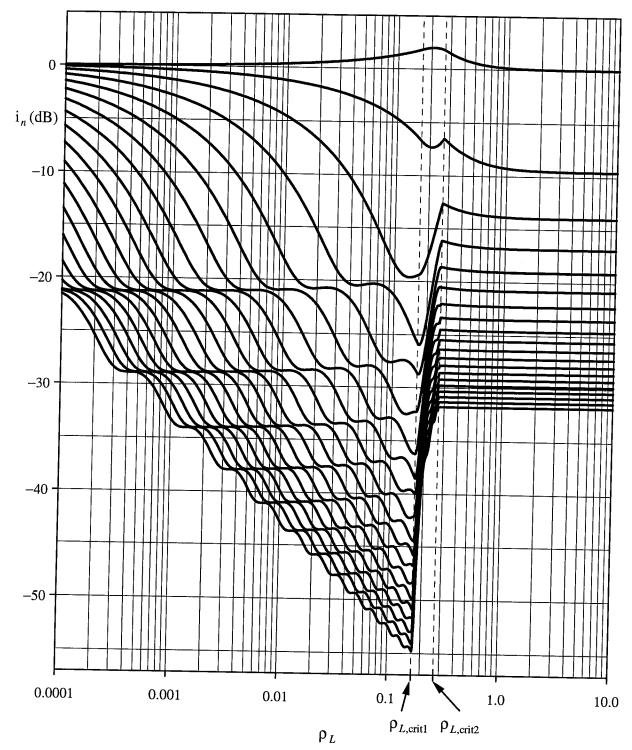

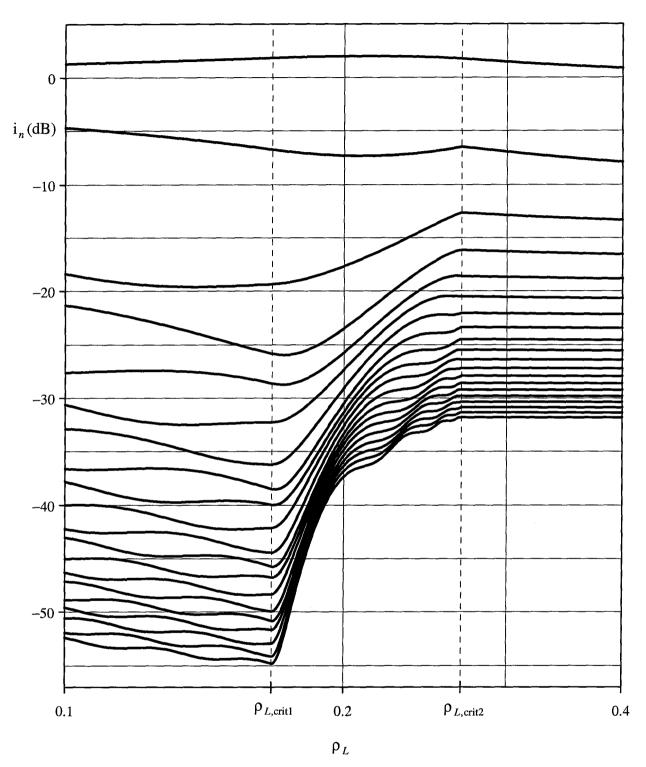

$$i_n = \frac{I_n}{I_{ideal}} \tag{3.3.31}$$

are computed by evaluating equations (3.3.24) and (3.3.27) numerically, and the results are plotted in figure 3.14 as a function of the normalized impedance  $\rho_L$ .

Figure 3.13: Power factor, distortion factor, and displacement factor for the line-side inductor filter as a function of normalized impedance  $\rho_L$ .