# The Class E/F Family of Harmonic-Tuned Switching Power Amplifiers

Thesis by

**Scott Kee**

In Partial Fulfillment of the Requirements

for the Degree of

Doctor of Philosophy

California Institute of Technology

Pasadena, California

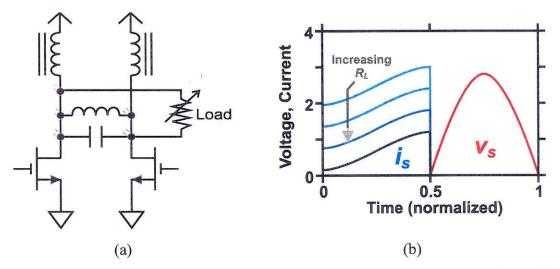

2002

(Defended Dec. 17<sup>th</sup>, 2001)

© 2002 Scott Kee

All Rights Reserved

# Acknowledgements

My advisor, Prof. David Rutledge, deserves special thanks for giving me the opportunity to study under his tutelage. Without his advice and guidance, and without the productive environment he has created in the MMIC group, this work would not have been possible. His keen insight and affable personality make working under him both enlightening and pleasurable. I would also like to thank the Jet Propulsion Laboratory, the Lee Center for Advanced Networking, the Army Research Office, National Science Foundation, and Xerox Corp. for their financial support of my research at Caltech.

I would like to acknowledge those at Caltech who have been of great assistance in this work. Ichiro Aoki deserves particular thanks, for without his inspiration this work would not have been begun and without his aid and support it would not have been successful. This topic of this thesis began as a result of discussions with Ichiro about his class-E amplifier design projects, and the demands imposed by his later designs helped push the investigations onward. I would also like to thank Prof. Ali Hajimiri, who along with Ichiro contributed to the development of the push/pull E/F<sub>odd</sub> switching amplifier idea. Kent Potter deserves much credit for his unfailing assistance and advice, having lent his experience and expertise on most of the various lab projects I have worked on here at Caltech. Finally, I would like to thank John Davis, who was of great assistance at the early stages of this work and helped me get by feet on the ground when I first began playing around with class E amplifiers in the lab.

This work would also not have been possible without the support of several people who have provided me with opportunities and inspiration in the past. The experience and knowledge I received working in Prof. Dan van der Weide's research group during my undergraduate studies at the University of Delaware have been invaluable in all of my

subsequent efforts. Much of the credit for any achievements I have been able to make also goes to my family, who have never failed to provide inspiration and support.

Finally, I would like to express my gratitude at having had the opportunity to meet and work with so many talented people during my time at Caltech. Such a group of interesting, friendly, ingenious, and exceptionally competent people one would be hard pressed to find anywhere else in the world. To all the members of the Rutledge and Hajimiri research groups I would particularly like to express my warmest regards and best wishes for the future.

## Abstract

A new family of harmonic-tuned switching amplifiers is introduced having the beneficial features of the class-E tuning while allowing improved performance to be achieved through additional harmonic tuning. This E/F family may be tuned to achieve the ZVS/ZdVS switching features characteristic of the class-E amplifier and, like the class-E tuning, accounts and compensates for the effect of the switch parallel capacitance. By tuning one or more overtones to the class-F<sup>-1</sup> tuning, however, the switching waveforms may be improved, lowering the peak voltage and reducing the RMS current. Additionally, the tolerance to large switch parallel capacitance is generally improved so that a larger switching device may be used, allowing reduction of the on-resistance. Due to these factors, the efficiency of E/F amplifiers is expected to exceed that of class E.

To demonstrate these advantages, methods of estimating the optimal efficiency of switching amplifiers using waveform properties are given. A general solution technique is then presented which allows the calculation of the ZVS tuning requirements and the resulting switching waveforms for an arbitrary harmonic tuning. Using these two tools, switching waveforms and resulting efficiency estimates are calculated for E/F amplifier tunings, which are then compared to class E.

Finally, potential application areas of the E/F technique are explored, and measured results of several first-generation E/F amplifiers are presented. Aside from efficiency benefits, E/F amplifiers also may achieve load-invariance, dual- and multi-band operation, high volumetric power densities, and efficient integrated circuit implementation using the Aoki distributed active transformer power combining structure.

## **Contents**

| Cl | napter 1: | Introduction                                         | I  |

|----|-----------|------------------------------------------------------|----|

|    | 1.1 Orga  | nnization of the Dissertation                        | 3  |

| Cl | hapter 2: | Efficiency of Power Amplifiers                       | 5  |

|    | 2.1 Amp   | olifier Loss Mechanisms                              | 6  |

|    | 2.1.1     | Drive Power Loss.                                    | 7  |

|    | 2.1.2     | Device Conduction Loss                               | 8  |

|    | 2.1.3     | Output Network Loss                                  | 9  |

|    | 2.2 Effic | ciency Measures                                      | 12 |

|    | 2.3 Som   | ne Important Relationships                           | 15 |

|    | 2.3.1     | Power Flow Relationships                             | 15 |

|    | 2.3.2     | Waveform Limitations: Power Consumption at Harmonics | 18 |

|    | 2.4 Effic | ciency of Common Amplifier Classes                   | 21 |

|    | 2.4.1     | Transconductance Amplifiers                          |    |

|    | 2.4       | 4.1.1 Class A                                        |    |

|    | 2.        | 4.1.2 Class AB, class B, class C                     |    |

|    | 2.4.2     | Saturated Transconductance Amplifiers                |    |

|    | 2.4.3     | Saturated Amplifiers with Harmonic Tuning            | 30 |

|    | 2.4.4     | Switching Amplifiers                                 | 34 |

| C  | hapter 3: | Switching Amplifier Properties                       | 39 |

|    | 3.1 Fun   | damental Operation                                   | 39 |

|    | 3.1.1     | Periodicity                                          | 40 |

|    | 3.1.2     | Waveform Constraints                                 | 40 |

|    | 3.1.3     | Treatment as a Time-Varying Linear Circuit           | 43 |

|    | 3.1.4     | Complementary Tunings                                |    |

|    | 3.2 Sca   | ling Properties                                      | 45 |

|    | 3.2.1     | Bias Scaling                                         | 45 |

|    | 3.2.2     | Impedance Scaling                                    |    |

| *  | 3.2.3     | Arbitrary Scaling: Concept of a "Tuning"             | 47 |

|    | 3.3 Swi   | tching Losses                                        | 48 |

|    | 3.3.1     | Turn-On Losses and ZVS Switching                     |    |

|    | 3.3.2     | Turn-Off Losses and ZCS Switching                    |    |

|    | 3.3.3     | Known Switching Amplifier Tunings                    |    |

|    | 3.3.4     | Class-D Amplifiers                                   | 51 |

| 3.3.4.1 Class-D                                                                    | 52           |

|------------------------------------------------------------------------------------|--------------|

| 3.3.4.2 Class-D <sup>-1</sup> ZVS Amplifier                                        |              |

| 3.3.5 Class-E Amplifiers                                                           |              |

| 3.3.5.1 Class E                                                                    |              |

| 3.3.5.2 Even Harmonic Resonant Class-E 3.3.5.3 Class-E <sup>-1</sup> ZCS Amplifier |              |

| 3.3.3.5 Class-E ZCS Ampiniei                                                       | 01           |

| Chapter 4: Predicting Switching Amplifier Po                                       | erformance62 |

| 4.1 Switch & Resistor Model                                                        | 63           |

| 4.1.1 Device technology model                                                      | 66           |

| 4.1.2 Efficiency Estimation                                                        | 67           |

| 4.2 Waveform Figures of Merit                                                      | 70           |

| 4.2.1 Peak Amplitude Limited Output Power                                          | 70           |

| 4.2.2 Efficiency Figures of Merit                                                  | 72           |

| 4.2.2.1 Device Size Limited Drain Efficien                                         | •            |

| 4.2.2.2 Capacitance Limited Drain Efficien                                         | •            |

| 4.2.2.3 Gain Limited Power Added Efficier                                          |              |

| 4.2.2.4 Capacitance Limited Power Added                                            |              |

| 4.3 Summary                                                                        | 81           |

| <b>Chapter 5: Predicting Switching Amplifier W</b>                                 | /aveforms83  |

| 5.1 Generalized Switching Amplifier                                                | 84           |

| 5.2 Solution Method                                                                | 86           |

| 5.3 Real-Valued Linear Algebra Implementation                                      | 91           |

| 5.3.1 Finding the Waveforms                                                        |              |

| 5.3.2 Solving for a Given I <sub>DD</sub>                                          |              |

| 5.3.3 Solving for a Given V <sub>DC</sub>                                          | 96           |

| 5.4 Determining a ZVS Tuning                                                       |              |

| 5.5 Other Applications                                                             |              |

|                                                                                    |              |

| Chapter 6: The E/F Switching Amplifier Fan                                         | nily104      |

| 6.1 Desired Properties                                                             | 105          |

| 6.2 The Class E/F Concept                                                          | 106          |

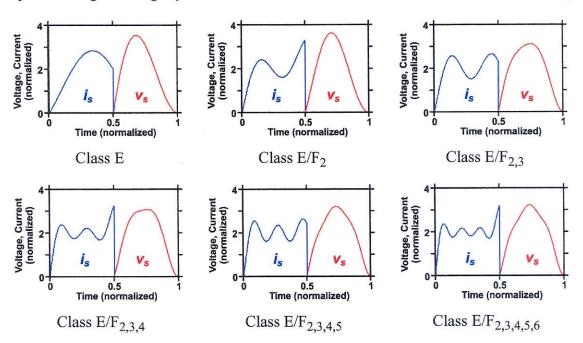

| 6.3 Class E/F Waveforms                                                            | 107          |

| 6.3.1 Individual Tuned Harmonics                                                   | 110          |

| 6.3.2 Odd Harmonics                                                                | 111          |

| 6.3.3 Even Harmonics                                                               | 112          |

|    | 6.3.4    | Complete N-Harmonic Tunings                           | 112 |

|----|----------|-------------------------------------------------------|-----|

|    | 6.4 Clas | ss E/F Performance Figures of Merit                   | 114 |

|    | 6.5 Prac | ctical Strategies for Implementing E/F                | 116 |

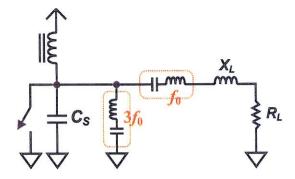

|    | 6.5.1    | Direct Implementations                                | 116 |

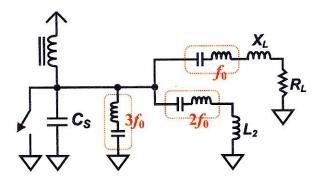

|    | 6.5.2    | Multi-Resonant Implementations                        | 117 |

|    | 6.5.3    | Symmetric Push/Pull Implementations                   | 117 |

|    | 6.6 Clas | ss F/E ZCS Amplifiers                                 | 121 |

|    | 6.7 Upo  | lated Switching Amplifier Taxonomy                    | 122 |

| Ch | apter 7: | The E/F <sub>odd</sub> Switching Amplifier Family     | 124 |

|    | 7.1 Clas | ss E/F <sub>odd</sub> Amplifiers                      | 124 |

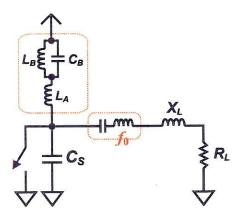

|    | 7.1.1    | E/F <sub>odd</sub> Concept                            | 124 |

|    | 7.1.2    | E/F <sub>odd</sub> Waveform Solution Technique        | 126 |

|    | 7.2 Cla  | ss E/F <sub>odd</sub> Family                          | 133 |

|    | 7.2.1    | Class E/F <sub>odd</sub> Family Waveforms             | 136 |

|    | 7.2.2    | Class E/F <sub>odd</sub> Performance Figures of Merit | 138 |

| Ch | apter 8  | New Opportunities and Applications                    | 140 |

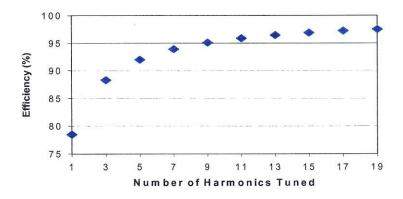

|    | 8.1 Imp  | proved Efficiency                                     | 140 |

|    | 8.2 Hig  | her Frequency                                         | 142 |

|    |          | id-Invariant ZVS Amplifiers/Inverters                 |     |

|    | 8.4 Free | quency Diversity                                      | 144 |

|    | 8.4.1    | Dual- and Multi-Band ZVS Amplifiers                   |     |

|    | 8.4.2    | Wideband ZVS Amplifiers                               |     |

|    | 8.5 Inte | grated Circuit Implementation                         | 150 |

|    | 8.5.1    | Circular Geometry / DAT                               | 151 |

|    | 8.6 Hig  | h Power HF/VHF Implementations                        | 155 |

|    | 8.6.1    | 7-MHz, 1-kW Class E/F <sub>2,odd</sub> Prototype      |     |

|    | 8.6.2    |                                                       |     |

|    | 8.7 Cor  | npact Implementations                                 | 163 |

## **List of Figures**

| Chapter 1: | Introduction              |              |

|------------|---------------------------|--------------|

| Chapter 2: | <b>Efficiency of Powe</b> | r Amplifiers |

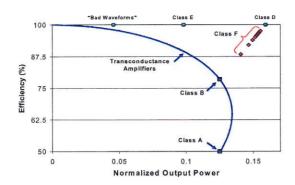

|   | rigure 2.1.  | fier efficiency.                                                                                        |           |

|---|--------------|---------------------------------------------------------------------------------------------------------|-----------|

|   | Figure 2.2:  | Power flow in a generalized power amplifier.                                                            | 7         |

|   | Figure 2.3:  | Simple device model disregarding feedback parasitics.                                                   |           |

|   | Figure 2.4:  | Impedance transformer component.                                                                        | .11       |

|   | Figure 2.5:  | Generalized single-transistor power amplifier.                                                          | .16       |

|   | Figure 2.6:  | Typical active device output port characteristics                                                       | .22       |

|   | Figure 2.7:  | Transconductance amplifier circuit topology                                                             | .23       |

|   | Figure 2.8:  | Class-A drain waveforms and load line                                                                   | .24       |

|   | Figure 2.9:  | Class-A/B waveforms and load line.                                                                      | .26       |

|   | Figure 2.10: | Class-B waveforms and load line.                                                                        | .26       |

|   | Figure 2.11: | Class-C waveforms and load line.                                                                        | .26       |

|   | Figure 2.12: | Drain efficiency and output power vs. conduction angle                                                  | .27       |

|   | Figure 2.13: | Saturated class-A waveforms and load-line                                                               | .29       |

|   | Figure 2.14: | Saturated class-B waveforms and load-line.                                                              | .29       |

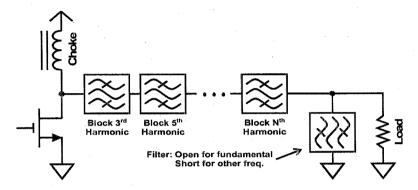

|   | Figure 2.15: | Class-F circuit conceptual implementation.                                                              | .31       |

|   | Figure 2.17: | Efficiency of maximally-flat voltage waveform class-F amplifiers                                        | .32       |

|   | Figure 2.16: | Maximally flat class-F waveforms and load-lines.                                                        | 32        |

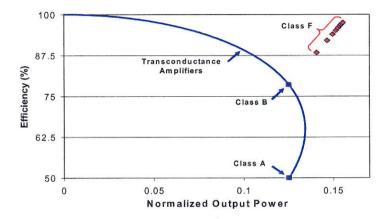

|   | Figure 2.18: | Efficiency vs. normalized output power for transconductance and class-F amplifiers.                     | 33        |

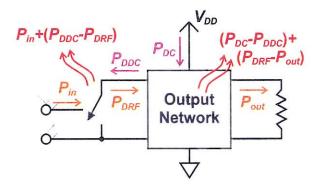

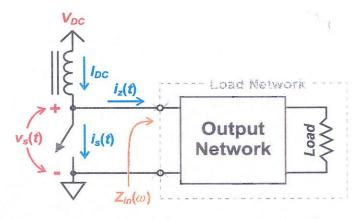

|   | Figure 2.19: | Generalized switching amplifier, showing power flow.                                                    | 35        |

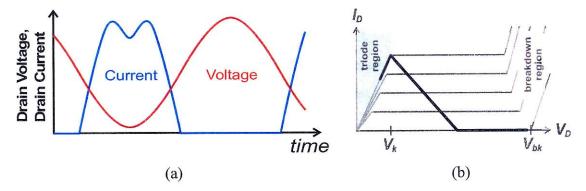

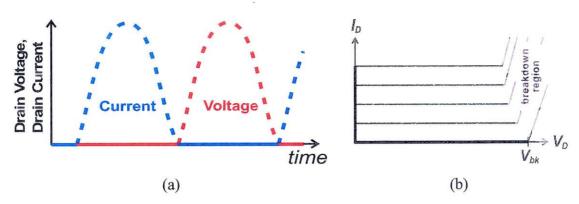

|   | Figure 2.20: | Switching amplifier conceptual waveforms and load-line                                                  | 36        |

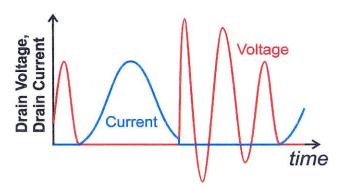

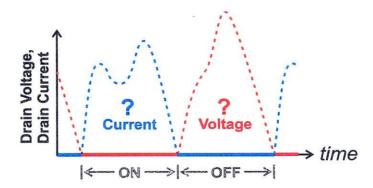

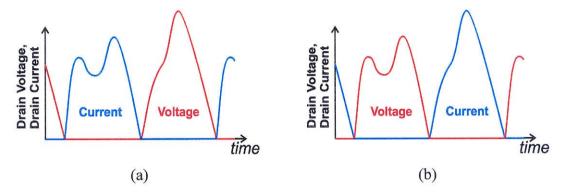

|   | Figure 2.21: | Undesirable switching amplifier waveforms.                                                              | 37        |

|   | Figure 2.22: | Efficiency vs. normalized output power for transconductance, class-<br>and several switching amplifiers |           |

| C | hapter 3: Sv | vitching Amplifier Properties                                                                           |           |

|   | Figure 3.1:  | Generalized switching amplifier.                                                                        | 39        |

|   | Figure 3.2:  | Switching amplifier waveforms after applying switching constraints                                      | <b>5.</b> |

|   |              |                                                                                                         | 42        |

|   | Figure 3.3:  | Dual amplifier waveforms.                                                                               | 45        |

| • |              |                                                                                                         |           |

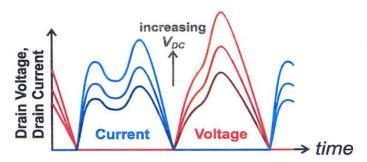

| Figure 3.4:   | Effect of bias scaling in switch voltage and current waveforms46                                               |

|---------------|----------------------------------------------------------------------------------------------------------------|

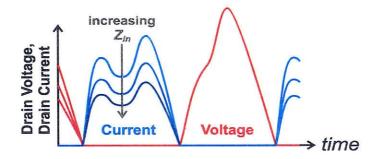

| Figure 3.5:   | Effect of impedance scaling in switch voltage and current waveforms.                                           |

| •             | 47                                                                                                             |

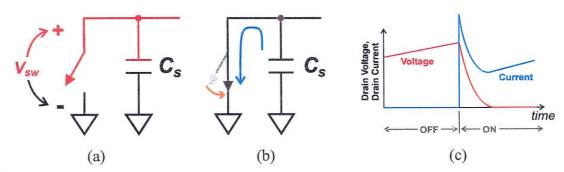

| Figure 3.6:   | Capacitive discharge loss                                                                                      |

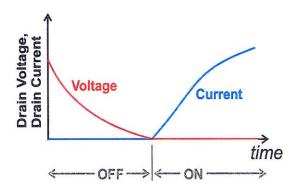

| Figure 3.7:   | ZVS turn-on transition50                                                                                       |

| Figure 3.8:   | Class-D amplifier circuit and waveforms                                                                        |

| Figure 3.9:   | Class-D <sup>-1</sup> amplifier circuit and waveforms54                                                        |

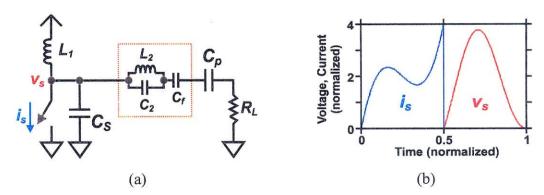

| Figure 3.10:  | Class-E circuit topology                                                                                       |

| Figure 3.11:  | Class-E power amplifier waveforms                                                                              |

| Figure 3.12:  | Second harmonic resonant class-E amplifier59                                                                   |

| Chapter 4: Pr | edicting Switching Amplifier Performance                                                                       |

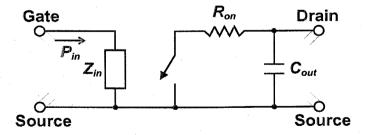

| Figure 4.1:   | Switch & resistor model for a FET switching device63                                                           |

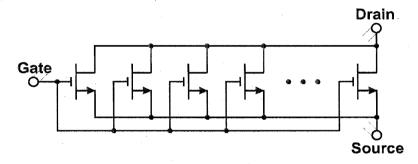

| Figure 4.2:   | Power device as a parallel connection of small "cell" devices66                                                |

| Chapter 5: Pr | edicting Switching Amplifier Waveforms                                                                         |

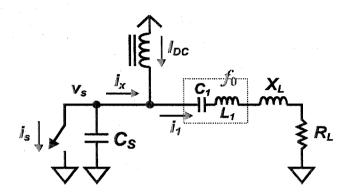

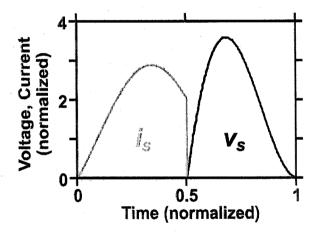

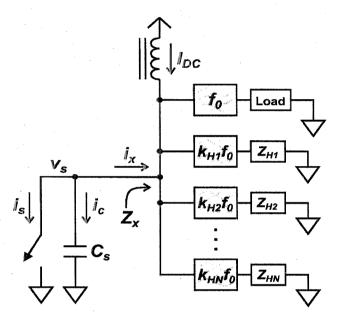

| Figure 5.1:   | Generalized switching amplifier with switch parallel capacitance and harmonic tuning at selected frequencies85 |

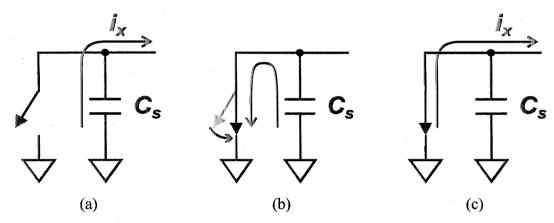

| Figure 5.2:   | Commutation behavior of the harmonic filter current $i_x$ 88                                                   |

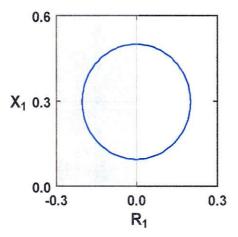

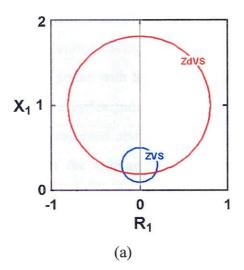

| Figure 5.3:   | Class-E ZVS circle in the (normalized) impedance plane100                                                      |

| Figure 5.4:   | Class-E ZVS and ZdVS circles in the (normalized) impedance plane and close-up of the ZVS circle102             |

| Chapter 6: Th | ne E/F Switching Amplifier Family                                                                              |

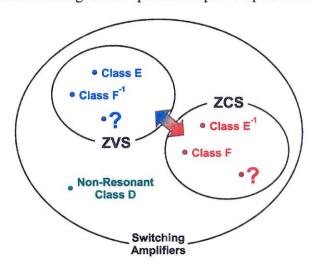

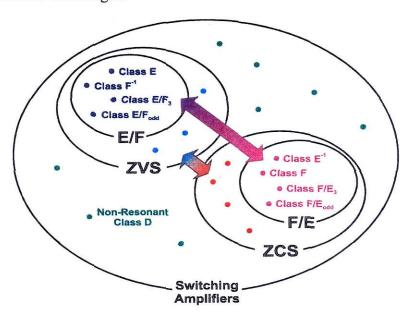

| Figure 6.1:   | Taxonomy of known switching amplifiers                                                                         |

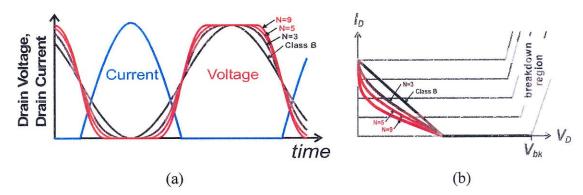

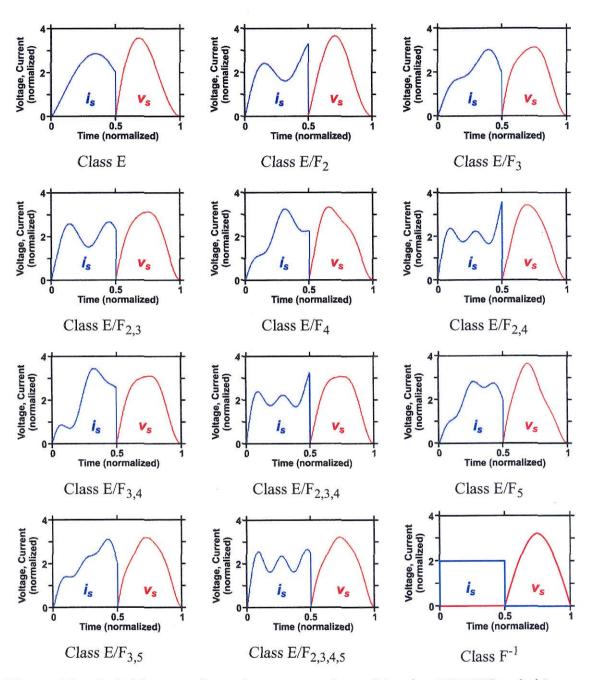

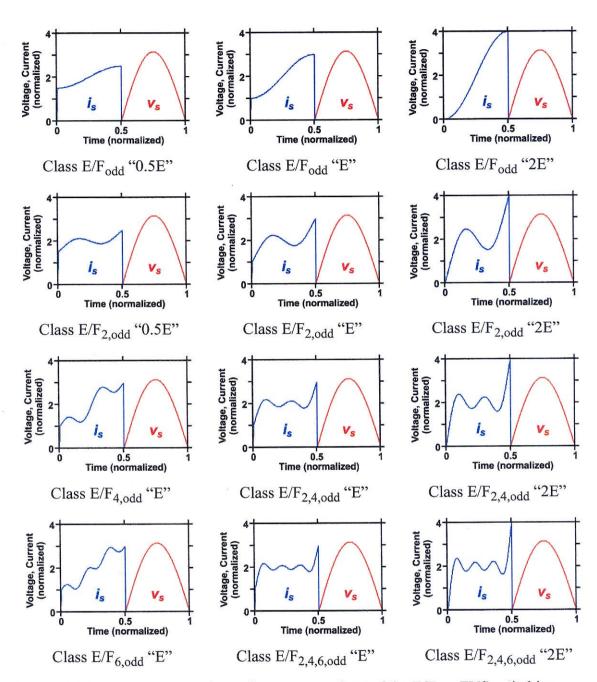

| Figure 6.2:   | Switching waveforms for some members of the class E/F ZVS switching amplifier family                           |

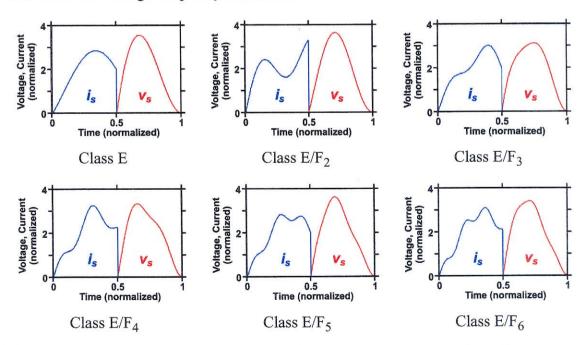

| Figure 6.3:   | Single-harmonic class E/F ZVS switching amplifiers110                                                          |

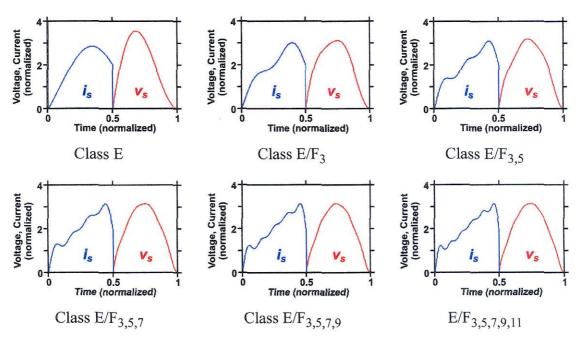

| Figure 6.4:   | Odd-harmonic class E/F ZVS switching amplifiers                                                                |

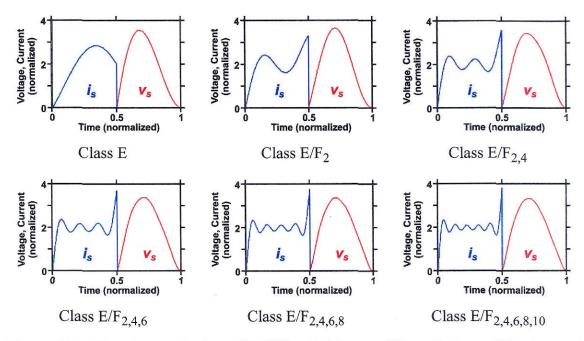

| Figure 6.5:   | Even-harmonic class E/F ZVS switching amplifiers112                                                            |

| Figure 6.6:   | Complete N-harmonic class E/F ZVS switching amplifiers113                                                      |

| Figure 6.7:   | Direct E/F <sub>3</sub> implementation using high-Q resonators116                                              |

| Figure 6.8:   | Direct E/F <sub>2,3</sub> implementation using high-Q resonators117                                            |

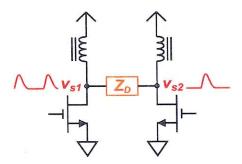

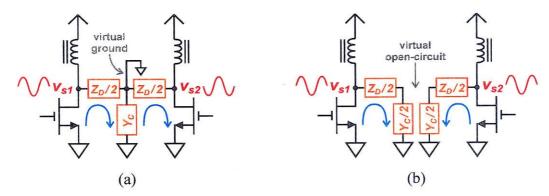

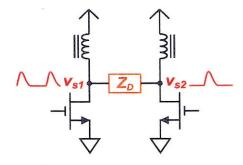

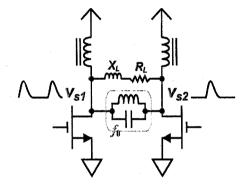

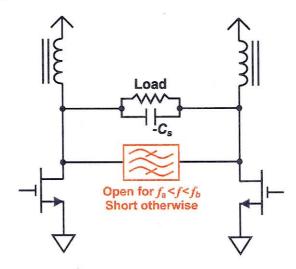

| Figure 6.10:  | Push/pull switching amplifier with differential load118                                                        |

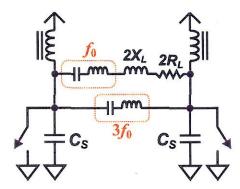

| Figure 6.9:   | Class E/F <sub>2,3</sub> implementation using a multi-resonant tuning circuit118                               |

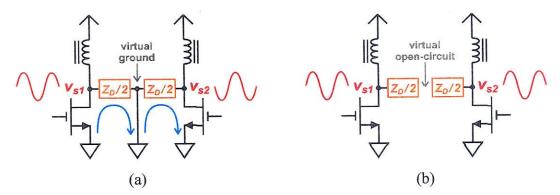

| Figure 6.11:  | Effect of differential load at odd harmonics and even harmonics 119                                            |

| Figure 6.12:  | Class E/F <sub>3</sub> push/pull implementation                                                                |

| Figure 6.13:  | Push/pull switching amplifier with T network load120                                                           |

|   | Figure 6.14: | Effect of differential load at odd harmonics and even harmonics121                                                |

|---|--------------|-------------------------------------------------------------------------------------------------------------------|

|   | Figure 6.15: | Class E/F <sub>2,3</sub> push/pull implementation                                                                 |

|   | Figure 6.16: | New switching amplifier taxonomy, including the new E/F and F/E families123                                       |

| C | hapter 7: Th | e E/F <sub>odd</sub> Switching Amplifier Family                                                                   |

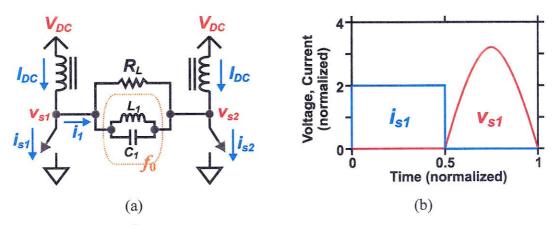

|   | Figure 7.1:  | Push/pull switching amplifier with differential load124                                                           |

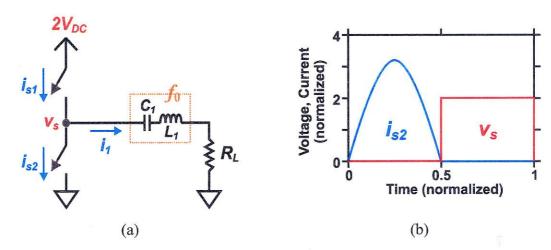

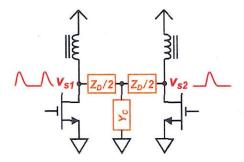

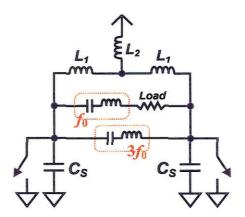

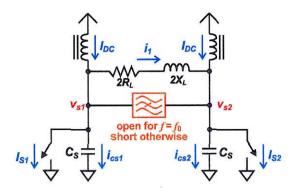

|   | Figure 7.2:  | Class E/F <sub>odd</sub> circuit implementation using a parallel LC resonator125                                  |

|   | Figure 7.3:  | Class E/F <sub>odd</sub> circuit model for analysis                                                               |

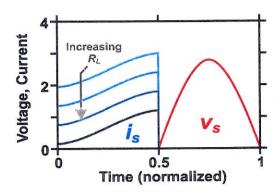

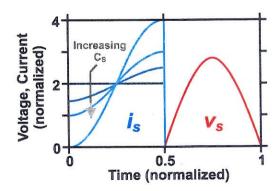

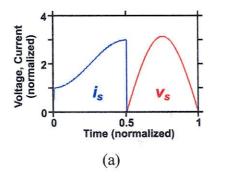

|   | Figure 7.5:  | Class E/F <sub>odd</sub> waveforms as output capacitance is varied                                                |

|   | Figure 7.4:  | Behavior of the E/F <sub>odd</sub> switching waveforms as the load is varied131                                   |

|   | Figure 7.6:  | Class E/F <sub>odd</sub> tunings for "E" and for "2E" sized devices                                               |

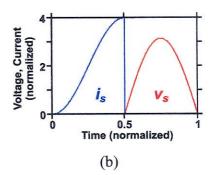

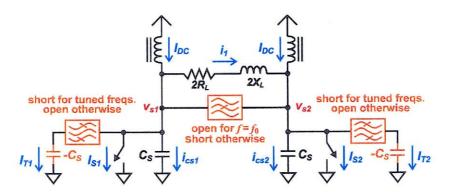

|   | Figure 7.7:  | E/F <sub>x,odd</sub> conceptual circuit implementation134                                                         |

|   | Figure 7.8:  | Switching waveforms for some members of the E/F <sub>odd</sub> ZVS switching amplifier family137                  |

| C | hapter 8: Ne | ew Opportunities and Applications                                                                                 |

|   | Figure 8.1:  | Capacitance limited switching amplifier performance for the given device technology as a function of frequency142 |

|   | Figure 8.2:  | Class E/F <sub>odd</sub> amplifier with changing load143                                                          |

|   | Figure 8.3:  | Tri-band class E/F <sub>odd</sub> amplifier conceptual schematic145                                               |

|   | Figure 8.4:  | Dual band class E/F <sub>odd</sub> amplifier implemented by Florian Bohn147                                       |

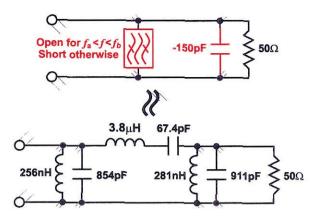

|   | Figure 8.5:  | Wideband class E/F <sub>odd</sub> amplifier concept148                                                            |

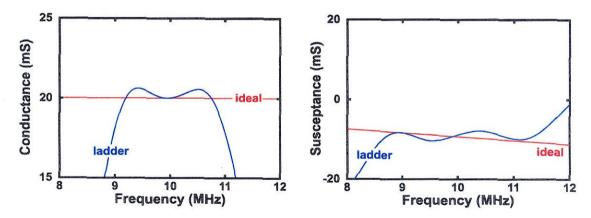

|   | Figure 8.7:  | Input admittance of the ladder filter                                                                             |

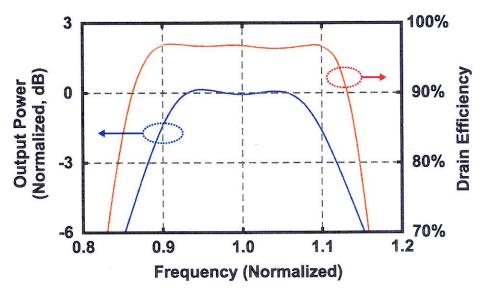

|   | Figure 8.6:  | Ladder filter to approximate negative capacitance over the operation band149                                      |

|   | Figure 8.8:  | Wideband Class E/F <sub>odd</sub> circuit and simulated performance150                                            |

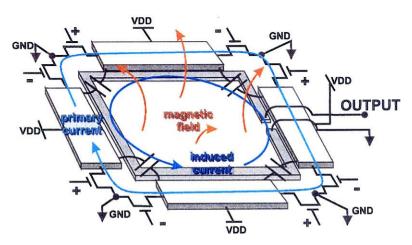

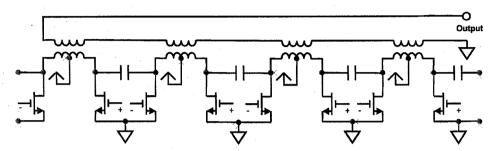

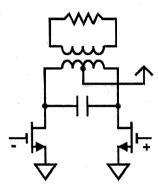

|   | Figure 8.9:  | Aoki circular-geometry distributed active transformer power combining circuit151                                  |

|   | Figure 8.10: | DAT equivalent circuit model152                                                                                   |

|   | Figure 8.11: | Equivalent circuit for one DAT push/pull pair153                                                                  |

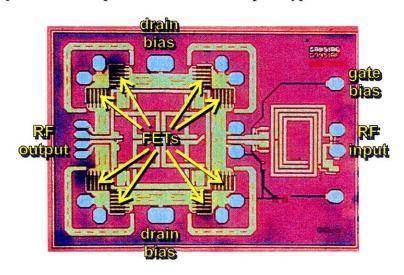

|   | Figure 8.12: | Die photo of E/F CMOS power amplifier using DAT power combining.                                                  |

| • | Figure 8.13: | DAT measured performance and simulated large-signal drain wave-forms                                              |

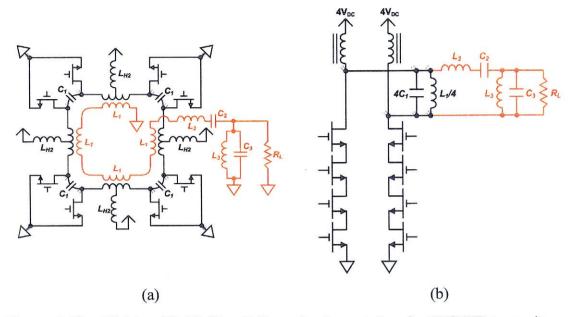

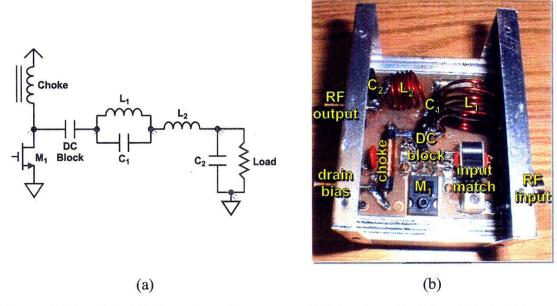

|   | Figure 8.14: | Circuit schematic of the prototype E/F <sub>2,odd</sub> amplifier156                                              |

|   | Figure 8.15: | Simulated waveforms with no package inductance and with 5 nH package inductance                                   |

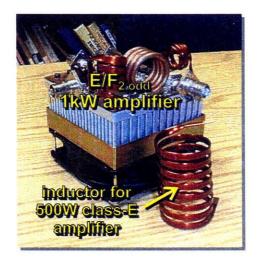

| Figure 8.16: | Photo of fabricated E/F <sub>2,odd</sub> 7MHz, 1kW prototype                        | 158      |

|--------------|-------------------------------------------------------------------------------------|----------|

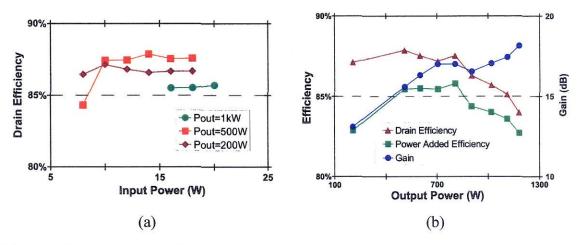

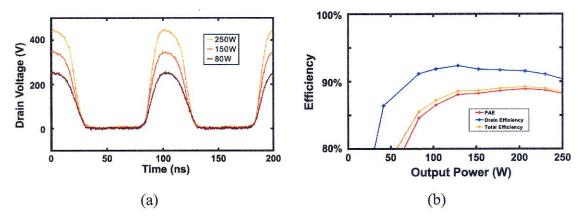

| Figure 8.17: | Measured E/F <sub>2,odd</sub> amplifier performance at 10MHz                        | 159      |

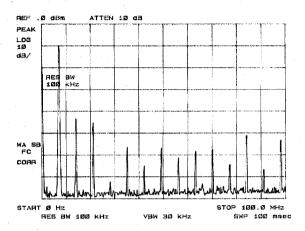

| Figure 8.18: | Measured output spectrum at 1kW output power                                        | 160      |

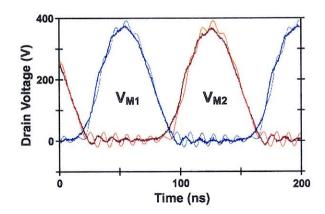

| Figure 8.19: | Measured and simulated drain voltage waveforms                                      | 161      |

| Figure 8.20: | Wideband DAT Class E/F <sub>2,odd</sub> implementation for HF/VHF tranapplications. |          |

| Figure 8.21: | Photo of 1 kW E/F <sub>2,odd</sub> amplifier and inductor from 500 W class          | s-E kit. |

|              |                                                                                     | 164      |

| Figure 8.22: | Quasi-E/F <sub>2,3</sub> compact power amplifier: schematic and photo               | 165      |

| Figure 8.23: | Measured performance of quasi-E/F <sub>2,3</sub> prototype                          | 166      |

#### Chapter

# Introduction

1

Due to the ever-increasing demand for communications, wireless connectivity, industrial power, and power conversion technology, the demand for high-efficiency, high-frequency power amplifiers has never been greater. Wireless markets demand high-efficiency amplifiers for portable units in order to extend battery lifetime. Wireless base-stations and other high-power RF transmitters require improved efficiency in order to increase reliability and lower the cost of heat-sinking. Industrial power applications such as RF plasma generation and RF induction heating units demand high efficiency to reduce power consumption and eliminate expensive forced-flow cooling techniques. Power converter applications in both the industrial and consumer markets demand amplifiers (and rectifiers) achieving higher efficiency, smaller size, and higher-frequency thereby allowing smaller, more efficienct power converters with faster response times.

In order to meet these demands, designers must select the technologies best suited to meet their various requirements. Unfortunately, there is often a trade-off between amplifier efficiency and amplifier linearity. In many applications, such as industrial RF power and power converters, linearity of the amplifier is not important and high-efficiency modes of operation such as class-C or class-E are attractive. In applications requiring significant amplification linearity, such as most wireless communication products, traditional transconductance amplifier technologies such as class-A and class-AB [1] are commonly used. Unfortunately, these techniques severely limit the power efficiency, making the desired cost and size reductions difficult to achieve.

In applications for which AM/AM and AM/PM distortion are tolerable [2] or compensated for [3], harmonic-tuned saturated and switching amplifiers provide a

higher-efficiency alternative. Amplifiers operating in class-E and class-F modes may routinely achieve efficiencies above 80%, sometimes approaching 100%, making them attractive when efficiency is paramount.

Unfortunately, only two types of amplifier tunings appropriate for high-frequency operation have been studied in the literature. Class-E amplifiers [4,5] have found most application as a higher-performance alternative to class-D amplifiers, due to their compensation for transistor output capacitance and elimination of turn-on switching losses. Additionally, the class-E design may be implemented with a relatively simple circuit. As a result, this class has been implemented over a wide range of frequencies from HF to microwave with great success [e.g. 7-14].

Class F [15,16] and its recently popularized dual, class F<sup>-1</sup> [17,20], have been presented and developed primarily as a means of increasing the saturated performance of class AB or class-B designs. As a result, the operating frequencies attainable have usually been somewhat higher, but the performance limitations due to the tuning requirements [25] and the lack of a simple circuit implementation suitable for nearly-ideal switching conditions have made this design a poor alternative at frequencies where class-E can be implemented.

Nevertheless, it has been noted [e.g. 17] that the waveforms which could in principle be achieved by class F and/or F<sup>-1</sup> would allow performance benefits over class-E designs. Additionally, limitations of the class E approach at high frequencies due to a finite tolerance for large transistor output capacitance have been identified [21].

This dissertation presents a new family of harmonic tunings with the promise of achieving the promised performance benefits of class F<sup>-1</sup> in the frequency range wherein the transistor is switching nearly ideally. Additionally, this tuning method may increase the amplifier's tolerance to large transistor output capacitance, improving the high frequency performance and extending the frequency range of this new tuning beyond that of class E. This new E/F family of tunings unifies class E and class F<sup>-1</sup> into a single

framework, and demonstrates varying degrees of trade-off between the simplicity of class-E and the high-performance of class F<sup>-1</sup>. All members of the E/F family have exact time-domain solutions, can be made to achieve class-E switching conditions, and have circuit implementations wherein the output capacitance of the switch is explicitly accounted for. Finally, some members of this tuning family have properties making them more appropriate for use in applications where class-E tunings might be difficult or impossible to implement.

#### 1.1 Organization of the Dissertation

Chapter 2 presents a background discussion of the nature and limitations of amplifier power efficiency and a comparison between the efficiencies of most commonly used amplifier classes. The low efficiencies achievable in non-switching amplifier classes is quite limited, motivating the introduction of switching amplifiers as discussed in Chapter 3. This chapter also presents background material, but with more depth and with a focus on switching amplifiers. General properties of switching amplifiers are presented, as well as more specific investigations of the well-known D and E switching amplifier classes.

Chapter 4 discusses some simple methods to compare the performance (i.e. efficiency and gain) of different switching amplifiers from the shapes of the voltage and current waveforms through the active device. Since some design choices affect the efficiency, the correct choices for optimal performance are derived, so that the comparisons made between tunings will take into account the optimal parameter choices for each tuning.

Chapter 5 introduces a new technique for analytical or numeric determination of the voltage and current switching waveforms for any user-defined harmonic tuning. Using this technique, harmonic tuning strategies may be treated generally, rather than being solved in a case-by-case basis as has been done in the past. The technique is

computationally efficient and variations of the technique allow for the calculation certain important design parameters, avoiding the need to discover them empirically.

Chapters 6 and 7 introduce the new E/F family of switching amplifier tunings. This family, which is a generalization of the class E and class F<sup>-1</sup> concepts, is the result of applying additional harmonic tuning to the basic class-E amplifier circuit. Using the solution technique of Chapter 5 and the estimation techniques of Chapter 4, the performance of tunings of this family are compared to that of class E, showing that performance may be significantly improved in certain applications. Finally, implementation strategies for these tunings are proposed.

Lastly, Chapter 8 highlights some of the applications where the E/F technique may allow for performance enhancement or desirable new design features. Several prototype amplifiers from 7MHz to 2.4GHz using E/F tunings are presented, illustrating that the technique is already being successfully applied in demanding applications.

# Chapter 2

# Efficiency of Power Amplifiers

One of the most important aspects of a power amplifier is its *power efficiency*, i.e. the ratio between the useful power generated by the amplifier and the power that the amplifier consumes. By increasing this ratio, the amplifier will consume less supply power and require less heat sinking, allowing a reduction of battery size and cost of portable units. Similarly, this reduces the operating cost of high-power equipment, and the manufacturing costs associated with heat sinking. For instance, if an amplifier with efficiency  $\eta$  is operated in a situation where the battery charge is limited to energy  $E_{charge}$ , and output power of  $P_{out}$  is required, the operation time  $t_{charge}$  is limited to:

$$t_{charge} = \eta \cdot \frac{E_{charge}}{P_{out}} \tag{2.1}$$

In other words, increase in efficiency results in a proportional increase in battery lifetime. A more striking condition is where a very large output power is desired, but the design limitation is a maximum tolerable dissipated power  $P_{diss}$ . In this case, the maximum achievable output power is:

$$P_{out} = \frac{\eta}{1 - \eta} \cdot P_{diss} \tag{2.2}$$

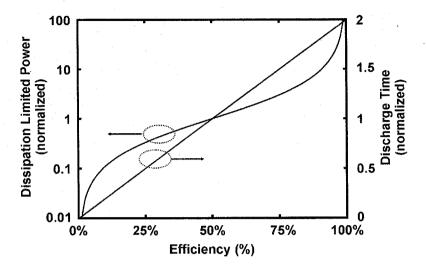

Thus, increased efficiency can result in a substantial increase in output power in industrial applications where heat removal is a driving factor in the design. Normalized results of battery discharge time and dissipation-limited output power are plotted in Fig. 2.1.

In order to improve the efficiency, it is necessary to identify the power dissipation mechanisms in the amplifier and reduce their effect to whatever degree possible. This chapter provides a brief overview of power amplifier efficiency issues, focusing on the

**Figure 2.1:** Dissipation-limited output power and battery discharge time vs. amplifier efficiency. Values are normalized to the performances of a 50% efficiency amplifier.

special case of the *narrowband* power amplifier, i.e. an amplifier whose operation can be reasonably assumed to be periodic.

#### 2.1 Amplifier Loss Mechanisms

In the most general sense, an amplifier is a frequency conversion device, wherein dc power is converted into power with a spectrum reproducing that of its input signal with some reasonable degree of accuracy. Thus the amplifier receives dc power, receives some amount of ac power to its input port, and supplies ac power to the load. An ideal amplifier would require an infinitesimally small amount of input power, and convert all of the dc power consumed into ac power delivered to the load. The ability to approximate these characteristics is measured by various amplifier efficiency measures.

In order to perform the frequency conversion, the amplifier requires one or more active devices, and a passive – usually linear and time invariant – network which provides

<sup>1.</sup> The ideal amplifier would have one additional property, namely the ability to produce an output exactly reproducing its input. This property is quantified by various distortion figures of merit.

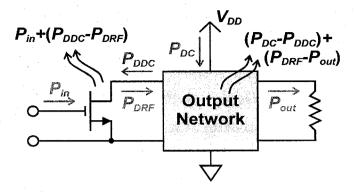

Figure 2.2: Power flow in a generalized power amplifier.

connection to the dc power supply and any necessary impedance transformation between the active device(s) and the load. Such an amplifier is shown in Fig. 2.2. Normally, some method of input matching is also required. This aspect of amplifier design will be largely ignored in this work since its effect on amplifier efficiency is relatively small, as long as care is taken [22], and acceptable methods are well known [e.g. 1,23].

The power flow for the amplifier begins with dc power  $P_{DC}$  entering the passive network. Of this power, some is dissipated by the network and the remainder,  $P_{DDC}$ , is supplied to the active device. The active device receives this dc power and some amount of input ac power,  $P_{in}$ . It dissipates some portion of this power, and converts the remainder into ac power,  $P_{DRF}$ , which it delivers to the output network. The output network, in turn, dissipates some portion of this power and delivers the remainder,  $P_{out}$ , to the load. The object of power amplifier design is to minimize the power loss associated with each step of this power transfer while at the same time achieving a desired level(s) of output power  $P_{out}$  and a tolerable level of distortion.

#### 2.1.1 Drive Power Loss

The amplifier requires some reference signal in order for it to determine the output waveform to generate. This signal consists of power delivered to and dissipated on the device input port. The active device then generates a similar signal with greater power

which it delivers to the output passive network. The gain – the ratio  $G_D$  between the input power  $P_{in}$  and the generated power  $P_{DRF}$  – is determined by a number of factors, including the device technology, bias conditions, frequency of operation, and the characteristics of the load presented to the device. Usually the gain of a power amplifier is relatively high, and so the input power loss is of secondary importance to other losses.

#### 2.1.2 Device Conduction Loss

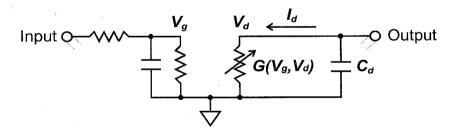

All of the popular solid-state active devices in use today are controlled resistors of some sort. To be more specific, the core of the device consists of a resistor<sup>1</sup> across the output port whose conductance is varied by the instantaneous values of the input and output waveforms. A simple device model appropriate for both bipolar and field-effect devices is shown in Fig. 2.3. Although this model incorporates the device output capacitance  $C_d$ , the analysis is generally simpler if this component is treated as being part of the output passive network, so that the resistive control mechanism can be dealt with independently of the passive parasitic components. Thus, in the following analysis any reference to the active device current should be understood to mean the current  $I_D$  through the controlled resistance.

Figure 2.3: Simple device model disregarding feedback parasitics.

The consequences of the resistive nature of the control mechanism in active devices has important implications in the design of high-efficiency power amplifiers. First, any

<sup>1.</sup> Most treatments introduce the transistor as a dependent **current source** rather than a dependent resistor. If the device operates as a current source, the resistor model is valid using R(t) = V(t)/I(t).

power absorbed by this resistance is truly dissipated, rather than stored for later recovery, motivating the desire to have as little power as possible being absorbed into the drain of the device at all times. This knowledge also allows the simple calculation of the power dissipated by the device as the product of the drain voltage  $V_d$  and the drain current  $I_d$ . To find the average power loss, the mean value of this product should be used. In the narrowband case, the waveforms may be assumed to be periodic with frequency  $f_0$  and so this average,  $P_{DD}$ , may be taken over a single cycle:

$$P_{DD} = P_{DDC} - P_{DRF} \approx f_0 \cdot \int_{0}^{1/f_0} (I_d V_d) dt$$

(2.3)

In most cases, the conduction loss of the amplifier is the largest source of dissipation, as the designs which are most commonly used tend to have significant times during which the drain voltage and current attain high values simultaneously. If reducing the loss were the only consideration, however, it would be desirable to ensure that whenever the drain current is significant that the drain voltage is nearly zero and vice-versa.

#### 2.1.3 Output Network Loss

Although not strictly necessary in all applications, amplifier design tends to demand the use of a network of passive, usually linear, devices between the active device and the load. The primary purpose of this network is usually to perform an impedance transformation so that the device is presented an impedance more compatible with the device characteristics and design goals than the desired load impedance. The second purpose served by these networks is to provide some level of signal filtering so that out-of-band distortion products and spurious signals are not delivered to the load. Finally, in high-efficiency amplifiers employing harmonics in the voltage and current waveforms, the network provides waveshaping by selectively tuning the harmonic impedances.

To see why impedance transformation is necessary, it is worthwhile to consider its effect on amplifier efficiency and maximum output power. Consider a narrowband class-A amplifier wherein the active device is a MOSFET operated as a controlled current source with output resistance  $r_{out}$ . Suppose that the drain voltage  $V_d$  must not exceed 10 V due to device breakdown limitations and that it is desired to achieve 1 W of output power into a  $50\Omega$  load. The requirede ac voltage signal on the load may be computed:

$$v_{ac} = \sqrt{2 \cdot (50\Omega) \cdot (1W)} = 10V \tag{2.4}$$

Unfortunately, if the load presented to the transistor is the  $50\Omega$  load, this ac voltage signal in class-A operation requires a peak voltage of at least  $2v_{ac}$  or 20V. In fact, the maximum output power achievable in class-A operation under these constraints is:

$$P_{out} = \frac{(5V)^2}{2 \cdot (50\Omega)} = 0.25W \tag{2.5}$$

Now consider the case wherein it is desired to achieve the 1W output power using a fixed supply voltage of 100V using a MOSFET capable of withstanding 250V. If the  $50\Omega$  load is directly presented, the voltage swing will again be  $\pm 10V$  and the current swing will be  $\pm 200 \text{mA}$ . The resulting minimum bias current for class-A operation is 200 mA, and so the dc power consumed from the supply will be:

$$P_{dc} = (100\text{V}) \cdot (200\text{mA}) = 20\text{W}$$

(2.6)

This represents an efficiency of only 5%, due primarily to the fact that the dc voltage is unnecessarily high for the small ac voltage swing required. If the supply voltage is fixed by other constraints, the efficiency must be improved by means other than reducing the supply voltage.

In order to achieve the desired output power and efficiency respectively, the  $50\Omega$  load must be transformed into a more desirable impedance. In the first case, the impedance presented to the MOSFET must be lowered, so that the output power can increase without increasing the peak voltage. In the second case, the impedance must be made higher, so

that the voltage can achieve a full  $\pm 100$ V drain voltage swing without increasing the output power.

This transformation can be accomplished by any number of well-known passive networks, such as coupled-inductor transformers, resonant lumped element networks, and many varieties of transmission line networks. Each has the same purpose, shown in Fig. 2.4, that being to transform its input power at one impedance into output power at another.

Figure 2.4: Impedance transformer component.

As will be shown later in this chapter, the efficiency of an amplifier generally improves with increasing generation of harmonics. Even in the event that harmonics are not intentionally generated to improve efficiency, the nonlinearity of most active devices is often sufficient to generate enough harmonic power to be troublesome in communications applications. It is usually undesirable to allow these harmonics to reach the load, and so the output passive network is often also used to filter the undesirable harmonic components out of the signal. In harmonic-tuned amplifiers, the network not only serves to reject the harmonic transmission to the load, but also will present desired impedance levels to the active device at some of the harmonic frequencies, allowing the designer a means to control the waveform shapes.

Unfortunately, the impedance transformation and filtering functions do not come without cost. The network will introduce additional power loss, degrading the overall efficiency. Generally, the efficiency of this network gets worse as the impedance

transformation ratio is increased, the harmonic rejection is increased, and the number of tuned harmonics is increased.

#### 2.2 Efficiency Measures

There are several measures of amplifier efficiency in general use today. The simplest is probably the *drain* (collector) efficiency, denoted here as  $\eta_D$ , which is defined as the ratio between the output power  $P_{out}$  and the dc power consumed  $P_{DC}$ :

$$\eta_D \equiv \frac{P_{out}}{P_{DC}} \tag{2.7}$$

This measure is appropriate in situations where the amplifier gain is high or where the input power comes at no cost, and can therefore be safely ignored. Additionally, the drain efficiency is useful in evaluating the conduction loss in isolation of input power loss. Since the drain efficiency ignores the effect of the input power, this measure helps measure the effectiveness of the amplifier in avoiding dissipation on the controlled resistance of the output port. Since this loss is significantly affected by choices made by the designer, such as the class of operation used and the harmonic tuning employed, the drain efficiency measures the effectiveness of this design choice in isolation from the device gain.

Somewhat less commonly used, but of perhaps more physical significance, is the *total* efficiency, denoted here as  $\eta_T$ , which is simply the ratio between the output power  $P_{out}$  and the sum of all powers delivered to the amplifier. Using the simplified model of Section 2.1, this would be:

$$\eta_T = \frac{P_{out}}{P_{in} + P_{dc}} \tag{2.8}$$

By truly evaluating the effectiveness of the net power flow in the amplifier, this measure can be used to measure the effectiveness of an amplifier in reducing the need for heat removal. This can be seen by noting that the total dissipated power is a simple function of the total efficiency and the output power:

$$P_{diss} = P_{DC} + P_{in} - P_{out} = \left(\frac{1}{\eta_T} - 1\right) \cdot P_{out}$$

(2.9)

Finally, the most commonly used measure is the *power added efficiency*, or PAE. This measure is computed as the ratio between the added power  $P_{out} - P_{in}$  and the dc power:

$$PAE = \frac{P_{out} - P_{in}}{P_{DC}} \tag{2.10}$$

An equivalent form for PAE is expressed in terms of the amplifier drain efficiency  $\eta_D$  and gain G:

$$PAE = \frac{P_{out}}{P_{DC}} \cdot \left(1 - \frac{P_{in}}{P_{out}}\right) = \eta_D \cdot \left(1 - \frac{1}{G}\right)$$

(2.11)

To see why this measure is useful and physically significant, consider a chain of N amplifiers, each with the same drain efficiency  $\eta_D$  and power gain G. The efficiency of such an arrangement can be computed. Counting from the final amplifier, k=1, to the first amplifier k=N, the input power of the k<sup>th</sup> amplifier is found to be:

$$P_{in}(k) = \frac{P_{out}}{G^k} \tag{2.12}$$

The output power of each stage is simply the input power of the next stage:

$$P_{out}(k) = \frac{P_{out}}{G^{k-1}} \tag{2.13}$$

The dc power consumed by each amplifier can be computed using the drain efficiency:

$$P_{dc}(k) = \frac{P_{out}}{\eta_D \cdot G^{k-1}} \tag{2.14}$$

Thus the total dc power consumed by the chain is:

$$P_{DC} = \sum_{k=1}^{N} P_{DC}(k) = \left(\frac{P_{out}}{\eta_D}\right) \cdot \left(\frac{1 - \frac{1}{G^N}}{1 - \frac{1}{G}}\right)$$

(2.15)

The total input power is simply the input power to the first stage:

$$P_{in} = \frac{P_{out}}{G^N} \tag{2.16}$$

Now the three efficiency measures may be computed:

$$\eta_{D, chain} = \eta_{D} \cdot \left(1 - \frac{1}{G}\right) \cdot \left(\frac{G^{N}}{G^{N} - 1}\right)$$

$$= PAE \cdot \left(\frac{G_{chain}}{G_{chain} - 1}\right)$$

(2.17)

$$\eta_{T, chain} = \eta_D \cdot \left(1 - \frac{1}{G}\right) \cdot \left[\frac{G^N}{G^N - (1 - \eta_D)}\right]$$

$$= PAE \cdot \left[\frac{G_{chain}}{G_{chain} - (1 - \eta_D)}\right]$$

(2.18)

$$PAE_{chain} = \eta_D \cdot \left(1 - \frac{1}{G}\right) = PAE \tag{2.19}$$

As can be seen from (2.19), the PAE of the amplifier chain is identical to the PAE of each individual amplifier in that chain. Additionally, if the gain of the chain is sufficiently high, both the drain efficiency and the total efficiency of the chain approach the PAE of the individual amplifiers used, as can be seen from (2.17) and (2.18). Thus PAE is an effective measure of the efficiency that could be achieved using a chain of similarly performing amplifiers.

#### 2.3 Some Important Relationships

Before discussing in detail the various strategies which are commonly employed to implement power amplifiers, some helpful theorems regarding fundamental power amplifier limitations will be presented. Again, it should be understood that the amplifiers in question are assumed to be narrowband in nature, i.e. the desired output can be accurately modelled as a slowly changing sinusoidal signal so that the signals present in the circuit can be assumed to effectively consist only of this fundamental frequency sinusoid and its harmonics. Additionally, the output passive network is assumed to be a linear and time-invariant (LTI) circuit. There is assumed to be only one power source present, which is a dc voltage (or current) generator. Although some of the conclusions drawn in the next few sections may seem trivial, it is important to keep them in mind as even these simple conclusions provide fundamental limitations on power amplifier performance.

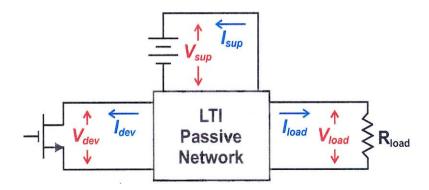

#### 2.3.1 Power Flow Relationships

A generalized power amplifier can be seen in Fig. 2.5. The amplifier consists of a three port LTI matching network with the active device connected to port one, the dc power supply connected to port two, and the load connected to port three. The voltage and current on the device port are denoted  $V_{dev}$  and  $I_{dev}$  respectively, the voltage and current on the supply port are denoted  $V_{sup}$  and  $I_{sup}$  respectively, and the voltage and current on the load port are labelled  $V_{load}$  and  $I_{load}$  respectively.

As the amplifier is narrowband, the voltages and currents on these ports can all be represented by a Fourier series consisting of the desired fundamental frequency  $f_0$  and its harmonics:

$$V_{dev} = V_{DC} + \sum_{k=1}^{\infty} v_k \cdot \cos(k \cdot \theta + \alpha_k)$$

(2.20)

Figure 2.5: Generalized single-transistor power amplifier.

$$I_{dev} = I_{DC} + \sum_{k=1}^{\infty} i_k \cdot \cos(k \cdot \theta + \beta_k)$$

(2.21)

where the  $v_k$ 's are the voltage harmonic amplitudes, the  $i_k$ 's are the current harmonic amplitudes, the  $\alpha_k$ 's are the phases of the voltage harmonics, the  $\beta_k$ 's are the phases of the current harmonics,  $V_{DC}$  is the dc voltage,  $I_{DC}$  is the dc current, and  $\theta$  is the normalized time variable defined as:

$$\theta = 2\pi f_0 t \tag{2.22}$$

Since the matching network is both passive and LTI, it cannot generate power at any harmonic, nor can it convert power from one harmonic to another. It can, however, dissipate some portion of the power at each frequency. These conditions can be stated precisely:

$$\underbrace{P_{dev}[k] + P_{sup}[k] + P_{load}[k] + P_{diss}[k] = 0}_{\forall k \in \{0...\infty\}}$$

(2.23)

where  $P_{dev}[k]$  is the power delivered to the active device at the  $k^{th}$  harmonic,  $P_{sup}[k]$  is the power delivered to the dc supply at the  $k^{th}$  harmonic,  $P_{load}[k]$  is the power delivered to the load at the  $k^{th}$  harmonic, and  $P_{diss}[k]$  is the (non-negative) power dissipated by the matching network at the  $k^{th}$  harmonic.

The dc power source enforces a constant voltage (or current) on its port, and therefore it cannot dissipate or deliver power except at dc. Since it is the only power source in the system, presumably it is delivering power, and so  $P_{sup}[0]$  must be negative:

$$\underbrace{P_{DC}[k] = 0}_{\forall k \neq 0} \tag{2.24}$$

$$P_{DC}[0] < 0 (2.25)$$

The load is passive and linear, and so the power absorbed at each harmonic must be non-negative:

$$\underbrace{P_{load}[k] \ge 0}_{\forall k \in \{0...\infty\}}$$

(2.26)

The active device, being the only non-LTI device in the system, is the only means by which power can be converted from one frequency to another. It is not, however, a power source, and so the net power absorbed by the device must be non-negative:

$$\sum_{k=0}^{\infty} P_{dev}[k] \ge 0 \tag{2.27}$$

There are several conclusions to be drawn from (2.23) - (2.27). The first observation is that the power absorbed by the active device  $P_{dev}[k]$  must be non-positive except for do since there are no other power sources in the system at these frequencies:

$$\underbrace{P_{dev}[k] \le 0}_{\forall k \ne 0} \tag{2.28}$$

Constraints on the output power can now be found. Combining (2.23) with (2.24) and (2.27). Keeping in mind that  $P_{load}[1]$  is the useful generated output power  $P_{out}$ :

$$P_{out} \le P_{dev}[0] + \sum_{k=2}^{\infty} P_{dev}[k] - P_{diss}[1]$$

(2.29)

This relationship is already useful, showing that generation of harmonic power by the active device degrades the efficiency, consisting of (at best) merely wasted power at undesired frequencies. This will have an effect on the selection of device waveforms later. The relationship can be strengthened by utilizing (2.28):

$$P_{out} \le P_{dev}[0] \tag{2.30}$$

which simply indicates that the output power cannot exceed the dc power supplied to the active device. Although seemingly obvious, this also has important implications on waveform selection.

#### 2.3.2 Waveform Limitations: Power Consumption at Harmonics

The results of the previous section, although useful, can be made more explicit in terms of the actual active device waveforms. In particular, using (2.20) and (2.21), the  $P_{dev}[k]$  terms can be explicitly specified in terms of the harmonic components of the device waveforms:

$$P_{dev}[0] = V_{DC}I_{DC} (2.31)$$

$$P_{dev}[k] = \frac{1}{2} v_k i_k \cos(\alpha_k - \beta_k)$$

$$\forall k \neq 0$$

(2.32)

Using these relations, (2.29) becomes:

$$P_{out} \le V_{DC}I_{DC} + \frac{1}{2} \cdot \sum_{k=2}^{\infty} v_k i_k \cos(\alpha_k - \beta_k) - P_{diss}[1]$$

(2.33)

all negative terms

Similarly, (2.30) becomes:

$$P_{out} \le V_{DC} I_{DC} \tag{2.34}$$

These two relationships establish what should be intuitive, but should still be kept closely at hand during the quest for high-efficiency amplification. Since power must be conserved, the device waveforms will always be such that the output power is at most equal to the dc power consumed minus the power generated at the harmonics.

Since generated harmonic power leads to reduced efficiency, it is advisable to establish the conditions which can be imposed in order to eliminate this loss. From (2.32), the conditions on the harmonic components rendering the generated power at that harmonic equal to zero can be found by inspection. If either the voltage or the current amplitude at that harmonic is equal to zero then the power generated is zero. Likewise, if the phase angle between the voltage and current is  $\pm 90^{\circ}$  there will be no power generated at this frequency. Since the design of the matching network is under the control of the designer, and since the network connected to the active device is LTI, the characteristics of the load are uniquely specified by the input impedance presented by the network to the active device. This impedance  $Z_{in}[k]$  is independent of the active device or the drive conditions, and places necessary constraints on the relationship between the voltage and current harmonics:

$$Z_{in}[k] = \frac{v_k}{i_k} \cdot [\cos(\alpha_k - \beta_k) + j \cdot \sin(\alpha_k - \beta_k)]$$

(2.35)

Using the above conditions on the waveforms, the conditions on the load network making the harmonic dissipation zero can be found. If the voltage amplitude is zero (and the current is nonzero), the input impedance is short-circuit. If the current amplitude is zero (and the voltage is nonzero) the impedance is open-circuit. If the phase angle difference is  $\pm 90^{\circ}$  then the impedance is purely reactive. The only other possibility is if both the voltage and the current are zero due to the harmonic not being excited by the device. In this case, the input impedance at that harmonic has no effect. Again, the conclusion reached is obvious in retrospect: By adjusting the input impedances at the harmonics to be either purely reactive, open-circuit, or short-circuit, the waveforms will

necessarily be such that the power generated at the harmonics will be zero. The only other means to eliminate harmonic power generation is to assure the harmonic is simply not excited by the device.

One final waveform constraint is that, due to the essential resistive nature of the active device, the device voltage and current waveforms must at all times have the same sign as each other. If at any time, the voltage and current were to have opposite sign, the device would be delivering instantaneous power into the load.

In summary, the following principles should be kept in mind:

#### Physicality constraints:

- The output power may not exceed the dc power delivered to the device.

- The output power may not exceed  $v_0 \cdot i_0$ .

- Waveforms should not be such that harmonic power need be delivered to the device.

- The waveforms should be such that  $v_k i_k \cos(\alpha_k \beta_k)$  is less than or equal to zero for all  $k \neq 0$ .

- The voltage and current waveforms should always have the same sign, so that the voltage is never positive when the current is negative and vice-versa.

#### **Efficiency considerations:**

- Generation of harmonic power by the active device either increases the dc power consumed or decreases the output power, thereby reducing efficiency.

- To minimize the harmonic power generated, the device waveforms should either

have no voltage at that harmonic, no current at that harmonic, or the phase angle

α-β between the voltage and current components at that harmonic should be 90°.

- Harmonics for which current or voltage exist in the waveforms should be tuned so that the device is presented with a pure reactance, a short-circuit, or an open-circuit.

Failure to keep in mind these seemingly obvious lessons can result in a designer choosing device operating conditions that are either non-physical or that have performances below initial expectations.

#### 2.4 Efficiency of Common Amplifier Classes

#### 2.4.1 Transconductance Amplifiers

The simplest and most common types of amplifiers are transconductance amplifiers. In these amplifiers, the active device is operated as a current source whose current is dependant almost entirely on the voltage presented to its input. This is made possible by the propensity of solid state devices to contain large regions of their transfer characteristic wherein the output current is largely independent of the output voltage<sup>1</sup>.

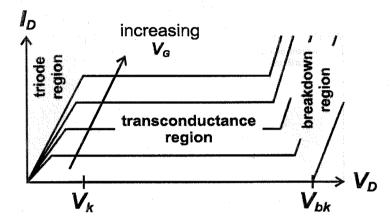

Typical output characteristics of a solid state active device, applicable to both bipolar and FET devices, is shown in Fig. 2.6. The plot consists of three regions, called here the triode region, the transconductance region, and the breakdown region. In the triode region, the device conducts large currents with relatively little voltage drop, and the current is very sensitive to the drain voltage  $V_D$ , increasing rapidly as this voltage is increased. In this region, the device acts effectively as a controlled resistor. Upon applying sufficiently large drain voltage, the device enters the transconductance region, wherein the device's current becomes insensitive to the drain voltage, being determined almost entirely by the input voltage  $V_g$ . In this region, the device acts effectively as a controlled current source. The voltage at which the transition occurs between the triode and transconductance regions is generally known as the knee voltage,  $V_k$ . As can be inferred from Fig. 2.6, this voltage is usually to some degree dependant on the drive level.

<sup>1.</sup> Most of the analysis in this section is also applicable to linear amplifiers constructed of devices, such as triode vacuum tubes, that do not effectively behave as transconductors. Such devices are encountered rarely today, so the specific case applicable to solid state devices is presented here.

Upon application of enough further voltage, the device enters a breakdown regime. This region is almost always to be avoided as it is accompanied by very high currents in conjunction with high voltages, and so leads to high power dissipation and often performance degradation or destructive failure of the device. The voltage at which the transition into this region occurs is usually referred to as the *breakdown voltage*,  $V_{bk}$ . Like the knee voltage, this value can also be somewhat dependant on the drive level.

Figure 2.6: Typical active device output port characteristics.

The fourth "region" of operation is the *subthreshold* region. This region is entered by lowering the input signal level sufficiently so as to effectively reduce the device's conductivity to zero. In this region, any voltage up to the breakdown voltage will essentially conduct no current.

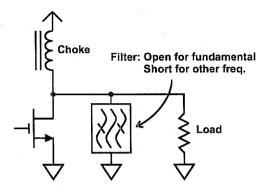

Typical transconductance amplifiers are constructed using a circuit functionally similar to the circuit in Fig. 2.7. The active device is used as a current source, driving a controlled current into a load network consisting of a harmonic filter and the resistive load to be driven. The harmonic filter is constructed so that its impedance at the fundamental frequency is very high, whereas the impedance at the harmonics is low. Typically, this filter is a parallel inductor/capacitor filter tuned to be resonant at the fundamental frequency. Using this arrangement, the impedance presented to the active device at the fundamental frequency is simply the load resistance, whereas the impedance at the

harmonics is much lower due to the filter. This has the effect of forcing the voltage across the output of the active device to be effectively sinusoidal for almost any current waveform driven by the active device, as the fundamental harmonic component of the current waveform is passed into the load resistance, whereas the higher harmonics of the current are passed through the much lower impedance of the filter and are therefore their representation in the voltage waveform is significantly reduced.

Figure 2.7: Transconductance amplifier circuit topology.

As the essential shape of the voltage waveform is constrained, the primary means whereby the amplifier performance may be varied is by modification of the current waveform used. A more complete discussion [1] of the various considerations involved in this choice would surely exceed the scope of this work, but the following sections highlight the effect that the most common choices have on the amplifier efficiency.

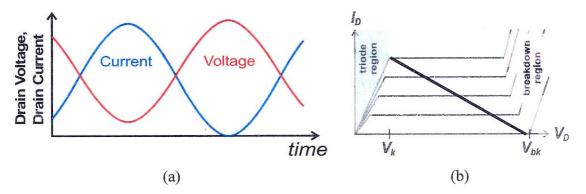

#### 2.4.1.1 Class A

In class-A mode, the active device is biased so that the device is continuously conducting current at all times. Ideally, the current through the device should duplicate exactly the shape of the input voltage signal and the dc bias current should be sufficient to ensure that the device continuously conducts positive current, and that the device remains at all times in the transconductance region, i.e. the voltage never falls below the knee voltage. Additionally, the waveforms should have a sufficiently low peak voltage to keep

the device out of the breakdown region. For the narrowband case, class-A waveforms and load line are shown in Fig. 2.8.

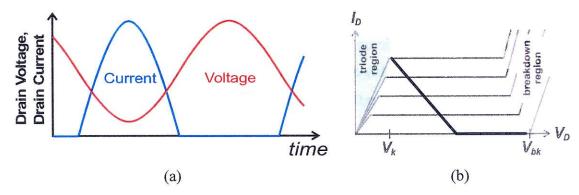

Figure 2.8: Class-A drain waveforms (a) and load line (b).

The maximum efficiency of a narrowband class A amplifier can be computed readily. The current waveform in this case is a sinusoid varying from zero to  $2I_{dd}$ :

$$I_D = I_{DD} \cdot (1 + \sin(\omega t)) \tag{2.36}$$

Similarly, the voltage is a sinusoid varying from the knee voltage  $V_k$  and  $V_{bk}$ :

$$V_D = \left(\frac{V_{bk} + V_k}{2}\right) - \left(\frac{V_{bk} - V_k}{2}\right) \sin(\omega t)$$

(2.37)

Using (2.36) and (2.37), the dc power delivered to the transistor is:

$$P_{dc} = I_{DD} \cdot \left(\frac{V_{bk} + V_k}{2}\right) \tag{2.38}$$

Similarly, the rf power delivered to the load is:

$$P_{out} = \frac{1}{2} \cdot I_{DD} \cdot \left(\frac{V_{bk} - V_k}{2}\right) \tag{2.39}$$

The drain efficiency is then found to be:

$$\eta_D = \frac{P_{out}}{P_{dc}} = \frac{1}{2} \cdot \left[ \frac{1 - V_k / V_{bk}}{1 + V_k / V_{bk}} \right]$$

(2.40)

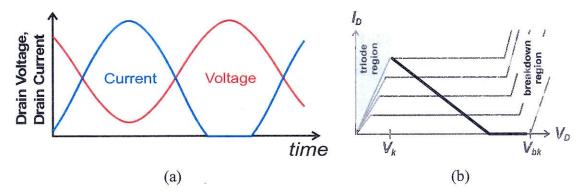

#### 2.4.1.2 Class AB, class B, class C

In order to further increase the efficiency of the transconductance amplifier, it is necessary to have at least one of the waveforms be non-sinusoidal. One common approach is to keep the voltage waveform the same as in the class-A approach, but change the current waveform so that there are periods of time wherein the active device is in a non-conducting state.

There are several advantages of this technique. First, the distortion of the current waveform can be readily generated by simply lowering the input bias to the active device so that the input voltage is sufficiently low during a part of the cycle to turn the device fully off (i.e. bring it into the subthreshold region). Thus, a sinusoidal input signal may still be used, and the input bias adjusted to vary the time during which the device is open. Additionally, by having a sinusoidal voltage waveform, the harmonic filtering requirements are relaxed.

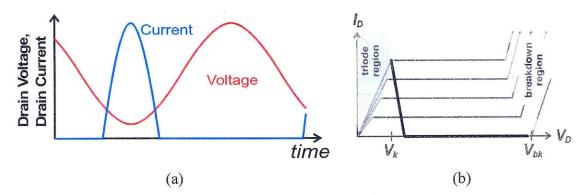

The waveforms and load-line for such an amplifier are shown in Fig. 2.9. The voltage waveform is sinusoidal as in the class-A case, but the current waveform has a period of time during which the current is zero (i.e. the device is acting as an open-circuit). As can be seen, this occurs during the time where the voltage is maximum, and so removing the current during this portion of the cycle can have a dramatic impact on the efficiency of the amplifier. This effect can also be seen in the load line, which shows the device spending the times of highest voltage in the subthreshold region, causing the line to bend away from the high loss areas of simultaneous high voltage and current.

Clearly this strategy represents a continuum of amplifier operating conditions running from the class-A case wherein the device is conducting for all but a single point in the cycle to very extreme cases wherein the device is conducting only for short pulses. In order to sensibly discuss these various cases, a terminology has been developed to classify these operating conditions. Class-A is used to denote the amplifier which conducts for a full cycle, class-B operated devices conduct for exactly half of the cycle, and class-C

Figure 2.9: Class-A/B waveforms (a) and load line (b).

Figure 2.10: Class-B waveforms (a) and load line (b).

Figure 2.11: Class-C waveforms (a) and load line (b).

operated devices conduct for less than half of the cycle. Similarly, the term class A/B is often used to denote devices which are non-conducting for less than half of the cycle. Representative waveforms and load lines for these operating classes can be seen in Figs. 2.8 to 2.11.

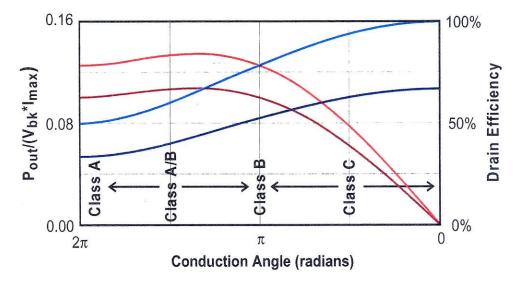

The efficiency achievable by this range of amplifiers is readily computed in a manner similar to the class-A case developed in Section 2.4.1.1. For the sake of brevity, the full analysis will not be given here, but a thorough treatment can be found in any number of texts, [e.g. 1]. The results are as follows:

$$\eta_D = \frac{1}{2} \cdot \left[ \frac{1 - V_k / V_{bk}}{1 + V_k / V_{bk}} \right] \cdot \left[ \frac{\alpha - \sin \alpha}{2 \sin(\alpha / 2) - \alpha \cos(\alpha / 2)} \right]$$

(2.41)

$$P_{out} = \frac{1}{8\pi} \cdot \left[ \frac{\alpha - \sin \alpha}{1 - \cos \alpha/2} \right] \cdot \left[ 1 - \frac{V_k}{V_{bk}} \right] \cdot V_{bk} \cdot I_{max}$$

(2.42)

where  $\alpha$  is the *conduction angle* defined to be the total number of radians during the cycle wherein the device is conducting,  $V_{bk}$  is the maximum voltage in the device waveforms, and  $I_{max}$  is the maximum current in the device waveforms. These results are plotted in Fig. 2.12.

Figure 2.12: Drain efficiency (blue) and output power (red) vs. conduction angle. The lighter shaded curves represent the ideal case where the knee voltage is zero, whereas the darker represents the case where the knee voltage is 20% of the breakdown voltage.

As can be seen, the efficiency of the amplifier can be increased arbitrarily by reducing of the conduction angle to increasingly concentrate the current into those parts of the cycle

where the voltage is low. Unfortunately, the effect of this concentration is that either the output power must be reduced or the peak current must increase, as is reflected in the falling red normalized output power curve in Fig. 2.12. Additionally, since the conduction angle is normally reduced by decreasing the bias voltage on the device input, the input rf amplitude must be increased as the conduction angle is reduced if the peak current is to remain the same. This effectively reduces the gain of the amplifier, making this technique limited to use only where the device gain is relatively high.

#### 2.4.2 Saturated Transconductance Amplifiers

Although the analysis presented in Section 2.4.1 assumes that the device voltage will not drop below the knee voltage  $V_k$  at any point during the cycle, this is not a necessary condition. An amplifier which is currently operating with the minimum voltage at the knee voltage can certainly be driven with a yet larger input, and it might be supposed that the efficiency might increase under this condition. The question then arises as to how the device waveforms will change under this *overdrive* condition.

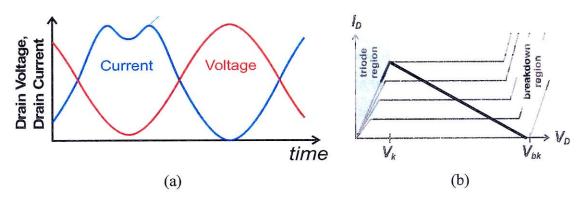

The effect can be readily evaluated by remembering that the knee voltage is defined as the transition between the transconductance and linear regions of the device operating characteristic. If the amplitude of the voltage waveform is to increase, and if the resonator forces the voltage to remain sinusoidal, then the voltage will be forced to drop below the knee voltage and the device will enter the triode region. Since the current in this region is always lower than the current that would be expected from the device for the same drive level, had the voltage been high enough for it to be operating in the transconductance region, the current waveform will begin to distort due to current reductions during the times where the voltage is below the knee. This effect can be seen in two example device waveforms of Fig. 2.13, a class-A example, and Fig. 2.14, a class B example.

This waveform distortion has several effects. Most obviously, the output power is higher, which is readily seen since the amplitude of the voltage waveform has been increased. The effect on efficiency is not so easy to evaluate, however. The distortion of

Figure 2.13: Saturated class-A waveforms (a) and load-line (b).

Figure 2.14: Saturated class-B waveforms (a) and load-line (b).

the current waveform has resulted in a redistribution of the current away from those times wherein the voltage is lowest, tending to reduce the efficiency. At the same time, the voltage for all points in the "negative" half of the cycle is reduced, so that the loss associated with this part of the cycle where the currents are the highest will to decrease, tending to increase the efficiency. The overall effect on efficiency is a result of these two processes, the net effect being to increase the efficiency very slightly for small levels of overdrive but to actually reduce it for significant levels of overdrive. The benefits in efficiency and output power for overdriving this type of amplifier are relatively modest, and the performance after design optimization is usually similar to the non-overdriven case analyzed previously [1].

30

#### 2.4.3 Saturated Amplifiers with Harmonic Tuning

In evaluating the saturated amplifier in the previous section, it should be clear that the principle shortcoming of the technique is its insistence on keeping a sinusoidal voltage waveform. This limits the fundamental voltage component of the voltage waveform to an absolute maximum of  $V_{bk}/2$ , limiting the achievable output power for a given peak voltage. More importantly, it limits the time period during which the voltage is near zero to only the small portion of the conduction angle where the sinusoidal voltage is at a minimum. In order to improve efficiency, then, the designer is forced to concentrate the device's current into this time period in order to achieve efficiency. Since the average (dc) current must be kept high enough to supply the active device with dc power according to (2.34), the peak current then must be made very high, causing excessive device strain and a lower achievable output power for a given peak current level.

In order to achieve additional efficiency under overdrive conditions, it is necessary to allow the waveform to take on non-sinusoidal shapes. Conceivably, under such relaxed constraints, the voltage waveform may be able to also take on a shape wherein it is nearly zero for some considerable time during which the device conducts current, thereby increasing the efficiency in much the same way as is done by reducing the current waveform duty cycle of transconductance amplifiers. By suitably adjusting the drive conditions and the impedances presented to the active device at the harmonic frequencies, harmonics could be added in the correct amplitude and phase so that the valley of the voltage waveform becomes "flatter".

There are any number of ways of doing this [17-19], but perhaps the most conceptually simple and certainly the most well studied is the class-F amplifier [15,16,1]. The basic idea of the class-F amplifier is to start with the class-B amplifier explored in Section 2.4.1.2, and begin to add odd harmonics to the voltage waveform so that it begins to increasingly resemble a square wave. Since the half-sinusoid current waveform contains no even harmonic overtones, the impedance at these added odd harmonics should be tuned to open-circuit, in principle allowing the harmonic voltages to exist without

harmonic currents. The class-F amplifier, then, attempts to achieve an N harmonic approximation to a square voltage waveform by open-circuiting the odd overtones up to the  $N^{\text{th}}$  harmonic. As in the class-B case, the even harmonics are tuned to short-circuit, allowing the even harmonics in the half-sinusoidal class-B current waveform to exist without resulting in undesirable even harmonic voltages. A circuit implementing this tuning is shown in Fig. 2.15.

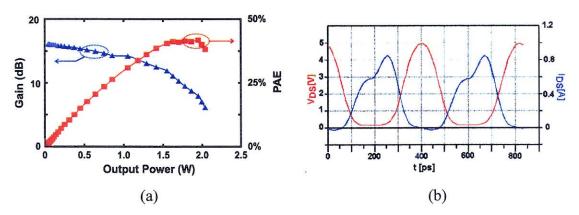

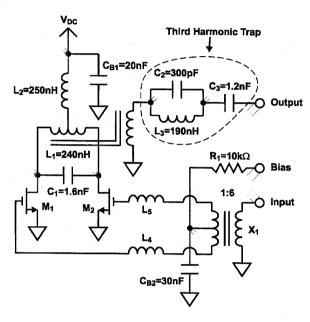

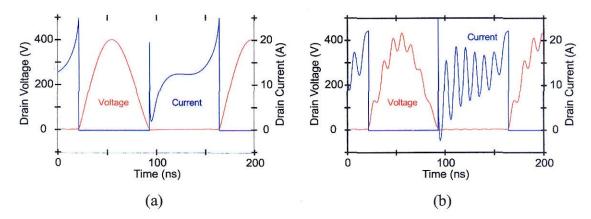

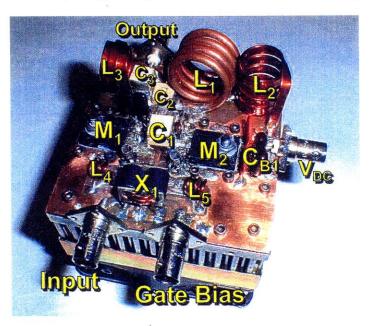

Figure 2.15: Class-F circuit conceptual implementation.