### TOPOLOGY AND ANALYSIS IN

### PWM INVERSION, RECTIFICATION, AND CYCLOCONVERSION

Thesis by

Khai Doan The Ngo

In Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

> California Institute of Technology Pasadena, California

> > 1984

(Submitted May 14, 1984)

# C 1984

Khai Doan The Ngo

All Rights Reserved

# iii

# to my parents

#### ACKNOWLEDGEMENTS

I would like to thank my advisors, Professors S. M. Ćuk and R. D. Middlebrook for welcoming me to their group at Caltech and bringing me up in Power Electronics. They have offered me the opportunity to explore an area still new and challenging to many of us. They have given me the freedom to select the research direction and to pursue it to our mutual satisfaction. I wish I could contribute more than just this small thesis to deserve their generous givings.

I am indebted to the Office of Naval Research and Naval Ocean Systems Center for their financial supports during the last few years. My special thanks go to Caltech for the Graduate Teaching Assistantships and the President's Fund that initiates research activities in the ac conversion field.

I would like to give credits to other members of the Caltech Power Electronics Group for their contributions to the content and format of this thesis. I am particularly grateful to Mr. X. L. Ma who suggests the sixstepped PWM for the buck rectifier.

I appreciate the generosity of all who have made my days at Caltech a unique, valuable experience. My gratitude to the Institute and memory of those yesterdays shall last.

iv

#### ABSTRACT

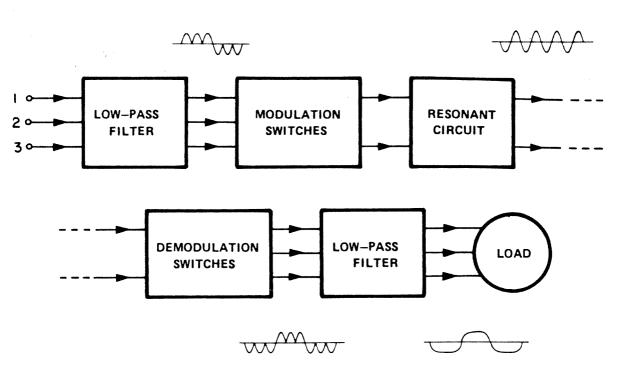

Topologies and analysis techniques in switched-mode dc conversion (dc-to-dc), inversion (dc-to-ac), rectification (ac-to-dc), and cycloconversion (ac-to-ac) are unified in this thesis. The buck, boost, buck-boost, and flyback topologies are used to demonstrate that familiar dc converters can be extended into equivalent ac converters. Although some of these are presented as fast-switching circuits, they have also been found in slowswitching applications. Thus, topology is the unifying factor not only over four fields of power electronics, but also within each field itself.

Describing equations are used to characterize low-frequency components of the inputs and outputs in fast-switching networks containing filters, excited by dc or balanced sinusoidal sources, and pulse-widthmodulated by dc or balanced sinusoidal duty ratios. They are first written in the stationary (abc) reference frame and then transformed to the rotating (ofb) coordinates. In the ofb coordinates, all balanced ac converters with any number of phases are reduced to a set of continuous, time-invariant differential equations describing a two-phase equivalent.

Steady-state, dynamic, and canonical models are then solved in the rotating frame of reference. Emphasis is stressed on circuit ideality sinusoidal outputs for sinusoidal inputs even though a switched network is nonlinear - and effects of filters on steady-state and small-signal frequency responses. These results are similar for a dc converter, inverter, rectifier, and cycloconverter of the same topology; this similarity again confirms that

v

the four converters are closely related. The cycloconverter is thus established as the generalized converter that degenerates to the other three under special input and output frequencies.

Practical issues discussed include the realization of the switches, modification of drive and topology for bidirectionality of power flow, isolation, switched-mode impedance conversion, and measurement techniques.

## TABLE OF CONTENTS

| ACKNOWLEDGEMENTS |                                        |                                                                                                                                                                                |                                  |  |  |

|------------------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|--|--|

| ABSTRACT         | ſ                                      |                                                                                                                                                                                | v                                |  |  |

| INTRODUC         | CTION                                  |                                                                                                                                                                                | 1                                |  |  |

| CHAPTER          | 1                                      | ANALYSIS OF FAST-SWITCHING PWM CONVERTERS                                                                                                                                      | 9                                |  |  |

|                  | 1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6 | Characterization of the Switch<br>Describing Equations of Fast-Switching PWM Converters<br>Transformation<br>Steady-State Analysis<br>Small-Signal Dynamics<br>Canonical Model | 10<br>12<br>20<br>25<br>28<br>31 |  |  |

| PART I           |                                        | SWITCHED-MODE INVERSION                                                                                                                                                        | 37                               |  |  |

| CHAPTER          | 2                                      | REVIEW OF EXISTING INVERTERS                                                                                                                                                   | 3 <b>9</b>                       |  |  |

|                  | 2.1<br>2.2<br>2.3                      | Inverters Switched at Low Frequency<br>Inverters Switched at Medium Frequency<br>Inverters Switched at High Frequency                                                          | 40<br>48<br>53                   |  |  |

| CHAPTER          | 3                                      | FAST-SWITCHING SINUSOIDAL PWM INVERTERS                                                                                                                                        | 59                               |  |  |

|                  | 3.1<br>3.2<br>3.3<br>3.4               | Description of Topologies<br>Steady-State Performance<br>Small-Signal Dynamics<br>Canonical Model                                                                              | 60<br>74<br>79<br>87             |  |  |

| viii     |                          |                                                                                                   |                          |  |  |  |

|----------|--------------------------|---------------------------------------------------------------------------------------------------|--------------------------|--|--|--|

| CHAPTER  | 4                        | PRACTICAL ASPECTS OF FAST-SWITCHING<br>SINUSOIDAL PWM INVERTERS                                   | 99                       |  |  |  |

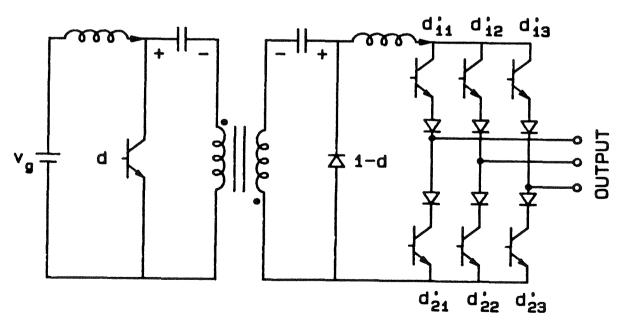

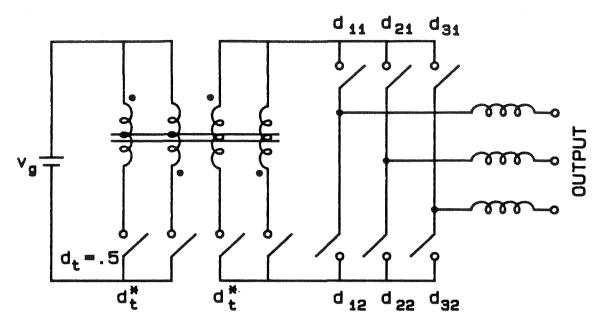

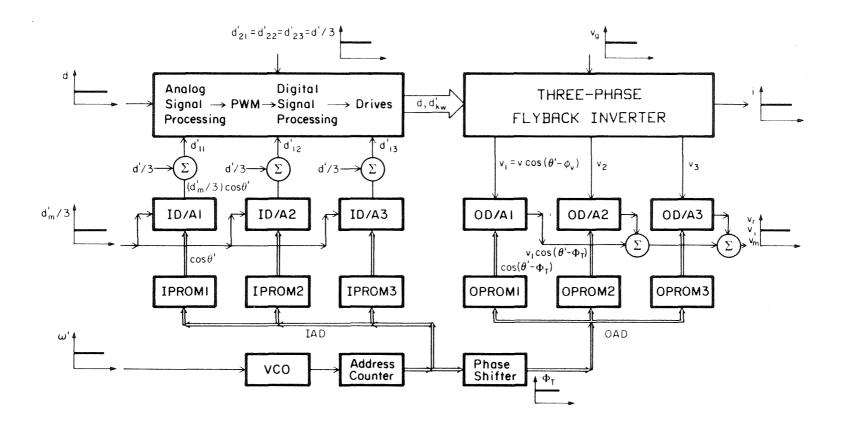

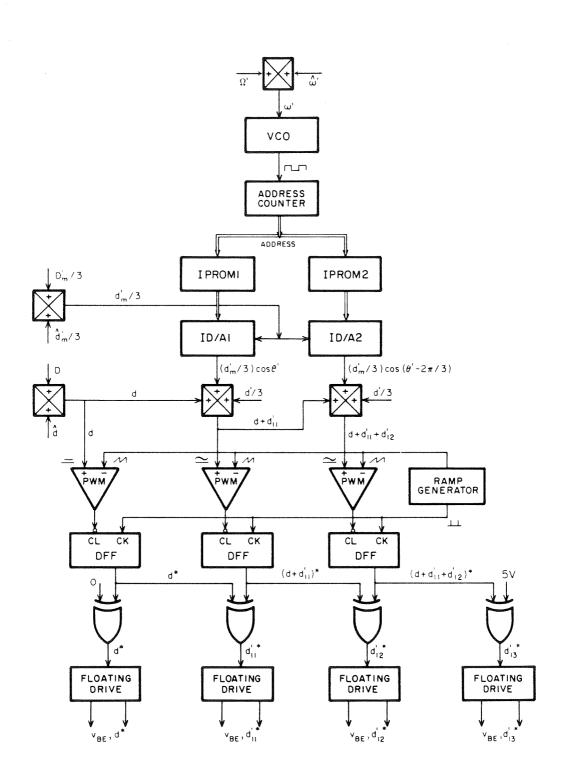

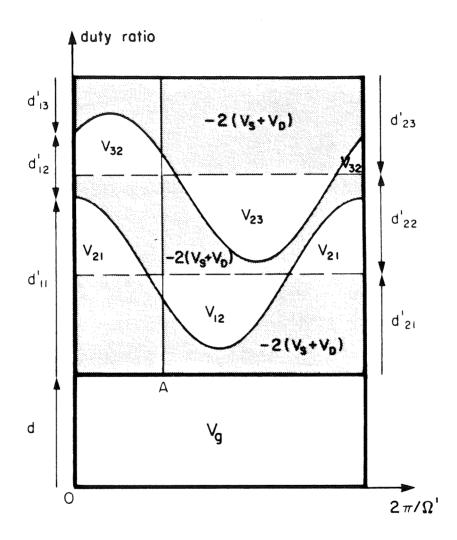

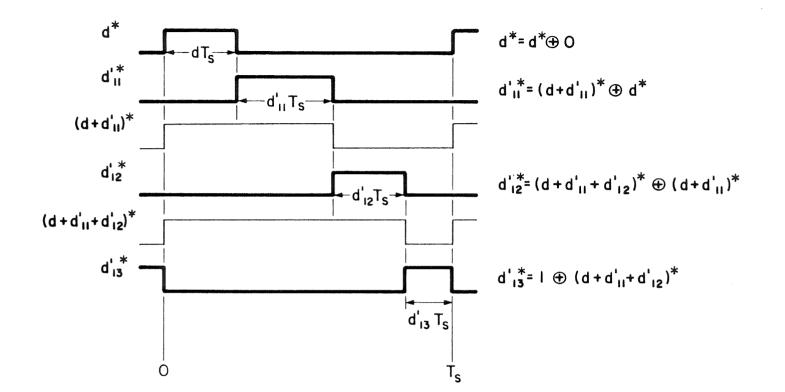

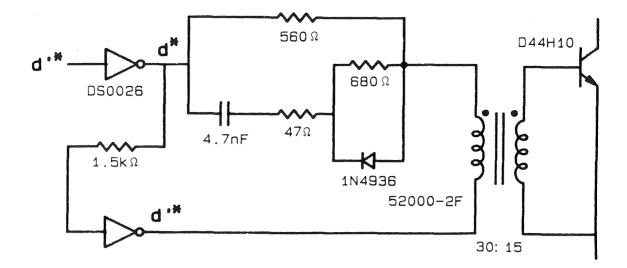

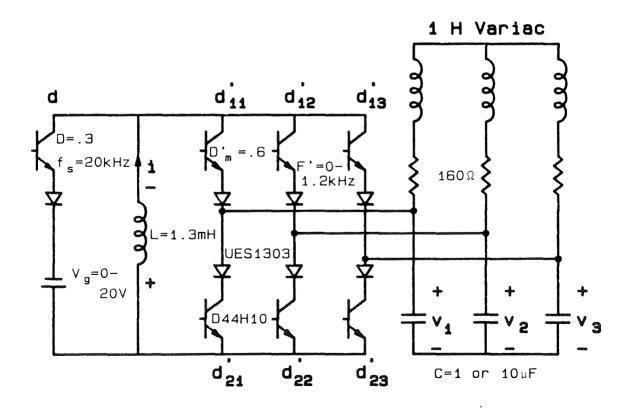

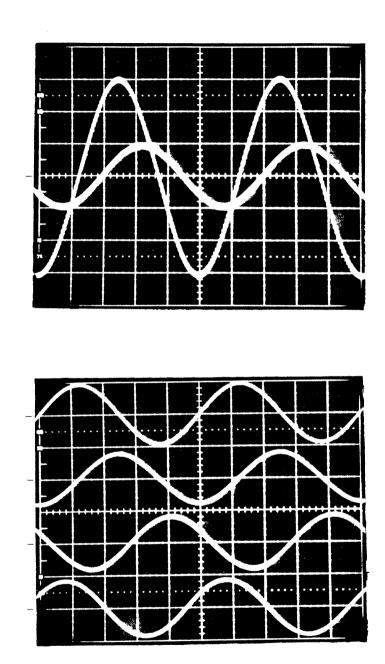

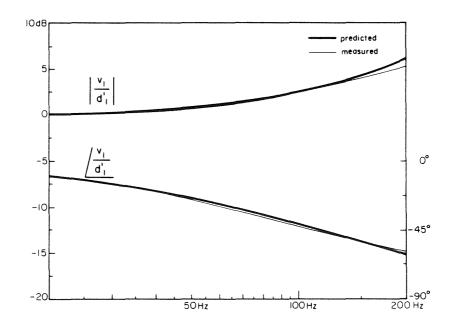

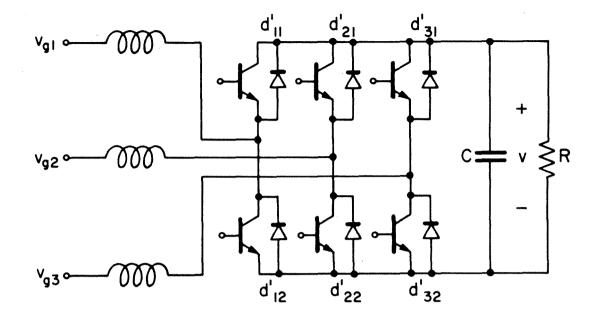

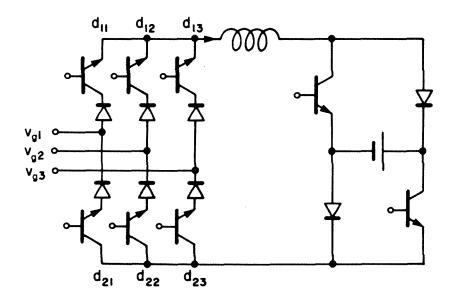

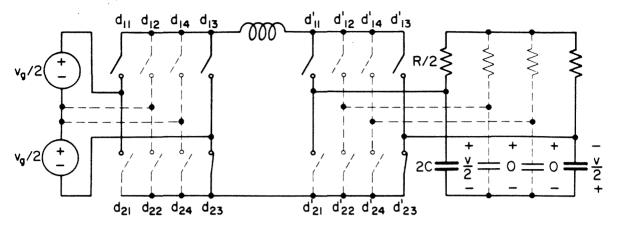

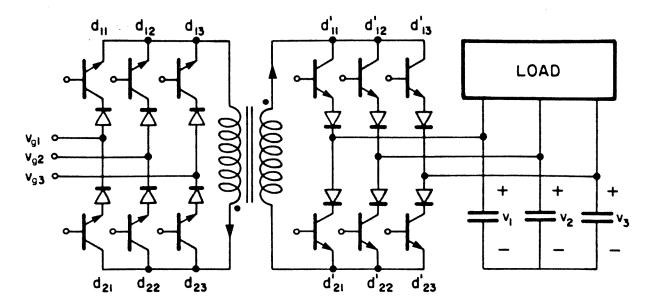

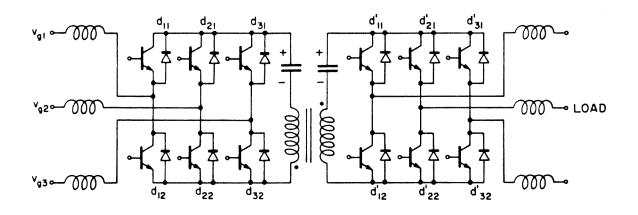

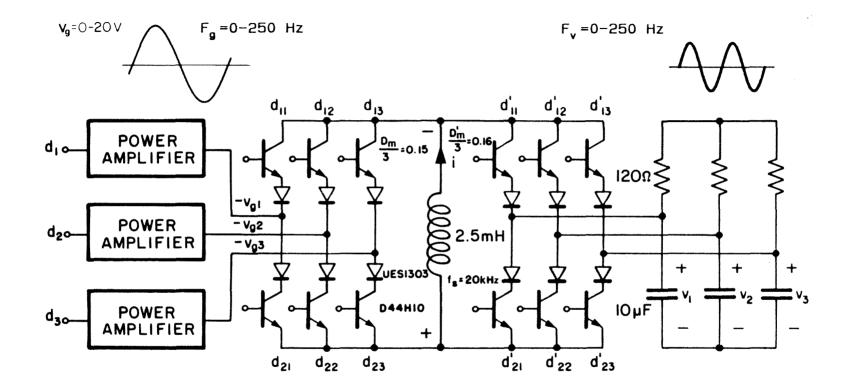

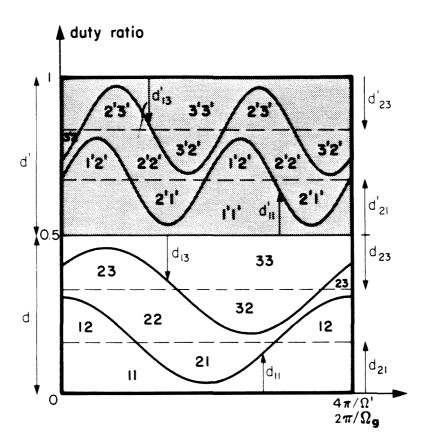

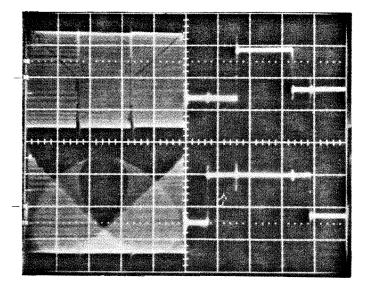

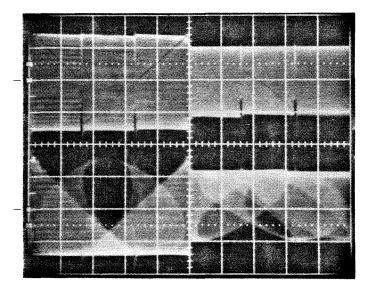

|          | 4.1<br>4.2<br>4.3<br>4.4 | Three-Phase Implementation<br>Isolation<br>Measurement Principle<br>Experimental Verification     | 99<br>116<br>119<br>122  |  |  |  |

| PART II  |                          | SWITCHED-MODE RECTIFICATION                                                                       | 143                      |  |  |  |

| CHAPTER  | 5                        | REVIEW OF EXISTING RECTIFIERS                                                                     | 145                      |  |  |  |

|          | 5.1<br>5. <b>2</b>       | Rectifiers Switched at Low Frequency<br>Rectifiers Switched at High Frequency                     | 147<br>153               |  |  |  |

| CHAPTER  | 6                        | FAST-SWITCHING SINUSOIDAL PWM RECTIFIERS                                                          | 1 <b>6</b> 5             |  |  |  |

|          | 6.1<br>6.2<br>6.3<br>6.4 | Description of Topologies<br>Steady-State Performance<br>Small-Signal Dynamics<br>Canonical Model | 165<br>177<br>186<br>190 |  |  |  |

| CHAPTER  | 7                        | PRACTICAL ASPECTS OF FAST-SWITCHING<br>SINUSOIDAL PWM RECTIFIERS                                  | 197                      |  |  |  |

|          | 7.1<br>7.2<br>7.3        | Three-Phase Implementation<br>Isolation<br>Fast-Switching Impedance Converters                    | 197<br>205<br>208        |  |  |  |

| PART III |                          | SWITCHED-MODE CYCLOCONVERSION                                                                     | 213                      |  |  |  |

| CHAPTER  | 8                        | REVIEW OF EXISTING CYCLOCONVERTERS                                                                | <b>2</b> 15              |  |  |  |

|          | 8.1<br>8.2               | Cycloconverters Switched at Low Frequency<br>Cycloconverters Switched at High Frequency           | <b>2</b> 15<br>222       |  |  |  |

,

| CHAPTER  | 9                               | FAST-SWITCHING SINUSOIDAL PWM CYCLOCONVERTERS                                                                                          | 229                      |

|----------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

|          | 9.1<br>9.2<br>9.3<br>9.4        | Description of Topologies<br>Steady-State Performance<br>Canonical Model<br>Reduction of Cuclesconverters to                           | 230<br>246<br>252        |

|          | 9.4                             | Reduction of Cycloconverters to<br>Dc Converters, Inverters, and Rectifiers                                                            | 258                      |

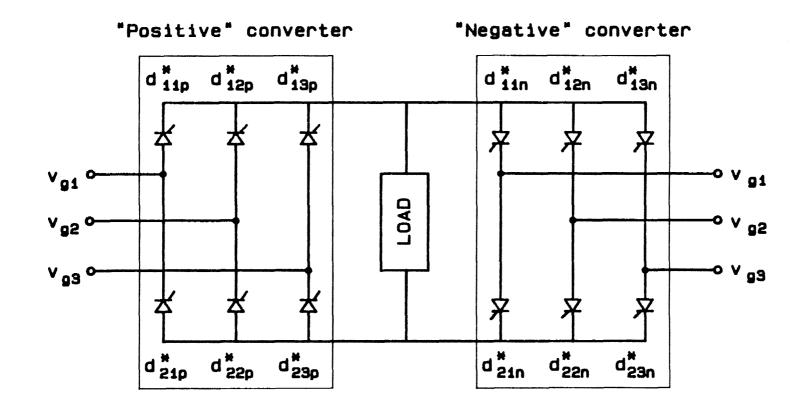

| CHAPTER  | 10                              | PRACTICAL ASPECTS OF FAST-SWITCHING<br>SINUSOIDAL PWM CYCLOCONVERTERS                                                                  | 263                      |

|          | 10.1<br>10.2                    | Three-Phase Implementation<br>Isolation                                                                                                | 263<br>271               |

|          |                                 | Fast-Switching Impedance Converters<br>Experimental Flyback Cycloconverter                                                             | 274<br>277               |

| CONCLUS  | ION                             |                                                                                                                                        | 287                      |

| APPENDIC | ES                              |                                                                                                                                        | <b>29</b> 5              |

| APPENDIX | A                               | TOPOLOGY AND ANALYSIS IN DC CONVERSION                                                                                                 | 297                      |

|          | A.1<br>A.2<br>A.3<br>A.4<br>A.5 | Description of Topologies<br>Steady-State Performance<br>Small-Signal Dynamics<br>Canonical Model<br>Relation of State-Space-Averaging | 297<br>299<br>299<br>301 |

|          |                                 | to Describing Equation Technique                                                                                                       | 305                      |

| APPENDIX | В                               | THE ABC-OFB TRANSFORMATION                                                                                                             | 309                      |

| REFEREN  | CES                             |                                                                                                                                        | <b>3</b> 11              |

,

#### INTRODUCTION

The four areas of switched-mode power conversion are *dc conversion* (dc-to-dc), *inversion* (dc-to-ac), *rectification* (ac-to-dc), and *cycloconversion* (ac-to-ac). Although dc converters as well as inverters, rectifiers, and cycloconverters have been coexisting for a long time, their applications and advances in semiconductor technology have led them to flourish in different directions. Dc converters serve delicate and low-power circuits, such as signal-processing ones, that require tight regulation, high-quality outputs, and fast dynamic responses. Owing to these high standards, dc power supplies have evolved to a close-to-ideal stage. Inverters, rectifiers, and cycloconverters, on the other hand, encounter more rugged and higher power applications, such as motor drives, that can tolerate poor waveforms and slow dynamic performance. Thus, harmonic heating, torque pulsation, poor power factor, electromagnetic interference, sluggish response, and so on, have been common problems generated by these high-power units.

The difference in application specifications, however, is only an excuse for the outperformance of dc converters over ac converters (i.e., inverters, rectifiers, and cycloconverters). The power-speed limitation of semiconductor devices, used to realize the switch, is the principal force that segregates the disciplines of power electronics. Current developments in switching devices, for instance, allow the transistor to switch a few tens of kVA below  $20 \, kHz$ ; the gate-turn-off (GTO) device, a few hundreds of kVA below  $500 \, Hz$ . Dc

converters fall in the low-power range and, hence, enjoy the advantages given by the fast bipolar junction transistor (BJT) and field-effect transistor (FET). High-power ac converters lose these benefits because they can use only the slow thyristor. The performance of medium-power converters, fortunately, has been improved recently owing to progress made in GTO fabrication.

Many advantages of fast switching are apparent from comparison of existing dc and ac power processors. First, *filters* are used more freely because their size diminishes with increasing switching frequency. They attenuate switching harmonics and, hence, smooth out terminal waveforms. They also absorb mismatches between stiff voltage or current sources to suppress excessive current or voltage spikes.

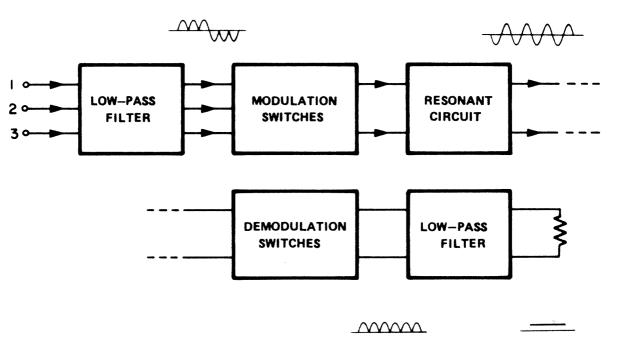

Second, reactive elements, together with high switching frequency, allow the development of *novel topologies* with *new operating principles*. This development can be carried out in two forms. In the simpler one, existing topologies are preserved, but their switches are operated according to some new strategies easier to implement with fast switching. *Pulse-width modulation (PWM)* and *resonance* are two well-known examples of such highfrequency energy processing techniques; the PWM category itself consists of a variety of drive policies. In the more advanced development method, innovative topologies are synthesized by topological manipulation of inductors, capacitors, and switches [3 and 4]. The number of useful circuit configurations increases quickly as more reactive components enter the power stage. A proof of this expansion is the large family of converters that have evolved in the dc conversion area.

Third, a larger number of topologies introduces a more diversified list of properties that encompass a broader range of applications. Thus, the *dc gain* does not have to be only of buck (step-down), but can also be of boost (step-up) or buck-boost type. Additional *control parameters* are available so that, for instance, the output amplitude can be adjusted not at the expense of input power factor. *Dynamic response* can be made very fast by increasing the switching frequency and, consequently, reducing the value of energy-storage components. *Isolation* is feasible because the isolation transformer is small and economical.

Fourth, it is possible to generate dc or sinusoidal waveforms at the input and output of the power processor in an open-loop fashion using only dc or sinusoidal control functions. This property is to be distinguished from the smoothness of waveshape discussed earlier; the dc or sinusoidal characteristic describes the low, useful frequency components of the spectrum while the smoothness property refers to the attenuation of switching harmonics. The high-quality output alleviates harmonic stresses at both the load and source, facilitates the understanding of the power stage, and simplifies the design of the overall system.

In the last few decades, the aforementioned attributes have been confined to dc converters because a sufficiently fast switch has not been available at the power level of most ac applications. Recently, however, breakthroughs in semiconductor fabrication have improved the speed of the switches in medium-power range. These progresses, together with the growing concern to reduce the contamination of the electrical environment by slow-switching circuits, have motivated the extension of fast-switching technology from the dc conversion into the inversion, rectification, and

cycloconversion fields. As dc conversion, ac conversion can be accomplished by either the *resonance* or the PWM principle. Although original steps have been reported in both directions, a great deal of fundamental works still need to be done. Since this task certainly takes more than the scope of one thesis, only the PWM area is enlightened here. It is hoped that analogous studies will be carried out for resonance conversion in the near future.

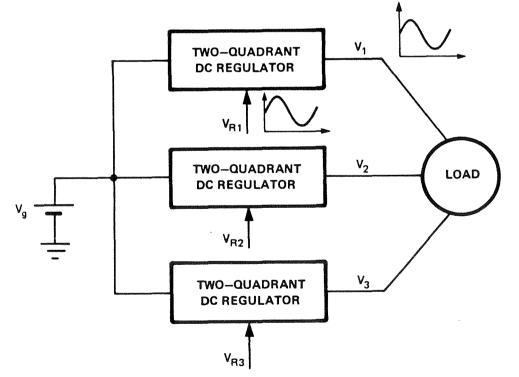

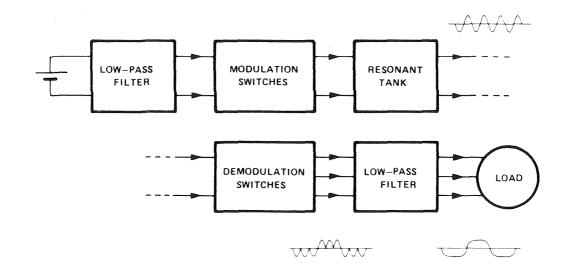

As many other new disciplines, fast-switching PWM ac conversion has started slowly. One of the first efforts parallels many dc regulators to create a multiple-input or multiple-output structure [19 and 28]. Such an approach has not received much attention because it ignores the polyphase synergism and, hence, uses too many components inefficiently. More [37] to synthesize *genuine*, basic thoughts are put in polyphase cycloconverters that require a minimal amount of switches to synthesize sinusoidal input and output waveforms. Nevertheless, reactive elements are assigned only secondary importance, and their topological function ignored. Because of this de-emphasis of the role of inductors and capacitors, [37] fails to discover a host of more useful ac-to-ac converters. Therefore, a unified, complete picture that describes basic and derived PWM topologies in all four areas of switched-mode conversion, explains their performance systematically, and displays their relationship still needs to be proposed.

A survey of the previous references reveals further that the analysis of fast-switching ac converters has been inadequate. *State-space-averaging* [2], intended for dc converters that have simple switching structures periodic at the switching frequency, cannot be generalized naturally to ac converters that contain a *large* amount of switches whose operations are *not* periodic at the switching frequency. Another modeling method has been

introduced recently in [1] for circuits without (or with negligible) filter components. Regrettably, it does not cover most practical cases in which filter corners, placed sufficiently low to attenuate the switching noise, do interfere with steady-state as well as dynamic performances. Therefore, a generalized analysis technique that represents with improved accuracy the steady-state and dynamic behaviors of fast-switching PWM dc converters, inverters, rectifiers, and cycloconverters still needs to be established.

Fortunately, the describing equation technique [10] has been devised for slow-switching ac converters. Since this method is very general, it applies to fast-switching PWM dc and ac networks as well. Describing equation is thus the unified analysis technique over all areas of power electronics and all ranges of switching frequency. Accuracy depends, of course, on the switching strategy, e.g., six-stepped, PWM, or something else.

The preceding two paragraphs embody the overall objectives of this thesis. The details of these objectives are:

- to revise analysis techniques for fast-switching PWM converters;

- to describe fast-switching open-loop

- inverter topologies that invert a dc input into sinusoidal

balanced polyphase outputs,

- rectifier topologies that rectify sinusoidal balanced polyphase inputs into a dc output, and

- cycloconverter topologies that convert sinusoidal balanced polyphase inputs into sinusoidal balanced polyphase outputs

all using sinusoidal pulse-width modulation; and

- to establish a *topological relationship* among dc converters, inverters, rectifiers, and cvcloconverters.

Most important in the above are the open-loop and sinusoidal control constraints imposed upon the power processors destined to generate ideal inputs and outputs. These strict criteria exclude the simplistic use of topologies with distorted outputs, for sinusoidal inputs, and then relying on feedback loops to suppress nonlinear harmonics. This thesis proposes to solve a more fundamental problem: to search for open-loop switched-mode networks that require only easy-to-synthesize sinusoidal functions to produce dc or sinusoidal quantities. Closed-loop operation is reserved to regulate, not to purify, output waveforms.

Since the analysis technique is universal to all fast-switching PWM converters whose useful bandwidth is restricted sufficiently below the switching frequency, it is discussed first in Chapter 1 without reference to any class of circuits. The *describing equation* method is established as the standard modeling procedure for the rest of the thesis. A procedure to derive the describing equations of a switched network is explained, and subsequent manipulations of these equations toward steady-state, dynamic, and canonical models investigated.

The next nine chapters are grouped into three parts: Part I for Inversion; Part II, Rectification; and Part III, Cycloconversion. The first chapter of each part reviews previous contributions in the respective field. The second details the topologies and studies their performance using the analysis technique outlined in Chapter 1; the topological relationship among the four kinds of converters is formulated in the last section of Chapter 9. The third chapter discusses practical aspects of the converters, such as

switch implementation, isolation, bidirectionality of power flow, impedance conversion, measurement principle, and so on, and verifies experimentally the theory predicted in the previous chapter.

The appendices at the end review dc conversion and the abc-ofb coordinate transformation used to simplify the analysis of balanced polyphase ac converters.

#### CHAPTER 1

#### ANALYSIS OF FAST-SWITCHING PWM CONVERTERS

This chapter consists of six sections. The first section reviews the characterization of a switch: its throws, switching functions, and *duty ratios*. The second section derives the *describing equations* of a switched-mode converter which identify duty ratios as control parameters. The third section transforms these equations to a new coordinate system in which all balanced polyphase ac circuits are represented by their *dc equivalents*. The last three sections then solve the transformed, time-invariant equations for their steady-state formulas, perturb them for their small-signal dynamics, and linearize them for their canonical model.

In what follows, the "boost inverter" merely serves as a concrete example of the general results. To fully appreciate the *analysis* methodology, it is best to disregard such *topological* issues as where this topology comes from, what it does, and, above all, *how it is switched*. As throughout the thesis, the switches here are assumed to be lossless, infinitely fast, and four-quadrant (i.e., they block and conduct in both directions); likewise, the components of all phases match and are ideal.

#### 1.1 Characterization of the Switch

Unlike many dc converters, which have only one double-throw switch, most polyphase ac converters contain two or more multiple-throw switches. Ac structures are thus more difficult to comprehend unless their switches are characterized in a systematic manner. Hence, this section is dedicated to the specification of a switch. To start, "switch" in this study is *not* used interchangeably for "transistor" as in the literature; instead, it simply refers to the device described below.

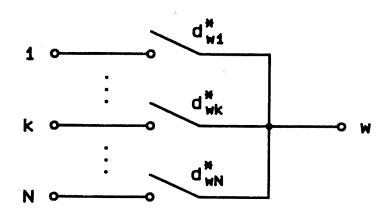

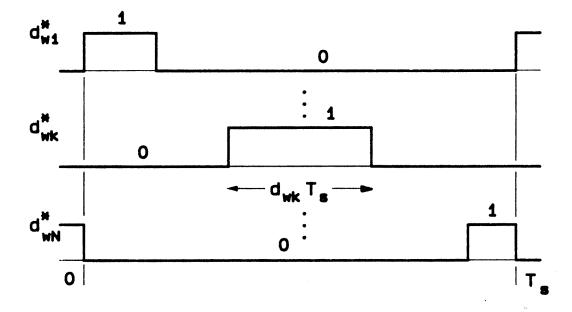

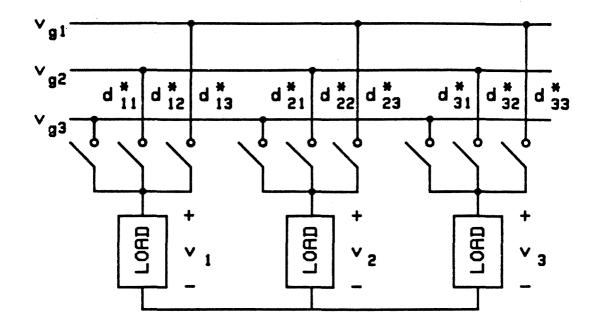

As is delineated in Fig. 1.1, an *N*-throw switch consists of *N* throws that connect pole w to terminals 1, ..., k, ..., and *N* in each switching period. The operation of each throw is specified by the switching function  $d_{wk}^{*}$ , where asterisk (\*) denotes switching function, which is one when the throw is closed and zero when the throw is open; the set of switching functions for the switch of Fig. 1.1 is illustrated in Fig. 1.2. A switch thus satisfies two constraints: only one switching function is high, and all switching functions must add up to one at any instant. The first constraint means that the position of the pole is always determinate while that of a throw is not. In other words, the pole is always connected to one of the *N* throws while a throw may be attached to nowhere. Hence, the open end of an inductor, whose current must flow somewhere, must be assigned to the pole, not a throw, of a switch.

The average of the switching function  $d_{wk}^*$  over each period  $T_s$  is the duty ratio  $d_{wk}$ . If  $d_{wk}$  varies at a frequency sufficiently slower than the switching frequency, it can be approximated to the continuous low-frequency component of the "quasi-periodic (at period  $T_s$ )"  $d_{wk}^*$ . In accordance with

Fig. 1.1 N-throw switch connecting pole w to positions 1,..., k,..., N.

Fig. 1.2 Switching function  $d_{wk}^*$  and duty ratio  $d_{wk}$ .

the second constraint in the previous paragraph, all duty ratios of the same switch should add up to one:

$$\sum_{k=1}^{N} d_{wk} = 1 \tag{1.1}$$

Therefore, at most (N-1) of the N throws can be controlled independently.

In summary, a multiple-throw switch can be characterized by its *switching functions* and *duty ratios*. The switching function, either one or zero, describes the on or off state of each throw. The duty ratio is the average of the switching function over a switching period; there are (N-1) independent duty ratios for an N-throw switch.

#### 1.2 Describing Equations of Fast-Switching PWM Converters

This section first obtains the *switching equations* of a *general* switched network, which can be of resonance, PWM, or any other type. The restriction to PWM is then invoked to derive the *describing equations* of fast-switching PWM converters.

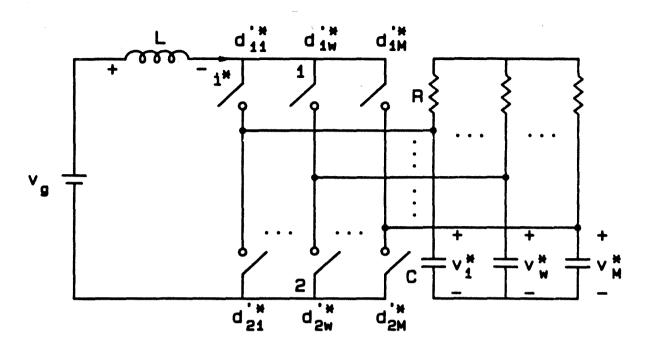

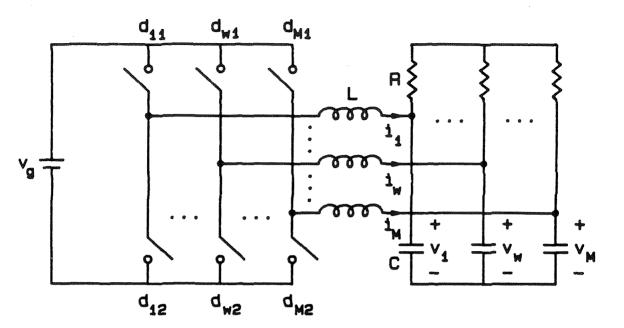

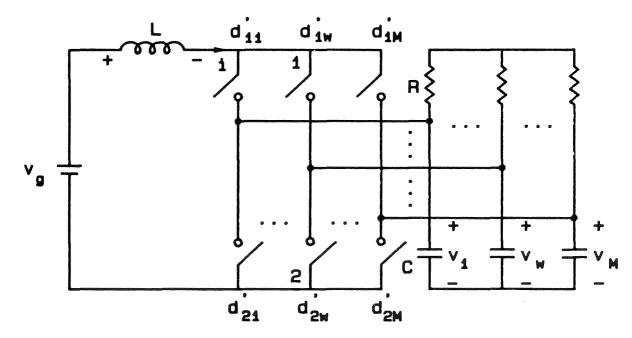

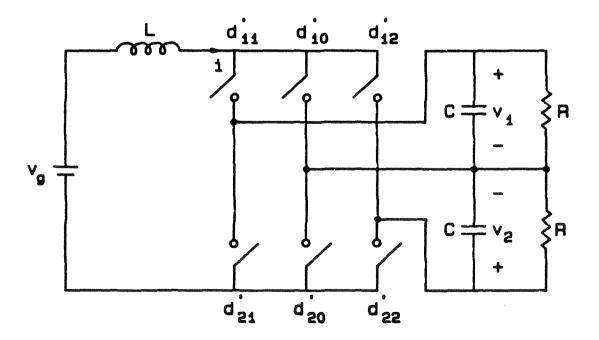

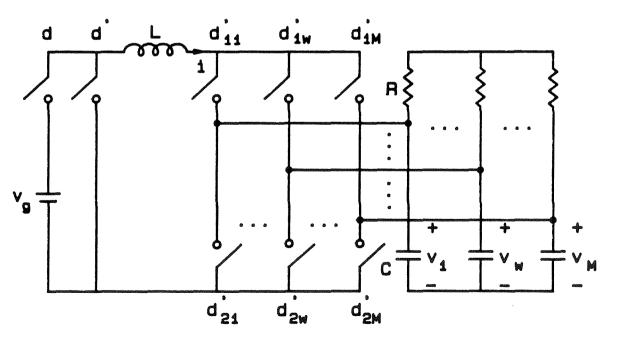

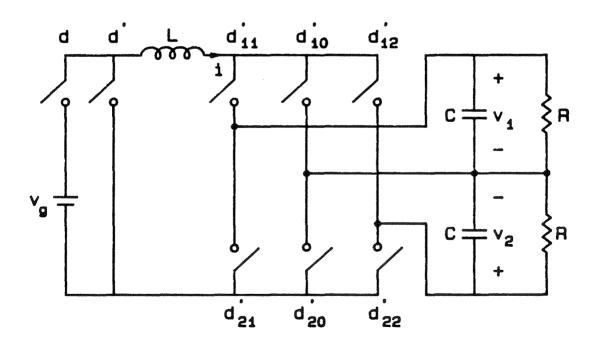

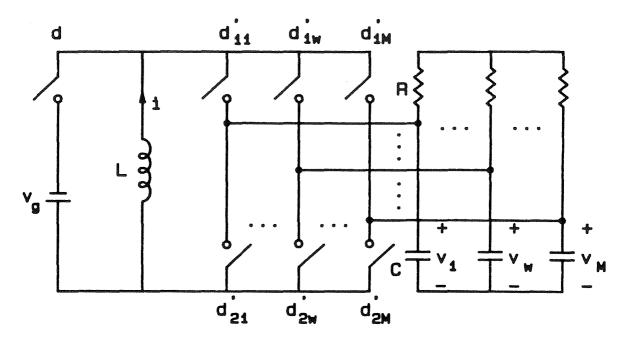

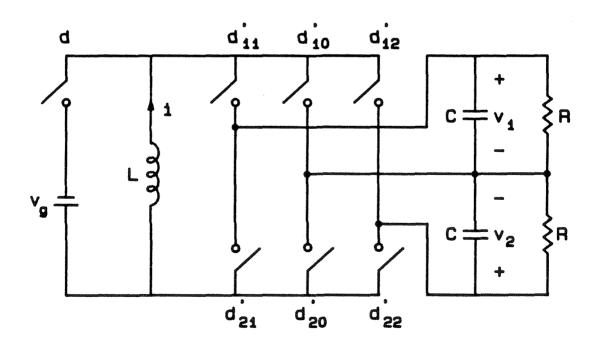

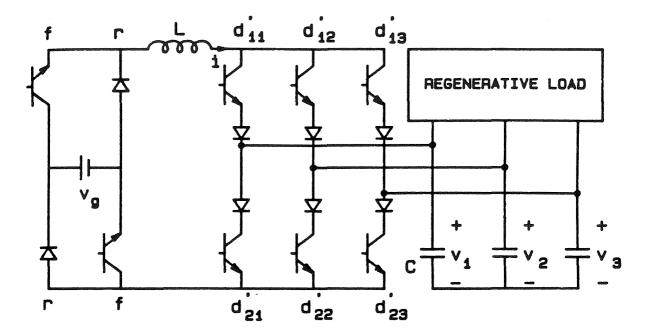

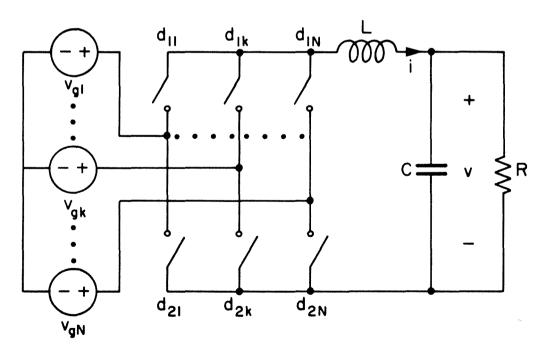

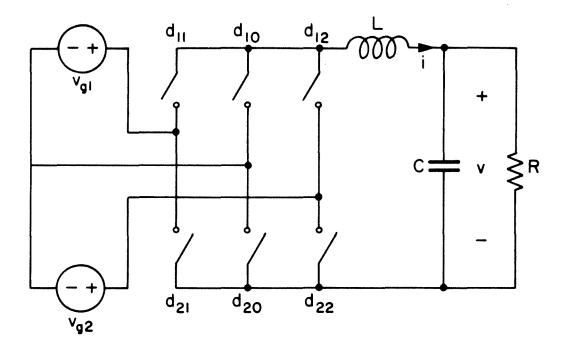

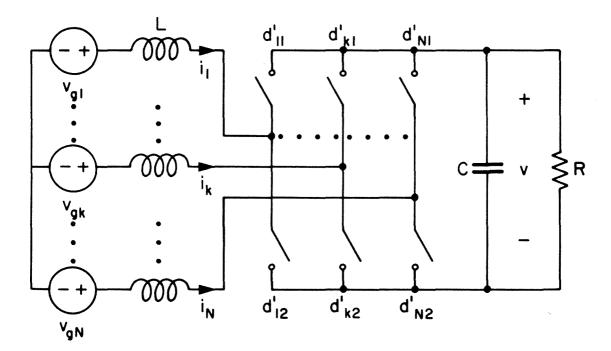

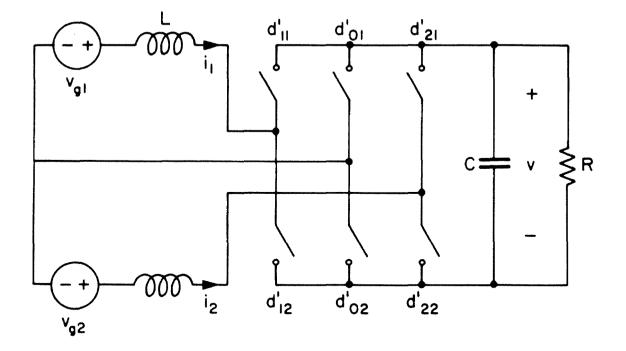

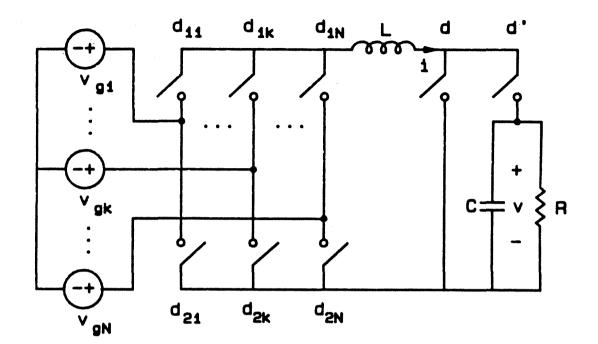

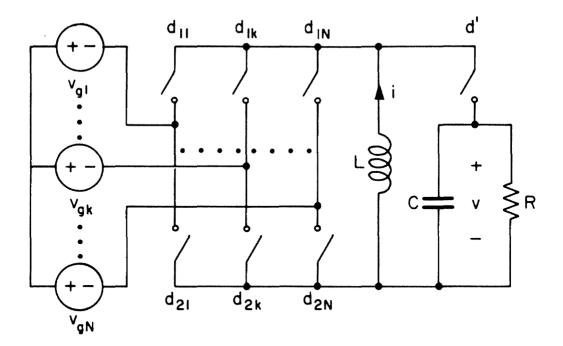

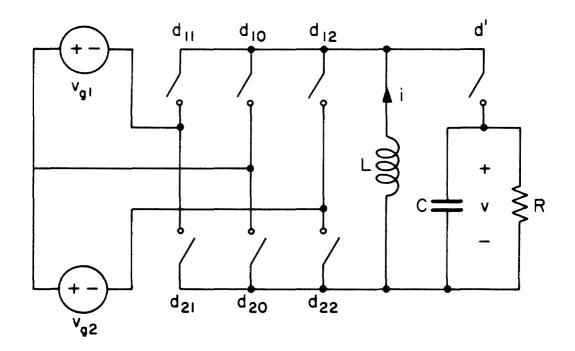

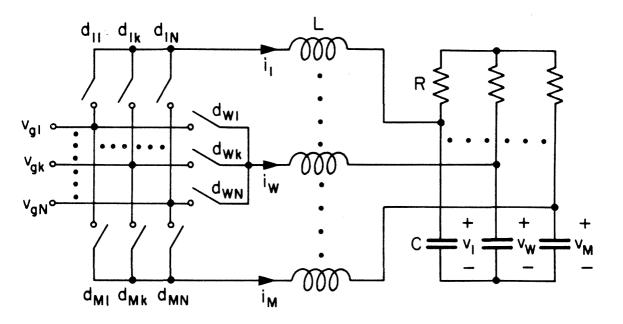

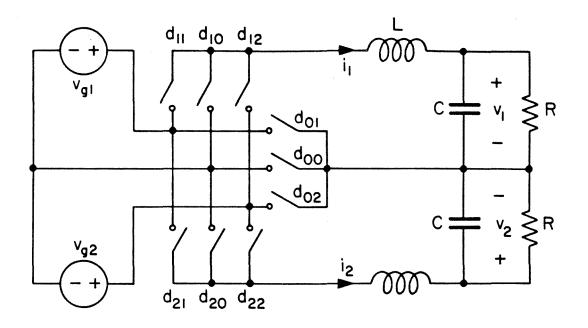

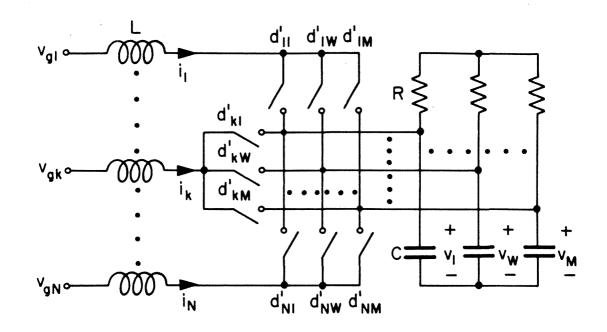

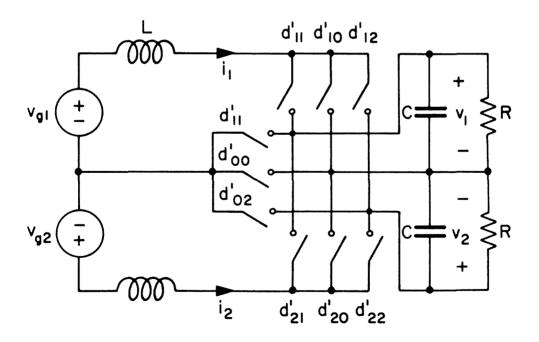

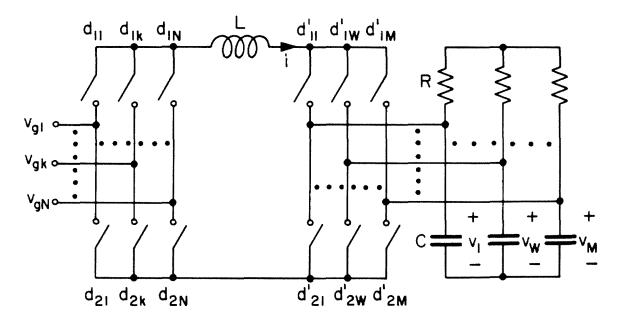

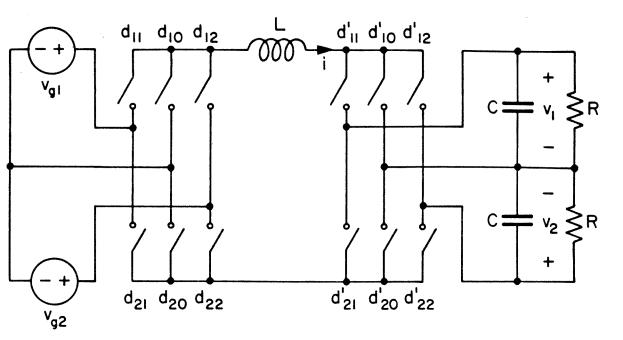

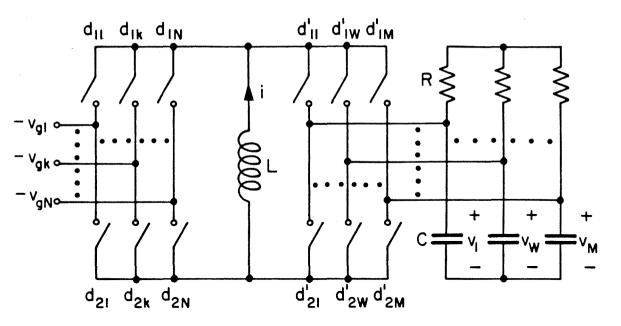

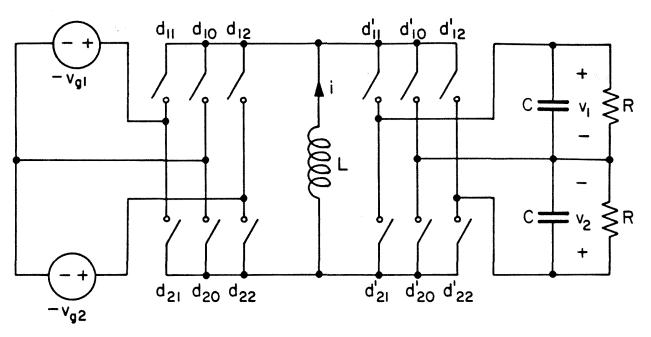

As an example, consider the *M*-phase boost inverter illustrated in Fig. 1.3. This circuit consists of two *M*-throw switches that invert the inductor current, supplied by the dc source, into polyphase currents driving an *M*-phase *RC* load. Note that the switch arrangement is classified as *two M*-throw, not *M* double-throw, switches so that the current in the inductor always has some place to flow to. Correct classification is essential in later assignment of modulations to the throws. States in the network are the inductor current  $i^*$  and capacitor voltage  $v_w^*$ , where asterisk (\*) implies an exact value and  $1 \le w \le M$ .

Fig. 1.3 M-phase boost inverter with two M-throw switches pulse-widthmodulated by sinusoidal functions.

If the common of the capacitors is selected as reference point, then the voltage at the upper pole is

$$\sum_{w=1}^{M} d'_{1w} v_w^*$$

and at the lower pole is

$$\sum_{w=1}^{M} d_{2w}^{\prime} v_{w}^{\ast}$$

where prime (') is used on functions of the switches at the output side of a topology. Note that the above have been obtained *without* any knowledge of *switching details*. Therefore, this step is applicable to any topology that consists of switches and reactive elements, regardless of how the switches

are operated.

Application of Kirchhoff's voltage law around the loop containing the source, inductor, and switches yields the following *exact* state-space *switching equation* for the inductor:

$$L\dot{i}^{*} = -\sum_{w=1}^{M} (d_{1w}^{*} - d_{2w}^{*}) v_{w}^{*} + v_{g}$$

(1.2)

where  $i^*$  means "the first time derivative of  $i^*$ ." Note that this result is independent of the choice of reference point. The analogous equation for the capacitor is

$$C\dot{v}_{w}^{*} = (d_{1w}^{*} - d_{2w}^{*})i^{*} - \frac{1}{R}(v_{w}^{*} - \frac{1}{M}\sum_{w=1}^{M}v_{w}^{*}), \quad 1 \le w \le M$$

(1.3)

In the above, the inductor current is switched into the capacitor via the first term, and the resistor current is drawn out by the second term.

In general, a switched-mode converter contains S switches, each of  $T_m$  throws, where  $1 \le m \le S$ . The number of controllable throws  $T_C$  is then

$$T_{C} = \sum_{m=1}^{S} (T_{m} - 1)$$

(1.4)

If  $T_c$  independent switching functions  $d_n^*$  (just for compactness, only one, instead of two, subscript is used to identify each switching function), where  $1 \le n \le T_c$ , are assigned to these  $T_c$  independent throws, the *exact* statespace switching equation of an ideal converter can be expressed as

$$\mathbf{P} \mathbf{\dot{x}^{*}} = \sum_{n=0}^{T_{c}} d_{n}^{*} (\mathbf{A}_{n} \mathbf{x}^{*} + \mathbf{B}_{n} \mathbf{u})$$

(1.5)

where

$$d_0^{+} = 1$$

(1.6)

$\mathbf{x}^*$  is the  $Q \times 1$  state vector (denoted by boldface),

P is the  $Q \times Q LC$  matrix (denoted by boldface),

$A_n$  is the  $Q \times Q$  constant matrix,

**u** is the  $R \times 1$  source vector,

$\mathbf{B}_n$  is the  $Q \times R$  constant matrix,

and the terms with subscript 0 account for the dependent throws in the topology. Equations (1.2) and (1.3) can be cast in the form of Eq. (1.5) if desired.

Equation (1.5) is exact and general in the sense that no particular mode of control has been specified for the switching function  $d_n^*$ . It is difficult to analyze because the switching functions are only piecewise continuous. Nevertheless, it does reduce to a manipulable form for those converters of the fast-switching PWM family.

By definition, the sources and duty ratios of a fast-switching PWM converter vary at a rate much slower than the switching frequency. By design, the LC corners of the circuit, usually compatible with the frequencies of the source and duty ratio vectors, are also placed well below the switching frequency to minimize the switching ripple. Thus, a fastswitching PWM topology receives slowly-varying inputs, further restricted to being dc or sinusoidal in this thesis, to generate slowly-varying outputs, expected to be dc or sinusoidal with a small amount of high-frequency ripple. Under these conditions, the modeling theorems in [1], proved under the assumption of negligible filter values, still apply. Therefore, the switching function  $d_n$  can be approximated by its duty ratio  $d_n$ ; and the exact state vector  $\mathbf{x}$  by the principal component  $\mathbf{x}$  of its "Fourier series." Within a modeling bandwidth sufficiently lower than the switching frequency and a modeling error sufficiently small, then, the useful, low-frequency variables of the system represented by Eq. (1.5) are related by the following describing equation:

$$\mathbf{P}\dot{\mathbf{x}} = \sum_{n=0}^{T_c} d_n (\mathbf{A}_n \mathbf{x} + \mathbf{B}_n \mathbf{u})$$

(1.7)

where asterisks have been dropped in going from the exact switching to the low-frequency describing equation. A more compact form of Eq. (1.7) is

$$\mathbf{P}\mathbf{x} = \mathbf{A}\mathbf{x} + \mathbf{B}\mathbf{u} \tag{1.8}$$

where

$$\mathbf{A} = \sum_{n=0}^{T_c} d_n \mathbf{A}_n \quad \text{and} \quad \mathbf{B} = \sum_{n=0}^{T_c} d_n \mathbf{B}_n \quad (1.9a,b)$$

A comparison of Eqs. (1.5) and (1.7) reveals that they are similar in form, the only difference being the asterisks in the former. Therefore, the two steps are essentially one, and the describing equation can be obtained expediently by inspection of the topology and use of basic definitions of circuit elements, Kirchhoff's laws, principle of superposition, and so on. Note, however, that the describing equation is *continuous* and, hence, more tractable than the switching equation.

It is obvious from the describing equation that only *duty ratios*, not exact switching details, influence the low-frequency behavior of fast-switching converters. Since many distinct switching functions may share the same duty ratio, there is no unique switching strategy to synthesize a given set of outputs. Topologically independent switches in a fast-switching network are thus also *functionally independent* in the sense that each of them requires simply its own duty ratios and does not have to be synchronized with the other switches. Hence, one more advantage of fast switching over slow switching is the infinite number of flexible drive policies available.

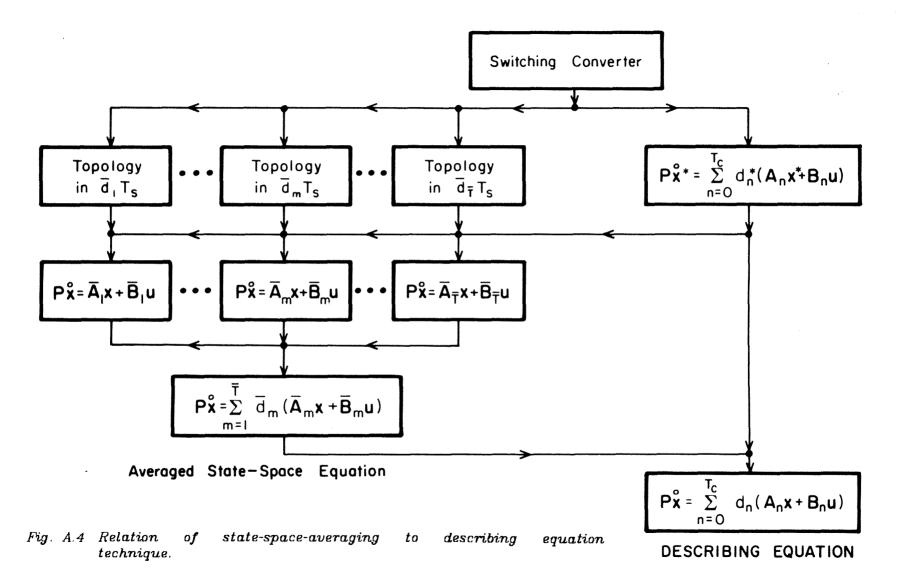

Now that the describing equation technique has been presented, it is proper to review the modeling history of switched-mode structures. Describing equation is actually a classical concept introduced to approximate the characteristics of nonlinear devices and systems. It has been applied to model slow-switching inverters [10], rectifiers, and cycloconverters [24]. Recently, along with the advent of fast-switching technology, the describing equation method has been extended to and, for the first time, justified mathematically in the *frequency* domain for fast-switching converters with negligible filter values in [1]. The results in [1] are simply extended in this thesis to include the effect of reactive components difficult to ignore in most practical designs.

The transition of the describing equation technique from slow switching to fast switching, however, has not been continuous. In between, state-space-averaging [2] has been proposed to treat dc and other simple converters. Its derivation is based on low-frequency approximation of the transition matrix in the *time* domain. When state-space-averaging is used, all possible switched topologies are first enumerated and assigned *topological duty ratios*. Linear equations of these topologies are then weighted by their respective topological duty ratios and summed up to provide the averaged state-space equation. State-space averaging clarifies the operation of simple

dc converters with only a few switched topologies repeated in every switching cycle. Because of its detailed topological description, however, it is not used here to model complex ac converters that have a large number of throws and, hence, switched networks. There are just so many of these switched circuits to enumerate and more-than-necessary topological duty ratios to consider, the *number* and *type* of which keep on varying from one switching period to another while the duty ratios are modulated. Describing equation escapes all these problems and, hence, is the proper modeling approach to reinstate.

A special case of Eq. (1.8) is the describing equations of Eqs. (1.2) and (1.3) for the boost inverter; the corresponding vectors and matrices are:

$$\mathbf{P} = \begin{bmatrix} L & \mathbf{o}_{\mathcal{H}}^{T} \\ \mathbf{o}_{\mathcal{H}} & C\mathbf{I}_{\mathcal{H}} \end{bmatrix}, \qquad \mathbf{x} = \begin{bmatrix} i \\ [v_{w}] \end{bmatrix}$$

(1.10a,b)

where  $I_M$  is the  $M \times M$  unity matrix,  $\mathbf{o}_M$  is the  $M \times 1$  zero vector, and  $1 \le w \le M$ ;

$$\mathbf{A} = \begin{bmatrix} 0 & -[d_{\boldsymbol{w}}]^T \\ [d_{\boldsymbol{w}}] & 1/R \left[ 1/M - \delta_{\boldsymbol{w}\boldsymbol{z}} \right] \end{bmatrix}, \qquad \mathbf{B} = \begin{bmatrix} 1 \\ \mathbf{o}_{\boldsymbol{y}} \end{bmatrix}$$

(1.10c,d)

where  $\delta_{wz}$  is 1 when w = z and is 0 otherwise; and

$$\mathbf{u} = v_{\sigma} \tag{1.10e}$$

In the above,  $d_{w}$  is the effective duty ratio and is related to the duty ratios

of the switching functions  $d'_{1w}^{*}$  and  $d'_{2w}^{*}$  by  $d'_{w} = d'_{1w} - d'_{2w}$ (1.11)

The performance of the inverter depends on what is assigned to  $d'_{w}$  or  $d'_{1w}$ and  $d'_{2w}$ . In this thesis, only easy-to-synthesize *sinusoidal* functions are considered; in this chapter, they are restricted further to being *continuous*.

In general, then, the duty ratio of each throw consists of a sinusoidal modulation and a dc component sufficiently large to make the duty ratio positive. Since the two switches are topologically independent, they can be modulated by *numerous* sets of balanced polyphase sinusoids that have independent amplitudes and phases:

$$d_{kw} = \frac{1}{M} + \frac{d_{mk}}{M} \cos \left[ \theta_k - (w-1) \frac{2\pi}{M} \right]$$

(1.12)

where

$$\theta'_{k} = \int_{0}^{t} \omega'(\tau) d\tau + \varphi'_{k}, \qquad d'_{mk} \le 1$$

(1.13a,b)

for

k = 1,2 and  $1 \le w \le M$  (1.13c,d)

Note that this kind of duty ratio assignment allows all duty ratios of one switch to sum up to one. In the above,  $\frac{d'_{mk}}{M}$  is the instantaneous modulation amplitude, and  $\omega'$  the instantaneous modulation frequency. The frequency can be any real number, where a negative frequency reverses the phase sequence.

Out of different selections of  $d'_{1w}$  and  $d'_{2w}$ , the one that maximizes the effective duty ratio should be chosen. An efficient  $d'_w$  results when  $d'_{1w}$ and  $d'_{2w}$  have equal amplitudes and opposite phases and can be expressed as

$$d'_{w} = \frac{2d'_{m}}{M} \cos \left[ \theta' - (w-1) \frac{2\pi}{M} \right]$$

(1.14)

where

$$\theta' = \int_{0}^{t} \omega'(\tau) d\tau$$

and  $d'_{m} \leq 1$  (1.15a,b)

Again, this is just one choice of  $d_w^{'};$  other interesting ones are discussed later.

To recap, *low-frequency* components of the inputs and outputs of a fast-switching PWM converter are related by the *describing equations* of the circuit. These equations identify the independent *duty ratios* of the switches as control variables. Therefore, the performance of the converter depends on duty ratios, not different combinations of switched networks, if all circuit parameters vary sufficiently slower than the switching frequency.

#### 1.3 Transformation

The describing equations written in the ordinary (or stationary or "abc") frame of reference may contain constant, if the converter is dc, or time-varying, if the converter is ac. duty ratios. Since a system of equations with constant coefficients is easier to analyze, especially dynamically, with standard techniques, it is beneficial to transform an ac system to an equivalent dc one whenever possible. With the "abc-ofb" transformation

introduced below, the existence of the dc equivalent also means that the ac converter possesses ideal (i.e., dc or sinusoidal) solutions.

A variety of transformations exist to convert a set of balanced sinusoids into its dc equivalent [23]. The one chosen here is the complex abc-ofb transformation (Appendix B). A complex transformation is preferred to a real one because the former allows the model of a converter using only one circuit while the latter requires two circuits coupled through dependent generators. Furthermore, the complex model is symmetrical while the real one is not. A result of real transformation frequently found in the literature is the dq equivalent circuit of an ac machine, composed of one network on the d-axis and another on the q-axis.

In general, the describing equation of a fast-switching PWM converter in one reference frame - abc, for instance - takes the form

$$\mathbf{P}\mathbf{\dot{x}} = \mathbf{A}\mathbf{x} + \mathbf{B}\mathbf{u} \tag{1.18}$$

Under the transformation

$$\mathbf{x} = \widetilde{\mathbf{T}}\widetilde{\mathbf{x}}$$

or  $\widetilde{\mathbf{x}} = \widetilde{\mathbf{T}}^{-1}\mathbf{x}$  (1.17a,b)

where tilde ( $\sim$ ) denotes a transformed or complex variable, Eq. (1.16) becomes

$$\widetilde{\mathbf{P}}\mathbf{\dot{\tilde{x}}} = \widetilde{\mathbf{A}}\mathbf{\tilde{x}} + \widetilde{\mathbf{B}}\mathbf{\widetilde{u}}$$

(1.18a)

or, to highlight control parameters:

$$\widetilde{\mathbf{P}}\dot{\widetilde{\mathbf{x}}} = \sum_{m=0}^{T_T} d_{Tm} (\widetilde{\mathbf{A}}_m \widetilde{\mathbf{x}} + \widetilde{\mathbf{B}}_m \widetilde{\mathbf{u}})$$

(1.18b)

where

$$\widetilde{\mathbf{A}} = \widetilde{\mathbf{T}}^{-1}\mathbf{A}\widetilde{\mathbf{T}} - \widetilde{\mathbf{T}}^{-1}\mathbf{P}\widetilde{\mathbf{T}}, \qquad \widetilde{\mathbf{P}} = \widetilde{\mathbf{T}}^{-1}\mathbf{P}\widetilde{\mathbf{T}} \qquad (1.19a,b)$$

$$\widetilde{\mathbf{B}}\widetilde{\mathbf{u}} = \widetilde{\mathbf{T}}^{-1}\mathbf{B}\mathbf{u}$$

, and  $d_{T0} = 1$  (1.19c.d)

In Eq. (1.18b),  $T_T$  is the number of independent transformed controls  $d_{Tm}$ and is generally less than or equal to the number of independent throws  $T_C$ . The transformed control vector containing  $d_{Tm}$  is the transformation of the duty ratio vector containing  $d_n$  by  $\widetilde{\mathbf{T}}$ ; it is related to the transformed state vector  $\widetilde{\mathbf{x}}$  via  $\widetilde{\mathbf{A}}_m$  and the transformed source vector  $\widetilde{\mathbf{u}}$  via  $\widetilde{\mathbf{B}}_m$ .

As an example of complex transformation, consider again the boost inverter characterized by Eqs. (1.10) through (1.15). If the topology is ideal, its inductor current is dc and its capacitor voltages sinusoidal. Therefore, the transformation takes the form

$$\widetilde{\mathbf{T}} = \begin{bmatrix} 1 & \mathbf{o}_{\mathcal{H}}^{T} \\ \mathbf{o}_{\mathcal{H}} & \widetilde{\mathbf{T}}_{v} \end{bmatrix}$$

(1.20)

Note that  $\widetilde{\mathbf{T}}$  consists of two smaller transformations that act separately on the inductor and capacitor states. The first one is a unity transformation that passes the inductor current intact to the new frame of reference. The second one is the *M*-phase abc-ofb transformation, Eqs. (B.2) and (B.3), that converts the real voltage vector  $[v_w]$  in the stationary (abc) frame of reference to the complex vector

$$[v_0 \ \widetilde{v}_f \ \widetilde{v}_3 \ \cdots \ \widetilde{v}_{M-1} \ \widetilde{v}_b]^T$$

in the rotating (ofb) coordinate system.

Substitution of Eqs. (1.10) through (1.15) and Eq. (1.20) into Eq. (1.19) results in

$$C \dot{v}_0 = 0$$

(1.21a)

and

$$C \dot{\tilde{v}}_{w} = -\frac{\tilde{v}_{w}}{R}$$

,  $3 \le w \le M - 1$  (1.21b)

The trivial relationship in Eq. (1.21a) suggests that  $v_0$  is indeterminate, i.e., all phase voltages may contain equal arbitrary dc offset components. These components, however, do not deliver any power because their differentials, seen by the load, are always zero. In practical circuits, the arbitrariness can be fixed to any known voltage by pulling the outputs to a dc level through large resistors. If this is not done, the leakage resistance across the capacitor forces  $v_0$  to zero.

The  $3^{rd}$  through  $(M-1)^{th}$  capacitor states are also trivial, as is evident from Eq. (1.21b). Unlike  $v_0$ , they are identically zero under all conditions. Therefore, they, as well as  $v_0$ , are ignored in the remainder of the discussion.

The only significant capacitor voltages that remain are the backward phasor  $\tilde{v}_b$ , proportional to the phasor characterizing the first capacitor voltage, and the forward phasor  $\tilde{v}_f$ , complex conjugate of  $\tilde{v}_b$ . The order of the balanced polyphase states thus reduces from  $M^{th}$  to  $2^{nd}$ , an important simplification found whenever the states constitute a balanced polyphase set. Therefore, all converters with three or more balanced phases are reducible to a two-phase equivalent. An analogous statement is well-known in the theory of ac machines, namely, all machines with three or

more windings on the stator or rotor are equivalent to the two-phase machine. Owing to this reducibility of polyphase systems, only the simple two-phase circuit needs be considered in place of much more complicated M-phase topologies, where M can go to infinity. The realization of two-phase converters to be coupled to two-phase motors or generators is treated in later chapters.

After the elimination of (M-2) capacitor states, the boost inverter becomes third-order: one for the inductor current and two for the capacitor voltages. If  $\widetilde{T}_v$  is in-phase with the effective duty ratio  $d'_w$ , the reduced matrix equation can be manipulated into

$$\mathbf{P}_{r} \mathbf{\tilde{x}}_{r} = (\mathbf{A}_{r} + \mathbf{A}_{d} d_{e}' + \mathbf{A}_{\omega} j \omega') \mathbf{\tilde{x}}_{r} + \mathbf{B}_{d} v_{g}$$

(1.22)

where

$$d'_{e} = \frac{\sqrt{M}}{2} \frac{2d'_{m}}{M} = \frac{d'_{m}}{\sqrt{M}}$$

(1.23)

is the *transformed duty ratio*, the transformation of the effective duty ratio  $d_w$  by  $\widetilde{T}_v$ ;

$$\mathbf{P}_{r} = \begin{bmatrix} L & 0 & 0 \\ 0 & C & 0 \\ 0 & 0 & C \end{bmatrix}, \quad \tilde{\mathbf{x}}_{r} = \begin{bmatrix} i \\ \tilde{v}_{f} \\ \tilde{v}_{b} \end{bmatrix}, \quad \mathbf{A}_{r} = \begin{bmatrix} 0 & 0 & 0 \\ 0 & -1/R & 0 \\ 0 & 0 & -1/R \end{bmatrix}$$

(1.24a,b,c)

$$\mathbf{A}_{d} = \begin{bmatrix} 0 & -1 & -1 \\ 1 & 0 & 0 \\ 1 & 0 & 0 \end{bmatrix}, \quad \mathbf{A}_{\omega} = \begin{bmatrix} 0 & 0 & 0 \\ 0 & C & 0 \\ 0 & 0 & -C \end{bmatrix}, \quad \mathbf{B}_{d} = \begin{bmatrix} 1 \\ 0 \\ 0 \end{bmatrix}$$

(1.24d,e,f)

In this formulation, all matrices are real even though the original  $\mathbf{A}$  and  $\mathbf{B}\mathbf{\widetilde{u}}$ are complex. Resistance is contained in  $\mathbf{A}_r$ ; capacitance and inductance,  $\mathbf{A}_{\omega}$ ; constants describing the duty ratios,  $\mathbf{A}_d$ ; and constants related to the source, B<sub>d</sub>.

All control parameters are placed outside the matrices so that they can be identified easily as  $d'_{e}$ ,  $\omega'$ , and  $v_{g}$ , where lower case signifies an instantaneous value. Therefore, rotating coordinates emphasize what is not apparent in stationary axes, namely, only the amplitude and frequency of duty ratio modulations influence the outcome and, hence, are the ones to control. Analysis and design problems are thus simple because both  $d'_{e}$  and  $\omega'$  are constant under steady-state condition. Note that  $d'_{e}$  is a control factor peculiar to fast-switching PWM and does not exist in low-frequency drives.

In retrospect, polyphase converters with dc or sinusoidal waveforms in the abc (or stationary) reference frame can be modeled by differential equations with *constant* coefficients in the ofb (or rotating) coordinate system. One method to transform from the abc to the ofb representation is the complex abc-ofb transformation. This transformation reduces the number of balanced polyphase sinusoidal states in the stationary axes from larger-than-two to just *two* and allows the model of converters with an *arbitrary* number of balanced phases by the *two*-phase converter. It replaces sinusoidal duty ratio modulations by their amplitude and frequency, dc under steady-state condition, and sinusoidal outputs their amplitude and phase.

### 1.4 Steady-State Analysis

Under steady-state condition, the inputs in Eq. (1.18b) take on the dc values  $D_{Tm}$  and  $\widetilde{\mathbf{U}}$ , where upper case indicates a steady-state variable. The corresponding output vector  $\widetilde{\mathbf{X}}$  is also dc and is computed by letting its derivative be zero in Eq. (1.18b):

$$\widetilde{\mathbf{X}} = -\left[\sum_{m=0}^{T_T} D_{Tm} \widetilde{\mathbf{A}}_m\right]^{-1} \left(\sum_{m=0}^{T_T} D_{Tm} \widetilde{\mathbf{B}}_m\right] \widetilde{\mathbf{U}}$$

(1.25)

An application of this result is demonstrated below for the boost inverter.

Steady-state results of the boost inverter are found by replacement of  $d'_{e}$ ,  $\omega'$ ,  $v_{g}$ , and  $\tilde{\mathbf{x}}_{r}$  in Eq. (1.22) by  $D'_{e}$ ,  $\Omega'$ ,  $V_{g}$ , and 0, respectively, and solving for  $\widetilde{\mathbf{X}}_{r}$  from the corresponding algebraic equation. The formula for the inductor current is

$$I = \frac{V_g}{2D_e'^2 R} \left[ 1 + \left( \frac{\Omega'}{\omega_p} \right)^2 \right]$$

(1.26)

where

$$\omega_p = \frac{1}{RC} \tag{1.27}$$

Since the transformed current is *real*, the actual current in the inductor is purely dc. This result confirms the ideality of the topology: dc input current is the only way to guarantee constant instantaneous power flow and, hence, promise sinusoidal outputs.

The backward voltage phasor can be proved to be

$$\widetilde{V}_{b} = \frac{V_{g}}{2D'_{g}} \left[ 1 - j \frac{\Omega'}{\omega_{p}} \right]$$

(1.28)

Unlike the inductor current, the capacitor voltage in the ofb frame is complex to signify that phase outputs in the abc axes are indeed sinusoidal. The true capacitor voltage  $v_w$  can be reconstructed from Eq. (1.28):

$$v_{w} = V \cos[\Omega' t - \Phi_{v} - (w - 1) \frac{2\pi}{M}] \qquad (1.29)$$

where, from Appendix B:

$$V e^{-j \Phi_{v}} = \frac{2}{\sqrt{M}} \widetilde{V}_{b} = \frac{V_{g}}{D'_{m}} \left[ 1 - j \frac{\Omega'}{\omega_{p}} \right]$$

(1.30)

It is apparent from Eq. (1.30) that the output amplitude is always higher than the input dc voltage; the inverter thus deserves its name. Note that unlike dc converters, ac converters depend on circuit impedances even under steady-state condition - L is the only element absent from the above results since its impedance is zero. Therefore, an ac converter can be classified neither as a voltage nor as a current source. The boost topology, however, does belong to the "current-fed" family because the output is fed by a dc current converted from the voltage source by the inductor.

The very existence of ideal solutions, Eqs. (1.26) through (1.30), for a *nonlinear* structure like the boost inverter, Eqs. (1.22) through (1.24), should not be taken for granted. Most ac topologies produce low-frequency distortion because of the nonlinearity inherent in switched-mode converters [20] and, hence, do not satisfy the objectives of this thesis. The recognition of the remaining few ideal switching networks is thus an important task to be pursued in later chapters. In review, steady-state solutions in the rotating coordinates are provided by homogeneous algebraic equations relating constant inputs to constant outputs. *Real* results correspond to *dc* values while *complex* results represent balanced polyphase *sinusoidal* states in the stationary reference frame.

#### 1.5 Small-Signal Dynamics

This section examines the dynamics introduced by filters used to attenuate the switching ripple in switched-mode converters. Because the converter is generally nonlinear (Eq. (1.22), for instance), dynamic study is restricted to only the *small-signal* sense. In other words, it predicts the responses of the system to small perturbations around a quiescent operating point. The ofb frame of reference provides a perfect medium for perturbed dynamics since the equations of the network already have constant coefficients there. Thus, there is no need to invoke the "quasi-dc" approximation [28] that has limited accuracy and allows only inefficient worst-case designs.

Let the input and output in Eq. (1.18b) consist of a steady-state and a perturbed component:

$$\widetilde{\mathbf{x}} = \widetilde{\mathbf{X}} + \widehat{\widetilde{\mathbf{x}}}$$

,  $d_{Tm} = D_{Tm} + \widehat{d}_{Tm}$ , and  $\widetilde{\mathbf{u}} = \widetilde{\mathbf{U}} + \widehat{\widetilde{\mathbf{u}}}$  (1.31a,b,c)

where caret implies small-signal perturbation. Substitution of these relations into Eq. (1.18b) and neglect of the resulting steady-state and second-order terms then yield the following response for the state vector in the Laplace domain:

$$\widehat{\widetilde{\mathbf{x}}}(s) = (s\widetilde{\mathbf{P}} - \sum_{m=0}^{T_T} D_{Tm}\widetilde{\mathbf{A}}_m)^{-1} [\sum_{m=0}^{T_T} (\widetilde{\mathbf{A}}_m\widetilde{\mathbf{X}} + \widetilde{\mathbf{B}}_m\widetilde{\mathbf{U}}) \widehat{d}_{Tm}(s) + (\sum_{m=0}^{T_T} D_{Tm}\widetilde{\mathbf{B}}_m) \widehat{\widetilde{\mathbf{u}}}(s)]$$

(1.32)

This state vector, however, is generally complex. Therefore, it is accompanied by a state-to-output equation that changes states into measurable real outputs:

$$\widehat{\mathbf{y}}(s) = \widetilde{C}\widehat{\widetilde{\mathbf{x}}}(s) + \widetilde{D}_d \widehat{\mathbf{d}}(s) + \widetilde{D}_u \widehat{\widetilde{\mathbf{u}}}(s)$$

(1.33)

For the boost inverter of Eq. (1.22), the perturbed state vector  $\hat{\mathbf{x}}_r$  is expressed as a function of the excitations  $\hat{d}_g$ ,  $\hat{\omega}'$ , and  $\hat{v}_g$  according to

$$\widehat{\widetilde{\mathbf{x}}}_{r}(s) = (s \mathbf{P}_{r} - \widetilde{\mathbf{A}}_{o})^{-1} [\mathbf{A}_{d} \widetilde{\mathbf{X}}_{r} \widehat{d}_{g}(s) + \mathbf{A}_{\omega} \widetilde{\mathbf{X}}_{r} j \widehat{\omega}'(s) + \mathbf{B}_{d} \widehat{v}_{g}(s)]$$

(1.34)

where

$$\widehat{\widetilde{\mathbf{x}}}_{\boldsymbol{r}}(s) = \begin{bmatrix} \widehat{\imath}(s) \\ \widehat{\widetilde{\upsilon}}_{\boldsymbol{f}}(s) \\ \widehat{\widetilde{\upsilon}}_{\boldsymbol{b}}(s) \end{bmatrix}, \qquad \widetilde{\mathbf{X}}_{\boldsymbol{r}} = \begin{bmatrix} I \\ \widetilde{V}_{\boldsymbol{f}} \\ \widetilde{V}_{\boldsymbol{b}} \end{bmatrix}$$

(1.35a,b)

and

$$\widetilde{\mathbf{A}}_{o} = \mathbf{A}_{r} + D_{e}^{'}\mathbf{A}_{d} + j\,\Omega'\mathbf{A}_{\omega} \qquad (1.35c)$$

In the above, the current can be used directly as an output because it is already real. The voltages, however, are complex and need be converted into their real equivalents before they can be measured by conventional setups.

The real representations of a phasor are its real and imaginary components or its amplitude and phase:

$$\widetilde{v}_{b}(t) = v_{r}(t) + j v_{i}(t) = v_{m}(t) e^{-j\varphi_{v}(t)}$$

(1.36)

From this equation, the output vector  $\hat{\mathbf{y}}(s)$  can be related to the state

vector  $\hat{\tilde{\mathbf{x}}}_r(s)$  by

$$\hat{\mathbf{y}}(s) = \widetilde{\mathbf{C}} \, \widehat{\widetilde{\mathbf{x}}}_r(s)$$

(1.37)

where

$$\hat{\mathbf{y}}(s) = \begin{bmatrix} \hat{\imath}(s) \\ \hat{\upsilon}_{r}(s) \\ \hat{\upsilon}_{i}(s) \\ \hat{\upsilon}_{m}(s) \end{bmatrix} \text{ and } \tilde{\mathbf{C}} = \begin{bmatrix} 1 & 0 & 0 \\ 0 & 1/2 & 1/2 \\ 0 & j/2 & -j/2 \\ 0 & \tilde{V}_{b}/2V_{m} & \tilde{V}_{f}/2V_{m} \end{bmatrix}$$

(1.38a,b)

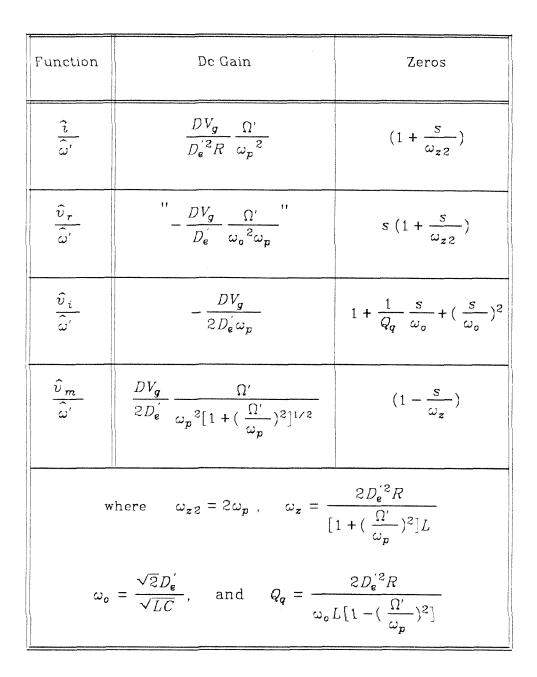

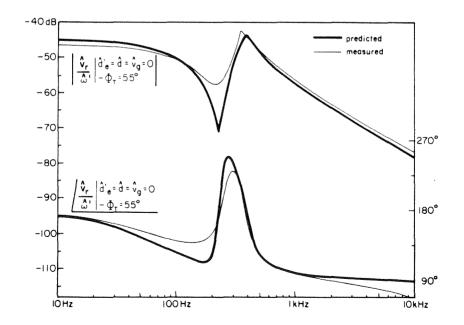

Equations (1.34) and (1.37) are used together to compute the control-to-output and line-to-output frequency responses. For instance, if only one input is perturbed at a time,

$$\frac{\widehat{\upsilon}_{m}}{\widehat{d}'_{g}} = -\frac{V_{g}}{2D'_{g}^{2}} \left[1 + \left(\frac{\Omega'}{\omega_{p}}\right)^{2}\right]^{\frac{1}{2}} \frac{\left[1 - \frac{s}{\omega_{z}}\right] \left[1 + \frac{s}{\omega_{z1}}\right]}{K(s)}$$

(1.39a)

$$\frac{\hat{\imath}}{\hat{\omega}'} = \frac{V_g}{D_g'^2 R} \frac{\Omega'}{\omega_p^2} \frac{1 + \frac{s}{\omega_{z2}}}{K(s)}$$

(1.39b)

or

$$\frac{\hat{v}_{r}}{\hat{v}_{g}} = \frac{1}{2D'_{e}} \frac{1 + \frac{s}{\omega_{p}}}{K(s)}$$

(1.39c)

where

$$\omega_{p} = \frac{1}{RC} , \qquad \omega_{z} = \frac{2D_{e}^{\prime 2}R}{\left[1 + \left(\frac{\Omega'}{\omega_{p}}\right)^{2}\right]L}$$

(1.40a,b)

$$\omega_{z1} = \left[1 + \left(\frac{\Omega'}{\omega_p}\right)^2\right] \omega_p \qquad \qquad \omega_{z2} = 2\omega_p \qquad (1.40c,d)$$

and

$$K(s) = 1 + \left[ RC + \frac{\Omega'^2 L C^2 R}{2D_e^{\prime 2}} + \frac{L}{2D_e^{\prime 2} R} \right] s + \frac{LC}{D_e^{\prime 2}} s^2 + \frac{LC^2 R}{2D_e^{\prime 2}} s^3$$

(1.41)

The denominator K(s), common to all transfer functions, is proportional to the characteristic polynomial of  $\widetilde{\mathbf{A}}_{o}$ . It emerges real amid all complex variable manipulations as the original system is realizable from real L, C, and R. It is of third order as expected. Since the topology is nonlinear, all dynamic corners are sensitive to the quiescent operating condition.

To summarize, dynamic analysis of switched-mode ac converters, both nonlinear and time-varying in the abc coordinates, can be studied conveniently in the ofb reference frame where the describing equations have constant coefficients. The nonlinearity is still there, but the system can be *linearized* by restriction of all perturbations to only small-signal. Equations have been developed to predict all control-to-output and line-to-output frequency responses. Dynamic corners are generally sensitive to steady-state parameters, such as modulation amplitude and frequency.

# 1.6 Canonical Model

The combination of steady-state (Eq. (1.25)) and perturbed (Eq. (1.32)) equations, or the dynamic equation without second-order terms, is the *linearized* system equation:

$$(s\widetilde{\mathbf{P}} - \sum_{m=0}^{T_T} D_{Tm}\widetilde{\mathbf{A}}_m)\widetilde{\mathbf{x}}(s) = \sum_{m=0}^{T_T} (\widetilde{\mathbf{A}}_m\widetilde{\mathbf{X}} + \widetilde{\mathbf{B}}_m\widetilde{\mathbf{U}})\widehat{d}_{Tm}(s) + (\sum_{m=0}^{T_T} D_{Tm}\widetilde{\mathbf{B}}_m)\widetilde{\mathbf{u}}(s)$$

(1.42)

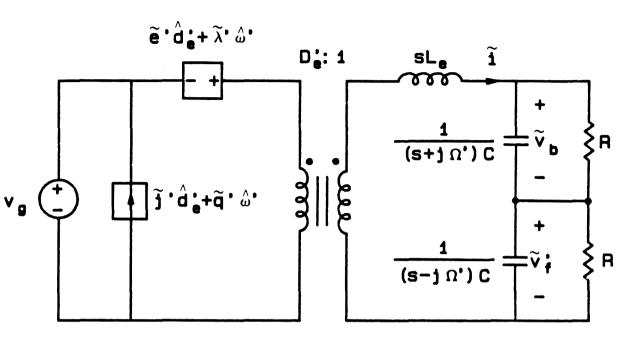

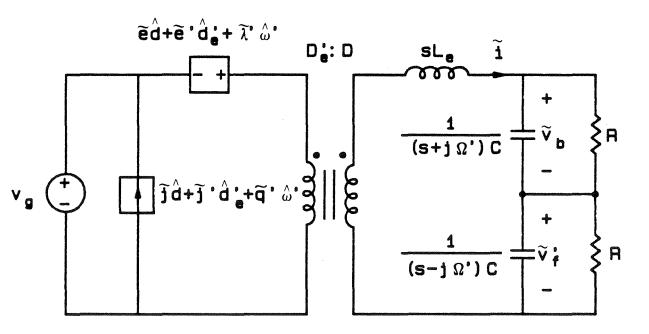

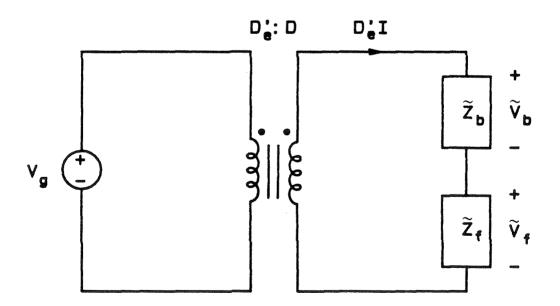

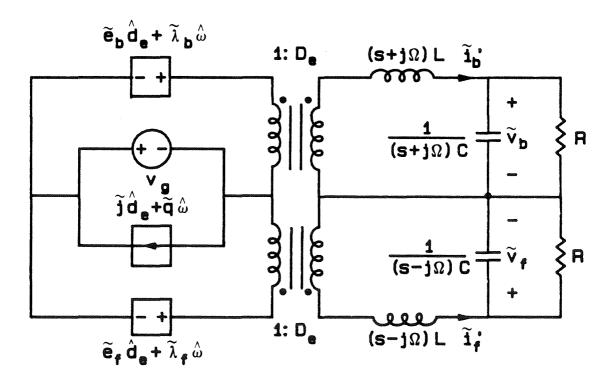

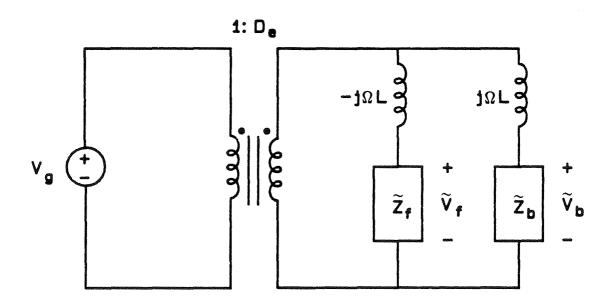

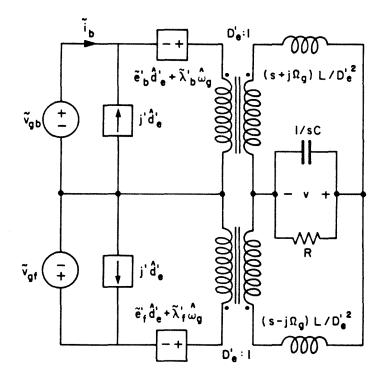

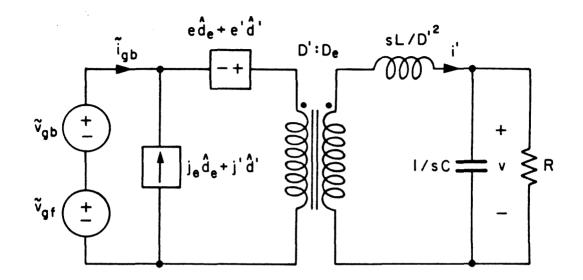

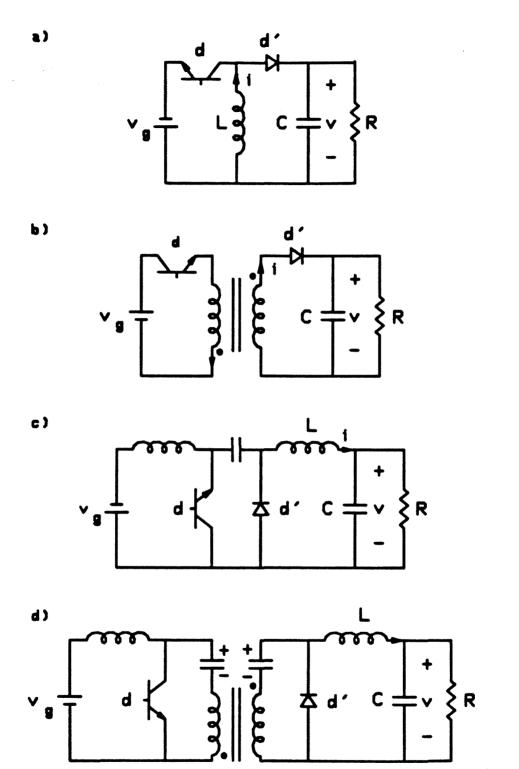

The pictorial representation of this linearized equation is the *canonical model*, a powerful tool that not only predicts steady-state and dynamic performances, but also illuminates the interaction between the input, load, filters, and switches.

Since the rotating coordinates have been more versatile than the stationary ones in the two previous analyses, they are retained here to discuss the equivalent circuit. Again, in the rotating frame of reference, an ideal converter is described by differential equations with constant particular, the complex ofb axes promise coefficients. In a single symmetrical model, instead of two unsymmetrical coupled circuits as the real dq axes. Therefore, the ofb coordinates are the most convenient common ground for later comparison of topologies in all four areas of power electronics.

To be "canonical", the model should identify correctly the output variable, input variable, conversion function, and filter topology. The output variable is usually the output voltage phasor, and the input variable the source current phasor. The conversion function is the heart of the model: it portrays how the switches convert power from one form to another and what the accompanying steady-state gain is. The filter topology explains the effects of reactive elements on steady-state and dynamic results and, in doing so, clarifies the conversion function. A step-by-step procedure to cast the linearized equations into the canonical model is explained below for the boost inverter.

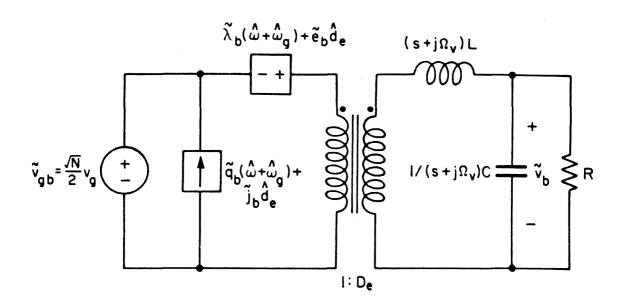

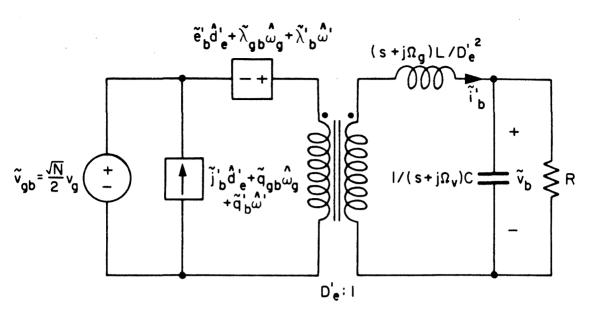

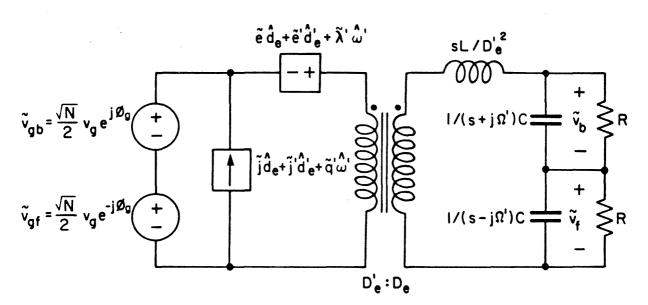

First, select the capacitor voltage phasor  $\widetilde{v}_b$  as the output and recall the linearized dynamic equation for this state:

$$\left[\frac{1}{R} + (s+j\Omega')C\right]\widetilde{v}_{b} = D_{e}'i + I\widehat{d}_{e}' - jC\widetilde{V}_{b}\widehat{\omega}'$$

(1.43)

Since no controlled generators are allowed at the output, the right-hand side of Eq. (1.43) is defined as an effective inductor current

$$\widetilde{i} = D_{e}'i + I\widehat{d}_{e}' - jC\widetilde{V}_{b}\widehat{\omega}' \qquad (1.44)$$

so that  $\widetilde{v}_{b}$  now satisfies

$$\left[\frac{1}{R} + (s+j\Omega')C\right]\widetilde{v}_{b} = \widetilde{i}$$

(1.45)

The above relation between  $\tilde{v}_b$  and  $\tilde{\imath}$  suggests that the impedance in square brackets is the first element of the model, as is shown in Fig. 1.4. Substitution of Eq. (1.44) into the linearized equation for  $\tilde{v}_f$ , the complex conjugate of Eq. (1.43), yields

$$\left[\frac{1}{R} + (s - j\Omega')C\right]\widetilde{v}_{f} = \widetilde{\iota} + jC(\widetilde{V}_{b} + \widetilde{V}_{f})\widehat{\omega}'$$

(1.46)

Again, to push the controlled source by  $\widehat{\omega}'$  to the input side of the model requires the definition

$$\widetilde{v}_{f} = \widetilde{v}_{f} - j \frac{V_{g}}{D_{e}'} \frac{RC\widehat{\omega}'}{1 + (s - j\Omega')RC}$$

(1.47)

Equation (1.46) then becomes

$$\left[\frac{1}{R} + (s - j\Omega')C\right]\widetilde{v}_{f} = \widetilde{\iota}$$

(1.48)

The impedance in Eq. (1.48) relating  $\widetilde{v}_f$  and  $\widetilde{\iota}$  thus becomes the second component of the model in Fig. 1.4.

Fig. 1.4 Linearized, continuous, and time-invariant canonical model of the boost inverter.

From the previous steps, it is clear that the true inductor current iand forward capacitor voltage  $\tilde{v}_f$  have to be sacrificed so that the physical output  $\tilde{v}_b$  is preserved as the model output and all controlled generators are eliminated at the output half of the model. Therefore, care must be taken not to interpret model states, except for the output, as converter states. The true states can be retrieved from the model via Eqs. (1.44) and (1.47).

There still remains the linearized equation of the inductor:

$$sLi = -D_{e}\tilde{v}_{b} - D_{e}\tilde{v}_{f} - (\tilde{V}_{f} + \tilde{V}_{b})\hat{d}_{e} + v_{g} \qquad (1.49)$$

Replacement of i and  $\tilde{v}_f$  in the above by  $\tilde{i}$  and  $\tilde{v}_f$ , respectively, and

manipulation of the resulting form to expose  $\tilde{\iota}, \tilde{\upsilon}_{f}, \tilde{\upsilon}_{b}$ , and  $v_{g}$  give the following for the inductor in the model:

$$sL_{\mathbf{g}}\widetilde{\boldsymbol{\iota}} = -\widetilde{\boldsymbol{\upsilon}}_{f}' - \widetilde{\boldsymbol{\upsilon}}_{b} + \frac{1}{D_{\mathbf{g}}'} \left(\widetilde{\boldsymbol{e}}'\widehat{\boldsymbol{d}}_{\mathbf{g}}' + \widetilde{\boldsymbol{\lambda}}'\widehat{\boldsymbol{\omega}}' + \boldsymbol{\upsilon}_{g}\right)$$

(1.50)

where

$$L_{\mathbf{g}} = \frac{L}{D_{\mathbf{g}}^{\prime 2}}, \qquad \widetilde{\mathbf{e}}' = D_{\mathbf{g}}' s L_{\mathbf{g}} I - \frac{V_{\mathbf{g}}}{D_{\mathbf{e}}'} \qquad (1.51a,b)$$

and

$$\widetilde{\lambda}' = -j RC \left[ \frac{V_g}{1 + (s - j \Omega')RC} + D_e' \widetilde{V}_b \frac{sL_e}{R} \right]$$

(1.51c)

Note that Eq. (1.50) automatically insures that the voltage source  $v_g$  in the model represents truthfully the actual dc supply, also  $v_g$ . At this stage, no more new current or voltage states can be defined. Nonetheless, the last term in this equation may be treated as the secondary voltage of a transformer whose turn ratio is the *inversion ratio*  $\frac{1}{D'_g}$  and whose primary is fed by the source and dependent voltage generators inside the parentheses. The inductor, transformer, and voltage generators involved in Eq. (1.50) are illustrated in Fig. 1.4.

The one parameter that the procedure outlined above may not account for correctly is the *source current*. Actually, this current is irrelevant as long as the source is assumed to be ideal - this is why the modeling process ignores it completely in the first place. Nevertheless, the source current should be modeled properly so that the equivalent circuit is useful in the presence of source impedance. From Fig. 1.4, the reflected current on the primary side of the transformer is

$$\frac{\widetilde{i}}{D_{e}'} = i + \frac{I}{D_{e}'} \,\widehat{d}_{e}' - \frac{jC\widetilde{V}_{b}}{D_{e}'} \,\widehat{\omega}' \tag{1.52}$$

Since the correct line current is only i, a controlled *current* generator must be inserted as shown in Fig. 1.4 to absorb the last two terms in the primary current. Thus,

$$\widetilde{j}' = \frac{I}{D'_{e}}$$

and  $\widetilde{q}' = -j \frac{CV_{b}}{D'_{e}}$  (1.53a,b)

The complete model thus characterizes faithfully both the output voltage and input current. It highlights the principal attributes of a power processor, namely, the control functions, conversion mechanism, and lowpass filters. Most importantly, it represents the nonlinear, switched, and time-varying converter by a *linear*, continuous, and time-invariant circuit.

In conclusion, describing equation, long used to study slow-switching drives and recently extended to model fast-switching converters, is adopted here as the generalized analysis technique. This method characterizes with a high degree of accuracy the dynamic relation between duty ratios and lowfrequency components of the waveforms in fast-switching PWM converters with reactive elements. State-space describing differential equations can be obtained, by inspection, in the abc frame of reference and then transformed, by the abc-ofb transformation, to the ofb coordinates in which they have constant coefficients. The transformed equations are set to zero for steadystate solutions, perturbed for small-signal dynamics, and linearized for a linear, time-invariant, and continuous canonical model.

# PART I

# SWITCHED-MODE INVERSION

#### CHAPTER 2

# **REVIEW OF EXISTING INVERTERS**

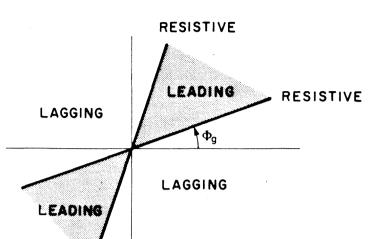

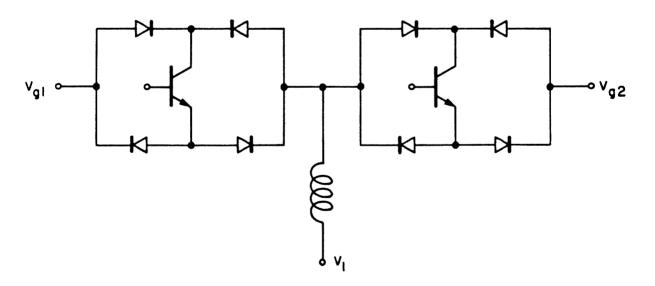

Many industrial applications, such as motor drives and uninterruptible power supplies, require the conversion of dc into ac power. This dc-to-ac power transformation is broadly called *inversion*, and the corresponding power processor the *inverter*. Although an inverter can have single-phase or balanced polyphase ac output, only the later type is considered in this thesis in accordance with the restriction of *constant instantaneous power flow* set forth in the Introduction. The terms "balanced polyphase" thus describe a set of two or more *sinusoidal* quantities that have the same amplitude and are displaced in phase by  $\pm 90^{\circ}$ , for a twophase (or semi-four-phase) system, or  $\pm \frac{360^{\circ}}{M}$ , for an  $M (\geq 3)$ -phase system.

Inverters can be divided into three groups according to the ratio of their switching to output (or inversion) frequency. The "slow-switching" group, reviewed in Section 2.1, consists of inverters switched at the inversion frequency. Although these circuits, topologically ideal, are free from *nonlinear* distortion, they suffer from *switching* harmonics too close to the useful frequency to be filtered. The "medium-switching" group, treated in Section 2.2, consists of inverters switched in the order of a decade above the inversion frequency. Although the switching harmonics in these circuits start at a higher frequency, they are still not separated far enough from the desired component to be attenuated effectively by filters of reasonable size.

The "fast-switching" group, surveyed in Section 2.3, consists of inverters switched above two decades of the output frequency. Although most of these topologies suppress the *switching* ripple easily by small filters, they are not genuinely balanced polyphase and, hence, generate *nonlinear* distortion as troublesome as the switching noise in the slow-switching family.

# 2.1 Inverters Switched at Low Frequency

This section deals with inverters whose switching frequency is of the same order as, and often equal to, the output frequency. A great deal of operation fundamentals, harmonic analysis techniques, and design procedures for these inverters can be found in [6] and [26]. Recent advances in the inversion field on both theoretical and practical grounds have been edited in [7]. A survey of these and other documents in the literature suggests that the voltage-source, current-source, and, to a lesser extent, step-synthesis inverters are typical of the slow-switching category.

### 2.1.1 Voltage-Source Inverter

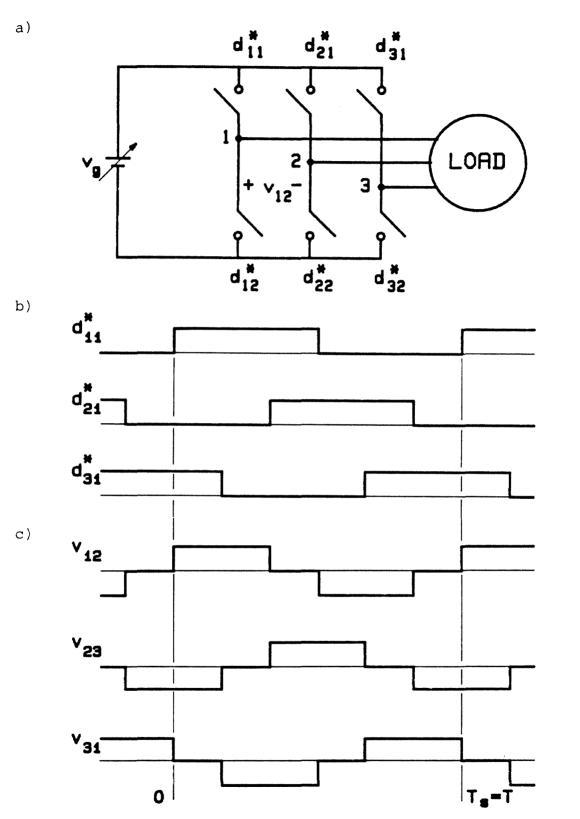

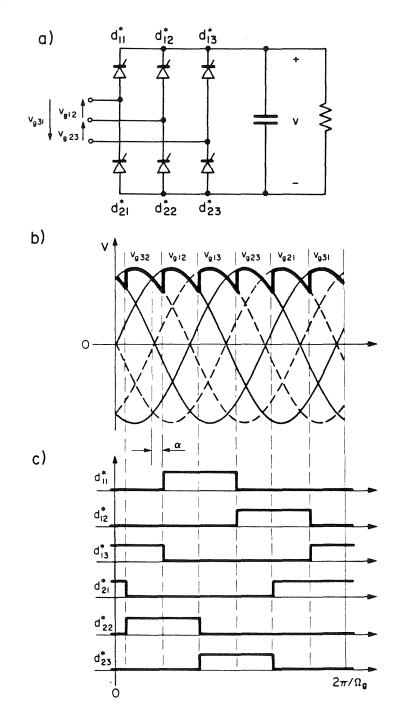

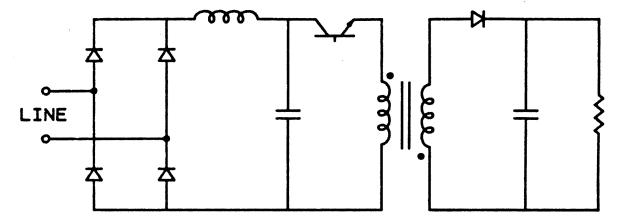

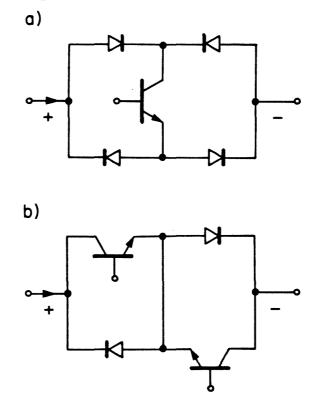

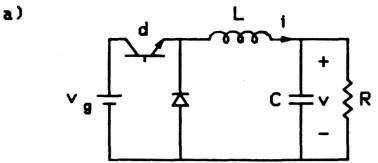

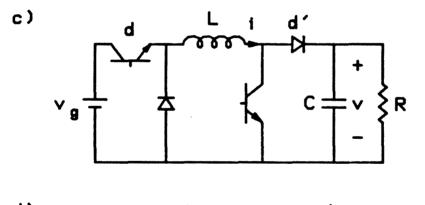

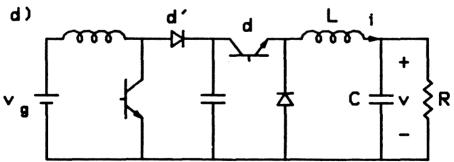

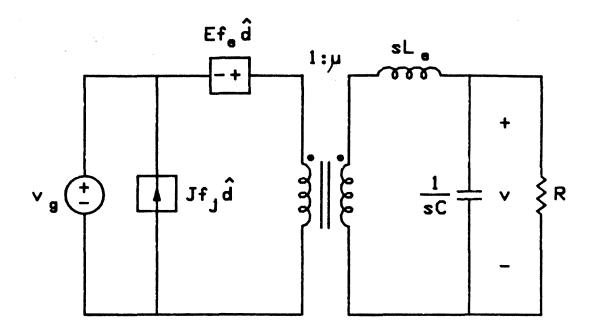

The voltage-source inverter [8] has been widely used as a variablevoltage, variable-frequency drive for ac machines. A three-phase topology simply consists of three double-throw switches permanently attached to the load, as is shown in Fig. 2.1a. In a practical circuit, each throw is realized by a pair of anti-parallel thyristor and diode ; and the variable voltage source, a phase-controlled rectifier followed by an LC filter.

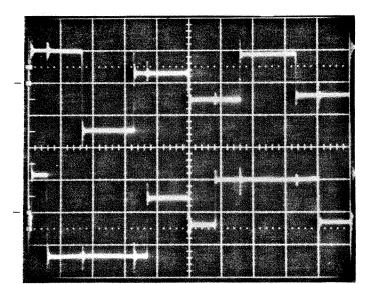

The three independent switching functions associated with the switches are sketched in Fig. 2.1b. Recall that according to the convention established in Section 1.1,  $d_{21}^*$  is the switching function for the first throw

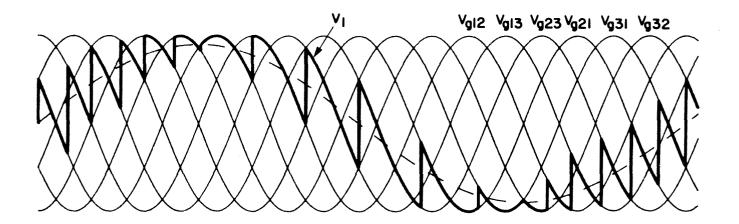

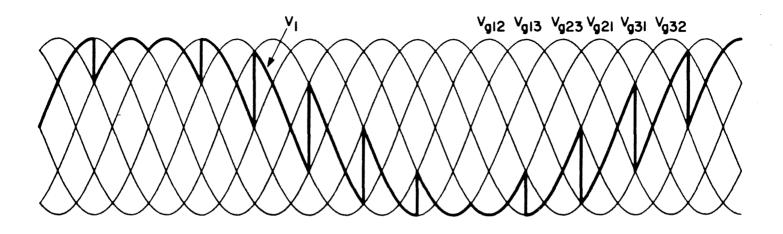

Fig. 2.1 (a) Voltage-source inverter, (b) six-stepped switching functions, and (c) line voltages.

of the second pole (switch), which brings the second phase of the load to the positive end of the source. Although the switches are functionally independent, their timing must follow the *six-stepped* schedule in Fig. 2.1b and *cannot be arbitrary* because three-phase symmetry needs be preserved. The resulting line-to-line, or line, voltages are illustrated in Fig. 2.1c. The frequency of these voltages is controlled by the switching frequency as the two are equal. Their amplitude, however, cannot be changed via the switches in the topology and, hence, must be adjusted via the dc supply which, therefore, is either a phase-controlled rectifier or a chopper.

The voltage-source inverter has been famous for its simplicity in drive and control. It, however, generates a fair amount of harmonics that cause additional heating and torque pulsation in motor loads. The use of phase control to regulate the amplitude draws current harmonics from the main and degrades the input power factor, generally lagging. These drawbacks have led to the gradual substitution of the six-stepped by the PWM drive in medium-power applications.

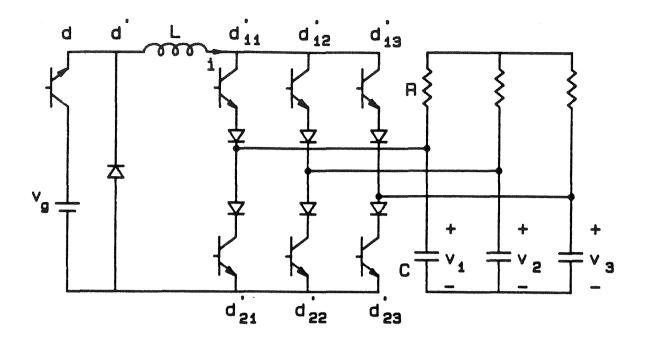

It is important to recognize that the harmonic problem in the voltage-source inverter is due to the low switching frequency, not the nonlinear distortion. In other words, the topology is already ideal and has the potential to synthesize sinusoidal waveforms if properly switched. This ideality is proved in the next chapter where the voltage-source *topology* itself is preserved, but the switches are operated at a much faster frequency and under the PWM principle.

#### 2.1.2 Current-Source Inverter

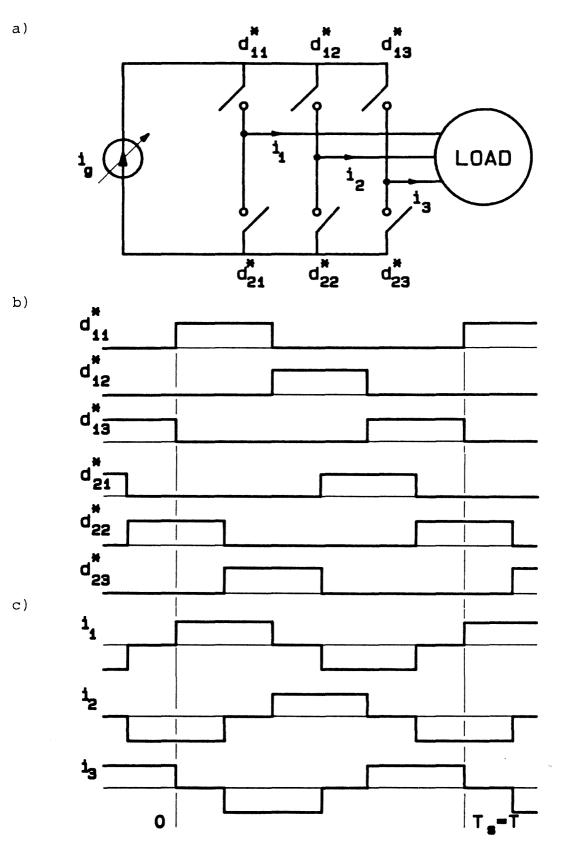

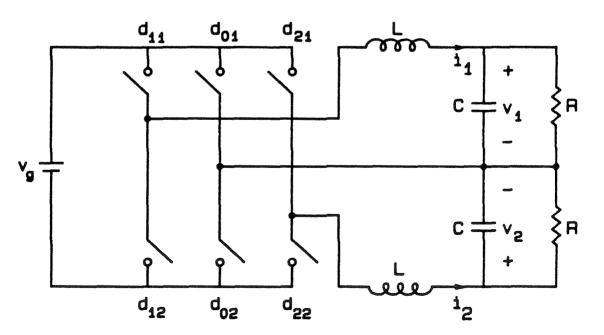

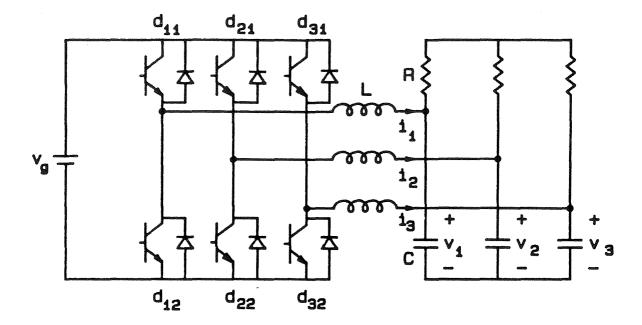

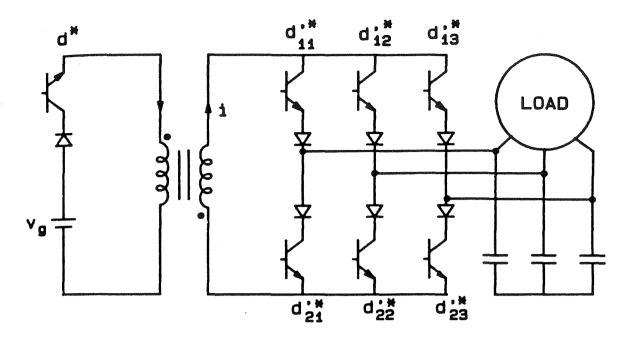

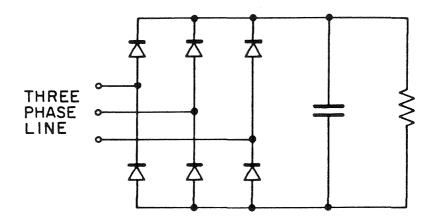

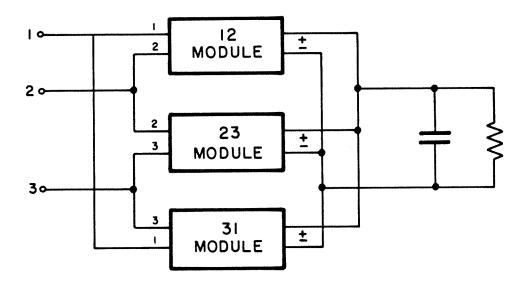

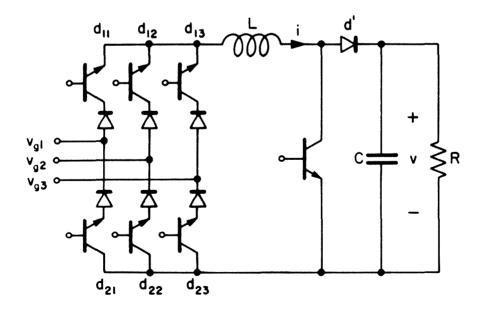

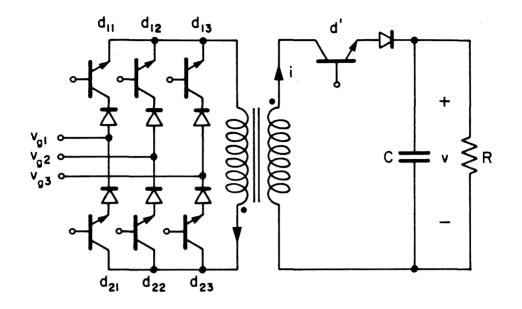

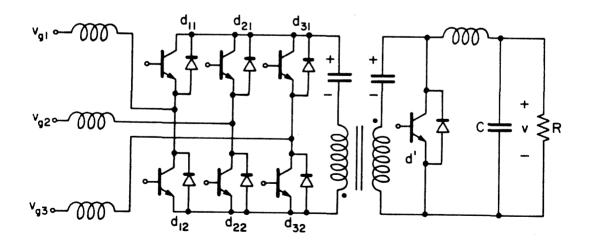

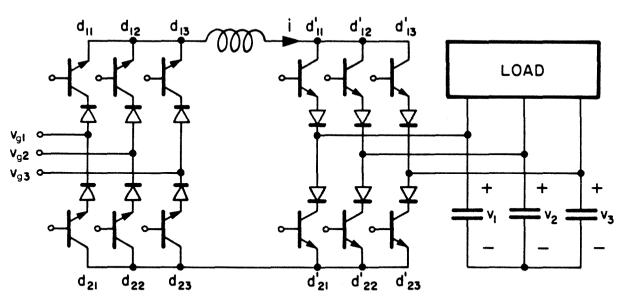

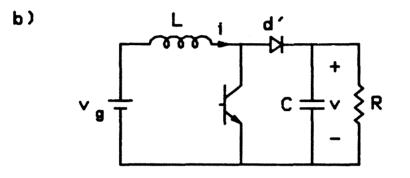

The current-source inverter [9] has gained considerable attention in the last several years. As is described in Fig. 2.2a, it consists of two triplethrow switches, instead of three double-throw switches as in the voltagesource inverter, permanently attached to a variable current source. In a practical circuit, each throw is realized by a thyristor; and the current source, a phase-controlled rectifier in series with a large inductor.

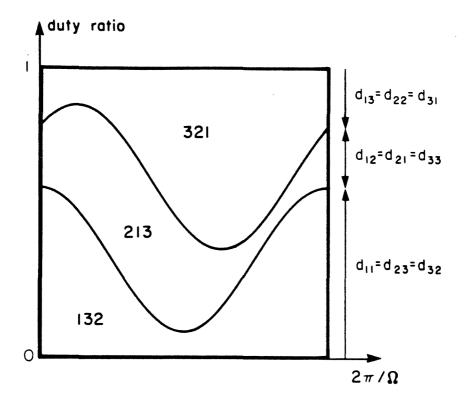

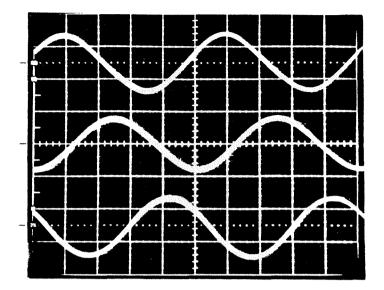

Although they are topologically independent, the two switches must be synchronized as in Fig. 2.2b to ensure three-phase symmetry. Whenever a phase of the load is contacted by a throw, it receives a current identical in form to the switching function of that throw. Therefore, each net phase current is simply the scaled difference between the switching functions associated with that phase, as is illustrated in Fig. 2.2c. Control of the output frequency is exercised via the switching frequency because the two are identical; adjustment of the amplitude is provided by the dc input.

The current-source inverter is free from the shoot-through faults found in the voltage-source inverter; in other words, no destruction occurs should more than one throw of the same switch be simultaneously activated. It also allows quick reversal of power flow when a phase-controlled rectifier is used at the input end. In spite of these merits, it still introduces lowfrequency harmonics at both input and output ports. The output harmonics incur heating loss and electrical torque pulsation, which further excites mechanical resonance detrimental to ac machines. The input noise propagates through the finite line impedance and distorts the bus waveform, creating interference problems. The power factor is generally lagging

Fig. 2.2 (a) Current-source inverter, (b) six-stepped switching functions, and (c) phase currents.

because of phase control. Besides the harmonic drawback, the currentsource inverter requires a bulky and expensive 60 Hz inductor. The size of the inductor, in turn, results in a very sluggish drive with poor dynamic performance. The inductive current source also induces large voltage spikes across the switches if it is fed directly into an inductive load, such as an induction motor.

As the voltage-source inverter, the current-source inverter is an ideal topology capable of synthesizing very clean power if it is switched at sufficiently high frequency and driven by PWM, instead of six-stepped, waveforms. Surprisingly, although the PWM voltage-source inverter has been proposed for a long time, the dual PWM current-source inverter still has not been reported. The major difficulty probably lies in the correct identification of the switches: if the switches in Fig. 2.2a were mistakenly represented as three double-throw switches, used for voltage-fed inverters, instead of two triple-throw switches, used for current-fed inverters, the synthesis of a PWM strategy would be impossible. PWM techniques for voltage- and current-fed dc-to-ac converters are studied in the next chapter and applied to the topologies in Figs. 2.1a and 2.2a to make them ideal.

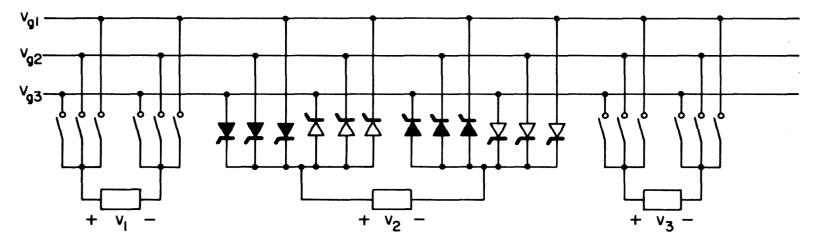

#### 2.1.3 Step-Synthesis Inverter

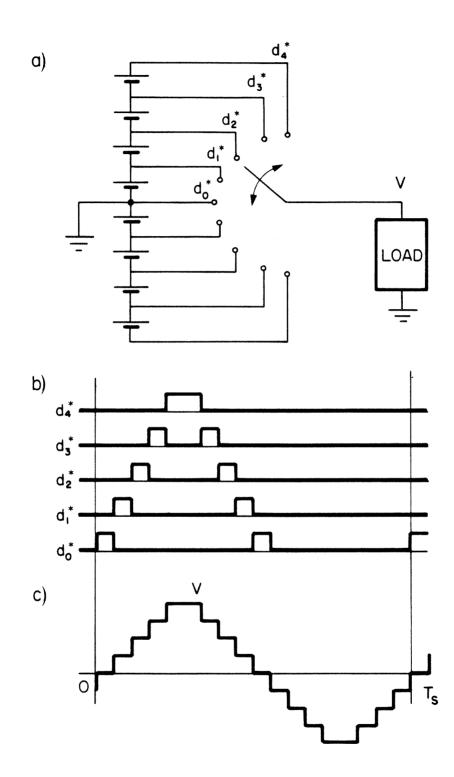

The step-synthesis inverter utilizes many slow throws to achieve the effect of a fast switch. Therefore, it may as well be placed in the fastswitching category if the classification is based on the step, instead of throw, frequency. The principle of step-synthesis is explored in Fig. 2.3 for one phase of a four-stepped circuit; the extension to three-phase is obvious. The inverter is composed of a multiple-throw switch attached to the load, as is seen in Fig. 2.3a. The throws connect the load to different voltage levels created by the bank of power supplies, realized by an autotransformer with the required amount of taps in practice [11]. In each cycle, the top five throws are activated according to the timing waveforms in Fig. 2.3b; the bottom four throws are controlled by functions  $180^{\circ}$  out-of-phase with those of the top four. The duty ratios are programmed to minimize the distortion in the "quantized" sine wave of Fig. 2.3c. Voltage control can be achieved through the source as in the previous two cases. Alternatively, two sinusoids like that in Fig. 2.3c can be synthesized and added to provide one output; their phases are then adjusted to vary the summed amplitude [12].

In principle, the quality of the output improves with a higher number of steps. This improvement, however, is at the expense of an excessive amount of switches and complex control circuitry. The stepsynthesis inverter is thus justified only for high-power applications that require sinusoidal waveforms.

In summary, this section has reviewed the voltage-source, currentsource, and step-synthesis inverters. The first topology is of the voltage-fed type and uses three double-throw switches to feed six-stepped voltages to the load. The second one is of the current-fed type and consists of two triplethrow switches that invert the input current into six-stepped output currents. The last inverter is of the voltage-fed type as the first one, but it adds more steps to the output voltage waveform to reduce the total harmonic distortion.

Fig. 2.3 (a) Stepped-synthesis inverter (b) four-stepped switching functions, and (c) phase voltage.

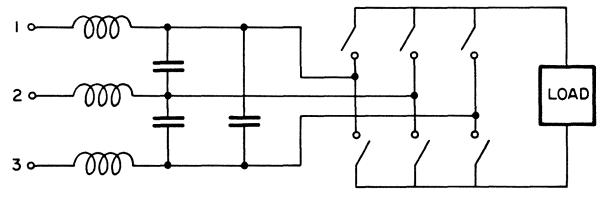

# 2.2 Inverters Switched at Medium Frequency

In the medium switching frequency range, "PWM inverter" refers generically to a voltage-source inverter (Fig. 2.1a) whose duty ratio varies from one switching cycle to the next. Even the switching frequency does not have to be constant. In 60 Hz applications, for instance, the practical switching speed may be anywhere from 60 Hz to 1 kHz, the upper bound being imposed by the slow speed of high-power semiconductor devices and the heat loss at high switching frequency [13 and 14]. Because of this medium switching frequency, it is impractical to separate the switching noise from the desired frequency component unless bulky inductors and capacitors can be tolerated. Therefore, ever since the introduction of the "sinusoidal PWM" (also called "triangulation method" or "subharmonic control") [13], a variety of other PWM schemes have been born mainly to optimize the harmonic figure. These ramifications include the "multimode" [14], "optimal" [15], "selective-harmonic-elimination" [16], "current-controlled" [17], and so on PWM strategies. The sinusoidal PWM is deferred until the next chapter where it is studied in depth (although the switching frequency there is much higher, the basic principle is still the same). The other kinds of PWM are reviewed below.

#### 2.2.1 Multimode PWM

The power-speed limitation of the thyristor and the switching loss usually restrict the switching frequency of PWM inverters below 500 Hz. Although this carrier frequency is sufficient if the desired output is only 10 Hz, it is hardly satisfactory if the load requires 100 Hz. In the later case, there are so few pulses in each inversion cycle that the performance of

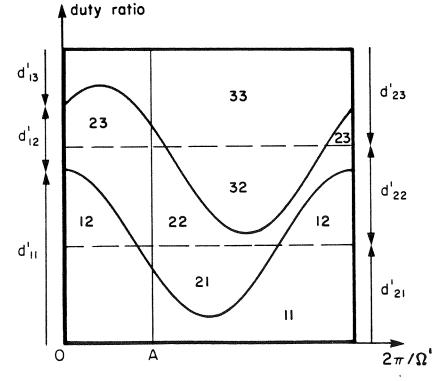

highly sensitive to the converter is the pulse number and the synchronization between the carrier and modulation signals. Without any synchronization, the difference between the switching and inversion frequencies accumulates into a slow beat frequency that modulates the output waveform. The resulting beat power gives rise to the troublesome fluctuation in the steady-state torque and speed of ac machines. Even if the two frequencies are perfectly synchronized, the purity of a PWM spectrum deteriorates to that of a six-stepped spectrum as the modulation frequency approaches the carrier frequency. Under this circumstance, the six-stepped drive is preferred to PWM drive because the former provides higher amplitude.