# THE USE OF JUNCTION TRANSISTORS IN SWITCHING CIRCUITS

Thesis by

Alfred Dale Scarbrough

In Partial Fulfillment of the Requirements

for the Degree of

Doctor of Fhilosophy

California Institute of Technology

Pasadena, California

Acknowledgments: I wish to express appreciation to the members of my thesis committee for helpful assistance and encouragement during the preparation of this report.

Thanks also are due to the Hughes Aircraft Company

for generously providing the transistors used in the experimental work described herein.

To my wife, Ruth, special thanks are due for patiently bearing the trials of a graduate student's wife.

Abstract: The theory of small signal linear junction transistor amplifiers is extended to develop design techniques which can be applied to the non-linear problems of switching circuit design.

Many of these techniques differ materially from the corresponding techniques of vacuum tube amplifier design.

The linear theory is criented toward the study of moderate-gain wide-band amplifiers driving non-inductive loads and being driven from non-inductive sources since switching circuit amplifiers commonly fall into this category, but many of the concepts have application to other amplifiers as well.

As an outgrowth of the linear theory, the transistor parameters which are important in flip-flop operation are discussed, and a new way to measure these parameters is described.

The general theory of flip-flop design is discussed in some detail, and design data is presented for the most useful of the basic flip-flop circuits. Flip-flops were designed by the method presented here and their measured performance compared with the predicted performance. The generally good agreement between theory and experiment is taken as verification of the usefulness of both the design data and the basic concepts used in the derivation of the design data.

It is concluded from this study that junction transistors are practical switching circuit elements, and it is confidently predicted that they will eventually see wide use.

## Table of Contents

| PART | TITLE                                                                           | PAGE |

|------|---------------------------------------------------------------------------------|------|

| T a  | INTRODUCTION                                                                    | 1    |

| Π.   | THE JUNCTION TRANSISTOR AS AN AMPLIFIER                                         | 6    |

|      | Preliminary Ideas                                                               | 6    |

|      | The Grounded Base Connection                                                    | 11   |

|      | The Grounded Emitter Connection                                                 | 18   |

|      | The Grounded Collector Connection                                               | 22   |

|      | Large Signal Junction Transistor Amplifiers                                     | 27   |

| III. | PULSE MEASUREMENT TECHNIQUES FOR JUNCTION TRANSISTOR PARAMETERS                 | 33   |

|      | The Measurement of C                                                            | 33   |

|      | The Measurement of $\omega_{0}$                                                 | 36   |

|      | The Measurement of $a_0/(1-a_0)$ and $\omega_0(1-a_0)$                          | 36   |

|      | Direct Measurement of the Grounded Emitter Current Gain Bandwidth Product       | 38   |

| IV.  | FLIP-FLOP CIRCUITS                                                              | 41   |

|      | Definitions                                                                     | 41   |

|      | Restrictions on the Amplifier                                                   | 41   |

|      | Possible Flip-Flop Circuit Configurations                                       | 146  |

| V.   | STATIC CONSIDERATIONS IN THE DESIGN OF SYMMETRIC JUNCTION TRANSISTOR FLIP-FLOPS | 48   |

|      | Static Design Objectives                                                        | 48   |

|      | The Basic Flip-Flop Circuit                                                     | 48   |

|      | The Static Flip-Flop Circuit                                                    | 49   |

|      | The Selection of $\mathbf{E}_{\mathbf{n}} - \mathbf{E}_{\mathbf{p}}$            | 50   |

|      | The Selection of the Maximum Collector Current                                  | 51   |

|      | The Selection of $R_{\mu}$ and $E_{p} - E_{3}$                                  | 53   |

|      | Design Telerances                                                                         | 56  |

|------|-------------------------------------------------------------------------------------------|-----|

|      | The Selection of $R_2$ , $R_3$ , $E_2$ , $I_{cp}(min)$ , and $a_o(min)$                   | 58  |

|      | The Available Output Current and the Selection of $\mathbf{R_1}$ and $\mathbf{E_1}$       | 62  |

|      | Sample Design of a Symmetric Junction Transistor Flip-Flop                                | 67  |

| VI.  | TRANSIENT CONSIDERATIONS IN THE DESIGN OF SYMMETRIC JUNCTION TRANSISTOR FLIP-FLOPS        | 73  |

|      | Transient Analysis Objectives                                                             | 73  |

|      | Notation                                                                                  | 74  |

|      | Calculation of the Rise Time                                                              | 76  |

|      | Region 1                                                                                  | 78  |

|      | Region 2                                                                                  | 80  |

|      | Region 3                                                                                  | 81  |

|      | The Influence of Circuit Parameters on the Hise Time                                      | 81  |

|      | Calculation of the Fall Time                                                              | 83  |

|      | Region A                                                                                  | 83  |

|      | Region B                                                                                  | 83  |

|      | Region C                                                                                  | 87  |

|      | The Influence of Circuit Parameters on the Fall Time                                      | 93  |

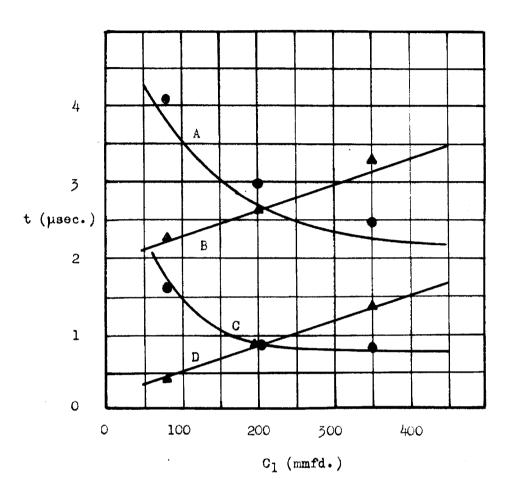

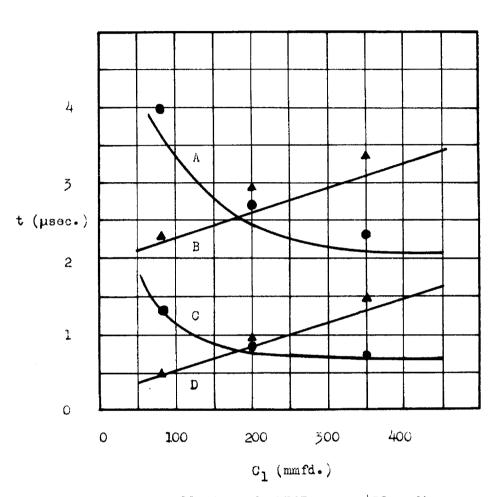

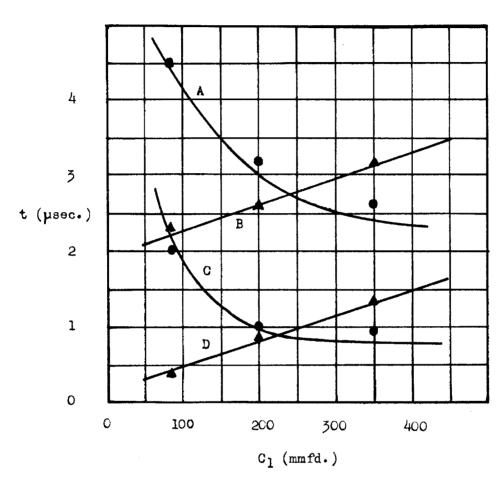

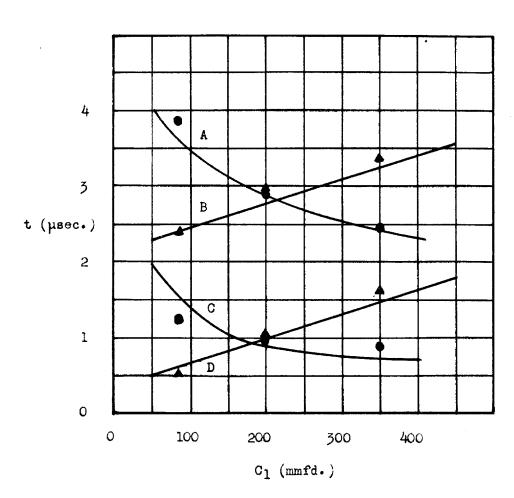

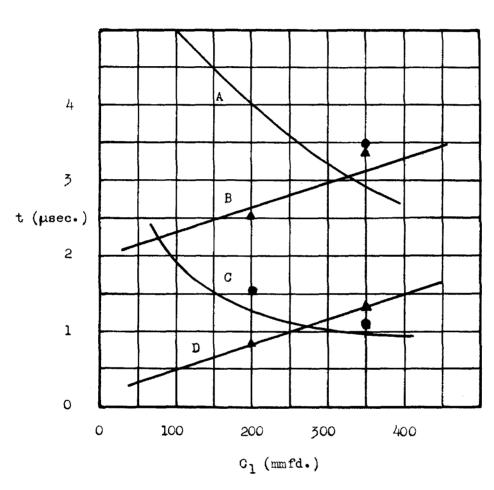

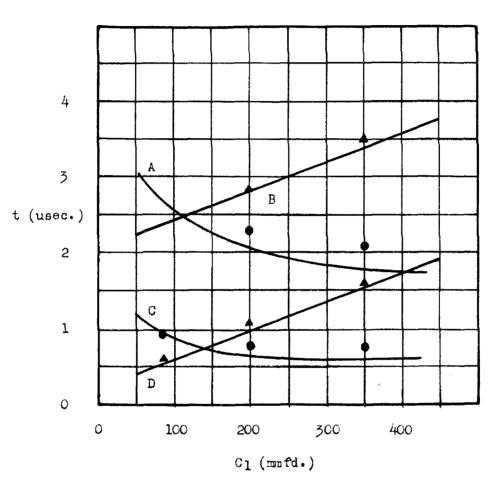

|      | Experimental Verification of the Transient Analysis and the Selection of $^{ m C}_{ m l}$ | 100 |

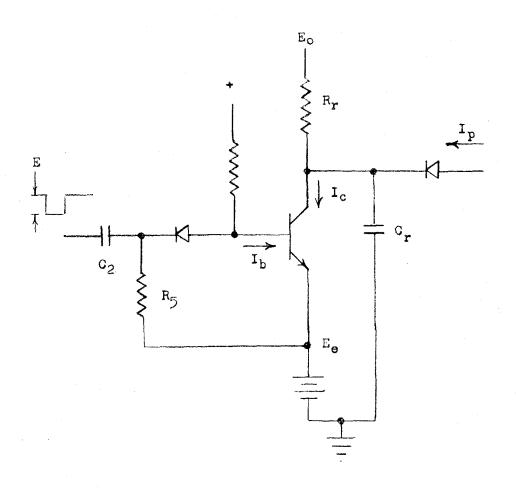

|      | Triggering the Flip-Flop                                                                  | 103 |

|      | The Complete Design of the Flip-Flop Circuit                                              | 105 |

| VII. | THE USE OF JUNCTION TRANSISTOR FLIP-FLOPS IN DIGITAL COMPUTING CIRCUITS                   | 107 |

|      | Logical Description of the Flip-Flop                                                      | 107 |

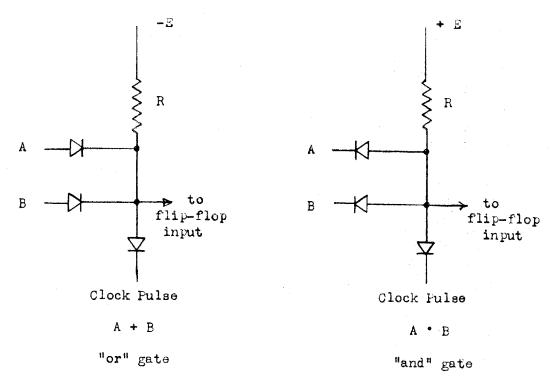

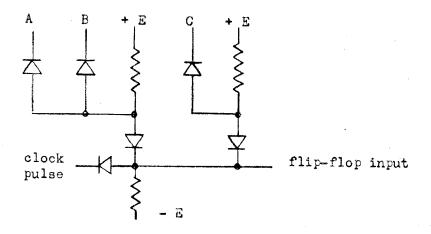

|      | Diode Gating Networks                                                                     | 108 |

|       | A Transistor Figure-of-Merit in Flip-Flop Circuits                         | 112 |

|-------|----------------------------------------------------------------------------|-----|

|       | $rac{I}{n}$ ncreasing the Usefulness of the Junction Transistor Flip-Flop | 113 |

| VIII. | APPENDIX                                                                   | 118 |

| IX.   | LIST OF REFERENCES                                                         | 123 |

| X.    | FIGURES                                                                    | 121 |

## I INTRODUCTION

The discovery of the transistor in 1948 by Bardeen and Brattain (Ref.1) was an event of singular importance to the electronic world, because it pointed the way to a number of solid state amplifying devices which could compete in many fields with the vacuum tube while offering the distinct advantages of greater ruggedness, smaller size, more efficient operation, and longer life.

Early transistors were a disappointment to many users, partly because manufacturing difficulties had prevented the production of stable, long-lived, devices; and partly because the use of transistors requires a distinctly different approach to circuit design than the use of vacuum tubes. In the years since the introduction of the transistor, improvements in manufacturing techniques have led to the production of devices which have a high order of stability and give promise of realizing the long life expectancy originally predicted. Also, with growing experience in the use of transistors, many of the problems arising from the application of transistors to active circuit design have been solved. The result is that the use of transistors is widespread today and is growing rapidly.

One of the important reasons for this growth in transistor usage was the introduction of the junction transistor, invented by Shockley in 1949 (Ref.2). The junction transistor does not have the characteristic instability which complicates linear circuit design using point contact transistors. It further appears that the junction transistor can be made more easily and cheaply than the point contact

transistor.

For these reasons, the trend in transistor circuit design has been toward the use of junction transistors and away from point contact transistors. However, it seems certain that each will continue to be best for certain uses.

In one field of application, electronic digital computers, the point contact transistor has been used much more extensively than the junction transistor. The reason for this is two-fold. It seemed that the inherent instability of the point contact transistor could be used to advantage in designing simple bi-stable devices and pulse generating and shaping circuits, and the early junction transistors were low frequency devices seemingly more suitable for audio amplifiers than for high speed computing circuits.

Even with presently available junction transistors which have far higher cut-off frequencies than the early units, many typical computer circuits, particularly pulse generators and very high speed flip-flops, can probably best be built with point contact rather than junction transistors.

It seems probable, however, that junction transistors have a place in the computing field; and it is the purpose of this study to evaluate some of the capabilities of these transistors in switching circuits. The work reported here is largely concerned with the use of junction transistors in flip-flop circuits since this is at once the switching circuit of the greatest fundamental importance and the switching circuit to which the junction transistor seems most

directly applicable.

The central problem in the analysis of junction transistor switching circuits, as it often is in engineering practice, is to approximate the physical system in such a way that useful quantitative results can be obtained without prohibitive mathematical complications.

The problem can be solved by first expressing the transistor properties in terms which permit useful, although approximate, solutions to circuit problems when the transistor experiences large signals and high frequencies; and then considering the detailed passive circuitry in terms of the characterization of the transistor, making further approximations if possible, to arrive at a practical solution to the complete problem.

Part II is concerned with the first aspect of the analysis problem, characterization of the transistor. Parts V and VI treat the flip-flop circuit in detail and develop an analytic technique for investigating all of its important properties.

To implement an analysis of this type, it is necessary both to determine which transistor parameters are significant and to find meaningful ways to measure these parameters. The fact that the transistors are to be used as large signal amplifiers suggests that large signal measurements, if they could be properly made, might provide the most useful design information. Fortunately, the large signal analysis suggests many ways that large signal measurements can be made. Part III is devoted to a description of some of the most important large signal measurements to provide a basis for

determining the transistor parameters to be used in the experimental verification of the transient analysis.

It seems desirable to devote some time to a general investigation of flip-flop circuits before attempting to deal with a specific case. Part IV is devoted to such an investigation and discloses the limitations on the amplifier thereby revealing the only possible junction transistor flip-flop circuit configurations.

Part VII is devoted to a discussion of the uses of the flip-flop.

It discusses some of its advantages and limitations and presents techniques for using additional transistors to overcome some of its limitations.

The conclusion from the material presented here must be that the junction transistor, by virtue of its performance, is a potential circuit element for use in digital computers. However, a number of considerations such as reliability, cost, size, weight, power requirements, immunity to shock, and availability must also enter into the selection of computer circuit elements.

Reliability is probably the primary consideration in computer design. For hearing aids (Ref.3) and more recently for computers (Ref.4) transistors are proving to be at least as reliable as the best vacuum tubes, and the quality of transistors is being improved rapidly. From the standpoint of cost, transistors are at present at a considerable disadvantage, but this situation is also improving rapidly.

The area of the digital computer field where it appears the junction transistor might be most useful, includes what might be

classified as the moderate speed machines having basic pulse rates of the order of 200 kc. or less. Flip-flops designed with presently available junction transistors are capable of providing useful current outputs of several milliamperes and of changing states in perhaps a microsecond. Such flip-flops can be used as fundamental building blocks for a moderate speed machine. Machines of this type have been used in airborne applications, and it appears that here, where size, weight, and power requirements are important considerations, is the most fruitful place for the application of junction transistors to digital computers.

## II THE JUNCTION TRANSISTOR AS AN AMPLIFIER

## Preliminary Ideas:

The junction transistor is an active three terminal network element. For the benefit of those who are more familiar with the vacuum tube, another three terminal active circuit element, it may be of benefit to draw a limited analogy between the vacuum tube and the transistor. The three terminals of the vacuum tube are the plate, the grid, and the cathode. The corresponding terminals of the transistor are the collector, the base, and the emitter.

The analogy can be used to find the input and output terminals for the basic amplifier circuits and to determine the phasing of input and output signals.

The transistor always has lower input impedance than the corresponding vacuum tube connection, and one must always consider input current although it is sometimes possible to neglect input voltage. The similarity of the vacuum tube to the transistor is increased considerably if one operates the vacuum tube in the positive grid region.

Physically, the junction transistor consists of a single crystal semi-conductor sandwich, the two extreme regions are of either n or p type semi-conductor and the central region is of the other type. The central region is the base, the two ends are the emitter and collector respectively. The transistor is not ordinarily symmetrical since different impurity concentrations and/or geometry are

required for most efficient functioning of the emitter and collector.

It is evident from the above description that the transistor resembles two junction diodes with a common base. For linear operation, the transistor is connected in such a way that the collector junction is back-biased (the voltage is across the junction in the direction to produce small current flow) and the emitter junction is forward-biased (the voltage is across the junction in the direction to produce large current flow). For n-p-n transistors this means the collector is positive with respect to the base, and the emitter is negative with respect to the base. For p-n-p transistors the polarities are reversed.

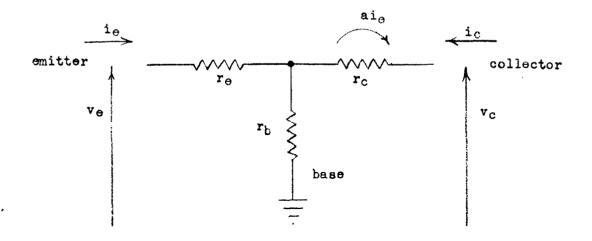

There have been many discussions in the literature of linear equivalent circuits for transistors. (Ref.5,6,7) Strictly speaking, these are useful only for small signal operation over a limited frequency range. Of the many possible circuits, the one which seems most appropriate for extension to large signals and wide frequency bands is the equivalent T given in its low frequency form in fig.II-1\*.

The attractive feature of this circuit is that the circuit elements have some correspondence with the physical characteristics of the transistor. Thus we identify  $\mathbf{r}_{\mathbf{c}}$  with the resistance of the collector barrier,  $\mathbf{r}_{\mathbf{e}}$  with the resistance of the emitter barrier, and  $\mathbf{r}_{\mathbf{b}}$  with the spreading resistance of the base region. The current generator constant  $\mathbf{a}$  is almost the same as the current

The figures are grouped together at the end of the report.

gain parameter a of the transistor.

This last statement is easily seen to be true by considering the set of linear equations represented by the equivalent circuit,

$$v_e = (r_e + r_b) i_e + r_b i_c$$

(II-la)

$$v_c * (ar_c + r_b) i_e + (r_b + r_c) i_c$$

(II-1b)

The current gain parameter is by definition the negative of the ratio of  $i_c$  to  $i_e$  with  $v_c$  equal to zero (i.e. with the collector short circuited). We have then

$$\alpha = -\frac{i_c}{i_e}\Big|_{v_c = 0} = \frac{ar_c + r_b}{r_b + r_c} = \frac{a}{1 + \frac{r_b}{r_c}} + \frac{r_b}{r_b + r_c} \approx a$$

(II-2)

since  $r_c \gg r_b$  for junction transistors.

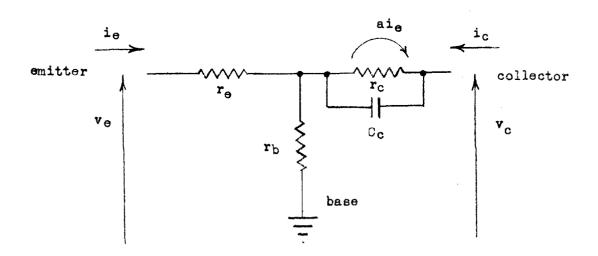

From the physical theory of transistors we know that each junction has a capacity associated with it. (Ref.2) It might seem to be necessary to shunt both  $r_c$  and  $r_e$  by suitable condensers as a first step toward extending the equivalent circuit to high frequencies. We recall, however, that  $r_e$  is approximately the forward resistance of a diode and hence is very small. An approximate analysis shows that the time constant of the emitter junction is very small compared to the other time constants of the circuit, so we simplify the equivalent circuit by including only the collector capacity.

Another result from the physical theory is that a has the frequency dependence of a delay line (Refs.8,9). This frequency dependence introduces reactive components at high frequencies which must be considered in any realistic attempt to study the high

frequency behavior of transistors. It is theoretically impossible to develop an exact equivalent circuit for the frequency variation of a since it would require an infinite number of circuit elements. The approach has been used to put this frequency dependence into the equivalent circuit by injecting the current through one or two sections of lumped constant delay line (Ref.10). The equivalent circuit is a cumbersome tool when it gets as complicated as even the simplest transistor equivalent circuit, however, it provides a convenient description of the important transistor parameters.

For switching circuit analysis it is convenient to use the circuit of fig.II-1 and simply assign a the first order frequency dependence which was calculated for  $\alpha$ . In terms of the LaPlace transform variable, s, this becomes

$$a = \frac{a_0 \omega_0}{s + \omega_0} . \tag{II-3}$$

The zero frequency value of this function is  $a_0$  and  $\omega_0$ , the cutoff frequency, is the angular frequency at which the amplitude of a

is down by  $(2)^{-1/2}$ . We note that this is also the point at which the

phase shift is 45 degrees. In actual transistors, these two points

do not occur at the same frequency since (II-3) is only approximately

true. This introduces some small complications in the theory which

will be discussed later.

Various more complicated equivalent circuits have been proposed which represent the high-frequency small-signal behavior of the transistor more closely than the circuit proposed here. For extension

to large signals, these refinements are perhaps unjustified in view of the approximations which must be made to treat the problem at all. Experience indicates that the proper approximations applied to this simple circuit will yield good first order solutions to switching circuit problems. For that reason the equivalent circuit of fig.II-2 has been chosen as the simplest characterization of the transistor which can profitably be used in switching circuit analysis. The rest of this work will be expressed in terms of that characterization.

Typical values for the equivalent T parameters for a junction transistor might be

r<sub>.</sub> = 5 x 10<sup>6</sup> ohms

C = 45 mmfd.

$r_a = 30 \text{ ohms}$

$r_{\rm h}$  = 60 ohms

$\omega_0 = 5 \times 10^6 \text{ rad./sec.}$

a<sub>0</sub> = •96

It is desirable to develop approximate expressions for such things as input impedance, output impedance, transfer impedance, open circuit voltage gain, and short circuit current gain for the various transistor connections. In doing this we will make use of the approximate values of the equivalent T parameters. That is, we will assume that  $\mathbf{r}_{e}$  and  $\mathbf{r}_{b}$  are always small compared to  $\mathbf{r}_{c}$  or  $\mathbf{r}_{c}(\mathbf{l}-\mathbf{a}_{o})$  and that time constants obtained by multiplying  $\mathbf{r}_{e}$  and  $\mathbf{r}_{b}$  by any circuit capacity are always negligible compared to other time constants in the circuit.

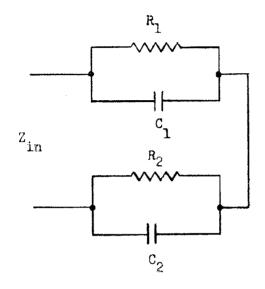

The circuits to be considered in detail are those which have generator impedances  $\mathbf{Z}_{\mathbf{g}}$  and load impedances  $\mathbf{Z}_{\mathbf{L}}$  which consist of a parallel combination of a resistor and a condenser. That is  $\mathbf{Z}_{\mathbf{g}}$  consists of  $\mathbf{r}_{\mathbf{g}}$  and  $\mathbf{C}_{\mathbf{g}}$  in parallel, and  $\mathbf{Z}_{\mathbf{L}}$  consists of  $\mathbf{r}_{\mathbf{L}}$  and  $\mathbf{C}_{\mathbf{L}}$  in parallel. In keeping with this notation we introduce the symbol  $\mathbf{Z}_{\mathbf{c}}$  which denotes the parallel combination of  $\mathbf{r}_{\mathbf{c}}$  and  $\mathbf{C}_{\mathbf{c}}$ .

The generator and load impedances are of such size that careful consideration must be given to approximations involving them. Ordinarily the resistive component of either load or source is much smaller than  $r_c$ , but the reactive terms can not be dropped because of this. As an example of the typical approximation procedure, the term  $z_g/z_c$  would be approximated as

$$\frac{z_{g}}{z_{c}} = \frac{c_{c}(\frac{1}{r_{c}}c_{c} + s)}{c_{g}(\frac{1}{r_{g}}c_{g} + s)} \approx \frac{c_{c} s}{c_{g}(s + \frac{1}{r_{g}}c_{g})}.$$

(II-4)

Exact expressions for the various impedance and gain functions are derived in Ref.10 for the characterization of fig.II-2. In the following sections the frequency dependence of a is inserted in these expressions to develop useful approximations for the gain and impedance functions in each of the three basic connections.

#### The Grounded Base Connection:

The grounded base connection is characterized by low input impedance, high output impedance, and no phase reversal. The current gain is less than one, but because of the high ratio of output to input impedance, power and voltage gain greater than one can be achieved.

The input impedance is given by

$$Z_{1n} = \frac{1}{Y_{1n}} = \frac{r_{e} r_{b} + Z_{e} \left[ r_{e} + r_{b}(1-a) \right] + (r_{e} + r_{b}) Z_{L}}{r_{b} + Z_{e} + Z_{L}}$$

$$\approx \frac{r_{e} + r_{b}(1 - \frac{a_{o} \omega_{o}}{s + \omega_{o}}) + (r_{e} + r_{b}) \frac{c_{e} s}{c_{L}(s + \frac{1}{r_{L} c_{L}})}}{1 + \frac{c_{e} s}{c_{L}(s + \frac{1}{r_{L} c_{L}})}}$$

$$= (r_{e} + r_{b}) \left\{ s^{2} + \frac{s c_{L} \omega_{o}}{c_{L} + c_{e}} \left[ \frac{1}{\omega_{o}} \frac{1}{r_{L} c_{L}} + \frac{r_{e} + r_{b}(1 - a_{o})}{r_{e} + r_{b}} + \frac{c_{c}}{c_{L}} \right] \right\}$$

$$= \frac{\omega_{o}}{r_{L}(c_{L} + c_{e})} \frac{r_{e} + r_{b}(1 - a_{o})}{r_{e} + r_{b}}$$

$$(s + \frac{1}{r_{L}(c_{L} + c_{e})}) (s + \omega_{e})$$

on the real axis; and two zeros, also in the left half-plane, which may be either real or complex conjugate depending on the parameters of the circuit. The magnitude of  $Z_{\rm in}$  for any frequency is the product of the distances from the point on the imaginary axis representing that frequency to the poles divided by the product of the distances from the point to the zeros. It follows from this geometric picture that the maximum value of the magnitude of the input

impedance occurs at either zero or infinite frequency. For the above expression, the maximum value occurs at infinite frequency and is  $r_e + r_h$ , a very small quantity.

The fact that the input impedance is small for all values of frequency makes possible a very important simplification in many practical circuits. If the driving impedance is large compared to the input impedance, one can compute the emitter current on the assumption that the emitter voltage is zero. This is the dual of the common assumption of vacuum tube theory that the grid current is zero.

Even though it results in a reduction of the power gain of a transistor stage, it is often desirable to drive the transistor from a high impedance source (relative to the input impedance) since this offers the advantages of greater bandwidth and more linear operation.

It is instructive to examine the input impedance for the simple special case of  $r_L$  very small. Taking the limit of expression (II-5) as  $r_L$  goes to zero gives

$$z_{in} = \frac{(r_e + r_b) \left[ s + \omega_o \frac{r_e + r_b(1 - a_o)}{r_e + r_b} \right]}{s + \omega_o}.$$

(II-6)

An equivalent circuit for this expression is given in fig. II-3 together with the values of the elements of the circuit. This circuit has the same zero and infinite frequency impedance as the more complicated expression of (II-5). It is seen that the low frequency reactive component of the input impedance of the grounded base

connection with  $Z_L = 0$  is inductive.

It is instructive in connection with the result of (II-6) to point out some of the limitations of the approximate formulas developed here. A glance at the equivalent circuit of fig.II-2 shows that the high frequency input impedance with the collector grounded must approach  $r_{\rm e}$  as the frequency becomes very high. This is in contrast to equation (II-6) which says it approaches  $r_{\rm e} + r_{\rm b}$ . This does not mean that the approximate formulas have no validity, but simply that they apply to a restricted frequency range. In practice, they can be applied with fair accuracy at frequencies up to the cutoff frequency. We have simply neglected high frequency poles and zeros of the form  $\tau$  (s +  $\frac{1}{\tau}$ ) where  $\gamma$  is small.

The output impedance of the grounded base connection is

$$z_{\text{out}} = \frac{1}{Y_{\text{out}}} = \frac{(r_b + Z_c) Z_g + r_e Z_c + r_e r_b + r_b Z_c (1-a)}{Z_g + r_e + r_b}$$

(II-7)

If  $z_g$  is large compared to  $r_e + r_b$ ,

$$z_{\text{out}} \approx z_{\text{c}}$$

(II=8)

The transfer impedance of the grounded base stage is

$$Z_{t} = \frac{(r_{b} + a Z_{c}) Z_{L}}{Z_{L} + r_{b} + Z_{c}} \approx \frac{a Z_{L}}{1 + \frac{Z_{L}}{Z_{c}}} \approx \frac{a_{o} \omega_{o}}{(C_{c} + C_{L})(s + \omega_{o}) \left[s + \frac{1}{r_{L}(C_{L} + C_{c})}\right]}$$

(II-9)

If the transistor is driven from a voltage source  $\mathbf{E}_{\mathbf{g}}$  through a series impedance  $\mathbf{Z}_{\mathbf{g}}$  which is large compared to the input impedance,

the input current i becomes

$$i_e = \frac{E_g}{Z},$$

(II-10)

and the output voltage  $e_c$  becomes

$$e_c = i_e Z_t = \frac{E_g}{Z_g} Z_t.$$

(II-11)

We define the ratio of  $e_c$  to  $E_g$  as the voltage gain  $A_{\mbox{\scriptsize t}}$  and we have

$$A_{t} = \frac{e_{c}}{E_{g}} = \frac{Z_{t}}{Z_{g}} = \frac{a_{o} \omega_{o}}{Z_{g}(C_{c} + C_{L})(s + \omega_{o}) \left[s + \frac{1}{r_{L}(C_{L} + C_{c})}\right]}$$

(II-12)

For the special case of  $r_1(C_1 + C_2)$  small this reduces to

$$\Lambda_{\rm t} = \frac{{\rm a_o \, \omega_o \, r_L}}{{\rm Z_g(s + \omega_o)}}. \tag{II-13}$$

If  $Z_g$  is simply a resistance, the cut-off frequency of  $A_{\dot t}$  is  $\omega_o$  . A more interesting case occurs when  $Z_g$  consists of a resistor  $r_g$  in parallel with a condenser  $C_g$  . Then

$$A_{t} = a_{0} \omega_{0} r_{L} c_{g} \frac{\left(s + \frac{1}{r_{g} c_{g}}\right)}{\left(s + \omega_{0}\right)}$$

(II-14)

If we choose  $1/r_g$   $C_g$  =  $\omega_o$  , the expression for voltage gain becomes

$$A_{t} = \frac{a_{o} r_{L}}{r_{g}}$$

(II-15)

which is first order independent of frequency. This means that the cut-off frequency becomes  $1/r_L(C_L+C_c)$  which was assumed to be very

much greater than  $\omega_0$ . Thus we see that under certain conditions it is possible to extend the bandwidth of a grounded base transistor amplifier by driving it through a suitable compensating input impedance.

The voltage gain of a grounded base amplifier is

$$A_{e} = \frac{(r_{b} + a Z_{c}) Z_{L}}{(r_{e} + r_{b}) Z_{L} + r_{e} Z_{c} + r_{e} r_{b} + r_{b} Z_{c}(1-a)} \approx \frac{a_{o} r_{L}}{r_{L}(r_{e} + r_{b})(C_{L} + C_{c})} s^{2} + \left\{\frac{r_{e} + r_{b}}{\omega_{o}} + r_{L}C_{c}(r_{e} + r_{b}) + r_{L}C_{L}[r_{e} + r_{b}(1-a_{o})]\right\} s} + r_{e} + r_{b}(1-a_{o}).$$

If we consider the special case of  $r_L(C_L+C_c)$  negligible compared to the other time constants of the circuit, the voltage gain reduces to

$$A_{e} = \frac{a_{o} \omega_{o} r_{L}}{(r_{e} + r_{b}) (\frac{\omega_{o} [r_{e} + r_{b} (1 - a_{o})]}{r_{a} + r_{b}} + s)}$$

(II-17)

which has cut-off frequency  $\omega_{c}$  given by

$$\omega_{c} = \frac{\omega_{o} \left[r_{e} + r_{b}(1 - a_{o})\right]}{r_{e} + r_{b}}.$$

(II-18)

The cut off frequency  $\omega_c$  is always less than  $\omega_o$ , but it may approach it if  $r_b$  is much smaller than  $r_e$ . If the amplifier is driven out of a zero impedance generator,  $\omega_c$  will be the cut-off frequency of the voltage gain from the generator to the output. If the amplifier is driven through a resistor, which is effectively the same as increasing

$r_e$  in (II-18), the cut-off frequency approaches  $\omega_o$ ; and if the proper compensating input condenser is used, the cut-off frequency can be increased to  $1/r_L(C_L+C_c)$ .

The increase in the bandwidth does not necessarily result in an increase in the gain bandwidth product. Driving from a zero impedance source results in a gain bandwidth product of  $a_o \omega_o r_L/(r_e+r_b)$  driving through a resistor  $r_g$  which is large compared to  $r_e+r_b$  reduces the gain bandwidth product to  $a_o \omega_o r_L/r_g$ , and driving through the compensated input impedance results in a gain bandwidth product of  $a_o/r_g(C_L+C_c)$ . The compensated gain bandwidth product may be either greater or less than the gain bandwidth product of the transistor driven from a zero impedance source depending on the values of the circuit constants.

The open circuit voltage gain is obtained from (II-16) by letting the load impedance become infinite. It is

$$A_{e}(\text{open circuit}) \approx \frac{a_{o} \omega_{o}}{C_{L}(r_{e} + r_{b}) (s + \omega_{o}) (s + \frac{1}{r_{c} C_{c}})}$$

(II-19)

The zero frequency value of this is

$$\frac{a_0 r_c}{r_e + r_b}.$$

(II-20)

It is apparent that even though the current gain is less than one in this connection, large values of open circuit voltage gain are possible because of the high ratio of  $r_{\rm c}$  to  $r_{\rm e}+r_{\rm b}$ .

The short circuit current gain of the grounded base connection is approximately a as given by (II-3).

#### The Grounded Emitter Connection:

The grounded emitter connection has higher input and lower output impedance than the grounded base stage. It produces a phase reversal and has both current and voltage gains greater than one.

The input impedance of the grounded emitter stage is

$$Z_{\text{in}} = \frac{1}{Y_{\text{in}}} = \frac{(r_e + r_b) Z_L + r_e Z_c + r_e r_b + r_b Z_c (1-a)}{Z_L + r_e + Z_c (1-a)}$$

(II-21)

$$r_{\rm L}(r_{\rm e}+r_{\rm b})(c_{\rm L}+c_{\rm c})s^2+\left\{(r_{\rm e}+r_{\rm b})(1+r_{\rm L}c_{\rm c}\omega_{\rm o})+r_{\rm L}c_{\rm L}\omega_{\rm o}[r_{\rm e}+(1-a_{\rm o})r_{\rm b}]\right\}s^2+c_{\rm L}c_{\rm L}\omega_{\rm o}[r_{\rm e}+(1-a_{\rm o})r_{\rm b}]$$

$$\approx \frac{+ \omega_{o} [r_{e} + r_{b} (1 - a_{o})]}{r_{r} (c_{L} + c_{e}) s^{2} + \{1 + \omega_{o} r_{L} [c_{e} + (1 - a_{o}) c_{L}]\} s + \omega_{o} (1 - a_{o})}$$

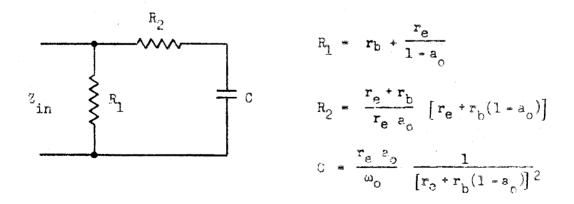

This expression, like the expression for the input impedance of the grounded base connection is difficult to use for practical computation. Since the poles of (II-21) are real, it falls in the class of expressions which have their maximum absolute value at either zero or infinite frequency. In this case the maximum value of the input impedance occurs at zero frequency and is

$$z_{in(max)} = r_b + \frac{r_e}{1-a_o}. \qquad (II-22)$$

The expression for the input impedance of the grounded emitter connection becomes much simpler for the special case of  $r_L$  small. Taking the limit of (II-21) as  $r_L$  goes to zero yields,

$$Z_{in} = \frac{(r_e + r_b) s + \omega_o r_e + \omega_o r_b (1 - a_o)}{s + \omega_o (1 - a_o)}$$

(II=23)

An equivalent circuit for this expression is given in fig.II-4 together with the values of the elements of the circuit. This circuit has the same zero and infinite frequency impedance as the more complicated expression of (II-21). It is seen that the low frequency reactive component of the input impedance of the grounded emitter stage is capacitive.

The input impedance of the grounded emitter stage is much higher than the input impedance of the grounded base stage; nevertheless, it is frequently desirable to drive the grounded emitter stage from such a high impedance generator that the input impedance can be neglected when calculating the base current. This results in improved linearity and easier computation, and can with proper compensation result in better frequency response.

The output impedance of the grounded emitter stage is

$$Z_{\text{out}} = \frac{r_{\text{e}} r_{\text{b}} + Z_{\text{c}} \left[r_{\text{e}} + r_{\text{b}} (1-a)\right] + Z_{\text{g}} \left[r_{\text{e}} + Z_{\text{c}} (1-a)\right]}{r_{\text{b}} + r_{\text{e}} + Z_{\text{g}}}$$

$$\approx Z_{\text{c}} (1-a) \approx \frac{s + \omega_{\text{o}} (1-a_{\text{o}})}{C_{\text{c}} (S + \omega_{\text{o}}) (s + \frac{1}{r_{\text{e}}} \frac{1}{C_{\text{c}}})}.$$

(II-24)

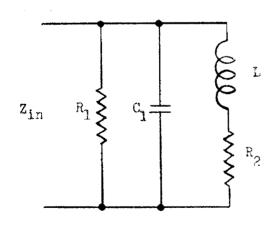

An equivalent circuit for the output impedance is given in fig.II-5.

The transfer impedance of the grounded emitter stage is

$$Z_{t} = \frac{(r_{e} - a Z_{c}) Z_{L}}{Z_{L} + r_{e} + Z_{c}(1 - a)}$$

$$\approx -\frac{a_{o} \omega_{o}}{(C_{L} + C_{c})} \frac{1}{s^{2} + \left[\frac{1 + \omega_{c} r_{L}[C_{c} + (1 - a_{o})C_{L}]}{r_{L}(C_{L} + C_{c})}\right] s + \frac{(1 - a_{o})\omega_{o}}{r_{L}(C_{L} + C_{c})}}.$$

(II-25)

If the transistor is driven from a voltage source  $E_g$  through a series impedance  $\mathbf Z_g$  which is large compared to the input impedance, the input current  $\mathbf i_h$  becomes

$$i_b = \frac{E_g}{Z_g}$$

(II=26)

and the output voltage ec becomes

$$e_c = i_b Z_t = \frac{E_g}{Z_g} Z_t$$

. (II-27)

If the ratio of  $e_c$  to  $E_g$  is defined as a voltage gain  $A_{\hat{t}}$  ,

$$A_{t} = \frac{e_{c}}{E_{g}} = \frac{Z_{t}}{Z_{g}} = \frac{-a_{o} \omega_{o}}{Z_{g}(C_{L} + C_{c})} = \frac{1}{s^{2} + \frac{1 + \omega_{o} r_{L} [C_{c} + (1 - a_{o})C_{L}]}{s^{2} + \frac{(1 - a_{o})\omega_{o}}{r_{L} (C_{L} + C_{c})}}.$$

For the special case of  $r_{T}$  small, this reduces to

$$A_{t} = -\frac{a_{o} \omega_{o} r_{L}}{Z_{g} [s + \omega_{o} (1 - a_{o})]}$$

(II-29)

If  $Z_g$  is a resistance, the cut-off frequency of  $A_t$  is  $\omega_o(1-a_o)$ . If  $Z_g$  is a resistor  $r_g$  in parallel with a condenser  $C_g$ ,  $A_t$

$$A_{t} = -\frac{a_{o} \omega_{o} r_{L} C_{g} (s + \frac{1}{r_{g} C_{g}})}{s + \omega_{o} (1 - a_{o})}$$

(II-30)

By choosing  $1/r_g$   $C_g = \omega_o(1-a_o)$ , we can make (II-30) frequency independent. For practical purposes, where  $r_L$  is not zero, this means that one can cancel the low frequency pole of (II-28) and the actual cut-off frequency will then be determined by the high frequency pole. Thus we see that in the grounded emitter connection

it is possible to increase the bandwidth by driving through a suitable compensating input impedance.

The voltage gain of the grounded emitter stage is

$$A_{e} = \frac{(r_{e} - a Z_{c}) Z_{L}}{(r_{e} + r_{b})Z_{L} + r_{e} Z_{c} + r_{e} r_{b} + r_{b} Z_{c}(1 - a)} \approx \frac{(II - 31)}{r_{L}(r_{e} + r_{b})(C_{L} + C_{c})} \approx \frac{r_{L}}{\omega_{o}} + r_{L} C_{c}(r_{e} + r_{b}) + r_{L} C_{L}[r_{e} + r_{b}(1 - a_{o})] s$$

$$+ r_{e} + r_{b}(1 - a_{o}).$$

We note that to the degree of approximation involved here this is the same (except for the negative sign) as the expression for voltage gain in the grounded base connection.

The voltage gain when  $r_{\rm L}$  is small is

$$A_{e} \approx \frac{a_{o} \omega_{o} r_{L}}{(r_{e} + r_{b}) (\frac{\omega_{o} [r_{e} + r_{b}(1 - a_{o})]}{r_{e} + r_{b}}) + s}$$

(II-32)

and the open circuit voltage gain is

<sup>A</sup>e(open circuit)

$$\approx \frac{a_o \omega_c}{C_L(r_e + r_b) (s + \omega_o) (s + \frac{1}{r_c C_c})}$$

(II-33)

which has the zero frequency value

$$\frac{\mathbf{a}_{0} \mathbf{r}_{c}}{\mathbf{r}_{e} + \mathbf{r}_{b}} \tag{II-34}$$

The short circuit current gain is

$$A_{i} = \frac{a Z_{c} - r_{e}}{r_{e} + Z_{c}(1-a)} \approx \frac{a}{1-a} \approx \frac{a_{o} \omega_{o}}{s + \omega_{o}(1-a_{o})}$$

(II-35)

The low frequency value of the short circuit current gain is  $a_o/(1-a_o)$  and the cut-off frequency is  $\omega_o(1-a_o)$ .

#### The Grounded Collector Connection:

The grounded collector connection has the highest input impedance and lowest output impedance of the basic transistor connections. It has voltage gain less than one, but the current gain is greater than one and substantial power gains are available. The connection does not provide a phase reversal.

The input impedance of the grounded collector stage is

$$Z_{\text{in}} = \frac{r_{\text{e}} r_{\text{b}} + Z_{\text{c}} [r_{\text{c}} + r_{\text{b}} (1 - a)] + Z_{\text{L}} (r_{\text{b}} + Z_{\text{c}})}{r_{\text{e}} + Z_{\text{c}} (1 - a) + Z_{\text{L}}}$$

$$\approx \frac{Z_{\text{L}} Z_{\text{c}}}{Z_{\text{L}} + Z_{\text{c}} (1 - a)} \approx \frac{Z_{\text{c}} \frac{Z_{\text{L}}}{1 - a}}{Z_{\text{c}} + \frac{Z_{\text{L}}}{1 - a}}$$

(II-36)

which has the form of an impedance  $Z_L(1-a)$  in parallel with  $Z_c$  . If  $Z_T$  is a resistor and condenser in parallel,

$$\frac{Z_{L}}{1-a} \approx \frac{S + \omega_{c}}{C_{L} \left(S + \frac{1}{r_{L} C_{L}}\right) \left[S + \omega_{c} (1-a_{c})\right]}$$

(II=37)

In the situation of greatest practical interest,  $\omega_{_{\rm O}}$  is much larger than either  $\omega_{_{\rm O}}(1-a_{_{\rm O}})$  or  $1/r_{\rm L}$  C $_{\rm L}$ . Under these conditions, (II=37) represents an impedance which cannot be realized as a passive circuit since it has a negative real part at sufficiently high

frequencies, (Ref.11). To see this, set  $s=j\omega$  and write (II-37) in rationalized form as

$$\frac{\frac{Z_{L}}{1-a}}{\frac{\omega_{o}^{2}(1-a_{o})}{r_{L}C_{L}} + \omega^{2}\omega_{o}\left[\frac{1}{\omega_{o}}\frac{1}{r_{L}C_{L}} - 1\right] + j\omega\left[\frac{\omega_{o}(1-a_{o})}{r_{L}C_{L}} - \omega_{o}^{2}(1-a_{o}) - \frac{\omega_{o}}{r_{L}C_{L}} - \omega^{2}\right]}{c_{L}\left\{\omega^{4} + \omega^{2}\left[\omega_{o}^{2}(1-a_{o})^{2} + \frac{1}{r_{L}^{2}C_{L}^{2}}\right] + \frac{\omega_{o}^{2}(1-a_{o})^{2}}{r_{L}^{2}C_{L}^{2}}\right\}}$$

It is evident from this expression that at sufficiently high frequencies, the input impedance of the grounded emitter connection looks like a series negative resistor and a capacitor (at a single frequency only, since both the resistance and capacitance are functions of frequency.)

A useful approximate expression for the real part of (II-38) can be obtained when  $1-a_0+1/\omega_0$  r<sub>L</sub> C<sub>L</sub> is negligible compared to one. Let

$$u = \frac{\omega^2 r_L c_L}{\omega_0 (1 - a_0)}$$

(II-39)

and

$$K = \frac{1}{\omega_{o} r_{L} C_{L}(1-a_{o})} + \omega_{o} r_{L} C_{L}(1-a_{o})$$

(II-40)

Then the real part of (II-38) is approximately

$$\frac{Z_{L}}{1-a} \bigg|_{\text{Real part}} \approx \frac{r_{L}}{1-a_{0}} \qquad \frac{1-u}{1+u^{2}+u K} \qquad (II-41)$$

The minimum value of this occurs at

$$u = 1 + (2 + K)^{1/2}$$

(II-42)

and has the value

$$\frac{r_{L}}{1-a_{o}} = \frac{1}{2+K+2(2+K)^{1/2}}.$$

(II-l<sub>1</sub>3)

Since the input impedance of the grounded collector stage has a negative real part at sufficiently high frequencies, the possibility of instability exists when the grounded collector stage is driven from a generator even though the output impedance of the generator can be represented as a passive network. A simple way to investigate the stability of the grounded collector stage when an arbitrary admittance Y is connected across the input terminals is to add admittance Y to the input admittance  $Y_{in}$  which is the reciprocal of (II-37). Zeros of the resulting admittance are zeros of the characteristic equation of the network hence if all the zeros of  $Y + Y_{in}$  are in the left half-plane the amplifier will be stable.

For most switching circuit uses of the grounded collector amplifier, Y consists of a parallel resistor and condenser to ground. Then

$$Y = G + Cs$$

(II- $\psi \downarrow \downarrow$ )

and

$$Y + Y_{in} = \frac{(s + a_1)(s + a_2)}{s + \omega_0}$$

(II-45)

where

$$a_{1}, a_{2} = \frac{c \omega_{0} + G + C_{L} \omega_{0} (1 - a_{0}) + \frac{1}{r_{L}}}{2 (C_{L} + C)} \left\{ 1 + \frac{h(C_{L} + C) G \omega_{0} + \frac{\omega_{0} (1 - a_{0})}{r_{L}}}{[C \omega_{0} + G + C_{L} \omega_{0} (1 - a_{0}) + \frac{1}{r_{L}}]^{2}} \right\}.$$

(II-46)

For this case, stability is assured.

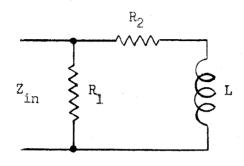

If Y consists of an inductance L to ground,

$$Y = \frac{1}{Ls}$$

(II-47)

and,

$$Y + Y_{in} = \frac{c_{L} Ls^{3} + c_{L} L \left[\frac{1}{r_{L}} c_{L} + \omega_{o}(1 - a_{o})\right] s^{2} + \left[\frac{c_{L} L \omega_{o}(1 - a_{o})}{r_{L} C_{L}} + 1\right] s + \omega_{o}}{Ls (s + \omega_{o})}.$$

(II-48)

This will be unstable if

$$\omega_{o} > \left[\frac{1}{r_{L}} + \omega_{o}(1 - a_{o})\right] \left[\frac{L}{r_{L}} + \omega_{o}(1 - a_{o}) + 1\right]. \tag{II-49}$$

Networks having more complicated values of Y are analyzed in the same way, but they will not be considered here since they occur rarely in practical switching circuits.

Once stability is assured grounded collector transistors can be used to reduce the loading on critical circuits. Under these conditions low frequency input impedance is of primary importance in determining the rise time of the driving circuit. A single time constant approximation to the input impedance is very useful for studying this case. It is obtained by neglecting the sterm in the numerator of (II-37) and neglecting the s<sup>2</sup> term obtained by multiplying out the denominator. The result is

$$\frac{Z_{L}}{1-a} \approx \frac{r_{L}}{1-a_{0}} = \frac{1}{1+a_{0} r_{L} C_{L}(1-a_{0})}$$

$$\frac{Z_{L}}{1-a_{0}} \approx \frac{r_{L}}{1+a_{0} r_{L} C_{L}(1-a_{0})}$$

(II-50)

which is just the impedance of a resistor  $r_L/1-a_o$ ) in parallel with a condenser  $c_1(1-a_o)+1/\omega_o$   $r_L$  .

To a first approximation then, the input impedance of a grounded collector amplifier driving a parallel RC load is the impedance of a parallel RC circuit with

$$R_{\rm in} = \frac{r_{\rm e} r_{\rm L}}{r_{\rm L} + r_{\rm e}(1 - a_{\rm e})}$$

(II-51)

and

$$c_{in} = c_e + c_L(1 - a_e) + \frac{1}{r_L \omega_o}$$

(II-52)

It will be noted that the input capacity contains a term which is dependent on the load resistance and the cut-off frequency of the transistor. It is imperative that transistors having high cut-off frequencies be used in this connection when low resistance loads are driven and high speed operation is required. For example, if  $r_{\tilde{L}}$  is 1,000 ohms and  $\omega_{0}$  is  $10^{7}$ , the input capacity due to this term is 100 mmfd, which may well be the major part of the input capacity.

The output impedance of the grounded collector amplifier is

$$z_{\text{out}} = \frac{r_{\text{e}} r_{\text{b}} + Z_{\text{c}} \left( r_{\text{e}} + r_{\text{b}} (1 - a) \right) + \left[ r_{\text{e}} + Z_{\text{c}} (1 - a) \right] Z_{\text{g}}}{r_{\text{b}} + Z_{\text{c}} + Z_{\text{g}}}$$

$$\approx \frac{1}{\left[ \frac{1}{r_{\text{g}} (C_{\text{g}} + C_{\text{c}})} + s \right] (\omega_{\text{o}} + s)}.$$

(II-53)

This impedance may be represented by one of the two passive equivalent circuits given in fig. II-5.

The voltage gain of the grounded collector amplifier stage is

$$A_{e} = \frac{Z_{c} Z_{L}}{r_{e} r_{b} + Z_{c} (r_{e} + r_{b}(1 - a)) + (r_{b} + Z_{c})Z_{L}} \approx 1.$$

(II.454)

For all the circuits of interest here, we may safely disregard any frequency dependence of the voltage gain. However, the transistor in this connection shares with the cathode follower the property of conducting in one direction only so the output waveform cannot follow the input waveform unless the time constants of the load circuit and the cut-off transistor are such that the output voltage can fall as fast as the input voltage.

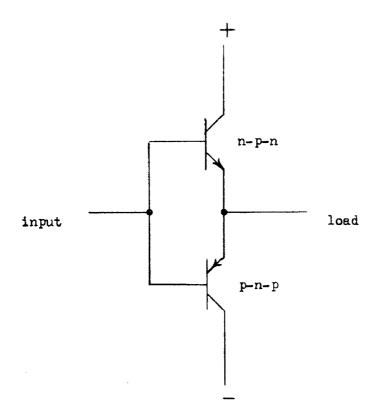

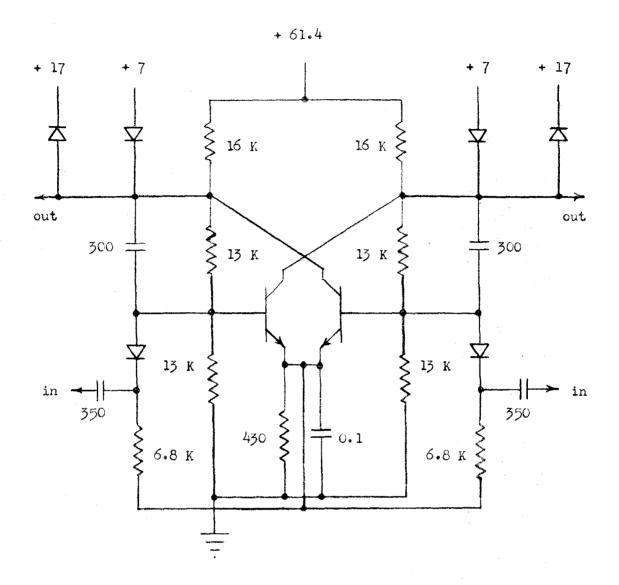

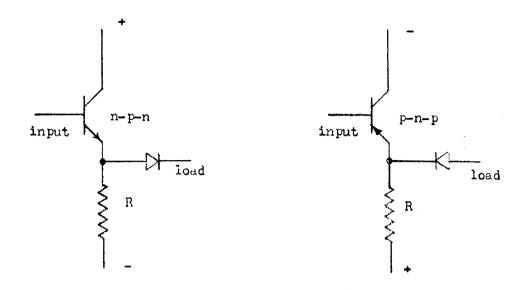

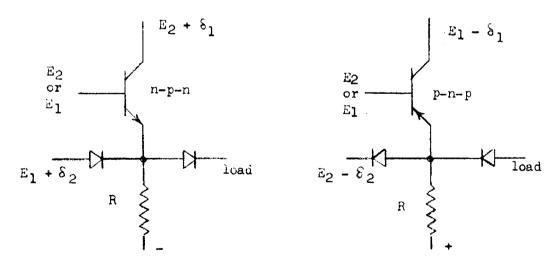

Since there are two types of transistors, npn and pnp, which conduct in opposite directions, it is possible to construct a simple grounded collector amplifier which will amplify positive and negative pulses with equal ease and drive a capacitive load without the necessity of expending power in a small load resistor. The circuit for this amplifier is given in fig. II-6.

The current gain of the grounded collector amplifier is

$$A_{i} = \frac{-Z_{c}}{r_{e} + (1-a)Z_{c}} \approx \frac{-1}{1-a} \approx \frac{s + \omega_{o}}{s + \omega_{o} (1-a_{o})}. \quad (\text{II} -55)$$

Because of the high value of current gain, substantial power gains are available in this connection even though the voltage gain is less than one.

# Large Signal Junction Transistor Amplifiers:

Any attempt to make an exact analysis of the large signal behavior of junction transistors, even one based on the approximate equivalent circuit, leads immediately to prohibitive computational difficulty. This statement is doubly true if the analysis is to be applied to flip-flop circuits because of the added complication of positive feedback.

The difficulty is principally due to the non-linearity of most of the elements of the equivalent circuit, even in the normal operating range of the transistor where the emitter junction is forward biased and the collector junction is back biased. In switching circuits it is sometimes desirable to operate the transistor cut-off (both junctions back biased) or saturated (both junctions forward biased). The parameters of the equivalent circuit change abruptly at the boundaries of the various operating regions.

One approach to the analysis of circuits which operate in more than one region is to assume that the elements of the equivalent circuit are linear in each operating region and that they change abruptly at the boundary of the region. By matching currents and voltages at the boundaries of the operating regions, it becomes possible to calculate the behavior of the circuit (Ref.12).

Another analysis uses an analytic approximation for the non-linearities (which is still non-linear of course) based on the fundamental physics of the transistor (Ref.13,lh). This method is a very satisfying one particularly for calculations in the saturation region. However, practical considerations still require the assumption of linear equivalent circuit elements (calculated from the analytic approximation) in each of the three regions of operation.

The flip-flop circuits to be analyzed here permit several important simplifications which make the assumption of linear equivalent circuit elements largely unnecessary and yet permit the calculation of circuit performance using linear techniques. These simplifications are possible because:

- The transistors are driven through impedances which are large compared to the input impedance of the transistor.

- The load resistance is small compared to the collector resistance.

- 3. Operation in the saturated region is prohibited.

The importance of condition 1 can easily be seen from fig. II-7. Curve A is a plot of collector current as a function of emitter current and exhibits a truly remarkable linearity. Curve B is a plot of collector current as a function of emitter voltage and is extremely non-linear. The difference in the two curves is a result of the non-linearity of the input impedance. If the transistor is operated in such a way that the input current is determined by external impedances (condition 1), curve A shows that the output current can be easily computed by a linear equation

$$I_c = -a I_e + I_{co}$$

(II-56)

which applies over the whole operating region.

In the grounded emitter and grounded collector connections, the base current is the control parameter. Since

$$-I_{e} = I_{e} + I_{b}$$

, (II-57)

equation (II-56) can be written

$$I_{c} = I_{b} \frac{a}{1-a} + I_{co} \frac{1}{1-a}$$

(II-58)

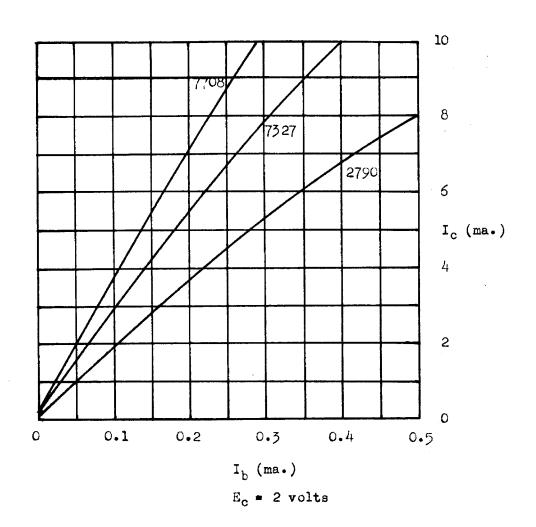

For many transistors plots of  $I_c$  vs.  $I_b$  are also quite linear even though non-linearities in (II-56) are multiplied by the large factor a /(1-a). Fig.II-8 is such a plot for a number of typical diffused junction n-p-n transistors. The impressive linearity of the current plots suggests that the small signal transfer impedances can be used for large signal analysis with good accuracy when condition 1 is met.

Because the load resistance is small compared with the collector resistance, changes in collector resistance which occur with changes in the operating point have a second order effect on the output of the amplifier. Hence the assumption that the collector resistance is constant does not seriously affect the accuracy of the analysis.

Because of condition 3 above, the collector is always back biased and the collector impedance is high. Under these conditions if the input impedance can be considered negligibly small (though non-linear), the approximate formulas developed above for the remaining network functions do not contain the non-linear resistances  $r_{\rm b}$  and  $r_{\rm e}$ . The important transistor parameters have been reduced to  $a_{\rm c}$ ,  $\omega_{\rm o}$ ,  $r_{\rm c}$ , and  $C_{\rm c}$ . The collector resistance is ordinarily negligibly large in the circuits to be considered. Of the remaining parameters  $a_{\rm o}$  and  $\omega_{\rm o}$  are relatively independent of operating point and

therefore can be considered constant with reasonable accuracy.  $C_{\rm c}$  is not independent of the collector voltage but is considered to be constant in this analysis in the interest of simplicity. In practice this results in small error because the amplifier ordinarily drives a capacity which is large compared to  $C_{\rm c}$  and also the value of  $C_{\rm c}$  which is used, is obtained by a measurement technique which gives the best linear approximation to  $C_{\rm c}$  over the actual operating range.

Operation in the saturated region has been prohibited because saturated flip-flops change state more slowly and require greater trigger impulses than unsaturated flip-flops. This is a result of an effect known as minority carrier storage. If the transistor amplifier is driven by either a current or voltage pulse, the output increases as the input is increased until the voltage across the collector junction becomes zero at the peak of the pulse. If the input is further increased no additional minority carriers can be removed from the base region by the collector so a concentration of these carriers builds up in the base region. When injection ceases at the emitter (at the end of the pulse) the collector voltage remains at the saturated value until the excess carriers have diffused out of the base region or recombined in it. It is easy to obtain delays of the order of 100 microseconds by this method if sufficient drive is available. Since any delay is detrimental to flip-flop operation, minority carrier storage (saturation) should be avoided for optimum design of flip-flop circuits.

In the cut-off region, both junctions are back biased and may be regarded as high resistances shunted by condensers. In the circuits to be described, the resistances will be negligibly large, but the capacities may be important in some cases. The emitter capacity can be measured in the same way as the collector capacity.

It is of interest in determining the static stability of a flipflop to be able to compute the currents which flow when the transistor

is cut-off. When the emitter junction is back biased, a small current

flows in the reverse direction. Equation (II-56) actually still applies in this case (Ref.13) which indicates that the collector current

is slightly less than I<sub>CO</sub> and the emitter current has some small

value in the reverse direction. The base current is the difference

between the emitter current and the collector current and hence has a

magnitude which is somewhat greater than the collector current. In

the circuits to be discussed, the back voltage across the emitter is

much less than the back voltage across the collector, hence the emitter

current is very small relative to the collector current. A satisfactory approximation is to set I<sub>e</sub> = 0 in (II-56) as the condition

for cut-off. A current I<sub>CO</sub> then flows in both the collector and

base of the cut-off transistor.

The principal effect of increasing the temperature of operation of a transistor is to increase  $I_{\rm co}$  since  $I_{\rm co}$  varies exponentially with temperature in such a way as to double every 8 to 10 degrees C. At room temperature,  $I_{\rm co}$  will ordinarily be a few microamperes and will be entirely negligible. However, at elevated temperatures, the stability of the flip-flop may be impaired because of the high value of cut-off current. For this reason, the flip-flop design equations necessarily include  $I_{\rm co}$  so that a particular circuit design can allow for a specified temperature rise.

### III PULSE MEASUREMENT TECHNIQUES FOR JUNCTION TRANSISTOR PARAMETERS

The previous discussion has pointed out that  $C_c$ ,  $\omega_0$ , and  $a_0$  are the most important parameters governing the behavior of transistors in switching circuits. Since these parameters are only quasi-linear, more accurate calculations can be made using these parameters if they can be measured in such a way that an effective value over the contemplated operating range is obtained.

The pulse measurement techniques proposed here, based on the approximate network functions previously derived, permit such large signal measurements of the transistor parameters.

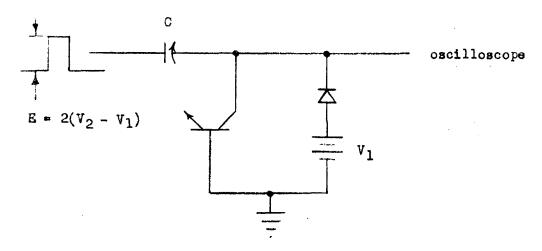

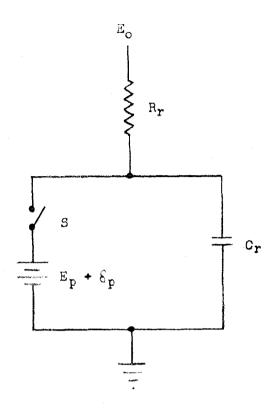

## The Measurement of $C_{ m c}$ :

Equation (II-8) shows that the output impedance of a grounded base amplifier with the emitter open is  $\mathbf{Z_c}$  which consists of a large resistor  $\mathbf{r_c}$  in parallel with  $\mathbf{C_c}$ . It is desired to measure this condenser in terms of an ideal condenser which would require the same charge to change from voltage  $\mathbf{V_1}$  to  $\mathbf{V_2}$ . A circuit to accomplish this is given in fig.III-la. The collector voltage on the transistor is constrained to be  $\mathbf{V_1}$  or some more positive potential by the battery and the high quality germanium point contact diode. If a rectangular positive pulse of good rise time (perhaps 0.1 microseconds) and short duration (perhaps 2 microweconds) having an amplitude of  $2(\mathbf{V_2}-\mathbf{V_1})$  is applied to the variable condenser, the collector at the transistor will rise with the pulse to a voltage  $\mathbf{V_1} + 2(\mathbf{V_2}-\mathbf{V_1})$   $\mathbf{C}/(\mathbf{C}+\mathbf{C_x})$  where  $\mathbf{C_x}$  is the sum of the stray

capacity,  $C_s$ , and  $C_c$ . If C is adjusted until the peak of the collector pulse is at  $V_2$ , the collector has the prescribed voltage swing and  $C = C_x$ . Narrow pulses are used so that there is no perceptible discharge of the condensers during the pulse. The value of  $C_s$  is measured by removing the transistor and  $C_c = C_x - C_s$ .

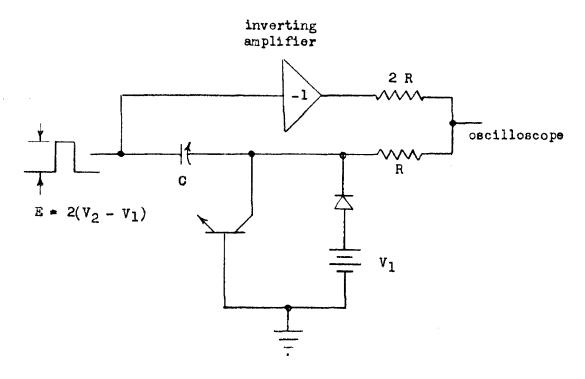

A more convenient method using an inverting amplifier is given in fig.III-lb. A null at the oscilloscope indicates that C is adjusted so that the collector pulse has half of the amplitude of the pulse from the pulse generator. For a further refinement C is calibrated in incremental capacity from its minimum capacity and shunted by a trimmer which can be adjusted to compensate for the stray capacity. The collector capacity can then be read directly from the calibrated condenser.

The collector capacity measured by this technique is just the ratio of the voltage change  $V_2 - V_1$  to the charge necessary to cause the collector voltage to change from  $V_1$  to  $V_2$ . Therefore, if this capacity were charged from a constant current source, the time required to charge from  $V_1$  to  $V_2$  would be exactly the same as the time required to charge a linear condenser of capacity  $C_c$  under the same conditions. The actual waveforms would be different of course, but since charging time is usually of more importance than waveshape and since conditions approximating constant current charging occur frequently in switching circuits, it appears that the collector capacity measured by this method is the most reasonable linear approximation to the collector capacity over the particular voltage range.

It is interesting to deduce the relationship between the usual small signal collector capacity  $^{\rm C}_{

m cs}$  and  $^{\rm C}_{

m c}$  measured by the pulse technique. The small signal collector capacity is defined as

$$c_{es} = \frac{dQ}{dV} \tag{III-1}$$

and according to theory (Ref.8) is given by

$$C_{cs} = KV^{-k}$$

(III-2)

where K is a constant, V is the collector voltage, and k has the value 1/2 for step junctions (which diffused junctions approximate) and 1/3 for graded junctions (which grown junctions approximate).

Combining (III-1) and (III-2)

$$KV^{-k} dV = dQ (III-3)$$

which can be integrated to give the charge required to change the collector voltage from 0 to  $\mathbf{V}_2$  ,

$$Q = \frac{K}{1-k} V_2^{(1-k)}$$

(III-l<sub>1</sub>)

from which we have

$$C_{e} = \frac{Q}{V_{2}} = \frac{C_{es}}{1-k} \tag{III-5}$$

The value of  $C_{\rm c}$  over a range from 0 to  $V_{\rm c}$  is thus the product of a constant which depends on the junction and  $C_{\rm cs}$ , the small signal collector capacity at collector potential  $V_{\rm c}$ .

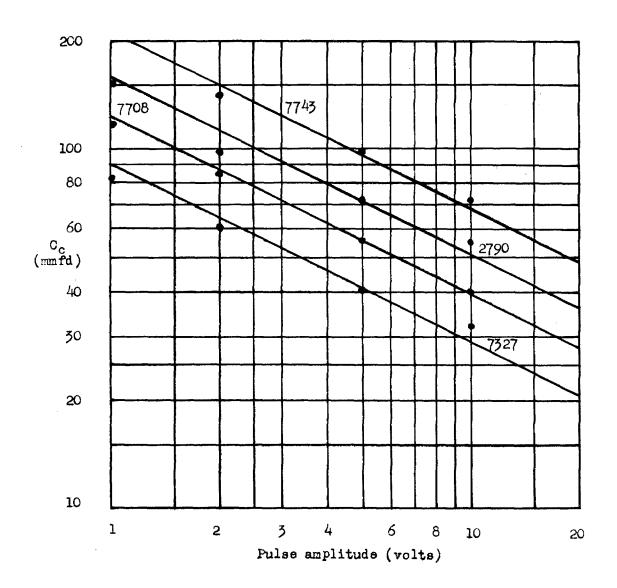

Substituting into (III-2) from (III-5) and taking the logarithm yields

$$\log c_{\rm e} = -k \log v_{\rm 2} + \log \frac{K}{1-k}$$

(III-6)

Thus a plot of  $C_c$  vs.  $V_2$  on log-log paper should be a straight line with slope -k. Fig.III-2 is such a plot for a number of diffused junction transistors. It is seen that k does indeed have a value very close to the theoretically correct value of 1/2.

# The Measurement of $\omega_o$ :

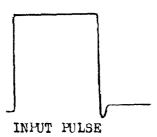

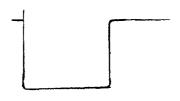

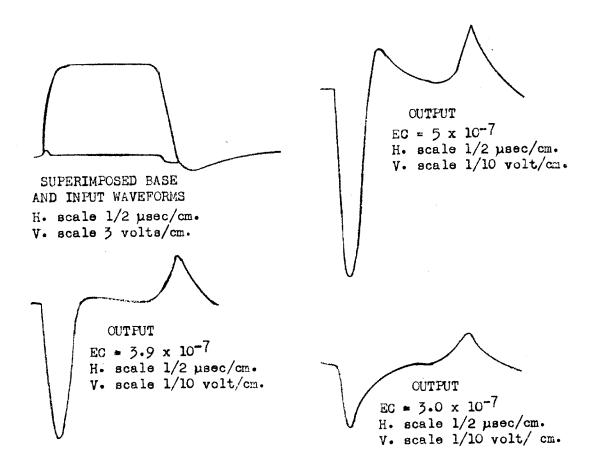

The basic circuit for the measurement of  $\omega_0$  is given in fig.III-3. The load resistor  $r_L$  is chosen so small that the approximation of equation (II-13) is valid. Under these conditions expression (II-14) shows that the amplifier is first order frequency independent if RC =  $1/\omega_0$ . Frequency independence can easily be detected if the circuit is driven by a voltage pulse having a very accurate rectangular shape and the output is observed by a broadband oscilloscope. The condition for frequency independence is that the output waveshape be as nearly as possible a replica of the input waveshape. Typical waveforms for a particular transistor in the circuit of fig.III-3 are shown in fig.III-4 as they appear for different values of C. From this figure it is apparent that it is relatively easy to obtain the proper value of C.

# The Measurement of $a_0/(1-a_0)$ and $\omega_0(1-a_0)$ :

It might seem to be redundant to offer methods of measuring both  $\omega_{\rm o}$  and  $\omega_{\rm o}(1-a_{\rm o})$ , but from a practical point of view, it is desirable to be able to measure both of these quantities. The measurement of  $\omega_{\rm o}$  is the measurement of the frequency at which the current gain of the grounded base amplifier is down by 3 db. The measurement of

$\omega_{0}(1-a_{0})$  is a measurement of the frequency at which the current gain of the grounded emitter connection is down 3 db. These two frequencies will have the indicated relationship only if a has the postulated frequency dependence which specifies both the amplitude and phase shift of a as a function of frequency. It is preferable to measure  $\omega_{0}(1-a_{0})$  when the transistor is to be used in the grounded emitter connection, and  $\omega_{0}$  when it is to be used in the grounded base connection.

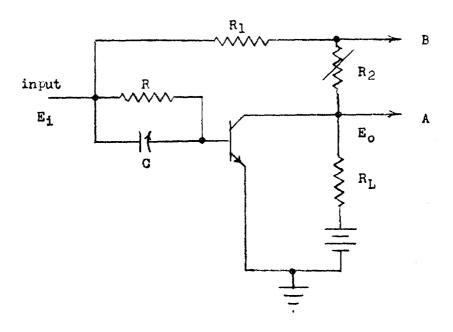

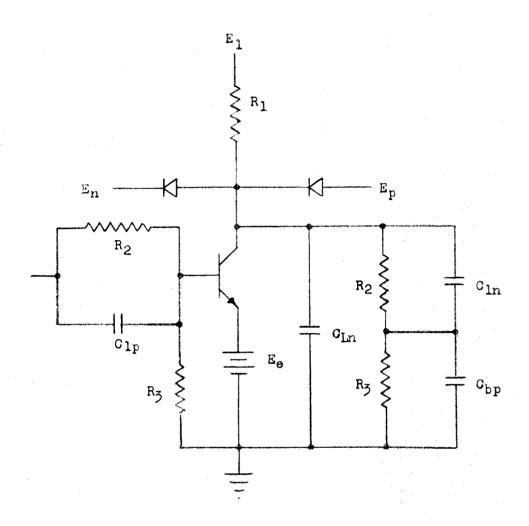

The basic circuit for measuring  $a_0/(1-a_0)$  and  $\omega_0(1-a_0)$  is given in fig.III-5. In this circuit  $r_L$  is chosen to be so small that the approximation of equation (II-29) is valid and  $R_2 \gg r_L$ . Equation (II-30) shows that the amplifier is first order frequency independent if  $1/RC = \omega_0(1-a_0)$ . Frequency independence is detected as before by driving the amplifier with a rectangular pulse and adjusting the condenser for best output waveshape. Typical waveforms obtained during this measurement are given in fig.III-6. It can be seen from this figure that the proper adjustments are easily made.

In order to operate the circuit, point A is observed with a wideband oscilloscope while C is adjusted for best output waveshape. The oscilloscope is then transferred to point B and  $R_2$  is adjusted for null. Under these conditions,

$$\omega_{o}(1-a_{o}) = \frac{1}{RC}$$

(III-7)

$$\frac{E_0}{R_2} = \frac{E_1}{R_1} \tag{III-8}$$

using (II-30)

$$\frac{E_0}{E_1} = \frac{R_2}{R_1} = \frac{a_0 r_L}{R(1-a_0)}$$

(III-9)

80

$$\frac{a_0}{1-a_0} = \frac{R_2 R}{R_1 R_L}. \tag{III-10}$$

$R_2$  may be calibrated directly in terms of  $a_0/(1-a_0)$  and C may be calibrated directly in terms of  $\omega_0(1-a_0)$  for greatest operating convenience.

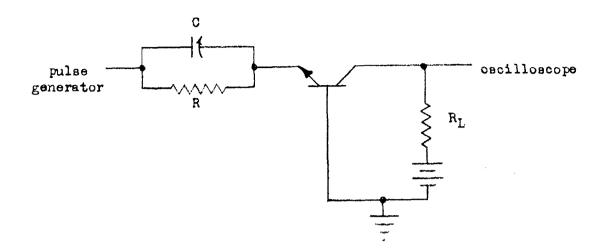

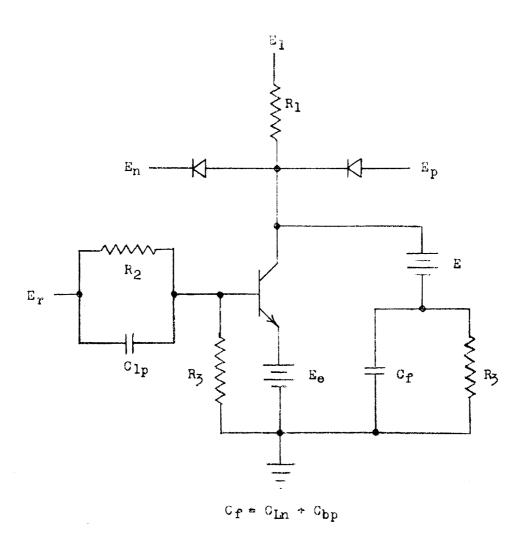

# Direct Measurement of the Grounded Emitter Current Gain Bandwidth Product:

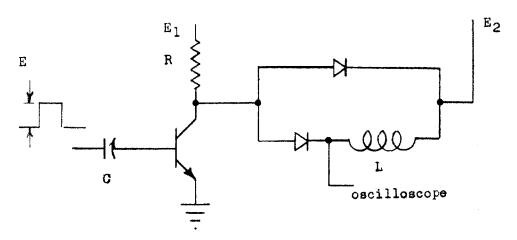

In the transient analysis of transistor circuits, the product  $a_{c}$   $\omega_{o}$  occurs frequently. If the transistor is used in the grounded emitter connection, it is to be understood that this quantity is actually the grounded emitter gain bandwidth product,  $\left[a_{o}/(1-a_{o})\right](1-a_{o})\omega_{o}$  which, as was shown above, is not necessarily equal to the gain bandwidth product in the grounded base connection. While this product may be obtained from the above measurement, it is more convenient to measure it directly. One circuit which permits measuring this product over a large current swing at a constant collector voltage is given in fig.III-7.

In the absence of an input pulse, the transistor is drawing a small current  $I_{co}/(1-a_o)$ .  $E_1$  and R are adjusted to give the desired current I and the collector voltage  $E_c$  is adjusted to the desired value by adjusting the clamp voltage  $E_2$ . If a rectangular

pulse from a low impedance pulse generator is applied to the relatively small input condenser C the condenser will charge to the peak amplitude of the pulse in a very short time (0.2 microseconds is a typical value) due to the low input impedance of the transistor. It is therefore possible to make the simplifying assumption that the input signal can be approximated by a current impulse of magnitude EC. Since the transistor has a very low impedance load, the forward resistance of a diode, the output current resulting from the input current impulse is given by the product of the current impulse and the inverse transform of the short circuit current gain of the grounded emitter stage given by (II-35). The collector current resulting from the input current impulse EC is then

$$I_c = \omega_o \omega_c \text{ EC e}^{-\omega_o(1-\omega_o)t}$$

(III-11)

No appreciable voltage will be developed at the collector until the peak value of  $I_{\rm c}$  exceeds the initial clamp current I . If EC is adjusted until the peak value of  $I_{\rm c}$  is just equal to I,

$$a_{O} \omega_{O} = \frac{I}{EC}$$

(III-12)

which provides the desired measurement of the gain bandwidth product.

The principal difficulty in making this measurement is to detect precisely when the peak value of  $I_{\rm c}$  is equal to I since the clamp diodes do not have zero forward resistance. A circuit arrangement to aid in detecting this critical value of peak current is included in fig.III-7. The clamp circuit is actually two diodes in parallel with an inductance in series with one of them. The inductance is chosen

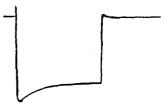

to have a natural period when shunted by the oscilloscope which is short compared with  $1/\omega_0(1-a_0)$  (0.3 microseconds is an appropriate value). If the current impulse is not large enough to disconnect the diodes, the inductance cannot ring. However, if the impulse disconnects the diodes, the inductance will ring. The peak value of  $I_c$  is taken to be equal to I at the first visible sign of ringing. This is a much more sensitive method of detection than observing the collector voltage with the oscilloscope. Typical waveforms obtained during this measurement are given in fig.III-8.

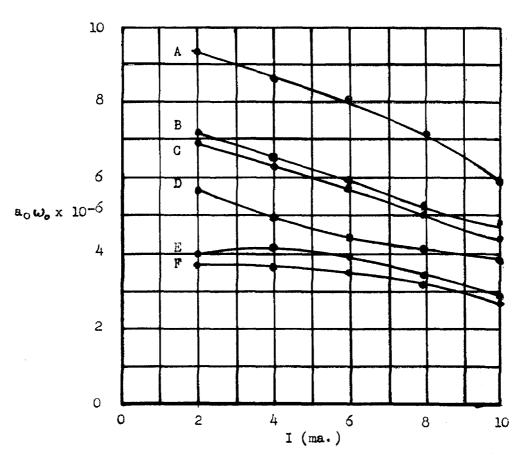

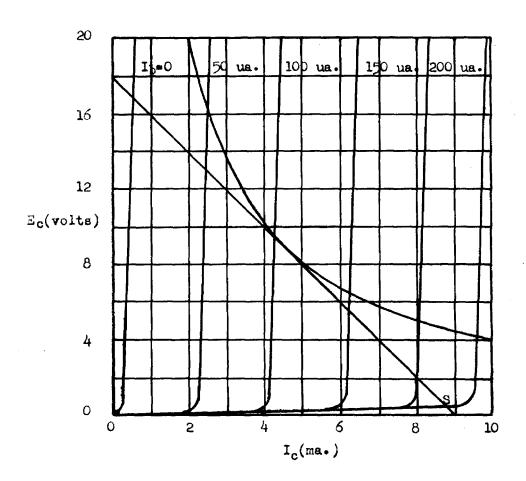

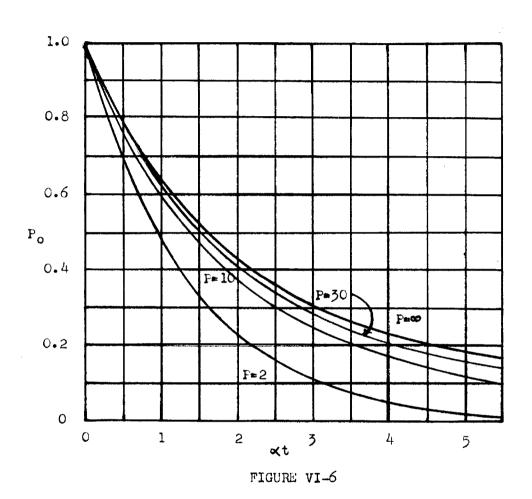

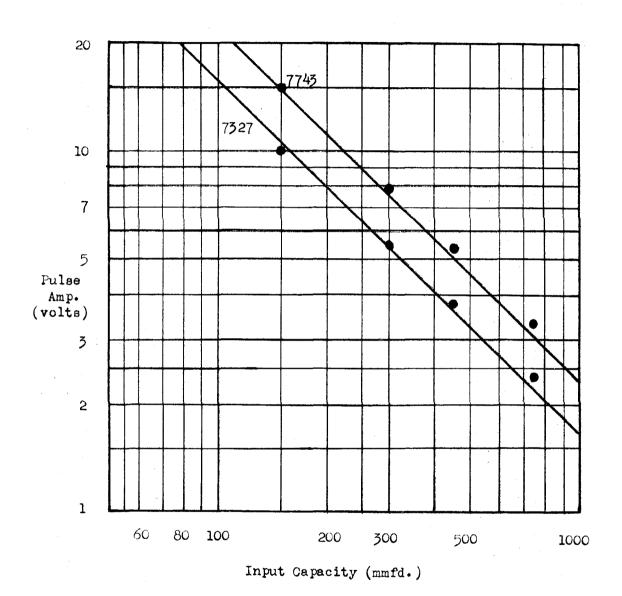

The values of grounded emitter gain bandwidth product were measured for a number of transistors as a function of collector voltage and peak current. The results of these measurements given in fig.III-9, show that in general  $a_0 \cdot \omega_0$  goes down as the peak current is increased and goes up as the collector voltage is increased.

In the subsequent transient analysis, it is desired to use the best average value of  $a_0$   $\omega_0$  as a constant in predicting the transient behavior of the transistor in flip-flop circuits. Although  $a_0$   $\omega_0$  is not subject to extreme variation over the operating region, fig.III-7 shows that the choice of the proper value is a matter of some conjecture unless the transistor is operated at constant collector voltage with a known current swing. When these conditions are not met, the value of  $a_0$   $\omega_0$  which is used in computation is the value measured when the collector voltage and peak current are approximately equal to the average values of these quantities in the interval over which it is desired to measure  $a_0$   $\omega_0$ .

### IV FLIP-FLOP CIRCUITS

### Definitions:

One of the most important switching circuits is the bi-stable circuit commonly known as a flip-flop. In recent years the meaning of this term has been extended to include a wide variety of devices which have two distinguishable stable states which may or may not be static. In this section a somewhat restricted class of flip-flop circuits (which nevertheless includes the most common circuits) will be examined from a general point of view to determine the requirements on the active elements used in the circuit.

The type of flip-flop considered here is a static, bi-stable device characterized by output signals which are one of two possible voltage states. It is possible to cause the circuit to change rapidly from one stable state to the other by applying suitable input triggering signals. Circuits based on negative resistance properties of devices such as point contact transistors are not considered because junction transistors (and vacuum tubes as they are normally used) do not exhibit negative resistance phenomena.

### Restrictions on the Amplifier:

The flip-flops to be discussed here can be considered as being made from a stable three-terminal amplifier, having input terminal 1 and output terminal 2 with terminal 3 grounded, by connecting terminals 1 and 2 together. If terminal 1 is connected to terminal

$$I_1 = I_2 \tag{IV-1}$$

and

$$E_1 = E_2. \tag{IV-2}$$

To see if flip-flop operation is possible, it is necessary to examine the singular points of the system. The singular points are those sets of values of the variables  $I_1$ ,  $I_2$ ,  $E_1$ , and  $E_2$  for which equations (IV-1) and (IV-2) are satisfied and for which the first and all higher derivatives of the variables with respect to time are zero. Clearly all singular points are points of equilibrium. A singular point is called a stable singular point if a region in the neighborhood of the singular point can be found such that a small initial displacement from the singular point results in small displacements of the variables with these displacements going to zero as time goes to infinity. It has been shown quite generally that stability of singular points of non-linear systems can be determined from an examination of the stability of the small signal linear system approximating the actual system in the neighborhood of the singular point(Ref.15).

In order to meet the design requirement of two stable states, the circuit formed when terminals 1 and 2 are connected together must have two stable singular points. It will be shown that it will also have an unstable singular point; and conversely, that the existence of the proper type of unstable singular point requires the existence of two other singular points which may be stable.

If both of conditions (IV-1) and (IV-2) are imposed simultaneously

an amplifier which can be used to make a flip-flop will exhibit unstable behavior over some part of the operating region. However, either of the conditions can be enforced independently and stable operation will obtain. For example, current generators could be used to make  $I_1 = -I_2 = I$ . For every value of I a definite value of  $I_1$  and  $I_2$  would be determined.

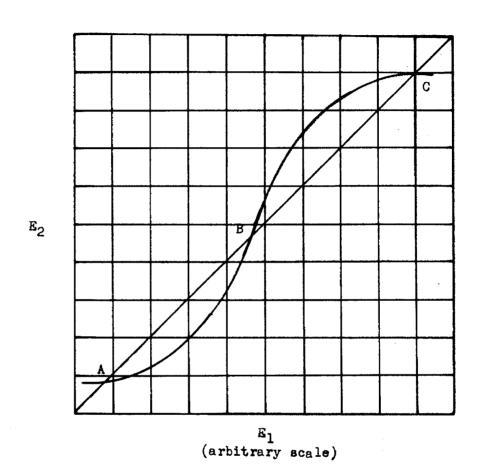

If a plot of  $E_1$  vs.  $E_2$  is made as I is varied, a curve is obtained which might resemble fig. IV-1. Points A, B, and C where the curve intersects the line  $E_1=E_2$  are singular points since the curve was taken point by point so that all the time derivatives were zero. For two stable states to exist, points A and C must be stable singular points. Point B will be an unstable singular point since if points 1 and 2 were connected together a small increase in  $E_1$  would tend to produce a larger increase in  $E_2$  which would tend to produce a larger increase in  $E_1$  and so on.

Unstable singular points such as the one at B, which can be shown to be unstable from the zero frequency behavior of the system in the neighborhood of the singular point, will be called d.c. unstable singular points. These points are easily recognized from a curve such as fig. IV-1 since the slope of the  $E_1$  vs.  $E_2$  curve is greater than 1 at a d.c. unstable singular point.

Since saturation is a characteristic of all physical amplifiers, the existence of a d.c. unstable singular point requires the existence of two additional singular points which are not d.c. unstable. The stability of these points must be determined by small signal analysis of the system in the neighborhood of the points.

In terms of the above definitions, a flip-flop can be formed by shorting together the input and output of a stable amplifier if the amplifier is such that a d.c. unstable singular point is formed and the additional singular points are stable.

The flip-flop conditions can be put in more useful form by writing the small signal linear equations for the amplifier in the neighbor-hood of point B. These are

$$i_1 = G_{11} e_1 + G_{12} e_2$$

(IV-3)

$i_2 = G_{21} e_1 + G_{22} e_2$

where the G's are the low frequency small signal admittance parameters of the amplifier and the lower case e's and i's are the differences between the actual currents and voltages and the values they would have at point B.

Since the amplifier is unconditionally stable,

$$G_{11} G_{22} - G_{12} G_{21} > 0.$$

(IV-4)

When 1 is connected to 2, the admittance equation for the resulting network is

$$i = (G_{11} + G_{22} + G_{12} + G_{21}) e$$

(IV-5)

and since this is to be unstable,

$$G_{11} + G_{22} + G_{12} + G_{21} < 0.$$

(IV-6)

This inequality is sufficient to assure that singular point B will have the proper type of instability.

It is shown in the appendix that a consequence of inequalities (IV-h) and (IV-6) is that the short circuit current gain  $A_{sc}$  is

$$\left|A_{sc}\right| = \frac{\left|G_{21}\right|}{G_{11}} > 1 \tag{IV-7}$$

and the open circuit voltage gain A is

$$|A_{oc}| = \frac{|G_{21}|}{|G_{22}|} > 1$$

. (IV-8)

Therefore, a stable amplifier which is to be used to make a flip-flcp by shorting its input to its output must have at the central singular point both d.c. open circuit voltage gain greater than one and d.c. short circuit current gain less than minus one.

The discussion thus far has been concerned primarily with those conditions which produce d.c. instability at the central singular point. It is equally important for flip-flop operation that the circuit be stable at the extreme singular points. At either extreme singular point, small signal linear equations can be written

$$i_1 = Y_{11} e_1 + Y_{12} e_2$$

$$i_2 = Y_{21} e_1 + Y_{22} e_2.$$

(IV-9)

The condition for stability when the input is shorted to the output is that

$$Y = Y_{11} + Y_{12} + Y_{21} + Y_{22}$$

(IV-10)

have no zeros in the right half-plane.

It is impossible to discuss this function unless the nature of the non-linearity is specified. In one very important special case, which is the only one of concern here, the amplifier has zero small signal gain for all frequencies at the extreme singular points. For this case, the extreme singular points are unconditionally stable.

### Possible Flip-flop Circuit Configurations:

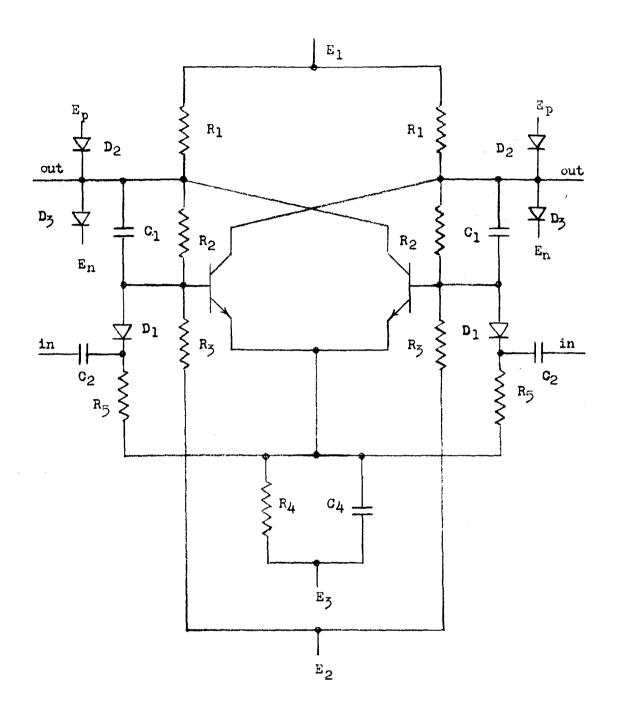

The above theory can be used to discard a large class of potential flip-flop amplifiers. In particular it has been shown that it is impossible to construct a flip-flop consisting solely of grounded base stages since it is impossible to get d.c. short circuit current gain greater than one in absolute value in the grounded base connection. Similarly, it is impossible to construct a flip-flop consisting solely of junction transistors in the grounded collector connection since it is impossible to get d.c. open circuit voltage gain greater than one in the grounded collector connection. It is possible to construct a flip-flop using a grounded base stage for voltage gain and a grounded collector connection for current gain. The grounded emitter stage provides both current and voltage gain greater than one in absolute value, but it also causes a phase reversal which makes it necessary to use two transistors in this connection to construct a flip-flop. Thus, the minimum number of junction transistors required to construct a flip-flop circuit is two, and these must be arranged either as a grounded base stage with a grounded collector stage, or as two grounded emitter stages.

Some insight into the relative usefulness of the two possible junction transistor flip-flops using no more than two transistors can be obtained by considering the analogous vacuum tube flip-flop circuits, for the preceding theory also shows that there are just

two possible vacuum tube flip-flop circuits using only two tubes.

The first of these circuits, using two grounded cathode tubes, is the familiar grid to plate coupled circuit which is analogous to the transistor flip-flop using two grounded emitter stages. This will be called the symmetric flip-flop because of its symmetrical complementary output signals and because it can be triggered in a symmetrical way by identical pulses applied to different but similar parts of the circuit.

The second vacuum tube circuit, the cathode coupled flip-flop, uses one grounded grid and one grounded plate stage. This is analogous to the transistor flip-flop having one grounded base and one grounded collector stage. This circuit will be called the unsymmetrical flip-flop. It has the disadvantages of having only one output (this can be overcome by a circuit modification) and of requiring unsymmetrical triggering. These disadvantages have made the cathode coupled flip-flop relatively unused.

It appears that the symmetrical transistor flip-flop will also be much more generally useful than the unsymmetrical flip-flop.

Therefore, the detailed design equations are derived for that type of flip-flop.

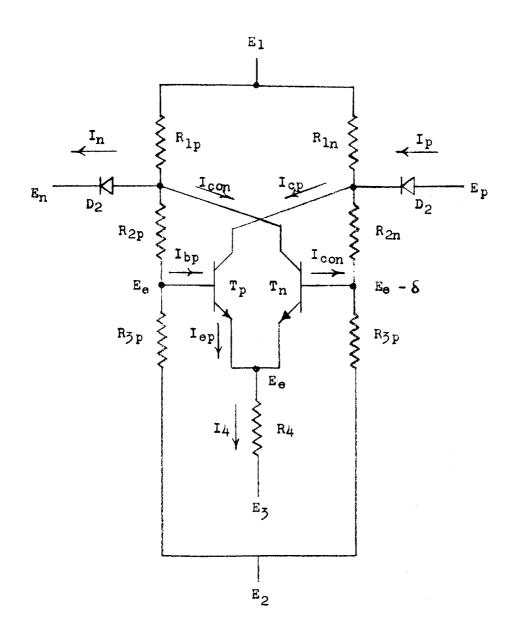

# V STATIC CONSIDERATIONS IN THE DESIGN OF SYMMETRIC JUNCTION TRANSISTOR FLIP-FLOPS

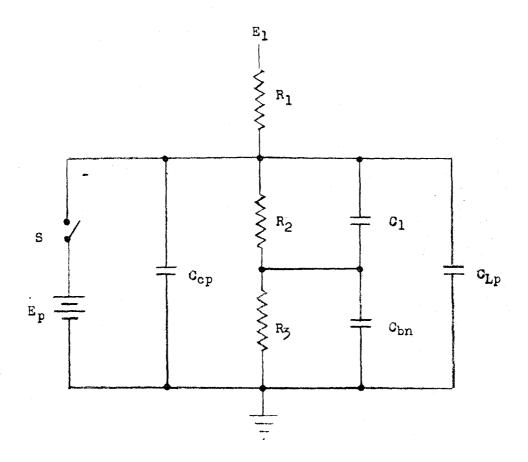

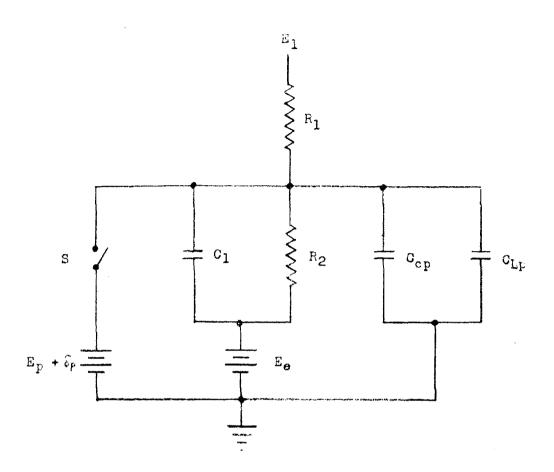

### Static Design Objectives: