# Software Register Synchronization for Super-Scalar Processors with Partitioned Register Files

Thesis by

Daniel Maskit

In Partial Fulfillment of the Requirements

for the Degree of

Doctor of Philosophy

California Institute of Technology Pasadena, California

1997

(Submitted December 12, 1996)

© 1997

Daniel Maskit

All Rights Reserved

### Acknowledgements

Many thanks to my advisor, Steve Taylor. Steve has taught me a great deal about parallel programming and about the practice of academia. He has encouraged me to do the work which I am interested in, allowed me to do things my way, and given me the confidence to believe in my intuition. In addition, Steve is one of the most generous people I have ever worked with. He treats his graduate students as his colleagues, and has done everything he can to make our graduate careers not just as productive, but as enjoyable, as possible.

Special thanks are also due to Bill Dally. Bill has gone out of his way to take an interest in my career. He has advised me both academically and professionally. He has offered his time and the time of others in his lab to further our common goals. I look forward to future productive work with Bill.

I would also like to thank the other members of my committee. Al Barr and Mani Chandy have participated in one way or another with almost all phases of my academic progress at Caltech. They have consistently been pleasant to work with, and obviously been interested in my progress. They have both encouraged me to broaden my horizons, and have introduced me to new and interesting ways of thinking about the world of computer science.

This work would not have been possible without the assistance and great patience of the members of the MIT Concurrent VLSI Architecture (CVA) Group. In particular Steve Keckler has taught me a great deal about architecture, VLSI, and technical writing (although this thesis reflects how much I had to learn far more than it reflects his positive influence). Others deserving of mention include Yevgeny Gurevich, Andrew Shultz, Fletcher Sandbeck, Andrew Chang, Nick Carter, and Michael Noakes.

A great debt is owed to Rich Lethin who set aside his own research to spend nearly

a year training me to the point where I could assume primary responsibility for the Multiflow compiler work. Rich's teaching skills and generosity were invaluable to my work.

In addition, all the members of the CVA group have conspired to be wonderful hosts to me during the many trips I made to Boston in the course of this work. They made me feel welcome, and treated me not so much as a visiting colleague, but as an honored guest.

While at Caltech I have continued the study of history inspired by my don from Sarah Lawrence College, Francis B. Randall. I have completed a history minor for my Ph.D. working primarily with Doug Flamming who has made this study both educational and fun.

My time in graduate school has been vastly improved both by the friends I left behind when I came to California: Jesse Lentchner and Rebecca Terner, Dirk Dawson and Laura Emerick, Bruce Musser, Ethan Galant and Leigh Hendrickson; as well as new friends I have made here at Caltech: Maneesh Sahani, Jennifer Linden, Len and Shelly Mueller, Eve Schooler and Bob Felderman.

I would also like to thank the other members of the Scalable Concurrent Programming Laboratory, both past and present: Mike Palmer, Marc Rieffel, Jerrell Watts, Bryan Chow, Yair Zadik, Dave Bourgeois, and Andy Fyfe. The lab has consistently been a good working environment, and a great group of people to socialize with.

The finest treasure that I have encountered during my time at Caltech, however, is my fiancee Kelly Smith. I look forward to many happy years with her.

I would be remiss if I did not mention my family. My father Bernie and his wife Wilma have been encouraging and supportive, and have maintained a warm household which allows me to continue thinking of New York as home.

My paternal grandmother Celia has always stood by and encouraged and made it very clear how proud she is of not only my accomplishments, but those of my brothers as well. It is a pleasure to continue to make her proud.

My mother Paula has been supportive of some of the very difficult decisions I have

had to make during my graduate career, and in the process has made her love for me obvious.

My brothers Sid and Jonathan have helped keep my feet on the right path, and provided many enjoyable days of exploring exotic places from the swamps of Louisiana to the bistros of Paris. I am extremely lucky to have siblings who are also wonderful friends.

I would finally like to acknowledge the critical support I received from my aunt, Mae Lord. Mae's untimely death has left me deeply saddened. I have been deprived of one of the finest confidants and advisors one could hope for.

The funding for the work described in this thesis has come from a variety of sources. I spent several years being funded by an NSF Graduate Fellowship, with the research project itself funded by the Advanced Research Projects Agency, ARPA Order number 8176, and monitored by the Office of Naval Research under contract number N00014-91-J-1986. The rest of the work was conducted with funding from the Advanced Research Projects Agency under contract number DABT63-95-C-0116. Some of the hardware resources used to run simulations reported on in this work were provided by the U.S. Air Force under Air Force Office of Scientific Research Grant F49620-95-1-0081. In addition, I was designated a finalist by the Hertz Foundation in 1994.

#### Abstract

Increases in high-end microprocessor performance are becoming increasingly reliant on simultaneous issuing of instructions to multiple functional units on a single chip. As the number of functional units increases, the chip area, wire lengths, and delays required for a monolithic register file become unreasonable. Future microprocessors will have partitioned register files. The correctness of contemporary super-scalar processors relies on synchronized accesses to registers. This issue will be critical in systems with partitioned register files. Current techniques for managing register access ordering, such as register scoreboarding and register renaming, are inadequate for architectures with partitioned register files. This thesis demonstrates the difficulties of implementing these techniques with a partitioned register file, and introduces a novel compiler algorithm which addresses this issue.

Whenever a processor using register scoreboarding or register renaming issues an instruction, either the scoreboard or the register name table must be accessed to check the instruction's sources and destination. If the register file is partitioned, checking the scoreboard or name table for a remote register is difficult. One functional unit cannot determine at runtime when it is safe to write to a register in another functional unit's register file. While these techniques can be supported through use of a global or partitioned scoreboard, such an implementation would be complex, and have latency problems similar to those of a monolithic register file.

This work discusses the organization of multiple functional units into loosely-coupled groups of functional units that can communicate via direct register writes, but with purely local hardware interlocks to force synchronization. A novel compiler algorithm, Software Register Synchronization (SRS), is introduced. A comparison between SRS and existing hardware mechanisms is conducted using the Multiflow compiler modified to generate code for the MIT M-Machine. Experiments to evaluate

the SRS algorithm are run on the M-Machine simulator being used for architectural verification. In order to support partitioned register file architectures, an alternative to traditional hardware methods for managing register synchronization needs to be developed. This thesis presents a novel compiler algorithm to address this need. The SRS algorithm is described, demonstrated to be correct, and evaluated. Details of the implementation of the SRS algorithm within the Multiflow compiler for the MIT M-Machine are provided.

## Contents

| A            | Acknowledgements                                        |                                                        |    |

|--------------|---------------------------------------------------------|--------------------------------------------------------|----|

| $\mathbf{A}$ | bstra                                                   | act                                                    | vi |

| 1            | Introduction                                            |                                                        |    |

|              | 1.1                                                     | Trends in Computer Architecture                        | 3  |

|              | 1.2                                                     | Register Synchronization                               | 6  |

|              | 1.3                                                     | Hardware Methods for Managing Register Synchronization | 8  |

|              | 1.4                                                     | A New Way of Organizing a Processor                    | 12 |

|              | 1.5                                                     | Related Work                                           | 14 |

|              |                                                         | 1.5.1 Instruction Scheduling for ILP                   | 15 |

|              | 1.6                                                     | The Trace Scheduling Algorithm                         | 17 |

|              |                                                         | 1.6.1 The Phase Ordering Problem                       | 21 |

|              |                                                         | 1.6.2 Instruction Reordering                           | 23 |

|              |                                                         | 1.6.3 Management of Splits and Joins                   | 25 |

|              | 1.7                                                     | Overview of the Dissertation                           | 28 |

|              | 1.8                                                     | .8 Contributions of this Dissertation                  |    |

|              | 1.9                                                     | Organization of the Dissertation                       | 30 |

| 2            | Register Synchronization for a Monolithic Register File |                                                        |    |

|              | 2.1                                                     | Example 1: Delayed Loads                               | 32 |

|              | 2.2                                                     | Example 2: Multiple Loads                              | 33 |

|              | 2.3                                                     | Development of Register Synchronization Definition     | 35 |

|              | 2.4                                                     | Overview of Solution                                   | 37 |

|   |     | 2.4.1  | Entering a Basic Block                          | 37 |

|---|-----|--------|-------------------------------------------------|----|

|   |     | 2.4.2  | Processing a Basic Block                        | 38 |

|   |     | 2.4.3  | Leaving a Basic Block                           | 38 |

|   | 2.5 | Algori | thm                                             | 40 |

|   | 2.6 | Correc | tness of the Algorithm                          | 43 |

|   |     | 2.6.1  | Basic Definitions                               | 43 |

|   |     | 2.6.2  | Definitions for Transitional Information        | 45 |

|   |     | 2.6.3  | Invariants, Preconditions and Postcondition     | 47 |

|   |     | 2.6.4  | Demonstration of Correctness                    | 48 |

|   |     | 2.6.5  | Managing Transfer of Control                    | 55 |

| 3 | Alg | orithm | Modifications for Trace-Scheduling              | 57 |

|   | 3.1 | Algori | thm Modifications for Trace Scheduling          | 57 |

|   |     | 3.1.1  | Processing a Trace                              | 58 |

|   |     | 3.1.2  | Trace Algorithm                                 | 59 |

|   |     | 3.1.3  | Correctness Modifications for Trace Scheduling  | 63 |

|   | 3.2 | Imple  | mentation of Software Register Synchronization  | 64 |

|   |     | 3.2.1  | Compiler Scoreboarding                          | 65 |

| 4 | Alg | orithm | Modifications for a Partitioned Register File   | 68 |

|   | 4.1 | VLIW   | +                                               | 69 |

|   |     | 4.1.1  | Algorithm Changes for VLIW+                     | 72 |

|   |     | 4.1.2  | Correctness Modifications for VLIW+             | 74 |

|   |     | 4.1.3  | Management of INCOMING while Scheduling a Trace | 76 |

|   | 4.2 | VLIW   | -Unknown                                        | 77 |

|   | 13  | МАР    |                                                 | 78 |

| 5            | Con | apiler Development and Architectural Evaluation | 80  |  |  |

|--------------|-----|-------------------------------------------------|-----|--|--|

|              | 5.1 | Predicated Operations                           | 81  |  |  |

|              |     | 5.1.1 Select Operations                         | 81  |  |  |

|              |     | 5.1.2 Conditional Branches                      | 82  |  |  |

|              | 5.2 | 64-Bit Execution                                | 83  |  |  |

|              | 5.3 | Local Register-to-Register Moves                | 83  |  |  |

|              | 5.4 | Constant Generation                             | 84  |  |  |

|              | 5.5 | Memory Addressing                               | 85  |  |  |

|              | 5.6 | Hardware Memory Segmentation                    | 87  |  |  |

| 6            | Exp | erimental Evaluation                            | 92  |  |  |

|              | 6.1 | Experimental Environment                        | 92  |  |  |

|              | 6.2 | Basic Benchmark Programs                        | 94  |  |  |

|              | 6.3 | SCP Applications                                | 96  |  |  |

|              | 6.4 | Dynamic Instruction Overhead                    | 98  |  |  |

|              | 6.5 | Performance Overhead                            | 100 |  |  |

|              | 6.6 | Application Experiment                          | 103 |  |  |

|              | 6.7 | Operating System Experiment                     | 105 |  |  |

|              | 6.8 | Discussion                                      | 106 |  |  |

| 7            | Con | Conclusions 1                                   |     |  |  |

|              | 7.1 | Results                                         | 109 |  |  |

|              | 7.2 | Future Work                                     | 110 |  |  |

|              | 7.3 | Conclusion                                      | 110 |  |  |

| $\mathbf{A}$ | The | MAP Instruction Set                             | 112 |  |  |

|              | A.1 | Anatomy of an Instruction                       | 112 |  |  |

|              | A.2 | Listing of Operations                           | 113 |  |  |

Bibliography

116

## List of Figures

| 1.1  | Tradeoff Between Compiler and Hardware Complexity in Com- |    |

|------|-----------------------------------------------------------|----|

|      | puter Designs                                             | 4  |

| 1.2  | Register Scoreboarding                                    | 9  |

| 1.3  | Abstract View of The MAP Processor                        | 13 |

| 1.4  | Operation of a Basic Block Compiler                       | 18 |

| 1.5  | Division of a Program into Basic Blocks and Traces        | 19 |

| 1.6  | Operation of the Multiflow Compiler                       | 20 |

| 1.7  | Encapsulation of Delayed-Binding Information              | 22 |

| 1.8  | Code Motion to Increase ILP                               | 24 |

| 1.9  | Code Motion Below Splits and Above Joins                  | 26 |

| 1.10 | Selection of Join Point to Minimize Hardware Delay        | 27 |

| 1.11 | Resource Usage Represented as a Partial Schedule          | 28 |

| 2.1  | Delayed Load                                              | 32 |

| 2.2  | Worst-case Timing for Delayed Load                        | 33 |

| 2.3  | Multiple Loads                                            | 34 |

| 2.4  | Worst-case Timing for Multiple Loads                      | 34 |

| 2.5  | Adjacent Block Scheduling                                 | 36 |

| 2.6  | State Transition Diagram                                  | 39 |

| 2.7  | State Transitions for Single-Instruction Scheduling       | 40 |

| 2.8  | General Outline of Algorithm                              | 42 |

| 2.9  | Scheduling Algorithm for a Basic Block                    | 44 |

| 2.10 | Algorithm for Merging STATE from Scheduled Successors .   | 45 |

| 3.1 | General Outline of Trace Algorithm                            | 60  |

|-----|---------------------------------------------------------------|-----|

| 3.2 | Scheduling Algorithm for a Trace                              | 61  |

| 3.3 | Routine to Manage State During Scheduling                     | 62  |

| 3.4 | Code Transformation to Convert a WAW hazard into a RAW Hazard | 67  |

| 4.1 | Remote Register Write for VLIW+ with Transfer Latency of      |     |

|     | One Cycle                                                     | 70  |

| 4.2 | Remote Register Write for VLIW+ with Zero-Latency Transfer    | 71  |

| 4.3 | General Outline of Algorithm for VLIW+                        | 73  |

| 4.4 | Scheduling Algorithm for VLIW+                                | 75  |

| 5.1 | Conditional Expressions that can use Predicated Operations    | 81  |

| 5.2 | Compilation of Conditionals using Predicated Operations       | 82  |

| 5.3 | Optimized Code Using Post-Increment Addressing                | 86  |

| 5.4 | Code Fragment from espresso                                   | 88  |

| 5.5 | Simple Implementation of memcpy                               | 89  |

| 5.6 | Efficient Implementation of memcpy                            | 90  |

| 5.7 | Correct Implementation of memcpy for the MAP Processor        | 91  |

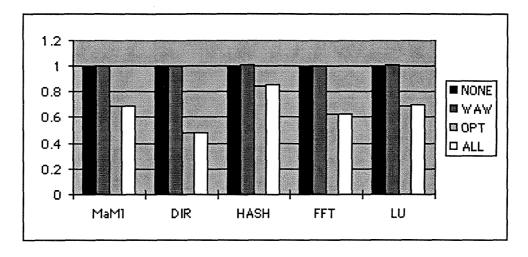

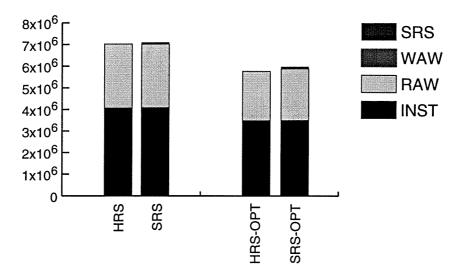

| 6.1 | Dynamic Instruction Counts - Normalized to NONE               | 98  |

| 6.2 | Inner Loop of LU                                              | 99  |

| 6.3 | Hash Table Insertion from the HASH Benchmark                  | 99  |

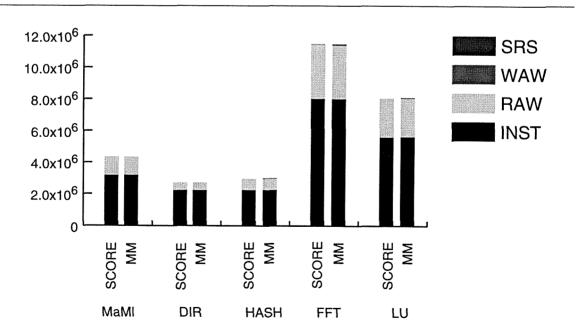

| 6.4 | Hardware vs. Software WAW Prevention: No Optimization         | 100 |

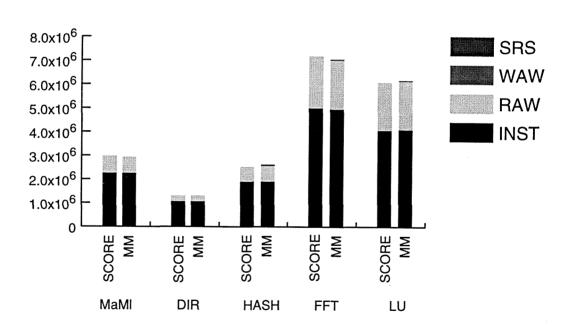

| 6.5 | Hardware vs. Software WAW Prevention: Optimization            | 101 |

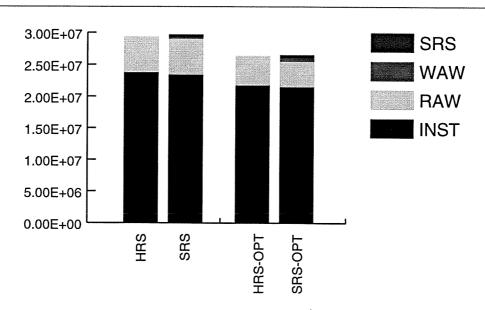

| 6.6 | Hardware vs. Software WAW Prevention for Compress             | 104 |

| 6.7 | Hardware vs. Software WAW Prevention for SCPlib               | 107 |

## List of Tables

| 5.1 | Count of EMPTY as a Percentage of Total Executed Instructions | 84  |

|-----|---------------------------------------------------------------|-----|

| 5.2 | Structure of an M-Machine Pointer                             | 87  |

| 6.1 | Memory Models Used For Experiments                            | 93  |

| 6.2 | Compile-Time Options Used For Experiments                     | 93  |

| 6.3 | Benchmarks Used For Experiments                               | 94  |

| 6.4 | Count of Inserted Barriers for Benchmark Programs             | 96  |

| 6.5 | Count of Inserted Barriers for SCP Applications               | 97  |

| 6.6 | Count of Inserted Barriers for Compress                       | 103 |

| 6.7 | Count of Inserted Barriers for SCPlib                         | 106 |

| A.1 | Anatomy of an Instruction                                     | 112 |

| A.2 | IALU Instructions                                             | 114 |

| A.3 | FALU Instructions                                             | 115 |

| A.4 | MEMU Instructions                                             | 115 |

## Chapter 1 Introduction

Increases in high-end microprocessor performance are becoming increasingly reliant on simultaneous issuing of instructions to multiple functional units on a single chip. As the number of functional units increases, the chip area, wire lengths, and delays required for a monolithic register file become unreasonable. Future microprocessors will have partitioned register files. The correctness of contemporary super-scalar processors relies on synchronized accesses to registers. This issue will be critical in systems with partitioned register files. Current techniques for managing register access ordering, such as register scoreboarding [59] and register renaming [60], are inadequate for architectures with partitioned register files. This work demonstrates the difficulties of implementing these techniques with a partitioned register file, and introduces a novel compiler algorithm which addresses this issue.

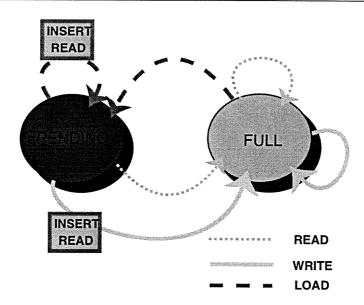

This thesis assumes a generic model of a partitioned register file system in which each functional unit is assigned to a local register file. More than one functional unit can be assigned to the same local register file. Functional units can read only from their local register file. All such reads access the local hardware scoreboard and are synchronizing operations. When an instruction issues, its destination register is marked EMPTY. Attempts to read an EMPTY register will stall until the register is marked FULL. Functional units can write to either their local register file, or to remote register files on the same chip. Writes do not access the scoreboard prior to issuing. The only access to the scoreboard performed by a write is to mark the destination register FULL after the write has completed.

State of the art high performance processors manage register synchronization through register scoreboarding or register renaming. When an instruction issues, ei-

ther the scoreboard or the register name table must be accessed to check its sources and its destination. If the register file is partitioned, checking the scoreboard or name table for a remote register is difficult, one functional unit cannot know when it is safe to write to a register in another functional unit's register file. While these techniques can be supported through use of a global scoreboard, or a partitioned scoreboard, they are complex to implement, and have latency problems similar to those of a monolithic register file.

An alternative to global scoreboarding or renaming is to change the model in which the functional units communicate with one another. Instead of communicating via general registers, remote register writes can be placed into a queue [18], to be read at the receiving functional unit's leisure. The receiving functional unit can then locally manage register synchronization within its own register file. This solution requires additional hardware, the queue, and can increase compiler complexity as queue write order could be critical. [18, 10].

This work discusses the organization of multiple functional units into loosely-coupled clusters. These are groups of functional units that can communicate via direct register writes, but with purely local hardware interlocks to force synchronization. A compiler algorithm, Software Register Synchronization (SRS) is introduced. A comparison between SRS and existing hardware mechanisms will be made. This comparison examines solutions for a contemporary super-scalar processor with a monolithic register file. The comparison is conducted using the Multiflow compiler modified to generate code for the MIT M-Machine. Experiments to evaluate the SRS algorithm are run on the M-Machine simulator being used for architectural verification.

#### 1.1 Trends in Computer Architecture

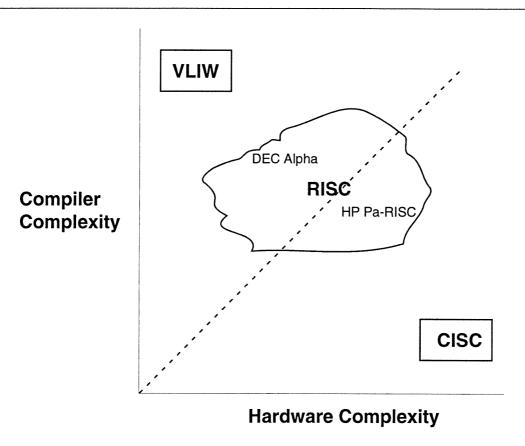

The first RISC microprocessor [46, 48] heralded a new era in computer architecture. Since the advent of RISC, emphasis in microprocessor design has been on balancing VLSI complexity with compiler complexity. Figure 1.1 shows the design space for a variety of architectures showing the tradeoff between these complexities. In this new era, progress in computer architecture has been driven by architectural innovation enabled by increases in available chip area as process feature size has decreased. One of the major areas of emphasis in early RISC architectures was the use of pipelining to increase instruction throughput. This emphasis on RISC and pipelining as a replacement for earlier microcoded designs revived the concept of static scheduling. Rather than having a complex control unit within the processor to manage all of the aspects of resource management, static scheduling performs some of this management within the compiler.

The MIPS (Microprocessor without Interlocked Pipe Stages) [32] processor developed at Stanford in the early 1980's was one of the early RISC architecture projects. This processor is of particular interest since, as its name suggests, it does not have hardware interlocks in the pipeline. Relative to the Berkeley RISC project [46, 47], the MIPS architecture places a higher emphasis on processor performance than on compiler simplicity. In order to simplify the pipeline hardware, hazard detection and avoidance is assigned to the compiler.

The next major development in architecture was superscalar microprocessors. This development drew on earlier computer designs, such as the CDC-6600 [59] which had superscalar designs but required multiple chips, and the IBM 360/91 [1] which was the first machine to use register renaming. The first of these chips was the America research processor which became the IBM RS/6000 [30, 45]. This processor has three functional units: fixed-point, floating-point, and branch. The emphasis of this

Figure 1.1: Tradeoff Between Compiler and Hardware Complexity in Computer Designs. This figure shows the spectrum of design space from a Complex Instruction Set Computer (CISC) like the DEC VAX which featured extensive microcoding to a VLIW machine which has all machine operation choreographed by the compiler.

design is on simplifying hardware without significantly adding to compiler complexity. One of the key ideas in this design is the separation of the register file into specific registers intended to be used by each functional unit. This functional separation reduces the circumstances in which the functional units will interfere with each other, but requires explicit compiler management of this interference when it does occur. For example, it is the compiler's responsibility to ensure that moving data from one register type to another is performed safely.

The most recent commercially available high-end processors, such as the Intel Pentium Pro [13], HP PA-8000 [27], MIPS R10000 [43], and the IBM/Motorola PowerPC 604 [44], feature up to six functional units, and hardware implementations of register synchronization techniques that allow out-of-order issuing of instructions. These machines employ complex hardware, which allows some degree of simplification within the compiler. For example, the coordination of out-of-order instruction issue is managed entirely in hardware.

An alternative approach to supporting multiple functional units is Very Long Instruction Word (VLIW) architectures. This term, coined by Josh Fisher [20], describes a machine with many functional units, and no interlocks. The compiler required for such a machine is quite complex, as it must statically schedule all of the machine's resources for each clock cycle. In such a machine, improper compiler choreography of operations can violate program correctness, or even crash the machine.

Current super-scalar designs allow reads and writes to a single register file from any one of the functional units, requiring, in general, two read ports and one write port on the register file for each functional unit. Since each write port requires one word-line for selection, and one bit-line to move the data [42], the size of the register file is a function of the square of the number of write ports. Thus, doubling the number of functional units results in a four-fold increase in the size of the register file. In addition the register file access delays increase due to parasitic capacitances:

wire parasitics due to longer bit- and word-lines as well as transistor parasitics for each port. Both area constraints and wire delays limit the practical number of register file ports.

In order to continue extracting more performance out of a single chip by adding additional functional units, it will be necessary to partition the register file. This solution will yield smaller register files and higher tolerance for delays in writing distant register files. One effect of partitioning the register file is an increase in compiler complexity as the compiler must take on responsibility for managing transfers between register files.

#### 1.2 Register Synchronization

Register hazards result when the relative order of instructions reading or writing their registers is not strictly controlled. Read-after-write (RAW) hazards occur when an instruction issues before the instruction producing its data has completed. Write-after-read (WAR) hazards occur when an instruction writes its result to a register before an instruction that was supposed to read the old value is able to issue. Write-after-write (WAW) hazards are due to instructions completing in a different order than they were specified (or assumed) by the compiler. Thus if two sequential operations A followed by B both write into the same register r1, and B completes before A, then r1 will have the incorrect result. Any subsequent instruction that reads from that register will get an incorrect result.

In purely sequential machines, WAW and WAR (collectively called WAX) hazards do not occur, as instructions are fetched and executed in exactly the order in which they are specified in the object code. However, the performance improvements seen in modern microprocessors have opened a window for these hazards. Pipelined processors in which register writes can occur from multiple stages of the pipeline,

non-blocking memory systems, multiple arithmetic units—such as floating point or superscalar units, and out-of-order instruction issue, often performed in hardware by high performance processors, all pose a threat of WAX hazards. Some examples of modern processors that use non-blocking caches, multiple arithmetic units, deep pipelines, and out-of-order execution are the MIPS R10000 [43], HP PA-8000 [27], Intel Pentium Pro [13], and the IBM/Motorola PowerPC 604 [44].

RAW hazards can be eliminated with a relatively simple hardware scoreboard, which marks registers empty when an instruction issues, and marks it full when the result returns. Instructions which attempt to read a register marked empty are blocked from executing until the empty register is marked full. RAW hazards are "true" hazards as they indicate the data dependencies between instructions; handling them in some way in hardware is usually necessary because they are frequent. Conceptually, WAX hazards can be eliminated with an infinite number of registers. No registers would be reused, and no WAX conflicts could occur. With a limited register set, registers must be reused. Without either software or hardware precautions, register reuse can result in WAX hazards, causing the program to produce incorrect results. WAR hazards may also be eliminated by prohibiting hardware out-of-order instruction issue completely; or by preventing an operation which writes a particular register from issuing prior to the completion of any instruction that precedes it in the static schedule that reads from the same register. WAW hazards are due to out of order instruction completion, which can be caused by variable instruction latency, and require special hardware for detection. This thesis focuses on reducing hardware complexity by moving WAW detection into the compiler and converting WAW hazards into RAW hazards that can be detected by the already necessary register scoreboard.

The motivation for this algorithm comes from compiler development for the MIT M-Machine [19] currently being designed by the Concurrent VLSI Architecture Group

at MIT. The Multi-ALU processor (MAP) chip, which serves as a single processing node in the M-Machine, performs remote memory accesses asynchronously, but does not check the synchronization state of registers prior to overwriting them. This allows processing to continue while awaiting completion of a remote memory access, but does not protect against WAW hazards. This architectural decision poses a challenge to the compiler: to efficiently support a non-blocking memory system while maintaining program correctness by preventing WAW conflicts. The MAP processor of the M-Machine features loosely-coupled CPUs on a single chip. Each of these processors can write the register files of all other processors on the same chip. Traditional methods of preventing WAW hazards are particularly problematic as they require each CPU to keep track of both local and remote registers. The simplified scoreboarding hardware of the MAP, the non-deterministic memory latencies, and the multiple clusters with distinct register files all require the efficient software solution described in this thesis.

# 1.3 Hardware Methods for Managing Register Synchronization

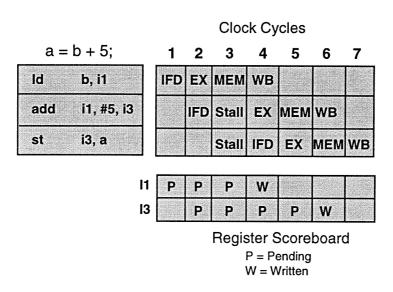

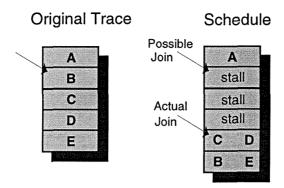

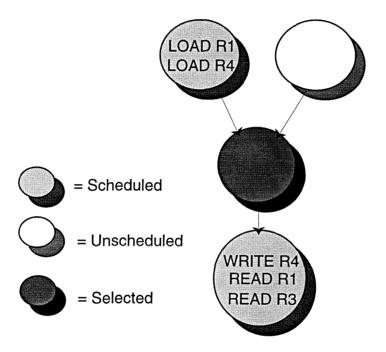

The two main hardware techniques for preventing WAW hazards in pipelined processors are register scoreboarding [59], and register renaming [60]. The DEC Alpha 21164 [16] uses register scoreboarding. This is illustrated in Figure 1.2 <sup>1</sup>. Within the machine's pipeline is a scoreboard for representing register state. When an instruction is issued, its destination register is marked pending, and cleared when the instruction completes. When a subsequent instruction that needs to write or read from a pending register is at the issue stage, the pipeline stalls until the register is written. No instructions proceed past the pipeline stage containing the scoreboard

<sup>&</sup>lt;sup>1</sup>The instruction set used in the examples is the MAP instruction set. Most operations take three arguments. The first two are operands, the third is a destination. More details on this instruction set can be found in Appendix A.

Figure 1.2: Register Scoreboarding. This figure shows a simplified machine pipeline with four stages, Instruction Fetch and Decode (IFD), Execute (EX), Memory Access (MEM) and Writeback (WB). The sample code is shown progressing through this pipeline. Due to the data dependencies in the code, the add is not able to proceed to the EX stage until the 1d enters the WB stage. The stall of the add delays the entrance of the st to the IFD stage. The state of the register scoreboard is also shown. When an operation enters the WB phase, the Pending state of the register is cleared in the first half of the cycle, allowing the dependent instruction to enter the EX phase. In this situation, the needed value is bypassed directly into a functional unit input, as well as being written to the register file.

until the condition which caused the stall has been handled. This form of score-boarding eliminates both RAW and WAW hazards, but prevents an opportunity of dynamically eliminating "false" WAW hazards: those hazards introduced as a result of how the program is executed.

Register renaming, such as used in the MIPS R10000 [43], provides the opportunity to eliminate the false WAW hazards by using more machine registers than are visible to the programmer. When an instruction is issued, the register name table is updated so that the destination register is given a new physical name and the virtual to physical translation is recorded. Subsequent instructions that read the virtual register are mapped to the physical register. If another instruction that targets the same virtual register is issued, then a new physical register is allocated and the virtual to physical translation is modified. Subsequent reads to the virtual register name will find the new physical register. Register renaming allows the number of live registers to be larger than the number of registers that can be named by the compiler. However, if the number of live registers is greater than the number of physical registers, the pipeline (like that of the scoreboard solution above) must stall.

Both scoreboarding and register renaming are suitable for today's architectures with single register files and a limited number of functional units. However, both techniques require access to global structures: the scoreboard or the name table. These structures will have latency problems similar to those of a monolithic register file as the number of functional units grows.

In the case of scoreboarding, the latency for accessing a global scoreboard would be incurred more than once for each instruction being issued. When a functional unit is ready to issue an instruction, a signal must be sent to the scoreboard to attempt to mark the target register pending. Execution cannot proceed until a return signal is received indicating that the register is now marked pending awaiting the completion of the instruction. When the instruction completes, the scoreboard needs to be written to update the state for the target register. For operands, it is necessary to check the state of the register, and delay execution until the source register is known to be full. The checking of the source operands can occur concurrently with the checking of the target register if enough ports on the scoreboard are provided.

For register renaming, it is necessary to examine all instructions that are ready to issue in a given cycle to determine which subset of those instructions can be issued. The logic required for this comparison needs to have write ports from all functional units, and grows in size as a function of the square of the number of these ports. The size and latency issues for this logic would be very similar to those encountered for a monolithic register file.

The software-only solution found in VLIW machines is applicable to machines in which all resources are scheduled in the compiler. The work in this thesis extends that work so that the software cooperates with the mechanisms provided in the hardware to handle the non-determinism present in the systems of today and tomorrow.

The complication posed by use of a partitioned register file occurs when a value needs to be written into a remote register file. One of the following conditions must be met for the transfer to be initiated:

- The writing functional unit must have determined that it is safe to write the remote register

- The remote register file must be capable of delaying the processing of the write until it is safe for it to occur

If all of the processors are executing in lockstep, as in a traditional VLIW, and the latency for memory accesses either is known or has a hard upper bound, the compiler is able to statically ensure the first of these conditions. Otherwise, the first of these conditions can only be met if there is global sharing of information among register banks and functional units. In particular, each functional unit needs to be

able to access the scoreboard associated with all register banks. This requirement for a globally accessible scoreboard has delay problems similar to those of a monolithic register file. In the absence of known memory latency and hardware write interlocks, WAW hazards can occur even within a single cluster of the MAP chip.

The second condition requires additional hardware, a queue, and represents a different organization of the processor. The finite nature of the queue can result in hardware deadlock. In addition, support for the queue can increase compiler complexity as queue write order could be critical.

#### 1.4 A New Way of Organizing a Processor

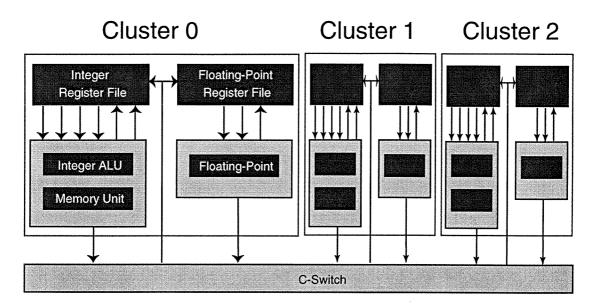

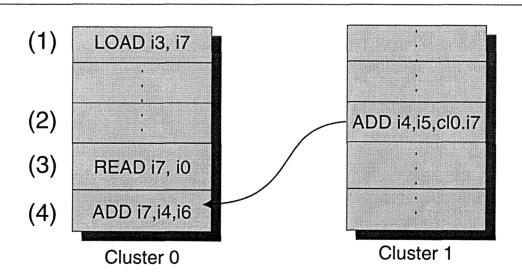

The Multi-Alu Processor (MAP), the processor for the MIT M-Machine, uses several mechanisms to improve processor throughput relative to a super-scalar or VLIW architecture. These mechanisms include loosely-coupled clusters of processors, and hardware multithreading. The MAP clusters are each similar to a super-scalar processor, containing integer, memory, and floating-point functional units with a common register file. All of the clusters within a single MAP have the ability to write the register files associated with all other clusters. Figure 1.3 shows the aspects of the MAP architecture that are relevant to this thesis.

The MAP processor is a prototype of future systems that will contain multiple ALUs and disjoint register files. Unlike VLIWs, the MAP cannot be completely statically scheduled, as the different clusters are allowed to issue instructions independently and memory latencies are variable due to the cache and virtual memory system. The MAP has nine functional units, three each of floating-point, integer, and address, which are organized into three clusters, each of which contains integer, memory, and floating-point units, as well as an integer and a floating point register file. The clusters communicate and synchronize through registers, as a portion of

Figure 1.3: Abstract View of The MAP Processor. The MAP Processor has three clusters each of which contains an integer ALU, double-precision floating-point unit, and a memory unit, as well as integer and floating-point register files. Data can be transferred register-to-register across the Cluster Switch (C-Switch). The arrows indicate read and write ports, each of which is capable of carrying one machine word in the indicated direction each clock cycle.

each cluster's register file may be written by other clusters.

Register synchronization is performed using a scoreboard and hardware RAW hazard detection. When an instruction issues, its destination register (if the destination is in the same cluster in which the instruction issues) is marked empty. When the instruction completes, its destination register is marked full. The complication occurs when an instruction from one cluster targets the register file of a remote cluster. In this case the register is not marked empty as the hardware required to do this is prohibitively expensive. Instead the receiver is required to execute an EMPTY instruction in order to mark the register empty prior to receiving the data. This allows RAW hazards to be eliminated even for remote register writes. The register scoreboard prevents RAW hazards and in-order instruction issue prevents WAR hazards; no hardware is provided to detect WAW hazards.

Further compiler work is required to take advantage of the loosely coupled pro-

cessor clusters and low interaction latency of the MAP chip. Non-determinism in execution timing requires that the compiler choreograph synchronization and communication between clusters. The current approach being explored for this work is scheduling the code within the compiler as if it were a VLIW with all units running in lockstep, and inserting code to synchronize clusters whenever an inter-cluster write is required. A variety of other schemes are also under consideration, including treating each cluster as an independent processor, and using inter-cluster writes as a very efficient form of inter-processor communication. Any technique that is used will require inserting code to synchronize two clusters prior to transferring data between them. Trivial extension of SRS will allow it to be used in the choreography between the clusters. Prior to permitting an inter-cluster register write, the compiler can determine the state of the register to be written using the software scoreboarding described here. If the local register to be written by the remote cluster is not full, the instruction notifying the remote cluster can be delayed by inserting a register barrier on the local cluster. This prevents the remote cluster from writing the local register until it is safe from WAW hazards.

#### 1.5 Related Work

The work presented in this thesis is most closely related to previous work in the fields of register allocation, and instruction-level parallelism (ILP). Previous work in computer architecture for ILP was presented in Sections 1.1 and 1.3. This section presents some of the background material in register allocation, and in compiler support for ILP.

The standard technique for performing register allocation is register coloring. This was originally presented by Chaitin [9, 8]. In the last decade there has been a significant number of publications seeking to improve upon this technique [2, 4, 11, 7, 5, 3].

This is still an area of active research. Recent research has focused on developing techniques to refine graph coloring to reduce the number of spills that are inserted into code. Most recently, work [6, 24] has focused on using different heuristics to decrease the amount of spilling that is performed. One of the fundamental assumptions of register coloring is that instructions will not be reordered once register assignments have been made. The instruction scheduling performed by the Multiflow compiler renders this technique unusable [23].

Compiler techniques for eliminating both RAW and WAW hazards have been proposed and implemented. Significant work on static scheduling for instruction-level parallelism, particularly in scheduling beyond basic block boundaries, was performed at Yale University [17], and was implemented in the Trace [12] family of VLIW computers produced by Multiflow. The Multiflow machine had up to 28 execution units and a register file partitioned across the units. The entire machine executed in lockstep with fully predictable latencies. The linchpin of this technology was the compiler [37] which statically scheduled long traces of code for instruction level parallelism. The compiler performed memory bank disambiguation to prevent multiple references to the same bank of memory in a given cycle, and there was no data cache. As all latencies could be statically determined and no out of order execution was allowed, all RAW and WAW hazards were eliminated by the compiler, and without complex hardware. Further details about the Multiflow compiler and trace-scheduling are presented in Section 1.6.

#### 1.5.1 Instruction Scheduling for ILP

There have been a variety of techniques proposed for increasing the amount of ILP available to the scheduling phase of a compiler. There are two classes of these techniques. One group focuses on scheduling beyond the boundaries of a basic block.

The other group works on loop transformations to increase parallelism within a basic block.

Trace-scheduling [17, 37] is covered in detail in Section 1.6. In summary, this algorithm uses heuristics to predict which direction conditional branches will go at runtime. This information is used to coalesce basic blocks into a single unit for scheduling called a trace. This algorithm performs similar code motion to that used for reordering instructions within a basic block to increase ILP, but allows code to move past conditional branches under some circumstances. The conditions under which such code motion is allowed are expanded upon in Trace Scheduling-2 [21].

Superblocks [33] are a variation on traces. The key difference is that a superblock only has one entrance point at the top, whereas a trace can also have entrance points into the middle. A hyperblock [38] is similar to a superblock, but contains predicated instructions. That is, a hyperblock may contain code from mutually exclusive basic blocks, with predicates on the execution of some instructions controlling whether or not they are executed. The target machine for such a construct supports predicated instructions in hardware.

There have been a variety of compile-time techniques used for increasing the amount of available ILP within a loop. In particular, software pipelining [36] exposes parallelism by overlapping instructions from different loop iterations without violating loop-carried data dependencies. Similarly, loop unrolling, duplicates the code within a loop which has the same overlapping benefits of software pipelining, and also reduces the number of conditional branches taken during loop execution.

Branch prediction can also be very powerful for increasing ILP. The compiler statically predicts which way a branch will go at run time, and schedules the code using that assumption. This can result in an increase in code size if an alternative piece of code is generated for when the branch takes the other direction. Some of

this code bloat can be reduced if the target architecture has predicated operations. There has also been work done on the feasibility of performing compiler-time branch prediction based on information gathered during previous runs of the program [22].

Another important area of research relating to compiler scheduling for parallelism is that of inter-procedural analysis. Traditionally compilers, including the Multiflow compiler, have restricted their data analysis to within individual procedures. Recently work has been conducted into the possibility of extending traditional analyses across procedural boundaries [61, 29, 28]. This work has the possibility of increasing the amount of ILP made available to the scheduling phase of a compiler.

#### 1.6 The Trace Scheduling Algorithm

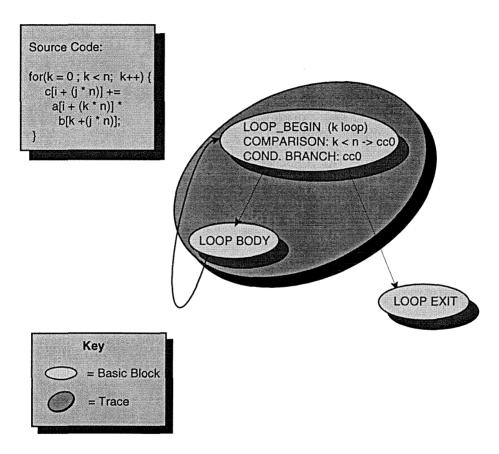

The motivation for trace scheduling is found in the problem of compiling for ILP. In general, it is difficult for a compiler to locate enough parallelism within a basic block to sustain utilization of multiple functional units. A compiler using the trace-scheduling algorithm seeks to overcome this obstacle by performing scheduling on a larger unit than a basic block. This larger unit is called a trace. A trace is allowed to span multiple basic blocks, and may contain conditional branches within it. Traces are not allowed to contain loop back edges. One important difference between a basic block and a trace is that a trace is allowed to have multiple exit and entry points.

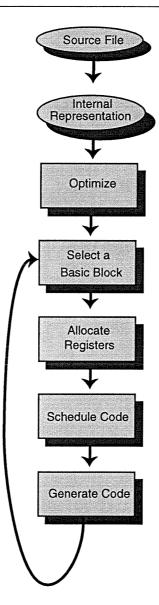

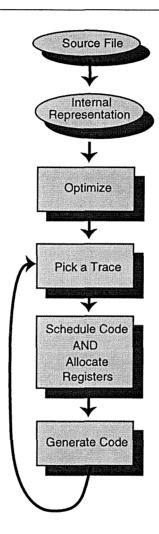

Figure 1.4 shows the steps performed by a traditional basic-block compiler. Within such a compiler the ordering in which blocks are scheduled is based on their position within the control-flow graph. This graph is traversed in some ordering, generally breadth- or depth- first. In contrast, trace-scheduling uses heuristics to predict which paths through the control-flow graph are most likely to be followed, and assembles these basic blocks into a trace to be scheduled as a unit. Figure 1.5 shows the selection of a trace from a control flow graph. The goal of the trace-picking

Figure 1.4: Operation of a Basic Block Compiler. A traditional compiler iterates over basic blocks in the program graph. For each block it first allocates registers, and then schedules operations onto the functional units of the target machine. When it has scheduled all of the basic blocks, it terminates.

Figure 1.5: Division of a Program into Basic Blocks and Traces. The Trace-picking heuristics predicts which direction the branch ending a basic block is most likely to go. The code most likely to be executed is added to the trace containing the branch. For loops, the heuristics assume that the loop body is more likely to be executed than the loop exit code.

heuristics is to identify the performance critical portions of the code first, so that they are not bound by resource constraints imposed by less important portions of the program. In particular, the trace-picking heuristics are intended to favor code composing inner loops of scientific computations. The general flow of operations

Figure 1.6: Operation of the Multiflow Compiler. The Multiflow compiler picks traces out of the program graph, and performs a single scheduling step which performs both register allocation and functional unit assignment at the same time. When the entire program has been scheduled, the compiler terminates.

within the Multiflow compiler is shown in Figure 1.6.

This compilation strategy involves significant departures from traditional compilers. These include performing register allocation and instruction scheduling as part

of the same compilation phase; reordering instructions to shorten a schedule; and duplicating instructions at trace split and join points. One of the most obvious of these departures is the division of the program into traces described above. The following sections provide details of some of the other interesting aspects of trace-scheduling.

#### 1.6.1 The Phase Ordering Problem

In a traditional basic block compiler there are usually independent scheduling phases for register allocation, and instruction scheduling. The separation of these two processes creates a phase ordering problem [23]. If register allocation is performed first, dependencies on register usage which are unrelated to program data dependencies can be introduced into the schedule. If instruction scheduling is performed first, it can be impossible to perform register allocation for the resultant schedule. To compensate for these problems, it is necessary to insert spills and restores after much of the scheduling information has been destroyed. In general, traditional compilers will perform register allocation first, as this results in less inefficiency.

The Multiflow compiler uses a different approach. Register allocation and instruction scheduling are performed as part of the same phase. The emphasis on this process is that priority for registers should go to the instructions that are going to be issued most frequently. One of the ramifications of this decision is that register coloring [9, 8] can not be used during trace-scheduling. One of the assumptions of register coloring is that instructions will not move relative to each other. As described in Section 1.6.2 the reordering of instructions is important to the efficiency of the code generated by the Multiflow compiler.

The key idea used for register allocation in the Multiflow compiler is *delayed* binding. Values are not assigned to registers until they are actually referenced. When

the first trace in the program is selected it has no constraints on register usage. Recall that the trace-picking heuristics are intended to select the performance-critical inner loops of scientific computations to be scheduled prior to any other portions of the code. If the target machine has sufficient registers, the inner loops will be executed with no spilling or extraneous copies. Any necessary spills are pushed out of the critical path of the program.

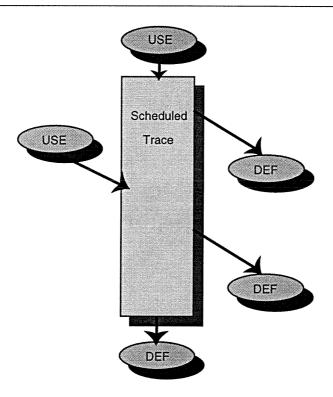

This mechanism functions by attaching information about bindings between variables and registers to scheduled traces. This process is called *bookkeeping* within

Figure 1.7: Encapsulation of Delayed-Binding Information. Once a trace has been scheduled, variable binding information is inserted into the program control-flow graph. A USE node indicates where this trace assumes that variables are upon entry. A DEF node indicates where variables are left upon exit.

the Multiflow compiler literature [17, 37]. This information is in the form of special nodes inserted into the control-flow graph. These nodes are inserted in between a piece of code which has just been scheduled, and any unscheduled code. USE nodes

are placed at *join* edges, and contain information as to where the scheduled code assumed variables to be located. When the adjoining unscheduled code is scheduled, it must ensure that these variables are left in the proper place. DEF nodes are placed at *split* edges, and contain information as to where the scheduled code has left variables. When the adjoining unscheduled code is scheduled, it must use these nodes to determine the initial location of the variables. This is shown in Figure 1.7. Until a variable is actually referenced, the location it is bound to is a temporary. Section 1.6.3 contains further discussion of *split* and *join* edges.

The generic name for these nodes is a Value-Location Mapping (VLM) [23]. When a trace is scheduled it has to reconcile the information in its entry and exit VLMs. If it is not possible to maintain a desired register binding throughout an entire trace, and no other registers are available for temporary storage, the variable in question must be spilled to and restored from memory.

# 1.6.2 Instruction Reordering

Instruction reordering is another technique that increases the amount of available ILP in code output by a compiler. The idea behind this reordering is that the sequential ordering of instructions within a program does not necessarily represent the data dependencies of instructions. If two operations do not share any data dependencies, then their execution order can be reversed without affecting the correctness of the program. Some instructions can be moved past conditional branches. When this occurs, it is sometimes necessary to insert compensation code to ensure that all of the required instructions are executed whichever way the conditional branches go. This section deals with code motion that does not require compensation code. Section 1.6.3 describes compensation code, and the circumstances under which it is required.

The data dependencies between instructions are represented as edges in the DAG of a trace. An instruction is unavailable for scheduling until all instructions on which it depends have been scheduled. Once all of these constraining operations have been scheduled, the instruction is data ready. Any ordering in which data ready instructions are scheduled should be safe, as these instructions are guaranteed to not have any true data dependencies. It is still necessary to ensure that no false data dependencies are introduced through register reuse. Figure 1.8 shows an example of legal code

#### Source Code

#### Sequential Schedule

| fmul | f1, f2, f3         |

|------|--------------------|

| fadd | f4, f3, f1         |

| sub  | i8, i9, i10        |

| sub  | i11, i9, i12       |

| add  | i10, i12, i8       |

|      | fadd<br>sub<br>sub |

#### Reordered Schedule

| falu<br>ialu | fmul<br>sub | f1, f2, f3<br>i8, i9, i10 |

|--------------|-------------|---------------------------|

| ialu         | sub         | i11, i9, i12              |

| falu         | fadd        | f4, f3, f1                |

| ialu         | add         | i10, i12, i8              |

| ICIO         | add         | 110, 112, 10              |

Figure 1.8: Code Motion to Increase ILP. If this code is scheduled based purely on the order in which operations occur in the source program, four cycles are needed to issue all of the instructions. Since there would certainly be a floating-point pipeline stall between the first and second instruction, this would take several additional cycles to complete. If the code is reordered, it is possible to increase the distance between the two floating point operations, thereby decreasing the duration of the pipeline stall. Also, the reordered schedule requires one fewer cycle to issue.

#### motion.

It is legal to move an instruction above a split if the result of the split is not to memory, and is not live on the off-trace edge. That is, if the result of the operation might be accessed if the branch goes opposite to the predicted direction, it cannot legally be moved. This code motion requires that the hardware be capable of delaying or suppressing the exceptions that might result from issuing an instruction out of order. For example, moving a division above the safety check ensuring that the divisor is not zero can cause a divide-by-zero exception.

This processing is similar to the scheduling performed by a compiler for a pipelined machine in order to minimize pipeline stalls [53, 25, 31]. The ability to schedule across basic block boundaries significantly expands the possibilities for such code motion. For a pipelined machine, the emphasis is on trying to fill all of the issue slots between the start of an instruction, and the clock cycle when it is legal to access the result of the instruction. For superscalar and VLIW machines, there is the added goal of increasing the available ILP in the program to take advantage of the available functional units.

#### 1.6.3 Management of Splits and Joins

When managing conditional branches, special handling is necessary to ensure that any instructions that have been moved beyond a branch are executed on all appropriate paths through the program; and that the machine resource restrictions are adhered to whichever direction of the branch is taken. The Multiflow compiler models these changes in control flow as *splits* and *joins*. Within the program graph, these transitions are modeled as edges which can contain instructions, and information about both machine state and the binding of variables to registers. The instructions within such an edge are *compensation code* required to maintain program correctness. The information about machine state is contained within *partial schedules*. Section 1.6.1 describes the management of variable-register bindings. Section 1.6.2 describes code motion beyond *splits* and *joins* that do not require *compensation code*. This section discusses *compensation code* and *partial schedules*.

#### Compensation Code

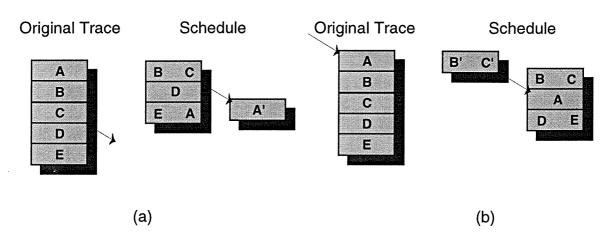

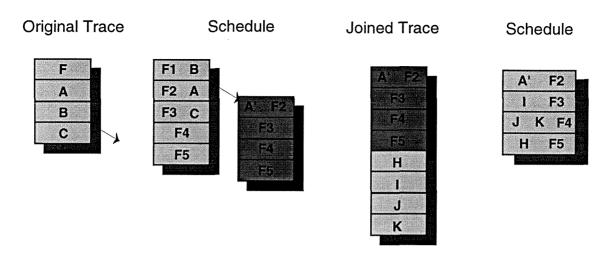

When an instruction is moved below a *split* or above a *join*, it is necessary to insert compensation code to ensure correctness of the compiled code. An example of the insertion of compensation code is shown in Figure 1.9. Any instruction that has

Figure 1.9: Code Motion Below Splits and Above Joins. (a) The original trace contains a *split* after instruction C. When the trace is scheduled, A is moved below the split. A copy of A, denoted A', is added as *compensation code* on the outgoing edge. (b) The original trace contains a *join* before instruction A. When the trace is scheduled, both B and C are moved above the *join*. Copies of B and C, denoted B' and C', are added to the incoming edge as *compensation code*.

moved beyond a branch will have to occur in at least two places in the generated code. This duplication of instructions can lead to code explosion. The Multiflow compiler contains safety mechanisms to restrict this code duplication. In particular, if a program is deemed to have grown too large, all further code motion which would require *compensation code* is forbidden. As this prohibition is unlikely to be invoked until after the traces most likely to be frequently executed have been scheduled, it should have little effect on the overall efficiency of the generated program.

Instructions that occur before a *join* point can tie up hardware resources. If one instruction is followed by stall cycles inserted into the schedule, and a *join* is allowed to happen once this instruction has issued, it is more efficient to wait until the stalls have happened as well. This is shown in Figure 1.10.

Figure 1.10: Selection of Join Point to Minimize Hardware Delay. The original trace contains a *join* after instruction A. When A is scheduled, it is followed by three hardware stall cycles. While the *join* could happen during the first of these stalls, it is more efficient to delay the *join* until just after the last stall.

In order to balance the possible delays due to hardware constraints with the amount of *compensation code* that is generated, the compiler selects the cycle at which a *join* occurs. Joining as early as possible minimizes *compensation code*, but can result in delays.

#### Partial Schedules

When transition between traces occur, it is possible that pipelines or other machine resources might be in use within an already scheduled trace. It is necessary to ensure proper modeling of this hardware resource usage. If there is a hardware resource such as a floating-point divide unit which can accept a new instruction once every five cycles, and an instruction using this resource is issued three cycles before a *split* point, this resource usage must be modeled to prevent a conflict when an adjacent trace is joined. This is represented as a *partial schedule*. The usage of the resource is copied onto the edge, but the instruction that requires the usage is not. This is shown in Figure 1.11. The resource information is added on to the top of the trace being joined. The scheduler ensures that this resource is not over-subscribed. An example of the importance of *partial schedules* can be found in Section 4.1.

Figure 1.11: Resource Usage Represented as a Partial Schedule. Instruction F is a floating-point instruction that ties up some hardware resource for five cycles. If a split occurs before those five cycles are up, the resource usage information must be copied onto the off-trace edge. When the trace being joined by this partial schedule is scheduled, both the compensation code and partial schedule information are incorporated into the trace. During scheduling, operations from lower down in the trace are allowed to move up and overlap with the resource usage information as long as they don't need the busy resource.

A busy resource does not consume an instruction issue slot. A machine could have one floating-point issue slot every cycle; and floating-point divide and add could use different hardware resources. The busy status of the divide unit would not prevent adds from being issued.

#### 1.7 Overview of the Dissertation

The current trend in high-performance microprocessors is towards improving performance by increasing the number of functional units on a single chip. These chips apply complex hardware solutions to the problem of register synchronization. The register file size, and accompanying wire lengths and delays, significantly increases as the number of functional units go up. The most obvious solution to this problem, partitioning the register file, rules out hardware implementations of existing register synchronization schemes. The delays incurred by the monolithic register file are still

present in the synchronization scheme for a partitioned register file. The limiting effect on processor clock speed caused by the delays entailed in a large number of functional units dictate that register files be partitioned, but the partitioned register file system requires a new approach to register synchronization.

This dissertation presents a novel compiler-based approach to this problem. This solution, the Software Register Synchronization (SRS) algorithm, is a synthesis of a known hardware technique, register scoreboarding, with an existing compiler scheduling algorithm, trace scheduling. The SRS algorithm relies on the existence of a local scoreboard at each register file which enforces a pipeline interlock when attempting to read a register which is marked as empty. This operation can be managed using purely local information. The Multiflow trace-scheduling compiler provides the ability to make decisions about register selection at the same time as functional unit selection. This allows the SRS algorithm to bias register use away from empty registers, as well as ensuring that local synchronization is performed on any potentially empty register prior to overwriting the register. The trace scheduler also provides a framework for propagating information between traces at compile time. This framework is utilized to propagate register state information across trace boundaries. Finally, the Multiflow compiler provides static scheduling and instruction reordering to increase the amount of available Instruction-Level Parallelism (ILP) in a program.

#### 1.8 Contributions of this Dissertation

This dissertation makes the following contributions:

• It identifies register size expansion as a limiting factor on degree of ILP in processors, proposes partitioning of register files to circumvent this limitation, and

- describes the problems in implementing traditional hardware register synchronization techniques in the presence of a partitioned register file.

- It proposes and demonstrates the correctness of a compiler algorithm, Software Register Synchronization (SRS) to manage register synchronization in both conventional super-scalar designs, and super-scalar designs with partitioned register files.

- It evaluates the performance characteristics of code compiled using the algorithm, and evaluates the M-Machine architecture as a compiler target.

# 1.9 Organization of the Dissertation

Chapter 2 describes a compiler algorithm for managing register synchronization within a system with a monolithic register file. This includes a description of the register synchronization problem, and a demonstration of the correctness of the algorithm. Chapter 3 extends the algorithm to function within a trace-scheduling compiler. This description includes details of the implementation of this algorithm within the Multiflow compiler, and necessary changes to the demonstration of correctness. Chapter 4 extends the algorithm to a multi-cluster environment. This includes the additional implementation notes, as well as changes to the demonstration of correctness. Chapter 5 describes some implementation details of the retargeting of the Multiflow Compiler to the M-Machine, accompanied by a critique of the M-Machine instruction set architecture. Chapter 6 provides experimental results. These results include an evaluation of the single cluster algorithm relative to hardware solutions for register synchronization. Chapter 7 proposes future directions for this work, and presents conclusions.

# Chapter 2 Register Synchronization for a Monolithic Register File

This chapter reformulates the issue of register synchronization, and presents a compiler algorithm for ensuring correct execution of compiled code on a processor with a monolithic register file. The original version of the algorithm is for a traditional basic-block compiler targeted for a single-cluster of the MAP. Following chapters will introduce additional constraints, and discuss the changes necessary to the algorithm to manage these additional issues. For the purposes of this discussion, the target architecture is defined as only enforcing register synchronization on reads. A demonstration of the correctness of the algorithm is presented.

Existing processors demonstrate that register synchronization is readily manageable for a monolithic register file using either register scoreboarding [59], or register renaming [60]. The algorithm is presented in this form to provide a base case of compatibility with existing techniques.

The set of possible machine operations can be divided into three categories based on their handling of register synchronization state. READ operations are the only operations that perform synchronization.

- LOAD places a value into a *destination* register. LOADs can complete asynchronously. When a LOAD is initiated a synchronization flag associated with the *destination* register is set. This flag is cleared when the LOAD completes.

- READ takes a value from a *source* register and uses it to perform some operation (such as *add*, *subtract*, *compare*, *etc.*). READS will not begin until the

synchronization flag on the source register is cleared.

• WRITE places a value into a destination register. WRITES will complete even if the synchronization flag on the destination register was set when they started. After a WRITE has completed, the synchronization flag on the destination register is always cleared.

# 2.1 Example 1: Delayed Loads

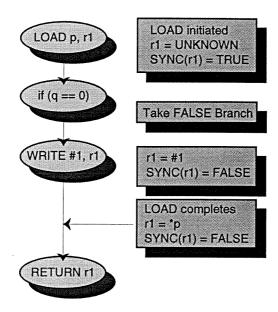

Figure 2.1 demonstrates the need for register synchronization: as WRITEs do not respect the state of their destination registers, out-of-order instruction completion can result in incorrect program execution. The value \*p is LOADED into r1. If q = 0, the program will stall until the LOAD completes, and then READ r1 and add it to r2. If  $q \neq 0$ , r1 could be WRITTEN before the LOAD completes. Figure 2.2 shows a worst-case timing sequence. In this case, the test fails, and #1 is WRITTEN to r1. Prior to the return, the LOAD completes, placing \*p in r1. The incorrect result is returned to the caller.

| a = *p;<br>if(q == 0)<br>a = a + b; | LOAD<br>EQUAL<br>BF<br>ADD<br>JMP | p, r1<br>q, 0, cc0<br>cc0, L1<br>r2, r1, r2<br>L2 | ; LOAD from location p into r1<br>; Check (q == 0)<br>; If false, branch to L1<br>;Add r1 to r2 |

|-------------------------------------|-----------------------------------|---------------------------------------------------|-------------------------------------------------------------------------------------------------|

| else                                | L1:                               |                                                   |                                                                                                 |

| a = 1;                              | MOVE<br>L2:                       | #1, r1                                            | ; WRITE r1                                                                                      |

| return a;                           | RETURN                            | r1                                                |                                                                                                 |

Figure 2.1: **Delayed Load**. This shows the source code and assembly language for a code fragment containing a WAW hazard. If the FALSE direction of the branch is taken, there would be two consecutive writes to the same register.

Figure 2.2: Worst-case Timing for Delayed Load. This diagram shows the timing of operations for the Delayed Load example that would generate the incorrect answer. In between the initiation and completion of the LOAD operation which uses r1 as its target, the number 1 is written into the r1. At the end of this execution r1 is supposed to contain 1, but contains instead \*p.

# 2.2 Example 2: Multiple Loads

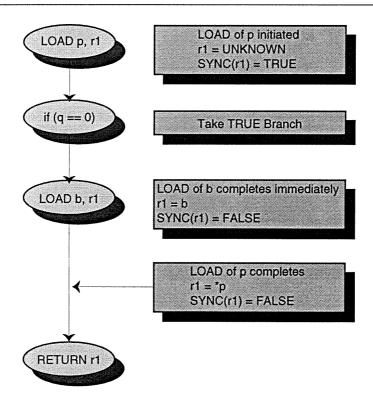

Figure 2.3 shows a second situation in which register synchronization is necessary: Two consecutive LOADs to the same register can complete in the wrong order, leaving the incorrect value in the register. The value p is LOADED into p. If p = 0, the value p is LOADED into p is LOADED into p into p into p is LOADED into p into p into p into p completes. The incorrect result is returned to the caller.

| a = *p;    | LOAD             | p, <b>r</b> 1 | ; LOAD from location p into r1 |

|------------|------------------|---------------|--------------------------------|

| if(q == 0) | $\mathbf{EQUAL}$ | q, 0, cc0     | ; Check $(q == 0)$             |

|            | BF               | cc0, L1       | ; If false, branch to L1       |

| a = *b;    | LOAD             | b,r1          |                                |

|            | L1:              |               |                                |

| a = a + c; | ADD              | r1,r4,r4      | ; READ r1, r4; WRITE r4        |

| return a;  | RETURN           | r4            |                                |

Figure 2.3: Multiple Loads. This program contains the source code and assembly language for a more subtle register synchronization problem. If the first load results in a remote memory access, and the second load hits in the cache, the second load could complete first, yielding the incorrect answer.

Figure 2.4: Worst-case Timing for Multiple Loads. This diagram shows the timing of operations for the Multiple Loads example that would generate the incorrect answer. The first LOAD misses in the primary cache, and takes several cycles to complete. The second LOAD hits in the primary cache, and completes immediately. The target register, r1, which is supposed to contain \*b, ends up containing \*p

# 2.3 Development of Register Synchronization Definition

This section further refines the specification of the register synchronization algorithm.

An initial statement of the specification is:

Guarantee that no WRITE or LOAD has as its destination a register whose synchronization flag is set.

This can be achieved within a basic block using a single forward pass over the block, inserting correction code when a problematic instruction is encountered. To achieve correctness READS can be inserted to force synchronization. Complications arise when dealing with transitions between basic blocks, as this requires propagating state information across block boundaries.

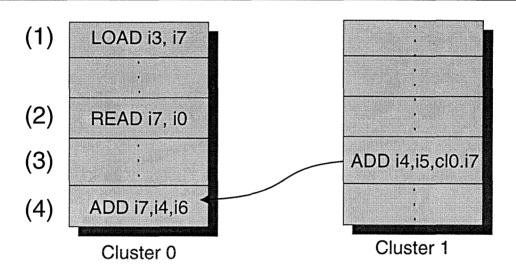

To preserve generality, the scheduling of basic blocks is assumed to have no fixed ordering. This is illustrated in Figure 2.5, which shows four basic blocks. Two of these basic blocks have already been scheduled; two of the blocks are as yet unscheduled. One of the unscheduled blocks has been selected to be scheduled. There are operations in both the preceding and succeeding scheduled block which might require action within the current block. If the first instruction in the selected block is WRITE R4, it is necessary to first insert a READ R4. If the last instruction is a LOAD R3, the READ R3 in the predecessor makes this a safe operation to perform.

Figure 2.5: Adjacent Block Scheduling. During code scheduling, traces are not processed in any fixed ordering. When scheduling a given trace, there could be both predecessors and successors containing operations that can affect the current trace. This diagram shows a portion of a program graph. The trace that has just been selected for scheduling inherits two registers from a scheduled predecessor that are PENDING as they are the targets of LOAD operations within that predecessor; but sees two registers that are GROUNDED by READ operations in a scheduled successor.

The problem of ensuring program correctness can be specified as:

Obtain register state information from scheduled predecessors. Generate a schedule for the current block, inserting synchronizing READS where required. Examine scheduled successors, insert any READS required for transition from current block into scheduled blocks. Ensure that state information made available to all predecessors and successors is correct.

## 2.4 Overview of Solution