# MODELLING, ANALYSIS, AND DESIGN OF SWITCHING CONVERTERS

Thesis by Slobodan M. Ćuk

In Partial Fulfillment of the Requirements

for the Degree of

Doctor of Philosophy

California Institute of Technology

Pasadena, California

1977

(Submitted November 29, 1976)

Dedicated to my parents

MILOJKO AND JULIJANA ĆUK

#### **ACKNOWLEDGMENTS**

I wish to express my deepest appreciation to my advisor,

Professor R. D. Middlebrook, who introduced me to the exciting

field of Power Electronics and provided me with outstanding guidance

during the course of this research.

Financial support by way of a Teaching Assistantship from the California Institute of Technology during my first year of graduate study, and by way of a Research Assistantship sponsored by the TRW Systems Group and the National Aeronautics and Space Administration (NASA) during my second year of graduate study, are also acknowledged.

I am very indebted to Ms. Dian Rapchak who did an excellent job of typing the text.

Finally, without the complete understanding and support of my wife, Nevenka, and our numerous discussions on this research area, this work would have been much more difficult.

#### **ABSTRACT**

The principal objective of this work on modelling and analysis of switching dc-to-dc converters and regulators is to obtain a linear model (either through state-space or linear circuit description), subject to appropriate restrictions, for the inherently nonlinear power stage in which the dc conversion is accomplished. A general unified approach to modelling and analysis of switching dc-to-dc converters is developed which is directly applicable to any dc-to-dc converter operating in either of two conduction modes (continuous or discontinuous inductor current), and which results in a final dynamic linear model either in terms of state-space equations or in terms of their corresponding linear circuit models. In particular, in Part I this analysis technique, called state-space averaging, is applied to the continuous conduction mode of converter operation, while in Part II appropriate extension of the method to the discontinuous conduction mode is made. In each case, the culmination of the modelling and analysis is achieved in the development of canonical circuit models which represent any such converter regardless of its detailed configuration.

The insights that emerge from the general state-space modelling approach (Parts I and II) lead in Parts III and IV to the <u>design of new converter topologies</u> through the study of generic properties of the cascade connection of basic buck and boost converters. This study paves the way in Part IV to the discovery of a new switching converter based upon capacitive rather than the usual inductive energy transfer. The new converter is shown to have substantial advantages over the conventional converters in its class in efficiency, performance, and also in size and weight.

Both the state-space averaged models and their corresponding circuit realizations provide the circuit designer with a powerful tool for <u>analysis</u> of existing converters as well as for <u>synthesis</u> of new converter topologies.

# TABLE OF CONTENTS

|             |                                                    | Page |

|-------------|----------------------------------------------------|------|

| ACKNOWLEDGN | MENTS                                              | iii  |

| ABSTRACT    |                                                    | iv   |

| INTRODUCTIO | NC                                                 | 1    |

| CHAPTER 1   | SWITCHING DC-TO-DC CONVERTERS AND REGULATORS       | 6    |

| 1.1         | Physical operation and basic properties of         |      |

|             | switching converters                               | 6    |

| 1.2         | Two operating modes and their dc relations in the  |      |

|             | steady-state regime                                | 10   |

| 1.3         | Switching ripple and pulsation of input and        |      |

|             | output currents                                    | 17   |

| 1.4         | Dynamic response of a switching converter;         |      |

|             | switching regulators                               | 22   |

| 1.5         | Generalized switching dc-to-dc converter           | 25   |

| 1.6         | Review                                             | 28   |

| GENERAL     | UNIFIED APPROACH TO MODELLING SWITCHING CONVERTERS | 31   |

| PART I      | CONTINUOUS CONDUCTION MODE                         | 31   |

| CHAPTER 2   | REVIEW OF THE NEW STATE-SPACE MODELLING TECHNIQUE  | 32   |

| 2.1         | Brief review of existing modelling techniques      | 33   |

| 2.2         | Proposed new state-space averaging approach        | 33   |

| 2.3         | New canonical circuit model                        | 37   |

| 2.4         | Extension to complete regulator treatment          | 39   |

| CHAPTER 3 | STATE-SPACE AVERAGING, HYBRID MODELLING AND          |     |

|-----------|------------------------------------------------------|-----|

|           | CIRCUIT AVERAGING                                    | 41  |

| 3.1       | State-space averaging                                | 41  |

| 3.2       | Hybrid modelling                                     | 55  |

| 3.3       | Circuit averaging                                    | 60  |

| CHAPTER 4 | CANONICAL CIRCUIT MODEL                              | 64  |

| 4.1       | Derivation of the canonical model through state-     |     |

|           | space                                                | 67  |

| 4.2       | Significance of the canonical circuit model and      |     |

|           | related generalizations                              | 75  |

| CHAPTER 5 | SWITCHING MODE REGULATOR MODELLING                   | 82  |

| 5.1       | Modulator stage modelling and complete regulator     |     |

|           | circuit model                                        | 84  |

| 5.2       | Analysis of switching-mode regulator                 | 86  |

| 5.3       | Input properties of switching regulators             | 88  |

| PART II   | DISCONTINUOUS CONDUCTION MODE                        | 91  |

| CHAPTER 6 | REVIEW OF THE NEW STATE-SPACE MODELLING TECHNIQUE    |     |

|           | IN THE DISCONTINUOUS CONDUCTION MODE                 | 92  |

| 6.1       | Brief review of existing modelling techniques        | 93  |

| 6.2       | New state-space and circuit averaging methods for    |     |

|           | switching converters in the discontinuous conduction |     |

|           | mode                                                 | 94  |

| 6.3       | New canonical circuit model for discontinuous        |     |

|           | conduction mode                                      | 100 |

|           | •••                                                  | Page |

|-----------|------------------------------------------------------|------|

| 6.4       | Extension to complete regulator treatment            | 101  |

| CHAPTER 7 | STATE-SPACE AVERAGING, HYBRID MODELLING AND          |      |

|           | CIRCUIT AVERAGING IN DISCONTINUOUS CONDUCTION MODE   | 105  |

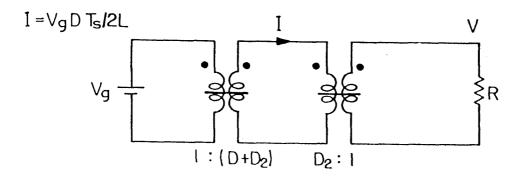

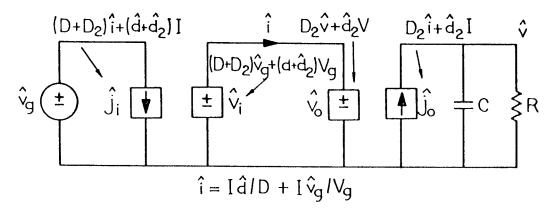

| 7.1       | State-space averaging                                | 105  |

| 7.2       | Hybrid modelling in the discontinuous conduction     |      |

|           | mode                                                 | 134  |

| 7.3       | Circuit averaging in the discontinuous conduction    |      |

|           | mode                                                 | 139  |

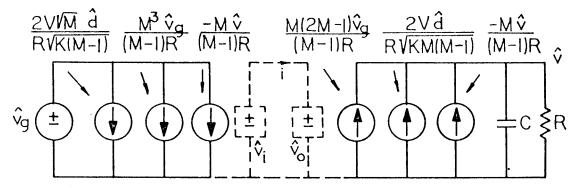

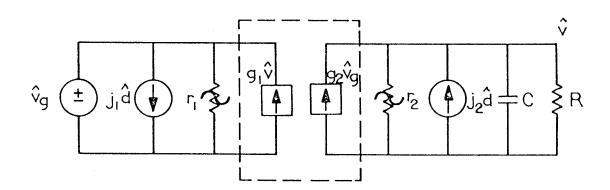

| CHAPTER 8 | CANONICAL CIRCUIT MODEL FOR DISCONTINUOUS CONDUCTION |      |

|           | MODE                                                 | 148  |

| 8.1       | Derivation of the canonical circuit models for       |      |

|           | discontinuous conduction mode                        | 149  |

| 8.2       | Summary of the canonical circuit model results for   |      |

|           | three common converters                              | 153  |

| 8.3       | Determination of the boundary between two            |      |

|           | conduction modes                                     | 157  |

| 8.4       | Experimental verification of the transfer properties | 162  |

| CHAPTER 9 | MODELLING OF SWITCHING REGULATOR IN DISCONTINUOUS    |      |

|           | CONDUCTION MODE                                      | 167  |

| 9.1       | Analysis of switching regulator in discontinuous     |      |

|           | conduction mode                                      | 169  |

| 9.2       | Input properties of switching regulators in          |      |

|           | discontinuous conduction mode                        | 171  |

|            |                                                      | Page |

|------------|------------------------------------------------------|------|

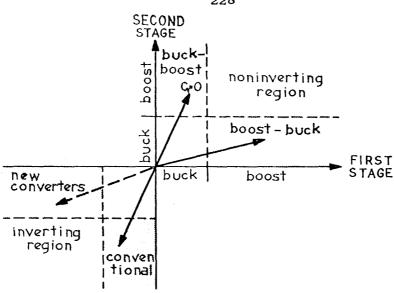

| GENERAL T  | HEORY AND DESIGN OF BUCK-BOOST CONVERTERS            | 176  |

| PART III   | CASCADE CONNECTION OF BUCK AND BOOST CONVERTERS      | 176  |

| CHAPTER 10 | GENERIC PROPERTIES OF CASCADE CONNECTIONS OF         |      |

|            | POWER STAGES                                         | 177  |

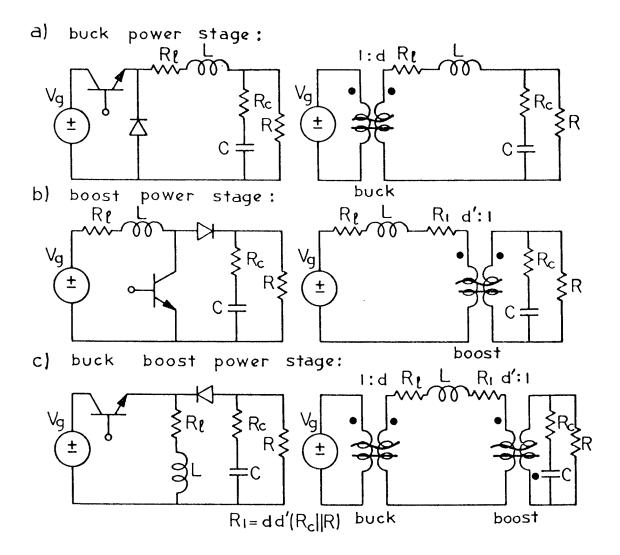

| 10.1       | Three common converters revisited                    | 179  |

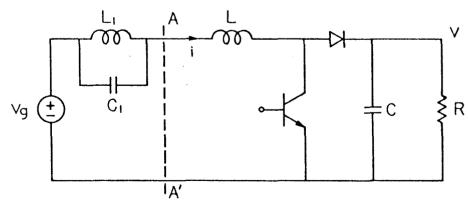

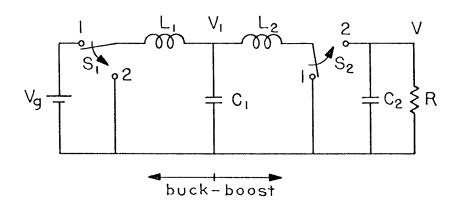

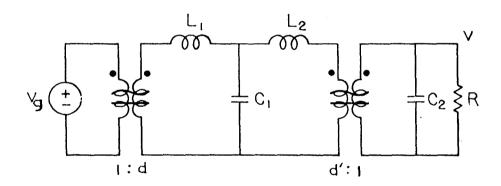

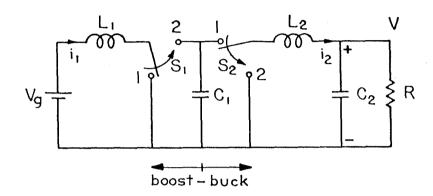

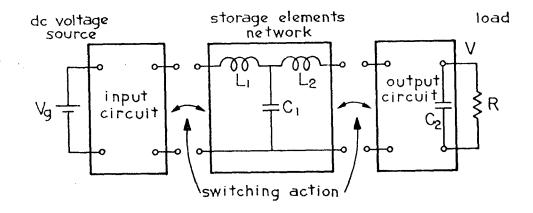

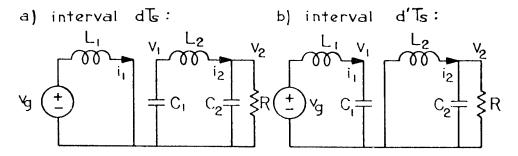

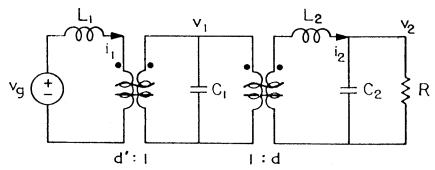

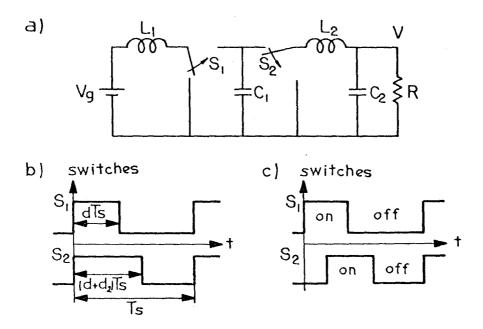

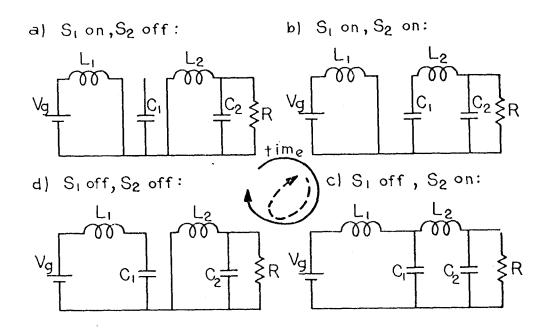

| 10.2       | Buck converter cascaded by a boost converter         | 181  |

| 10.3       | Boost converter cascaded by buck converter           | 189  |

| 10.4       | Energy transfer principles for general dc conversion | 192  |

| CHAPTER 11 | MODELLING AND EXPERIMENTAL VERIFICATION OF           | •    |

|            | CASCADED BOOST-BUCK CONVERTER                        | 196  |

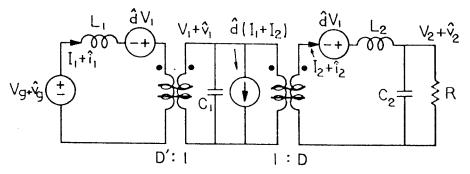

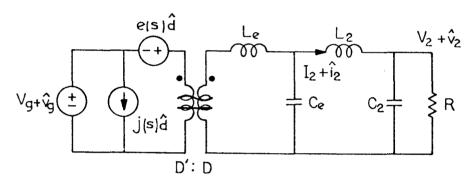

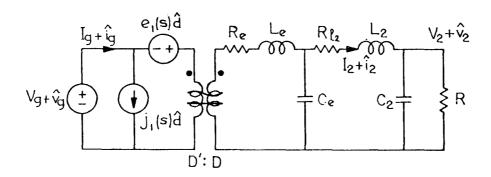

| 11.1       | Modelling of the boost-buck noninverting converter   | 197  |

| 11.2       | Experimental verification of the modelling           |      |

|            | predictions                                          | 206  |

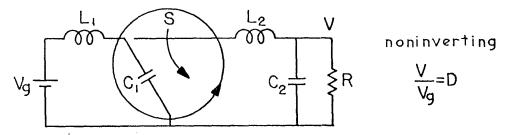

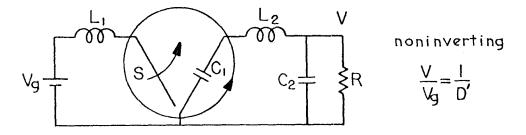

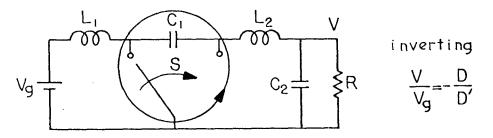

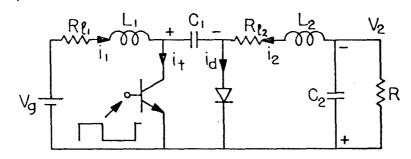

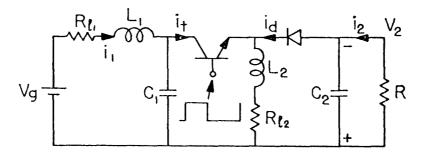

| PART IV    | NEW OPTIMUM TOPOLOGY SWITCHING CONVERTER             | 212  |

| CHAPTER 12 | DISCOVERY OF A NEW OPTIMUM TOPOLOGY SWITCHING        |      |

|            | CONVERTER                                            | 213  |

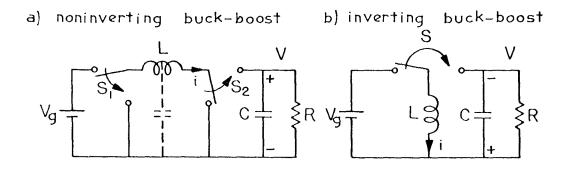

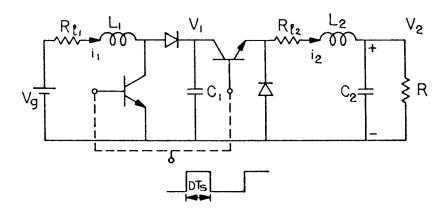

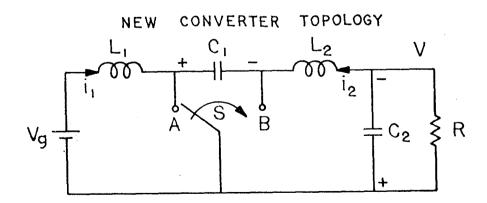

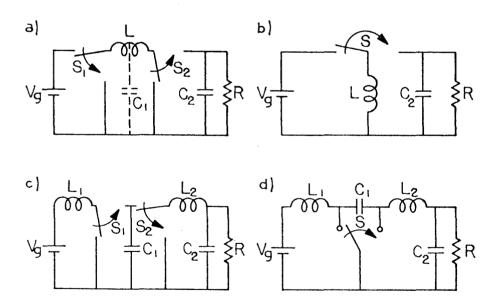

| 12.1       | Topological reduction of number of switches          | 215  |

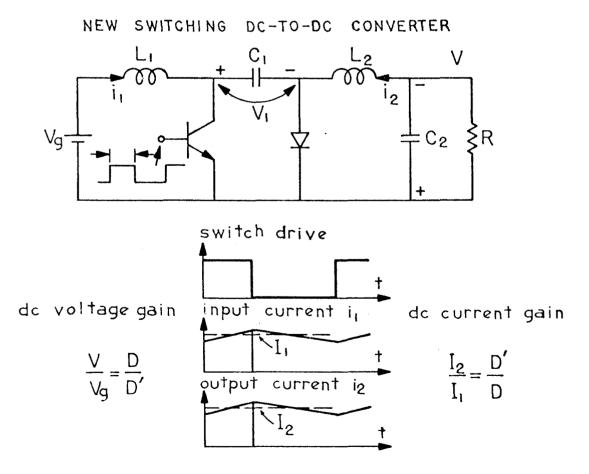

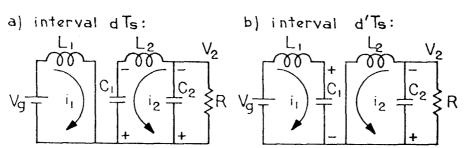

| 12.2       | Physical realization and basic operation of the      |      |

|            | new converter                                        | 220  |

| 12.3       | Advantages of the new optimum topology converter     | 223  |

| 12.4       | General theory of buck-boost converters              | 226  |

| 12.5       | Correlation among buck, boost and new converter      |      |

|            | topologies                                           | 229  |

|            | •                                                  | Page |

|------------|----------------------------------------------------|------|

| 12.6       | Modelling and experimental verification of the     |      |

|            | new converter                                      | 232  |

| CHAPTER 13 | COMPARISON OF THE NEW CONVERTER AND CONVENTIONAL   |      |

|            | BUCK-BOOST CONVERTER                               | 236  |

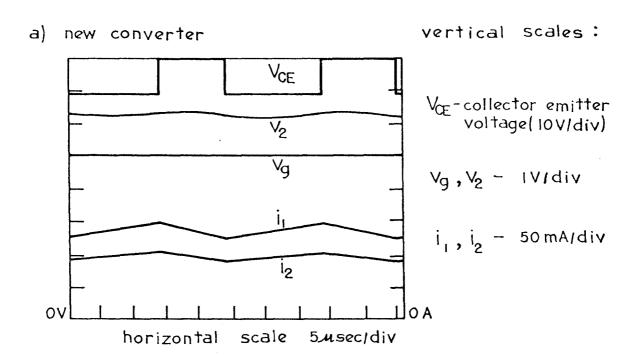

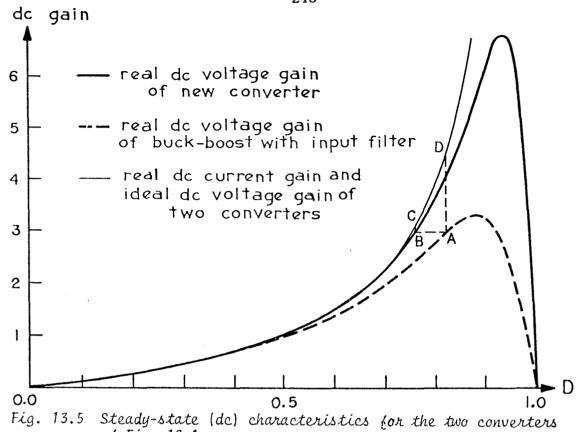

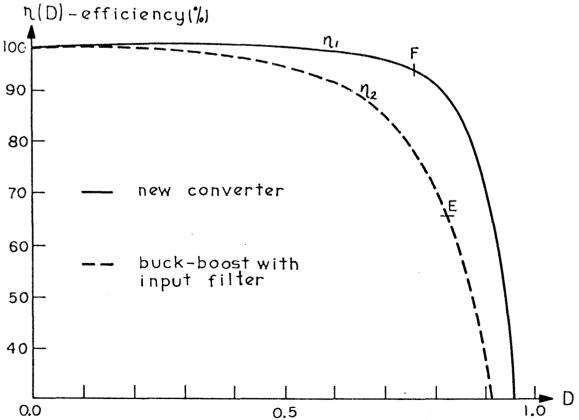

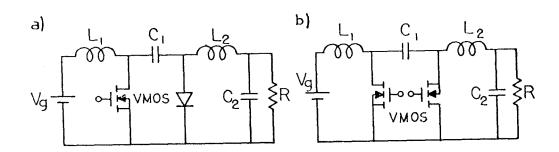

| 13.1       | Experimental test circuits of the two converters   | 237  |

| 13.2       | Switching ripple comparison                        | 238  |

| 13.3       | Comparison of the transistor and diode dc losses   |      |

|            | and transistor switching losses for the idealized  |      |

|            | case $(R_{\ell_1} = R_{\ell_2} = 0)$               | 242  |

| 13.4       | Comparison of the resistive dc losses only         | 246  |

| 13.5       | Real transistor and diode dc losses and transistor |      |

|            | switching losses ( $R_{ll}$ , $R_{l2} \neq 0$ )    | 249  |

| 13.6       | Comparison of ESR losses of the output capacitance | 250  |

| 13.7       | Size and weight reduction in the new converter     | 252  |

| 13.8       | Summary of the advantages of the new switching     |      |

|            | converter                                          | 253  |

| CHAPTER 14 | IMPLEMENTATION OF THE NEW SWITCHING CONVERTER      |      |

|            | AND FUTURE AREAS OF INVESTIGATIONS                 | 255  |

| 14.1       | Implementation of the new converter with VMOS      |      |

|            | power transistors                                  | 256  |

| 14.2       | Closed loop switching regulator implementing the   |      |

|            | new converter                                      | 257  |

.

|             | ^                                                  | Page |

|-------------|----------------------------------------------------|------|

| 14.3        | Discontinuous conduction mode in the new converter | 259  |

| 14.4        | Search toward new, innovative converter topologies | 260  |

| CONCLUSION  |                                                    | 262  |

| APPENDICES  |                                                    | 266  |

| APPENDIX A  | On the linear approximation of the fundamental     |      |

|             | matrix                                             | 269  |

| APPENDIX B  | The fundamental approximation in the state-space   |      |

|             | averaging approach                                 | 273  |

| APPENDIX C  | Derivation of the exact dc conditions and their    |      |

|             | simplification under linear approximation of the   |      |

|             | exponential matrices                               | 279  |

| APPENDIX D  | State-space averaging step extended to converters  |      |

|             | with multistructural (three or more) topological   |      |

|             | changes within each period                         | 288  |

| COMPUTER PR | ROGRAMS                                            | 295  |

| REFERENCES  |                                                    | 304  |

#### INTRODUCTION

The ever increasing demand of society for new and more abundant sources of energy, as well as for means of better and more efficient conversion to a medium suitable for widespread use such as electrical energy, has provided a healthy environment for the recent growth of the new, interdisciplinary field of Power Electronics. Functions to be performed by electronic power processing systems include a wide range, from efficient conversion of dc source voltage from one voltage to another, to inversion of dc to single-phase or multiple-phase ac, and controlled conversion of ac to dc. The applications also cover a wide spectrum, from a power supply in a hand-held calculator, through a variety of spacecraft systems including solar array and battery power conditioning, to industrial process control and electric utility bulk power inversion.

However, it comes as no surprise that this new field has offered some unmatched challenges owing to its unique combination of the three major disciplines of electrical engineering: electronics, power, and control. Classical signal processing electronics, coupled with the advent of semiconductor devices capable of handling substantial amounts of power, is used to control the power (or electrical energy) flow from some raw source of electrical energy (such as solar cells, for example), to the user (load). But in distinction with signal-processing electronics, where the power efficiency is of minor concern, here, as in classical power systems, it becomes the major issue, owing to the relatively large amounts of power involved. Power

efficiency makes mandatory the use of control devices, such as transistors and SCR's (silicon controlled rectifiers) in a repetitive switching mode, thus further increasing the problems of modelling the dynamic behavior of power switching circuits because of their inherent <u>nonlinear</u> nature. In addition, in many instances, the power conversion or inversion function is coupled with a requirement for regulation, and <u>stability</u> problems naturally arise because the self-correcting feature is usually obtained by employing <u>electronic</u> <u>feedback</u> in a closed-loop system. It is in this context particularly that a fusion of viewpoints of the power, control, and electronics disciplines is most necessary and also potentially fruitful.

However, the bringing together of these disciplines in order to achieve the general understanding and consequent innovation in power processing electronics systems is not merely their accumulation, but rather requires a revised look at their specific interrelations from the component to the system level. For example, a signal-processing electronics engineer usually thinks in terms of active devices used in either linear or switching mode together with resistors and capacitors; he avoids inductors and transformers. On the other hand, a power-processing electronics engineer must think in terms of active devices used in the switching mode together with capacitors, inductors, and transformers; he must avoid resistors in the interest of maintaining high efficiency in the power path. This important distinction requires a different way of thinking about circuit function realization. From the system point of view, one has only to recognize, for example, a dc-to-dc switching regulator as a dc, wide-band, nonlinear

sampled-data control system (with the ever-present high-efficiency constraint), to appreciate the challenge of bringing together these various disciplines.

Hence, the area of <u>modelling</u> and <u>analysis</u> of power processing systems, owing to their inherent nonlinear nature, becomes an even more challenging task, particularly in view of the lack of adequate analysis tools at the disposal of the circuit designer working in this field. In connection with that, the choice of parameter values in already existing circuit topologies, as well as the <u>design</u> of new circuit topologies is likewise a very difficult one.

The major thrust and purpose of this work is to provide the circuit designer with analytical tools which are accurate enough for practical purposes, yet simple enough to apply to give him powerful tools for design-oriented analysis in one of the major areas of electronic power processing: <a href="majorsize:switching-dc-to-dc-converters-and/or-regulators">switching-dc-to-dc-converters-and/or-regulators</a>. In addition, this analysis through appropriate linear circuit models provides the necessary insight which may lead to innovative converter topologies, offering better and near optimum performance.

The structure of this work has been divided into two distinct yet firmly interconnected major divisions: general unified approach to modelling and analysis of switching dc-to-dc converters, presented in Parts I and II, and design of new converter topologies presented in Parts III and IV, which has been directly made possible by the insights gained from the analysis methods of Parts I and II. Chapter 1, which is placed outside and in front of these four parts, is

intended to familiarize the reader with the basic switching conversion concepts and at the same time to introduce both the analysis difficulties as well as to designate the possible areas of performance improvements in switching converter design.

The principal objective of the work on modelling and analysis of dc-to-dc converters and regulators (Parts I and II) is to obtain a linear model (either through <a href="state-space">state-space</a> or <a href="linear circuit">linear circuit</a> description), subject to appropraite restrictions, for the inherently nonlinear power stage in which the dc conversion is accomplished. Such converters operate in one of two modes: a two-state mode referred to as the "continuous conduction mode," in which inductor currents do not fall to zero (as modelled in Part I), and a three-state mode, "discontinuous conduction," in which an inductor current falls to zero (Part II).

The culmination of this work is a canonical circuit model for a dc-to-dc converter in the continuous conduction mode which properly represents both the line and duty ratio transfer functions and also, for the first time, correctly represents the converter input impedance. The principal advantage of the canonical model is that it represents any such converter regardless of its detailed configuration.

The corresponding canonical circuit model for a dc-to-dc converter in the discontinuous conduction mode is obtained in Part II, which not only confirms that the line and duty ratio transfer functions become first-order, in contrast to the second-order functions of the continuous conduction case, but also for the first time correctly represents the input impedance.

Both canonical models are made possible by a powerful technique called <a href="state-space">state-space</a> averaging developed in both Parts I and II, which unifies and places in perspective what had previously been considered distinct analytic methods.

The insights gained by the <u>state-space averaging approach</u> of Part I and Part II leads in Part III to the study of the generic properties of a new class of buck-boost converters obtained by cascade connection of basic buck and boost converters.

Finally, this study culminates in Part IV in the discovery of a new switching converter based upon capacitive rather than the usual inductive energy transfer. The new converter is shown to have substantial advantages over conventional converters in efficiency, performance and also in size and weight.

#### CHAPTER 1

#### SWITCHING DC-TO-DC CONVERTERS

#### AND REGULATORS

In this introductory chapter several common switching dc-to-dc converters are introduced and their physical operation briefly explained. The basic property, dc-to-dc voltage and current level conversion, is arrived at following some simplified arguments based on fundamental physical laws in order to familiarize the reader with some of the basic quantitative relationships.

Upon this initial exposure to the nature of the problems associated with the analysis of these essentially nonlinear circuits; the general, unified, and complete method of modelling and analysis of any switching dc-to-dc converters (even those yet to be invented) developed and presented in chapters to follow will be more easily grasped.

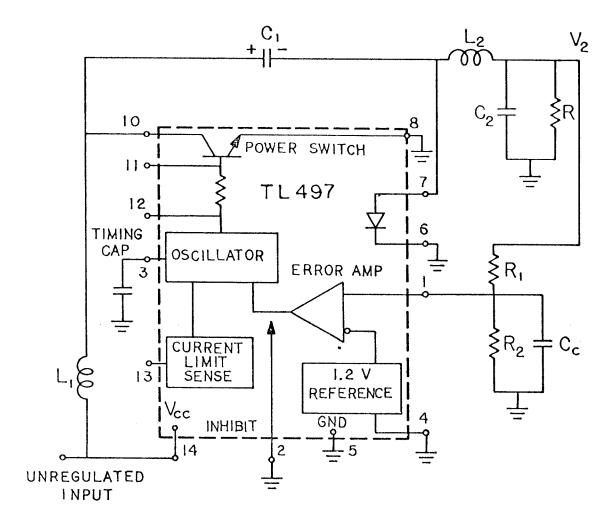

### 1.1 Physical operation and basic properties of switching converters

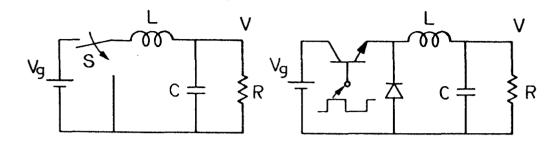

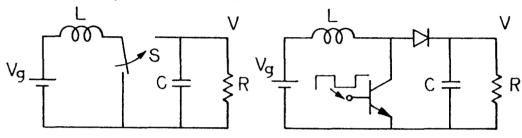

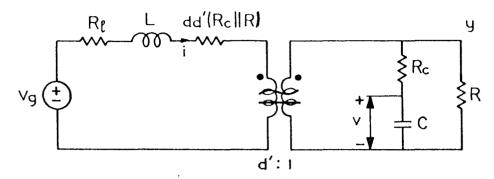

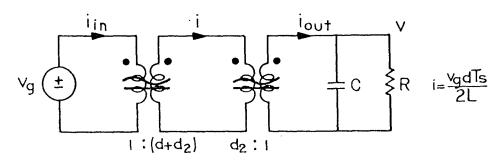

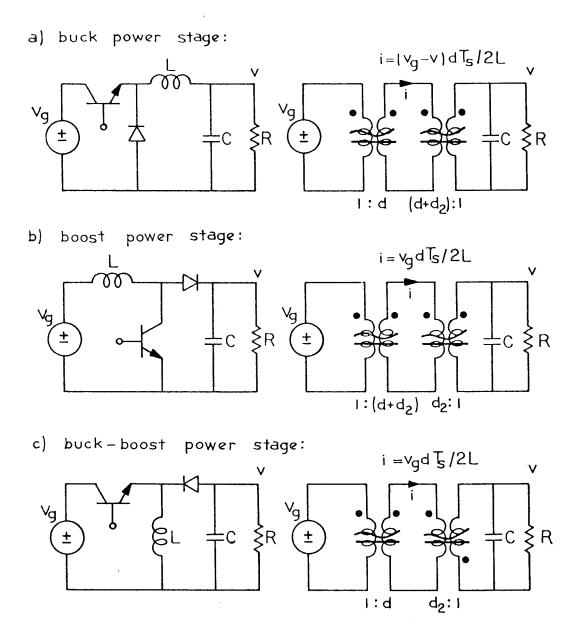

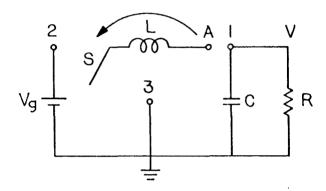

We begin with the three common switching converters (also called power stages because of their power handling capability) depicted in Fig. 1.1. While in Fig. 1.1a the topological structure of these converters independent of any particular switch realization is shown, in Fig. 1.1b a bipolar transistor, commutating diode realization of the single-pole double-throw switch S is used. It is also evident from Fig. 1.1b that transistors are used in their switching mode: either fully turned on (corresponding to the position

boost power stage:

buck - boost power stage:

Fig. 1.1 Three common switching dc-to-dc converters:

a) topological configuration independent of switch realization b) bipolar transistor implementation of the switch S.

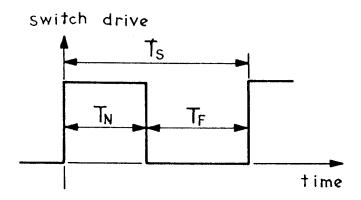

of switch S in Fig. 1.1a) or fully off (the other position of switch S). This is obtained by bringing a periodic switch drive signal as shown in Fig. 1.2 to the base of the transistor. The frequency of repetition of this signal is defined as the switching frequency  $f_s = 1/T_s$ , and for discussion purposes will be considered constant. The fraction of the complete period  $T_s$  for which the transistor is on is defined as the steady state duty ratio  $D = T_N/T_s$ . The diode in

each converter acts as a switch automatically synchronous with the transistor. That is, when the transistor is on, the diode is reverse biased and effectively off; as soon as the transistor becomes off, the diode is forced to conduct by the continuous inductor current, and stays on as long as there is a positive inductor current.

Fig. 1.2 Definition of the periodic switch drive.

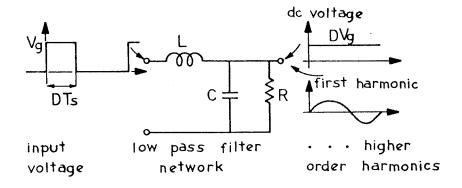

Consider now more closely the simplest of these converters, the buck power stage (sometimes called the step-down or chopper converter because of its property of reducing the input dc voltage). With assumption of ideal transistor and diode switches, the buck power stage can be equivalently represented as in Fig. 1.3.

Fig. 1.3 Basic dc conversion function of buck power stage viewed through harmonic decomposition and principle of superposition.

Fourier harmonic decomposition of the periodic input voltage and the principle of superposition show that the output voltage consists of a dc voltage V = DV $_g$  and ac harmonics with fundamental at the switching frequency  $f_s$ . If the low-pass filter elements are chosen such that its corner frequency  $f_c = 1/(2\pi\sqrt{LC})$  is much smaller than the switching frequency  $f_s$  ( $f_c << f_s$ ), all harmonics are substantially attenuated leading to very small output voltage ripple. Hence, even though present, the output voltage ripple can be reduced to an arbitrarily small value by proper choice of filter elements.

A significant feature of the switching converter is that a  $\frac{\text{degree of control}}{\text{degree of control}}$  over the output dc voltage has been introduced through its dependence on the duty ratio D. Therefore, simply by varying the switch drive duty ratio one is able to change the output dc voltage. Also, since by definition  $0 \le D \le 1$ , it is apparent that the buck power stage is capable only of reducing the dc input voltage level.

Another very important property of the converter is immediately apparent. For a properly designed filter, the ripple voltage is negligible, and the output current is dc current only  $I_{out} = V/R$ . However, input current flows only during the interval when the transistor is on, and hence  $I_{in} = DI_{out}$ . Therefore, the efficiency of the converter in this ideal case is 100% since

$$\frac{P_{\text{out}}}{P_{\text{in}}} = \frac{VI_{\text{out}}}{V_{\text{g}}I_{\text{in}}} = D \frac{1}{D} = 1$$

The key to this ideal 100% efficiency is in the fact that the control device, the transistor, is used in the switching mode, unlike its

use in a linear regulator as a linear dissipative element or variable resistance. However, in reality the voltage across a real transistor when it is turned on is not zero as for ideal switch S, but its saturation voltage  $V_{\text{CEsat}}$  is usually 0.3V-IV. Likewise, the diode has some forward voltage drop of the same order which also slightly degrades the efficiency of a real converter. Nevertheless these losses are negligible in comparison with losses present in a linear regulator.

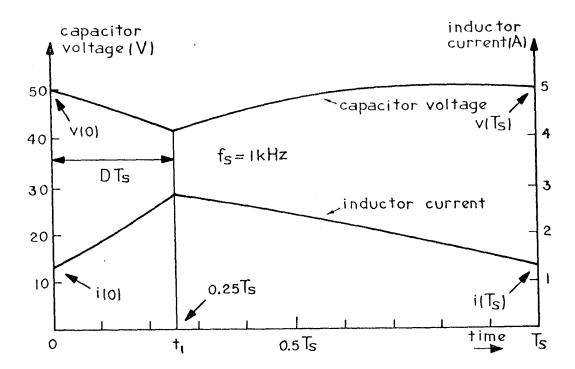

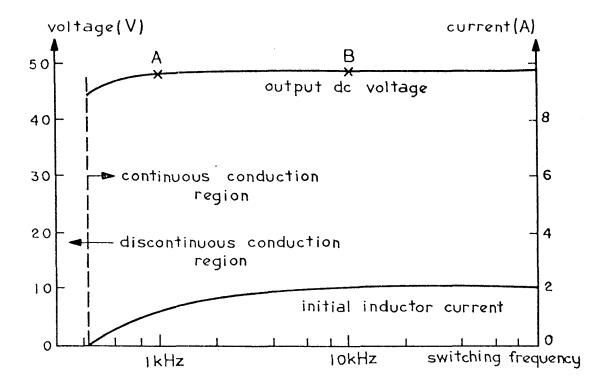

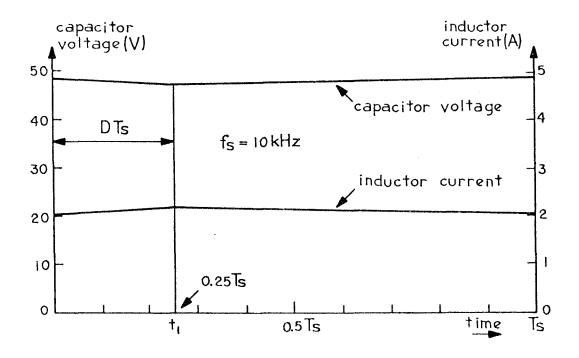

# 1.2 Two operating modes and their dc relations in the steady-state regime

So far two important characteristics of switching converters have been established: a degree of control through duty ratio drive D, and high efficiency of operation. There are, however, some other features peculiar to these converters which, even though present, are not so clearly displayed in the buck power stage example. Let us therefore consider the buck-boost converter, in which these additional features are most visible.

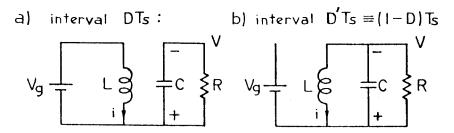

For the two positions of the switch S in the buck-boost converter of Fig. 1.1, the two switched network configurations shown in Fig. 1.4 are obtained, from which it is clear that a <u>topological structural</u> <u>change</u> occurs within each period and the <u>circuit configuration</u> is changed periodically from that of Fig. 1.4a to that of Fig. 1.4b. Both switched networks in Fig. 1.4 are <u>linear</u> by themselves, but it is due to this periodic structural change that the converter itself is a nonlinear circuit. It is exactly here where the difficulty in modelling and analysis of these converters arises.

Fig. 1.4 Two switched networks for the buck-boost converter operating in the continuous conduction mode.

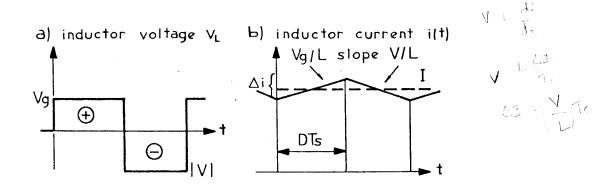

Another interesting observation about the role of the inductance can be made: it acts as an energy transferring device between input source voltage  $V_g$  and output load R, by accumulating the energy in the form of a magnetic field during the first interval  $T_sD$  and then releasing it to the load during the subsequent interval  $T_sD$ , thus charging the output capacitor negatively as shown in Fig. 1.4b. With assumption of LC filter values properly chosen for low (negligible) output voltage ripple, the inductor voltage and current waveforms in this steady state, so called "continuous conduction mode", are as shown in Fig. 1.5.

Fig. 1.5 Energy storage inductor steady-state waveforms in the continuous conduction mode.

The continuous conduction mode refers to operating conditions and converter parameter values for which the instantaneous inductor current does not fall to zero at any time during the switching cycle, as shown in Fig. 1.5b. This is directly connected with the existence of only two switched networks during each cycle, as was shown in Fig. 1.4.

Let us now find for this operating mode the static conditions, that is, the dc voltage and current level conversion relations in the steady state regime. Here "steady state regime" signifies the fact that the duty ratio D is held constant over a sequence of switching cycles, thus leading to the current and voltage periodicity requirements:

steady

$$i(0) = i(T_S)$$

for inductor current

state  $v(0) = v(T_S)$  for capacitor voltage

Then, from Faraday's law

$$\int_{0}^{T} v_{L}(t)dt = L \int_{i(0)} di = L[i(T_{S}) - i(0)] = 0$$

(1.1)

in steady state. Evaluation of the integral on left with help of Fig. 5a gives

$$V_g DT_S + V(1-D)T_S = 0$$

or

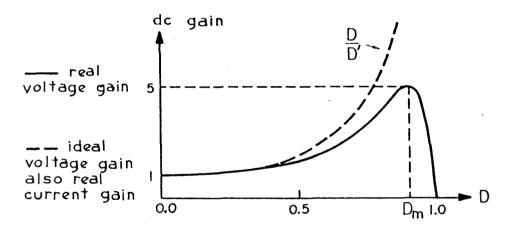

$$\frac{V}{V_g} = -\frac{D}{1-D}$$

(1.2)

which is the ideal dc voltage gain for the buck-boost converter.

It is now obvious that the buck-boost power stage is capable of producing a dc output voltage which is either smaller (for D < 0.5) or larger (for D > 0.5) than the input voltage, and hence realizes

a general dc conversion function. Since none of the lossy elements has been accounted for, the dc current gain in this ideal 100% efficient case would be  $I_{out}/I_{in} = D^i/D$ .

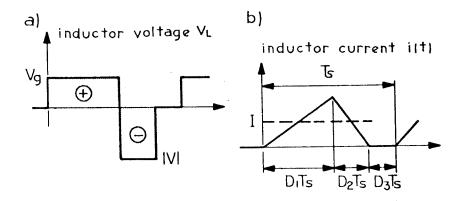

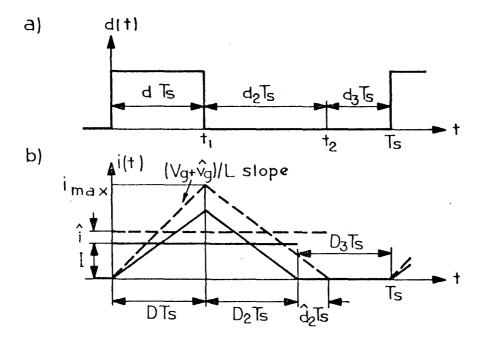

Consider now the case in which the energy stored in the inductor during the first interval  $T_SD_1 \equiv T_SD$  is completely released to the output load before the switching cycle  $T_S$  has ended, causing the inductor current to become zero for the last portion of the period  $T_S$ . This could happen if the switching period—has been sufficiently increased, or if the inductance has been substantially reduced and hence it has shortened the time interval necessary to release energy to the output. Even if neither change has occurred, but instead the load resistance R is increased sufficiently to cause lowering of the average inductor current I shown on Fig. 1.5b to the point where  $i(0) = i(T_S) = 0$ , the instantaneous inductor current becomes as shown in Fig. 1.6b. The converter is thus operating in the so-called "discontinuous conduction mode," in which the name clearly originates from the discontinuous inductor current waveform in Fig. 1.6b.

Fig. 1.6 Steady-state inductor waveforms in the discontinuous conduction mode.

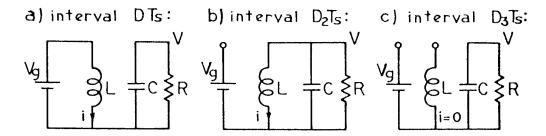

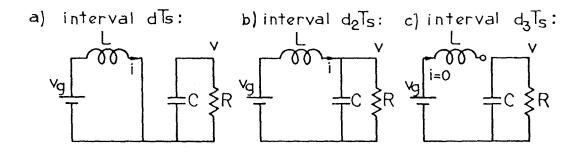

The immediate consequence of operation in the discontinuous conduction mode is that there are <u>three</u> different switched network configurations inside each switching period  $T_S$  as shown in Fig. 1.7.

Fig. 1.7 Three switched networks for the buck-boost converter operating in the discontinuous conduction mode:

a) transistor on, diode off, b) transistor off, diode on, c) transistor off, diode off.

At the end of the second interval  ${}^T_s {}^D_2$ , the energy stored on the inductor has been completely released to the load and inductor current vanishes. Hence, the inductor voltage becomes zero which causes the diode to become reverse biased and hence nonconducting for the last interval  ${}^T_s {}^D_3$ , for which interval the third switched network topology shown in Fig. 1.7c is formed. As for the continuous conduction mode topological structural changes—take place within each period, but for the discontinuous conduction mode the changes are among three different switched network topologies as displayed in Fig. 1.7.

It is important to emphasize that the two properties described above for the buck-boost converter example -- inductive energy transfer principle and two modes of operation -- are not restricted to this particular example but are general in nature. They are applicable not only to the other two converters shown in Fig. 1.1 but also to any switching converter so far known.

Let us now, however, complete the comparison between the two modes of operation for the buck-boost converter example. The steady state dc voltage conversion ratio might be found as before by use of Faraday's law and Fig. 1.6a as:

or

$$V_g DT_s + VD_2 T_s = 0$$

$$\frac{V_g}{V_g} = -\frac{D}{D_2}$$

(1.3)

However, the interval  $D_2T_s$ , which determines how deep in the discontinuous conduction mode the converter is operating, is yet to be determined. This can be accomplished by finding an alternative relation for the dc voltage ratio, based upon the 100% efficiency property of the ideal converter. From Fig. 1.6b,  $I_{in} = DI = D^2V_gT_s/2L$  and so  $P_{in} = V_gI_{in} = D^2V_g^2T_s/2L$ ; then,  $P_{out} = V_g^2/R$  so from  $P_{in} = P_{out}$

$$D^{2} \frac{v_{g}^{2}}{2L} T_{s} = \frac{v^{2}}{R}$$

which leads to

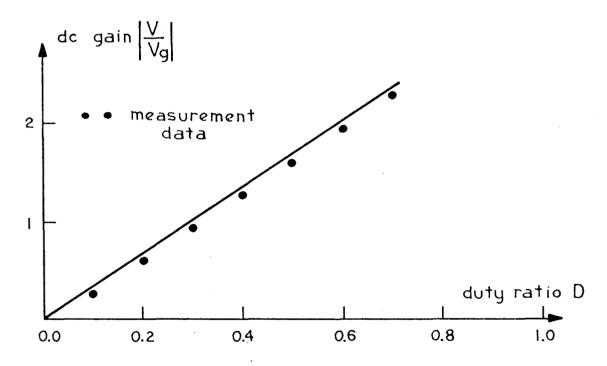

$$\left|\frac{V}{V_{\mathbf{q}}}\right| = \sqrt{\frac{TR}{2L}} D \tag{1.4}$$

V Vy

or

$$\left| \frac{V}{V_g} \right| = \frac{D}{\sqrt{K}}$$

where

$$K = \frac{2L}{R} f_s$$

Comparison between (1.3) and (1.4) gives immediately

$$D_2 = \sqrt{K} \tag{1.5}$$

so that the dimensionless parameter K determines then the length of

the second interval  $D_2T_s$ . It is interesting to note that the second interval  $D_2$  is determined solely by K so that, for a given converter the second interval is a constant affected only by the load resistance R. This is not true for the buck or the boost converter, in which the second interval is dependent not only upon K but also upon the duty ratio D.

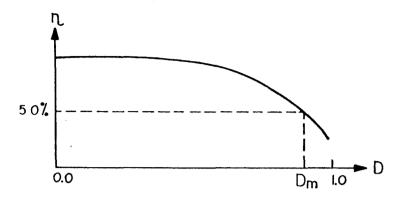

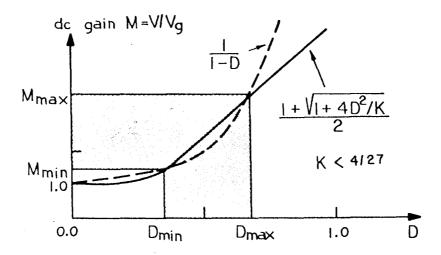

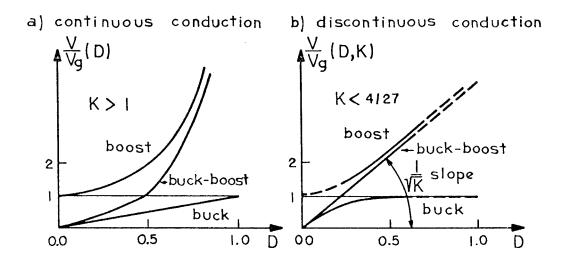

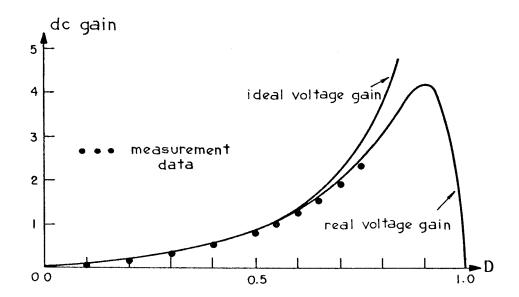

For the buck-boost converter, comparison between (1.2) and (1.4) shows that in the continuous conduction mode the dc gain is a highly nonlinear function of duty ratio D only (1.2), while in the discontinuous conduction mode it is a linear function of duty ratio D but also dependent on the dimensionless parameter K (1.4).

The boundary between the two modes of operation is easily found from Fig. 1.6b as:

$$D_3 = 0 \Rightarrow D_2 = 1 - D \Rightarrow D' = \sqrt{K}$$

(1.6)

Furthermore, a criterion to determine in which of the two modes the converter is operating can be established in the form of an inequality relationship among circuit parameter values L,R switching frequency  $f_s$ , and duty ratio D of the switching drive as follows:

### continuous conduction mode

$$D' < \sqrt{K}$$

(1.7)

# discontinuous conduction mode

where  $K = 2L/RT_S$  is a dimensionless parameter.

For instance, when  $K \ge 1$  the converter will <u>always</u> be operating in the continuous conduction mode regardless of the control--duty

ratio D, while for K < 1 it will operate in the discontinuous conduction mode for D < 1 -  $\sqrt{K}$ .

To illustrate this with a numerical example, let L = lmH,  $f_s = 10 \text{kHz}$ , and  $R = 10 \Omega$ . Then, K = 2 and the converter will always operate in the continuous conduction mode. However, if the load resistance is increased to  $R = 100 \Omega$ , K = 0.2 and the converter will operate in the discontinuous conduction mode for D < 0.553. This example also justifies why the continuous conduction mode is sometimes also called "heavy mode" (low resistance R and heavy loading) while the discontinuous conduction mode is referred to as "light mode" (higher resistance R and therefore light loading).

# 1.3 Switching ripple and pulsation of input and output currents

Now that the two distinct modes of operation of switching dc-to-dc converters have been clearly distinguished, the physical origin of their appearance understood and the quantitative measure describing the transition between two modes of conduction correlated with circuit physical parameters, we can proceed to expose some of the undesirable features inherent in the switching converters of Fig. 1.1 in both conduction modes.

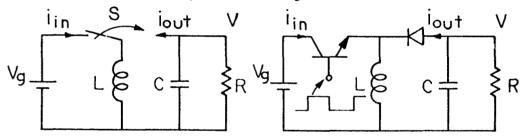

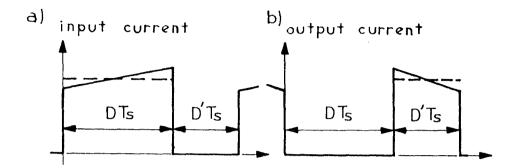

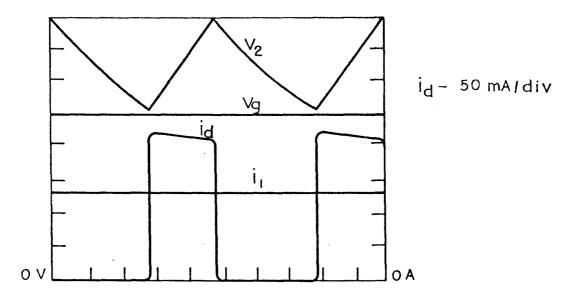

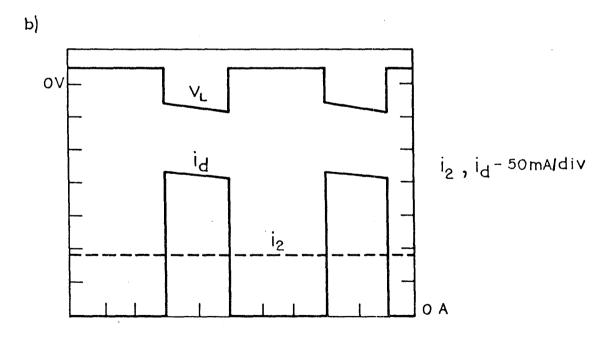

Consider now both input and output currents (designated i<sub>in</sub> and i<sub>out</sub> in Fig. 1.1) for the buck-boost converter in the continuous conduction mode. Even though the converter is operating in the continuous conduction mode, owing to the switching action of the transistor and diode, both currents are as illustrated in Fig. 1.8.

Fig. 1.8 Input and output current of the buck-boost converter operating in the continuous conduction mode.

It can easily be verified that the buck converter has the same pulsating <u>input current</u> as shown in Fig. 1.8a. This invariably requires that an input filter (usually a single-section low-pass L,C filter) be put in front of these two converters to smooth out the substantial current ripple component at the switching frequency drawn from the line supply. That way, electromagnetic interference (EMI) problems generated by the abrupt variation in energy flow (pulsating current) are reduced, and contamination of the environment by the undesired electromagnetic disturbances alleviated.

On the other hand, the boost converter of Fig. 1.1 has the same pulsating output current, as the buck-boost converter in Fig. 1.8b, which is primarily responsible for the much higher output voltage ripple of these two converters compared to the buck power stage with the same storage element values and operating conditions (switching frequency  $f_s$ , duty ratio D, and continuous conduction mode). The smaller voltage ripple in the buck power stage is a consequence of the nonpulsating output current (similar to that shown in Fig. 1.5a) with very small current ripple  $\Delta i_{out}$  which can easily be found as

$$\Delta i_{out} = \frac{V}{L} D'T \qquad (1.8)$$

Consequently, the output voltage ripple  $\Delta v$  is obtained from

$$\Delta v(peak-to-peak) = \frac{\Delta i_{out}}{8f_sC} = \frac{VD'}{8L Cf_s^2}$$

(1.9)

and the relative output voltage ripple  $\Delta v/V$  is:

$$\frac{\Delta V}{V} = \frac{\pi^2}{2} D' \left(\frac{f_c}{f_s}\right)^2 \tag{1.10}$$

where

$$f_c = \frac{1}{2\pi\sqrt{LC}}$$

Here  $f_c$  is the corner frequency of the low-pass filter formed by L and C. Since the ultimate requirement of the dc-to-dc converter is to provide dc level change and output dc voltage only, this poses a restriction on the choice of filter elements. Namely, from (1.10) output voltage ripple will be negligible if the following requirements are satisfied:

$$f_{c} \ll f_{s}$$

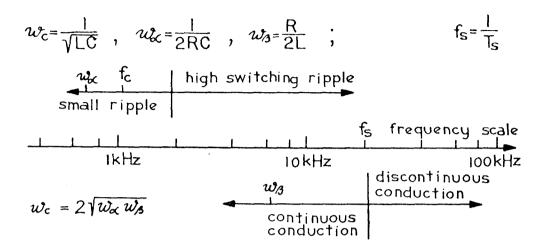

$f_{c} = 1/2\pi\sqrt{LC}$  where  $G_{c} = 1/2\pi\sqrt{LC}$  (1.11)  $G_{c} \ll f_{s}$   $G_{c} = 1/2RC$

The second inequality condition in (1.11) comes from requirement of negligible output voltage change during the interval  $T_sD$  (see Fig. 1.4a) when capacitance C discharges into load R.

As a numerical illustration for the typical parameter values, in continuous conduction mode, L = 6mH, C =  $40\mu F$ ,  $f_s$  = 20kHz,

R = 60 , we obtain  $f_c$  = 330Hz,  $\omega_\alpha$  = 21Hz and inequalitites (1.11) are well satisfied. Hence from (1.10)  $\Delta v/V \sim (f_c/f_s)^2 \sim 10^{-4}$  or the output voltage ripple is of the order of 0.01% for the buck converter.

For the same element values but for the buck-boost converter, since the output current ripple is now from Fig. 1.8b,  $\Delta i_{out} = I_{load} = V/R$ , the output voltage ripple becomes load current dependent and is:

$$\Delta v = D \frac{I_{load}}{f_s C} \Rightarrow \frac{\Delta v}{V} = D \frac{1/RC}{f_s}$$

(1.12)

or of the order of several percents for the given numerical example.

A similar result is obtained for the boost converter.

Hence for the two converters with <u>pulsating output current</u>, almost two order of magnitudes higher voltage ripple is obtained. It could be reduced to an acceptable level by increase of capacitance C or by increase of the switching frequency  $f_s$ ; in that case, however, the fundamental requirement (1.11) for low output voltage ripple would be even better satisfied than for the buck converter example.

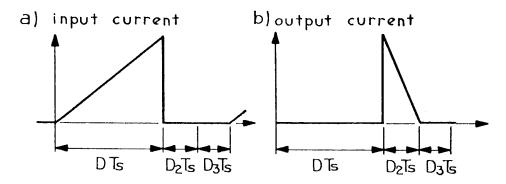

It is now no surprise that both EMI and output voltage ripple would be further degraded in the <u>discontinuous conduction mode</u>, since then both input and output current become even more pulsating, as illustrated for the buck-boost converter in Fig. 1.9.

Suppose that the transition to the discontinuous conduction mode is made by significantly lowering the inductance from that used in the continuous conduction mode. Highly impulsive current in Fig. 1.9b would then cause an intolerable output voltage ripple, unless either

Fig. 1.9 Input and output current of the buck-boost converter operating in the discontinuous conduction mode.

the output capacitance C or switching frequency is increased, or both. In any case this has the consequence that the fundamental "small-ripple" restrictions for the "natural frequencies,"  $f_{\rm C} << f_{\rm S}$  and  $\omega_{\alpha} << f_{\rm S}$ , would be even better satisfied. As an example, for the typical set of values in the discontinuous conduction mode L = 60µH, C = 400µF,  $f_{\rm S}$  = 100kHz, R = 60 $\Omega$  we get  $f_{\rm C} \simeq 1.02$ kHz and  $\omega_{\alpha} \simeq 2$ Hz, thus satisfying inequalities (1.11) to a high degree. In essence, one recognizes that the burden of filtering out the switching ripple has been shifted from an equal share among inductance and capacitance in the continuous conduction mode completely to the capacitance in the discontinuous conduction mode. The inductance has retained only its energy transferring property but has lost its filtering property.

We therefore emphasize at this point the importance of the simple inequality requirements (1.11) placed as restrictions on the choice of parameter values in order to reduce the switching ripple inherent in all these converters to an acceptable level. When these relationships are properly recognized and incorporated in the model-

ling procedure a tremendous simplification of the analysis is obtained, and yet the derived results are accurate enough for all practical purposes. They are also the underlying basis of the general unified approach to modelling and analysis of switching converters which will be presented in Part I and Part II.

Besides having its importance and implication on the theoretical modelling procedure devised later, the relation (1.11) in conjunction with, for example, (1.10) exposes yet another interesting feature of switching dc-to-dc converters -- reduction of size and weight. Simple increase of switching frequency  $f_s$  would allow proportional increase of corner frequency  $f_c$  while still retaining the same switching ripple. Hence, the inductance and capacitance could be chosen smaller in value and size. However, this would not be achieved without a cost; increase in switching frequency would degrade the efficiency of the converter owing to increase in "switching losses," which become pronounced when the switching transistor rise and fall times become a substantial part of the switching period. The efficiency of conversion and quality of the switching transistor would pose the upper bound on the switching frequency.

# 1.4 Dynamic response of a switching converter; switching regulators

So far we have demonstrated only the steady state or <u>static</u> characteristics of switching converters. They would, of course, be sufficient to characterize the converter if it were used in an <u>open</u> loop fashion, namely, if the converter were used alone for voltage

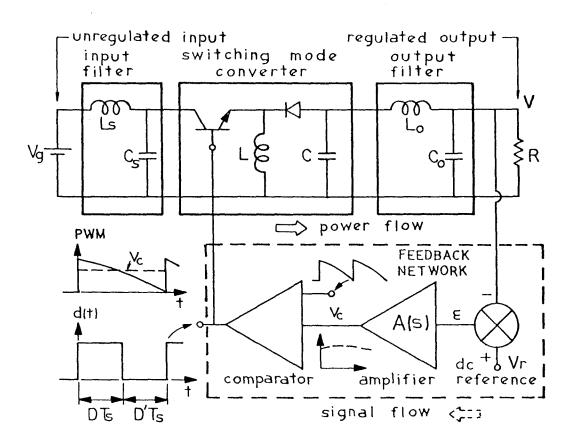

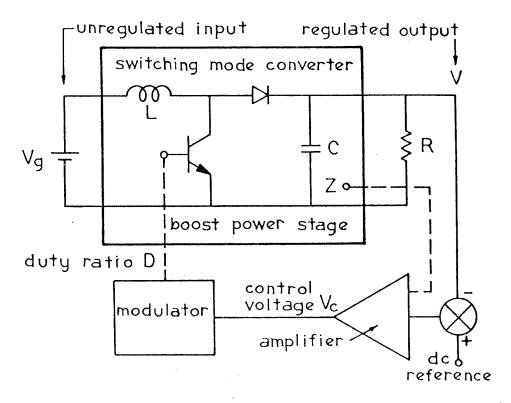

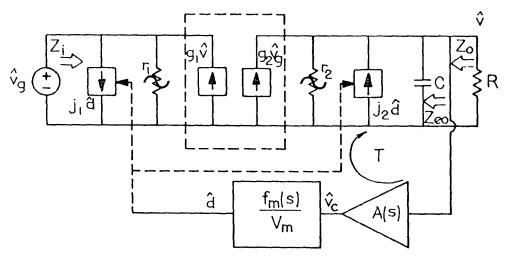

level conversion by setting the transistor steady state duty ratio externally at some predetermined value. However, quite often the primary source of energy is unregulated and could have a wide range of voltage variation; on the other hand, a typical requirement is that the voltage (or sometimes current) supplied at the output to a user (some other electronic or electrical equipment) be maintained constant over a wide range of loading conditions. This is naturally achieved by the application of negative feedback in a closed-loop configuration, such as that shown in Fig. 1.10 depicting a typical switching regulator.

Fig. 1.10 Switching regulator: closed-loop implementation of the switching dc-to-dc converter.

For concreteness, the switching mode converter is represented by a buck-boost power stage, and the input and possible additional output filter are incorporated to smooth out the pulsating input and output currents as discussed before. Also a particular type of pulse width modulator (PWM) is used in which the on-off signal to the switch is produced by comparison of a sawtooth clocked waveform with the feedback signal as illustrated in Fig. 1.10 and sometimes referred to as a single-edge clocked pulse-width modulator.

As seen from Fig. 1.10 the error  $\epsilon$  between the regulator output v and reference  $v_r$  is amplified (and possibly compensated) to produce an analog control signal  $v_c$  which further changes the duty ratio of the digital on-off signal d(t) as necessary to maintain a constant output voltage regardless of any source and load variations. However, as in all feedback systems, careful investigation of the closed loop is required to determine <u>stability</u> and <u>dynamic response</u>. For small-signal analysis, the problem of loop gain determination can be broken down into two parts: first, find how small-signal variations  $\hat{v}_g$  and  $\hat{d}$  superimposed upon the steady state, or dc, inputs  $v_g$  and D to the converter alone determine a small-signal converter output  $\hat{v}$  superimposed on its steady state value V; and second, determine how this perturbation  $\hat{v}$  is propagated through the feedback network to form a self-correcting modulation drive  $\hat{d}$ . The first problem of establishing the dynamic response of the power processing part, the

switching mode converter itself, is a very challenging problem owing to inherently nonlinear behavior of the converter, and will be thoroughly dealt with in remaining chapters. The second problem of modelling the dynamic behavior of the signal processing part, containing the modulator stage, will also be touched upon later, and hence the small-signal linear model of the complete closed loop switching regulator obtained.

Finally let us make the following simplifying observation. Even though a switching converter is nonlinear, and hence a sinusoidal test signal (such as  $\hat{v}_g$ ) would produce a number of harmonics, all higher order harmonics may be neglected since the nonlinearity is followed by a very effective low-pass filter which attenuates them substantially with respect to the fundamental. This is the so-called describing function (DF) approximation, which can also be used experimentally to determine this linearized frequency response by observation of the output disturbance at the same frequency as the injected test sinusoidal signal.

# 1.5 Generalized switching dc-to-dc converter

It is now not hard on the basis of the previous discussion to visualize a general switching dc-to-dc converter, as shown in Fig. 1.11, where elements are purposely shown not interconnected in order to emphasize relative freedom of the choice of topology.

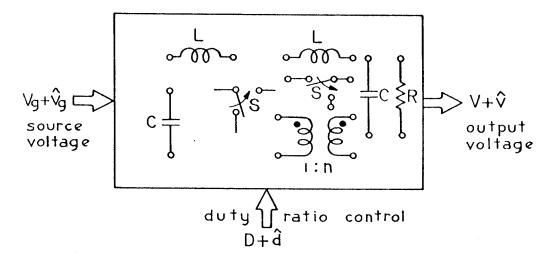

Fig. 1.11 Generalized switching dc-to-dc converter.

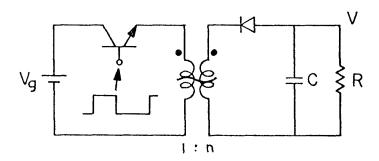

A generalized switching converter could consist of a number of energy storage elements (not necessarily a single inductor and capacitor as in the converters of Fig. 1.1), transformers and synchronous switches (again not restricted to the single switch as in Fig. 1.1) which are arranged in a topology such that the periodic opening and closing of the switches would guide the input power through the switching network in such a way that dc level conversion is obtained at the output.

There are, however, two general restrictions which have to be placed on the choice of interconnection of elements and their values:

1. Topology of the converter is not quite random, but the storage elements (inductors and capacitors) have to be arranged in such a way as to form effectively a <u>low-pass</u> <u>filter</u> if the prime <u>dc</u> input power is to be allowed to propagate to the converter output. 2. If the switching ripple caused by periodic action of the switches is to be negligible, the natural filter frequencies  $f_c$  and  $\omega_\alpha$  must be significantly smaller than the switching frequency  $f_s$ .

As seen from Fig. 1.11 the two independent inputs for the steady state (dc) static operation of the converter are line dc voltage  $V_g$  and steady state duty ratio D, while for the dynamic (ac) response, they are line voltage variation  $\hat{v}_g$  and duty ratio modulation  $\hat{d}$ .

This generalized converter also has two modes of operation as previously illustrated on the buck-boost example. In the continuous conduction mode the topology of the converter is periodically changed between <u>two</u> switched networks (analogous to that in Fig. 1.4) while in the discontinuous conduction mode <u>three</u> switched network structures are clearly distinguished (compare with Fig. 1.7).

Note, however, that this generalized switching converter can have multistructural change (more than two switched networks) even in the continuous conduction mode (see Appendix D, for example). Likewise, the discontinuous conduction mode is not restricted to just three structural changes, though that is the minimum necessary to exhibit such behavior. Nevertheless, we will in Part I analyse the continuous conduction mode with only two structural changes, and in Part II the discontinuous conduction mode with only three structural changes because all the essential features of the two modelling methods are present in these

cases. The extension to the multistructural change is quite simple as demonstrated in Appendix D for the converters with three or four structural changes (also referred to as "three-state" and "four-state" converters, respectively) operating in the continuous conduction mode, and in Chapter 6 (Section 6.2) for the discontinuous conduction mode with more than three structural changes per switching period.

# 1.6 Review

It is for the generalized switching converter with the features described in Section 1.5 for which a general, unified method of modelling and analysis in both conduction modes will be developed. In particular, in Part I this general modelling technique is developed in detail for the continuous conduction mode of converter operation. In Part II, these techniques are extended with suitable modifications to include modelling of the converters operating in the discontinuous conduction mode. In both cases, a novel general and unified state space averaging technique is used to arrive at the general equations describing both static and dynamic properties of any switching dc-to-dc converter (pictorially represented in Fig. 1.11). Besides enabling some general results not previously attainable, the method lends itself easily to extraction of very useful circuit model realizations for any particular converter. Commonly used converters, shown in Fig. 1.1, are repeatedly used to demonstrate various models.

The ultimate goal and objective, however, of the modelling

procedure was not only to provide the tool for both static and dynamic analysis of existing converters, but through the circuit models and general conclusions to give additional insight and incentive to the circuit designer to devise new, better and possibly optimum converters.

In fact, it will be shown in Parts III and IV that this goal has been achieved. Indeed, Part III is a result of the search for such converter topologies which would confirm the general predictions made by the canonical circuit model of Part I, since the known existing structures failed to exhibit this generality. This has led naturally, first, to the idea of interconnecting existing converter structures into useful topologies, and cascade connection of switching converters as described in Part III turned out to be a very powerful one, from both theoretical and practical points of view. On the side of theory, it has finally confirmed the general modelling results of Part I. In addition, it has suggested a renewed look at the three "basic" converters of Fig. 1.1, through recognition that the buck-boost power stage may be considered as a buck converter cascaded with a boost converter, and thus leaving only the first two converters of Fig. 1.1 to be considered truly basic. This crucial observation paved the way for the discovery of a new switching converter which employs a novel and optimum circuit topology, and which is shown in Part IV to outperform any switching converter in its class.

Finally, after the foundations for modelling and analysis are firmly laid down in Parts I and II, and then used subsequently in

Parts III and IV to show in a rather natural and logical order how some new converter topologies could be devised, the thesis concludes with a number of research areas wide open for future investigation: discontinuous conduction mode in new converters, possible new modes of operation, and various technological implementations of synchronous switches are just a few examples.

# GENERAL UNIFIED APPROACH TO MODELLING SWITCHING CONVERTERS

# PART I

CONTINUOUS CONDUCTION MODE

### CHAPTER 2

#### REVIEW OF THE NEW

## STATE-SPACE MODELLING TECHNIQUE

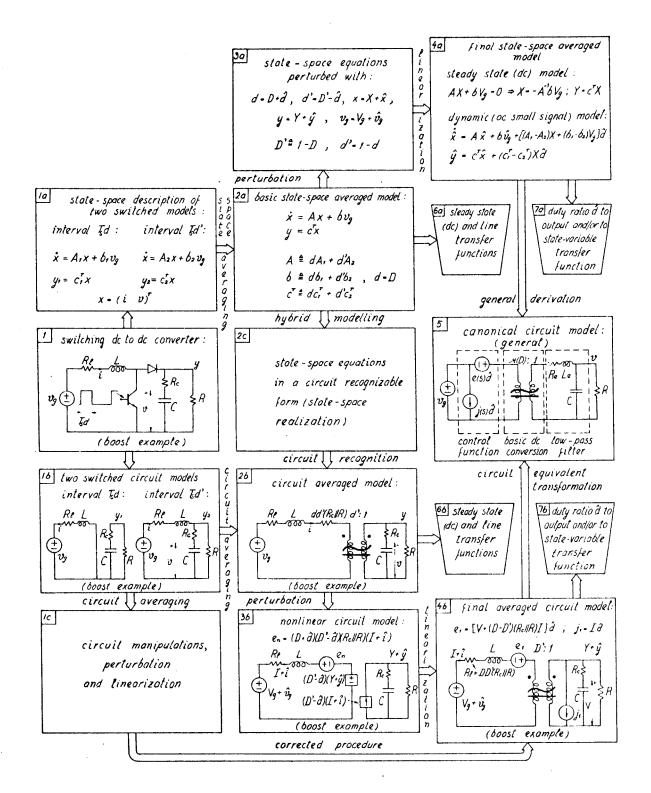

The purpose of this chapter is to present a short, concise review of the most important interrelationships among various building blocks in the complete structure of the new modelling technique. Through this exposition of the various interconnections and procedural steps summarized in the Flowchart of Fig. 2.1 a twofold purpose will be achieved. First, the details of the modelling procedures which are presented in the remaining chapters of this Part I will be easier to grasp once it is understood how and where they fit into the complete modelling picture. Second, after the details of modelling are thoroughly explained in Chapters 3, 4 and 5, illustrated on numerous examples and fully comprehended, it will serve as a quick and easy reference guide and reminder containing all the essential information about the modelling in the continuous conduction mode.

However, because of its overview feature, this chapter will be relatively narrower in scope than, for example, Chapters 3 and 4 where the detailed development of the new modelling technique is given and the results discussed in depth.

# 2.1 Brief review of existing modelling techniques

In modelling of switching converters in general, and power stages in particular, two main approaches - one based on state-space modelling and the other using an averaging technique - have been developed extensively, but there has been little correlation between them. The first approach remains strictly in the domain of equation manipulations, and hence relies heavily on numerical methods and computerized implementations. Its primary advantage is in the unified description of all power stages regardless of the type (buck, boost, buck-boost or any other variation) through utilization of the exact state-space equations of the two switched models. On the other hand, the approach using an averaging technique is based on equivalent circuit manipulations, resulting in a single equivalent linear circuit model of the power stage. This has the distinct advantage of providing the circuit designer with physical insight into the behavior of the original switched circuit, and of allowing the powerful tools of linear circuit analysis and synthesis to be used to the fullest extent in design of regulators incorporating switching converters.

# 2.2 Proposed new state-space averaging approach

The method proposed in this work bridges the gap earlier considered to exist between the state-space technique and the averaging technique of modelling power stages by introduction of state-space averaged modelling. At the same time it offers the

advantages of both existing methods—— the general unified treatment of the state-space approach, as well as an equivalent linear circuit model as its final result. Furthermore, it makes certain generalizations possible, which otherwise could not be achieved.

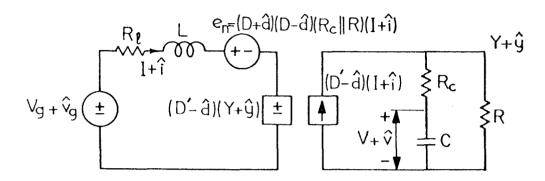

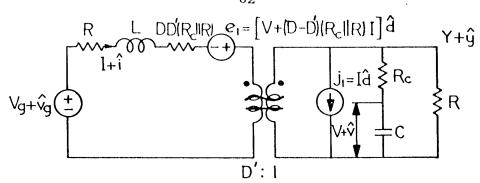

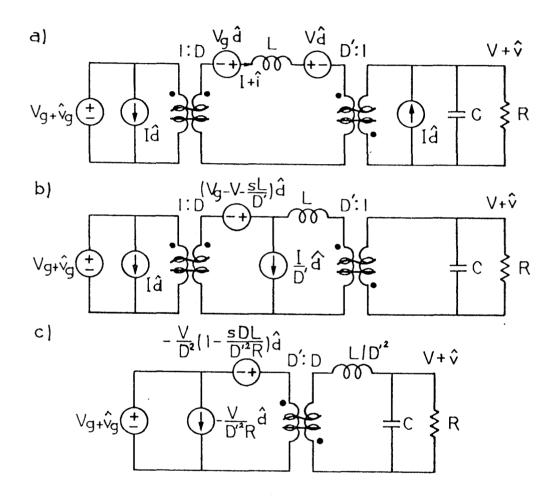

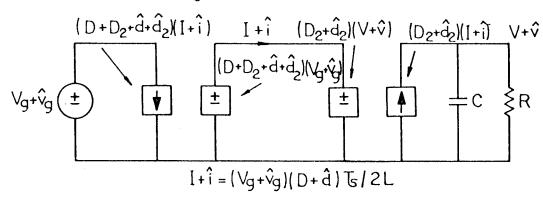

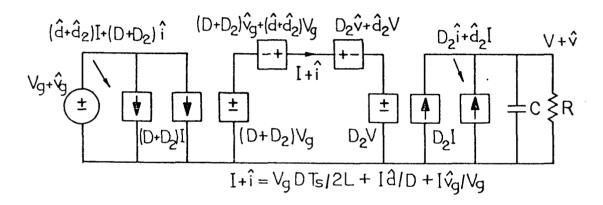

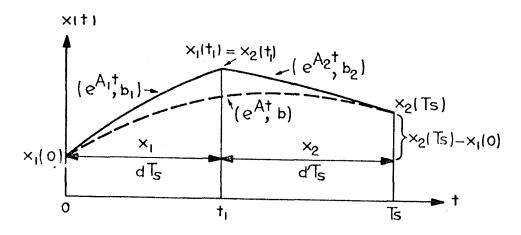

The proposed state-space averaging method, outlined in the Flowchart of Fig. 2.1, allows a unified treatment of a large variety of power stages currently used, since the averaging step in the statespace domain is very simple and clearly defined (compare blocks la and 2a). It merely consists of averaging the two exact state-space descriptions of the switched models over a single cycle Ts, where  $f_s = 1/T_s$  is the switching frequency (block 2a). Hence there is no need for special "know-how" in massaging the two switched circuit models into topologically equivalent forms in order to apply circuitoriented procedure directly, as required in [1] (block 1c). Nevertheless, through a hybrid modelling technique (block 2c), the circuit structure of the averaged circuit model (block 2b) can be readily recognized from the averaged state-space model (block 2a). Hence all the benefits of the previous averaging technique are retained. Even though this outlined process might be preferred, one can proceed from blocks 2a and 2b in two parallel but completely equivalent directions: one following path a strictly in terms of state-space equations, and the other along path b in terms of circuit models. In either case, a perturbation and linearization process required to include the duty ratio modulation effect proceeds in a very straightforward and formal manner, thus emphasizing the corner-stone character of blocks 2a and 2b. At this stage (block 2a or 2b) the steady state (dc) and line to

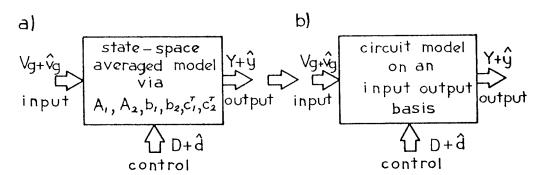

Fig. 2.1 Flowchart of averaging approaches in modelling switching dc-to-dc converters, leading to the canonical circuit model (block 5). Path a: general state-space modelling; Path b: circuit transformation method.

output transfer functions are already available, as indicated by blocks 6a and 6b respectively, while the duty ratio to output transfer function is available at the final-state model (4a or 4b) as indicated by blocks 7a and 7b. The two final state models 4a and 4b then give the complete description of the switching converter by inclusion of both independent controls, the line voltage variation and the duty ratio modulation.

Even though the circuit transformation path b might be preferred from the practical design standpoint, the state-space averaging path a is invaluable in reaching some general conclusions about the small-signal low-frequency models of any dc-to-dc switching converter (even those yet to be invented). Whereas, for path b, one has to be presented with the particular circuit in order to proceed with modelling, for path a the final state-space averaged equations (block 4a) give the complete model description through general matrices  $A_1$ ,  $A_2$  and vectors  $b_1$ ,  $b_2$ ,  $c_1^T$ , and  $c_2^T$  of the two starting switched models (block la). This is also why along path b in the Flowchart a particular example of a boost power stage with parasitic effects was chosen, while along path a general equations have been retained. Specifically, for the boost power stage  $b_1 = b_2 = b$ . This example will be later pursued in detail along both paths.

In addition, the state-space averaging approach offers a clear insight into the quantitative nature of the basic averaging approximation, which becomes better the further the effective low-pass filter corner frequency  $f_c$  is below the switching frequency  $f_s$ ,

that is,  $f_c/f_s$  << 1. This is, however, shown to be equivalent to the requirement for small output voltage ripple, and hence does not pose any serious restriction or limitation on modelling of practical dc-to-dc converters.

Finally, the state-space averaging approach serves as a basis for derivation of a useful general circuit model that describes the input-output and control properties of any dc-to-dc converter.

# 2.3 New canonical circuit model

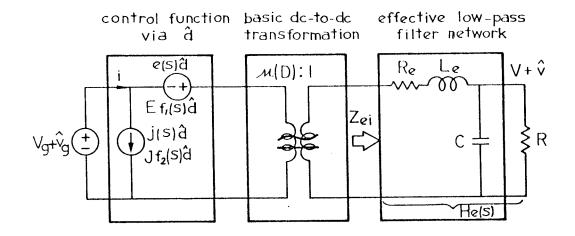

The culmination of any of these derivations along either path a or path b in the Flowchart of Fig. 2.1 is an equivalent circuit (block 5), valid for small-signal low-frequency variations superimposed upon a dc operating point, that represents the two transfer functions of interest for a switching converter. These are the line voltage to output and duty ratio to output transfer functions.

The equivalent circuit is a canonical model that contains the essential properties of <u>any</u> dc-to-dc switching converter, regardless of the detailed configuration. As seen in block 5 for the general case, the model includes an ideal transformer that describes the basic dc-to-dc transformation ratio from line to output; a low-pass filter whose element values depend upon the dc duty ratio; and a voltage and a current generator proportional to the duty ratio modulation input.

The canonical model in block 5 of the Flowchart can be obtained following either path a or path b, namely from block 4a or 4b, as

will be shown later. However, following the general description of the final averaged model in block 4a, certain generalizations about the canonical model are made possible, which are otherwise not achievable. Namely, even though for all currently known switching dc-to-dc converters (such as the buck, boost, buck-boost, Venable [3], Weinberg [4] and a number of others) the frequency dependence appears only in the duty-ratio dependent voltage generator but not in the current generator, and then only as a first-order (singlezero) polynomial in complex frequency s; however, neither circumstance will necessarily occur in some converter yet to be conceived. In general, switching action introduces both zeros and poles into the duty ratio to output transfer function, in addition to the zeros and poles of the effective filter network which essentially constitute the line voltage to output transfer function. Moreover, in general, both duty-ratio dependent generators, voltage and current, are frequency dependent (additional zeros and poles). That in the particular cases of the boost or buck-boost converters this dependence reduces to a first order polynomial results from the fact that the order of the system which is involved in the switching action is only two. Hence from the general result, the order of the polynomial is at most one, though it could reduce to a pure constant as in the buck or the Venable converter [3].

The significance of the new circuit model is that <u>any</u> switching dc-to-dc converter can be reduced to this canonical fixed topology form, at least as far as its input-output and control properties are concerned, and hence it is valuable for comparison of

various performance characteristics of different dc-to-dc converters. For example, the effective filter networks could be compared as to their effectiveness throughout the range of dc duty cycle D (in general, the effective filter elements depend on duty ratio D), and the configuration chosen which optimizes the size and weight. Also, comparison of the frequency dependence of the two duty-ratio dependent generators provides insight into the question of stability once a regulator feedback loop is closed.

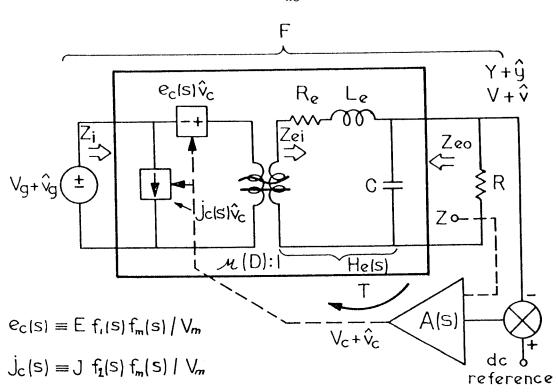

# 2.4 Extension to complete regulator treatment

Finally, all the results obtained in modelling the converter or, more accurately, the network which effectively takes part in switching action, can easily be incorporated into more complicated systems containing dc-to-dc converters such as the switching regulator in Fig. 1.10. For example, by modelling the modulator stage along the same lines, one can obtain a linear circuit model of a closed-loop switching regulator. Standard linear feedback theory can then be used for both analysis and synthesis, stability considerations, and proper design of feedback compensating networks for multiple-loop as well as single-loop regulator configurations.

In summary, the review in this chapter has shown that the new general state-space averaging method is directly applicable to any switching dc-to-dc converter, even those whose topologies have not yet been conceived, namely to the generalized switching converter of Fig. 1.11. By simply following path a in the Flowchart of Fig. 2.1 both static (dc) and dynamic (ac) characteristics of the converter

are easily obtained. The only assumption made is that the converter operates in the continuous conduction mode, hence there exist only two switched circuit models (or their equivalent linear state-space description through triples  $(A_1, b_1, c_1^T)$  and  $(A_2, b_2, c_2^T)$  as shown in block la of the Flowchart in Fig. 2.1).

In addition, for any particular converter, the circuit averaged model results from following path b in the Flowchart. Finally, as a culmination of both approaches, a new canonical circuit model exhibiting fixed topology is obtained (block 5 in the Flowchart) which makes certain general conclusions possible.

After being so general in this chapter, we proceed with the specific derivations and illustrative examples in Chapters 3 and 4.

#### CHAPTER 3

# STATE-SPACE AVERAGING, HYBRID MODELLING AND CIRCUIT AVERAGING

Several paths in the Flowchart of Fig. 2.1 are explored in detail in this chapter and are illustrated by appropriate examples. Since the justification of the basic state-space averaging step (going from block la to 2a in the Flowchart of Fig. 2.1) is lengthy and involved, the corresponding derivations are shown separately in Appendices A, B and C. This way they will not hide or interfere with the simple sequence of steps explained in this chapter, which are to be followed in order to arrive at the final static and dynamic model of the converter.

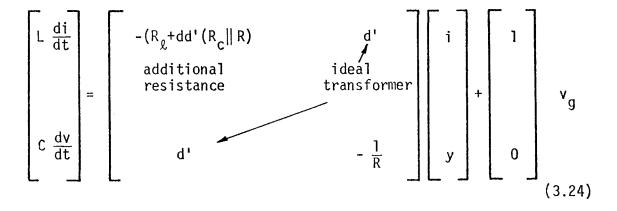

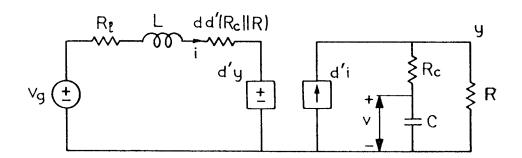

# 3.1 State-space averaging

In this section the state-space averaging method is developed first in general for any dc-to-dc switching converter, and then demonstrated in detail for the particular case of the boost power stage in which parasitic effects (esr of the capacitor and series resistance of the inductor) are included. General equations for both steady-state (dc) and dynamic performance (ac) are obtained, from which important transfer functions are derived and also applied to the special case of the boost power stage.

Basic state-space averaged model

The basic dc-to-dc level conversion function of switching converters is achieved by repetitive switching between two linear

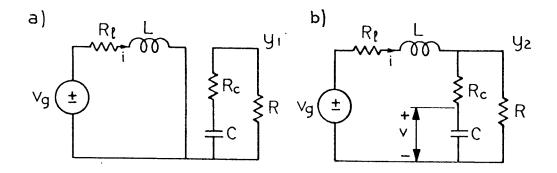

networks consisting of ideally lossless storage elements, inductances and capacitances. In practice, this function may be obtained by use of transistors and diodes which operate as synchronous switches. On the assumption that the circuit operates in the continuous conduction mode in which the instantaneous inductor current does not fall to zero at any point in the cycle, there are only two different "states" of the circuit. Each state, however, can be represented by a linear circuit model (as shown in block lb of Fig. 2.1) or by a corresponding set of state-space equations (block la). Even though any set of linearly independent variables can be chosen as the state variables, it is customary and convenient in electrical networks to adopt the inductor currents and capacitor voltages. The total number of storage elements thus determines the order of the system. Let us denote such a choice of a vector of state-variables by x.

It then follows that any switching dc-to-dc converter operating in the continuous conduction mode can be described by the state-space equations for the two switched models:

(i) interval

$$T_s d$$

: (ii) interval  $T_s d'$ :

$$\dot{x} = A_1 x + b_1 v_g$$

$$\dot{x} = A_2 x + b_2 v_g$$

$$y_1 = c_1^T x$$

$$y_2 = c_2^T x$$

(3.1)

where  $T_s d$  denotes the interval when the switch is in the on state and  $T_s(1-d) \equiv T_s d'$  is the interval for which it is in the off state, as shown in Fig. 1.2. The static equations  $y_1 = c_1^T x$  and  $y_2 = c_2^T x$  are necessary in order to account for the case when the output quantity does not coincide with any of the state variables, but is

rather a certain linear combination of the state variables.

Our objective now is to replace the state-space description of the two linear circuits emanating from the two successive phases of the switching cycle  $T_S$  by a single state-space description which represents approximately the behavior of the circuit across the whole period  $T_S$ . We therefore propose the following simple averaging step: take the average of both dynamic and static equations for the two switched intervals (3.1), by summing the equations for interval  $T_S$ d multiplied by d and the equations for interval  $T_S$ d multiplied by d'. The following linear continuous system results:

$$\dot{x} = d(A_1 x + b_1 v_g) + d'(A_2 x + b_2 v_g)$$

$$y = dy_1 + d'y_2 = (dc_1^T + d'c_2^T)x$$

(3.2)

After rearranging (3.2) into the standard linear continuous system state-space description, we obtain the basic averaged state-space description (over a single period  $T_s$ ):

$$\dot{x} = (dA_1 + d'A_2)x + (db_1 + d'b_2)v_g$$

$$y = (dc_1^T + d'c_2^T)x$$

(3.3)

This model is the basic averaged model which is the starting model for all other derivations (both state-space and circuit oriented).

Note that in the above equations the duty ratio d is considered constant; it is not a time dependent variable (yet), and particularly not a switched discontinuous variable which changes between 0 and 1 as

in [1] and [2], but is merely a fixed number for each cycle. This is evident from the model derivation in Appendix B. In particular, when d = 1 (switch constantly on) the averaged model (3.3) reduces to a switched model (3.1i), and when d = 0 (switch off) it reduces to switched model (3.1ii).

In essence, comparison between (3.3) and (3.1) shows that the system matrix of the averaged model is obtained by taking the average of two switched model matrices  $A_1$  and  $A_2$ , its control is the average of two control vectors  $b_1$  and  $b_2$ , and its output is the average of two outputs  $y_1$  and  $y_2$  over a period  $T_s$ .

The justification and the nature of the approximation in substitution for the two switched models of (3.1) by state-space averaged model (3.3) is indicated in the Appendices. It has already been shown in Chapter 1 that the requirement of low output switching ripple places the natural frequencies  $\omega_{\alpha} = 1/2RC$  and  $f_{c} = 1/2\pi\sqrt{LC}$ significantly lower than the switching frequency  $f_s = 1/T_s$  (see for example (1.11)). These two restrictions on the choice of elements, namely  $\omega_{\alpha}/f_{s}$  << 1 and  $f_{c}/f_{s}$  << 1 are shown in Appendix A to lead to a very accurate approximation of the fundamental matrix  $e^{\mathsf{At}}$  by its first-order linear term, or  $e^{\mbox{\it At}} \sim \mbox{\it I} + \mbox{\it At}.$  This linear approximation of the fundamental matrix is shown in Appendix B to lead directly to the state-space averaging step, namely replacement of the two linear continuous models (3.1) by a single continuous model of (3.3). In addition, in Appendix C it is shown that in the steady state regime, the exact dc conditions could be found which under the same linear approximation of fundamental matrices reduce to the dc conditions

obtained from basic averaged state-space model (3.3).

The model represented by (3.3) is an averaged model over a single period  $T_s$ . If we now assume that the duty ratio d is constant from cycle to cycle, namely, d = D (steady state dc duty ratio), we get:

$$\dot{x} = Ax + bv g

y = c^{T} x$$

(3.4)

where

$$A = DA_{1} + D'A_{2}$$

$$b = Db_{1} + D'b_{2}$$

$$c^{T} = Dc_{1}^{T} + D'c_{2}^{T}$$

(3.5)

Since (3.4) is a linear system, superposition holds and it can be perturbed by introduction of line voltage variations  $\hat{v}_g$  as  $v_g = V_g + \hat{v}_g$ , where  $V_g$  is the dc line input voltage, causing a corresponding perturbation in the state vector  $x = X + \hat{x}$ , where again X is the dc value of the state vector and  $\hat{x}$  the superimposed ac perturbation. Similarly,  $y = Y + \hat{y}$ , and

$$\hat{x} = AX + bV_g + Ax + bV_g$$

$$Y + \hat{y} = c^T X + c^T \hat{x}$$

(3.6)

Separation of the steady-state (dc) part from the dynamic (ac) part then results in the steady state (dc) model

$$AX + bV_g = 0; Y = c^T X Y = -c^T A^{-1} bV_g$$

(3.7)

and the dynamic (ac) model

$$\hat{\hat{x}} = A\hat{x} + b\hat{v}_g$$

$$\hat{y} = c^T\hat{x}$$

(3.8)

It is interesting to note that in (3.7) the steady state (dc) vector X in general depends only on the dc duty ratio D and resistances in the original model, but not on the storage element values (L's and C's). This is so because X is the solution of the linear system of equations

$$AX + bV_g = 0 (3.9)$$

in which L's and C's are proportionality constants. This is in complete agreement with the first-order approximation of the exact dc conditions shown in Appendix C, which coincides with expression (3.7).

From the dynamic (ac) model, the line voltage to state-vector transfer functions can be easily derived as:

$$\frac{\hat{x}(s)}{\hat{v}_{g}(s)} = (sI-A)^{-1}b$$

$$\frac{\hat{y}(s)}{\hat{v}_{g}(s)} = c^{T}(sI-A)^{-1}b$$

(3.10)

Hence at this stage both steady state (dc) and line transfer functions are available, as shown by block 6a in the Flowchart of Fig. 2.1. We now undertake to include the duty ratio modulation effect into the basic averaged model (3.3).

#### Perturbation

Suppose now that the duty ratio changes from cycle to cycle, that is,  $d(t) = D + \hat{d}$  where D is the steady state (dc) duty ratio as before and  $\hat{d}$  is a superimposed (ac) variation. With the corresponding

perturbation definition  $x = X + \hat{x}$ ,  $y = Y + \hat{y}$ , and  $v_g = V_g + \hat{v}_g$  the basic model (3.3) becomes:

$$\hat{x} = AX + bV_g + \hat{Ax} + b\hat{v}_g + [(A_1 - A_2)X + (b_1 - b_2)V_g]\hat{d} + [(A_1 - A_2)\hat{x} + (b_1 - b_2)\hat{v}_g]\hat{d}$$

dc term line duty ratio variation nonlinear second-order term

$$(3.11)$$

$$Y + \hat{y} = c^TX + c^T\hat{x} + (c_1^T - c_2^T)\hat{x}\hat{d} + (c_1^T - c_2^T)\hat{x}\hat{d}$$

dc ac ac term nonlinear term term term term

The perturbed state-space description is nonlinear owing to the presence of the product of the two time-dependent quantities  $\hat{x}$  and  $\hat{d}$ .

Linearization and final state-space averaged model

Let us now make the small-signal approximation, namely that departures from the steady state values are small compared to the steady state values themselves:

$$\frac{\hat{v}_{\mathbf{q}}}{V_{\mathbf{q}}} \ll 1, \quad \frac{\hat{d}}{D} \ll 1, \quad \frac{\hat{x}}{X} \ll 1 \tag{3.12}$$

Then, using approximations (3.12) we neglect all nonlinear terms such as the second-order terms in (3.11) and obtain once again a linear system, but including duty-ratio modulation  $\hat{d}$ . After separating steady state (dc) and dynamic (ac) parts of this linearized system we arrive at the following results for the final state-space averaged model.

Steady state (dc) model:

$$X = -A^{-1}bV_{q}, Y = c^{T}X = -c^{T}A^{-1}bV_{q}$$

(3.13)

Dynamic (ac small-signal) model:

$$\hat{\hat{x}} = A\hat{x} + b\hat{v}_g + [(A_1 - A_2)X + (b_1 - b_2)V_g]\hat{d}$$

$$\hat{y} = c^T\hat{x} + (c_1^T - c_2^T)X\hat{d}$$

(3.14)

In these results, A, b and  $c^{T}$  are given as before by (3.5).

Equations (3.13) and (3.14) represent the small-signal low-frequency model of any two-state switching dc-to-dc converter working in the continuous conduction mode.

From (3.14), the duty ratio modulation  $\hat{d}$  to state-variable  $\hat{x}$  or to output  $\hat{y}$  transfer functions are directly obtained as:

$$\frac{\hat{x}(s)}{\hat{d}(s)} = (sI-A)^{-1}[(A_1-A_2)X + (b_1-b_2)V_g]$$

$$\frac{\hat{y}(s)}{\hat{d}(s)} = c^{T}(sI-A)^{-1}[(A_1-A_2)X + (b_1-b_2)V_g] + (c_1^{T}-c_2^{T})X$$

(3.15)

It is important to note that by neglect of the nonlinear term in (3.11) the source of harmonics is effectively removed. Therefore, the linear description (3.14) is actually a linearized describing function result that is the limit of the describing function as the amplitude of the input signals  $\hat{v}_g$  and/or  $\hat{d}$  becomes vanishingly small. The significance of this is that the theoretical frequency response obtained from (3.14) for line to output and duty ratio to output transfer functions can be compared with experimental describing function measurements as explained in [1], [2], or [8], in which

small-signal assumption (3.12) is preserved. Very good agreement up to close to half the switching frequency has been demonstrated repeatedly [1], [2], [3], [7].

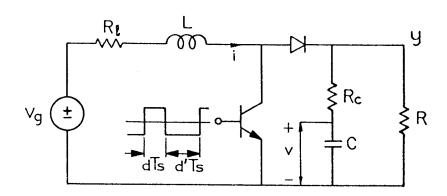

Example: boost power stage with parasitics

We now illustrate the method for the boost power stage shown in Fig. 3.1.

Fig. 3.1 Example for state-space averaged modelling: boost power staye with parasitics included.

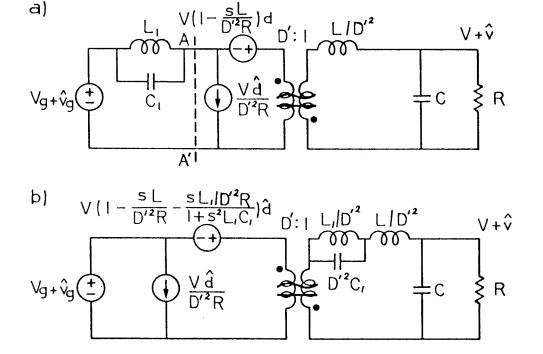

Fig. 3.2 Two switched circuit models of the circuit in Fig. 3.1 with assumption of ideal switches. All elements in the final state-space averaged model (3.13) and (3.14) are obtained:  $A_1$ ,  $b_1$ ,  $c_1^T$  from a) for interval  $dT_s$ , and  $A_2$ ,  $b_2$ ,  $c_2^T$  from b) for interval  $d^TT_s$ .

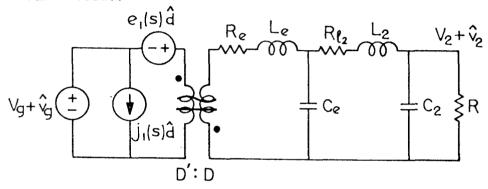

With assumption of ideal switched, the two switched models are as shown in Fig. 3.2. For choice of state-space vector  $\mathbf{x}^T = (\mathbf{i} \ \mathbf{v})$ , the state-space equations become: