Silicon Integrated Arrays: From Microwave to IR

> Thesis by Behrooz Abiri

In Partial Fulfillment of the Requirements for the degree of Doctor of Philosophy

# Caltech

CALIFORNIA INSTITUTE OF TECHNOLOGY Pasadena, California

> 2018 Defended October 23, 2017

# © 2018

Behrooz Abiri ORCID: [0000-0002-3317-2752]

All rights reserved except where otherwise noted

To my love Sara and to my parents.

## ACKNOWLEDGEMENTS

I have always followed one rule in my life: never start something unless you do your best to accomplish it perfectly. And this has really paid off. It is needless to say that I was fortunate to grow up in a family who taught me this and provided me with the means of success, and I am grateful of my parents for this.

I have enjoyed working with two great supervisors. Interestingly, both of them are named Ali! My journey to Caltech couldn't have started without help of my Master's adviser, Prof. Ali Sheikholeslami, who introduced me to my PhD supervisor Ali Hajimiri. Prof. Hajimiri has been a great role model for me. He taught me how to be courageous and brave to fail.

I also thank my thesis committee members Professors Azita Emami, Sanders (Sandy) Weinreb, Andrei Faraon, Changhuei Yang, and Kerry Vahala, who was not available for my defense exam but was a committee member of my Candidacy exam.

When I joined Caltech, I knew that I would be focusing on high-frequency integrated circuits, but I wasn't expecting to reach optical frequencies. I am grateful to Prof. Firooz Aflatouni, who introduced me to the world of optics. I couldn't have had as many tapeout opportunities if it wasn't for Dr. Michael Hochberg and Tom Baehr-Jones for providing access to IME foundry through OpSIS. I also would like to thank all my silicon photonic collaborators, Aroutin, Angad, Andy, Reza, Steve, and Saman who were tremendously helpful in brain storming and helping in measurement.

I was fortunate to be involved in one of the most ambitious projects in Caltech, Space solar power initiative (SSPI). Not only did it increase my knowledge of space structures and solar cells, it taught me team work in a large scale university project. I am grateful to all the members of the project, especially the principal investigators Prof. Ali Hajimiri, Harry Atwater and Sergio Pellegrino, students, post docs and research scientists Matan, Austin, M. Reza, Brian, Stefan, Dennis, Pilar, Emily, Michael, Ali, Terry, Mellanie, Ashish, Nicolas, Manan, and many other who were involved in the project.

Through the involvement of this project, I was fortunate to work with Dr. Florian Bohn who taught me discipline the German way. Working with him was a pleasure and I look forward to working with him outside of Caltech. I couldn't have made ISSCC submission deadline if it wasn't for the generosity and help of Amir, who taught me how to use the turn table for mm-Wave measurements.

I would also like to thank the rest of of CHIC and MICS Lab, Alex(es), Kaushik(s), Parham, Elliott, Abhinav, Aryan, Manuel, and Xavier for being good lab-mates and helping with software and design tools.

Purchasing equipment and consumables would have been a disaster if it wasn't for the help of Michelle and Tanya. David was also very helpful in fixing and organizing the lab. I wish he had joined our lab sooner!

And last but not least, I would like to thank my love Sara for her patience during the tape-outs and paper deadlines and for always being a supporter of my ambitions.

# ABSTRACT

Integrated chips have enabled realization and mass production of complex systems in a small form factor. Through process miniaturization many novel applications in silicon photonics and electronic systems have been enabled. In this thesis I have provided several examples of innovations that are only enabled by integration. I have also demonstrated how electronics and photonics circuits can complement each other to achieve a system with superior performance.

## PUBLISHED CONTENT AND CONTRIBUTIONS

- [1] B. Abiri and A. Hajimiri. A 69-to-79GHz CMOS multiport PA/radiator with +35.7dBm CW EIRP and integrated PLL. In *Digest of Technical Papers IEEE International Solid-State Circuits Conference*, volume 61, 2018. ISBN 9781509049394. doi: 10.1109/ISSCC.2018.8310355.

B.A. proposed the idea, designed the electronic integrated circuits including the on chip antenna, and performed the measurements.

- [2] B. Abiri, F. Aflatouni, and A. Hajimiri. A self-equalizing photo detector. In 2014 IEEE Photonics Conference, IPC 2014, 2014. doi: 10.1109/IPCon.2014. 6995315.

B.A. proposed the idea, designed the silicon photonics integrated circuits, and performed the measurements.

- [3] B. Abiri, F. Aflatouni, A. Rekhi, and A. Hajimiri. Electronic two-dimensional beam steering for integrated optical phased arrays. In *OFC 2014*, pages 1–3, March 2014. doi: 10.1364/OFC.2014.M2K.7.

B.A. was involved in the development of the concept and proposed device calibration process and performed the measurements.

- [4] B. Abiri, F. Aflatouni, and A. Hajimiri. Self-equalizing photodiodes, a hybrid electro-optical approach to tackle bandwidth limitation in high-speed signaling. *Optics Express*, 25(16), 2017. doi: 10.1364/OE.25.019137.

B.A. proposed the idea, designed the silicon photonics integrated circuits, and performed the measurements.

- [5] Behrooz Abiri, Andy Zhou, Firooz Aflatouni, and Ali Hajimiri. An adjustable self-equalizing photo detector. In *Optical Fiber Communication Conference*, page W3A.3. Optical Society of America, 2015. doi: 10.1364/OFC.2015. W3A.3.

B.A. conceived the idea, designed the photonic IC and was involved with testing the IC.

- [6] F. Afiatouni, B. Abiri, A. Rekhi, H. Abediasl, H. Hashemi, and A. Hajimiri. Electronic laser phase noise reduction. In *Digest of Papers - IEEE Radio Frequency Integrated Circuits Symposium*, 2013. ISBN 9781467360586. doi: 10.1109/RFIC.2013.6569578.

B.A. proposed the CMOS electronic architecture and was involved with the design of the electronic IC and measurements.

- [7] F. Aflatouni, B. Abiri, A. Rekhi, and A. Hajimiri. Nanophotonic coherent imager. *Optics Express*, 23(4), 2015. doi: 10.1364/OE.23.005117.

B.A. was involved in the development of the concept and was involved with the measurement setup assembly.

- [8] F. Aflatouni, B. Abiri, A. Rekhi, and A. Hajimiri. Nanophotonic projection system. *Optics Express*, 23(16), 2015. doi: 10.1364/OE.23.021012.

B.A. was involved in the development of the concept and was involved with the measurement setup assembly.

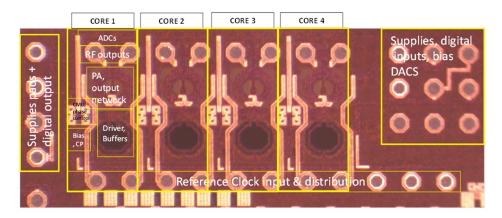

- [9] F. Bohn, B. Abiri, and A. Hajimiri. Fully integrated CMOS X-Band power amplifier quad with current reuse and dynamic digital feedback (DDF) capabilities. In *Digest of Papers - IEEE Radio Frequency Integrated Circuits Symposium*, 2017. ISBN 9781509046263. doi: 10.1109/RFIC.2017.7969054. B.A. designed the frequency synthesizer, phase shifters, and ADC required for the system. He also was involved with the measurement and proposed the PID controller that controlled the operation of the system.

- [10] S. M. Bowers, B. Abiri, F. Aflatouni, and A. Hajimiri. A compact optically driven travelling-wave radiating source. In *OFC 2014*, pages 1–3, March 2014. doi: 10.1364/OFC.2014.Tu2A.3.

The optical domain of the design was performed by B.A. He was also involved with measurement effort.

- [11] Reza Fatemi, Behrooz Abiri, and Ali Hajimiri. A One-Dimensional Heterodyne Lens-Free OPA Camera. In *Conference on Lasers and Electro-Optics*, page STu3G.3, Washington, D.C., 6 2016. OSA. ISBN 978-1-943580-11-8. doi: 10.1364/CLEO\\_SI.2016.STu3G.3.

The chip was designed and laid out by B.A. He was also involved in the measurement of the IC.

- [12] Reza Fatemi, Behrooz Abiri, and Ali Hajimiri. An 8x8 Heterodyne Lens-less OPA Camera. In *Conference on Lasers and Electro-Optics*, page JW2A.9, Washington, D.C., 5 2017. OSA. ISBN 978-1-943580-27-9. doi: 10.1364/ CLEO\\_AT.2017.JW2A.9. The chip was designed and laid out by B.A. He was also involved in the

The chip was designed and laid out by B.A. He was also involved in the measurement of the IC.

[13] A. Hajimiri, B. Abiri, and F. Aflatouni. Hybrid electro-optical solutions for high-speed connectivity (invited). In 2015 IEEE Optical Interconnects Conference, OI 2015, 2015. ISBN 9781479981793. doi: 10.1109/OIC.2015. 7115677.

B.A. was involved with development of concepts and measurements of the systems described in this review paper.

[14] A. Khachaturian, B. Abiri, and A. Hajimiri. A compact spiral Mach-Zehnder Interferometer Modulator on SOI process. In *IEEE International Conference* on Group IV Photonics GFP, volume 2015-Octob, 2015. doi: 10.1109/Group4. 2015.7305996.

B.A. proposed the concept of spiral MZI to reduce device size, designed the silicon photonics integrated circuits.

[15] A. Khachaturian, B. Abiri, A. Zhou, and A. Hajimiri. Monolithic Mach-Zehnder Interferometer Modulator in an unmodified CMOS process. In 2015 IEEE Photonics Conference, IPC 2015, 2015. doi: 10.1109/IPCon.2015. 7323627.

B.A. helped with the design and measurement.

[16] S. Saeedi, B. Abiri, A. Hajimiri, and A. Emami. Differential optical ring modulator: Breaking the bandwidth/quality-factor trade-off. In *European Conference on Optical Communication, ECOC*, volume 2015-Novem, 2015. doi: 10.1109/ECOC.2015.7341731.

B.A. proposed the optically differential drive, verified the theoretical analysis and helped with measurement.

# TABLE OF CONTENTS

| A algorithm in                                                                   |  |  |  |

|----------------------------------------------------------------------------------|--|--|--|

| Acknowledgements                                                                 |  |  |  |

| Published Content and Contributions                                              |  |  |  |

|                                                                                  |  |  |  |

| Bibliography    vii      Table of Contents    x                                  |  |  |  |

|                                                                                  |  |  |  |

|                                                                                  |  |  |  |

| List of Tables                                                                   |  |  |  |

| Chapter I: Introduction                                                          |  |  |  |

| 1.1 Contributions         4                                                      |  |  |  |

| 1.1         Contributions         4           1.2         Organization         6 |  |  |  |

| Chapter II: Silicon Photonics: Integrating Complex Optical Systems on a Chip 7   |  |  |  |

|                                                                                  |  |  |  |

|                                                                                  |  |  |  |

| I I I I I I I I I I I I I I I I I I I                                            |  |  |  |

|                                                                                  |  |  |  |

| 3.1 Necessity of Channel Equalization                                            |  |  |  |

| 3.2 An Overview of Equalization Techniques                                       |  |  |  |

| 3.3 Design and Implementation                                                    |  |  |  |

| 3.4 Measurement Results                                                          |  |  |  |

| 3.5 Conclusion                                                                   |  |  |  |

| Chapter IV: Lens-Free Projection Systems Using Optical Phased-Arrays 35          |  |  |  |

| 4.1 Introduction                                                                 |  |  |  |

| 4.2 Integrated Optical Phased Arrays                                             |  |  |  |

| 4.3 Amplitude-Phase Coupling Effect                                              |  |  |  |

| 4.4 Proposed Integrated Optical Phased-Array with Per-Channel High               |  |  |  |

| Speed Phase Control                                                              |  |  |  |

| 4.5 Measurement Results and Image and Video Projection                           |  |  |  |

| 4.6 Conclusion                                                                   |  |  |  |

| Chapter V: Lens-Free Imaging Systems Using Optical Phased-Arrays 48              |  |  |  |

| 5.1 Introduction                                                                 |  |  |  |

| 5.2 Phased Array Receiver                                                        |  |  |  |

| 5.3 OPA Receiver Design                                                          |  |  |  |

| 5.4 Measurement setup                                                            |  |  |  |

| 5.5 Measurement and Results                                                      |  |  |  |

| 5.6 Conclusion                                                                   |  |  |  |

| Chapter VI: LIDAR Imager with Sub-mm Depth Resolution                            |  |  |  |

| 6.1 Introduction                                                                 |  |  |  |

| 6.2 Coherent Imager Architecture                                                 |  |  |  |

| 6.3 Measurement results                                                          |  |  |  |

| 6.4 Conclusion                                                                | 74         |  |  |  |

|-------------------------------------------------------------------------------|------------|--|--|--|

| Chapter VII: A Compact High Power mm-Wave Radiator for Low Voltage            |            |  |  |  |

| CMOS Technology                                                               | 75         |  |  |  |

| 7.1 Motivation                                                                | 75         |  |  |  |

| 7.2 Radiator Design                                                           | 75         |  |  |  |

| 7.3 PLL Design                                                                | 81         |  |  |  |

| 7.4 Distribution Network                                                      | 82         |  |  |  |

|                                                                               | 82         |  |  |  |

| Chapter VIII: Wireless Power Transfer from Space                              | 88         |  |  |  |

| 8.1 Introduction                                                              | 88         |  |  |  |

| 8.2 General Proposed Concept                                                  | 88         |  |  |  |

| 8.3 Photovoltaics                                                             | 90         |  |  |  |

| 8.4 Microwave Power Generation and Control                                    | 96         |  |  |  |

| 8.5 Antenna Design                                                            | )4         |  |  |  |

| 8.6 Structures and Deployment                                                 | 0          |  |  |  |

| 8.7 Discussion on System Integration                                          | 7          |  |  |  |

| 8.8 Clock multiplication with programmable phase control                      | !3         |  |  |  |

| 8.9 High efficiency, high power rectenna design                               | 28         |  |  |  |

| 8.10 PA Stacking: As regulator free solution to PA and PV voltage mismatch 13 | 64         |  |  |  |

| Chapter IX: Other Works                                                       | 2          |  |  |  |

| 9.1 Integrated Laser Linewidth Reduction                                      | 2          |  |  |  |

| 9.2 Electro-optical mm-Wave Power Generation and Radiation 14                 | 9          |  |  |  |

| 9.3 Breaking the Bandwidth/Quality-Factor Trade-off in Optical Ring           |            |  |  |  |

| Resonators                                                                    |            |  |  |  |

| 9.4 Reducing Mach-Zehnder Interferometer Footprint                            | <i>i</i> 9 |  |  |  |

| 9.5 Improving Photodiode Bandwidth and Power Capability 16                    | <b>j</b> 1 |  |  |  |

| Bibliography                                                                  | 5          |  |  |  |

xi

# LIST OF ILLUSTRATIONS

| Numbe | r                                                                         | Page |

|-------|---------------------------------------------------------------------------|------|

| 1.1   | Hertz transmitter and receiver [23]                                       | . 2  |

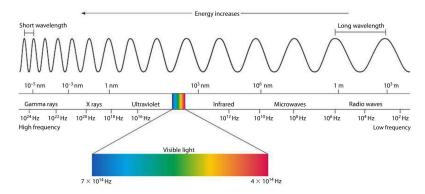

| 1.2   | Electromagnetic spectrum                                                  | . 2  |

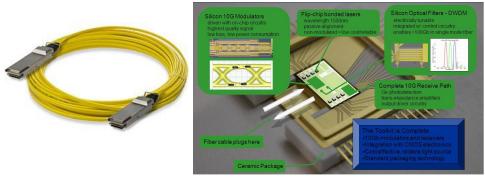

| 1.3   | Active optical cables marries the ease of use of copper cables with       |      |

|       | speed of fiber optics                                                     | . 3  |

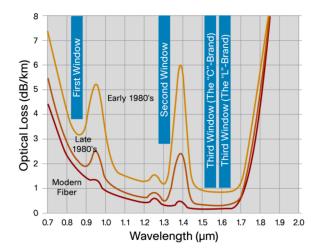

| 2.1   | Optical fiber loss for different wavelengths [1]                          | . 7  |

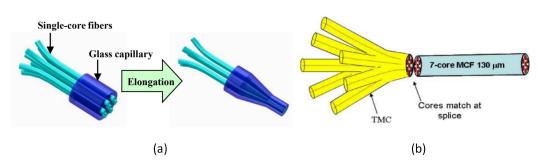

| 2.2   | Connecting single mode fibers to multi-core fibers. (a) Creation of       |      |

|       | bundle [128] and (b) alignment needed for splicing [185]                  | . 8  |

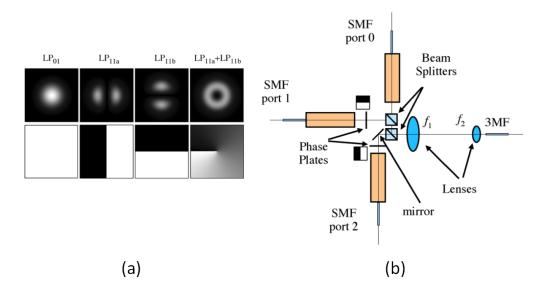

| 2.3   | (a)Examples of amplitude (top) and phase (bottom) profiles of modes       |      |

|       | excited in a few-mode fiber for MDM. (b) Setup required to multiplex      |      |

|       | the modes in and out of the fiber [142]                                   | . 9  |

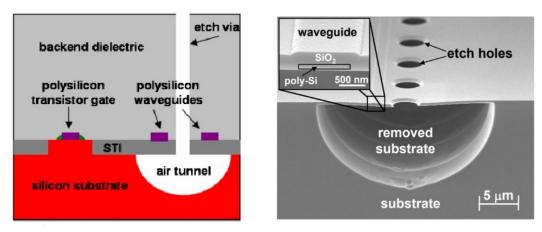

| 2.4   | Removal of substrate to reduce leakage of light to the substrate [78].    | . 10 |

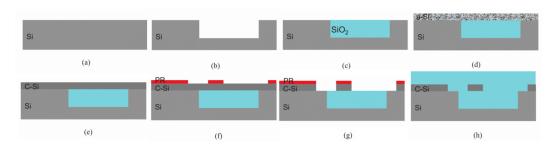

| 2.5   | Creating single crystals form amorphous silicon to reduce the loss of     |      |

|       | optical waveguide [90]                                                    | . 11 |

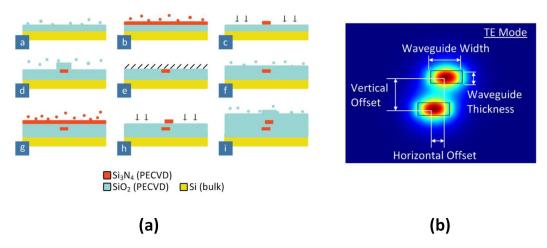

| 2.6   | (a) A fabrication steps of a multi-layer silicon nitride optical platform |      |

|       | and methods to couple light from one layer to the other layer [151].      | . 12 |

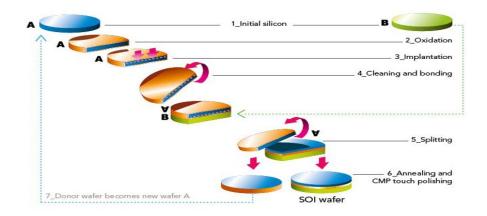

| 2.7   | Fabrication steps for SOI wafers [6]                                      | . 13 |

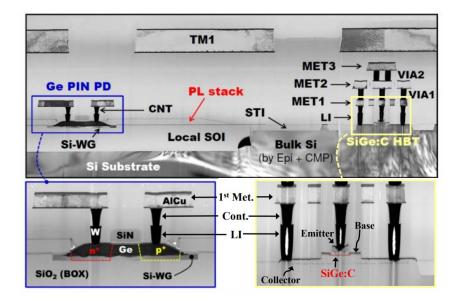

| 2.8   | Cross section of EPIC process developed by IHP [106]. In this             |      |

|       | process both bulk SiGe/CMOS devices and SOI photonics structures          |      |

|       | are integrated.                                                           | . 14 |

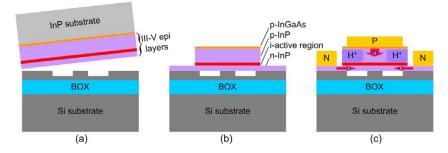

| 2.9   | Process of (a) bonding (b) etching and (c) contact formation in a         |      |

|       | III-V gain medium on SOI process. No stringent alignment during           |      |

|       | placement is required [103]                                               | . 14 |

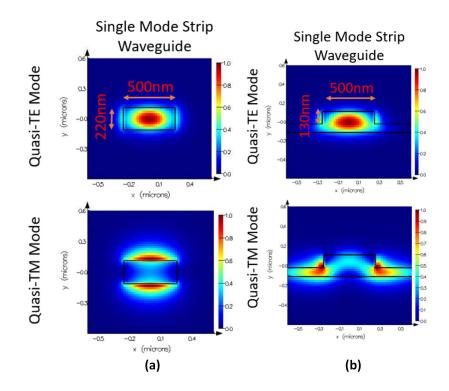

| 2.10  | (a) Single mode strip and (b) strip loaded waveguides and the profile     |      |

|       | of quasi TE/TM modes that it supports                                     | . 16 |

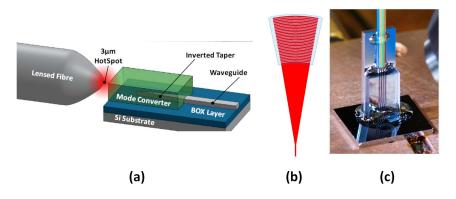

| 2.11  | Chip to fiber couplers. (a) Edge coupler [44] (b) grating coupler         |      |

|       | layout and (c) packaging [5]                                              | . 17 |

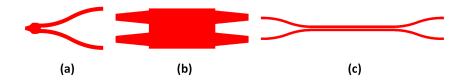

| 2.12  | (a) Y-Junction, (b) MMI coupler, and (c) directional coupler $\ldots$     | . 17 |

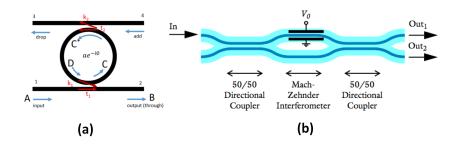

| 2.13  | (a) Ring resonator [3] and (c) MZI modulator [4]                          | . 19 |

| 2.14  | Ge based photodiodes in SOI process. (a) Vertical and (b) Lateral         |      |

|       | designs [105]                                                             | . 21 |

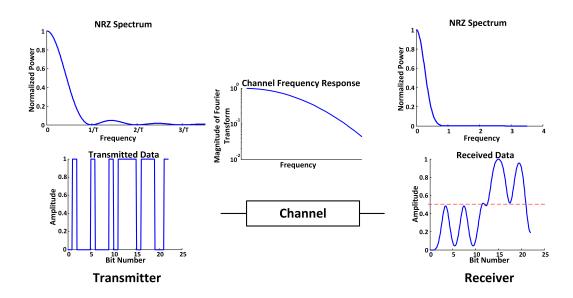

| 3.1  | Effect of bandwidth limited channel on the transmitted data. A simple  |    |

|------|------------------------------------------------------------------------|----|

|      | threshold based data recovery is not possible after removing the high  |    |

|      | frequency content of the signal.                                       | 22 |

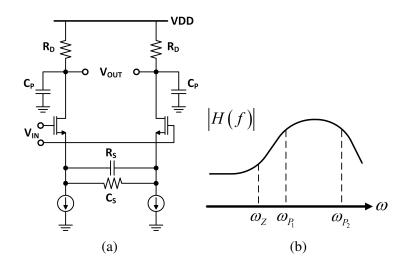

| 3.2  | (a) Example of equalizers implemented in electrical domain [68]. (b)   |    |

|      | Typical transfer function of electrical equalizers. Due to parasitic   |    |

|      | capacitances, such equalizers are band-limited.                        | 23 |

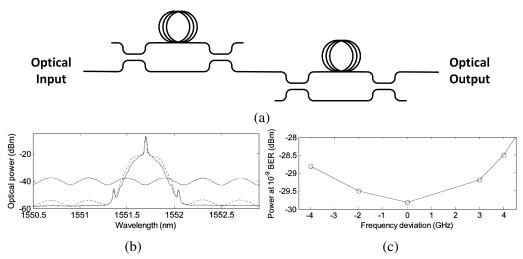

| 3.3  | (a) An example of optical equalizer implementation [56]. (b) Mea-      |    |

|      | sured optical spectra of the modulated signal without (solid line) and |    |

|      | with (dotted line) equalization. The sinusoidal line shows the trans-  |    |

|      | missivity through the equalizer. (c) Equalizer sensitivity vs. laser   |    |

|      | frequency deviation [56]                                               | 24 |

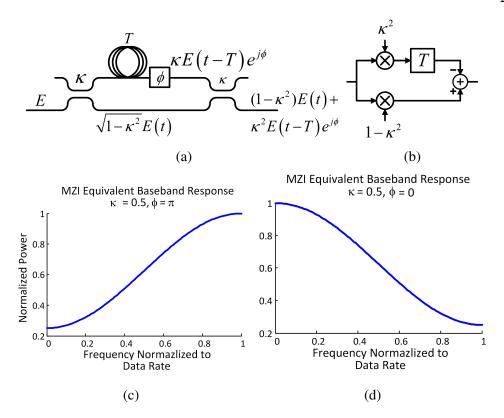

| 3.4  | (a) Example of an FIR optical equalizer implementation. (b) Block      |    |

|      | diagram of the desired filter. (c) An example of desired response. (d) |    |

|      | Undesired response of same implementation due to laser wavelength      |    |

|      | drift                                                                  | 25 |

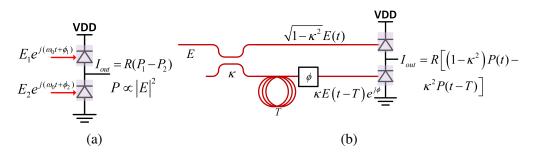

| 3.5  | (a) Optical phase independent subtraction by using photo-diodes. (b)   |    |

|      | A carrier wavelength insensitive hybrid electro-optical equalizer      | 26 |

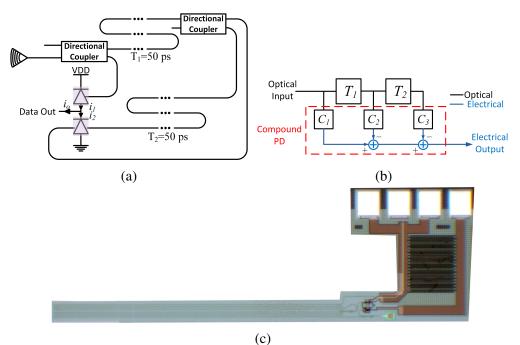

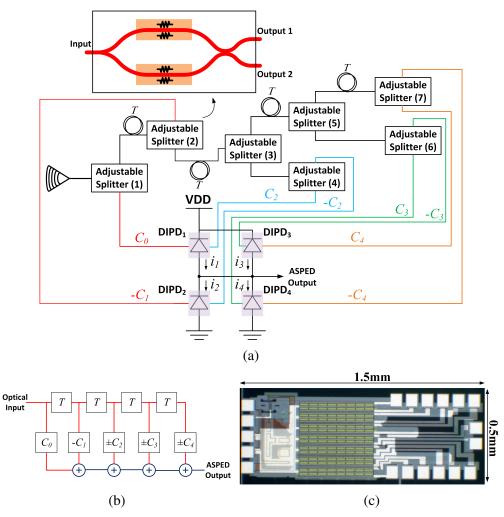

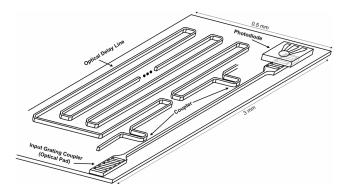

| 3.6  | Implemented 2-tap self-equalizing photo-detector. (a) The block        |    |

|      | diagram. (b) Equivalent signal flow diagram. (c) Die photo of the      |    |

|      | implemented IC.                                                        | 28 |

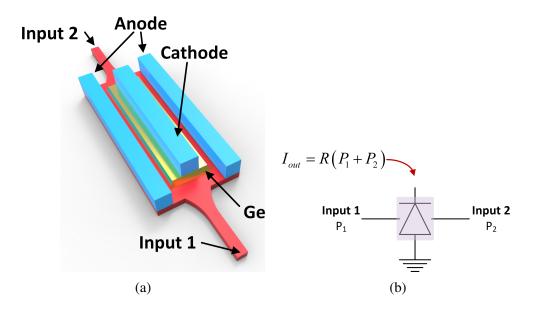

| 3.7  | (a) Dual input photo-diode and (b) its symbol. Optical power of        |    |

|      | two signal is summed and converted to electrical current within one    |    |

|      | junction                                                               | 29 |

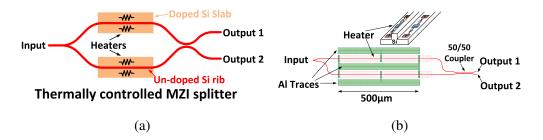

| 3.8  | Dynamic tap coefficient adjustment with a thermally controlled MZI.    |    |

|      | (a) Schematic diagram of the MZI and (b) the corresponding layout.     |    |

|      | Heaters are implemented by doping the slab section of the waveguide    |    |

|      | and passing current through them.                                      | 29 |

| 3.9  | The block diagram of implemented adjustable self-equalizing PD         |    |

|      | (ASEPD) and (b) its signal flow diagram, (c) the die photo of the      |    |

|      | ASEPD                                                                  | 31 |

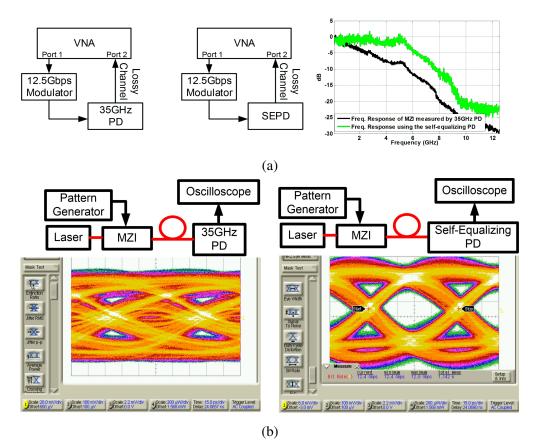

| 3.10 | Measurement results showing bandwidth enhancement in a band-           |    |

|      | width limited optical link. (a) Measurement setup for measuring the    |    |

|      | electro-optical bandwidth using a 35GHz PD and SEPD and mea-           |    |

|      | sured comparison of the two frequency responses showing 7dB of         |    |

|      | enhancement. (b) Comparison of 12.5Gbps eye-diagrams of the re-        |    |

|      | ceived data without and with SEPD                                      | 32 |

xiii

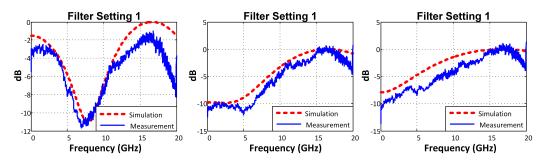

| 3.11 | Demonstration of frequency response adjustment capability in ASEPD.                                                      | 33 |

|------|--------------------------------------------------------------------------------------------------------------------------|----|

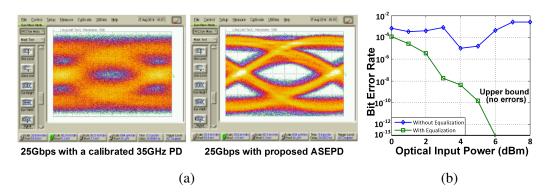

| 3.12 | (a) Demonstration of eye opening capability of the ASEPD at 25Gbps.                                                      |    |

|      | (b) Demonstration of improvement in receiver sensitivity before and                                                      |    |

|      | after utilization of ASEPD for a bandwidth limited channel at 12.5Gbps.                                                  | 33 |

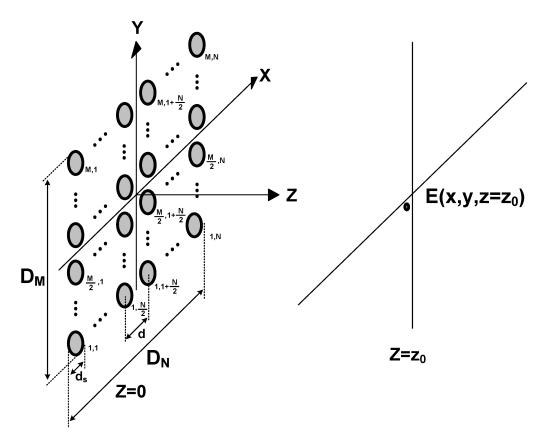

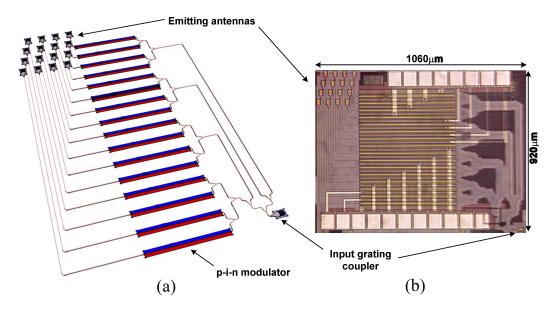

| 4.1  | The $M \times N$ -element optical phased array                                                                           | 36 |

| 4.2  | The cross section of the array patterns formed at $z_0 = 3cm$ plane for                                                  |    |

|      | an OPA with $d = 50 \mu m$ and $\lambda = 1.55 \mu m$ for both loss-less and lossy                                       |    |

|      | phase shifters. (a) $M = N = 4$ , $\alpha = \frac{\pi}{8}rad^{-1}$ , $\Delta\phi_m = \Delta\phi_n = \frac{\pi}{3}$ , and |    |

|      | (b) $M = N = 16, \alpha = \frac{3\pi}{16}rad^{-1}, \Delta\phi_m = \Delta\phi_n = \frac{\pi}{3}$                          | 39 |

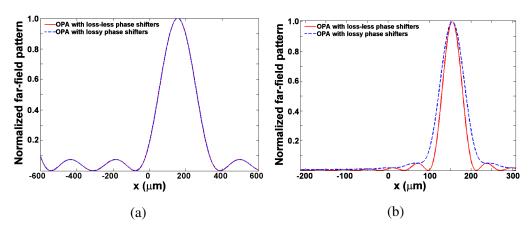

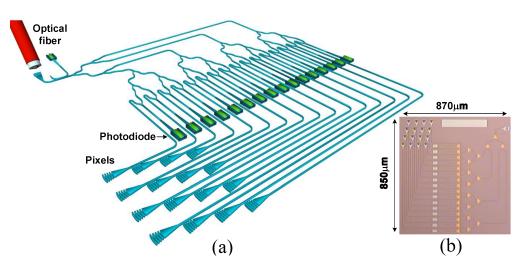

| 4.3  | (a) The structure of the reported $4 \times 4$ integrated optical phased array                                           |    |

|      | with perchannel high speed phase control and (b) the chip micro-                                                         |    |

|      | photograph of the fabricated OPA.                                                                                        | 40 |

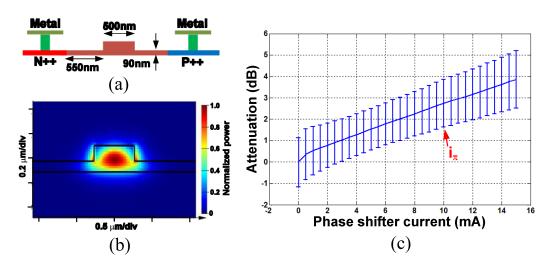

| 4.4  | (a) The cross section of the p-i-n phase modulator used in the proposed                                                  |    |

|      | OPA, (b) the propagation mode profile of the modulator, and (c) the                                                      |    |

|      | measured excess attenuation of the p-i-n modulators in proposed OPA.                                                     | 41 |

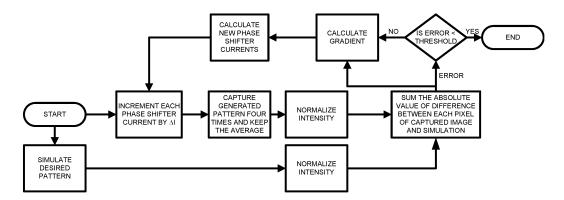

| 4.5  | The flowchart of the optimization process                                                                                | 41 |

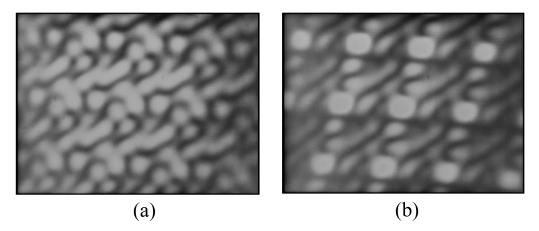

| 4.6  | The pattern of the OPA for zero relative phase setting ( $\Delta \phi_m = \Delta \phi_n =$                               |    |

|      | 0) captured using FJW View-R-Scope 85400A IR camera;(a) before                                                           |    |

|      | $gradient \ decent \ optimization, \ and \ (b) \ after \ gradient \ decent \ optimization.$                              | 43 |

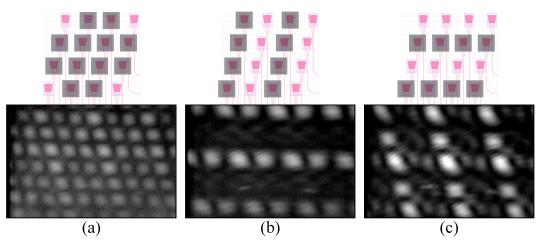

| 4.7  | Top: the OPA element radiation status (only highlighted elements are                                                     |    |

|      | radiating), bottom: the far-field pattern. (a) The far-field pattern of                                                  |    |

|      | the OPA when all elements except for the ones at the corners of the                                                      |    |

|      | array are turned off (b) the far-field pattern of the OPA when elements                                                  |    |

|      | on every other columns are turned off, and (c) the far-field pattern of                                                  |    |

|      | the OPA when all elements on every other rows are turned off                                                             | 44 |

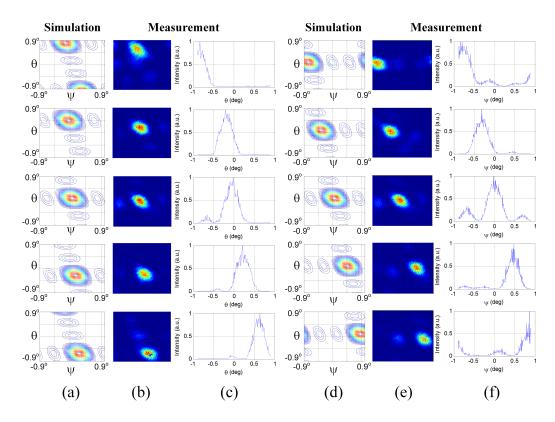

| 4.8  | The vertical beam steering; (a) simulation, (b) measurement, and                                                         |    |

|      | (c) far-filed pattern cross section. The horizontal beam steering;(d)                                                    |    |

|      | simulation, (e) measurement, and (f) farfiled pattern cross section                                                      | 45 |

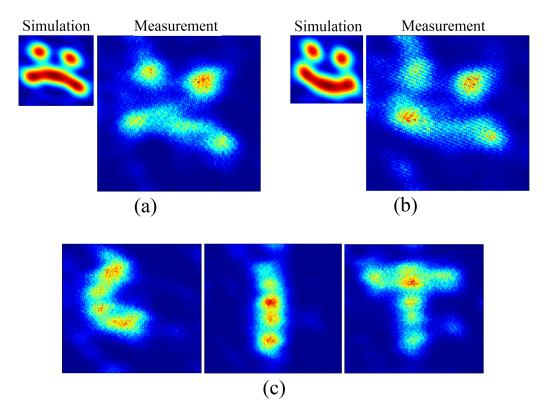

| 4.9  | Projected images by fast vector scan of the beam spot; (a) smiley                                                        |    |

|      | face (simulation on left), (b)sad face (simulation on left), and (c)                                                     |    |

|      | individual letters of CIT (California Institute of Technology)                                                           | 46 |

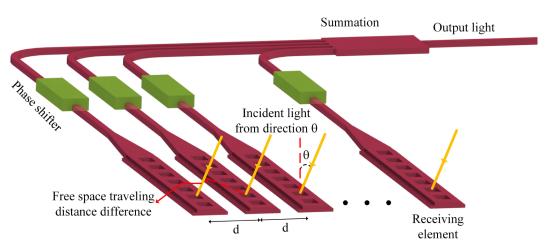

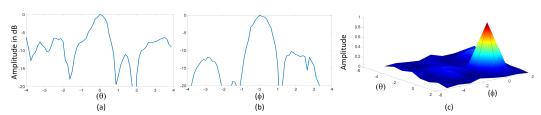

| 5.1  | Conceptual schematic of a 1D optical phased array receiver                                                               | 49 |

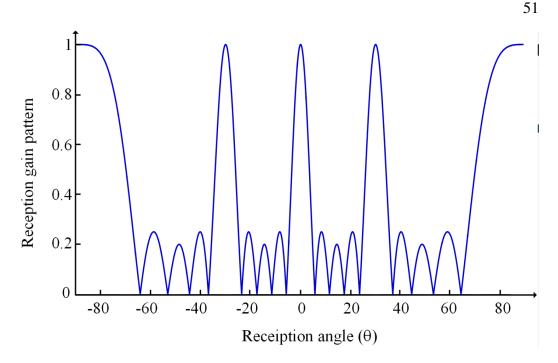

| 5.2  | Array pattern for a 5-element array with spacing $2\lambda$ and omnidirectional.                                         | 51 |

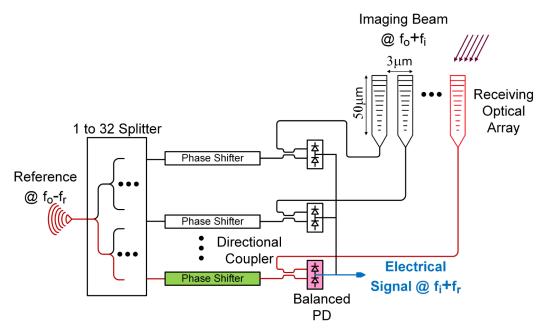

| 5.3  | The schematic structure of the designed heterodyne OPA receiver.                                                         |    |

|      | Colored path shows the processing of a single element                                                                    | 53 |

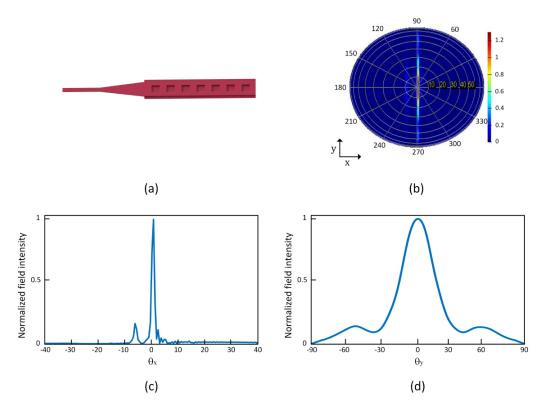

| 5.4  | (a) Simplified illustration of 1D grating coupler (b) Far-field pattern        |    |

|------|--------------------------------------------------------------------------------|----|

|      | of the grating coupler on a hemisphere (c) Far-filed pattern of the            |    |

|      | grating coupler at $\theta_y = 0$ (d) Far-filed pattern of the grating coupler |    |

|      | at $\theta_x = 1^\circ$ .                                                      | 54 |

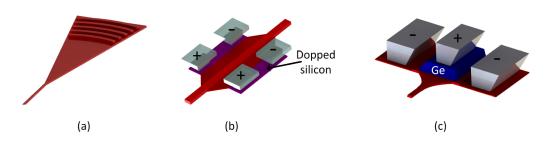

| 5.5  | (a) Focusing grating coupler (b) Thermal phase shifter (c) Germa-              |    |

|      | nium photodiode                                                                | 56 |

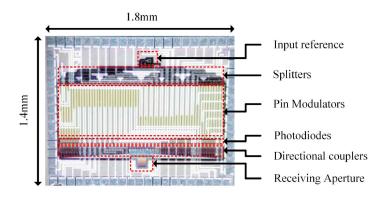

| 5.6  | Fabricated OPA receiver chip.                                                  | 57 |

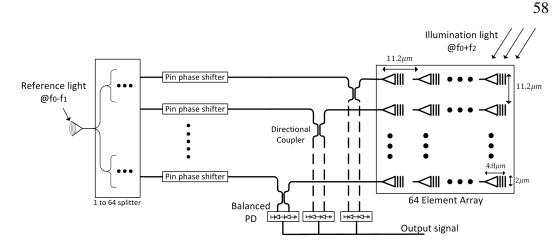

| 5.7  | Block diagram of 8×8 phased array receiver                                     | 58 |

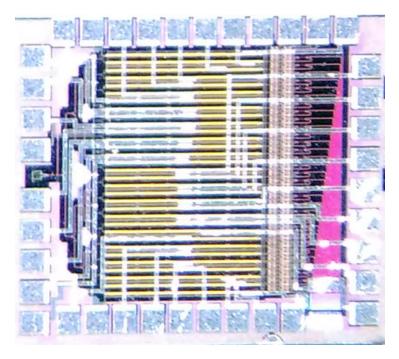

| 5.8  | Die photo of fabricated $8 \times 8$ OPA receiver chip implemented in IME      |    |

|      | process                                                                        | 58 |

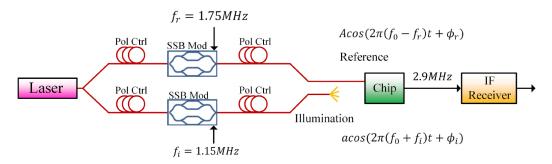

| 5.9  | Block diagram of the measurement setup                                         | 59 |

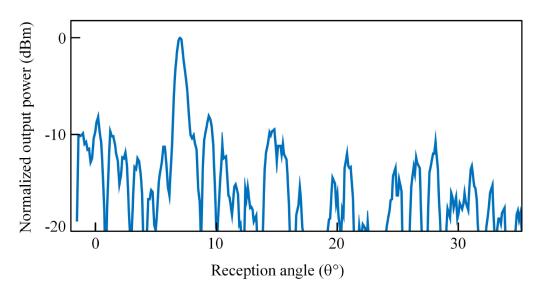

| 5.10 | Measured reception pattern of the OPA receiver for $7^{\circ}$                 | 60 |

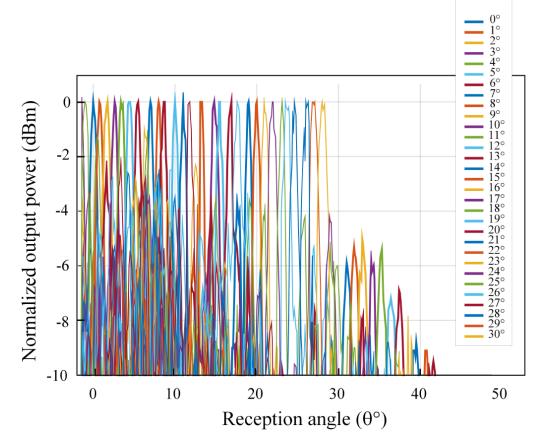

| 5.11 | Measured reception pattern of the OPA receiver for $0^{\circ} - 30^{\circ}$    | 61 |

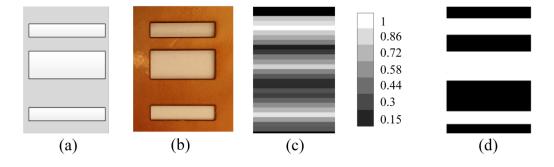

| 5.12 | (a) Barcode design, (b) Fabricated barcode from copper sheet, (c)-(d)          |    |

|      | Captured image of the barcode in gray-scale and B&W with the OPA               |    |

|      | camera                                                                         | 61 |

| 5.13 | (a) Normalized receiving pattern cross section of yz-plane (b) Nor-            |    |

|      | malized receiving pattern cross section of xy-plane. (c) Normalized            |    |

|      | 3D pattern                                                                     | 62 |

| 5.14 | (a) Sanded plexiglass (b) Copper tape covered imaging target. (c)              |    |

|      | Captured image in gray scale.                                                  | 62 |

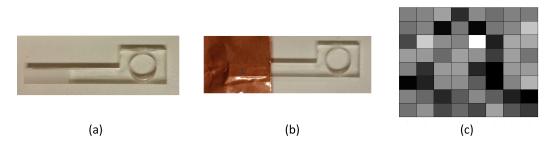

| 6.1  | (a) The structure of the $4 \times 4$ NCI, in which the light coming from      |    |

|      | the object is collected using 16 grating couplers (pixels) is shown. A         |    |

|      | fraction of the coherent light that is used to illuminate the object is        |    |

|      | guided using an optical fiber and is coupled into the chip through a           |    |

|      | grating coupler. This coupled light is combined with the collected             |    |

|      | optical signals from the object and is photo-detected using on-chip            |    |

|      | silicon-germanium photodiodes. (b) The NCI micro-photograph im-                |    |

|      | plemented on standard IME silicon-on-insulator process.                        | 65 |

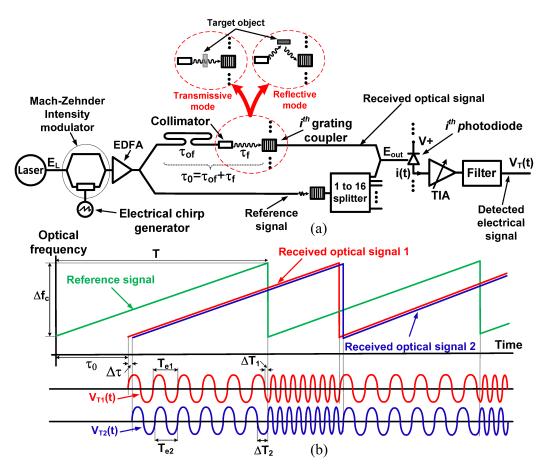

- Simplified block diagram of the imaging system for one pixel (grating 6.2 coupler) is shown. (b) The optical and electrical signals at different points of the imager are depicted. The number of zero crossings per chirp period is used as a coarse estimate for the delay difference between the top arm and the bottom arm. The time difference between the last zero crossing in  $V_{T1}(t)$  and  $V_{T2}(t)$  and the end of the frequency ramp is used to find the fine estimate for the relative delay between two arms.

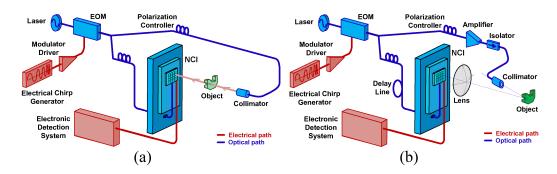

- The block diagram of the transmissive measurement setup using in-6.3 tegrated NCI is shown. The collimated infrared beam passes through the substantially transparent object (at the operating wavelength) and is collected by the 16 pixels of the imager. The collected optical signal is combined with the reference signal, a fraction of the coherent source output is used for illuminating the object, and is photo-detected. The photo-current is then directed to the electronic detection system. (b) The block diagram of the reflective mode measurement setup is depicted. The amplified output of the coherent source is collimated and is used to illuminate the object. A lens is

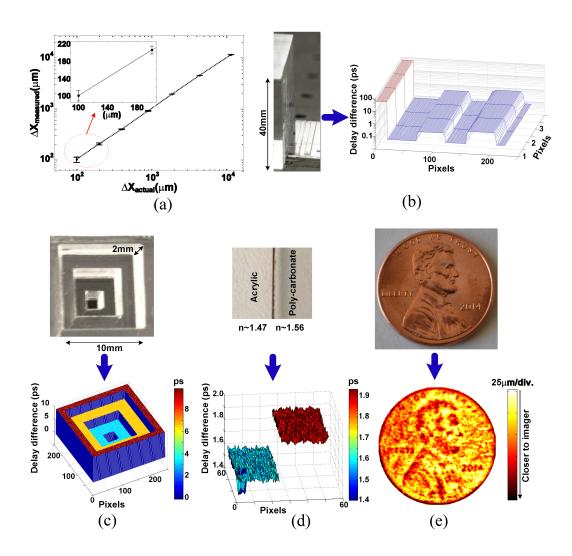

- Fig. 4. (a) The measured distance vs. actual distance in  $\mu$ m for 6.4 transmissive mode is shown. (b) The concurrent high depth resolution and large dynamic range offered by the integrated NCI in the transmissive mode is demonstrated. A 4cm object and two small pedestals with sub-100 $\mu$ m depth difference are concurrently imaged (left: the object, right: the 3D image). (c) The transmissive 3D image of a transparent pyramid is shown (top: the object, bottom: the 3D image). (d) The index of refraction contrast imaging using integrated NCI is demonstrated; top: two materials with the same thickness, bottom: the index contrast image. (e) The depth image of the US one-cent coin taken using the integrated NCI in the reflective mode is shown. The measured free-space relative propagation delay corresponding to the image depth is represented by pixel colors; pixels represented by dark red are closer to the imager. The image is

66

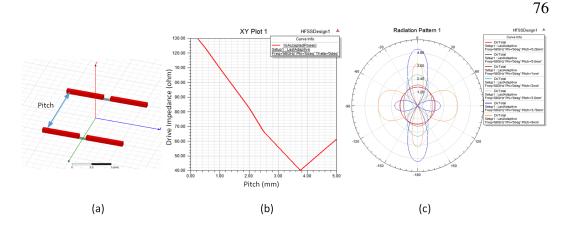

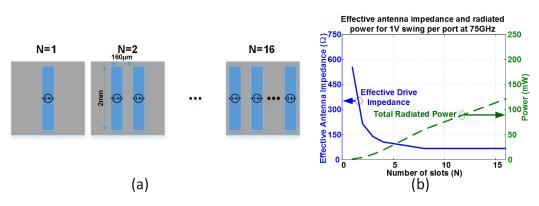

| 7.1  | Coupling of two dipole antennas. (a) Simulation setup. (b) Effective drive impedance and (c) radiation pattern as a function of pitch of the |    |

|------|----------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | two dipoles.                                                                                                                                 | 76 |

| 7.2  | (a) An example of tightly coupled slot array antenna. (b) Effective                                                                          |    |

|      | drive impedance of tightly coupled slot antennas and total radiated                                                                          |    |

|      | power assuming 1V swing per port.                                                                                                            | 78 |

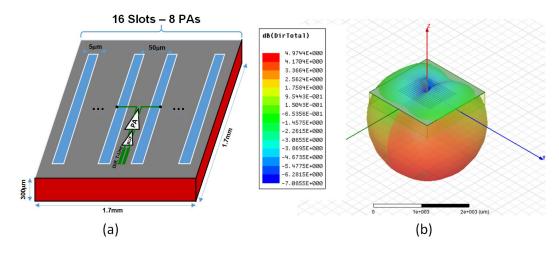

| 7.3  | (a) Dimension of implemented on chip slot array. (b) Simulated                                                                               |    |

|      | radiation pattern.                                                                                                                           | 79 |

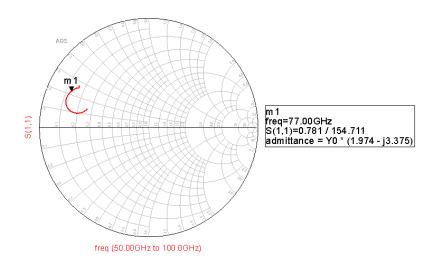

| 7.4  | Effective impedance of radiator from each port (All ports are driven                                                                         |    |

|      | in phase)                                                                                                                                    | 80 |

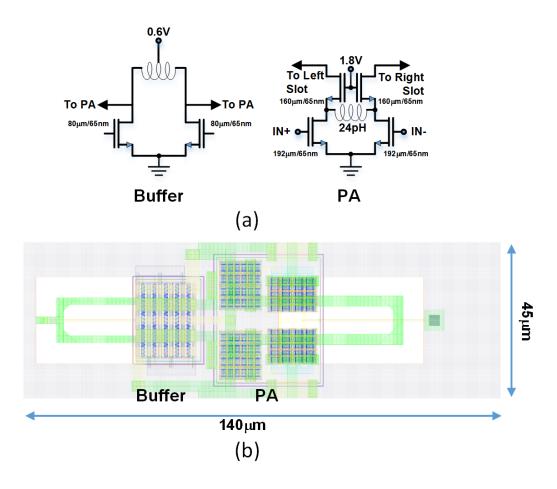

| 7.5  | (a) Schematic of PA driver (Buffer) and PA. (b) Layout of the PA and                                                                         |    |

|      | Buffer                                                                                                                                       | 80 |

| 7.6  | Block diagram of implemented IC.                                                                                                             | 81 |

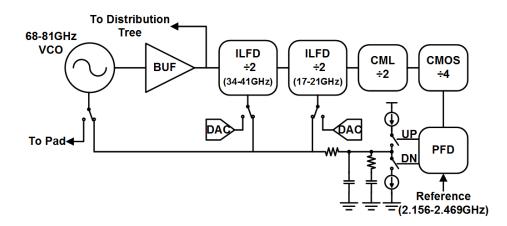

| 7.7  | Schematic of VCO and ILFD                                                                                                                    | 82 |

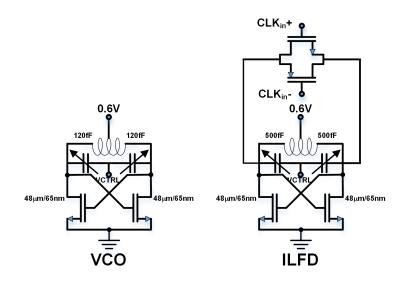

| 7.8  | Layout of the 77GHz distribution tree                                                                                                        | 82 |

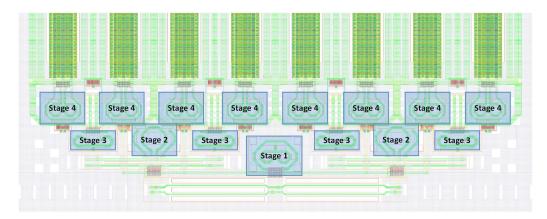

| 7.9  | (a) Die photo of fabricated chip. (b) Measurement Setup                                                                                      | 83 |

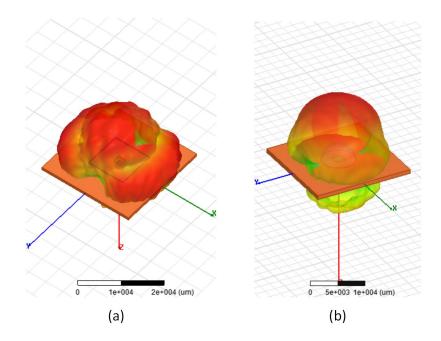

| 7.10 | (a) Radiation pattern with $1 cm \times 1 cm \times 300 \mu m$ diamond heatsink and                                                          |    |

|      | (b) with 6.35mm diameter hemispherical aluminum oxide lens                                                                                   | 84 |

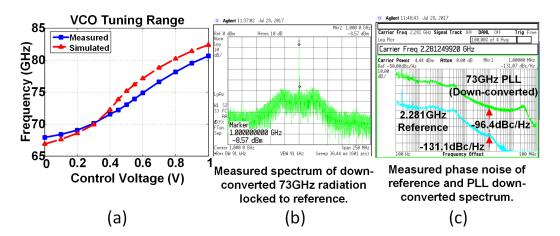

| 7.11 | (a) Tuning range of VCO. (b) Down-converted spectrum of locked                                                                               |    |

|      | PLL at 73GHz. (c) Phase noise measurement of the VCO                                                                                         | 84 |

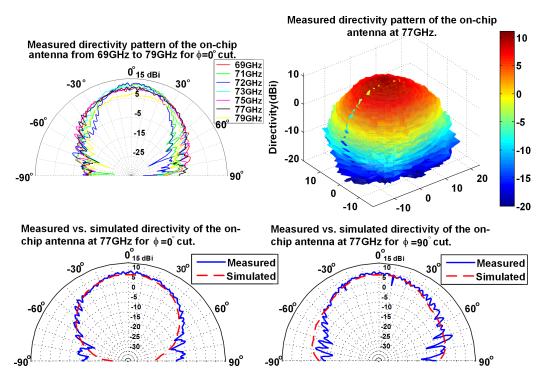

| 7.12 | Measured pattern of the antenna form 69GHz to 79GHz. The full 3D                                                                             |    |

|      | pattern for 77GHz is shown on top right.                                                                                                     | 86 |

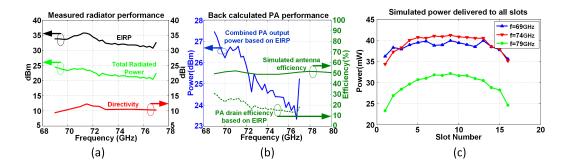

| 7.13 | (a) Measured EIRP, Directivity and TRP of the radiator. (b) Simulated                                                                        |    |

|      | antenna efficiency and calculated total PA output power and its drain                                                                        |    |

|      | efficiency. (c) Simulated power delivered to each port of the radiator.                                                                      | 87 |

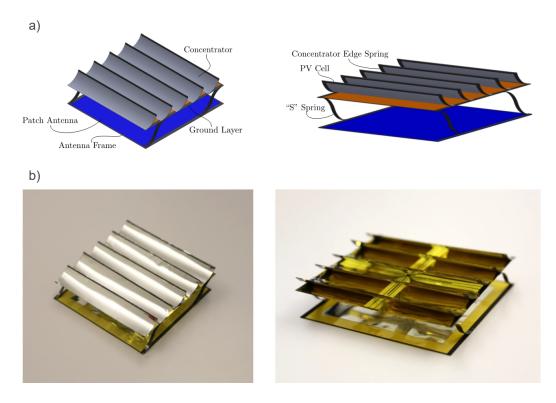

| 8.1  | (a) Schematics of general modular tile architecture and (b) Fabricated                                                                       |    |

|      | mock-up prototypes.                                                                                                                          | 89 |

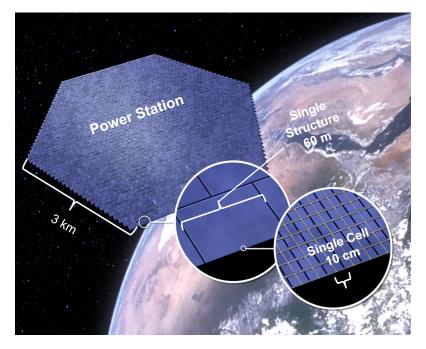

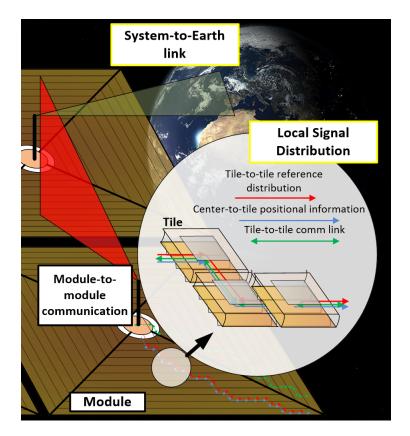

| 8.2  | Conceptual drawing of the power station in orbit with detail inset                                                                           |    |

|      | showing the organizational hierarchy.                                                                                                        | 90 |

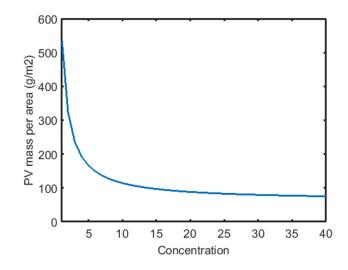

| 8.3  | Areal density vs. concentration for PV + concentrator                                                                                        | 91 |

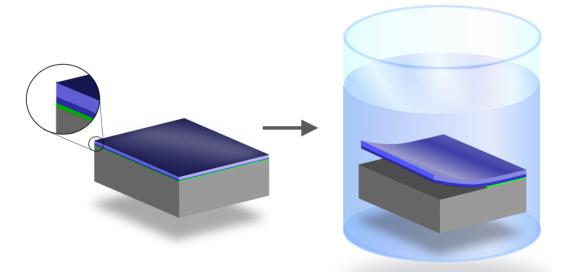

| 8.4  | Schematic of the epitaxial liftoff process. The weight of the photo-                                                                         |    |

|      | voltaic component can be further reduced by removing the inactive                                                                            |    |

|      | growth substrate from the device.                                                                                                            | 92 |

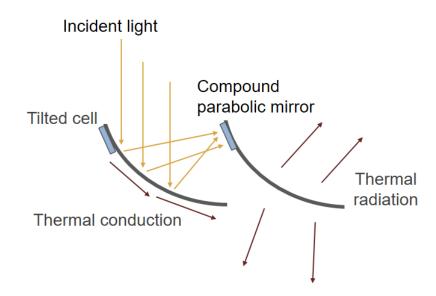

| 8.5  | Schematic of parabolic half trough concentrator.                                                                                             | 93 |

xvii

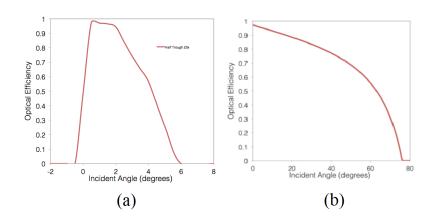

| 8.6  | Simulated optical efficiency as a function of angle for $20 \times$ concentration along a) the concentrating axis and b) along the non- |

|------|-----------------------------------------------------------------------------------------------------------------------------------------|

|      | concentrating axis                                                                                                                      |

| 8.7  | Thermal simulations for different concentration and $20\mu m$ aluminum                                                                  |

|      | heat spreader                                                                                                                           |

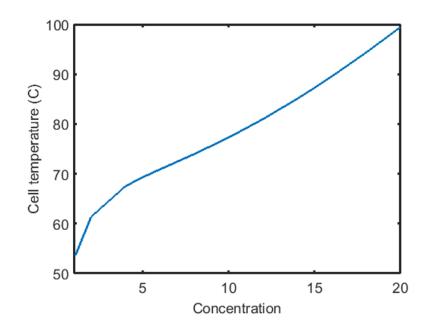

| 8.8  | a) Optical efficiency as a function of wavelength for a 20x Ag Venetian                                                                 |

|      | blind concentrator (gray) and external quantum efficiencies for each                                                                    |

|      | junction of a common triple junction space solar cell. b) Expected                                                                      |

|      | spectral current generation for a triple junctrion solar cell in a 20x                                                                  |

|      | Venetian blind Ag concentrator under AM0 illumination 96                                                                                |

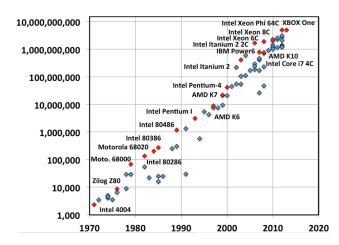

| 8.9  | Transistor count of commercial CPUs by year [166]                                                                                       |

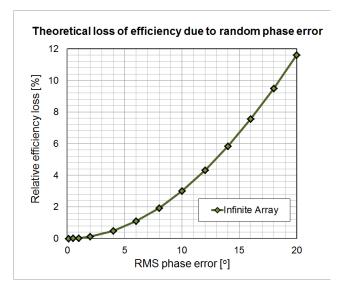

| 8.10 | Theoretical loss of RF power in main lobe due to random phase errors. 99                                                                |

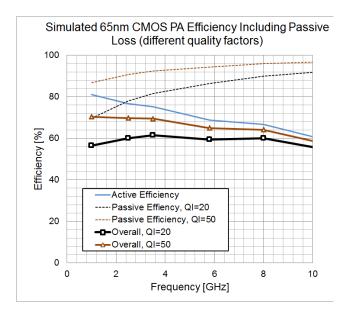

| 8.11 | Simulated active only, passive only and overall PA efficiency over                                                                      |

|      | frequency for required output power levels and power enhancement                                                                        |

|      | ratios                                                                                                                                  |

| 8.12 | Hierarchical signal and reference distribution                                                                                          |

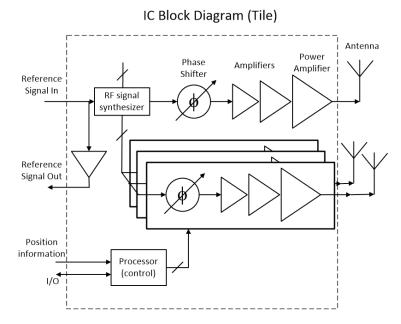

| 8.13 | Simplified block diagram of RF integrated tile electronics. The refer-                                                                  |

|      | ence signal is used to locally generate an RF signal and can be locally                                                                 |

|      | buffered for redistribution                                                                                                             |

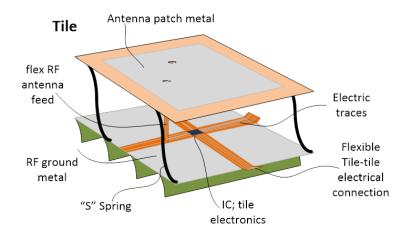

| 8.14 | Tile structure (not shown to scale) showing patch antenna metal and                                                                     |

|      | ground layer, location of integrated circuit and electrical connections 105                                                             |

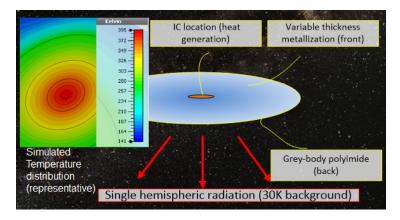

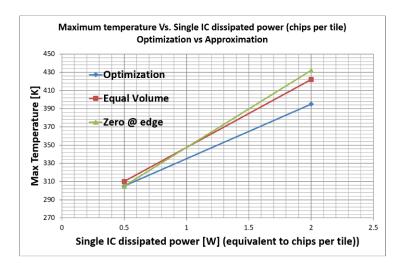

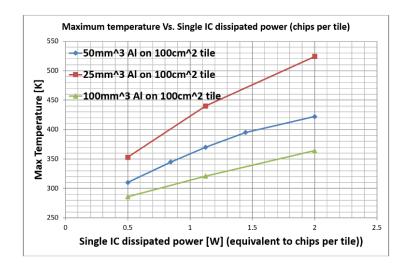

| 8.15 | Simulation setup for simulating the temperature rise of the integrated                                                                  |

|      | circuit in the tile                                                                                                                     |

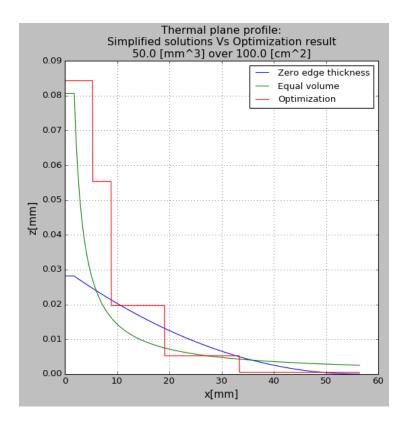

| 8.16 | Metallization thickness profiles from center (IC location) to edge of                                                                   |

|      | tile for a nominal metallization of $5\mu m$ Al equivalent                                                                              |

| 8.17 | Simulated IC temperature for three metalization profiles using a total                                                                  |

|      | Al volume of $50$ mm <sup>3</sup>                                                                                                       |

| 8.18 | Effect of Aluminum thickness on the IC's temperature 109                                                                                |

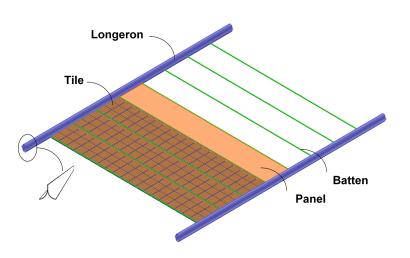

| 8.19 | A short segment of a single strip. The longeron has a cross-section                                                                     |

|      | similar to a TRAC boom. For clarity, some of the tiles have been                                                                        |

|      | omitted                                                                                                                                 |

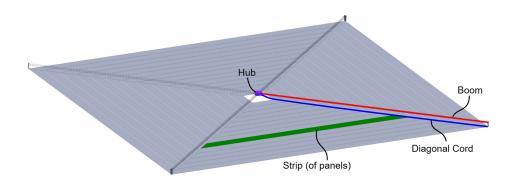

| 8.20 | Spacecraft structural architecture                                                                                                      |

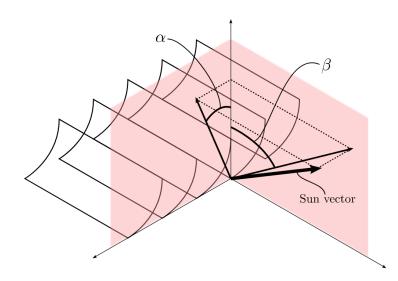

| 8.21 | The sun vector at each tile is decomposed into a component in the                                                                       |

|      | plane of concentration, at an angle $\alpha$ to the tile normal, and a com-                                                             |

|      | ponent perpendicular to the plane of concentration, at an angle $\beta$ 114                                                             |

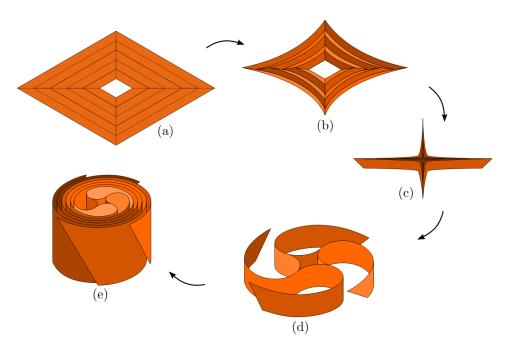

| 8.22 | Spacecraft packaging concept. For clarity, only the outermost strips            |

|------|---------------------------------------------------------------------------------|

|      | are shown in (d) and (e)                                                        |

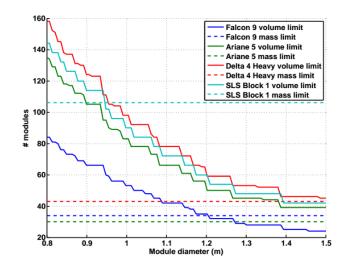

| 8.23 | Number of modules that can be fit within the payload fairing of typical         |

|      | launch vehicles for different diameters of the packaged modules 118             |

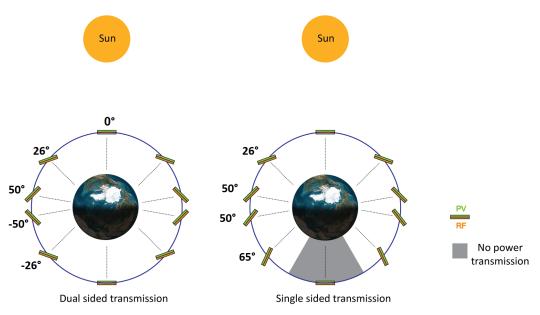

| 8.24 | Single and dual-sided capacity factor schematic                                 |

| 8.25 | General rectenna structure                                                      |

| 8.26 | Initial mechanical prototype of our space based solar power tile 124            |

| 8.27 | Block diagram of reference distribution inside the DC to RF IC 125              |

| 8.28 | (a) Block diagram of clock multiplier unit (CMU). (b) Die photograph            |

|      | of the test structure                                                           |

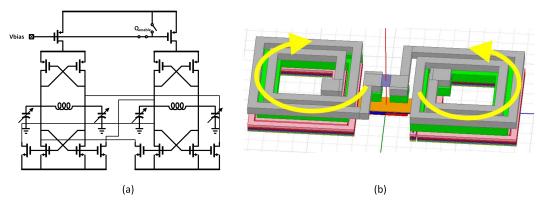

| 8.29 | (a) Quadrature VCO schematic (b) Compact figure 8 inductor design               |

|      | for the QVCO                                                                    |

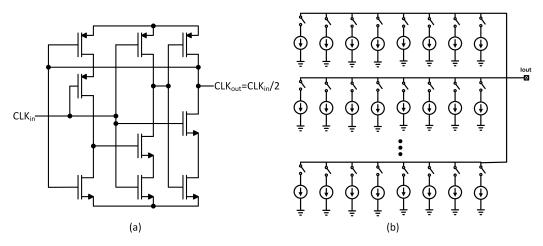

| 8.30 | (a) Clock divider based on true single phase DFF, (b) Thermometer               |

|      | coded current DAC                                                               |

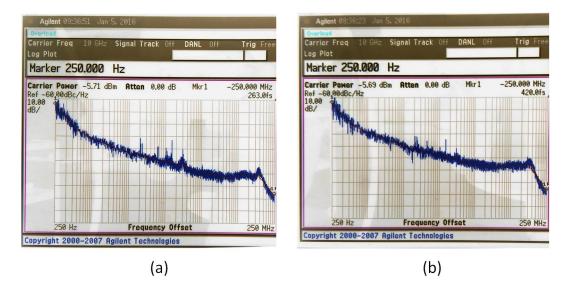

| 8.31 | Phase noise and jitter of the CMU test structure when (a) DAC current           |

|      | is set to zero and (b) when DAC current is at full range                        |

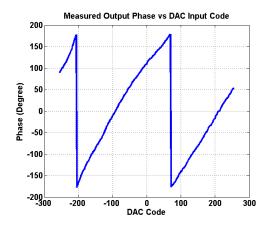

| 8.32 | Measured output phase vs DAC input code of CMU                                  |

| 8.33 | (a) Schematic of a simple diode rectifier and (b) the corresponding             |

|      | voltage and current waveforms                                                   |

| 8.34 | (a) Block diagram of proposed harmonic termination for the rectifier,           |

|      | and (b) idealized voltage waveforms                                             |

| 8.35 | (a)-(b)Two prototypes of the rectifier designed with (c), (d) their             |

|      | conversion efficiencies over input power and (e), (f) total efficiencies        |

|      | over frequency                                                                  |

| 8.36 | (a) The dual polarized patch antenna and (b) its S11                            |

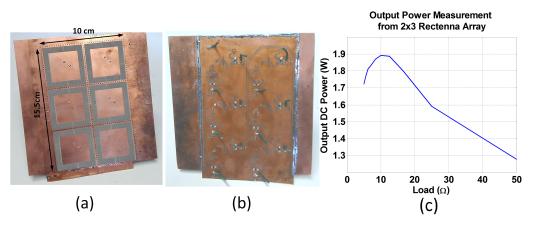

| 8.37 | (a) Front and (b) back side of the 2x3 rectenna array. (c) Output DC            |

|      | power vs load                                                                   |

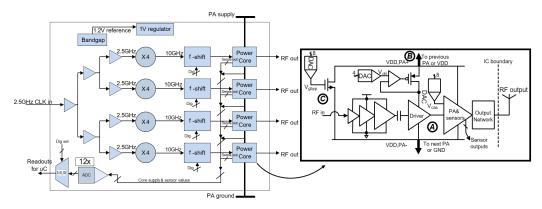

| 8.38 | Simplified block diagram of the integrated X-Band power amplifier               |

|      | quad                                                                            |

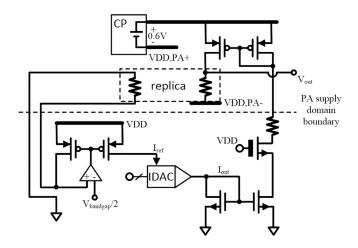

| 8.39 | Bias current generation used for crossing supply domain boundaries.             |

|      | DACs and regulators operate in the common supply domain, provid-                |

|      | ing currents across boundaries to generate voltage offsets proportional         |

|      | to a bandgap voltage in the PA supply domains                                   |

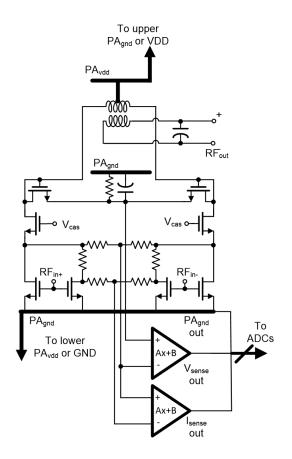

| 8.40 | Circuit detail for PA core, cascode peak voltage, and DC current                |

|      | detectors, as well as supply level readout for digitally assisted operation 137 |

| 8.41 | Die photograph of implemented power amplifier quadrant                          |

xix

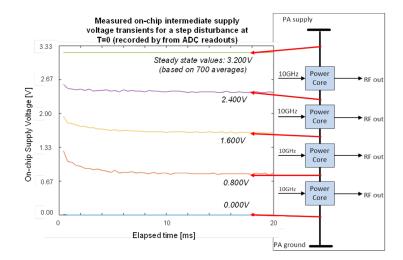

| 8.42 | Measured supply voltage regulation for PSD controller under distur-      |

|------|--------------------------------------------------------------------------|

|      | bance at iteration t=0                                                   |

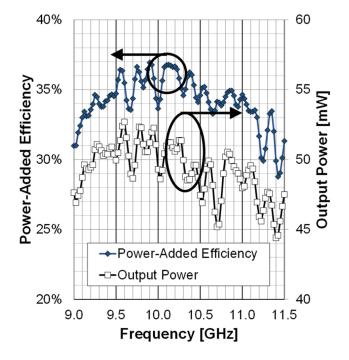

| 8.43 | Measured PAE and output power over frequency                             |

| 8.44 | Measured output power over cascode voltage                               |

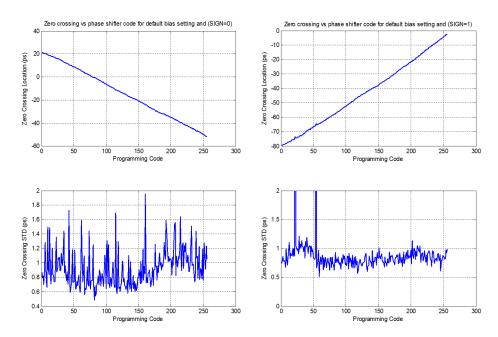

| 8.45 | Measured relative signal zero crossing location and standard devia-      |

|      | tion versus phase program for positive (left) and negative (right) code  |

|      | settings. The absolute crossing times for a programming code of zero     |

|      | coincide for a total of 140ps of timing control                          |

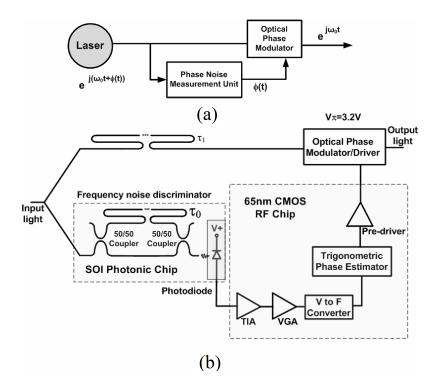

| 9.1  | (a) The conceptual block diagram of a feed-forward laser phase noise     |

|      | reduction, and (b) the block diagram of the proposed phase noise         |

|      | reduction scheme                                                         |

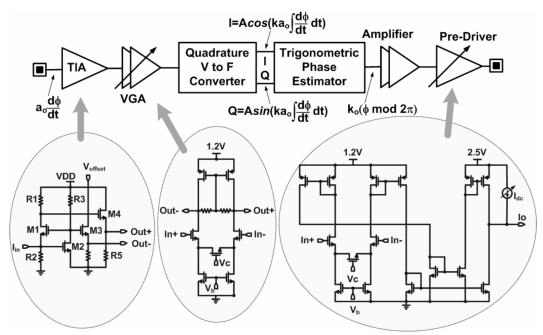

| 9.2  | The block diagram of the proposed architecture implemented in a          |

|      | CMOS RF chip                                                             |

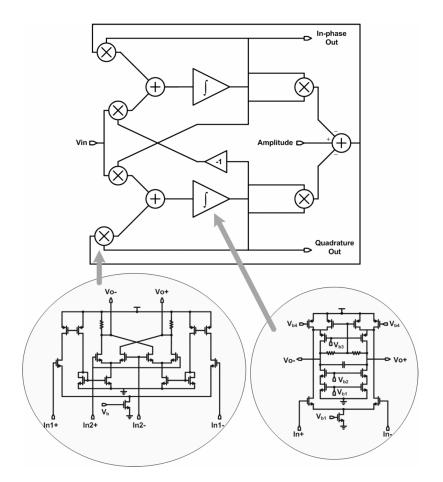

| 9.3  | (a) The block diagram of a direct voltage-to-frequency converter,        |

|      | (b) the folded balanced Gilbert cell multiplier, and (c) the non-ideal   |

|      | integrator                                                               |

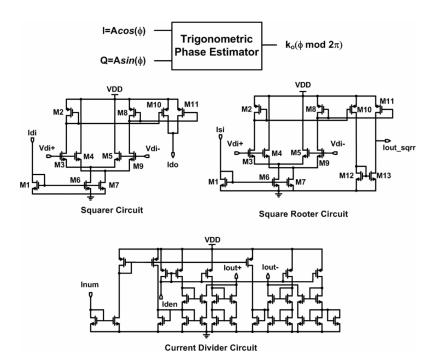

| 9.4  | The schematics of the squarer, the square-rooter, and the current        |

|      | divider as the building blocks of the trigonometric phase estimator      |

|      | are shown                                                                |

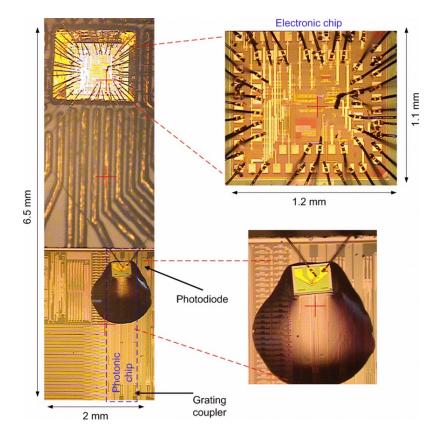

| 9.5  | The integrated frequency noise discriminator implemented in IMEC         |

|      | SOI process                                                              |

| 9.6  | The micro-photograph of the RF chip (fabricated in a 65nm CMOS           |

|      | process) and the hybrid integration with photonic SOI chip (with         |

|      | 100nm minimum feature size) and the photodiode                           |

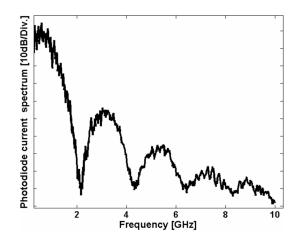

| 9.7  | The output frequency spectrum of the photonic frequency discrimi-        |

|      | nator chip                                                               |

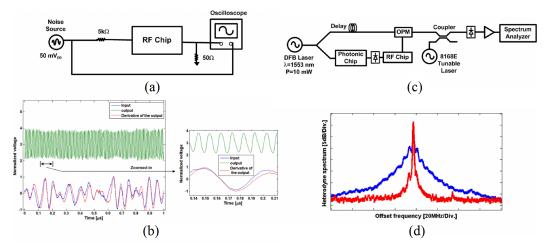

| 9.8  | (a) The RF chip stand-alone measurement setup, (b) the measured          |

|      | integration and wrapping performance of the RF chip, (c) the laser       |

|      | phase noise reduction measurement setup, and (d) the measured laser      |

|      | spectrum before and after phase noise reduction                          |

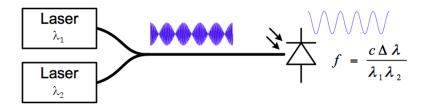

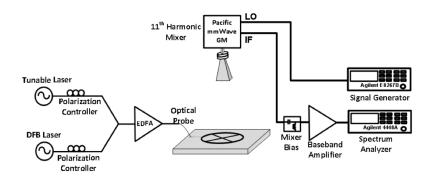

| 9.9  | Optoelectronic mm-Wave generation                                        |

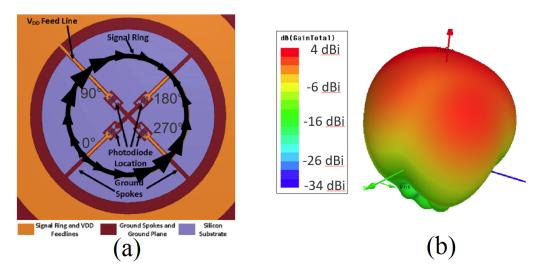

| 9.10 | (a) Multi-port radiator with traveling wave current overlay and (b)      |

|      | associated radiation pattern with silicon substrate at 180GHz 151        |

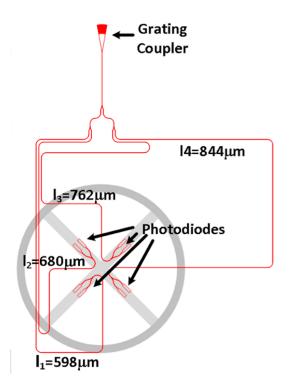

| 9.11 | Layout of optical multi-port driven radiator's optical distribution net- |

|      | work                                                                     |

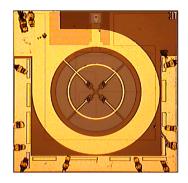

| 9.12 | Die photo of the fabricated optoelectronic radiator                      |

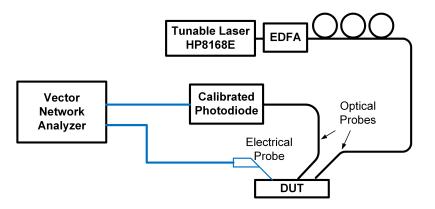

| 9.13 | Measurement setup.                                                     | 154 |

|------|------------------------------------------------------------------------|-----|

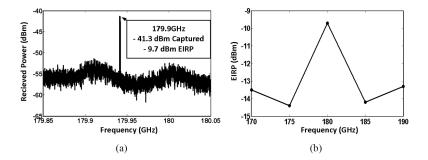

| 9.14 | Calibrated spectrum of the measured broadside radiation at 180 GHz     |     |

|      | (a), and measured frequency response of the effective isotropically    |     |

|      | radiated power (EIRP) in the broadside direction (b).                  | 154 |

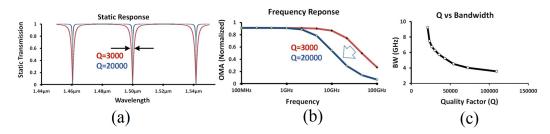

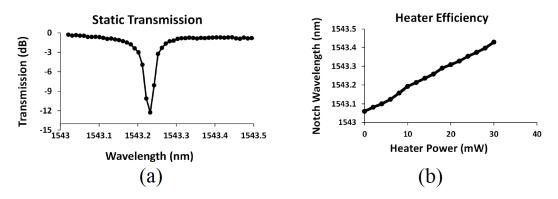

| 9.15 | Index-modulated ring's (a) static transmission (b) optical frequency   |     |

|      | response (c) simulated Q vs -3dB bandwidth                             | 155 |

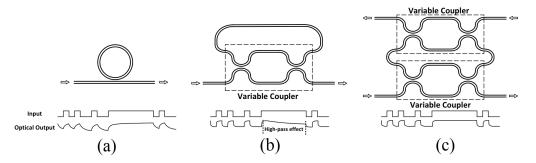

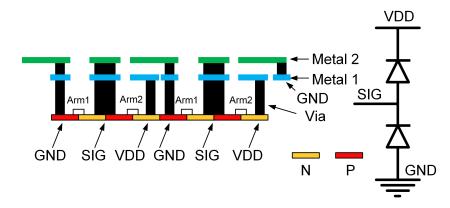

| 9.16 | (a) Index-modulated ring (b) Coupling-modulated ring (c) Proposed      |     |

|      | differential ring modulator                                            | 155 |

| 9.17 | Block diagram of the differential ring modulator                       | 156 |

| 9.18 | Die micrograph of the fabricated prototype and measurement setup.      |     |

|      | (a) Optical input grating coupler (b) Y-junction (c) heater for phase  |     |

|      | shift controller (d) photodiode connected to one output for testing    |     |

|      | purposes (e) Optical output grating coupler                            | 157 |

| 9.19 | Measurement setup                                                      | 158 |

| 9.20 | Output eye diagram of the differential ring modulator opening at (a)   |     |

|      | 5Gbps (b) 10Gbps                                                       | 158 |

| 9.21 | (a) Measured steady-state transmission of the ring near a notch (b)    |     |

|      | tunability of the ring                                                 | 159 |

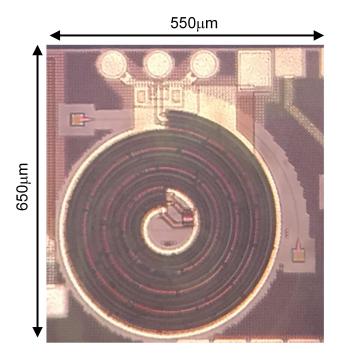

| 9.22 | Die photo of spiral MZI modulator                                      | 160 |

| 9.23 | Partial cross section of the MZI structure. The spiral MZI allows for  |     |

|      | a push-pull operation of the phase shifters                            | 160 |

| 9.24 | Measurement setup for characterizing the modulator Bandwidth           | 161 |

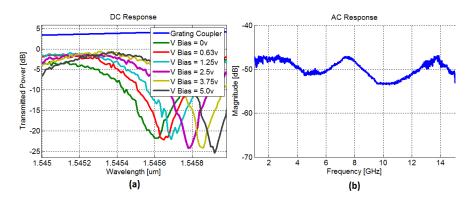

| 9.25 | (a) Measured DC response of the modulator (b) Measured frequency       |     |

|      | response of the modulator                                              | 161 |

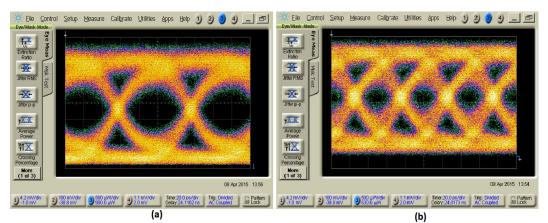

| 9.26 | (a) 12.5Gbps eye diagram, (b) 20Gbps eye diagram                       | 162 |

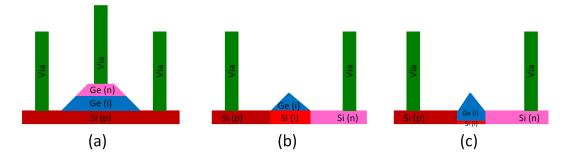

| 9.27 | (a) Vertical PD provided in IME design kit. (b) Lateral PD utilizing   |     |

|      | self stop property of Ge growth. (c) Proposed lateral PD with reduced  |     |

|      | transit time due to increased overlap of junction electrical field and |     |

|      | generated free carriers                                                | 162 |

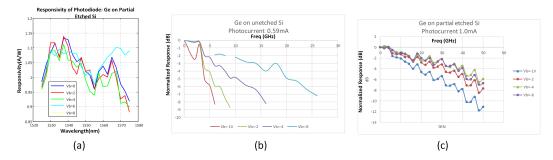

| 9.28 | (a) Measured responsivity of proposed PD for different reverse bias    |     |

|      | voltages. (b) Frequency response of PD on unetched Si for photocur-    |     |

|      | rent of 0.6mA. (c) Frequency response of proposed photodiode for       |     |

|      | photo current of 1.0mA                                                 | 163 |

|      |                                                                        |     |

xxi

# LIST OF TABLES

| Numbe | r Pag                                                                                       | <i>ze</i> |

|-------|---------------------------------------------------------------------------------------------|-----------|

| 7.1   | Comparison table of proposed radiator with state of the art designs 8                       | 7         |

| 8.1   | Impact of ripples in support structure on antenna performance 10                            | 6         |

| 8.2   | (a) Breakdown of mass contributions and total mass for a $10 \text{cm} \times 10 \text{cm}$ |           |

|       | tile. and (b) for a 60m×60m module                                                          | 9         |

| 8.3   | Performance summary and comparison to prior work                                            | -1        |

| 9.1   | Performance summary and comparison with other works 14                                      | .9        |

## NOMENCLATURE

- AGC. Automatic Gain Control.

- AOC. active optical cable.

- **ASEPD.** Adjustable Self-Equalizing Photo-Diode.

- **ASIC.** Application Specific Integrated Circuit.

- CFRP. Carbon Fiber Reinforced Plastic.

- CMU. Clock Multiplier Unit.

- DAR. Distributed Active Radiator.

- **DDD.** Displacements Damage Dose.

- **DFB.** Distributed Feed-Back.

- EDFA. Erbium Doped Fiber Amplifier.

- EIRP. Effective Isotropic Radiated Power.

- GEO. Geostationary Earth Orbit.

- **IC.** Integrated Circuit.

- **ILFD.** Injection Locked Frequency Divider.

- LEO. Low Earth Orbit.

- LNA. Low Noise Amplifier.

- LUT. Look-up Table.

- MCU. Micro-Controller Unit.

- MMF. multi-mode fiber.

- MPD. Multi-Port Driven.

- MZI. Mach-Zehnder Interferometer.

- MZM. Mach-Zehnder Modulator.

- NCI. Nanophotonic Coherent Imager.

- **OPM.** Optical Phase Modulator.

- **PA.** Power Amplifier.

- **PER.** Power-Enhancement Ratio.

- PLL. Phase Locked Loop.

- PV. Photovoltaics.

- QAM. Quadrature Amplitude Modulation.

- Rectenna. Rectifying Antenna.

- Rectenna. Rectifying Antenna.

- **RF.** radio frequency.

- SEPD. Self-Equalizing Photo-Detector.

- **SiP.** Silicon Photonics.

- **SMF.** single-mode fiber.

- **SNR.** Signal-to-Noise Ratio.

- SOI. silicon on insulator.

- **SSB.** Single Side-Band.

- **SSPI.** Space Solar Power Initiative.

- TIA. Trans-Impedance Amplifier.

- **TID.** Total Ionization Dose.

- **TRP.** Total Radiated Power.

- **VCO.** Voltage Controlled Oscillator.

- VGA. Variable Gain Amplifier.

- **VSWR.** Voltage Standing Wave Ratio.

## INTRODUCTION

James Clerk Maxwell is considered the founding father of electro-magnetism. He consolidated the works of other great scientists such as Ampere and Faraday in a set of equations from which he derived the electromagnetic wave propagation equation and showed that these waves propagate at the speed of light. Thus, it can be said that he was the first person who connected light to electromagnetism. While the wave nature of the light was well known at the time, it took more than twenty years to discover the electromagnetic wave propagation produced by electricity and magnetism. Heinrich Hertz discovered these waves by using a spark gap and a simple dipole antenna in the transmitter side and a loop antenna in the receiver side as shown in figure 1.1. He initially thought that these waves have no practical use; however, engineers soon recognized the importance of these waves as a means of radio telegraphy. In less than 20 years, trans-Atlantic communication was possible. This achievement attracted more attention to radio-frequency (RF) communication and soon many different electronic circuitry components and architectures were invented that allowed manipulation of the lower frequency portion of the electromagnetic spectrum.

The electromagnetic spectrum is shown in figure 1.2, which spans from radio waves to gamma rays. Even though the same underlying physical principle applies to optical wave propagation, advancement in optical components and architectures that allowed manipulation of optical waves remained very limited. This can mainly be attributed to the very small wavelengths of visible and infrared spectrum which requires very precise systems to manipulate and control them. Recent advancement in lithography has enabled mass production of many precise and well controlled systems on a very small scale with very low cost and has revolutionized the design of optical and photonic systems.

Similar to RF transceivers in the beginning of 20<sup>th</sup> century, the main driving force for development of integrated photonics is communication. The development of extremely low loss optical fibers and very large available bandwidth in such fibers have been the the main motivation of research in the field of optical fiber communication. The deployment of TAT-8, the first transatlantic optical fiber cable, in

(a) Hertz first transmitter (b) Hertz loop receiver

Figure 1.1: Hertz transmitter and receiver [23].

Figure 1.2: Electromagnetic spectrum

1988 allowed close to 40,000 phone conversation at the same time between Europe and North America. The high cost of deployment of optical links dropped rapidly as faster and cheaper optical modulators and photodiodes became available. The invention of EDFA in end of 1980s further reduced the cost of deployment of long haul optical links.

As the Internet boomed in the late 1990s, many attempts were made to build local area networks out of optical fibers. The integration of laser and optical modulators had already brought the price of components down. However, the cost of deployment remained high due to time consuming cleaning and aligning the connections. Multi-mode fibers (MMF) allowed lower cost deployment, but they lost the main advantage of single mode optical fibers (SMF) which was the bandwidth. Soon optical fibers

(a) Hertz first transmitter

(b) Hertz loop receiver

Figure 1.3: Active optical cables marries the ease of use of copper cables with speed of fiber optics.

lost the battle to electronic systems that took advantage of Moore's law and provided a lower cost and more reliable solution for local area networks.

Soon researchers in optical communication realized that they could take advantage of Moore's law and beat the electronics in their own home turf with the use of Silicon on insulator (SOI) wafers. Silicon is transparent in the optical communication wavelengths of 1310nm and 1550nm and has much larger index or refraction compared to silicon dioxide, both are the materials that can be cheaply produced and precisely patterned. The large index contrast between silicon and silicon dioxide allows very tight confinement of light inside the silicon waveguide and having very small bend radii [88]. The cost reduction resulted from Co-integration of electronic circuits with photonic circuits on the same package or even on the same die as well as the increasing demand for higher data rates of server farms paved the way for a new category of optical interconnects called active optical cables (AOC) as it is shown in Fig. 1.3. These cables accept electrical inputs and outputs and perform the electro-optical and opto-electrical conversion in the connector. So from the end user they are no different than an electrical cable. This simplifies the use of the cables as no fiber cleaning and alignment is needed by the end user and hence the cost of deployment is reduced. One other benefit of these cables is that they can be designed to be compatible with electrical connectors such as Ethernet, Thunderbolt, or SFP++, but allow for much higher data rates over larger distances.

Silicon-photonics (SiP) applications is not limited only to transceiver applications. The platform enables realizing very complex optical systems in a single chip that can be easily mass produced with very low cost. Thanks to high precision lithography, optical components can be fabricated with very tight tolerances and with very good matching to each other. Similar to electronic ICs where matching of elements is vastly utilized by designers, similar design techniques can be utilized in SiP to achieve systems that would be otherwise very complex or expensive.

It can be argued that one of the most prominent advantage of SiP platform is empowering the manipulation of light in nanometer scale level. This allows engineering the wavefront of light, and as will be presented later in chapters 4 and 5, it will be seen how this can create new systems that were not possible to make previously.

#### 1.1 Contributions

The contributions of this work can be categorized into three main categories of photonics, electronics/antenna design, and combining electronics and photonics to obtain superior systems.

The following is a list of contributions in the photonics category:

- First demonstration of optical phased array transmitter with rapid beam steering capability.

- First demonstration of a lens-free projection system utilizing optical phased arrays.

- First demonstration of optical phased array receiver with heterodyne architecture.

- First demonstration of lens-free imaging with an optical phased array receiver.

- Demonstration of a 3D imager with highest measured depth accuracy.

- Resolving the bandwidth/quality factor trade-off of micro-ring resonators with a differential driven coupling modulation scheme.

- Footprint reduction of high-speed Mach-Zehnder (MZI) by wrapping the interferometer around itself in a spiral shape.

- Proposing a new design approach to increase bandwidth and power handling ability of Ge photodiodes in a standard SiP SOI process.

The electronic circuit design contributions encompass the work done in space solar power initiative (SSPI) which at the time of this writing is an on going project with collaboration of Professor Harry Atwater and Professor Sergio Pellegrino research groups. The aim of the project is to harvest solar energy from space and transfer the power via RF waves generated by kilometer scale phased-array transmitter towards earth. Our group is responsible for RF power generation, phase and timing synchronization, antenna design, and RF power recovery. My contributions to this project can be summarized as follows:

- RF phase synchronization through design of a phase adjustable Clock Multiplier Unit (CMU).

- Design of SAR ADCs for on-chip calibration and sensing as well as digital control circuitry

- Design of rectennas for wireless power recovery with both off the shelf and CMOS integrated Schottky diodes.

The other contribution of this work in the electronic/electromagnetism category is proposal of new multi-port antenna. Below is a list of contributions associated with this proposed antenna structure:

- Proposal of the first proximity field power combining radiator, aimed to increase the radiation power density from an integrated circuit while reducing the optimum drive impedance, allowing higher power delivery from low voltage CMOS transistors.

- Design and fabrication of a tile-able transmitter with programmable phase control enabling the first hybrid nearfield/farfield power combination topology.

A holistic approach towards electronic and photonic circuits allows for creation of systems that can improve performance of either photonic or electronic circuits by taking advantage of what other technology better provides. For example, silicon photonics provide very high bandwidth low loss delay lines which can be used to improve the performance of electronic circuitry such as data equalizers. Below is a list of contributions that utilize this holistic approach in design:

• First demonstration of a self-equalizing photodiode which can be used to improve data rate of optical communication links.

- Laser linewidth reduction with dedicated ASIC .

- Frequency tunable mm-Wave generation through electro-optical mixing.

## 1.2 Organization

In the following chapters of the thesis, I will present a summary of my research over the last 6 years of my studies at Caltech.

In chapter II I will provide a background on integrated photonics with an emphasis on silicon photonics. Chapter III will present self-equalizing photodiode and adjustable self-equalizing photodiode design and measurement results. Optical phased array transmitter and receiver implementation and measurement results are presented in chapters IV and V, respectively. Chapter VI presents the integrated silicon photonic LIDAR imager.

In chapter VII I'll present a new approach and methodology to design on chip antennas targeted for high power CMOS radiators. A prototype implementation of such methodology is also presented. Chapter VIII summarizes the joint effort in SSPI project to provide globally available electricity produced from space.

The rest of my contributions in laser line-width reduction, electro-optical mm-Wave power generation and radiation, enhanced optical ring resonator based modulators, MZI modulator footprint reduction, photo-diode bandwidth improvements, and proposal and design of on chip optical tweezers are summarized in chapter IX. The conclusion of my thesis and future works are presented in chapter X.

#### Chapter 2

# SILICON PHOTONICS: INTEGRATING COMPLEX OPTICAL SYSTEMS ON A CHIP

#### 2.1 Photonics Integration on Silicon

As the demand for faster data links has increased over the last decade, the penetration of optical fiber communication has out grown from long haul continental and intercontinental to shorter haul networks in urban and rural networks. Since the main cost of such networks is dominated by the cost of deployment (excavation, fiber placement, etc.) there was no justification to further reduce the cost of the active devices such as optical transceivers, switches, and repeaters. The main motivation in such networks was and still remains to be to increase the data rate that can be sent through a single fiber. Traditionally this effort was focused on utilizing the full bandwidth available in optical fibers. As shown in Fig. 2.1. For long haul communication, this would be the window at around 1550nm due to availability of erbium doped fiber amplifiers and provides close to 11.5THz of bandwidth. This large bandwidth could not be utilized completely through a single channel, and hence multiple channels are used in wavelength multiplexing systems. Coherent modulation schemes such quadrature amplitude modulation (QAM) can be also used in each channel to increase the spectrum efficiencies and hence improve the data rates. In order to further increase data rate, multi-core fibers [145] have been introduced which allow incredible speeds well above 1Pb/s over a single fiber.

Figure 2.1: Optical fiber loss for different wavelengths [1].

Figure 2.2: Connecting single mode fibers to multi-core fibers. (a) Creation of bundle [128] and (b) alignment needed for splicing [185].

These fibers as shown in Fig. 2.2 require very complex connector and splicing apparatus, but the cost of fiber deployment justifies the use such complex and expensive connectors and splicers.

The reliability and advantages of optical fiber links have now been completely proven by the several decade long deployment and utilization around the world and there is no doubt that fibers will replace copper in wide area networks such as urban networks. Almost no telecom service provider deploys copper based links anymore, and up until recently copper has only been limited to smaller networks such as within building and office networks, where the lower cost and difficulty of deployment does not justify the the use of optical links.

The emergence of cloud computing and cloud service providing has been a big game changing for optical link communications. The proliferation of such services has resulted in growth of large datacenters providing such services. Copper based links are not capable of providing the bandwidth-distance product that these data centers require, and hence optical links have become ubiquitous in such centers. Multi-mode (MM) fibers in conjunction with VCSEL based transmitters have been the dominant player in the market since the large optical core of the fiber requires less tolerance in alignment of laser to the fiber and fiber to fiber, which in turns results in lower price of components and ease of deployment. However, MM fibers suffer from mode dispersion and have a much lower bandwidth-distance product compared to single mode fibers. Multiplexing data in a single MMF is complicated. Mode division multiplexing requires complicated MIMO digital signal processing to deconvolve the crosstalk between the different modes, and is quite power hungry [142]. Also complicated setups are required to Multiplex the modes in and out of the MMF as shown in Fig. 2.3.

Figure 2.3: (a)Examples of amplitude (top) and phase (bottom) profiles of modes excited in a few-mode fiber for MDM. (b) Setup required to multiplex the modes in and out of the fiber [142].

As mentioned earlier, reliable high data rates through single mode fibers have been demonstrated through WDM and lately through spatial division multiplexing (SDM) and this has attracted interest to utilize same techniques in datacenters. Unfortunately the cost and complexity of such systems makes their use in datacenters prohibitive. Integrated photonics and especially silicon photonics have shown an attractive solution to the cost and complexity problem of high speed optical links. Integration allows one to make very complicated systems in large volumes with a very low cost and since silicon processing is quite advanced, thanks to large electronic industry based on silicon based ICs, it has been chosen as one the industry platforms for integrated photonics. The precision of IC fabrication in silicon allows for higher yields of components and systems compared to other integrated platforms[159]. However, silicon has its own disadvantage for photonic processing as it does not have a direct bandgap and as a result generating photons is very inefficient on silicon. In the following parts of this section, I'll give brief overview of the different silicon photonics platforms and their advantage and disadvantages.

### SiP on Bulk Silicon

If silicon photonics is intended to be fabricated along with bulk silicon electronic devices such as BJTs, this platform is the cheapest and easiest option. In this type of platform, the waveguides and other photonic components can be realized by

Figure 2.4: Removal of substrate to reduce leakage of light to the substrate [78].

deposition and etch of polycrystalline silicon [17, 78], deposition of amorphous silicon and later converting it to crystalline silicone [90], or deposition and etch of silicon nitride.

There are two challenges with the deposition of polycrystalline silicon as waveguides. One is the high loss of optical propagation in the waveguide, which occurs due to light scattering at the grain boundaries and absorption of light due to the dangling bonds on the surface of the grains [17], and the other challenge is the leakage to the substrate in CMOS processes, where the silicon oxide thickness (STI layer) under the the waveguides is not not large enough to prevent the leakage of light to the substrate[78].

There are several methods to reduce the loss of polycrystalline optical waveguides and some of them need to be applied concurrently. Surface polishing to reduce the surface roughness of the waveguides and hence reducing the scattering as well as hydrogenation of the waveguide to reduce the dangling bonds on the grain boundaries have been suggested as effective methods to improve the loss performance [17]. Even with these techniques losses are above 10dB/cm [90].

In order to improve the confinement of the light in the waveguide and reduce the leakage to the substrate, [78] proposes a method to remove the substrate underneath the polycrystalline waveguide. This method as shown in Fig. 2.4 can improve the loss to close to 10dB/cm for the polycrystalline waveguides.

It is possible to further reduce the loss of the silicon waveguide in a bulk process by converting the deposited amorphous silicon to crystalline silicon as proposed by [90]. The steps required to achieve this are shown in Fig. 2.5. First a trench is etched

11

Figure 2.5: Creating single crystals form amorphous silicon to reduce the loss of optical waveguide [90].

in the bulk Si and is filled with silicon dioxide. After CMP and planarization, a thin layer of amorphous silicon is deposited on the surface of the wafer covering both the silicon and silicon dioxide regions. Through a process called solid phase epitaxy, the amorphous silicon is converted to single crystalline using the substrate as seed. Through this crystallization the loss of the optical waveguide can be reduced to around 6dB/cm, which is still higher than what can be achieved with SOI processes. Nonetheless, crystallization step requires extra thermal processing which may affect doping profiles and hence is not CMOS compatible.

The other option is to deposit silicon nitride  $(Si_3N_4)$  and use the index contrast between silicon nitride and silicon dioxide to confine light. The waveguides created by nitride may exhibit lower confinement compared to silicon due to lower index contrast; however, they can achieve very low loss of 0.1dB/m if bending losses are ignored [33]. Multiple layer of optical waveguides can also be formed using nitride and light can couple from one layer to other layer simply by running the two layers along each other (Fig. 2.6). The downside of using silicon nitride is that it is not a semiconductor so no fast modulator can be made out of it.

#### Silicon on Insulator Based SiP

Silicon on insulator (SOI) is the most widely adopted platform for silicon photonics. Soitec invented a method [16] to achieve well defined and high quality SOI wafers which is now widely used for silicon photonic platforms. Figure 2.7 shows the process steps of making SOI wafers. The fabrication of the SOI wafer involves two wafers. One is used as a substrate and the other is used to create the device layer ion SOI process. The desired thickness of oxide layer under the silicon layer is first grown on the substrate wafer. The device wafer undergoes a heavy dose of proton implantation such that small cracks are formed underneath the device wafer surface. The device wafer is then flipped and thermally bonded to the substrate wafer. Due

Figure 2.6: (a) A fabrication steps of a multi-layer silicon nitride optical platform and methods to couple light from one layer to the other layer [151].

to the presence of the cracks in device wafer, splitting the wafer results in leaving a thin layer of single crystalline silicon on the substrate wafer. After CMP polishing the desired thickness of silicon is obtained on the SOI process.

Waveguides are obtained in the SOI process by simply placing a photoresist where the waveguide needs to be and etching away the rest of the silicon. Low loss waveguides of 0.4dB/cm for single mode silicon waveguides [79] and extremely low loss of 0.026dB/cm [101] with multi-mode fibers can be achieved.

The SOI process also provides the ability to modulate the phase of light through a process called free carrier plasma dispersion, which allows fabrication of high speed modulators for optical links. Epitaxial growth of germanium on SOI enables integration of photodiodes on the same wafer. The availability of CMOS transistors on SOI processes implies that silicon photonic and electronic circuits can coexist on the same wafer as well.

#### **SOI/Bulk hybrid SiP Platfrom**

As mentioned in the previous subsection, SOI platform enables integration with CMOS electronic devices. Optical modulators, however, typically require large amplitude swings which can be well addressed with BJTs and HBTs. Also SOI process is not well suited for high power application as the oxide layer impedes the heat transfer from the transistors to the heat sink.

To address the mentioned issues, IHP (innovation for high performance Microelectronics) research center in Germany has developed a hybrid bulk/SOI process which

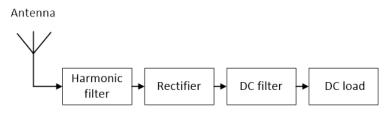

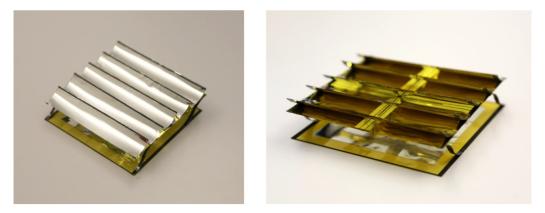

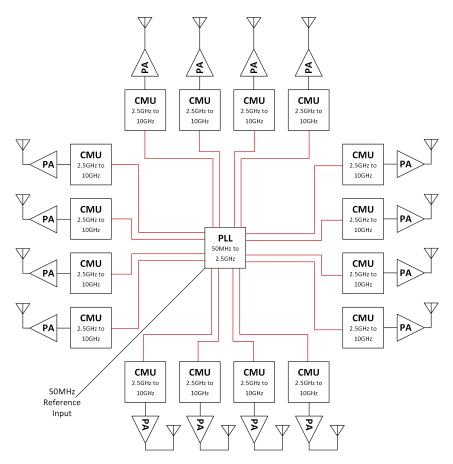

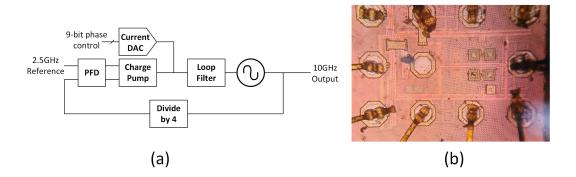

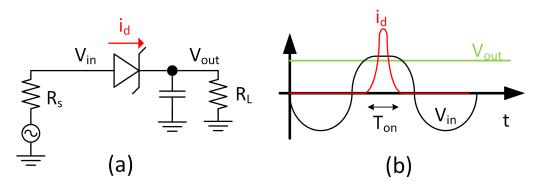

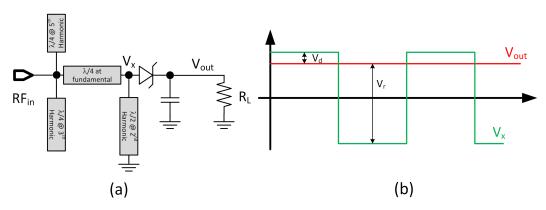

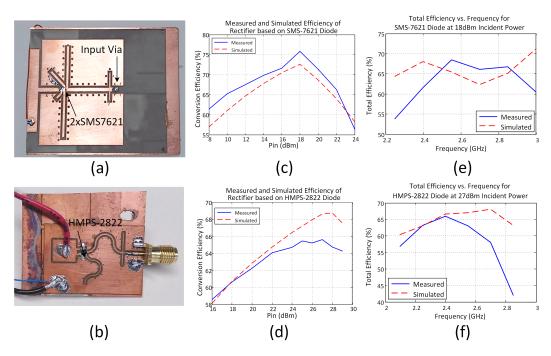

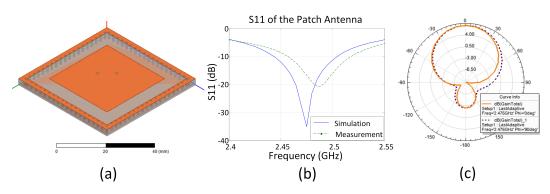

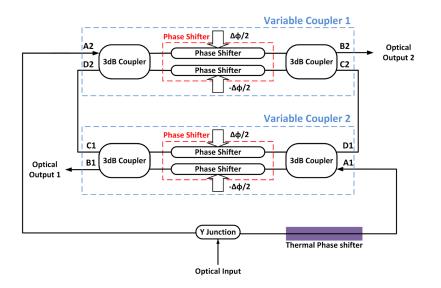

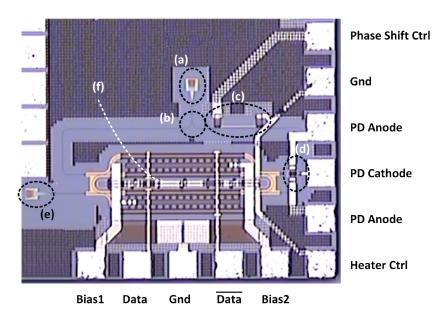

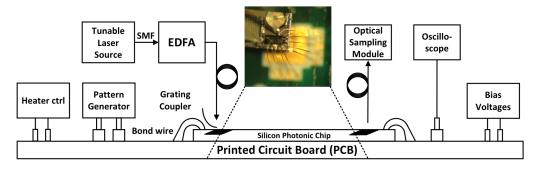

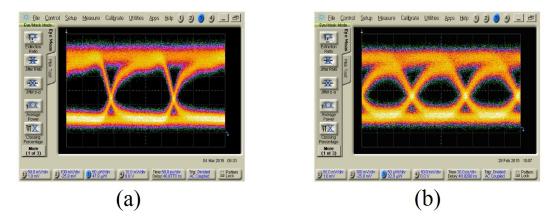

Figure 2.7: Fabrication steps for SOI wafers [6].