# Hierarchical Composition of VLSI Circuits

Thesis by

Telle Elizabeth Whitney

In Partial Fulfillment of the Requirements

for the Degree of

Doctor of Philosophy

California Institute of Technology

Pasadena, California

1985

(Submitted May 21, 1985)

©1985

Telle Elizabeth Whitney

All Rights Reserved

to my parents

Din, Beverly, and June

# Acknowledgments

Special acknowledgment is due to Dr. Ivan Sutherland whose ideas on using circles and lines for representing geometry, from his polygon package, inspired the work presented in this thesis.

I'd also like to express my deepest appreciation to Carver Mead, my advisor, for his warmth, his insights, his constant support and patience. He has been a tremendous inspiration and has contributed greatly to my life through the expression of his philosophy in our many lengthy discussions, his views on science, and his incredible humanism.

I'd like to thank my committee, each contributed to this thesis in a unique way: to Chuck Seitz for his concern and help over the years, to Dick Lyon whose careful study and extensive comments made the final weeks a real joy, and to Al Barr and Dr. David Rutledge for their comments and help.

The formation of "the group" created an environment of comradeship that allowed scientific study, and I am grateful for the chance to participate. I'd like to thank all of my fellow students for their friendship and support. An extra special thanks is due Jim Campbell for doing all those things that need to be done in order to maintain a productive lab.

Thanks to the many participants of the Silicon Structures Project, who are too numerous to mention. The people associated with the project made the initial years of my graduate study both productive and a pleasure.

I am truly indebted to John Wawrzynek for both his constant support and remarkable insights. He always provided a reason for trying a little harder when things were going wrong. He was a sounding board for my ideas, and examined each one carefully and thoroughly. He pointed out when I was wrong, and sometimes applauded when I made progress. He was always there.

This thesis was formatted using Donald Knuth's T<sub>E</sub>X, and printed on an Apple LaserWriter, with figures described in Postscript directly incorporated into the text using Textset software. My thanks to the people at Adobe systems, Inc., and Textset, Inc. for their help in making this formatting approach possible. Glenn Gribble deserves special appreciation since he pulled the various software pieces together, and locally made it possible. Also, thanks to Lounette Dyer for originating and suggesting this formatting approach, and providing software support. An extra special thanks to Calvin Jackson, who was always there to answer questions, offer suggestions, and provide technical support.

I owe many thanks:

to my colleagues in the field who provided fruitful interactions over the years, to my family who always encouraged me to strive for the best, and to my friends who made the day-to-day worthwhile.

This work was supported by the System Development Foundation.

#### **Abstract**

A transistor level representation for VLSI circuits is presented. This representation is simple but general, technology independent, hierarchical, and maintains connectivity, circuit schematic information, and the information for mask geometry.

A transistor level cell is represented as the interconnection of devices along with their types, sizes and placement, and the cell's typed ports. Connection is represented explicitly by shared connection points. The ports describe the interface between this cell and other cells. This representation, together with a set of synthesis and analysis rules, enforces the description of strictly legal designs. The synthesis rules ensure that each structure is correct by construction. The analysis rules check for geometrical design rule violations which cannot, by their nature, be enforced by construction.

A file of technology dependent information indicates how to implement each transistor type, interconnect type and connection point type, as well as how structure types may interact.

Cells described in this representation may be composed hierarchically to form larger cells. Given a valid composition, the topology, geometry and connectivity of the composite structure is guaranteed to be legal.

A working system supporting this hierarchical representation is also described. This system currently supports design rules for nMOS and cMOS/bulk, and has produced chip descriptions that have been both fabricated and tested.

# **Table of Contents**

|                                        | Acknowledgments                                                                                                                                                                                                    | i                                |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

|                                        | Abstract                                                                                                                                                                                                           |                                  |

|                                        | List of Figures                                                                                                                                                                                                    | vii                              |

| 1.1                                    | Introduction.  Structural Design Representations  Overview of the Thesis                                                                                                                                           |                                  |

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6 | The Pooh Representation The Pooh Topological Representation GDR Representation Geometrical and Topological Representation. Circuit Synthesis Rules Circuit Analysis Rules Simulation Interface Geometry Generation | 11<br>13<br>14<br>16<br>18       |

| 3.1<br>3.2                             | Synthesis Algebra                                                                                                                                                                                                  | 20<br>20<br>23<br>30             |

| 4.1<br>4.2                             | Node Synthesis  Node Equivalence  Path Connectivity Representation  Node Propagation Algorithm                                                                                                                     | 32<br>33<br>33<br>36             |

| 5.1<br>5.2<br>5.3                      | Analysis Algebra  Primitive Operations  The Geometrical Design Rules  Point Analysis  Path Analysis                                                                                                                | 39<br>39<br>42<br>45<br>48       |

| 6.1<br>6.2<br>6.3<br>6.4               | Pooh Hierarchical Composition  Cell Representation  A Composition Algorithm  Composition Connectivity  Composition GDR Verification  Proof of Closure Under Composition                                            | 54<br>54<br>56<br>63<br>65<br>73 |

| -                                      | System Considerations                                                                                                                                                                                              | 82<br>82                         |

|                 | Storing Paths and Points   | 88<br>91                 |

|-----------------|----------------------------|--------------------------|

| 8.1<br>8.2      | A Pooh System              | 101<br>101<br>106<br>113 |

| Appendix I. 1 2 | Experimental Layout Format | 116<br>116<br>118<br>121 |

| Appendix II.    | Geometrical Design Rules   | 124<br>129               |

|                 | Bibliography               | 131                      |

# List of Figures

| Figure 1-1     | Cells and Interconnection of Cells              |

|----------------|-------------------------------------------------|

| Figure 1-2     | Design Representations                          |

| Figure 1-3     | Circuit to Geometry Representations             |

| Figure 1-4     | The Pooh System                                 |

| Figure 2-1     | Topological Sized Schematic For A Register Cell |

| Figure 2-2     | Paths, Segments and Transistors                 |

| Figure 2-3     | Register Cell Stick Diagram                     |

| Figure 2-4     | Segments, Points and Transistors                |

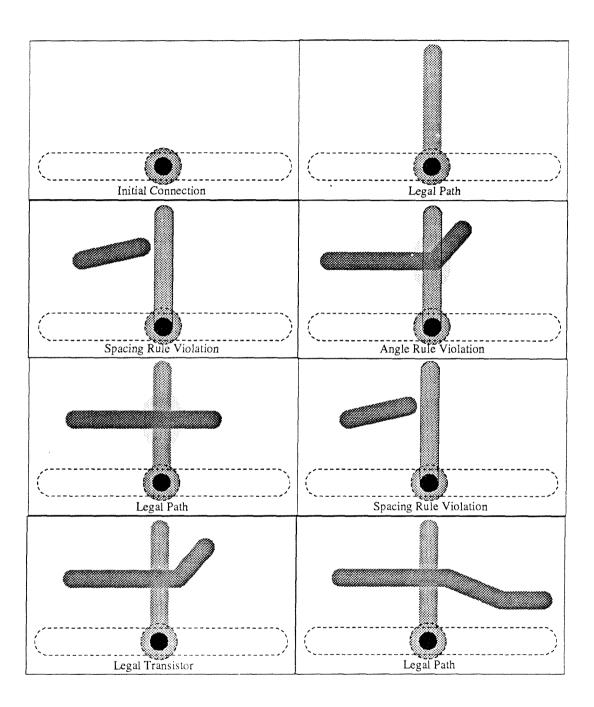

| Figure 2-5     | Synthesis Rules                                 |

| Figure 2-6     | Legal Angle of Connection                       |

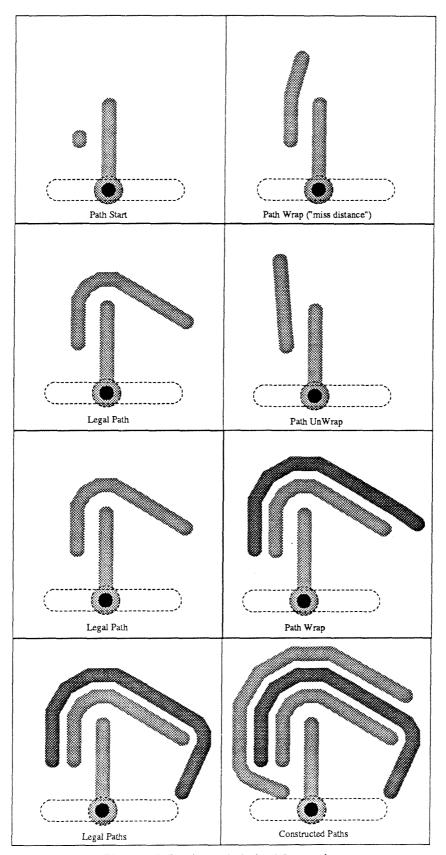

| Figure 2-7     | "Miss" Distance                                 |

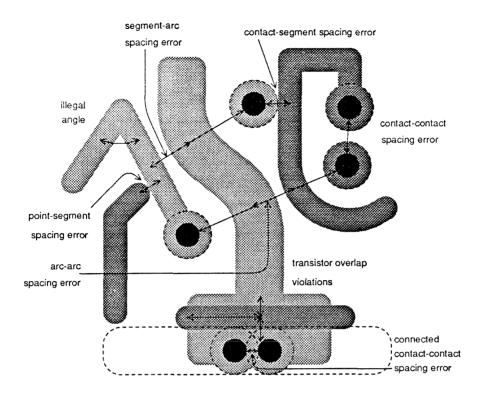

| Figure 2-8     | Analysis Rules                                  |

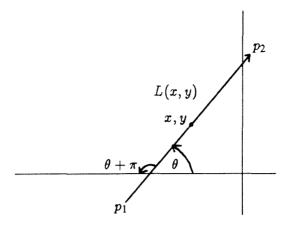

| Figure 3-1     | Line Calculation                                |

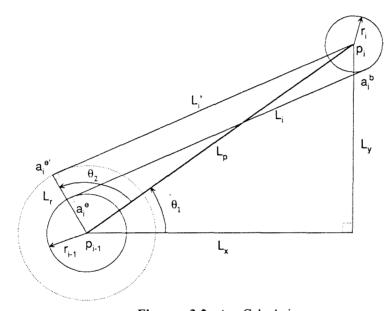

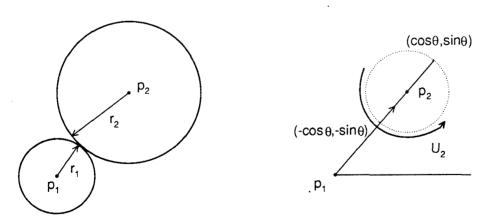

| Figure 3-2     | Arc Calculation                                 |

| Figure 3-3     | Arc Representation                              |

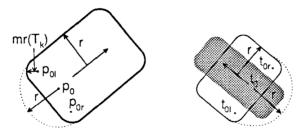

| Figure 3-4     | Minimum Radius Segment                          |

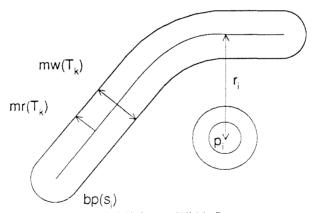

| Figure 3-5     | Wide Path Segment                               |

| Figure 3-6     | Arc Interference                                |

| Figure 3-7     | An Illegal Segment                              |

| Figure 3-8     | Transistor Overlap                              |

| Figure 3-9     | Intersection Points                             |

| Figure 4-1     | Connected Paths                                 |

| Figure 4-2     | Interconnection Path                            |

| Figure 4-3     | Connection Regions                              |

| Figure 4-4     | Two Transistor Paths                            |

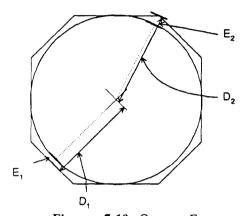

| Figure 5-1     | Arc Overlap Detection                           |

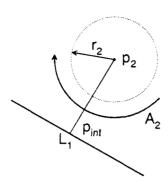

| Figure 5-2     | Line-Arc Proximity Detection                    |

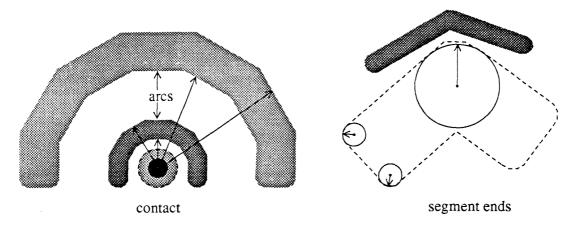

| Figure 5-3     | Path End Conditions                             |

| Figure 5-4     | A Transistor Point                              |

| Figure 5-5     | Contacts Spacing 4                              |

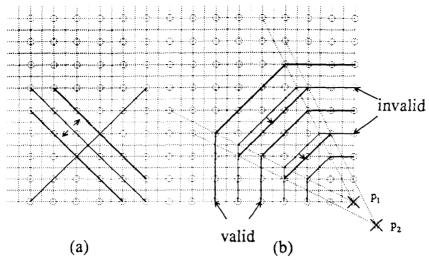

| Figure 5-6     | Legal and Illegal Segment Connections 4         |

| Figure 5-7     | Legal Connections between Segments              |

| Figure 5-8     | Example Paths5                                  |

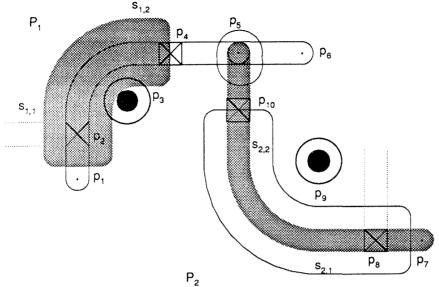

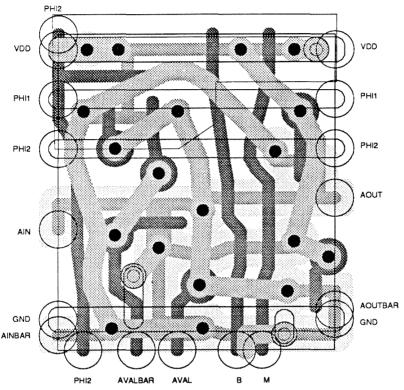

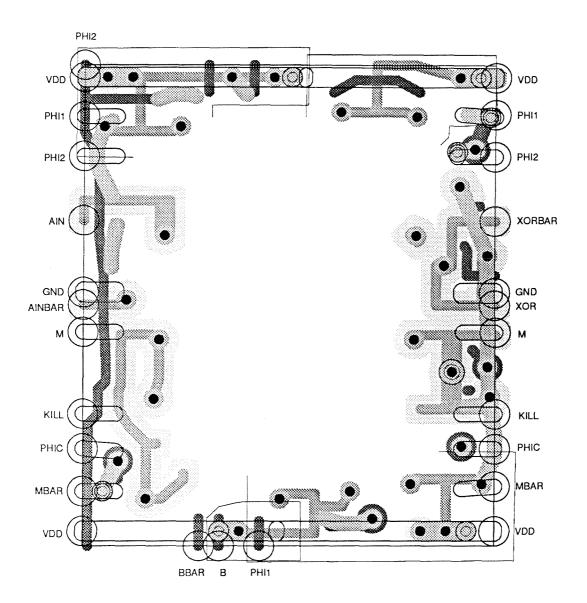

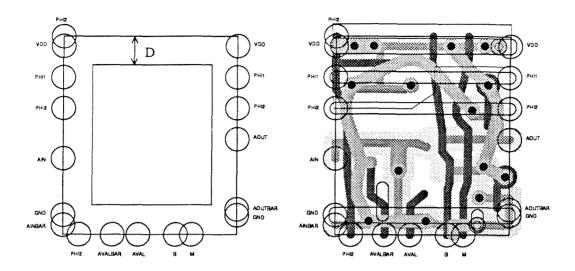

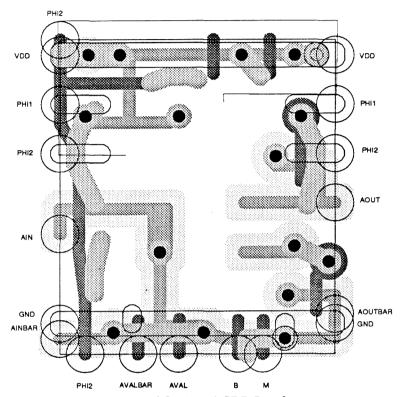

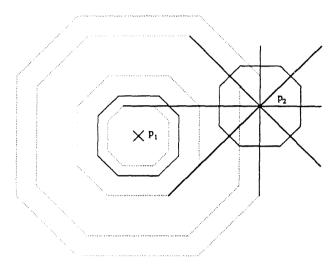

| Figure 6-1     | Bit Serial Multiplier Leaf Cell                 |

| Figure 6-2 (a) | Full Geometry Of One Bit Stage                  |

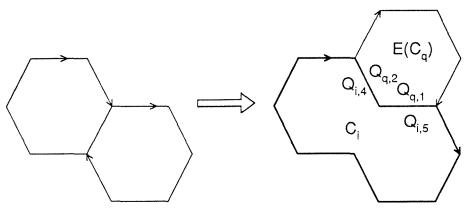

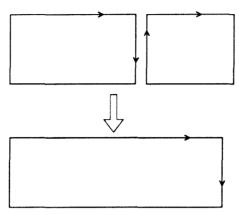

| Figure 6-2 (b) | Composition of Cells                            |

| Figure 6-2 (c) | Cell Abstraction                                |

| Figure 6-3     | Concave Connecting Sides6                       |

| Figure 6-4     | Connecting Sides                                |

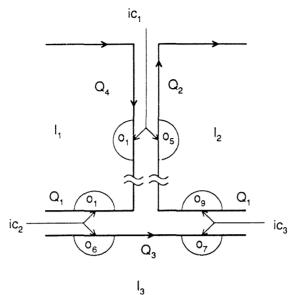

| Figure 6-5  | Internal connections                                       | 64  |

|-------------|------------------------------------------------------------|-----|

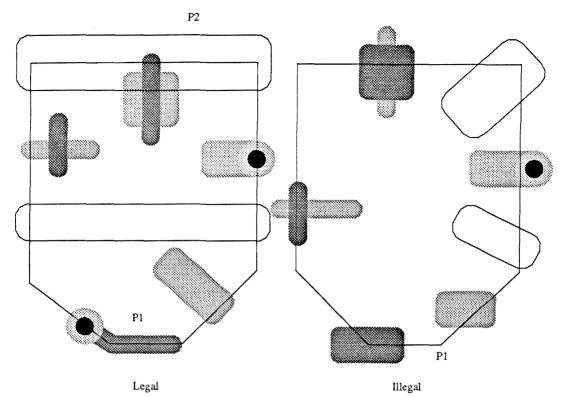

| Figure 6-6  | Legal and Illegal Cells                                    | 67  |

| Figure 6-7  | GDR Interesting Paths and Points                           | 68  |

| Figure 6-8  | Actual GDR Interface                                       | 70  |

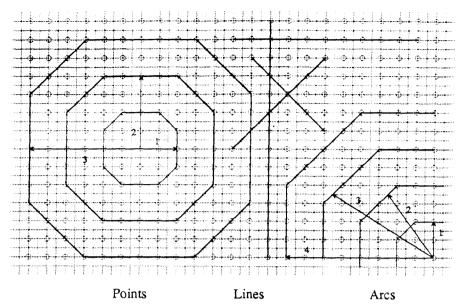

| Figure 7-1  | Geometry Generated From Circle                             | 83  |

| Figure 7-2  | A twelve sided circle approximation                        | 83  |

| Figure 7-3  | Polygon Error                                              | 84  |

| Figure 7-4  | Point Geometry                                             | 85  |

| Figure 7-5  | Arc Geometry                                               | 86  |

| Figure 7-6  | The Point Array                                            | 89  |

| Figure 7-7  | A Segment Array                                            | 90  |

| Figure 7-8  | Transistors and Wires in the Integer Pooh                  | 92  |

| Figure 7-9  | The integer grid and Unit Circle                           | 92  |

| Figure 7-10 | Octagon Error                                              | 93  |

| Figure 7-11 | Circles, Lines and Arcs                                    | 94  |

| Figure 7-12 | Distance Between Two Points                                | 97  |

| Figure 7-13 | Possible Invalid Elements                                  | 99  |

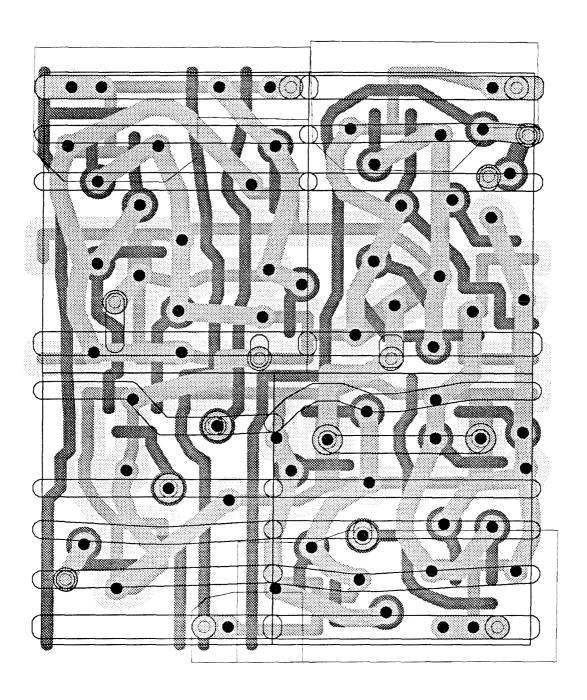

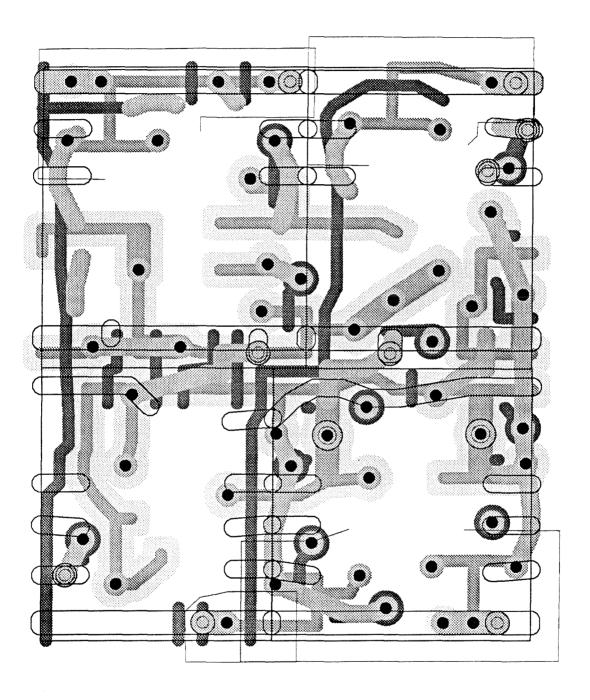

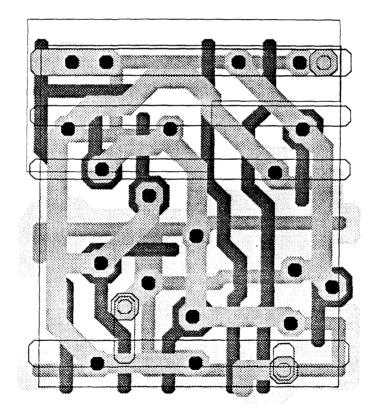

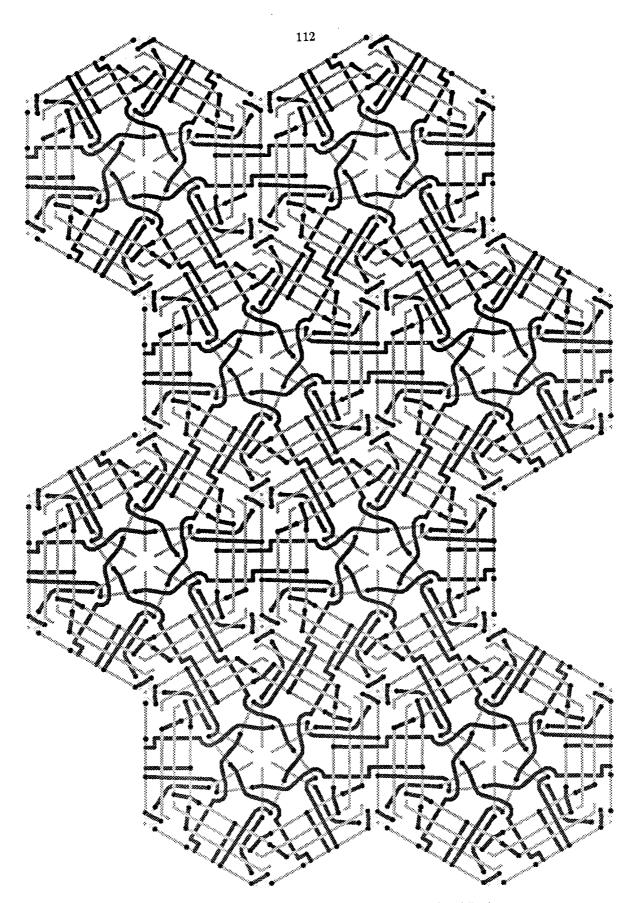

| Figure 7-14 | The Integer Pooh version of the Bit Serial Multiplier Cell | 99  |

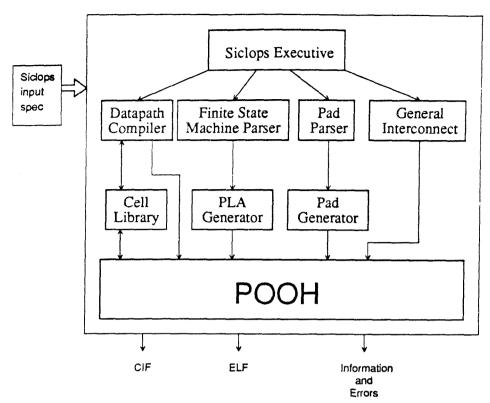

| Figure 8-1  | The Siclops Silicon Compiler                               | 102 |

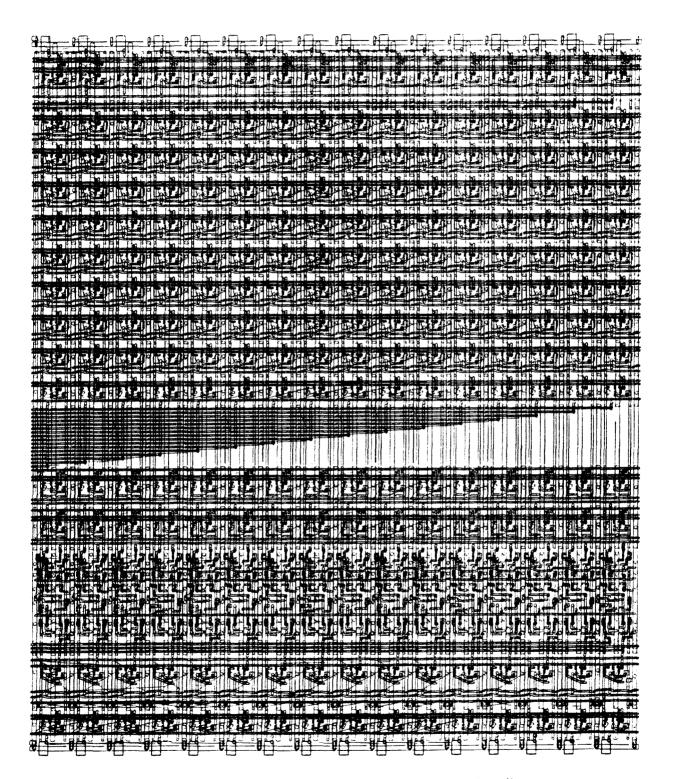

| Figure 8-2  | A Datapath Generated by the Datapath Compiler              | 104 |

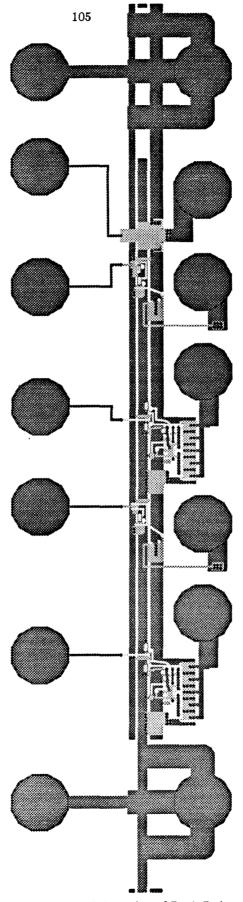

| Figure 8-3  | A Set of Pooh Pads                                         | 105 |

| Figure 8-4  | Tigger Interactions                                        | 107 |

| Figure 8-5  | Tigger "missing" Interactions                              | 108 |

| Figure 8-6  | Possible Edit Functions                                    | 110 |

| Figure 8-7  | The wiring diagram for the Two Dimensional Retina          | 112 |

|             |                                                            |     |

## 1. Introduction

The design of a correct integrated circuit has become an increasingly difficult problem as the complexity has increased [Moore 79]. Current Very Large Scale Integrated Circuit (VLSI) chips contain over 100,000 transistors, and million transistor chips are foreseen in the near future. Using the well-known structured design methodology [Mead 80, Mead 83], the complexity of designing these large systems is drastically reduced by adopting a hierarchical design methodology and by maintaining consistent design representations throughout the design process.

A hierarchical design methodology defines a large system design problem in terms of a set of smaller more manageable problems. A hierarchical integrated circuit design is defined recursively as a cell where a cell is the interconnection of cells and transistors.

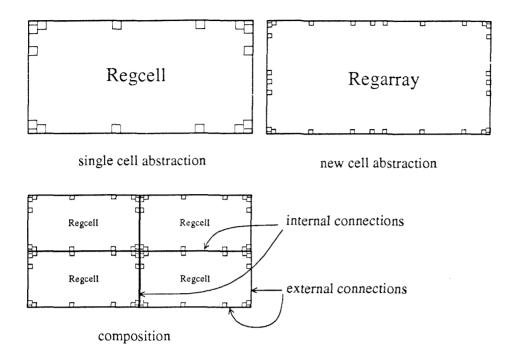

This definition allows us to view each cell as an abstraction. Each cell is represented by its ports and port characteristics. With this information, cells may be interconnected without detailed knowledge of their internal structures. The interconnection then produces a new cell abstraction, as shown in Figure 1-1. Internally, each cell is characterized by three unique representations: (1) a functional specification, (2) a timing model, and (3) a structural description.

The functional specification of the cell is an abstraction of the behavior of the cell circuit. Initially, this functional description may be a circuit description, but a low level circuit description quickly becomes unwieldy. Instead, there is often a concise description that completely characterizes the cell behavior. The key to the functional hierarchy is cell functional descriptions that are composed to form the functional description at the next level of the hierarchy [Chen 83]. Thus the behavior of a cell may be derived from that of its sub-cells and is used to describe and simulate the design. Often cells are semantic units [Chen 83], where only the fixed point behavior of the cell affects connected cells. Otherwise, the cells are syntactic units, and are treated differently during system simulation. In either case, functional descriptions are composed hierarchically, and may be used for simulation or formal verification.

The timing model is a description of the dynamic delay thorough a cell [Lin 84]. At the lowest level, the timing may be derived directly from the circuit. As with the functional description, the timing information is composed to form the timing description at the next level in the hierarchy. Each cell, at every level in the hierarchy, includes a timing abstraction that fully characterizes the cell and may be used to evaluate the delay through the design.

The structural description of the cell is a description of the cell topology. Each cell is an interconnection of transistors and other cells. A structural cell abstraction indicates the topology of interest during composition. As with the functional description and

Figure 1-1: Cells and Interconnection of Cells

the timing abstraction, the cell structural abstraction is composed to form the structural description at the next level in the hierarchy.

In the structured design methodology described in this thesis, cells are defined by these three abstractions. Assuming consistent representations at the lowest level of the hierarchy, composition produces consistent representations at all other levels. This thesis focuses on the structural aspects of a cell, but the structural representation always has a corresponding functional and timing definition.

## 1.1 Structural Design Representations

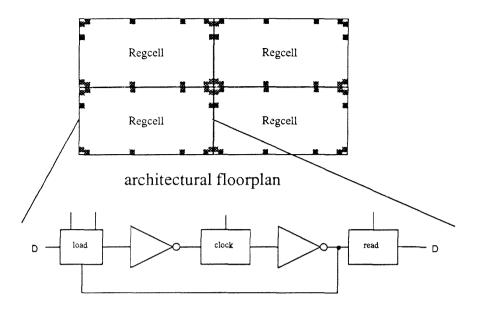

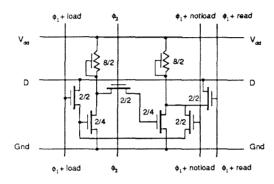

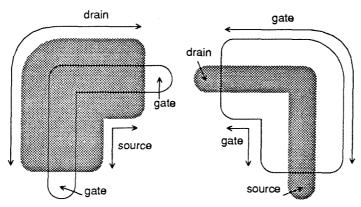

The design of a cell spans many structural design representations. Each representation incorporates information important to the overall design. Often the difference between two related descriptions, or "levels" of the design, is that one contains an abstraction of the other, which has implementation details. A typical structural approach to a VLSI design incorporates the following design representations: (1) architectural floorplan, (2) logic diagram, (3) circuit diagram, and (4) mask geometry description. Figure 1-2 illustrates an example of the four design representations of a simple register. Larger designs will, of course, have more levels. An architectural floorplan is a definition of the large blocks which together comprise the system. A logic diagram is the interconnection of logic blocks. Each logic block is a small unit such as a multiplexor or an adder. A circuit diagram is the interconnection of transistors. The mask geometry description is a collection of colored polygons.

Given multiple levels, a designer is faced with ensuring consistency between

# logic diagram

# circuit diagram

mask geometry

Figure 1-2: Design Representations

the different abstractions. It is absolutely necessary that the logic diagram correctly implements the architectural specification, that the circuit correctly implements the logic diagram, and that the layout corresponds to the circuit.

Given the ability to view a single cell as an abstraction, we now focus on the problems of specifying the implementation of the abstraction at the lowest level. The problems are of the same type the designer encounters at every level of design: ensuring that one level of representation or refinement matches the other. At the circuit level, it is essential that the mask geometry implements the circuit.

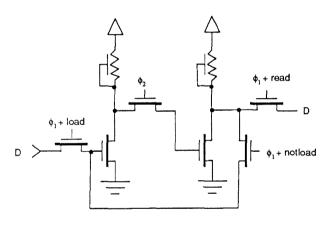

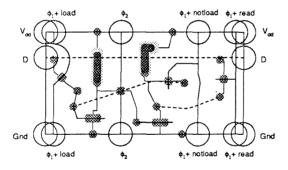

Several representations are used in generating mask geometry from a circuit diagram (shown in Figure 1-3): (1) Circuit Diagram, (2) Sized Schematic, (3) Topological Sized Schematic, (4) Sticks Diagram, and (5) Mask Geometry. Each is a refinement of the previous one. The process can be thought of as a successive binding of the necessary attributes of a finished design. First, a designer must assign sizes to each of the circuit's transistors, to form a sized schematic. Then, the designer decides on the relative placement of the cell's interfaces or ports. The ports determine a large portion of the topology of the cell. Next, the designer worries about relative placement of the transistors to create the topological sized schematic. Then, layers are assigned to the circuit elements and the interconnect to form the sticks diagram. Finally, the designer generates a set of boxes and polygons on different fabrication layers to define the mask geometry. In actual practice expert designers often skip one of more of these steps, and carry the information informally.

The designer then faces the task of determining whether the mask geometry implements the sized schematic. This job is typically done by extracting the circuit [Baker 80] from the geometrical description and then checking to see if the sized schematic and the extracted circuit are the same. Finally, after ensuring circuit consistency, the designer processes the geometry using a Design Rule Checker (DRC) program to find geometrical design rule (GDR) violations. The methods available for checking consistency and performing DRCs tend to be time consuming and error prone.

This thesis describes an alternative approach in which both a sized schematic and the mask geometry are generated from a single representation. Rather than performing the time-consuming and error-prone task of checking the consistency between these two levels of design representation, circuit diagram and mask geometry, a designer specifies the circuit in a uniform representation. The problem of checking the consistency between the two representations is eliminated. Also, the representation embodies a natural but precise way of expressing rules dictated by the fabrication technology. Design Rules such as device sizing and GDRs may be expressed at the level of the structures of the technology, namely, devices and interconnection.

The approach of describing a circuit at a symbolic level was first addressed by John Williams in his "sticks" representation [Williams 77]. He proposed a scheme in which a cell is described in terms of structures such as devices and interconnection wires. He then proposed a "compaction" scheme where a program moves structures as close together as possible according to the GDRs. Several compactors are currently working [Mosteller 81, Hsueh 80]. These systems have many nice properties, but they have not been widely accepted. A fundamental limitation of existing compaction approaches is that they separate the inherently two-dimensional problem of geometrical design rule

circuit diagram

topological sized schematic

stick diagram

mask geometry

Figure 1-3: Circuit to Geometry Representations

checking into two separate one-dimensional problems. Compaction is done first in the x-direction and then in the y-direction (or vice-versa). Rules that are two-dimensional in nature are either ignored or mapped into one of the two static dimensions. Another peculiar quirk of current sticks systems is that devices may extend in only one dimension. Thus if the length of the device is in the x-direction, then the width can only be in the y-direction and the transistor may not bend.

This thesis describes a symbolic "sticks-like" representation and a set of operational algorithms called Pooh [Whitney 83]. It has the following attributes: (1) simple but general (2) independent of any particular technology, (3) capable of expressing the designer's intent [McGrath 80], (4) expresses the design rules in terms of the representation primitives, (5) represents high density designs, (6) contains connectivity, circuit schematic, and mask geometry information, and (7) is hierarchically composible.

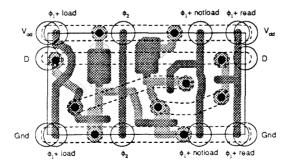

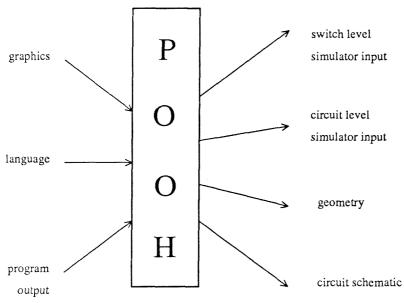

Figure 1-4 indicates how the Pooh representation is used. Pooh provides a service to the user by defining an automatically checked representation for designs at the circuit level. From this representation switch level simulator input, circuit level simulator input, geometry, and a schematic diagram are easily generated. The user interface may either be graphical or language based. Alternatively, Pooh is used as the base level cell representation for a silicon compiler.

Figure 1-4: The Pooh System

Pooh was designed with MOS technology in mind. Currently both nMOS and cMOS/bulk are supported, though other technologies are easily expressed. All the simple illustrative examples in this thesis are nMOS. Some of the actual designs are cMOS.

#### 1.2 Overview of the Thesis

There are four pieces of work presented in order to establish the representation presented in this thesis:

1) the representation of transistors and interconnection,

- 2) the synthesis algorithms for constructing these elements,

- 3) the analysis algorithms for detecting illegal interactions between elements, and

- 4) a general technique for abstracting the topology of a cell and composing cells into topologically and geometrically correct high-level cells.

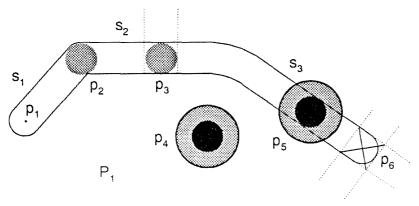

Chapter 2 is an overview of the transistor level Pooh representation. The primitive elements in the Pooh representation are lines, arcs and circles. Transistors, interconnection wires, and connection points are defined in terms of these elements.

There are three types of algorithms necessary to ensure the correct description of the topology, geometry, and connectivity of the Pooh representation. Chapter 3 describes the Pooh synthesis algorithms. The synthesis algorithms allow the construction of GDR correct transistors, wires and connections points. Chapter 4 describes the algorithms for propagating the node information of the circuit. Chapter 5 introduces the Pooh analysis algorithms. The analysis algorithms check the interactions between the elements necessary in order to guarantee the GDR correctness of the circuit. Since each element is constructed according to the GDRs, these interactions are typically simple and small in number.

The composition of circuits is the key to making the Pooh representation a viable solution for describing VLSI. Chapter 6 describes the composition of Pooh cells. First, an abstraction of the cell is derived. Then cells are composed to form the next level in the hierarchy. In Pooh, a legal composition guarantees the topology, geometry and connectivity of the composite structure.

Chapter 7 addresses some of the considerations of a system that supports the Pooh representation. An actual Pooh system uses a circle approximation instead of a true circle, and the affect of the circle approximation is explored. Interactions between the Pooh paths and points must be quickly detected to make Pooh a useful tool. A data structure that allows easy access to the Pooh elements is described. This chapter also describes a simplified version of the Pooh algorithms. These algorithms support vertical, horizontal and forty-five degree lines, and are integer based.

Chapter 8 concludes this thesis by describing an implementation of a Pooh system. This implementation supports two separate interfaces. The original Pooh system was an embedded language, used as the base level representation for the Siclops silicon compiler. The second system described is Tigger, a graphical circuit editor that enforces GDRs interactively.

# 2. The Pooh Representation

## 2.1 The Pooh Topological Representation

The standard circuit-level representation of basic cells for a VLSI design is the topological sized schematic. To date, the information conveyed by this level in the design has had no formal representation. It incorporates relative placement, transistor sizes and interface ports. In addition, layer information is usually attached to interconnect by either convention or context. Interconnect either connects to a transistor, or goes around it. A sized schematic does not depend on absolute placement, but is drawn with relative placement. The relative placement of the interface ports in a cell determine a large portion of its internal topology. Thus the step from a topological sized schematic to the Pooh representation is a small one.

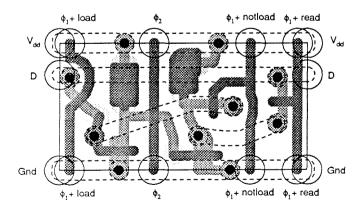

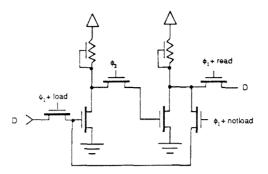

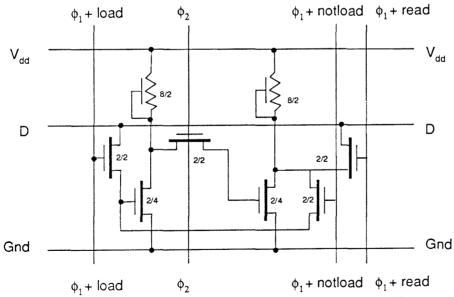

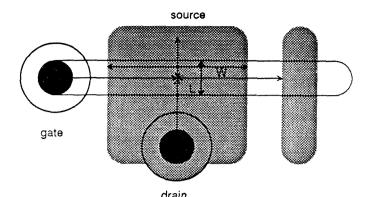

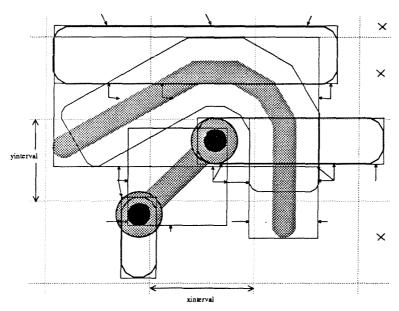

A topological sized schematic cell is specified by its devices, interconnection wires and ports. Each device is a transistor with a position and an orientation. Each interconnection wire is a single electrical node between two or more devices. Each port is a connection point of one of the cell's electrical nodes to nodes of other cells. Figure 2-1 illustrates a Pooh topological sized schematic.

Figure 2-1: Topological Sized Schematic For A Register Cell

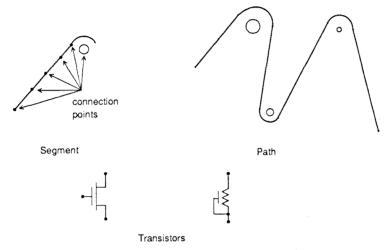

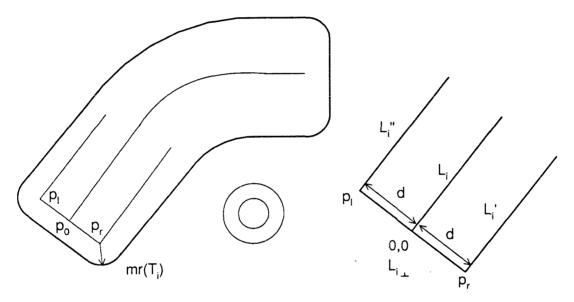

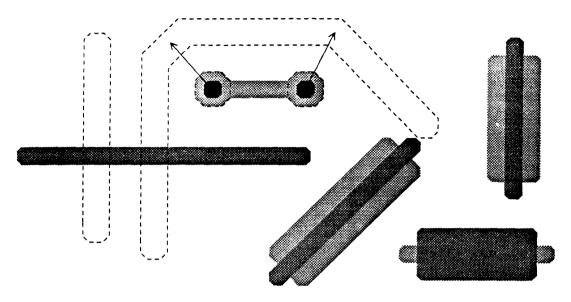

A topological sized schematic is expressed in Pooh using three primitive structures: (1) a typed point, (2) a segment and (3) a path. A typed point is a position along with associated type information. It is used to represent both devices—where the

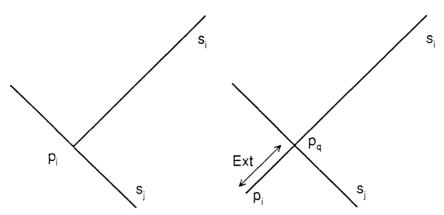

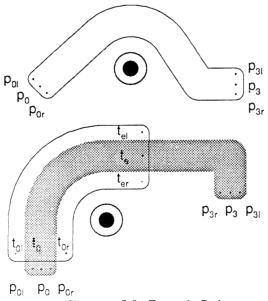

type indicates the type of transistor, and connection points. Each transistor definition includes strength information in the form of Length/Width, an orientation, and three electrical nodes—source, drain and gate. A segment is a directed line segment and an arc. The end of the line segment is the tangent point on a circle of radius r centered at the segment end point. The arc is defined by the end of the line segment, the segment end point, and a direction. If the arc radius r is zero, then the arc is of zero length, and the end of the line segment is the segment end point. Paths are sequences of segments. An interconnection wire is represented as a set of connected paths of the same electrical node. A connection point is a typed point (or "dot") where a connection occurs between either two paths, or a path and a device. Ports are represented as typed points where the type indicates what type of connection may occur at this port. Figure 2-2 shows examples of these elements.

Figure 2-2: Paths, Segments and Transistors

A topological sized schematic differs from a standard circuit schematic in several important ways. In particular, additional information is present in a topological sized schematic that is not in the normal schematic.

A circuit schematic may be represented as a bipartite graph, with vertex partitions representing the nodes and the transistors. The edges between the two partitions represent the connectivity. The information conveyed by this circuit schematic can be fully captured using a one-dimensional representation. For example, let  $n_1

ldots n_m$  denote the node vertices, and  $t_1

ldots t_p$  denote the transistor vertices. Then, we may represent the circuit as two arrays: N of length m, and T of length 3p, and represent the connectivity as stored indices from one array into the alternate array. Obviously, this representation is one dimensional, and yet it contains sufficient information to fully represent the circuit graph.

A topological sized schematic incorporates information beyond the normal schematic. The device sizes are necessary attributes of the transistor vertices in any actual design. The crucial step, however, is the relative placement of the ports and the interconnect. This step takes the schematic from the realm of a one-dimensional representation to the two-dimensional world of integrated circuits.

Relative placement is the process of basing the position of an object, in this case interconnect or ports, on the placement of other objects. Previous work has focused on automatically generating a stick diagram from a circuit schematic coupled with device sizes and a partially ordered set of ports [Ng 84, Wolf 83]. This work separates the potentially non-planar circuit graph into a set of planar graphs, which must correspond to the different interconnection layers on the target chip. The next step is to create two constraint graphs from these circuit graphs, which describe the ordering of the components in the x-dimension and in the y-dimension, similar to the constraint graphs used in one-dimensional sticks compactors [Mosteller 81, Hsueh 80].

In fact, the ordering inherent in the topological sized schematic is not one-dimensional at all. A topological sized schematic contains lines, representing interconnection, and components, representing transistors and ports. This schematic's relative placement information is two-dimensional in nature, and is naturally representing by lines "missing" or "going around" components.

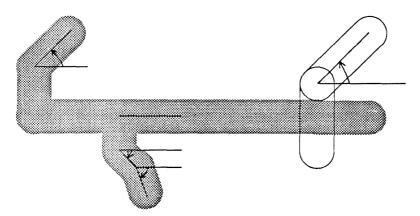

A stick diagram [Williams 77] is a topological sized schematic with "colored" interconnect and devices. The color indicates the layer on the silicon implementation for the interconnect and transistors. A stick diagram is shown in Figure 2-3. A stick transistor level design is represented as the interconnection of transistors along with their types, sizes and placement. The primitives of the representation are transistors, interconnect and connection points. Transistors are the devices of the technology, each of which have a length and a width. Each transistor is either a path or a point. Interconnect is implemented by typed paths connected by two or more connection points. Connection points are points, with associated type information, where an electrical connection occurs between two or more paths.

Figure 2-3: Register Cell Stick Diagram

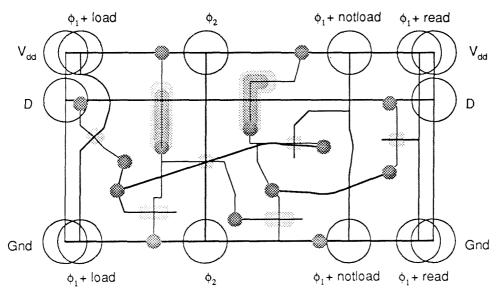

In the Pooh topological representation, the notion of relative placement is implemented in the following manner: transistors and interconnect are represented as a series

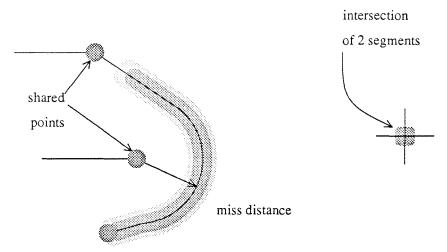

of segments as shown in Figure 2-4. Each segment may either connect to a point, or go around it. Connectivity is represented explicitly by multiple references to the same point. If a segment goes around a point, the distance is a "miss distance" and forms an arc around the point. Small transistors are often conveniently formed by the intersection of two segments as shown in Figure 2-4.

Figure 2-4: Segments, Points and Transistors

A circuit described in this manner maintains the connectivity information through shared points and represents a properly connected set of transistors. This information is more than enough to represent a topological sized schematic and a stick diagram, and is nearly sufficient to construct design-rule correct mask geometry.

The Pooh representation formalizes the notions of shared points, segments, and "miss" distances into a complete topological circuit representation. This representation, together with the Pooh synthesis and analysis rules, form the Pooh algebra of circuits.

Interconnect and transistor paths are a sequence of path segments. Every path segment is a directed line segment and an arc. The placement of each path segment is defined by two connection points. Other connection points may be attached along the straight portion of a path segment.

Connection and transistor points express the connectivity of the paths. A transistor point is formed at the intersection of the channel and gate path segments. A connection point is formed either by placing the end point of a path segment or by connecting one path to another.

This representation coupled with the Pooh synthesis and analysis rules ensure the description of strictly legal designs. The synthesis rules allow only valid interconnection between points and paths and construct transistor paths such that they meet the length and width constraints. The analysis rules ensure that path segments cross only at valid connection and transistor points.

## 2.2 GDR Representation

A stick diagram differs from a schematic in that the stick interconnect wires, transistors and connection points are "colored" according to the Geometrical Design Rules (GDRs).

GDRs are rules dictated by the fabrication technology that govern how structures may be placed together. A stick diagram demonstrates some of the assumptions about a particular technology, such as that there are multiple interconnection layer types, and multiple transistor types.

Since a chip description is an interconnection of transistors, it make sense to represent the GDRs in terms of transistors and their connections instead of the traditional technique of representing GDRs in terms of the fabrication layers. Thus the Pooh GDR representation contains a list of technology dependent information that describes how to create transistors, interconnect and connection points, and how to connect these structures together.

The GDR descriptions are generic definitions for a particular technology. Each element in a cell is an instance of one of the definitions. The GDRs fall into two categories—descriptions of legal structures and descriptions of legal interactions between structures. The descriptions of individual structures include a logical layer type. This layer type is symbolic as opposed to a physical or geometrical layer [Williams 77]. For example, in nMOS, polysilicon, diffusion and metal are logical layer types. Each of these have a single physical layer—polysilicon, diffusion and metal. A Low Resistance Connector (LRC) is an nMOS logical layer that is comprised of three physical layers—polysilicon, diffusion and buried. In cMOS, there are at least four logical layers—polysilicon, metal, p-diffusion, and n-diffusion. Both the p-diffusion and the n-diffusion logical layers are often composed of multiple geometrical layers.

Each interconnect type description consists of:

- 1) a logical layer type,

- 2) a minimum width,

- 3) the geometrical layers that comprise this logical layer, and

- 4) the geometrical overlap rules.

Each transistor type description has a:

- 1) transistor type,

- 2) channel logical layer,

- 3) gate logical layer,

- 4) minimum gate width,

- 5) minimum channel width,

- 6) minimum extension of gate and channel layers beyond the gate region,

- 7) the geometrical layers that comprise this transistor, and

- 8) the geometrical overlap rules.

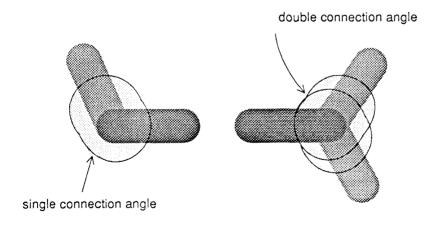

Connection points are connections between one or more paths. If these paths are of the same type, then the connection point rules are defined by the transistor and interconnect rules. However if the connection point is between paths of different types, then the connection point is called a contact and has its own unique GDRs. Each contact description consists of:

- 1) the connection point type,

- 2) the number of physical connection points,

- 3) for each point, the legal logical connection layers.

- 4) the legal angle or angles of connection for each legal interconnect type, and

- 5) reference to the geometrical implementation description.

The GDR interaction rules include both spacing and angle rules. Each spacing description includes both a rule that applies to structures of different electrical nodes, and a second rule that applies to structures of the same node. Angle rules are always between paths of the same node. Spacing rules are:

- 1) Minimum Interconnect to Interconnect Spacing,

- 2) Minimum Interconnect to Transistor Spacing,

- 3) Interconnect to Contact Spacing,

- 4) Transistor to Transistor Spacing,

- 5) Transistor to Contact Spacing, and

- 6) Contact to Contact Spacing.

#### Angle rules are:

- 1) Minimum Interconnect to Interconnect Angle,

- 2) Minimum Interconnect to Transistor Angle, and

- 3) Minimum Transistor to Transistor Angle.

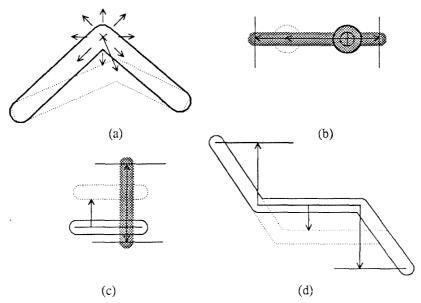

# 2.3 Geometrical and Topological Representation

Pooh constructs the geometry of a circuit in a manner aimed at reducing the designrule enforcement task. Devices and interconnect are expressed as a center-line, and are generated algorithmically. The geometry of transistors and interconnect is formed by maintaining a constant radius around each line segment and point. Connection points are expressed as points and are constructed as circles. We can use simple Euclidean geometrical operations between center-lines and points to perform all design rule calculations. The problem of performing operations between the complex edges of mask polygons is completely avoided. This section describes these instances of the GDR definitions.

Transistors are either a path or a point. A "wide" transistor path is defined with:

- 1) a transistor type,

- 2) a name,

- 3) a list of the segments that form the path of the gate,

- 4) a length and width,

- 5) one or more transistor points where connections occur,

- 6) two or more connection points,

- 7) the distance from the start of the path to the transistor's gate region,

- 8) the point indicating the end of the gate region, and

- 9) three electrical node numbers (source, drain and gate).

A "long" transistor path is similarly defined with the channel, rather than the gate, as the center-line layer. A transistor point has the following attributes:

1) a transistor type,

- 2) a name,

- 3) an X,Y coordinate,

- 4) the channel segment or segments,

- 5) the gate segment, and

- 6) three electrical node numbers.

Each interconnect path has the following attributes:

- 1) an interconnect type,

- 2) a width,

- 3) a list of the segments that form the path,

- 4) multiple connection points,

- 5) an electrical node number, and

- 6) the electrical capacitance of this path.

Each connection point has these attributes:

- 1) a type,

- 2) an X,Y coordinate,

- 3) an orientation,

- 4) a node number, and

- 5) a list of the path segments that share this point.

#### 2.4 Circuit Synthesis Rules

There are several types of synthesis rules in Pooh. Some rules are inherent to the Pooh system and govern how points and segments are composed to form structures. For example: a path segment may "miss" a connection point, but is restricted to connect ("miss" distance equal to zero) to a transistor. The other types of rules govern both how structures are connected together and how structures are physically made. These rules are kept in the technology description, and include information such as the actual distance a path segment must "miss" a connection point, and how to make a particular type of connection point or transistor.

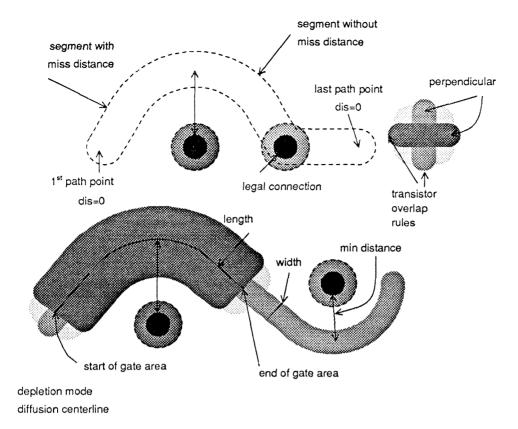

Pooh enforces the construction of correct interconnect and transistor paths as shown in Figure 2-5. It enforces a minimum width on all interconnect paths, and a minimum width and length on transistor paths. For a transistor path, the length and width parameters coupled with the transistor overlap rules yield the end point of the transistor gate area. Such a path then continues as an interconnect path with the logical layer of the center-line.

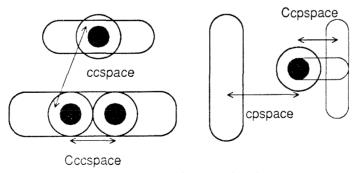

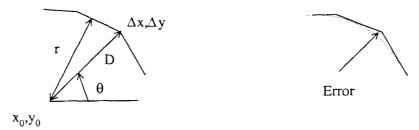

Pooh applies a set of rules to the construction of the sequence of segments that form the interconnect and transistor paths. Each segment may include many connection points, but two points define its physical placement—the first and last points. A segment, rather than connecting to these two points, may instead "miss" them. The arc of this segment is defined by its last point, a "miss" distance and the next segment. The sign of the "miss" distance indicates the sense in which the segment goes around the point. If the "miss" distance is zero, then the last point is indeed a connection point, and the arc is of zero length. Pooh then ensures that the path layer is one of the legal logical

Figure 2-5: Synthesis Rules

connection layers for the point type, and adjusts the angle of the connection point to match the legal angle of connection as shown in Figure 2-6. The first and the last point of the path must have a zero "miss" distance. Figure 2-7 illustrates the use of the "miss" distances.

Figure 2-6: Legal Angle of Connection

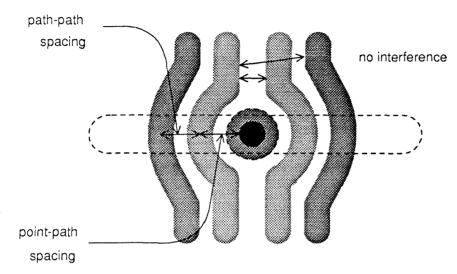

The spacing rules govern the segment to point "miss" distances based on the path to point spacing and the path to path spacing. If the current segment is the first segment to "miss" a point, or if there isn't a spacing rule between this segment and the point's other segments, then the "miss" distance is calculated as the spacing rule between this segment's path type and the point's type. Otherwise Pooh finds the point's segment with the largest "miss" distance that interferes with this segment and adds to the "miss" distance the spacing rule between this segment's path type and the interfering segment's path type.

Figure 2-7: "Miss" Distance

Pooh enforces an additional set of rules in the construction of transistor points. The channel and the gate segments must connect ("miss" distance equal to zero) to a transistor point. If the transistor point is not part of a transistor path, the gate segment and the channel segment must be perpendicular as shown in Figure 2-5.

There are paths that define entire regions: the well in cMOS is one example. These "surround" paths are similar to other pooh paths, except that the polygons described by the paths are closed — the first point is equivalent to the last point. Pooh constructs these paths by enforcing a direction during segment synthesis; all surround paths are clockwise.

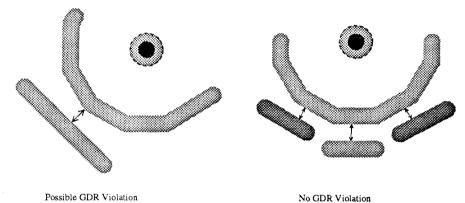

## 2.5 Circuit Analysis Rules

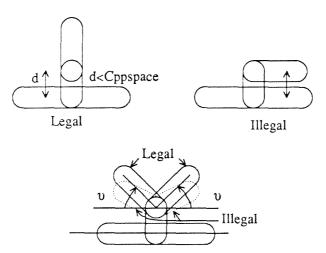

Most GDRs are enforced correct by construction during the creation of the Pooh paths. Some analysis is necessary to enforce the remaining GDRs. Analysis determines illegal interactions between interconnect paths, transistor paths and connection points. The synthesis rules ensure the correct construction of the individual structures, so what remains at the analysis phase is ensuring correct spacing and angles between adjacent structures. During the analysis phase Pooh only looks at structures that are "close" to the current structure, i.e., within the maximum GDR bounding box that surrounds the current structure. Figure 2-8 illustrates possible interactions.

Figure 2-8: Analysis Rules

The distance from each point to surrounding connected and unconnected points and lines is compared to the minimum spacing rules. If the point is a transistor, then the four closest points are checked for valid overlap. Often the transistor overlap is GDR correct by construction, but existing points may violate transistor overlap rules and thus must be checked. If the point is a contact, then the closest connected contacts are checked for valid connected contact spacing. Finally the point's distance from surrounding segments and points is calculated and compared to both the minimum point to point (contact—contact) and point to path (contact—interconnect and contact—transistor) distances.

Pooh checks to ensure that the distance from each segment to surrounding points and segments is greater than or equal to the minimum GDR spacing rules. First, it marks all directly connected segments, ensuring that connected path—path spacing rules are met. Next, it checks that this segment's distance from surrounding contacts is greater than the appropriate point—path spacing rule. It then checks that this segment's distance from the two end points of all unmarked surrounding segments is greater than or equal to the appropriate path to path spacing rule, and that the segments do not cross. If either of the two segments contain non-zero arcs, the arc—arc or line—arc distance is calculated and compared to the spacing rule. Finally, for each of this segment's connection points, Pooh checks the angle between this segment and the point's other connecting segments. The angle between two segments that connect to the same point must be greater than or

equal to the minimum path to path angle.

The analysis of surround paths is similar to that of other paths with a single exception: distances are signed. If points and segments occur inside the surround path, with a negative distance, then the distance must be greater than or equal to the inside GDR spacing rule. Otherwise, the points and segments occur outside the surround path, with a positive distance, and the distance must be greater than or equal to the outside GDR spacing rule.

#### 2.6 Simulation Interface

Simulation is a necessary and important part of the verification of a design. The GDR algorithms guarantee design rule correct circuits, and the typed ports provide a mechanism for statically checking the composition of signals. But, it is still necessary to simulate a circuit, and have some degree of assurance that the geometry is equivalent to the simulated circuit. Simulation input is easy to generate from the same Pooh representation from which geometry is generated.

Pooh supports three different kinds of simulation—depending on the level of detail a designer is interested in. The three types are:

- 1) an analog device simulator, such as SPICE [Nagel 75],

- 2) a logical switch level simulator such as Mossim [Bryant 82], and

- 3) a dynamic timing simulator such as the one developed by Tzu-Mu Lin, at Caltech [Lin 84].

The information necessary to interface to these various simulators is easily derived, since Pooh maintains a list of the transistors, along with their types and strengths, and the node numbers of all the interconnection wires, along with their sizes.

# 2.7 Geometry Generation

At the completion of a design, a geometrical description may be generated from the Pooh representation. Since Pooh enforces GDRs, a designer may use a strict Pooh representation up until the time of mask description for fabrication. Therefore geometry generation is a very small part of the computation necessary to complete a design.

For each technology, Pooh maintains the information needed to go from the Pooh representation to geometry. This information is:

- 1) for each logical layer and transistor type the geometrical layers and the overlap rules between the geometrical layers, and

- 2) for each connection point a reference to the geometrical object that implements this point.

Points are modeled as fixed geometrical objects. Paths are modeled as algorithmic geometrical objects and therefore each path generates a unique set of polygons. This information is kept in the technology file along with the design rule data.

Often, fabrication houses or silicon foundries find it necessary to modify or process geometry files for a particular technology. The processing often includes bloats, shrinks and scaling. Shrinking geometry while maintaining the electrical connectivity is a very difficult problem for general polygons and wires. Since the centers-lines of Pooh

paths are connected, called skeletal connectivity, it is equally easy to perform bloats, shrinks and scaling of designs generated by Pooh.

# 3. Synthesis Algebra

This chapter describes how we may construct each path such that it meets the GDR constraints. The computational complexity of calculations between paths is minimized by the choice of elementary structures: points, lines and arcs. Points are represented as circles. Lines are represented by their directed and normalized line equation. Interconnection, transistors, ports and connection points are composed from these elements.

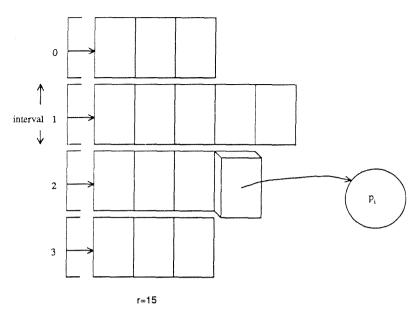

In the following section, let  $P_k$  denote a Pooh path, where a Pooh circuit is a set of paths  $\mathcal{P}$  and  $P_k \in \mathcal{P}$ . Each path includes an initial point  $p_0$  and a set of m segments  $S_k \equiv \{s_1, s_2, \ldots s_m\}$ . The placement of each path segment  $s_i$  is based on the two points  $p_{i-1}$  and  $p_i$  and both the segment's arc radius  $r_i$ , and the last segment's arc radius  $r_{i-1}$ . Given a point  $p_j$ , let  $x_j$ ,  $y_j$  denote the point's x-coordinate and y-coordinate respectively.

## 3.1 Primitive Representations

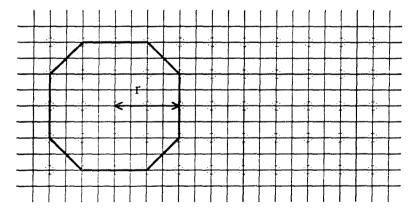

#### Circles

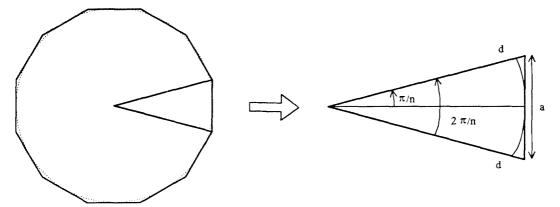

A unit circle is a convenient way of representing both points and arcs, of which larger constructs may be composed. A circle allows calculations to be performed between lines and points without introducing polygonal edges. Mask geometry cannot, however, be created using perfect circles—therefore Pooh uses an n-point circle approximation. The polygonal approximation and its effect on the calculations presented in this chapter are discussed in detail in Chapter 7. The next section assumes perfect circles.

#### Lines

The line segment portion of a segment  $s_i$  is represented by the normalized line equation:

$$L_{i}(x, y) = A_{i}x + B_{i}y + C_{i}$$

where  $A_{i}^{2} + B_{i}^{2} = 1$  (3-1)

and, for a point x, y on the line:

$$L_i(x,y)=0.$$

In Figure 3-1, the point  $p_2$  is the end point of the segment s if the segment radius is zero. Otherwise  $p_2$  is the starting point of the segment's arc. This figure illustrates the line calculation for the line L(x, y):

Figure 3-1: Line Calculation

Given two points  $p_1$  and  $p_2$ , the normalized coefficients A, B, and C are computed as follows:

$$Len = \sqrt{(x_2 - x_1)^2 + (y_2 - y_1)^2}$$

$$A = -\sin\theta = (y_1 - y_2)/Len$$

$$B = \cos\theta = (x_2 - x_1)/Len$$

$$C = -Ax_1 - By_1.$$

(3-2)

The slope of this line is -A/B or  $\tan \theta$ . An equivalent line L'(x, y), in the opposite direction (from  $p_2$  to  $p_1$ ), is computed based on the angle  $\theta' = \theta + \pi$ :

$$\sin \theta' = \sin(\theta + \pi) = -\sin \theta$$

$A' = -A$

$\cos \theta' = \cos(\theta + \pi) = -\cos \theta$   $B' = -B$

$C' = -C$

The distance D between the line equation  $L_i(x, y)$  and a point  $p_q$  is found by [Sutherland 78]:

$$D = A_i x_q + B_i y_q + C_i (3-3)$$

where the sign of D indicates the direction of the point with respect to the line. The Pooh line equation was chosen such that a negative D indicates the point is on the right hand side of the line and a positive D indicates the point is on the left hand side of the line.

The intersection point  $p_{int}$  between the two lines  $L_1(x, y)$  and  $L_2(x, y)$  is found as follows [Sutherland 78]:

$$\det = B_1 A_2 - A_1 B_2$$

$$p_{int} = \left( (B_2 C_1 - B_1 C_2) / \det, (A_1 C_2 - A_2 C_1) / \det \right). \tag{3-4}$$

#### Arcs

Arcs, like line segments, are directional and the sign of the arc radius  $r_i$  indicates its direction. A positive radius indicates a counter-clockwise direction, and a negative radius indicates a clockwise direction. In the following section, let  $A_i$  denote the arc associated with the segment  $s_i$ ,  $a_i^b$  be the arc's starting point, and  $a_i^e$  be the arc's ending point.

An arc  $\mathcal{A}_i$  is determined by three points  $p_{i-1}$ ,  $p_i$ ,  $p_{i+1}$ , and three radii  $r_{i-1}$ ,  $r_i$ ,  $r_{i+1}$ . The pair  $p_{i-1}$ ,  $r_{i-1}$  determines the starting point of the arc  $a_i^b$ , the pair  $p_i$ ,  $r_i$  indicates the placement of  $\mathcal{A}_i$ , and the pair  $p_{i+1}$ ,  $r_{i+1}$  determines the ending point of the arc,  $a_i^c$ . The following equations present the calculations necessary for finding the line segment  $L_i(x,y)$ , that joins the arcs  $\mathcal{A}_{i-1}$  and  $\mathcal{A}_i$ , with  $r_i > 0$  and  $r_{i-1} < 0$ . From there, we may generalize the calculation to all signed radii. Figure 3-2 illustrates this calculation.

Figure 3-2: Arc Calculation

$$\begin{aligned} |L_r| &= r_i - r_{i-1} \\ |L_x| &= x_i - x_{i-1} \\ |L_y| &= y_i - y_{i-1} & L'_i \parallel L_i \\ |L_p| &= \sqrt{|L_x|^2 + |L_y|^2} & L_r \perp L_i \\ |L'_i| &= \sqrt{|L_p|^2 - |L_r|^2} \\ \theta' &= \theta_1 + \theta_2 \\ \cos_i(\theta') &= \frac{|L_x||L_r| - |L_y||L'_i|}{|L_p|^2} \\ \sin_i(\theta') &= \frac{|L_y||L_r| + |L_x||L'_i|}{|L_p|^2} \end{aligned}$$

The arc starting point  $a_i^b = (x_i - r_i \cos_i(\theta'), y_i - r_i \sin_i(\theta'))$ . Let us define a point on the unit circle:

$$p_i^c = (-\cos_i(\theta'), -\sin_i(\theta')). \tag{3-5}$$

Then, the arc beginning point  $a_i^b = (x_i + r_i x_i^c, y_i + r_i y_i^c) = p_i + r_i p_i^c$  and the last arc's ending point  $a_{i-1}^e = p_i - |r_{i-1}|p_i^c$ . But,  $r_{i-1} < 0$  by definition, therefore  $a_{i-1}^e = p_i + r_{i-1}p_i^c$ . In general, we may compute the tangent point  $p_i^c$  on the unit circle, and then use the sign of the radii to determine the ending point of  $\mathcal{A}_{i-1}$ , and the beginning point of  $\mathcal{A}_i$ . The ending point of  $\mathcal{A}_i$  is found while calculating the starting point of  $\mathcal{A}_{i+1}$ . The calculation is:

$$a_{i}^{b} = p_{i} + r_{i}p_{i}^{c}$$

$$a_{i-1}^{c} = p_{i-1} + r_{i-1}p_{i}^{c}.$$

(3-6)

The arc representation is  $\mathcal{A}_i = (r_i, p_i, p_i^c, \mathcal{A}_{i+1})$  from which we may easily compute  $a_i^b$  and  $a_i^c$  from (3-6). An illustration of a positive and a negative arc, based on the same unit circle points  $p_0$  and  $p_1$ , is shown in Figure 3-3. In practice, the points on the unit circle are chosen from a set of pre-calculated points, as is discussed in Chapter 7.

Figure 3-3: Arc Representation

## 3.2 Path Synthesis

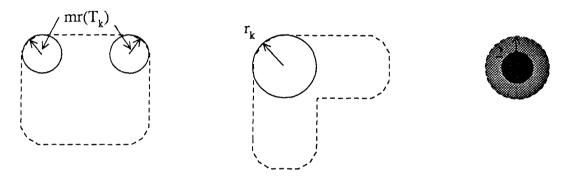

Pooh constructs a path  $P_k$  "correct" according to the GDRs. The following definitions of GDRs are introduced:

$$mw(T_k) \equiv minimum \ width \ of \ a \ path \ of \ type \ T_k$$

$mr(T_k) \equiv mw(T_k)/2$   $minSpace(s_i, s_j) \equiv minimum \ spacing \ between \ paths \ of \ type \ T_k \ and \ T_l$   $where \ s_i \in S_k \ and \ s_j \in S_l$   $PminSpace(s_i, p_q) \equiv minimum \ spacing \ between \ a \ path \ of \ type \ T_k \ where \ s_i \in S_k$  and the point  $p_q$ .

A path  $P_k$  is defined by a path type  $T_k$ , a width  $W_k$ , where  $W_k \ge mw(T_k)$ , an initial point  $p_0$ , and a set of m segments  $S_k$ . Each of the path segments is synthesized in sequence to construct a valid path. Each path segment has four points of possible interest. These points are the first and last points of the segment, and the first and last points of the segment's line segment. Let us define four functions to aid in the description of a path segment:  $lp(s_j)$  for the last (previous) point of the segment  $s_j$ ,  $lr(s_j)$  for the last radius of the segment  $s_j$ ,  $lp(s_j)$  for the starting point of the line segment  $L_j(x, y)$ , and  $ep(s_j)$  for the ending point of the line segment, as follows:

$$lp(s_j) = \begin{cases} p_0, & j = 1 \\ p_{j-1}, & \text{otherwise.} \end{cases}$$

$$lr(s_j) = \begin{cases} 0, & j = 1 \\ r_{j-1}, & \text{otherwise.} \end{cases}$$

$$bp(s_j) = \begin{cases} lp(s_j), & lr(s_j) = 0 \\ a_{j-1}^e, & \text{otherwise.} \end{cases}$$

$$ep(s_j) = \begin{cases} p_j, & r_j = 0 \\ a_j^b, & \text{otherwise.} \end{cases}$$

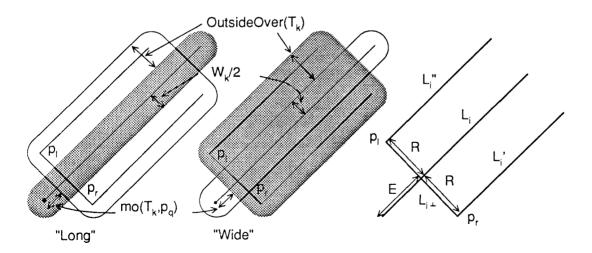

A minimum width path  $P_k$  is defined by the locus of points exactly half the minimum width, or  $mr(T_k)$ , distance away from the path center-line. A path  $P_l$  whose width is greater than the minimum width is defined by the locus of points exactly  $mr(T_l)$  distance away from the path skeleton. This skeleton is the path center-line expanded by the width  $W_l$  minus the minimum radius.

A minimum width path segment  $s_i$  where  $s_i \in S_k$  of the path  $P_k$  is shown in Figure 3-4. Notice that the starting point  $bp(s_i)$  is surrounded by a half circle whose radius is  $mr(T_k)$ . In fact, the path  $P_k$  is defined by the locus of points exactly  $mr(T_k)$  distance away from the path center-line. This path  $P_k$  is defined as a set of m segments,  $r_m = 0$ , where each segment consists of a composition of an arc and a line identical to the one shown in Figure 3-4.

Figure 3-4: Minimum Width Segment

A path  $P_l$  where  $W_l > mw(T_l)$  is defined by the locus of points exactly  $mr(T_l)$  distance away from the path skeleton. The path skeleton surrounds the center-line by

a distance  $d = W_l/2 - mr(T_l)$  as shown in Figure 3-5. The line segment portion of each segment  $s_i \in S_l$  is defined as three parallel lines  $L_i(x,y)$ ,  $L_i'(x,y)$  and  $L_i''(x,y)$  where  $C_i' = C_i + d$ , and  $C_i'' = C_i - d$ . Each path segment arc is identical to the arc of a minimum width path. The line  $L_{i\perp}(x,y) = -B_i x + A_i y$ . The calculation of a wide path's end conditions at the points  $p_0$  and  $p_m$ , is based on  $L_1(x,y)$ ,  $L_1'(x,y)$ ,  $L_1''(x,y)$ ,  $L_1''(x,y)$ , and  $L_m(x,y)$ ,  $L_m'(x,y)$ ,  $L_m'(x,y)$ ,  $L_m(x,y)$ , respectively. The offsets from  $p_0$  to the two points  $p_l$  and  $p_r$ , as shown in Figure 3-5, are:

$$p_l = (A_1 d, B_1 d)$$

$p_r = (-A_1 d, -B_1 d).$  (3-7)

from equation (3-4). The point offsets from  $p_m$  are similarly calculated.

Figure 3-5: Wide Path Segment

#### Segment Synthesis

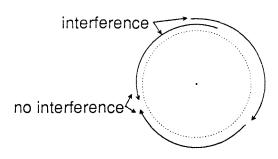

Each segment  $s_i$  is initially designated by a point  $p_i$ , a direction  $q_i = \pm 1$ , and a connection status. Let  $ValidConnect(s_j, p_q)$  denote a function that indicates whether or not there is a valid connection between  $s_j$  and  $p_q$ . If  $s_i$  connects to the point  $p_i$  and if  $validConnect(s_i, p_i)$ , then  $r_i$  is the design rule correct connection radius, often equal to zero. Otherwise, if the segment does not connect,  $r_i$  is calculated based on the design rules. If other segments have not previously "missed" the point  $p_i$ , then  $r_i$  is equal to  $PminSpace(s_i, p_i)$ . Otherwise we must detect interference between this arc  $A_i$  and all other arcs  $A_i$  where  $p_i \equiv p_i$ , as illustrated in Figure 3-6. In order to detect arc interference,  $A_i$  must be defined, which in turn implies that  $r_i \neq 0$  to use equation (3-6). Therefore, initially we let  $r_i = q_i$ .

Let  $U(A_a)$  denote a unit arc defined as:

$$U(\mathcal{A}_q) = (p_q^c, p_{q+1}^c, dir)$$

$$dir = \begin{cases} 1, & r_q \ge 0 \\ -1, & r_q < 0. \end{cases}$$

Figure 3-6: Arc Interference

These functions detect interference between two unit arcs  $U_1$  and  $U_2$ :

```

define in(U_1, U_2): boolean

arc ranges overlap

enddef

define otherhalf (U_1): U

p_q^c \leftarrow -p_q^c; \quad p_{q+1}^c \leftarrow -p_{q+1}^c;

enddef

define reverse (U_1): U

dir \leftarrow -dir;

enddef

define interfere (U_1, U_2): boolean

interfere \leftarrow if dir_1 > 0 and dir_2 > 0 then in (U_1, U_2)

ef dir_1 > 0 and dir_2 < 0 then in (U_1, otherhalf(reverse(U_2)))

ef dir_1 < 0 and dir_2 > 0 then in(otherhalf(reverse(U_1)), U_2)

else in (reverse (U_1), reverse (U_2))

fi

enddef

```

The detection of arc overlap is simplified when defined in terms of the underlying circle approximation. Therefore, the definition of the function in is postponed until the circle approximation is described. Chapter 7 includes the definition of in.

If we assume that the segments that depend on a point  $p_q$  are maintained in a list sorted by increasing arc radius |r|, then the following algorithm finds the minimum design rule correct "miss" distance between  $s_q$  and  $p_q$ :

```

define minimum_distance (s_q, p_q): distance var min_dis: distance; min_dis \leftarrow PminSpace (s_q, p_q); while there is another segment missing p_q do s' \leftarrow next segment; if interfere (U(s_q), U(s')) then if minSpace(s_q, s') > 0 then min_dis \leftarrow |r'| + minSpace(s_q, s') fi fi od minimum_distance \leftarrow if r_q < 0 then -min_dis else min_dis fi enddef

```

Once the segment arc radius  $r_i$  is calculated using minimum\_distance,  $\mathcal{A}_i$  is defined by (3-6), and  $L_i(x,y)$  is calculated using (3-1). Given this complete segment definition, it is possible to detect and prevent an invalid segment. It is possible to indicate a miss direction such that a segment loops, as shown in Figure 3-7, which is never desirable. The dot product between the line  $L_i(x,y)$  and the line connecting  $a_i^b$  and  $a_i^c$ , shown in the figure as  $L_c$ , detects this condition between two consecutive segments. If the segment is found to be invalid, Pooh replaces the two segments by a single segment as shown in the figure.

Figure 3-7: An Illegal Segment

The point  $a_i^b$  represents the tangent point of the segment  $s_i$  on the circle of radius  $|r_i|$  centered at  $p_i$ , and the point  $a_i^e$  represents the tangent point of the segment  $s_{i+1}$  on the same circle. In order to prevent these two line segments from crossing, the angle  $\theta$

between  $s_i$  and the line connecting  $a_i^b$  and  $a_i^e$  must be greater than or equal to 90°. If  $-90^\circ < \theta < 90^\circ$  then  $s_i$  is ignored.

$$Dot = s_i \cdot L_c = \cos \theta = A_i A_c + B_i B_c$$

The segment construction rules described thus far allow us to define any legal interconnection path. The rules must be extended to incorporate transistor paths.

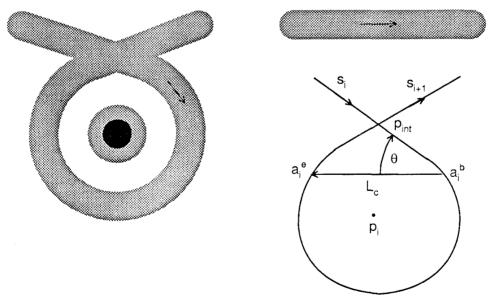

### Transistor Synthesis

With respect to synthesis algorithms, transistor paths differ from interconnection paths in two ways: (1) the presence of two logical layers—channel and gate, and (2) a Length/Width parameter that determines when one of the logical layers ends. A transistor path is composed of the center-line layer and the outside layer, one of which is the channel, the other the gate. If the center-line layer is the gate, then the outside layer is the channel and the path is a "wide" transistor, otherwise the path is a "long" transistor, as shown in Figure 3-8. Let us call these two layers  $Center(T_k)$  and  $Outside(T_k)$  for a transistor of type  $T_k$ . Let  $\mathcal{L}_k$  denote the Length/Width parameter that determines when the  $Outside(T_k)$  layer ends. The path width  $W_k$  governs the width of the center-line layer as shown in Figure 3-8. The parameter  $\mathcal{L}_k$  governs the length of the outside layer  $Outside(T_k)$ . There is a set of overlap design rules for each transistor type that dictate the distance each of the logical layers must overlap the gate region. The two definitions for the overlap rules are  $OutsideOver(T_k)$  for the outside overlap, and  $CenterOver(T_k)$  for the center-line overlap.

Figure 3-8: Transistor Overlap

Figure 3-8 illustrates the beginning of a transistor path. We must calculate the point offsets  $p_l$  and  $p_r$  such that the  $OutsideOver(T_k)$  and  $CenterOver(T_k)$  rules are satisfied. The lines  $L_i(x,y)$ ,  $L'_i(x,y)$ , and  $L''_i(x,y)$  are the same lines used in Figure

3-5. The line  $L_{i\perp}(x,y) = -B_i x + A_i y + E$ . Let the minimum overlap be defined as:

$$mo(T_k, p_q) = \left(CenterOver(T_k) - mr(Center(T_k))\right) \max \left(PminSpace(Outside(T_k), p_q)\right).$$

The two point offsets  $p_l$  and  $p_r$  are calculated (from equation (3-4)) by:

$$E = mo(T_k, p_q) + mr(Outside(T_k))$$

$$R = W_k/2 + OutsideOver(T_k) - mr(Outside(T_k))$$

$$p_l = (A_iR + B_iE, B_iR - A_iE)$$

$$p_r = (-A_iR + B_iE, -B_iR - A_iE).$$

(3-8)

This equation allows us to calculate the beginning of a transistor path. We must also end the transistor region. Pooh uses the parameter  $\mathcal{L}_k$  to determine the segment  $s_n$ , such that  $1 \leq n \leq m$ , and on which the center-line length achieves  $\mathcal{L}_k$ .

The parameter  $\mathcal{L}_k$  governs the size of the transistor along the center-line. If  $Center(T_k)$  is the channel then the parameter is the transistor length, and  $W_k$  is the transistor width. If  $Center(T_k)$  is the gate then the parameter is the transistor width and  $W_k$  is the transistor length. Given that the length is less than the total path length, or  $\mathcal{L}_k + mo(T_k, p_0) + mo(T_k, ep(s_n)) \leq \sum_{i=1}^m (|L_i(x, y)| + arclen(\mathcal{A}_i))$ , then we must find the segment  $s_n$ , such that:

$$\sum_{i=1}^{n-1} (|L_i(x,y)| + \operatorname{arclen}(\mathcal{A}_i))$$

$$\leq \mathcal{L}_k + \operatorname{mo}(T_k, p_0) + \operatorname{mo}(T_k, \operatorname{ep}(s_n))$$

$$\leq \sum_{i=1}^{n} |L_i(x,y)| + \sum_{i=1}^{n-1} \operatorname{arclen}(\mathcal{A}_i).$$

This condition assumes that  $\mathcal{L}_k$  is achieved on the line segment portion of a path segment. A segment that meets these constraints may not exist, if the length is achieved on the arc portion of a segment, which implies that for some q:

$$egin{aligned} &\sum_{i=1}^{q} |L_i(x,y)| + \sum_{i=1}^{q-1} arclen(\mathcal{A}_i) \ &\leq \mathcal{L}_k + mo(T_k,p_0) + mo(T_k,ep(s_q)) \ &\leq \sum_{i=1}^{q} (|L_i(x,y)| + arclen(\mathcal{A}_i)). \end{aligned}$$

If this second condition is true, then we insert a segment s' that approximates the arc  $\mathcal{A}_q$  at the position that  $\mathcal{L}_k$  dictates between the segments  $s_q$  and  $s_{q+1}$ . Then,  $\mathcal{L}_k$  is achieved on the segment s' by design, and thus the segment  $s_n = s'$ .

We may use the segment  $s_n$  to determine the two point offsets  $p_l$  and  $p_r$  that yield a transistor path that meets the specified  $\mathcal{L}_k$  constraint. We let

$$E = \sum_{i=1}^{n} (|L_i(x,y)|) + \sum_{i=1}^{n-1} \operatorname{arclen}(A_i) - \mathcal{L}_k - mo(T_k, p_0) + mr(\operatorname{Outside}(T_k)),$$

and then compute the points using equation (3-8). The transistor path continues in the center-line logical layer as if it were an interconnection path of type  $Center(T_k)$ .

#### Surround Path Synthesis

The synthesis of a surround path  $P_k$  differs from other paths in three ways: (1) the path width is always twice the minimum radius, or  $W_k = 2 \times mr(T_k)$ , (2) the first and last points of the path are the same, or for a path  $P_k$  with m segments,  $p_0 = p_m$ , and (3) the sign of the segment arc radius  $r_j$ , for  $s_j \in S_k$ , indicates whether the point  $p_j$  is inside or outside the path. Surround paths define entire regions and are clockwise paths by construction. Pooh enforces these three restrictions, and otherwise constructs surround paths in the usual manner.

### 3.3 Point Calculations

The placement of a point determines the placement of one or more path segments, but it may also be determined by one or two line segments using the line intersection equation (3-4). It is possible to designate a point as placed at the intersection of two line segments. The placement of such a point may be computed directly from (3-4). It is even possible to designate a segment  $s_i$  as placed perpendicular to segment  $s_j$ , where  $s_i$  and  $s_j$  are in general not members of the same path's set of segments.

Given the segments  $s_i$ ,  $s_j$  and  $p_1$ =bp( $s_i$ ), we may calculate the point  $p_i$ , with  $r_i$ =0, ensuring that  $s_i \perp s_j$ . The point  $p_i$  is either at the intersection of  $s_i$  and  $s_j$ , as shown in Figure 3-9, or there is another point  $p_q$  at the intersection of  $s_i$  and  $s_j$  and  $p_i$  is some distance Ext past  $p_q$ , as shown in Figure 3-9. This latter type of calculation is used to construct a point that meets the transistor overlap rules, given the transistor point  $p_q$ . The calculation to find the point  $p_i$  at the intersection of  $s_i$  and  $s_j$  is:

$$L_{i}(x,y) = -B_{j}x + A_{j}y + C_{i}$$

$$C_{i} = B_{j}x_{1} - A_{j}y_{1}$$

$$p_{i} = (B_{j}C_{i} - A_{j}C_{j}, -A_{j}C_{i} - B_{j}C_{j})$$

(3-9)

from equation (3-4). Equation (3-9) may be extended to calculate a point beyond the intersection of  $s_i$  and  $s_j$ . If  $s_i$  is of type  $T_k$ , and the transistor point  $p_q$ , at the intersection of  $s_i$  and  $s_j$ , is of type  $T_l$ , then the calculation is:

$$Ext = if T_n = Center(T_t) then CenterOver(T_t) else OutsideOver(T_t) fi$$

$$p_i = (B_i C_i - A_i(C_i + Ext), -A_i C_i - B_i(C_i + Ext)).$$

(3-10)

Contacts may or may not be symmetrical, according to the target set of GDRs. If a contact type is asymmetrical, then the point's orientation is important. If the GDRs

Figure 3-9: Intersection Points

dictate that the connection angle of a path type is fixed with respect to a contact, then Pooh orients the contact according to the GDRs. If more than one segment with a fixed connection angle connects to the same contact, then additional points, with different orientations are superimposed. Figure 2-6 illustrates oriented contacts.

The orientation angle  $\varphi$  of the contact point  $p_q$  is easy to compute, given the segment  $s_i$  of type  $T_k$ . If the point  $p_q$  is a contact of type  $c_q$ , then let the function  $fixedAngle(c_q, T_k)$  denote the GDR specified connection angle of  $c_q$  with respect to  $s_i$ . Then:

$$\theta = \arccos(B_i)$$

from (3-2)

$\varphi = \theta + fixedAngle(c_q, T_k).$

In this chapter I have described how, given a minimal amount of information, we may construct each path such that it meets the design rule constraints. This section has alluded to the circuit connectivity several times. The next chapter discusses synthesizing the connectivity of a collection of paths. I will then examine the calculations necessary to detect problems between paths.

# 4. Node Synthesis

The Pooh representation must express the connectivity of the transistors and their interconnection. There are two aspects to this problem. First, the description must contain sufficient information to provide the possibility of detecting whether or not two elements are connected. An element, in this context, is either a path or a point. Second, given any two elements within a Pooh circuit, there must be a quick way of detecting their underlying connectivity.

The first condition affects the composition of Pooh paths and points. The underlying philosophy is that any circuit level representation must express the designer's intent [McGrath 80]. In Pooh, any two elements that are connected share at least one reference to the same point. That is, connectivity is represented explicitly in the representation.

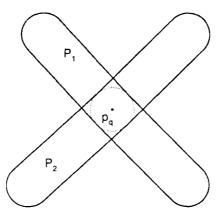

A simple example of shared references is shown in Figure 4-1. Two metal paths,  $P_1$  and  $P_2$ , each consisting of a single segment, are shown in the figure. These two metal paths are obviously connected since at one point they cross. The Pooh composition rules state that  $P_1$  is connected to  $P_2$  if and only if there exists a point  $p_q$  such that  $p_q$  is contained in both the  $P_1$  and  $P_2$  path definitions. Otherwise  $P_1$  is not connected to  $P_2$  and the Pooh analysis rules (described in Chapter 5) detect a spacing violation between  $P_1$  and  $P_2$ .

Figure 4-1: Connected Paths

The second condition mandates that there is a quick algorithm for determining whether or not any two elements are connected. Pooh uses Martin Rem's Equivalence class algorithm [Dijkstra 76] to note the elements' connectivity. Pooh elements are separated into equivalence classes using this algorithm, and then connectivity is detected by checking whether two elements are in the same equivalence class.

# 4.1 Node Equivalence

Pooh assigns each element a unique increasing positive node number, and then uses Rem's Algorithm to record connected elements. For each collection of paths there is an array nodenumbers that indicates the connectivity. Two elements with node numbers  $N_1$  and  $N_2$  are connected if and only if nodenumbers  $[N_1]$  = nodenumbers  $[N_2]$ . Given the array nodenumbers, the algorithm for asserting connectivity can be expressed:

```

define equivalence (N_1, N_2:

integer)

var al, a2 : integer;

a1 \leftarrow nodenumbers[N_1];

a2 \leftarrow nodenumbers[N_2];

while al \neq a2 do

if a2 < a1 then

nodenumbers [N_1] \leftarrow a2;

N_1 \leftarrow a1;

al ← nodenumbers[al];

else

nodenumbers[N_2] \leftarrow a1;

N_2 \leftarrow a2;

a2 ← nodenumbers[a2];

fi

od

enddef

```

The algorithm works by equating both node numbers  $N_1$  and  $N_2$ , two nodes of a tree, to the smallest integer k reachable from either  $N_1$  or  $N_2$ . Initially all node numbers are in separate equivalence classes, represented as trees of numbers. Then, each time equivalence  $(N_1, N_2)$  is invoked, a new tree is implicitly created that includes both  $N_1$  and  $N_2$ . If there are n node numbers, then the longest tree's path length may be n, in which case the worst case cost of executing n equivalence statements is  $O(n^2)$ . But, since each time equivalence is invoked, it flattens out the reachable tree, the expected height of any given tree remains less than  $\log(n)$ , in which case the cost of executing n equivalences is  $O(n \log(n))$ .

Any transistor, either a path or point type, is assigned three node numbers: source, drain and gate. Each interconnection path and connection point is assigned a single node number. Assuming that each time two elements are connected, equivalence of the two connecting node numbers  $N_1$  and  $N_2$  is invoked, then detecting whether or not any two elements are connected is simply whether or not nodenumbers  $[N_1] = nodenumbers [N_2]$ .

# 4.2 Path Connectivity Representation

This section describes the construction of a set of Pooh paths such that they fully maintain the circuit connectivity. It uses the notation introduced in Chapter 3. A Pooh circuit consists of a set of paths  $P \equiv \{P_1, P_2, \dots P_z\}$ , and a set of points  $\mathbf{p} \equiv \{p_1, p_2, \dots p_r\}$ . Each transistor, either a path  $P_k$  or a point  $p_k$ , includes three node numbers source<sub>k</sub>,  $drain_k$ , and  $gate_k$ . Each interconnect path  $P_l$  or connection point  $p_l$  includes a single

node number  $node_l$ . Let  $transistor(P_k)$  denote a function that indicates whether or not the path  $P_k$  is a transistor path, and let  $ptran(p_q)$  denote a function that indicates whether or not a point  $p_q$  is a transistor point.

In the following discussion, a path segment is designated for convenience as  $s_{k,j}$ . The notation  $s_{k,j}$  is shorthand for the  $j^{th}$  segment of the path  $P_k$ , or  $s_j \in S_k$  in the path  $P_k$ .

Each path segment maintains a set of points  $p_{k,j} \equiv \{p_1, p_2, \dots p_n\}$ , and a connection status for the points  $cs_{k,j} \equiv \{cs_1, cs_2, \dots cs_n\}$ . The points are maintained strictly for connectivity reasons, with the exception of  $p_n$ , that also determines the segment's placement. The point  $p_n$  may or may not be connected, all other points  $p_j$ , j < n, are connected by construction. This point  $p_n \equiv p_j$  on segment  $s_j \in S_k$  associated with the path  $P_k$ , described in the last chapter. Each connection status entry  $cs_i \in \{NoConnect, Connect, CSource, CDrain, PSource, PDrain\}$ . The first four connection status values denote the following: not connected, connected, connected to the source of a transistor point, and connected to the drain of a transistor point, respectively. The last two status values denote connecting a point to the source of a transistor path and connecting a point to the drain of a transistor path. The Pooh construction rules restrict the exact connection status values a particular point may have associated with it.