Automated Wiring Analysis of Integrated Circuit Geometric Data

bу

Charles R. Lang

Submitted in Partial Fulfillment of the Requirements for the Degree of Master of Science

CALIFORNIA INSTITUTE OF TECHNOLOGY

Computer Science Department

August 9, 1979

2891:TR:79

#### Abstract

Methods are presented by which the wiring data of an NMOS Integrated circuit be extracted from its may mask information. The procedures involved utilize the capabilties of a general purpose polygon package. The polygon operations are defined to enhance their use in application, however, the package is suitable for other uses, such as, design rule checking. The analysis is performed hierarchial symbol definitions of on mask The geometry is presumed to be described in geometry. (Caltech Intermediate Form). The analysis attempts to recognize three basic types of structures in the geometry: transistor devices (and capacitors), 2) 1) interconnection structures and 3) global interconnection Definitions are put forth for the distinction structures. of global and local wires. The data extracted from symbol geometry is the percent utilization of each symbol's area by each of the three types of structures. The purpose behind the extraction of this data is its use in the development and evaluation of wiring models for custom NMOS Two approaches are presented which extract such desian. The first is heuristic and depends on built-in assumptions of how the NMOS process is generally used. This technique loses accuracy if a design style falls outside these assumptions. The second technique is a method by which the topology of design may be extracted from The geometric objects, from which devices and geometry, interconnections are made, are preserved, such that wiring information can be obtained precisely. This method is complex and requires considerable computation, however,

the topology extracted may also be used to verify the geometric data against the original design topology.

# Table of Contents

| Abstract                                               | 2  |

|--------------------------------------------------------|----|

| List of Figures                                        | 6  |

| Chapter I: Introduction                                | 7  |

| 1.1 Background                                         | 7  |

| 1.2 Data Collection for Wiring Analysis                | 9  |

| 1.3 Overview                                           | 13 |

| Chapter II: Definition of Wiring Statistics            | 16 |

| 2.1 Data Collection Requirements                       | 16 |

| 2.2 Definition of a Device                             | 20 |

| 2.3 Global versus Local Wire                           | 22 |

| 2.4 Wiring Statistics                                  | 23 |

| Chapter III: Description of Polygon Manipulations      | 25 |

| 3.1 Polygon Requirements                               | 25 |

| 3.2 Logical Operations                                 | 29 |

| 3.3 Inflation and Deflation                            | 32 |

| 3.4 Selection of Sheets                                | 33 |

| 3.5 Other Operations                                   | 34 |

| Chapter IV: Heuristic Computation of Wiring Statistics | 38 |

| 4.1 Recognition of Structures by Heuristic Methods     | 38 |

| 4.2 Extraction of Devices                              | 39 |

| 4.3 Estimation of Symbol Area                          | 45 |

| 4.4 Extraction of Global Wire from Local Wire          | 48 |

| Chapter V: | Extraction of Circuit Topology          | 55  |

|------------|-----------------------------------------|-----|

| 5.1 Devi   | ces and Device Connections              | 55  |

| 5.2 Coll   | ecting Symbol Nets                      | 59  |

| 5.3 Exte   | rnal Connections                        | 46  |

| 5.4 New    | Devices Created by Symbol Interactions  | 69  |

| Chapter VI | : Results of Investigation              | 71  |

| 6.1 Prog   | ram Performance                         | 71  |

| 6.2 Anal   | ysis Data                               | 73  |

| Chapter VI | I: Conclusions                          | 76  |

| 7.1 Fact   | ors Influencing Polygon Manipulation    | 76  |

| 7.2 Desi   | rable Restrictions in the Specification |     |

| of A       | rtwork                                  | 77  |

| 7.3 The    | Requirement for Wiring Analysis         | 80  |

| References |                                         | 85  |

| Appendix I | : Skeletal Specification of a           |     |

|            | Simula Polygon Package                  | 88  |

| Appendix I | I: Simula Definition of CLASS Symbol    | 99  |

| Appendix I | II: Simula Program for Computing        |     |

|            | Wiring Statistics                       | 112 |

| Appendix I | V: CIFX, A Simula Program for           |     |

|            | Building Database Files From CIF        | 117 |

| Appendix V | : Implementation of Additional          |     |

|            | Polygon Operations                      | 139 |

# List of Figures

| Figure Follows |                                              | ws Page |

|----------------|----------------------------------------------|---------|

| 2.1 Lay        | out of a Complex Gate                        | 17      |

| •              | out of a Super Buffer                        | 17      |

| •              | out Illustrating Global and Local Wire       | 22      |

| 3.1 Self       | fintersection and Retracing of Polygons      | 29      |

| 3.2 Log.       | ical Operations Using Polygons               | 31      |

| 3.3 Def:       | lation of Polygons                           | 33      |

| 3.4 Inf        | lation of Polygons                           | 33      |

| 3.5 Merc       | ging of Symbol Wires and Boxes Into Polygons | 36      |

| 4.1 Ider       | ntification of Devices                       | 44      |

| 4.2 Find       | ding the Boundaries of a Symbol              | 47      |

| 4.3 The        | Annulus of a Symbol                          | 49      |

| 4.4 Find       | ding Possible External Contacts of a Symbol  | 51      |

| 4.5 Sept       | aration of Global and Local Wire             | 53      |

| S.i Find       | ding the Sizes and Connections to Devices    | 57      |

| 5.2 Grou       | uping Interconnection Structures into Nets   | 60      |

# Chapter I

## Introduction

# 1.1 Background

o f complex integrated circuits requires consideration to be given to the resources utilized by the devices and subcircuits. interconnection of. measures, the percentage of available area used by these interconnections is a large portion of the integrated circuit. The ability to estimate the size of a design and hence its manufacturing cost is very important to the eventual marketing or internal use of the part. appropriate models for the wiring of integrated circuits such estimates are usually poor. In addition, automatic design aids, such as, placement and routing programs are made more costly and less reliable if good interconnection models are not available.

the past, considerable effort has been given 10 solutions of these problems for printed circuit cards. Some of these techniques have found applicability in the integrated circuits. However, two major of 1) The differences exist between these two media. homogeneous medium. Devices, wiring and a subclicuits all share the same space. With printed circuit cards, devices of all kinds are packaged outside of the wiring space such that the device or the subcircuit makes

for area on the interconnection medium. 2) The no demand subcircuits and devices of a silicon chip have various input and output connections. The physical position of these "pins" need not be fixed but can be moved 07 as required by the designer. The layout of a printed board is restricted in that the devices to be interconnected have a **Bubcircuits** (components) standard pinout that cannot be changed at the whim of layout designer or layout program. This ability of a chip designer to optimize the pinout of various devices cells is not always utilized in order that the cells be standardized in the same way as SSI/MSI parts have been standardized for printed circuit cards.

This paper is restricted to consideration of the design of scale integrated circuits built using the NMOS large process. Even within this area a variety of design styles standard cell and true custom Gate array, methodologies have been used to design NMOS circuits. model predicting the wirability of various sizes and types of gate arrays has been developed by Heller[i] and has been used successfully to predict the wiring space requirements achievable gate density of several master designs. It is only by the collection of data from a number high quality IC designs that such models can developed or verified.

In addition to the design methods above, a regularized style which integrates the circuit topology and layout with the intended function of the design has been put forth by Mead and Conway [2]. This style is characterized by a hierarchy of circuit blocks which are defined by the designer in a top down manner but with close regard for the

physical and electrical constraints to be encountered low levels of the design. The architectures machines are planned with data and control path topologies will layout and fit together in a regular manner when implemented in mask geometries. What would otherwise be logic is performed by PLA's and ROM's. Extensive use is made of "pass" transistors as steering logic dynamic circuits are frequently utilized. The resulting designs are built using a small number of basic designs which are placed regularly about the IC with little or no "random" interconnections. In power consumption, area requirements, logic function and particularly in ease techniques offer of design, these advantages traditional design styles.

# 1.2 Data Collection for Wiring Analysis

is important that wiring models be extended (or new ones created) to include this type o f design. investigations by Heller131 indicate that the wiring models used for master slice designs do not predict the IC such regularized designs. The collected from development of these models and those for future design techniques require massive amounts of data to be collected and evaluated using real IC designs. This thesis presents automatic means of analyzing the mask geometry of integrated circuit designs to provide various measurements indicating the utilization of the chip by devices, interconnecting wires and subcircuits.

The data to be collected most preserve the hierarchy and partitioning specified by the designer. Otherwise, the

analysis will be limited to the lowest hierarchial level, that of transistors. More interesting though, is the wiring and space requirements of higher level functions, such as, registers, ALU's, PLA's, et cetera. If experience can be gained with a large number of designs, the data taken concerning these common functions can make possible predictions of the areas required by them in future designs. This knowledge, if used in planning could result in fewer subsequent layout iterations and an early, accurate prediction of overall die To size. preserve the designer's structure in the analysis of the design, the geometry specification expressed CIF (Caltech Intermediate Form) is used as the input to the analysis program. CIF is defined in Mead and Conway Central to the choice of CIF is it's ability to define geometry symbols in terms of basic shapes and subsymbols. Also, it is hoped that CIF will become a standard means of specifying IC geometry allowing a wider range of designs to be analyzed.

Before going further, a philosophical question must be answered. Why analyze the wiring of integrated circuit designs? Why not just build them and be done with Analyses of all kinds serve to aid in the development of predictive models in the hope that these can bе to reduce future costs and errors. The subsequently used fact that project managers are not satisfied with accuracy of size and cost estimates (designs always overrun initial estimates) and the fact that good placement routing procedures do not exist for the truly custom layout of IC's, point out that the existing models for the wiring of custom IC's are not acceptable. However, the advent of the silicon compiler and other very fast automated design

generators could remove the need for size estimates and some of the traditional design tools. An IC design program know as Bristle Blocks has been developed by Johannsen[4] which can automatically assemble, layout and specify geometry for a large class of finite state machines in a matter of weeks. Such systems can remove the need for predictive tools if they are able to complete the real design in such a short time.

It is clear that for master slice designs wiring space prediction must be accurate since one master slice image must accomodate a large number of logic designs (part numbers). If the amount of space made available for wiring is inappropriate, either poor utilization of the devices on the die will result or the die will be larger than necessary. In both cases a higher cost will be paid to produce a given function. True custom designs have a different economy. Since each part need not be larger than necessary, the manufacturing cost is determined by the die size (and other factors not related to its wiring).

Why then, do we need these analysis tools and models in True custom IC design requires the mapping custom design? of a hierarchy of successively refined circuits onto planar space of the chip. If this is done automatically, each node of the tree requires the mapping of subclircuits and devices be placed and then interconnected. Since the subcircuits must be mapped (implemented silicon) prior to their use in higher level circuits, this operation is recursive and continues to fall through hierarchy until circults built soley with primitive elements (transistors) are encountered. These circuits are placed and routed and the operation moves one level up the

tree, repeating the operation until the entire design implemented. At each node in the tree decisions must be made which place the devices and subcircuits in a relationship with each other which will result in a minimum amount of area used for wiring and an aspect ratio and pinout which are suitable for instances of the circuit in higher level functions. To make these decisions there must be some model that can be used to allocate a near optimal amount of space about the devices and subcircuits to used for interconnections. The model would have available as input the size and number of devices, the size and pinout of each subcircuit. To build and evaluate such a model, the analysis proposed here must extract, for each design hierarchy, the size and number of the node in the the size and number of. pins (input/output devices. connections) of each subcircuit and the area utilized in the design to interconnect the objects.

purpose behind the study of wirability is its use Another measurement tool. Companies and individuals as a frequently must make decisions which select one fabrication process out of several or one design aid over another. intelligent decisions some type of data is required from the candidates which embodies experiences with process or design aid. Usually people rely on intuition or "aut reaction" for such data because good measures with to compare the alternatives are not available. extraction of simplistic measures such as the number of devices per unit area can be of importance since this is a good indication of how efficient the interconnection ο₽ the process are or how effective the structures placement and routing algorithms of a CAD package are. A11 area and distance measures should be in some type of

process independent unit to allow separation of wiring data from process and lithography, the lambda unit used by MeadI21 is suitable for this purpose. If, for example, it is necessary to decide between a master slice approach and a polycell style, such measures as the percentage of area used for wiring (outside the cells or book functions) are an accurate measure of how well each utilizes the chip. The data can be collected from several designs, even if they differ in design rules. The data is made comparable by expressing dimensions in lambda and/or percentages. Such data, if available to management, can make easier the long range planning of a company's technology path and make its success more probable.

#### 1.3 Overview

It is the purpose of this thesis to show how wiring data may be extracted automatically from the CIF specification of an NMOS chip. The operations involved are based on a set of polygon manipulations and are applied hierarchially to the elements of the design. There are two approaches to the gathering of this information.

The first approach is heuristic and interprets the mask data correctly in the vast majority of cases. The exception cases will not affect the outcome and resulting statistics that are accumulated in any significant way. The heuristic method is straightforward and requires less processing than more exact methods. The data taken from IC designs is of little use in any absolute sense but is very useful when compared with data taken from other chips. Thus, it is more important that the data be extracted by a

standard method than that the method be absolutely precise in its calculations.

mecond method is precise and much more extensive in complexity and processing time than the first. However, to justify itself it produces a reconstruction of the circuit topology as determined by the masks. process information can be compared with the original specification of the chip topology made by the designer to verify chip has be implemented faithfully. The actual comparison is beyond the scope of this paper. The extraction of topology is an operation currently performed in design automation systems. However, if in this process, program accounts for the silicon resources used in building various circuit the structures (transistors, interconnection wires, subcircuits), the data required by the wiring model can be accumulated.

Both methods are presented and explained, as well as, the polygon operations on which they are based. Some demonstration of their operation is also given using small circuits. The topology extraction requires computation than the heuristic method. Insufficient test were made with both to precisely determine performance difference between them. However, it can be safely said that the heuristic methods improve run times by least a factor of three and probably more for large designs.

The programs were written entirely in SIMULA and the important sections of code are listed in the text and in the appendices. The SIMULA language provides a very good environment for writing such algorithms but incurs an

overhead that makes the execution of large polygon operations slower than it would otherwise be. In addition, the garbage collection system contains an error preventing large, long programs from running to completion. This problem has prevented the use of test cases of all but a small size. The problems on which the program has executed demonstrate that such data can be extracted from IC mask data automatically.

# Chapter II

# Definition of Wiring Statistics

## 2.1 Data Collection Requirements

Several types of data should be collected from IC designs. To be useful for the purposes described an analysis program must recognize various device and interconnection structures in the shapes appearing in the masks. This chapter selects what objects are to be recognized by the program and what computations are to be made using these objects.

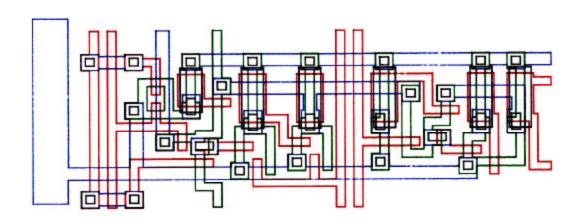

The figures describing NMOS geometry in this paper utilize a standard set of colors to the different process masks involved. Blue represents aluminum, red represents polysilicon, green represents diffusion and black represents contact cuts. Black is also used here to indicate ion implantation.

To satisfy the requirements of wiring model verification or development, several features of the design must be extracted. As stated previously, the hierarchy of the design is to be preserved in the data extracted, such that those objects which belong to higher level structures are separated from those which are particular to the portion of the design at hand.

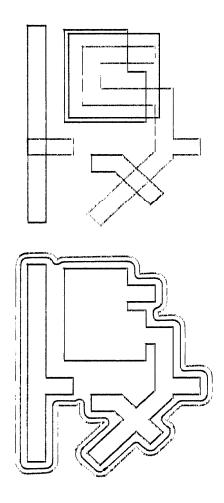

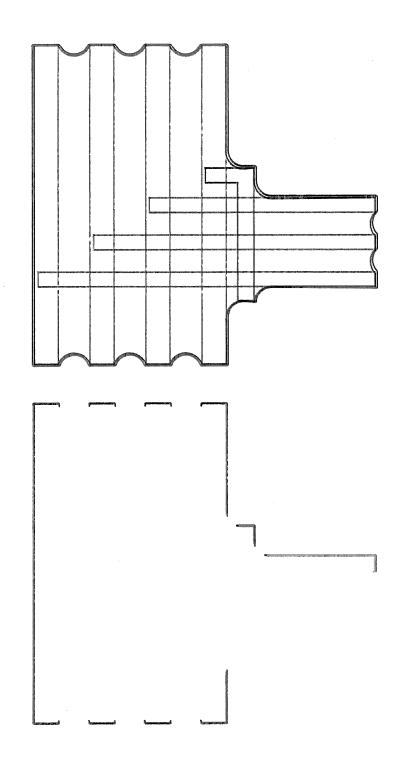

FIGURE 2.1 LAYOUT OF A COMPLEX GATE

FIGURE 2.2 LAYOUT OF A SUPER BUFFER

FIGURE 2.1 LAYOUT OF A COMPLEX GATE

FIGURE 2.2 LAYOUT OF A SUPER BUFFER

data is to be extracted from mask The wiring described by CIF 2.0. The design hierarchy is expressed α tree of symbol definitions. Each definition may consist of constructions of boxes, wires (tracks), simple polygons and instances of subsymbols. Recursion is not allowed, however, the depth of definitions is not restricted. A complete definition of CIF 2.0 is found in Mead and Conway [2]. The memanticm of CIF do not restrict the manner in which the designer specifies the IC. The wide range of variation possible within the bounds of CIF is a major cause of complexity in the extraction of wiring data. Presently, there does not seem to be a reasonable set of restrictions that would be acceptable to the users of CIF desired that the program be operable on a wide range of Thus, to be useful, the recognition of objects designs. the extraction data must be as general as possible and perform properly regardless of the designer's CIF style.

For each symbol In the hierarchy one fundamental distinction can be made. Devices can be distinguished from interconnection. This ĺВ not an obvious easy classification of the geometrical shapes. Devices can include subsymbols and these are identified by the syntax of CIF. The remaining devices are transistors of theme, some may not have been required by the Of types. designer to perform the function of the chip. They may be only as a less than optimum interconnection. Figure 2.1 illustrates a complex gate of a type which could find where both the active high and active low senses of its input terms are available. In a case like this seen that some of the transistors are not being used as such but as a connection from one side of a polysilicon

wire to another without requiring use of the metal layer. In addition, the use of NMOS transistors as capacitors for bootstrapping or charge storage purposes must not be confused with wiring structures.

Once device structures are separated from interconnection structures, further operations are necessary to winnow wiring that belongs essentially to structures higher in the hierarchy than the one being studied. Such wires are those that make a demand on the area of the symbol but serve to interconnect objects not part of the current symbol. portions of the wires in a symbol are termed global and those which exist to interconnect parts of the current symbol local. This is not a clear distinction since wires may pass through a symbol in order to connect external objects but may also connect to internal devices at one or more points. It seems reasonable to expect that portion of such wires may be considered local and the remaining portion global.

Once these objects are separated from each other, it is a simple matter to compute their area. However, the total area of the symbol is not well defined especially if it does not fully utilize the three important interconnection layers (poly, diffusion and metal). To correctly account for unequal use of the layers, the area of the symbol must represented as the sum of the area it requires on each of these three layers. The various objects can then be expressed as a percentage of the symbol's total area. Also, interconnection area should be expressed length by dividing its total area by the center to center distance between wires (usually the minimum width minimum spacing). The area computations provide the

measures of how efficiently the circuit was implemented and for high quality designs, represent a characteristic of the particular type of function that has been implemented.

Ιt may also be necessary to determine the number o.f components making up the circuit (devices and subsymbols) the average number o f terminals (input/output This connections) made to these components. information that would normally be used in an a priori prediction of the necessary wiring space of the circuit. clear example of its use would be in the estimation of the Rent exponent (Landman and Russo [5]) for LSI circuits. design systems make available the structural topological data describing a design from the parameters of the Rent equation can be extracted more easily than from the mask geometry. However, as part of topological data extraction, the connections between verification with the components must be determined for original design.

The three basic elements that must be identified to provide wirability data are: 1) the area occupied by devices (transistors); 2) the area occupied by interconnection wires and 3) the area occupied by global interconnection wires that are present in the definition of To give meaning to these numbers, the area of the entire symbol must be determined. An important measure be derived by subtraction of the foregoing from the total area of the symbol giving the unused or wasted area Once the topology of the symbol is known, the design. finer measures can be formulated, such as, occupied by power distribution structures. Most statistics can be expressed on a per layer basis giving some insight

into the manner in which different layers are utilized.

It should be noted that although these quantities are to be generated on a per symbol basis, there is the opportunity for any degree of instantiation of the symbol hierarchy in order to accumulate statistics for the entire design or any portion of it at the transistor level.

### 2.2 Definition of a Device

It is necessary that a standard be set that makes clear what is meant by a device. In some sense, all structures of an integrated circult design are devices. extent, even what are meant to be wires act as series resistors and capacitances to the substrate. The primary distinction between such parasitics and a depletion load, for example, is the intent of the designer. devices can be defined as those structures which act as active or passive circuit elements and were both placed and the designer. Anything else must provide desired by isolation between devices or connections between devices, the latter being wires in the ideal sense.

What is now needed is a more workable definition of a device which can approximate the intent of the designer. With few exceptions, NMOS devices must involve a polysilicon structure placed physically above a diffused area. Exceptions take the form of diffusion wires used as resistors, such as in the resistor ladder of an analog to digital converter. Every occurrence of polysilicon above diffusion is not a transistor. An example is a butting or buried contact, both have coincident poly and diffusion but

both are used as a portion of an interconnection. instances of poly and diffusion together may actually form a transistor but could be used as a wire (the implanted gate inputs of Figure 2.1) or could be used as a capacitor, which is another variation of a device. If the designer draws a device, there must be an intention to cause a mignificant interaction between the gate of the device and its drain and source. Once apparent devices which contacts are eliminated, this definition can serve t o in fact, separate the remaining structures which are, transistors but are not intended to be used as such by the designer. This does not eliminate capacitors, which though they are not used as transistors, there is nevertheless a significant interaction between their gate and drain/source connections making them devices.

This definition is difficult to apply in practice since it determination of what is "significant" requires BOME the gate and channel region. interaction between the confusion possible is a comparison between example of the implanted input transistors of Figure 2.1 and a second stage pullup of a super buffer as shown in Figure 2.2. other than a device, first has been defined to be second is definitely a device yet both appear geometrically the same, Resolution of problems such as this requires some analysis of the topology of the circuit to second guess the intention of the designer. Since such analyses are generally not deterministic, it may be preferable to apply some simplification to solve the problem. expected that the contributions made in error methods will be insignificant.

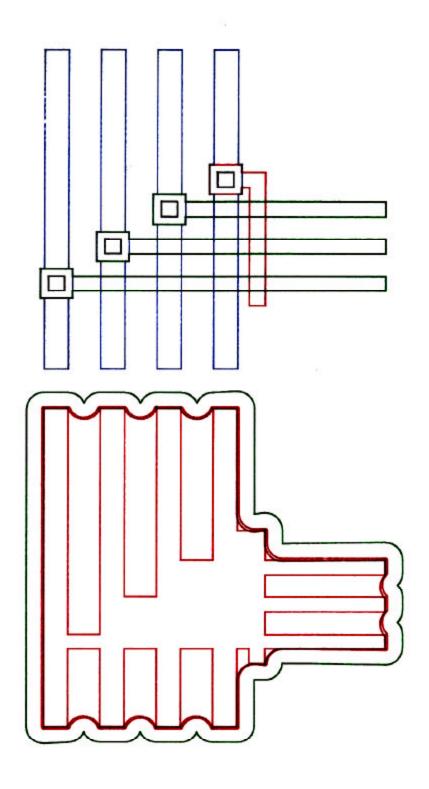

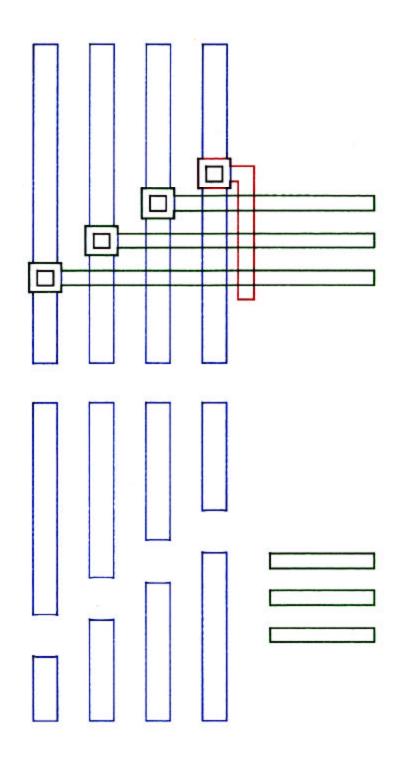

FIGURE 2.3

LAYOUT ILLUSTRATING GLOBAL and

LOCAL WIRE

FIGURE 2.3

LAYOUT ILLUSTRATING GLOBAL and

LOCAL WIRE

#### 2.3 Global versus Local Wire

One of the most difficult operations is that of separating local wiring structures from global ones. This results in part from the lack of a clear definition distinguishing the two. The attempt is made here to adequately define the differences between local wire and global wire.

To some extent, every connection by a symbol to objects external to itself involves the use of some global wire. It is possible that a particular wire in a symbol may only connect external objects. The other extreme is the wire which connects only internal objects and must surely be considered a local wire. Figure 2.3 shows a typical low level symbol which embodies wires some of which are clearly global or local and several which are not clearly either. The wires which run vertically from top to bottom clearly place a demand on the area of the cell in order to connect the next higher cell to the next lower one. This would indicate at least some portion of these wires must be considered global.

Any rule applied here to separate the global part from the local part will be arbitrary, depending on exactly what information one expects to derive from the data. It is important that some standard rule exist so that the information derived from different IC's will be comparable.

A definition has been chosen with some intuitive basis and partially due to its simplicity. Also, this definition has already been used by Heller[3] in the manual extraction of wiring data. It is desirable that the data extracted

automatically be computed on a similar basis with that previously collected by hand.

The definition defines global wire to be that portion which makes contact with an external object up to but not including any contact made to objects within the symbol. Thus wires which make no internal connection are determined to be entirely global and those which make no external connection whatsoever are defined as local wire. For simplicity, contacts with other mask layers are considered to be internal connections. This last qualification causes some confusion with wires that traverse several layers in making external connections. Parts of these, by this rule, are considered local wire.

As with the definition of devices, these rules do not always perform properly in practice, nor are they simple to implement. However, it is more important that a standard method be set for separating global and local wire than that the absolute numbers extracted be perfect. Therefore, simplifications will again be used where they are expedient to avoid expensive processing to handle exceptional circumstances.

## 2.4 Wiring Statistics

Once devices are recognized and remaining interconnection structures separated into global and local wire, several useful figures can be computed. For each CIF symbol, a wiring analysis program should compute the following for each layer and for the symbol as a whole:

- i) area of the symbol (square lambda)

- 2) area and percent of (1) occupied by devices

- 3) area and percent of (1) occupied by subsymbols

- 4) area and percent of (1) occupied by connections

- a) area and percent area occupied by local wire

- b) area and percent area occupied by global wire

- c) (a) as a percentage of (4)d) (b) as a percentage of (4)

- 5) unused area

These quantities can be used to characterize part or all of an IC design and permit the development of wiring models for all types of NMDS LSI designs.

### Chapter III

# Description of Polygon Manipulations

# 3.1 Polygon Requirements

Discerning structures in the geometry of the masks of an integrated circuit requires the ability to manipulate two dimensional geometric shapes. In some cases, these shapes can be restricted to rectangles, or to orthogonal shapes, to orthogonal shapes including 45 degree lines, etc. restrictions can be made, simplifications usually result the programming of operations on them. It may always be expected that at some point exceptions will have to be made and the restrictions dropped. The authors of automated design aids have never been long successful at limiting the use of a technology by legislating rules beyond those required by physical processes. It is for these the wiring analysis program must be capable of performing its function on arbitrary IC designs. accomplish this it must be capable of performing operations on general two dimensional shapes.

The shapes commonly found in integrated circuit design are rectangles and wires (or tracks). Wires, as used here, indicate some path and an associated width. Polygons represented as a sequence of points enclosing an area may also be found. It is not unusual to encounter wires and polygons whose boundaries are non-orthogonal. At the

present time, the machines which produce integrated circult masks do so using rectangular apertures. It is possible that circular apertures could be used in the same way as Gerber photoplotters are used to make printed circuit of. artwork, avoiding SOME the processing problems associated with sharp corners. Complex shapes, such as diffusion area of Figure 2.1, are specified using some set In this way shapes with holes of the shapes above, themselves be generated on the masks. In the may manipulation of such shapes, it may be necessary to the entire enclosed area (with or without holes) as one entity. This leads to the concept of a general polygon as a collection of one or more sheets, where each sheet is a sequence of edges which enclose Sheets must some area. have a sense which indicates whether they are holes or The edges of the sheets should be either substance. straight lines or circular arcs to accomodate certain polygon manipulations which may produce nonlinear results.

The operations required upon polygons include the set of common logical operations but more significantly the ability to inflate or deflate shapes. Most of these same capabilities are central to design rule checking. Design verification requires many of these functions and may well be included as part of the same program.

The definition of polygons having multiple sheets and both curved and straight edges provides consistency among the operations. The various logical operations may result in single sheets being fragmented, however, the collection of fragments is also a single polygon. Inflation (bloating to some) and deflation, if thought of as the locus of points a particular distance within or beyond the original boundary,

will generate circular arcs at the vertices of the edges. Again, this definition of a polygon permits such nonlinear edges.

A description of the algorithms and techniques required to implement a polygon package of this type is found A package has been implemented in SIMULA Sutherland [6]. in the referenced by Sutherland and is also described package goes as far as implementing all the The attributes of edges, sheets and polygons including the o f polygons, inflation (negative intersection positive), and the retracing of the sheets of a polygon. permits the edges of a polygon to be intersected and the intersection points inserted into the sheets. sheets of the polygon may then be retraced such that the edges of sheets do not cross edges of themselves or sheets and are, at most, coincident with other edges. Edges are directed and thus have a right and left side from of view of someone traversing the edge in its defined direction. By convention, the substance of a sheet is the left of its edges, thus sheets which are always to outlined clockwise are holes, those This polygon package counterclockwise enclose substance. works and has been used in the first implementation of a wiring analysis program.

The abilities provided by the polygon package as it stands are insufficient for use by the wiring analysis. The package lacks the means to build polygons of the type described from CIF text. Also, the basic logical operations, such as intersection, union and difference must be constructed from the attributes of the package. A SIMULA skeleton of the desired operations and structure

(from a user's point of view) of a polygon package suitable for wiring analysis, topology extraction and design rule checking is listed in Appendix I. The listing is commented to explain the function of the items shown. The polygon package of Sutherland [6] has been extended to provide these functions. Appendix V lists the Simula code required to make the extensions. In addition, procedures have been written to build a database file from the CIF specification and make the data available to the polygon package such that polygon objects can be built from the CIF through a database file.

The purpose of the database file is to permit the execution of the analysis on a substantial amount of data without the need for data to occupy more than a small amount of the of the computer (DEC PDP-20). The addressing space database manipulation programs were authored by Ullner [7] and provide relational abilities, as well as, random access to disk files. Appendix IV is a listing of a program which reads CIF files and builds a database file. The definition of the database relations and tuples is not general insofar the storage of mask geometry. as it is suited only to CIF However, it satisfies the needs of representing The program (called CIFX) makes standard CIF parser written by Tarolli and Rowson (8). CIFX allows options to be set which control whether or not all geometric shapes are converted to simple polygons of type understood by CIF. The analysis program requires that roundflashes) all CIF objects (boxes, wires and translated to CIF polygons (represented by a sequence of points). CIFX is able to translate a CIF 2.0 file database at a rate of about 10 lines of CIF per CPU second on a DEC-20.

## 3.2 Logical Operations

Given the general type of polygons described above, a small set of operations on them is all that is required to fill the needs of the wiring analysis program. A complete list of these operations and descriptions of their function is in Appendix I. Beginning with the Sutherland [6] polygon package, some additional procedures are required in order to do logical operations on polygons.

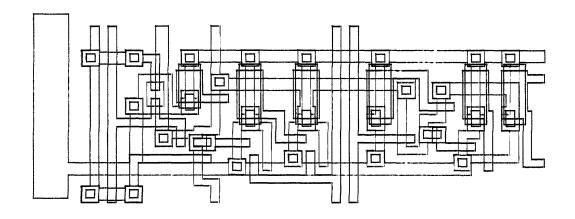

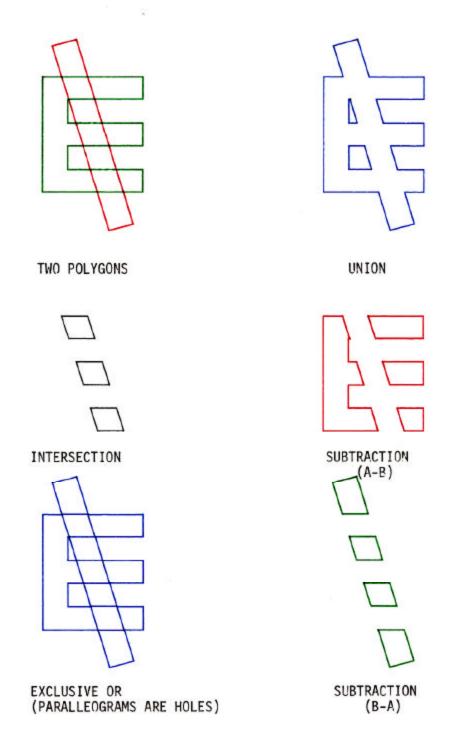

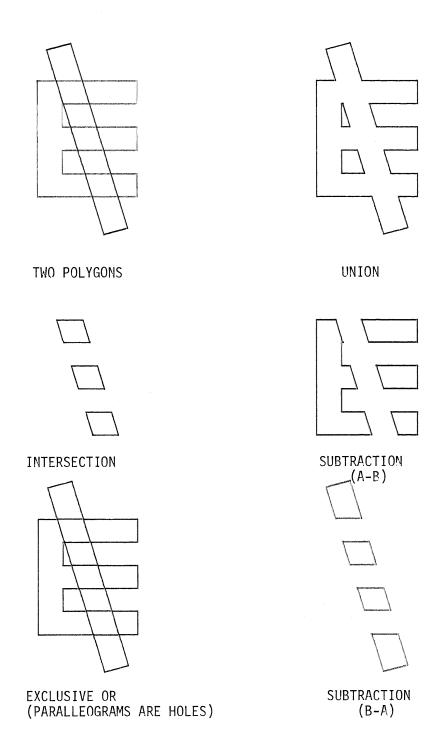

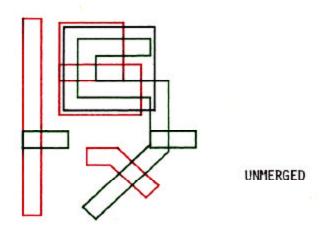

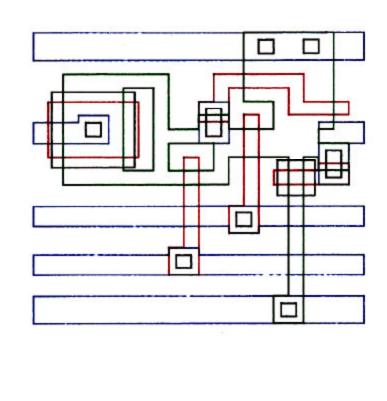

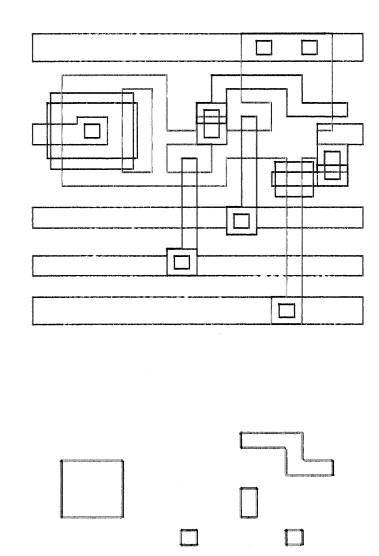

two polygons (each with any number of sheets) are to be intersected or unioned, they may be combined into a single polygon containing all the sheets of each. The resulting polygon may then be selfintersected and its sheets The areas bounded by the sheets of the polygon may be said to be wrapped by the polygon. The wrap of a point in the plane is the number of times a cursor would travel fully around the point in a counterclockwise direction as it traced out the edges of each sheet in their defined direction. The wrap number is more fully discussed Sutherland [9]. The combination of two polygons which are originally well formed each having no selfintersections will combine to enclose their original areas with a wrap number of 1. In areas where sheets of one polygon overlay sheets of another, areas will be enclosed with a wrap number of 2. This is illustrated in Figure 3.1. is combined with the green "E" to form a single multi-sheet polygon. The polygon is selfintersected and its sheets In the second part of Flaure 3.1 the new set sheets is shown with black used to trace the sheets Which separate an area of wrap number 1 from an area of 0. Blue

FIGURE 3.1

SELFINTERSECTION AND RETRACING OF POLYGONS

TRIMMED

SELFINTERSECTED

FIGURE 3.1

SELFINTERSECTION AND RETRACING OF POLYGONS

is used to trace those sheets which separate 2 from i. This serves to illustrate both the retracing of sheets and the concept used in trimming sheets from a polygon in the generation of logical operations.

The trimming routine must compute the wrap number of points inside the sheet and the wrap number of those outside with respect to the entire polycon. Two points selected, one inside and one outside of each sheet. mot possible, given any particular edge to compute location of two points and be sure they will be in the desired relationship to the sheet. The operation proceeds by selecting an edge, computing the location of two points that will probably straddle the boundary of the sheet their wrap numbers. If the points are computing opposite sides of the sheet boundary then the wrap numbers If they do not differ, then both points are either inside or outside the sheet. If this case edge is selected and a new pair of points is found. If the wrap numbers of the points differ by more than then the points are on opposite sides of the boundaries of This is usually the result than one sheet. multi-traced edges occurring where one sheet has coincident edges with another.

The trimming procedure takes a single integer argument which is used to determine which sheets are to be extracted from the polygon. Where the intersection of two polygons is desired, all those sheets which separate area of wrap number 2 from area of wrap number 1 are part of the intersection. Other sheets may be removed. Selection the sheets to be removed requires the trimming procedure to find two points for each sheet whose wrap numbers differ by

exactly one. Points whose wrap numbers differ by more than one give no indication of which of the two or more sheets involved should be removed. This algorithm breaks down when two sheets exactly overlay each other, having edges coincident. However, it does permit the operations of intersection and union to be performed. For intersection, all those sheets which do not separate areas of wrap number 2 from area of wrap number 1 are removed. For those not separating areas of wrap number 1 from wrap Operations with more than number 0 are removed. operands, such as the intersection of three polygons, can be constructed by looking for sheets bounding areas of higher wrap number.

To make possible arbitrary logical operations on polygons, a negation operator must be available. This function must be able to reverse the sense of all sheets of a such that all substance becomes holes and all holes become Where sheets enclose other substance. sheets, description is not complete. However, the operation of negation is merely the reversing of the order of all and vertices of each sheet and reversing the edges direction of each edge. Using negation the operations of "exclusive or" and subtraction may be constructed as well as any other logical operations.

Figure 3.2 shows examples of common logical operations performed on the polygons of Figure 3.1. Intersection, union, exclusive or and subtraction are shown. Unfortunately the direction of the edges of the sheets is not visible in such drawings.

FIGURE 3.2

LOGICAL OPERATIONS USING POLYGONS

FIGURE 3.2

LOGICAL OPERATIONS USING POLYGONS

#### 3.3 Inflation and Deflation

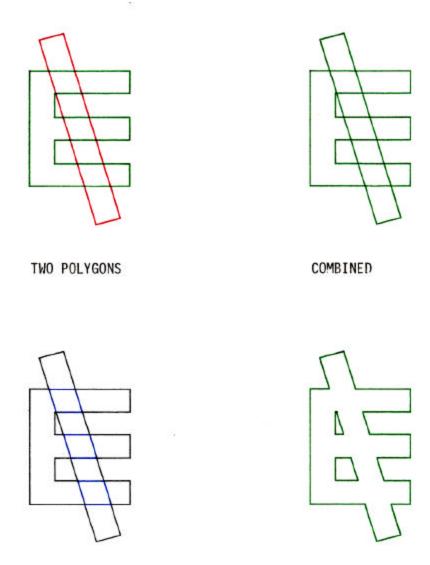

The recognition of devices and other applications such as design rule checking require that polygons be shrinkable and expandable. To be consistent, a polygon which is expanded by a particular size and subsequently shrunk by the same amount should reconstruct the original polygon. This and the desire to avoid the detection of false design rule errors brought about by corner to corner proximity of polygons lead one to the use of circular arcs as edges in general polygons. The algorithms and conventions used in the manipulation of circular arcs is given in Sutherland [10].

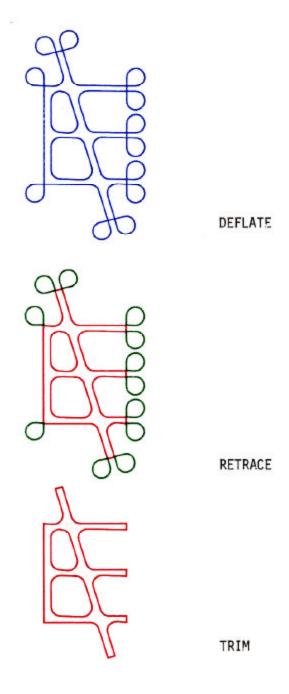

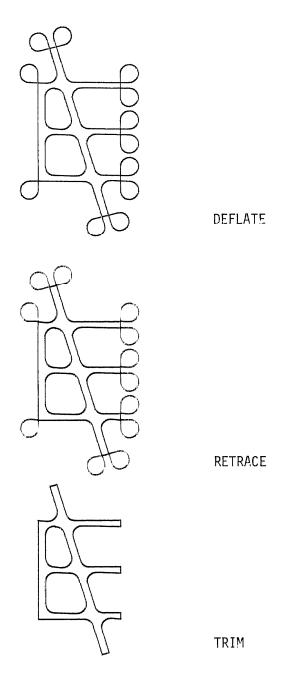

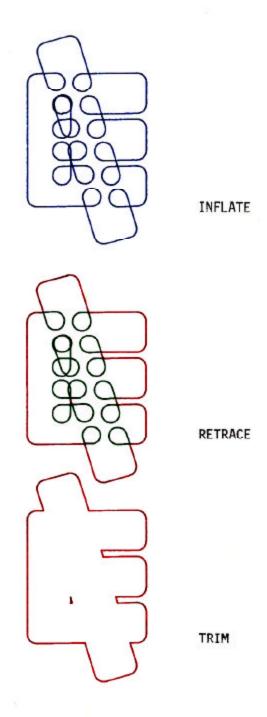

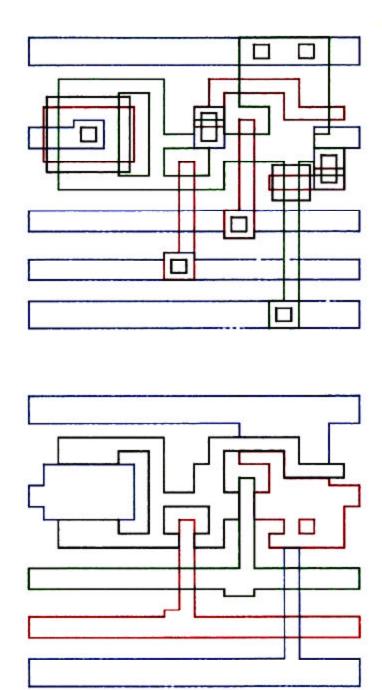

It is evident that the expansion of a sheet with convex corners will result in a new sheet having arcs about the corners of the original sheet. The arcs are the locus of points a fixed distance from the vertices of the sheet. Inside corners or concavities in a sheet cause "curlicues" to be generated upon expansion. These portions of the new sheet cause some areas of the sheet to become doubly The shrinking of polygons has the opposite effect at sharp corners. Convex corners beget curlicues outside the sheet wrapping areas negatively. substance of concave corners shrink to circular arcs (fillets). 3.4 illustrate the result of inflation and 3.3 and Since the curlicues represent doubly wrapped deflation. holes in free space and are redundant, they must be removed before logical operations can be performed on If left as is, the trimming procedure will not be able to distinguish intersecting areas from redundancies due to inflation or deflation.

FIGURE 3.3

DEFLATION OF POLYGONS

FIGURE 3.3

DEFLATION OF POLYGONS

If the inflated sheets are selfintersected and retraced, the trimming procedure can be used to extract the redundant sheets before applying logical operations. The successive frames in Figures 3.3 and 3.4 illustrate this process. Positive sheets that are smaller than the amount of shrinkage applied will be shrunk into holes in free space and eliminated. Sheets representing holes will similarly disappear if expanded by more than their size.

The property of these polygons which causes them to reverse if shrunk sufficiently is very useful in the separation of different silicon structures from each other. It also provides a method by which the width and length of transistors may be determined, this is discussed fully in Chapter V.

#### 3.4 Selection of Sheets

Two other functions, which do not fall in the category of logical operations, are necessary to topology extraction. These functions conditionally extract sheets from a polygon where a given sheet either encloses some particular point or where the sheet overlaps or encloses some part of another polygon. The trimming procedure described above falls into this category.

To enable a program to find those sheets of a given layer that make contact with other layers through cuts in the oxide, a procedure must be available which can test a sheet for overlap with another sheet (a contact cut) and conditionally remove the sheet intact from its polygon for

in other operations. Such a procedure may be able to accomplish this function without the expense of fully intersecting one polygon with another. Processing can be reduced if only the fact of intersection need be known the precise geometry of it. This is obviously the case if sheets are to be selected on the basis of whether or nnt they enclose a particular point. The wrap number of the point with respect to the individual sheets must computed but no more. Those sheets which yield a wrap number about the point which is non-zero are selected. detection o f overlap between two polygons for the extraction of certain sheets or for design rule can be simplified over general intersection. This problem is discussed by Sutherland and Sproull [10]. T.f interested in detecting the overlap of polygons which must always enclose another set of polygons, then the problem that of. computing wrap numbers. reduces to mimplification can be applied to the melection of sheets which overlap a polygon of contact cuts provided that it is assured that design rules have been met.

### 3.5 Other Operations

Several other operations are necessary in the manipulation of polygons and the computation of wiring statistics.

The computation of the quantities outlined in Chapter II obviously require that the area of a polygon be known. The area of a polygon is a signed quantity where sheets representing holes contribute negatively to the total area of a polygon.

FIGURE 3.4

INFLATION OF POLYGONS

FIGURE 3.4

INFLATION OF POLYGONS

It will be found the computation of the width and length of transistors in Chapter V also requires a procedure for obtaining the perimeter of a polygon. For multi-sheet polygons, the perimeter is the sum of the length of all the edges in all the sheets. If this method is used, redundant sheets as described above will also contribute to the perimeter if present.

the Two routines are necessary 10 avordmi overall efficiency of the program. Successive operations upon polygons can cause unnecessary vertices and edges to generated and made part of the sheets of the polygon. example of this is two sequential collinear edges separated a vertex. One edge would do. A procedure is needed to clean the sheets and eliminate such excesses. Also, program will require less memory and computation time if operations used on polygons are permitted cannibalize the data structures of the operands in generating their result. If this is be the to simple procedure is required which returns an independent copy of a polygon to be used to preserve the operands when necessary.

The symbol call of CIF allows the user to specify that the symbol being called be translated, rotated or mirrored when instantiating it in the symbol in which the call command appears. This operation is known as a transformation and can be thought of the multiplication of a 3 by 3 matrix with every point of the object to be transformed. A full discussion of these operations can be found in Newman and Sproull [12]. Any of the transformations possible in CIF (and a few more besides) can be represented by a 3 by 3 matrix where three of the elements are fixed values which

never change (requiring only six values to be stored). Transformations of transformations ad infinitum can be represented by one matrix which is the multiplication of all the individual matrices (in the proper order). When polygons, representing symbols, are to be instantiated in another symbol, a transforming procedure must be available to apply the transformation to the polygon.

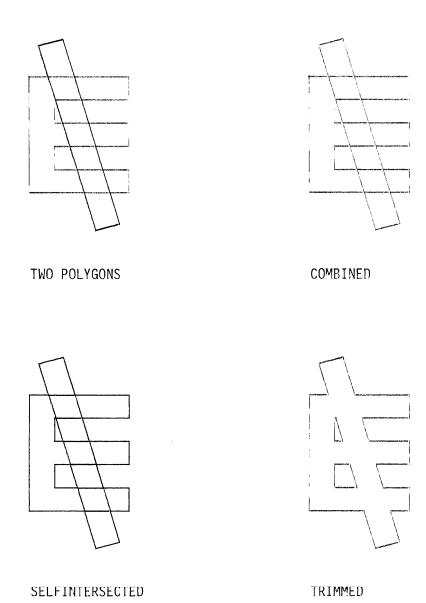

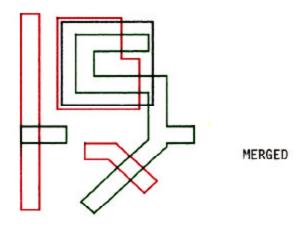

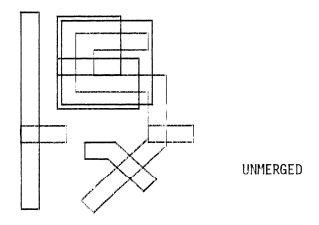

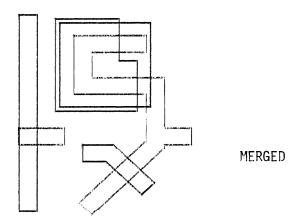

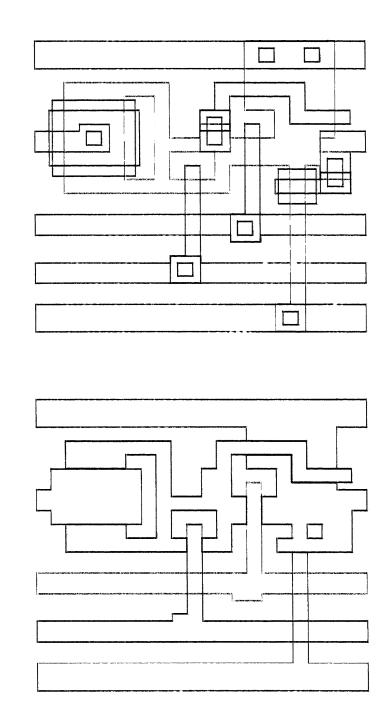

Even after CIF objects are converted to CIF polygons and the CIF polygons are used to produce the more general sheets of polygons described in this chapter, the resulting objects are not suitable for wiring analysis. The wiring analysis program treats each layer of each symbol as one entity, rather than a collection of simple shapes. This necessary since if the abutting shapes making up a wire connection on the metal layer are individually shrunk, they draw apart and cease to make a connection. The shapes of each layer must be coalesced into the complete shapes would see on the finished masks before they can be manipulated, Figure 3.5 shows both the CIF specification of a symbol and the form it must take in the polygon package. Each layer must be freed of redundant overlaps and collapsed into the largest sheets possible before logical operations can be applied. This means only that all shapes of each layer must be "ORed" with each other and the doubly wrapped areas trimmed off. In effect, each layer is then represented by one polygon containing the minimum set of sheets and edges required to outline the areas specified in the CIF file for that layer.

All the procedures and capabilities discussed in this chapter are listed in Appendix I and have been implemented in the original polygon package (Sutherland [6]) or in the

first version of the wiring analysis program. In addition, procedures for printing and plotting the polygons are available along with debugging aids. The attributes and capabilities of this polygon package, though general, execute at speeds and with memory requirements which make it unsuitable for large problems. It is hoped that the efficiency and algorithms involved can be improved to increase the useability of these functions.

FIGURE 3.5

MERGING OF SYMBOL WIRES and

BOXES INTO POLYGONS

FIGURE 3.5

MERGING OF SYMBOL WIRES and

BOXES INTO POLYGONS

### Chapter IV

## Heuristic Computation of Wiring Statistics

## 4.1 Recognition of Structures by Heuristic Methods

is possible, though not precise, to extract wiring analysis data from geometry without the need to examine topology of the circuit. The usages of NMOS for digital purposes have enough in common to permit a small number of rules to be used in the recognition of devices and wires. The application of the rules does not guarantee the results The obvious benefit of such a to be always correct. method, in spite of its inability to correctly interpret situations, 1 3 it# lower COST simplifications used must be accurate enough to prevent errors from causing significant deviations in the results.

The goal of this method is to compute the required wiring statistics using only polygon manipulations. Picture recognition of this type depends on experience with the structures to be detected in the generation of algorithms to do the job automatically. Unless care is taken, can result in the misinterpretation of structures encountered. 7 I important normally 1.55 the simplifications make as few assumptions about the design style as possible.

The succeeding sections of this chapter describe polygon n·f devices operations for the extraction interconnection and global wire from local. The detection of devices is much less difficult than the distinction between global and local wire. This is because devices must have some physical basis while the distinction between local wire is conceptual and has no necessary alobal and manifestation in the physical geometry o f However, it does have meaning to the designer and the need for wiring data requires that methods be available to Both operations, as described here, this distinction, mistake some types of structures for other in the analysis of the chip. The more frequent of these exceptional situations are explained in the last section.

### 4.2 Extraction of Devices

NMOS devices involve the interaction of polymilicon with diffusion. The operation of intersection used between these two layers results a polygon containing all devices. To eliminate the degenerate devices, potential such as, butting and buried contacts, the polygon shrunk by one half the minimum size of a transistor (1 lambda) plus some tolerance. All degenerate transistors will then become sheets with negative areas and can be The polygon can then be extracted from the polygon. expanded by the amount it was shrunk. It is then necessary to remove from the poly and diffusion layers, portions which make up the devices. To accomplish this the polygon representing the devices is expanded by one minimum spacing and subtracted from both the poly and diffusion layers. The sheets remaining in the

diffusion and metal layers then represent interconnection structures only. The segment of Simula code below shows how this is done using the objects and attributes of Appendix I. The syntax and semantics of Simula are defined in Birtwistle, et al [13] and Birtwistle [14].

```

! Temporaries to hold copies of polygons;

REF(polygon) temppoly, tempdiff, tempdev;

! Make copies of poly and diffusion layers;

temppoly:-symbola.layer(poly).copy;

tempdlff:-symbola.layer(dlffusion).copy;

! AND poly and diffusion layers,

I put into devices -- Then shrink them;

symbol.devices:-symbol.layer(poly)

.intersect(symbol.layer(diffusion));

symbol.devices.shrink(1.001);

! Test each sheet of the devices for negative area, ;

! If negative extract it;

FOR si-symbola.devices.nextsheet(s) WHILE s=/=NONE DO

BEGIN

IF s.area(0 THEN symbola.devices.extractsheet(s);

END:

! Inflate the remaining devices and make a copy of them;

symbola.devices.inflate(1.001+2.0);

tempdev:-symbola.devices.copy;

! Subtract them from the poly layer, make a new copy;

symbola.layer(poly):-temppoly.subtract(tempdev);

tempdev:-symbola.devices.copy;

! Subtract devices from the diffusion layer;

symbola.layer(diffusion):-tempdiff.subtract(tempdev);

```

The inflation of the devices two lambda beyond their original size is done to include the polysilicon that must overlap the diffusion. This is a simplification, since in the direction of current flow, there is no overlapping

poly. The intent is to account for the area occupied by depletion loads and the overlapping of the pulldown by polysilicon as well as possible. In the direction of current flow, transistors may be packed very close, with only the two lambda polysilicon spacing required between In some complex gates this situation may occur This type of design is usually, though not frequently. always, limited to enhancement pulldowns. In the direction orthogonal to current flow, transistors may be packed with three lambda between them (minimum diffusion spacing). However, this implies that the gates of such transistors must all be in common resulting in a circuit that would have a very rare usage. In practice, depletion loads would almost never be constructed in this way because to do so shorts inverter outputs together. Enhancement pulldowns built in this manner could concelvably be used to control several inverters, but the diffusion from which inverters would be built would not typically be next to each other.

These observations lead one to believe that MOS transistors may be placed two lambda apart if their source/drain connections in common configuration), are series (a However, the usual placement in the other direction lambda spacing. This is brought about by the requires six two lambda overlap required by each of the two transistors spacing required between their and the two lambda respective gates. To account precisely for this variable spacing would require that the channel direction of each transistor be known and the transistor "stretched" direction to account for the inequality. If the transistor is non-orthogonal, or of an unusual shape this can be difficult. However, experience with NMOS technology shows that these exception cases are rare and the vast majority of the transistors can be characterized with simple polygon manipulations. If the devices (the intersection of poly and diffusion minus the degenerate cases) are inflated two lambda beyond their normal size, depletion loads are reasonably accounted for. Enhancement devices may be placed closely in complex gate circuits but are small devices in comparison to the depletion loads and if they are over inflated a small amount of area may be accounted for twice by ajoining transistors. This can be removed by the following line of code.

# symbola.devices.selfintersect.retrace.trim(1);

This will remove any doubly wrapped areas of the devices. There are always inaccuracies encountered when experience or frequency data is used to simplify processes. Here it is possible to regard more area as that of devices, due to the overinflation of enhancement devices, than may actually be the case. The experience on which the recognition is based would suggest that this will be a small amount.

If additional processing is available, much of this inaccuracy can be eliminated with additional operations. Since usage of the pullup loads and the pulldowns are different and to a large extent are visibly different types of devices, they can be recognized without regard for the topology and treated differently. Enhancement transistors are rarely used as pullups and depletion transistors are rarely used as pulldowns. A large amount of the inaccuracy make be removed if the implantation layer is used to distinguish depletion from enhancement devices. The above code for separating the devices from the interconnect would

be modified to become the following:

```

PROCEDURE Getdevices(symbola); REF(symbol)symbola;

BEGIN

! Temporaries to hold copies of polygons;

REF(polygon) temppoly, tempdiff, tempddev, tempndev;

! Make copies of poly and diffusion layers;

temppoly: -symbola.layer(poly).copy;

tempdiff; -symbola, layer (diffusion), copy;

! AND poly and diffusion layers, ;

! put into devices -- Then shrink them;

symbol.ndevices:-symbol.layer(poly)

.intersect(symbol.layer(diffusion));

symbol.ndevices.shrink(1.001);

! Test each sheet of the devices for negative area;

FOR si-symbola.ndevices.nextsheet(s)

WHILE S=/=NONE DO

BEGIN

IF s.area(0 THEN

symbola.ndevices.extractsheet(s);

END:

! Reinflate the remaining devices;

symbola.ndevices.inflate(1.001);

! Separate the depletion transistors from ;

! enhancement;

symbola.ddevices:-symbola.ndevices

.extractmatching(symbola,layer(implant));

! Inflate each type of device appropriately ;

! and make copies;

tempddev:-symbola.ddevices.inflate(3)

.selfintersect.retrace.copy;

tempndev: -symbola.ndevices.inflate(1)

.selfintersect.retrace.copy;

! Subtract them from the poly layer, ;

! make a new copy;

symbola.layer(poly):-temppoly.subtract(tempddev)

.subtract(tempndev);

tempddev:-symbola.ddevices.copy;

tempndev:-symbola.ndevices.copy;

```

END of Getdevices;

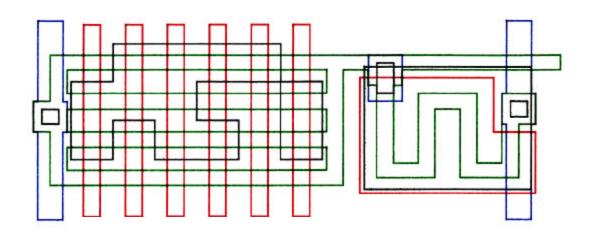

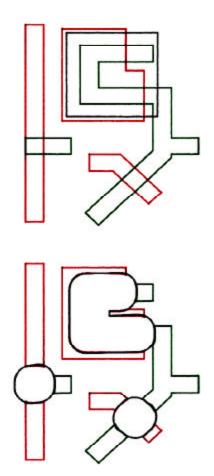

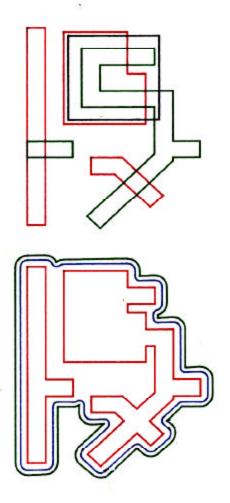

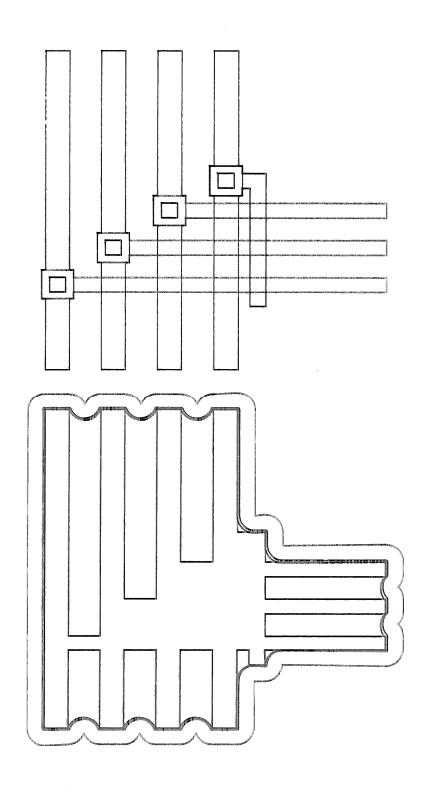

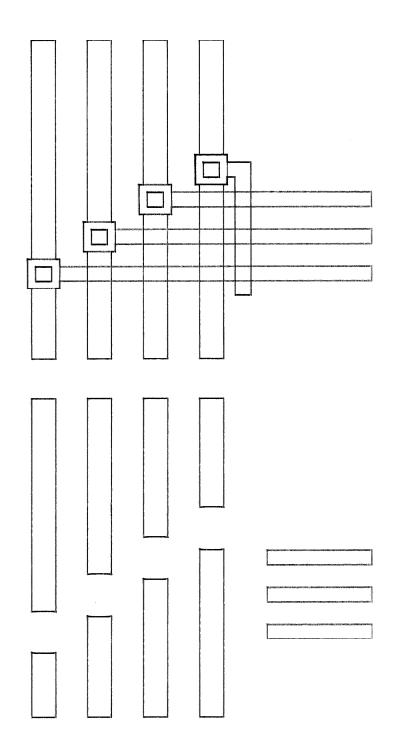

Figure 4.1 shows the operation of this algorithm on a small cell. The interconnection structures are left in their original colors and the devices are outlined in black. There are, of course, situations in which this algorithm misinterprets the geometry. It is believed that these would be too few to cause their combined effect to be seen the in the statistics accumulated for a design.

The algorithm also extracts capacitors properly and expands them by the correct three lambda. Capacitors do not share poly or diffusion with other devices unless they are part of the same net. This means that capacitors will usually have to be built with two lambda overlapping poly and one-half the minimum poly spacing built around them as are most depletion load devices.

Passive resistors built using long runs of poly or diffusion are not detected. However, this type of device is rare even in analog circuits and is not important to the wiring analysis of digital systems.

Other devices can be made if a second layer of polysilicon is available. Usually these are capacitors and can be detected by merely intersecting the two poly masks. The programs and algorithms of this thesis are currently limited to NMOS processes with single layer polysilicon and no buried contact mask. The extensions required to analyze designs that use these two features can be easily made but

DEVICE AREAS IN BLACK

FIGURE 4.1

IDENTIFICATION OF DEVICES

FIGURE 4.1

IDENTIFICATION OF DEVICES

require additional computations.

### 4.3 Estimation of Symbol Area

To make the statistics computed for a symbol meaningful, the area occupied by the entire symbol must be determined. As with many structures of a chip, it is difficult to define the boundaries of a symbol without knowledge of exactly what surrounds it. The heuristic method being discussed in this chapter attempts to estimate the area of the symbol using only the contents of the symbol as data. As with devices, there are situations in which such methods become unreliable. Experience with NMOS designs permits boundaries to be defined that are most probably correct.

The boundary of a symbol must extend at least one-half the minimum line spacing beyond the structures of the symbol. The structures of the symbol may occupy several layers, be disjoint and have holes or other areas that may be utilized by surrounding symbols. What is needed is a bounding hull that outlines the area of the symbol which external symbols must violate to affect the symbol. Those areas through which there is no room for a minimum size wire or which are completely enclosed must be inside the hull.

These boundaries must be computed separately for each interconnection layer (metal, poly and diffusion). They are constructed from the primitive structures of the symbol as well as the hulls of its subsymbols. The procedure to accomplish this is straightforward. For each layer, all the hulls of subsymbols (for that layer) and all the locally defined areas are OR'ed together. Then all the holes of the

resulting polygon are removed, since these represent enclosed areas. The remaining sheets are then inflated by one minimum spacing and one-half the minimum width for that layer, closing off any slots into which a minimum size wire cannot enter. The doubly wrapped areas are removed and the polygon is shrunk by one-half the minimum spacing and one-half the minimum width such that the remaining sheets one-half a minimum spacing larger than they originally but now have many of the slots in their "skyline" filled in. Redundancies are again removed and the resulting polygon is a reasonable outline of the symbol on that layer.

bounding hulls of each layer of the symbol become attributes of the symbol and used in are further operations. The area of each bounding hull is also recorded and becomes an important statistic with which to the results of other computations. Some hulls may have zero area if a given symbol does not utilize a particular layer. It should be noted, that the units of area used here, are square lambda and are not process dependent. they may be compared with the areas of employing older or newer design rules providing the basic processes are not significantly different. Below is a Simula program which finds the bounding hull of each of the three layers as discussed above.

PROCEDURE Hulls(symbola); REF(symbol)symbola; BEGIN

REF(polygon)hull; INTEGER 1,layer;

! Loop to get each layer of the symbol; FOR layer:=1 STEP 1 UNTIL 3 DO BEGIN

```

Imake a copy of the layer of the symbol;

hull: -symbola.layer(layer).copy;

! Loop to get all the hulls of subsymbols;

! for this layer;

FOR 1:=1 STEP 1 UNTIL symbola.subsymbols.length

DO BEGIN

REF (instance) inst;

! Get the hull of the subsymbol;

! and combine a copy with hull;

! Call Hulls recursively ;

! if subhull is not present. ;

inst:-symbola.subsymbols(i) QUA instance;

IF inst.sym.hull(layer) == NONE THEN

Hulls(inst.sym);

hull:-hull.combine(inst.sym.hull(layer).copy

.Xform(inst.tr));

END;

! Through out the doubly wrapped areas ;

! and all the holes;

hull.selfintersect.retrace.trim(1);

hull extractholes;

! Inflate it, trim it, then deflate it ;

! and trim it;

hull.inflate(spacing(layer)+width(layer)/2);

hull.selfintersect.retrace.trim(1);

hull.deflate((spacing(layer)+width(layer))/2);

hull.selfintersect.retrace.trim(1);

! Put the hull into the symbol attributes;

symbola.hull(layer):-hull;

END;

END of Hulls;

```

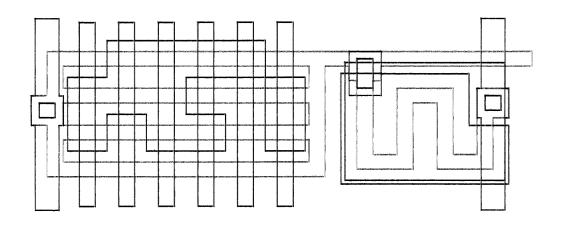

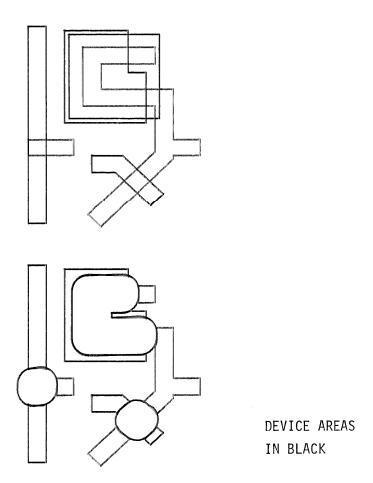

The execution of this procedure on a simple symbol is illustrated in Figure 4.2.

The sources of error in this algorithm are due to its ignorance of external connections of the symbol to other symbols. Where wires of one symbol abutt or overlap to

FIGURE 4.2

FINDING THE BOUNDARIES OF A SYMBOL

FIGURE 4.2

FINDING THE BOUNDARIES

OF A SYMBOL

make a connection, this algorithm will count the contact area to be in the hulls of both symbols making them appear larger than they really are. In higher level symbols which combine two such symbols, this is corrected since it results in doubly wrapped area and is reduced to singly wrapped area when the hulls are ORed together. is then non-accumulating and merely results in some optimism in size of the symbol. The wasted area of a if it is not enclosed, will not be counted as part of the symbol area. This will overshadow any optimism due external connections. Such wasted area will be accounted for in the next higher level of the symbol hierarchy.

### 4.4 Extraction of Global Wire from Local Wire

The extraction of global wire from local wire without the use of connection information is difficult not only because polygon operations are not easily able to recognize it but also because the definition of global wire is not a clear one. The definition requires some recognition of those structures that make external connections. This implies that internal connections be visible and distinguishable from external connections. Internal connections can be identified as places where wires intersect devices and subsymbols. External connections are difficult to detect and to be precise would require that the topology be known.

The detection of possible external connections requires some assumptions be made about the usual form in which they are made. Generally, a wire which is to connect to an external symbol will end at the edge of the symbol of which

it is a part. This need not always be true, since a wire from another symbol may intrude far into the symbol before making a connection, Also, a wire may be laid over a symbol from an external source and drop a contact to another layer i B through which a connection made. These de sign usually occur in regularized techniques d o not structured design and hopefully d o not represent α significant fraction o f the external connections symbols. If such techniques are important to the analysis, then the topology extraction of Chapter V must be used to find all the external connections of a symbol.

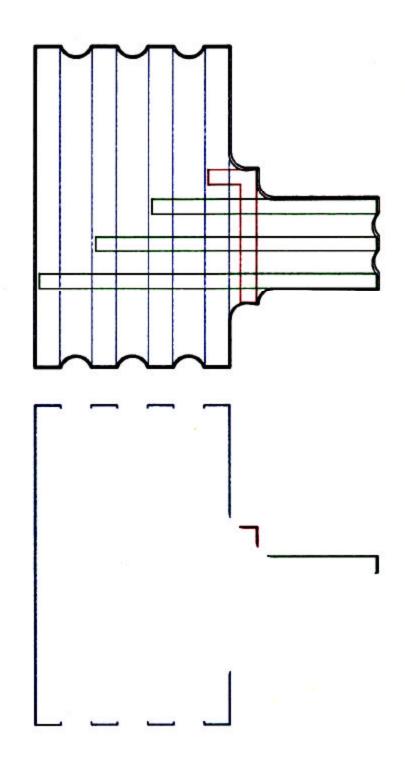

One heuristic method of separating global wire from local wire using only polygon manipulations, uses the symbol boundary computed earlier. A new boundary is constructed using the union of the hulls of the three interconnection layers after they have each been shrunk by one-half their minimum spacing. The result is a polygon which encloses all the symbol and is slightly larger than it needs to be to enclose the largest objects. From this a very thin annulus donut is made. A copy of the polygon is made and shrunk by a small amount such that it is too small to enclose objects of the symbol. It is then reversed (made into a hole) and added as a sheet of the original polygon, result is a thin ring about the symbol which the objects on the perimeter overlap. Figure 4.3 shows this annulus in red for the simple symbol. Below is a procedure which will generate the annulus of a symbol. The annulus is computed prior to the extraction of devices to be sure that the devices are included.

PROCEDURE Annulus(symbola); REF(symbol)symbola; BEGIN

FIGURE 4.3

THE ANNULUS OF A SYMBOL

FIGURE 4.3

THE ANNULUS OF A SYMBOL

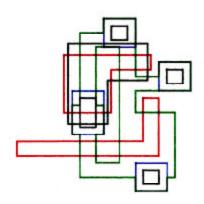

If this annulus is then intersected with the objects making up the symbol (excluding the subsymbols), possible external connection areas are found. As explained above, these may not be all the external connection areas but they should be most of them. Further, not all of the areas found by the intersection will be external connections, some may merely be the sides of structures adjoining the edge of the symbol.

Many of the intersections will "bend" around the corners of wires. To remove the portions of the ends sides of intersections that correspond to the the end, the thin intersections must be broken rather than where they turn corners. To do this, a copy of intersection may be inflated (by a size greater than the width of the intersection) generating "curlicues" at inside or concave corners. The curlicues may be extracted and subsequently subtracted from the original intersection polygon, causing intersections with bends to be broken at each turn. This leaves the polygon with a set of sheets that may or may not be external connection points.

To distinguish some of the external connections from most of the false intersections, the area of the intersection Connections are usually made can be an indicator. size wires, the exceptions are usually power minimum distribution. If a maximum width is set for the width of external connection, the various contacts with the annulus may be culled with respect to their area. The area a sheet which is an external connection must be less than or equal to the chosen width multiplied by the width of the annulus (.002 as computed above). Thus those sheets of greater area may be removed and the remaining sheets high probability of actually being external connections. Also, it is known that the connections must have a minimum area as well. This size can be used to cull out some of the small sheets that may have originated on the sides of wires and were broken from other parts of the intersection with the annulus.

Few external connections fall outside of this recognition procedure. Figure 4.4 indicates the external contacts seen by the described method. A Simula implementation is listed below. These contacts are found after the devices have been extracted such that devices are not mistaken for contacts (although some could have external contacts).

PROCEDURE Xcontacts(symbola); REF(symbol)symbola; BEGIN

INTEGER 1;

! Loop to do each interconnection layer; FOR 1:=1 STEP 1 UNTIL 3 DO BEGIN

FIGURE 4.4

FINDING POSSIBLE EXTERNAL CONTACTS

OF A SYMBOL

FIGURE 4.4

FINDING POSSIBLE EXTERNAL CONTACTS

OF A SYMBOL

```

REF(sheet)s;

! Intersect a copy of the annulus with ;

! a copy of each layer;

symbola.xcontact(i):-symbola.annulus.copy

,intersect(symbola,layer(i),copy);

! Inflate a copy of the intersection by ;

! more than the width of the intersections, ;

I then save the curlicues;

curlicues:-symbola.xcontact(i).copy

inflate(,003).trim(1);

! Subtract the curlicues from the original ;

I uninflated intersections, breaking open;

! the intersections at bends;

symbola.xcontact(1):-symbola.xcontact(1)

.subtract(curlicues);

! Compute the area of each sheet and remove if;

! it is outside the max and min then ;

! extract the sheet;

FOR s:-symbola.xcontact(1).nextsheet(s)

WHILE sm/mNONE DO BEGIN

REAL as

a:=s.area;

IF a)maxxcon OR a(minxcon THEN

symbola.xcontact(1).extractsheet(s);

END of sheet loop;

END of layer loop;

END of Xcontacts;

```

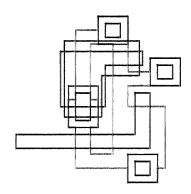

Given the external contacts of the symbol, the global wire may be separated from the local wire. Devices have been previously removed from the wire layers thus breaking wires which connect the gates of polysilicon transistors in sequence. The contact cuts of a symbol may regarded an internal connection. usually be a B Infrequently, global wire may change layers using a contact the contact cuts are inflated to a size slightly larger than the minimum size wires, they may be subtracted from the interconnection cutting it up into segments. If a segment contains an external contact, then it may be considered alobal, the rest are local wires. The parts subtracted added back to the local wire arbitrarily, two types of wire, global and local may then be expanded by one-half their minimum spacing and their area computed for statistics of the symbol. Figure 4.5 shows the wire separated from the symbol by these means. Below is the listing a Simula procedure for implementing this separation.

```

PROCEDURE SeparateWires(symbola); REF(symbol)symbola;

BEGIN

REF(polygon)blgcuts,tempw,tempc;

! Inflate the Contact cuts and put in a temporary;

bigcuts:-symbola.layer(cuts).copy.inflate(1.001);

! For each layer, separate the global from local;

FOR 1:=1 STEP 1 UNTIL 3 DO BEGIN

! Subtract the Cuts from the wires;

tempw:-symbola.layer(1).copy

,subtract(bigcuts.copy);

! Save the pleces removed from the wire;

tempc:-symbola.layer(i).copy

.intersect(bigcuts.copy);

! Extract the wire that touches;

! external contacts - this is global;

symbola.globalwire(i):-tempw.extractmatching(

symbola,xcontacts(i));

! Put the subtracted pieces and ;

! whats left together - this is local;

symbola, localwire(i):-tempw.union(tempc);

```

END of layer loop;

END of SeparateWires;

FIGURE 4.5

SEPARATION OF GLOBAL AND LOCAL WIRE

FIGURE 4.5

SEPARATION OF GLOBAL AND LOCAL WIRE

This heuristic method of separating global wire from local can misinterpret the geometry in many instances. Experience with the program and data taken from a number of designs will determine if these instances are rare enough to ignore. While the program has not run on a large body of designs, the algorithms presented have been applied by hand to a wide variety of symbols. The conclusion reached is that errors introduced into the wiring statistics by misinterpretation are less than 5 percent.

#### Chapter V

### Extraction of Circuit Topology

### 5.1 Devices and Device Connections

As in the previous chapter, devices must be recognized and, in addition, their sizes and types must be determined. gate must be identified so drain and that connections to them can be found. Of course, depletion mode transistors can be distinguished from enhancement mode devices by intersecting them with the ion implantation However, capacitors Must be recognized and differentiated from transistors. If the topology extracted from the mask data is to be used in the verification of the design, all the device and interconnection recognition must be precise. In practice, some assumptions have to be made to permit the programming of the problem with reasonable however, exceptions to any efficiency, restrictions made by these procedures must be highly improbable.

The recognition of devices, the determination of their sizes and their connection points, can be carried out as part of one operation. First of all, as with the heuristic method, the polysilicon and diffusion layers are intersected giving sheets which may be transistors. Again, these are shrunk, culled by area and expanded back to original size to eliminate false devices caused by butting

contacts. The devices are then subtracted from the diffusion layer.