Incomplete Charge Transfer in Overlapping Gates Charge Coupled Devices

Thesis by

Amr M. Mohsen

In Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

California Institute of Technology

Pasadena, California

1973

(Submitted March , 1973)

### ACKNOWLEDGEMENTS

Grateful thanks are due to my advisors Dr. Carver Mead and Dr. T. C. McGill for their constant guidance and enduring patience throughout the course of this work. I would like to acknowledge my gratitude to Dr. Herbert Keller for providing assistance essential to the completion of this work. Grateful thanks are due Dr. J. O. McCaldin, Dr. J. W. Mayer, Dr. N. George. Dr. R. D. Middlebrook and Dr. C. H. Wilts for the many attentions and encouragement they have given me during this work, and to Mrs. Carol Norris and Mrs. Kathy Ellison for typing and preparing this thesis, and for their secretarial work. The financial support of the Corning Glass Foundation is gratefully acknowledged. The work reported here was supported in part by the Office of Naval Research and the Naval Research Laboratory.

ii

### ABSTRACT

We have developed a numerical simulation of the charge transfer in the overlapping gates charge coupled devices. The transport dynamics were analyzed in terms of thermal diffusion, self-induced fields and fringing fields under all the relevant electrodes and the interelectrode regions with time varying gate potentials. We have also developed a lumped circuit model of charge coupled devices. Using this model simple analytic expressions describing the charge transfer with various clocking waveforms are derived. This model can be used to study the charge transfer characteristics for other device structures, dimensions, clocking waveforms and voltages, thus providing practical charge coupled device and circuit design tools.

Using the numerical simulation and lumped circuit model, the influence of clocking waveforms and clocking schemes on CCD operation are studied. It is concluded that increasing the clocking scheme complexity allows a better control of the storage and transfer of the signal charge and hence improves the signal dynamic range and charge transfer characteristics. It is shown that the performance of charge coupled devices is better with push clocks (that push the charge from one storage site to another) than with drop clocks (that create deeper potential wells to transfer the charge). The performance of charge coupled devices is shown to be basically superior to the MOS bucket brigade.

We have also developed a simple model to study the incomplete charge transfer due to trapping in the interface states. Incomplete

iii

charge transfer due to trapping in interface states is shown to limit the performance of CCDs at low frequencies. The most dominant effect is trapping in the interface states under the edges of the gates parallel to the active channel. The influence of the device parameters, dimensions and clocking waveforms on the signal degradation is discussed. Design features of CCD structures which would reduce the incomplete charge transfer due to interface states are presented. It is shown that increasing the clock voltages, increasing the signal charge or using dynamic push clock reduces the incomplete charge transfer due to interface states.

The contents of this thesis have been published under the following titles:

> "Charge Transfer in Overlapping Gates Charge Coupled Devices" A. M. Mohsen, T. C. McGill and C. A. Mead, <u>Journal of Solid</u> State Circuits, SC-8, No. 3, June 1973.

"The Influence of Interface States on Incomplete Charge Transfer in Overlapping Gates Charge Coupled Devices", A. M. Mohsen, T. C. McGill, Y. Daimon and C. A. Mead, Journal of Solid State Circuits, SC-8, No. 2, April 1973.

"Push Clocks: A new approach to charge coupled device clocking", A. M. Mohsen, T. C. McGill, M. Anthony and C. A. Mead, <u>Appl. Phys. Letters</u>, <u>22</u>, 4, February 15, 1973, pp. 172-175.

"Charge Transfer in Charge Coupled Devices", A. M. Mohsen, T. C. McGill and C. A. Mead, <u>ISSCC Digest of Technical Papers</u> <u>15</u>, 1972, pp. 248-249.

The contents of this thesis have also been presented in the following conferences:

"Physics of Charge Coupled Devices", Invited Review Talk given at the Gordon Research Conference, Meriden, New Hampshire, August 1972.

"The Influence of Clocking Waveforms on CCD Operation", presented at the International Device Research Conference at Edmonton, Canada, June 1972.

"Charge Transfer in Charge Coupled Devices", presented at the International Solid State Circuits Conference, Philadelphia, Pa., February 1972.

A motion picture simulation of the various stages of the charge transfer process with two-phase and four-phase clocking schemes was produced directly from the results of the numerical simulation developed in this thesis. The CCD movie has been presented in the conferences mentioned above and is included in the "Semiconductor Memory Course" prepared by Texas Instruments on video tapes. The CCD movie is published in the Journal of Solid State Circuits (June 1973) as three sequences of page-flip movie.

# TABLE OF CONTENTS

| Ŧ  | ACKNOWLEDGMENT                   |                                                                   |          |  |  |

|----|----------------------------------|-------------------------------------------------------------------|----------|--|--|

|    | ABSTRACT                         |                                                                   |          |  |  |

| 1. | INTRODUCTION                     |                                                                   |          |  |  |

| 2. | . THEORETICAL MODEL              |                                                                   |          |  |  |

|    | 2.1                              | Transport Equations                                               |          |  |  |

|    | 2.2                              | Approximations                                                    |          |  |  |

|    | 2.3                              | Nonlinear Diffusion Equation                                      | 13       |  |  |

| 3. | FREE CHARGE TRANSFER             |                                                                   |          |  |  |

|    | 3.1                              | Push and Drop Clocks                                              |          |  |  |

|    | 3.2                              | Two-Phase Clocking Schemes                                        | 21       |  |  |

|    |                                  | 3.2.1 Complete Charge Transfer Mode                               | 23       |  |  |

|    |                                  | (A) Drop Clock<br>(B) Push Clock                                  | 23<br>34 |  |  |

|    |                                  | 3.2.2 Incomplete Charge Transfer Mode                             | 49       |  |  |

|    | 3.3                              | Four-Phase Clocking Scheme                                        | 55       |  |  |

|    |                                  | 3.3.1 Complete Charge Transfer Mode                               | 56       |  |  |

|    |                                  | <ul><li>(A) Drop Clock</li><li>(B) Push Clock</li></ul>           | 56<br>56 |  |  |

|    |                                  | 3.3.2 Incomplete Charge Transfer Mode                             | 60       |  |  |

|    | 3.4                              | Signal Degradation                                                | 60       |  |  |

| 4. | TRAPPING IN THE INTERFACE STATES |                                                                   |          |  |  |

| x  | 4.1                              | Incomplete Charge Transfer Due to Trapping in<br>Interface States |          |  |  |

|    | 4.2                              | Model and Approximations                                          |          |  |  |

|    | 4.3                                                                                           | Trap Oc             | cupation in Steady State and Transient                     | 78       |  |  |

|----|-----------------------------------------------------------------------------------------------|---------------------|------------------------------------------------------------|----------|--|--|

|    | 4.4                                                                                           | Trappin<br>Gates    | g in the Interface States under the Storage                | 80       |  |  |

|    | 4.5                                                                                           | Trappin<br>Gates    | g in the Interface States under the Transfer               | 83       |  |  |

|    | 4.6                                                                                           | Trappin<br>the Gate | g in the Interface States under the Edges of<br>es         | 87       |  |  |

| N  | 4.7                                                                                           | Numeric             | al Results                                                 | 91       |  |  |

|    | 4.8                                                                                           | Discuss             | ion                                                        | 101      |  |  |

| 5. | CONCI                                                                                         | LUSIONS             |                                                            | 111      |  |  |

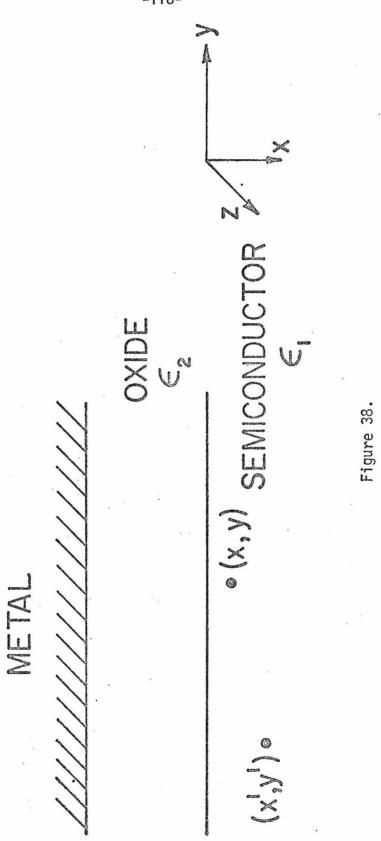

|    | APPE                                                                                          | NDIX 1.             | Green Function Solution of the Potential in MIS Structure  | a<br>117 |  |  |

|    | APPENDIX 2. Derivation of the Surface Potential Gradi<br>under the Gate Electrodes and in the |                     |                                                            |          |  |  |

|    |                                                                                               |                     | Interelectrodes Regions                                    | 124      |  |  |

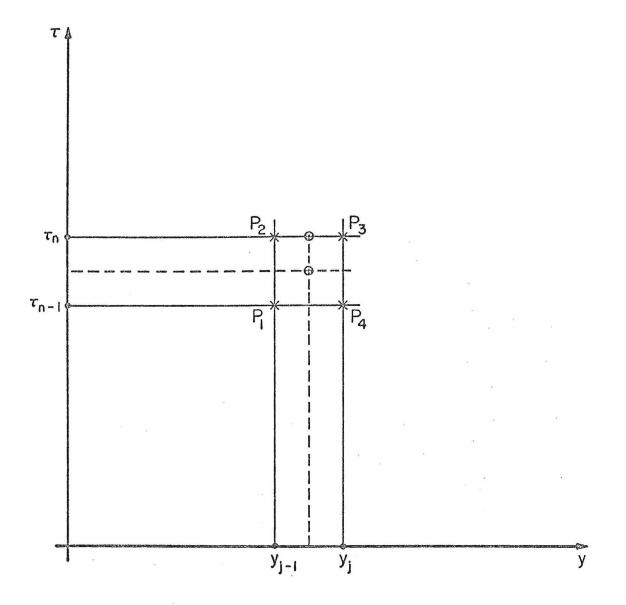

|    | APPEI                                                                                         | VDIX 3.             | Numerical Solution                                         | 127      |  |  |

|    | APPEI                                                                                         | NDIX 4.             | Steady State Current and Charge under the<br>Transfer Gate | 147      |  |  |

|    | APPEI                                                                                         | NDIX 5.             | Lumped Circuit Model of Charge Coupled<br>Devices          | 150      |  |  |

|    | APPEI                                                                                         | NDIX 6.             | Transient Occupation of the Interface States               | 5156     |  |  |

|    | FOOTI                                                                                         | NOTES               | * * * * *                                                  | 160      |  |  |

|    | REFERENCES<br>FIGURE CAPTIONS                                                                 |                     |                                                            |          |  |  |

|    |                                                                                               |                     |                                                            |          |  |  |

÷

## Chapter 1

### INTRODUCTION

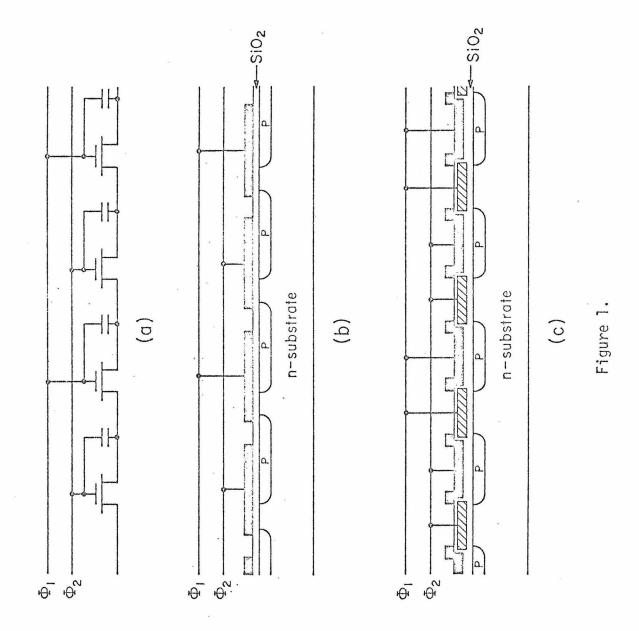

The idea of making a shift register for analog signals and using it as a delay line dates back to the beginning of the fifties.<sup>(1)</sup> Sampled values of the analog signal can be stored in the form of charges on a series of capacitors. The transfer of charge between these storage capacitors can be controlled by switches driven by clock pulses. By analogy with the old fire-fighting method, in which buckets of water are passed along the line, circuits of this type were called "bucket brigade delay lines". However, these delay lines have not come into general use because of the inevitable complexity and bulk of the switches. In 1969, Sangster<sup>(2)</sup> proposed an integrated circuit version of the bucket brigade delay line with the advantages of low cost, high packing density and compatibility with the existing semiconductor technology. Figure (1) shows a two-phase MOS bucket brigade. Each stage consists of a MOS transistor and a storage capacitor. The signal charge is stored in the p-diffusion islands and the transfer of charge is controlled by the clock pulses,  $\phi_1$  and  $\phi_2$ .

In 1970, Boyle and Smith<sup>(3)</sup> showed that the signal charge packets could be stored and transferred in potential wells at the semiconductorinsulator interface under electrodes without using p-diffusion islands as in the MOS bucket brigade. For efficient coupling of the potential wells at the interface the electrodes should be closely spaced. The resulting structure is commonly known as the charge coupled device and

-2-

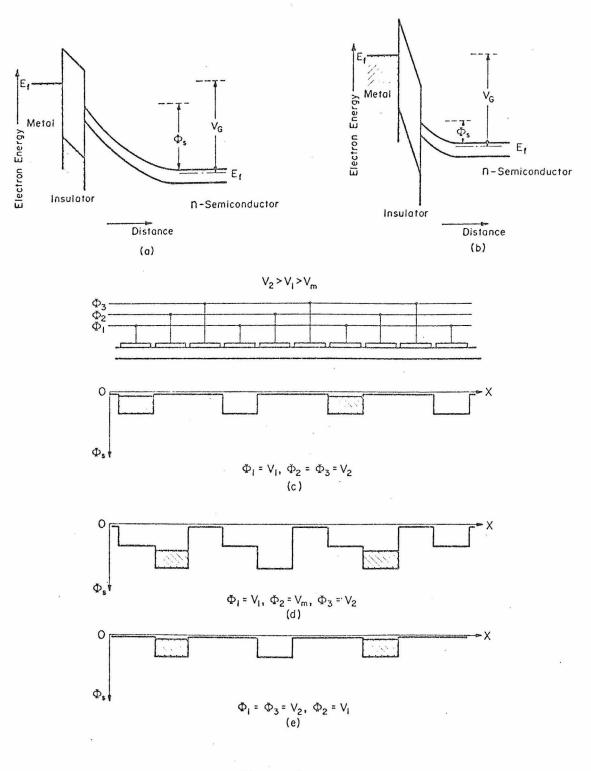

is shown in Fig. (2c). In Fig. (2a) and (2b) the band diagram of a metal-insulator-n semiconductor is shown to illustrate the creation of potential wells at the interface when a voltage pulse is applied to the metal electrode. Minority carriers injected in reponse to a digital or analog signal or generated by photons could be stored as charge packets in these potential wells resulting in a decrease in depth of the potential well. The storage and transfer of the charge packets are controlled by the clocking pulses driving the closely spaced electrodes as shown in Fig. (2c,d,e) where a three phase clocking scheme is used.

So charge coupled devices (CCDs) are a new class of semiconductor structure operating in nonequilibrium. In essence CCDs are analog, dynamic, passive shift register that permits the design of complex functional devices. Currently there is a great interest in these devices as they have important applications for digital memories, selfscanned imagers and analog signal processing. In order to design and properly operate charge coupled devices with optimum performance an understanding of the physical limitations on the performance of these devices is essential.

From the operation of charge coupled devices, it is clear that the main limitations on the performance of these devices are due to the incomplete transfer of the signal charge; trapping of the signal charge in the interface states; thermal generation currents from the generation centers at the interface, the depletion regions, and the substrate and the noise generated during the storage and transfer of the signal charge along the interface.

-3-

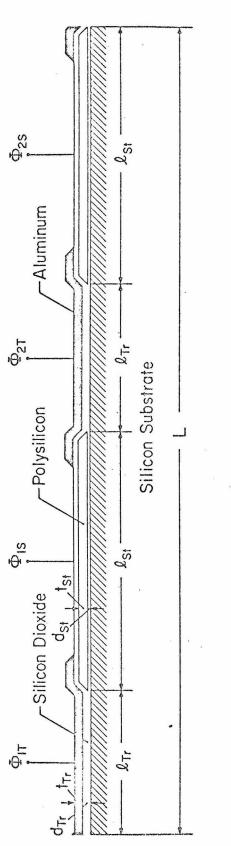

Figure 2.

In this thesis, we present a detailed study of the limitations on the performance of charge coupled devices due to incomplete free charge transfer and trapping in the interface states and their dependence on the device parameters and clocking waveforms. In our work we have considered the overlapping gate structure (shown in Fig. (3)) as it is presently the most technically promising structure for the large scale application of the devices. Compared to the simplicity of the threephase metal gate  $CCD^{(3,4)}$  and the resistive gate  $CCD^{(5)}$ , the interelectrode spacing in the overlapping gate structure is reduced to an oxide thickness and the overlapping electrodes provide good control of the surface potential in the entire channel region, seal the active channel from any external contaminations, shield out the charge repulsion. and thus enhance the charge transfer, Overlapped gate CCDs can be easily manufactured with two levels of metalization technology such as silicon gate and refractory gate technology. (6,7) The two levels of metalization also simplifies the layout of large CCD arrays.

We have developed a detailed numerical simulation of the charge transfer process in the overlapping gate charge coupled devices. With some assumptions and approximations, which are shown to be well satisfied, we have solved the nonlinear nonlocal equations describing the transfer dynamics, under all the relevant gate electrodes and interelectrode regions with time varying gate potentials using a new finite difference scheme, the Box scheme.<sup>(8)</sup> We have developed a simple lumped circuit model of charge coupled devices. This model can

-5-

be used to study the charge transfer characteristics for other device structures, dimensions, clocking waveforms, and voltages, thus providing practical charge coupled device and circuit design tools. Using the numerical simulation and the lumped circuit model we have studied the influence of clocking waveforms and clocking schemes on the performance of charge coupled devices and we present a fundamental comparison of the performance of bucket brigade and charge coupled devices. Finally, we have developed a simple model to study the influence of trapping in the interface states on the incomplete charge transfer and present design features of CCD structures to reduce it.

## Chapter 2

### THEORETICAL MODEL

In this chapter we present the equations that describe the storage and transfer of charge in charge coupled devices. We also discuss the assumptions and approximations that we have used to reduce the nonlinear-nonlocal transport equations to nonlinear diffusion equations.

In the calculations presented below we have considered p-channel<sup>2</sup> devices with dimensions consistent with typical layout tolerances of silicon gate technology. One unit cell of the overlapping gate structure using silicon gate technology is shown in Fig. (3).

# 2.1 Transport Equations

The storage and transfer of charge along the insulator-semiconductor interface is described by the continuity equation:

$$\frac{\partial q}{\partial t} = \frac{-\partial}{\partial x} J_{x} - \frac{\partial q}{\partial t} \Big|_{\text{Trapping}} + \frac{\partial q}{\partial t} \Big|_{\text{Th. Generation}}, \quad (1)$$

where

$$J_{X} = -D \frac{\partial q}{\partial x} - \mu q \frac{\partial \phi_{S}}{\partial x}$$

(2)

q is the surface charge density of the free minority carrier,  $J_{\chi}$  is the sheet current density, and  $\phi_{s}$  is the surface potential. D and  $\mu$  are the minority carrier diffusion and mobility at the interface respectively. x is the distance along the interface in the direction of charge transfer.  $\frac{\partial q}{\partial t} |_{Th. Generation}$  is the rate of generation of Surface charge due to thermal generation currents from generation centers at the interface, the depletion regions and the substrate. For a total delay time from the input to the output of the device much smaller than the storage time of the interface, the effect of thermal generation can be neglected.  $\frac{\partial q}{\partial t} |_{Trapping}$  is the total rate of

capture of the mobile carriers due to their interaction with the interface states in the band gap. Since the mobile carriers interact with interface states within an energy range of the order of thermal voltage and for the low interface state density obtainable with the present thermally grown silicon oxide, the rate of capture or emission of the mobile carriers by the interface states is smaller than the divergence of the sheet current density in Eq. (1). Thus one can obtain the free charge transfer characteristics by neglecting  $\frac{2q}{r}$  in Eq. (1) and calving the cantinuity acustion. The

in Eq. (1) and solving the continuity equation. The Trapping

effects of trapping on the incomplete charge transfer can then be calculated by studying the interaction of the mobile carriers with the interface states from the Shockley-Read-Hall equations together with the surface charge density profiles q(x,t) under the gates. Thus the free charge transfer continuity equation reduces to

$$\frac{\partial q}{\partial t} = \frac{\partial}{\partial x} \left[ D \frac{\partial q}{\partial x} + \mu q \frac{\partial \Phi_s}{\partial x} \right]$$

(3)

The surface potential gradient  $\frac{\partial \Phi_s}{\partial x}$  is due to the variable

surface charge density and the two-dimensional nature of the CCD structure. For given electrode potentials, device geometry, and charge density profile, the surface potential gradient is obtained from the solution of the two-dimensional Poisson equation. Thus a rigorous treatment of the free charge transfer problem would require the simultaneous solution of Eq. (3) and the two-dimensional Poisson equation. While this rigorous approach is conceptually possible, the cost of such an analysis leads us to seek some valid approximation to simplify the solution.

# 2.2 Approximations

The surface potential gradient due to variations in the surface charge density (self-induced fields) can be obtained, according to the standard gradual channel approximation.<sup>(9)</sup> In this approximation, we take the gradient of the surface potential  $\Phi_s$  obtained from the onedimensional solution of the Poisson equation with the parameters of the solutions chosen to correspond to the one-dimensional cut through the structure. In Appendix I, we show, using a Green's function solution of the two-dimensional Poisson equation for an arbitrary minority charge density profile, that the gradual channel approximation is reasonably accurate when the lateral variation of the various charges over a distance on the order of the depletion layer width is small.

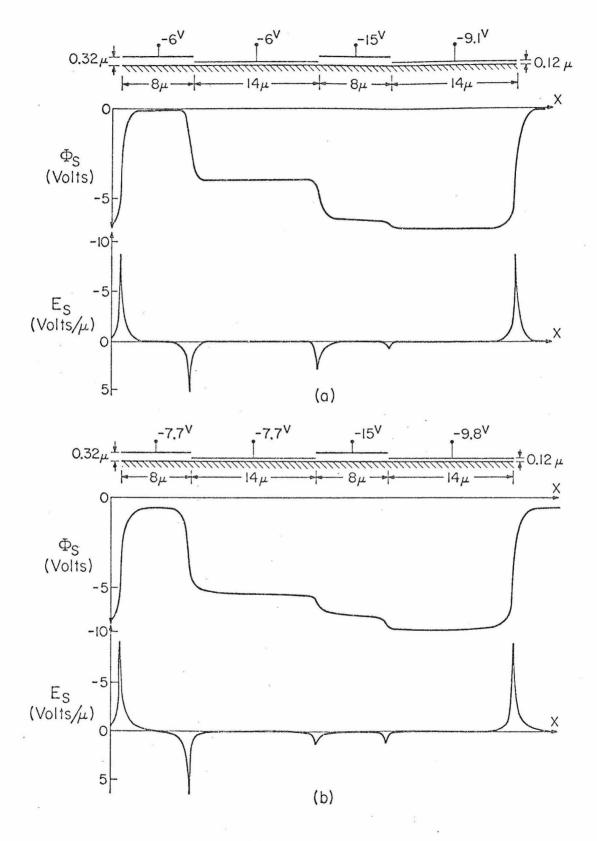

The surface potential gradient under the electrodes due to the adjacent electrodes (fringing fields) are obtained by solving the two-dimensional Poisson equation of the CCD structure. In Fig. (4) we have plotted the surface potential and surface potential gradient

-10-

Figure 4.

along the semiconductor insulator interface. These plots were obtained from the solution of the two-dimensional Poisson equation (10) of an overlapping gate CCD with the electode voltages corresponding to the stages of the charge transfer and with most of the signal last charge in the receiving storage electrode. The fringing fields in devices with dimensions consistent with typical layout tolerances of MOS technology are of the order of a few hundreds volts/cm. During the first stages of the charge transfer process the self-induced fields are typically few thousands volts/cm, therefore, the fringing fields are only important at the last stages of the charge transfer when the self-induced fields become very small. Accordingly the fringing field profile under the electrodes obtained from a twodimensional solution of the Poisson equation of the CCD structure with the gate voltages corresponding to the last stages of the charge transfer and with most of the signal charge in the receiving electrode can be used during the entire charge transfer process.

The two-dimensional solution of the Poisson equation for the overlapping gate structure shown in Fig. (4) illustrates that the surface potential under the interelectrode regions varies quite smoothly for different gate electrode potentials. Therefore we have used a smooth interpolating polynomial to approximate the surface potential in these regions. We have also assumed a constant surface mobility to simplify the transport equations. The dependence of the surface mobility on the normal surface field and the surface potential gradient along the interface introduce negligibly small error on the charge transfer characteristics of typical minimum geometry devices.<sup>4</sup>

### 2.3 Nonlinear Diffusion Equation

In Appendix II, we show that according to the above assumptions the surface potential gradient under the gates or in the interelectrode regions can be written in the form

$$\frac{\partial \Phi}{\partial x} = L(x,t) + M(x,t) q + N(x,t) \frac{\partial q}{\partial x} \qquad (4)$$

Substituting in Eqs. (3), the continuity equation reduces to the nonlinear diffusion equation:

$$\frac{\partial q}{\partial t} = \frac{\partial}{\partial x} \left[ D \frac{\partial q}{\partial x} + \mu q \left( L + Mq + N \frac{\partial q}{\partial x} \right) \right]$$

(5)

If fringing fields under the gate electrodes are negligible then L = M = 0.

The dynamics of the charge transport in each bit is thus described by equations similar to Eq. (5) with the appropriate functions, L, M, and N under the storage and transfer electrodes and the interelectrode regions. At the junction points between the different regions, the surface potential and surface charge density must be continuous and the current must be conserved.

We have solved the set of nonlinear equations with the appropriate boundary conditions using a new finite difference scheme, the Box scheme.<sup>(8)</sup>The numerical formulation of the problem<sup>5</sup> and its accuracy is treated in detail in Appendix III.

### Chapter 3

# FREE CHARGE TRANSFER

We have shown in Chapter 2 that the charge transfer dynamics in each bit of the charge coupled device can be described by a nonlinear diffusion equation. In this chapter we will present the results of the manerical solutions of these nonlinear equations when the device is corrated with different clocking schemes and waveforms. A comparison of the charge transfer characteristics obtained from the lumped circuit model of the device developed in Appendix IV and V with the numerical ensults is also presented.

#### 1.1 Push and Drop Clocks

The closely spaced electrodes of the charge coupled device Can be driven by clocking pulses that may have various shapes and waveforms to control the storage and transfer of the charge along the interface. In general clocking pulse waveforms could be classified into two basically different types: drop clocks and push clocks. With drop clock the signal charge is stored below a gate at a holding voltage is which is a fraction of the largest clock voltage  $V_m$  that the mid structure can tolerate; charge transfer occurs when  $V_m$  is then is then is plied to the adjacent gates, and the charge flows to the potential minimum thus created. With push clocks the charge is stored under a is held at  $V_m$ , and transferred to a nearby gate, also at  $V_m$ , by falsing the potential of the gate where the charge has been residing if thus "pushing" the charge to the next gate. Charge coupled devices can be operated with two-phase, three-phase, or four-phase clocking schemes by push clocks, drop clocks, or a combination of push and drop clocks. With three-phase and four-phase clocking schemes the electrodes of the overlapping gate structure are equal in size so that charge may be stored under each gate during the transfer process. Alternatively the upper electrodes may be made smaller and used to control the transfer of charge between the buried storage electrodes. In this case, four-phase, two-phase, and single-phase clocking schemes may be used to control the storage and transfer of charge for both serpentine and parallel signal flow.

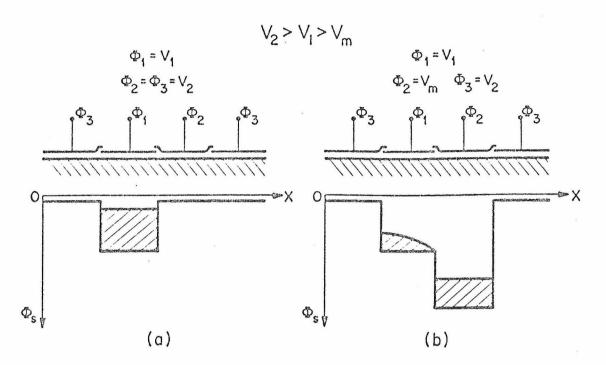

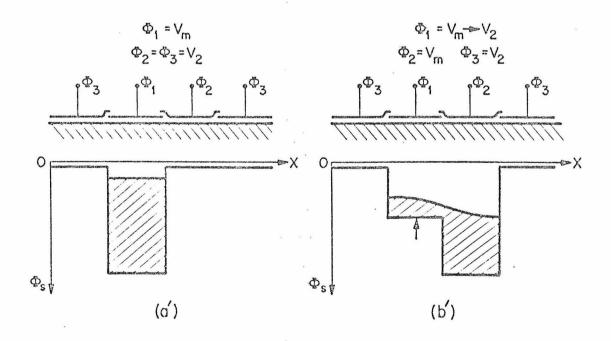

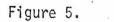

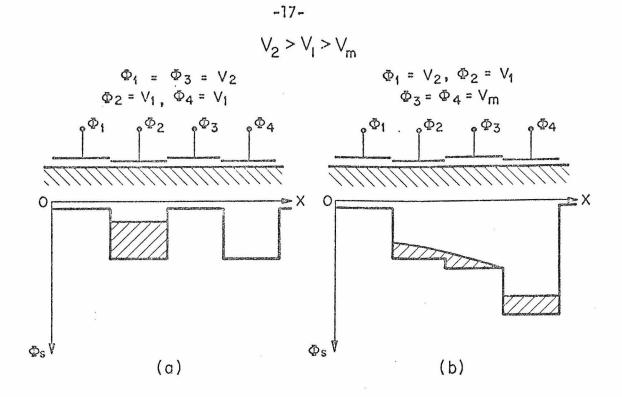

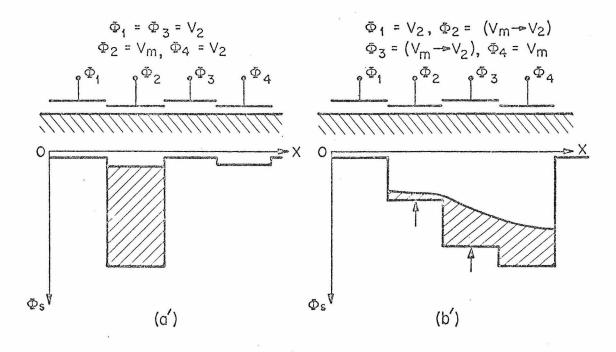

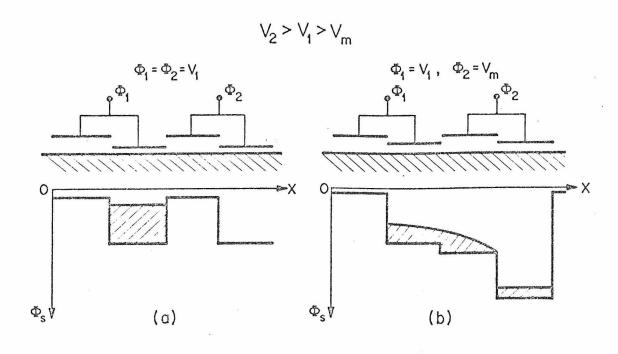

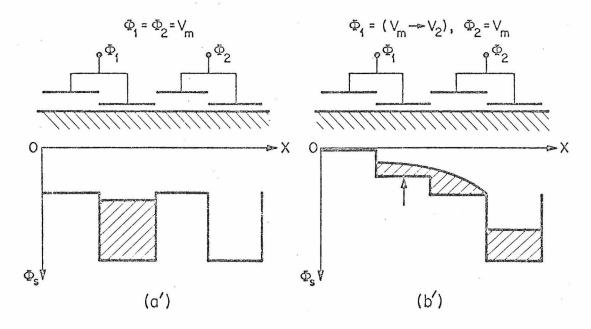

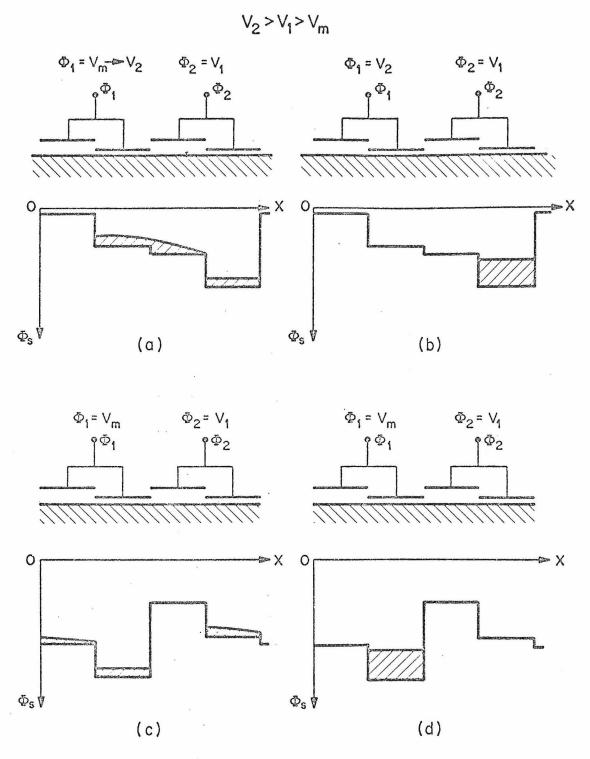

A detailed explanation of push clock operation and comparison with drop clocks can be made with the aid of Figs. (5), (6), and (7). These figures depict charge storage and transfer in three-phase, four-phase, and two-phase CCD's respectively with both drop and push clocks. The particular clock voltages shown apply to the case of p-channel devices, in which all clock voltages are negative.  $V_m$  is the minimum (most negative) clock voltage that can be used, as determined by some constraint such as field oxide threshold;  $V_1$  is the holding voltage (in the drop clock case); and  $V_2$  is a resting (gate-off) voltage; thus  $V_2 > V_1 > V_m$ .

The drop clock case is shown first; the signal charge is stored under a gate at potential  $V_1$  (Figs. 5a, 6a, and 7a). To effect charge transfer, the voltage of the next gates is lowered to  $V_m$  (Figs. 5b, 6b, and 7b); the charge flows to the local potential minimum thus created. In the push clock case, the signal

-15-

charge is initially held under a storage gate which is at  $V_m$  (Figs. 5a', 6a', and 7a'). At the beginning of the charge-transfer operation, the voltages of the next gates are lowered to  $V_m$ . The potential of the original storage gate is then <u>gradually</u> raised, and the charge stored there is pushed to the area under the next storage gate (Figs. 5b', 6b', and 7b'). As the potential of the original storage gate continues to rise, more of the charge under it is brought to a potential higher than that under the transfer gate, and so is able to flow to the next storage gate. Finally the original storage gate reaches its resting potential,  $V_2$ .

It can be seen from the preceding discussion that the push clocks allow a greater fraction of  $V_m$  to be used in storing the signal charge, and thus provide a greater dynamic range and signal to noise ratio than drop clocks. Also as will be shown in the next sections, the push clock scheme yields better charge-transfer efficiency at both high and low frequencies, and allows a definite advantage in highspeed operation to be obtained from the use of a four-phase clock. In Figs. (6) and (7), it is clear that the charge transfer for the two-phase drop clock and four-phase drop clock are similar, therefore increasing the clock complexity from two-phase to four-phase with drop clocks does not improve the performance of the device. However the push clock takes full advantage of the more flexible control of the surface potential under the different electrodes. For example in Fig. (6a') during storage times the transfer gates can be turned off by the resting voltage  $V_2$  and the storage gates can be heavily turned on by the minimum voltage  $V_m$ . The maximum signal charge which may be stored under the storage gate is thus almost a full bucket. <sup>6</sup> Also, since the transfer gates are controlled independently, they can be turned on heavily during the first stages of the transfer process, as shown in Figs. (6b') to enhance the rate of charge transfer. Thus increasing the clocking scheme complexity with push clock allows better control of the storage and transfer of the signal charge and hence provides larger signal dynamic range, larger signal to noise ratio and better performance, especially at high frequency.

The waveforms of the different phases of the dynamic push clocks must be overlapping. Since the rate of charge transport along the interface is finite the rise times  $T_r$  of the clocking pulse have minimum permissible values. If these values are exceeded the surface potential under the gates exceeds  $2\phi_F$  and some of the signal charge will be injected into the substrate where it is lost by recombination. For example, the minimum rise time of the two-phase push clock is given by (as shown in Eq. (20) below)

$$T_{r_{min}} \sim 2 \frac{\ell_{St}\ell_{Tr}}{\mu} \frac{C_{St}}{C_{Tr}} \cdot \frac{1}{V_{c}}$$

where  $\ell_{\rm Tr}$  and  $\ell_{\rm St}$  are the lengths of transfer gate and storage gate.  $\mu$  is the surface mobility.  $C_{\rm St}$  and  $C_{\rm Tr}$  are the effective oxide and depletion layer capacity under the storage and transfer gates respectively.  $V_{\rm c}$  is equivalent to the clocking voltage amplitude. For minimum geometry electrodes (~10 microns) and reasonable clock voltage amplitudes (~5 volts),  $T_{\rm rmin}$  is much smaller than the finite rise and fall times which are unavoidable in practical clock drivers (~tens of nanosecond). Hence, the finite rise and fall times that would delay the charge transfer with drop clocks are advantageously used with push clocks to push the charge from one storage site to another.

A single clocking phase could be used to operate the device as shown in Fig. (8). In this case the same two-phase structure of Fig. (7) is used, and one of the clocking phases  $\phi_2$  is kept at a constant voltage  $V_1$ , while the other phase  $\phi_1$  is changed between  $V_m$  and  $V_2$ . When  $\phi_1$  changes from  $V_m$  to  $V_2$  the signal charge is pushed from under  $\phi_1$  to under  $\phi_2$  in one half cycle. In the other half cycle when  $\phi_1$  changes from  $V_2$  to  $V_m$  the signal charge flows to the deeper potential well under  $\phi_1$ . Instead of applying a bias voltage  $V_1$  on  $\phi_1$ , ion implantation or the charge storage properties of double dielectric structure could be used. As compared with the two-phase and four-phase clocking scheme, the signal phase clocking scheme utilizes a smaller fraction of the surface potential swing to store the signal charge and, therefore, the device will have smaller signal dynamic range, signal to noise ratio, and transfer efficiencies.

### 3.2 Two-Phase Clocking Scheme

In the two-phase clocking scheme only two clock phases are used to control the storage and transfer of charge along the interface. The asymmetry in the surface potential needed to provide the directionality of the signal charge transfer can be achieved by using

-21-

-22-

a step in the channel oxide<sup>(7)</sup> or an ion implanted barrier<sup>(13)</sup> or the charge storage properties of double dielectric structures.<sup>(14)</sup> In this section we present some of the calculations of the charge transfer characteristics of two-phase overlapping gates CCDs where the asymmetry of the structure is achieved by a step in the channel oxide. However our results can be applied to all other structures with the appropriate modifications.

3.2.1 Complete Charge Transfer Mode

In the complete charge transfer modes the charge under the storage gate is transferred to the following gates; none is deliberately retained.

(A) Drop Clock: With drop clock the signal charge is stored below a gate at a holding voltage  $V_1$  which is a fraction of the largest clock voltage  $V_m$  that the MOS structure can tolerate; charge transfer occurs when  $V_m$  is then applied to the adjacent gates and the charge flows to the potential minimum thus created.

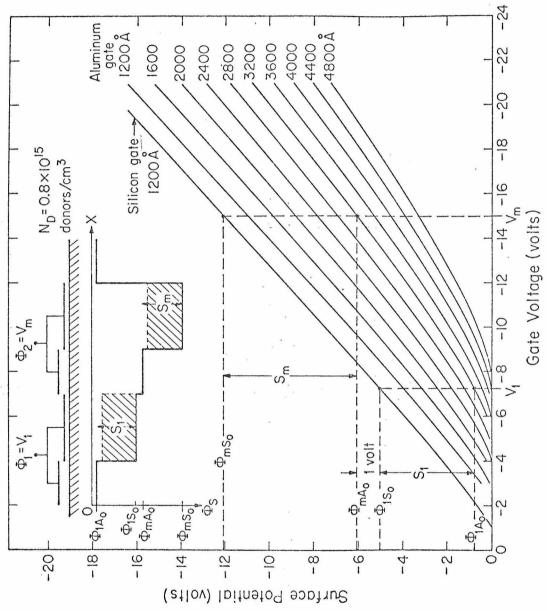

In Fig. (9) we have plotted the one-dimensional relation between the surface potential and the gate voltage for a polysilicon gate with 1200 Å oxide and for an aluminum gate with different oxide thickness for a substrate doping of 8 x  $10^{14}$  donors/cm<sup>3</sup>. Since in the twophase clocking scheme the surface potential under each successive set of transfer and storage gates is controlled by a single clocking voltage, the maximum amount of charge that can be stored under the storage gate without spill over and the fringing fields under it depend on the silicon oxide thickness under the transfer and storage gates.

Figure 9.

-24-

Therefore, for optimum operation of the device, the oxide thickness under the storage and transfer gates should be properly chosen.  $^7$

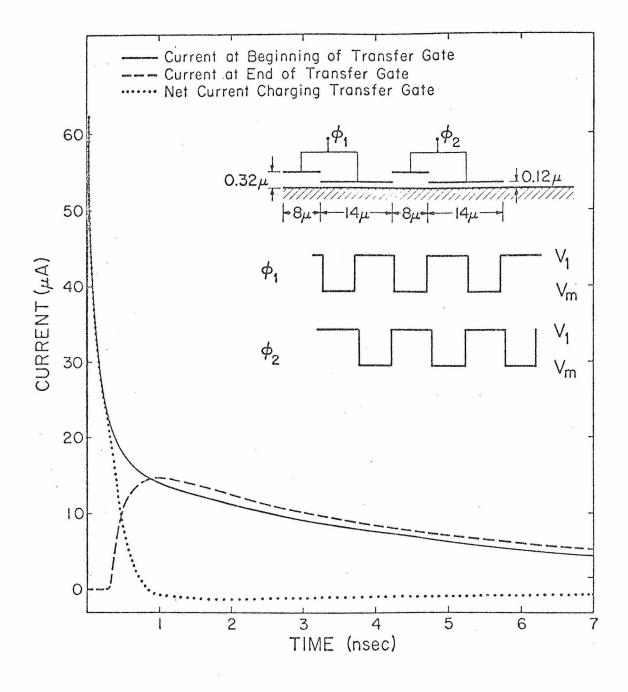

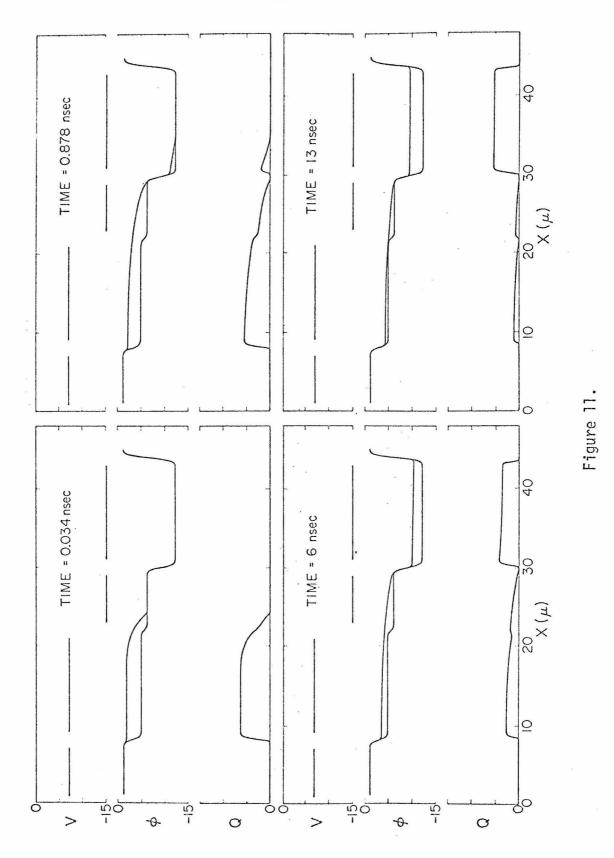

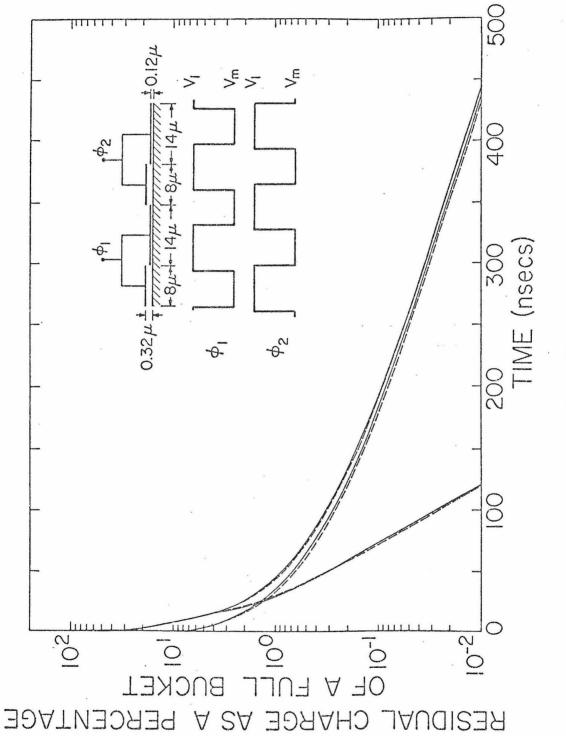

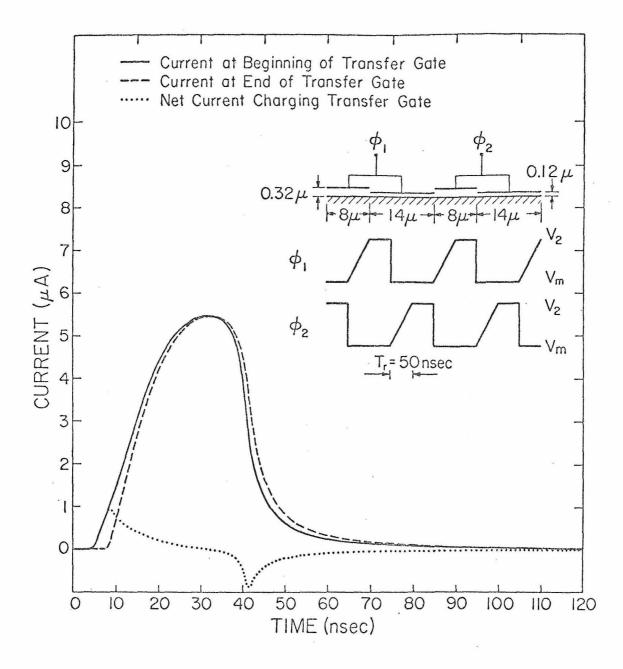

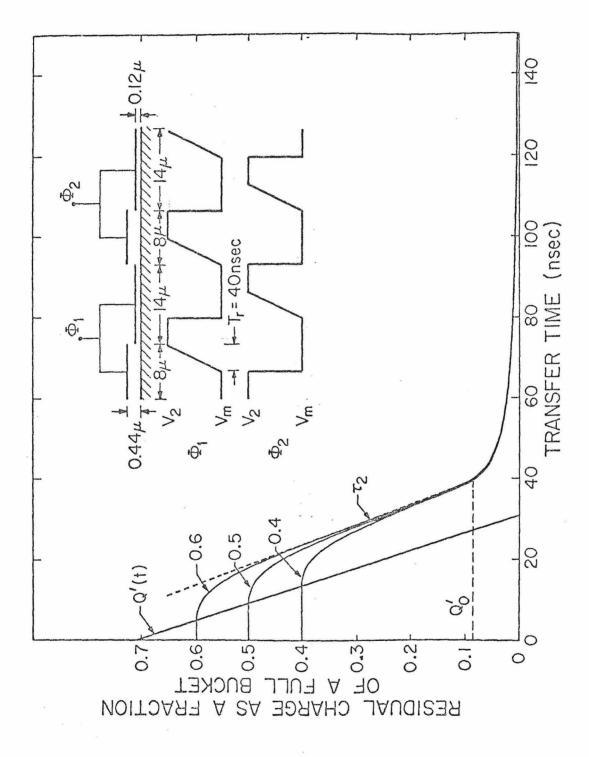

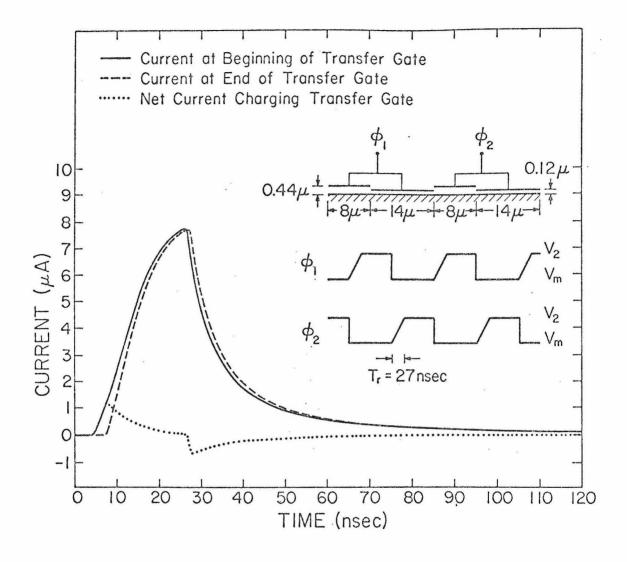

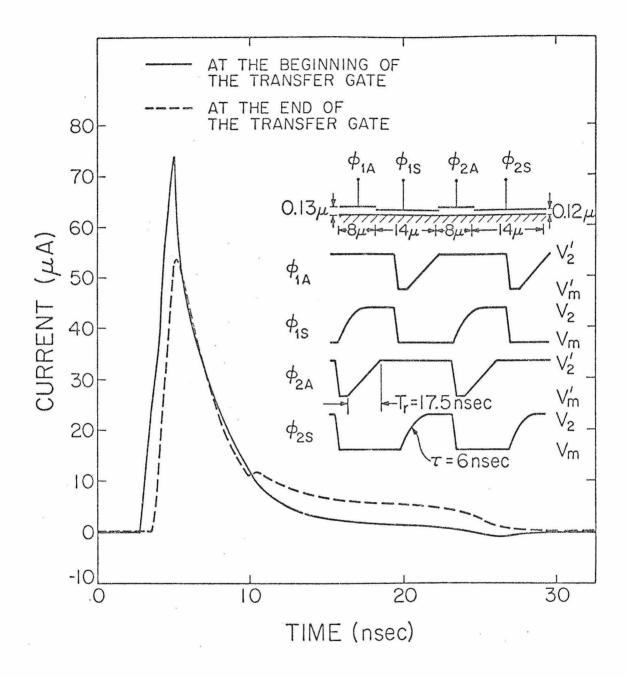

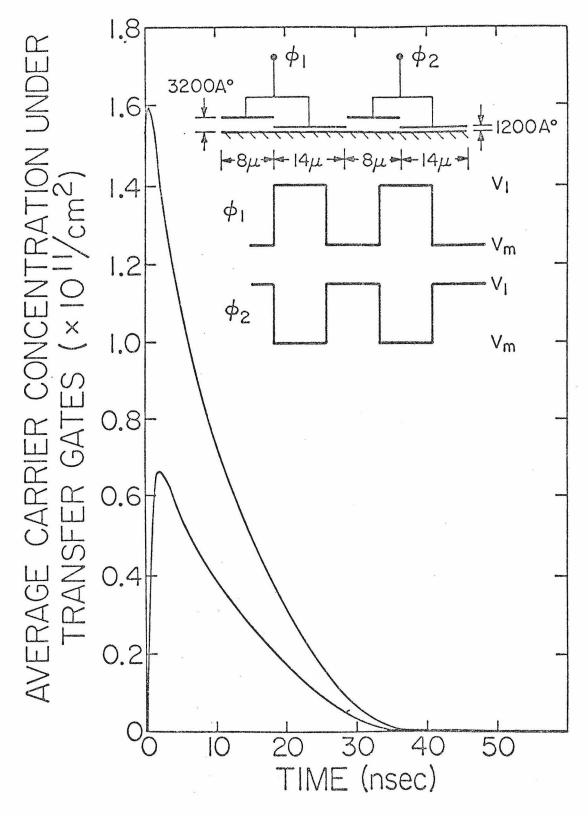

We have simulated numerically the charge transfer characteristics for the device shown at the top of Fig. (10) clocked by square wave drop clocks with zero fall and rise times. <sup>8</sup> The transient currents at the beginning and end of the aluminum transfer gate and the net current charging it are shown in Fig. (10). Zero time corresponds to the instant when  $\phi_2$  decreases to  $\,V_m^{}\,$  starting the charge transfer. The current at the beginning of the gate increases from zero sharply to about 60 µamp and then decreases rapidly. The surface charge takes about 0.3 nanoseconds propagating under the transfer gate to reach its end. The transfer gate is charged rapidly during the first nanosecond and then is discharged slowly. In Fig. (11) a few frames are shown to illustrate the details of the charge transfer at its initial stages. A perfect sink at the end of the storage gate being discharged is formed after about 13 nanoseconds. The large surface potential gradient in the interelectrode regions between the transfer gate and the receiving storage gate sweeps out the minority carriers fast enough to create an almost perfect sink of charge there during all stages of the transfer. In Fig. (12) we have plotted the residual charge under the source storage gate as a percentage of a full bucket for two different initial charges equivalent to about 3 volts and 1 volt with a substrate doping of 8 x  $10^{14}$  donors/cm<sup>3</sup> and  $10^{14}$  donors/cm<sup>3</sup>. Consideration of the transient currents at the ends of the transfer gate and the surface charge and surface potential profiles under the

-25-

Figure 10.

Figure 12.

-28-

gates during the charge transfer show that the charge transfer divides naturally into several distinct stages.

(i) In the first stage, the charge initially confined under the source storage gate spreads to charge up the adjacent transfer gate for a fraction of a nanosecond.

(ii) In the second stage, the charge transfer is limited by the transport of charge across the transfer gate to the next storage gate. The transfer gate acts as a MOS transistor at pinch off with the storage gates as its source and drain. Thus the source and receiving storage gates are capacitors charged and discharged through the transfer channel.

According to the lumped circuit model discussed in Appendix V the decay of the residual charge under the gates is described by

$$\frac{d}{dt} (Q_{St} + Q_{Tr}) = \frac{-\mu C_{Tr} W}{2 \ell_{Tr}} \left[ 2KT(\phi_{mT} - \phi_{mTo}) + (\phi_{mT} - \phi_{mTo})^2 \right]$$

(6a)

$$Q_{St} = w \ell_{St} C_{St} (\phi_{1s} - \phi_{1so}) , \quad (6b)$$

$$Q_{Tr} = \frac{2}{3} W R_{Tr} C_{Tr} (\phi_{mT} - \phi_{mTo}) , \qquad (6c)$$

$$\phi_{mT} \stackrel{\sim}{=} \phi_{1s}$$

;  $\phi_{mT}' = \phi_{mTo}$ , (6d)

where  $Q_{St}$  and  $Q_{Tr}$  are the total charges under the source storage gates and transfer gates.  $\phi_{1s}$  and  $\phi_{1so}$  are the surface potential under the source storage gate with and without surface charge when its yoltage is equal to  $V_1$ .  $\phi_{mT}$  and  $\phi_{mT}$ ' are the surface potential

with charge at the beginning and at the end of the transfer gate respectively, and  $\phi_{mTo}$  is the surface potential under the transfer gate without charge when its voltage is equal to  $V_m$ .  $C_{St}$  and  $C_{Tr}$ are the effective oxide and depletion layer capacity under the storage and transfer gates.  $\ell_{St}$  and  $\ell_{Tr}$  are the lengths of the storage and transfer gates, W is the active channel width, and KT is the thermal voltage. Since in this stage  $(\phi_{mT} - \phi_{mTo}) >> KT$ , then for an initial total charge  $Q_o$  the residual charge under the storage gate decreases hyperbolically and is given by:

$$Q = \frac{Q_0 + Q'}{1 + \left(\frac{t - t_1}{\tau_2}\right)} - Q'$$

, (7)

where Q' =  $w\ell_{St}C_{St}(\phi_{1so} - \phi_{mTo})$ ,  $t_1$  is the time at which the second stage starts and  $\tau_2$  is given by

$$\tau_2 = 2 \frac{{}^{\ell} Tr^{\ell} St}{\mu} \frac{C_{St}}{C_{Tr}} \frac{R}{\frac{(Q_0 + Q')}{W^{\ell} St C_{St}}}, \quad (8)$$

where

$$R = 1 + \frac{2}{3} \frac{{}^{\ell} Tr^{C} Tr}{{}^{\ell} St^{C} St}$$

(9)

When the charge under the storage gate decreases to a small value  $Q_0$ ', the discharge current becomes so small that the electric field in the transitional region between the source storage gate and the next transfer gate can sweep out the carriers fast enough to form an almost perfect sink of charge there. <sup>9</sup> This brings the second stage to an

end at a time t<sub>2</sub> given by

$$t_2 = t_1 + \tau_2 \frac{Q_0 - Q_0'}{Q_0' + Q_1'}$$

For the device parameters given below:

$$\ell_{St} = 13.5 \text{ microns} \qquad \ell_{Tr} = 7 \text{ microns} \\ C_{St} = 3.5 \times 10^{-8} \text{ Farad/cm}^2 \qquad C_{Tr} = 1.45 \times 10^{-8} \text{ Farad/cm}^2 \\ \mu = 200 \text{ cm}^2/\text{sec.volt} \\ \frac{Q'}{W^2 \text{St}^C \text{St}} = 0.8 \text{ volts} \qquad \frac{Q_0'}{W^2 \text{St}^C \text{St}} = 0.48 \text{ volts}$$

(10)

and for a signal charge equivalent to about 3 volts we obtain  $\tau_2 \stackrel{\simeq}{=} 6.9$  nsec and  $t_2 = 13$  nsec. For a signal charge equivalent to about 1 volt, we obtain  $\tau_2 \stackrel{\simeq}{=} 14.6$  nsec and  $t_2 = 5.9$  nsec.

(iii) In the third stage the charge transfer is limited by the transport of charge out of the storage gate with an almost perfect sink at its end. The storage gate can be considered in this stage also as a capacitor discharged through a transfer channel which is the same storage gate. Thus according to the lumped circuit model it can be easily shown (or by expanding the denominator in Eq. (A5-6)) that the residual charge under the storage during the first part of this stage (when  $\frac{Q(t)}{W^2 St^C St} > KT$ ) decreases almost hyperbolically with a time constant  $\tau_3$ . So,

where  $\alpha$  is a constant of the order of unity (about 1.2). During this stage the charge is spread over the entire gate even if fringing fields are appreciable.

(iv) In the last stage of the charge transfer, the self-induced fields become negligible. The residual charge decreases exponentially with a time constant that depends on thermal diffusion and the fringing fields under the storage gate.

For the device we have considered here and for a substrate doping of 8 x 10<sup>14</sup> donors/cm<sup>3</sup> and larger, fringing fields under the storage gate are negligible. For t > t<sub>3</sub> the residual charge under the storage gate decreases exponentially with the thermal diffusion time constant  $\tau_d = \frac{\ell_{St}^2}{2.5 D}$ , where

$Q(t_3) \sim W_{St}C_{St}KT$   $t_3 = t_2 + \frac{\pi}{2}\tau_d$  (13)

For the device we have considered and for substrate doping equal to  $10^{14}$  donors/cm<sup>3</sup>, solutions of the two-dimensional Poisson equation at the end of the charge transfer show a minimum fringing field  $E_{min}$  under the storage gate of about 70 volt/cm and an average value E of about 140 volt/cm. The fringing fields considerably enhance the

-32-

rate of charge transfer. The single carrier transit time across the storage gate  $t_{tr}$  due to fringing fields is given by

$$t_{tr} = \int_{\substack{\text{over storage}\\\text{gate length}}} \frac{dy}{\mu E(y)} = \frac{\ell_{St}}{\mu E} = \frac{\ell_{St}^2}{\mu \Delta \phi} , \quad (14)$$

where  $\vec{E}$  is the average fringing field under the storage gate,  $\Delta \phi$  is equal to  $\vec{E}\ell_{St}$  and is related to the voltage drop across the storage gate due to fringing fields.

Under the influence of the fringing fields, the charge profile under the storage gate starts to drift after a time  $t_3 = t_2 + t_{tr}$  for about one single carrier transit time and then becomes stationary at a position that depends on the minimum fringing field  $E_{min}$ . The residual charge then decreases exponentially with a final decay time constant given approximately by

$$\frac{1}{\tau_{f}} = 4 \left( \frac{\pi^{2} D}{4 \lambda_{St}^{2}} \right) + \frac{\left( \mu E_{min} \right)^{2}}{4 D} \qquad (15)$$

The factor 4 in the second term is due to the large fields at the edges of the gate. For negligible fringing fields this factor takes a value of unity. The exponential decay is due to the diffusion at the tail end of the residual charge packet under the storage gate irrespective of the fringing field profile. Fringing fields alone, without diffusion and self-induced fields, will sweep out the residual charge under the storage gate in a single carrier transit time.

The transition between the hyperbolic regime of the third stage and the exponential regime of the last stage of the charge is rather broad and is best described by Eq. (A5-9) in Appendix V

$$\frac{Q_{st}}{Q_{o}} \approx \frac{\exp\left(-(t-t_{2})/\tau_{f}\right)}{1 + \frac{Q_{o}}{\frac{2}{3}C_{st}^{\ell}St^{W}} \cdot \frac{1}{2KT} \cdot \frac{\tau_{f}}{\tau_{d}} \left[1 - \exp\left(-(t-t_{2})/\tau_{f}\right)\right]}$$

(16)

The dashed lines 10 in Fig. (12) are obtained from Eq. (7) and (16) with the device parameters given in Eq. (10).

(B) Push Clocks: With push clocks the charge is stored under a gate held at  $V_m$  which is the largest clock voltage the MOS structure can tolerate. The charge is transferred to a nearby gate also at  $V_m$  by raising the potential of the gate where the charge has been residing and thus pushing the charge to the next gate.

For optimum operation of the device with two phase push in the complete charge transfer mode, the oxide thickness under the storage and transfer gates should be properly chosen. <sup>11</sup>

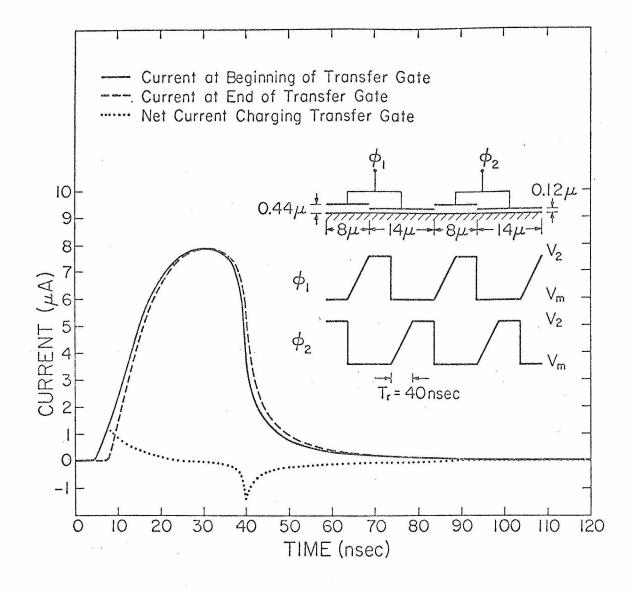

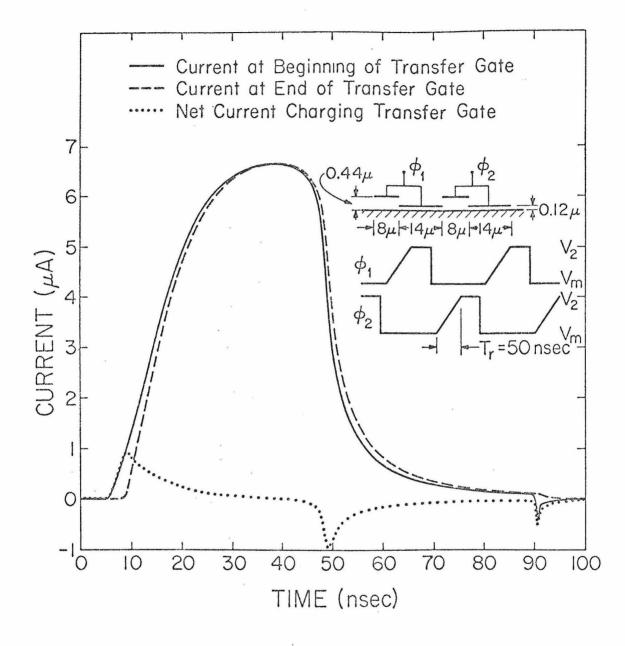

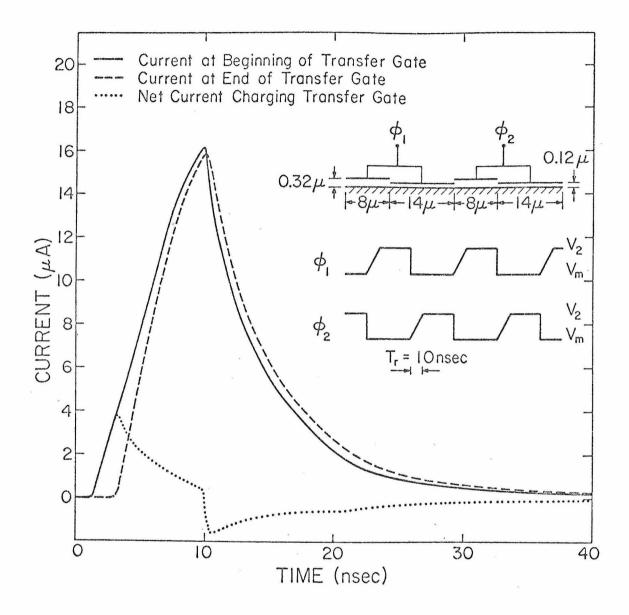

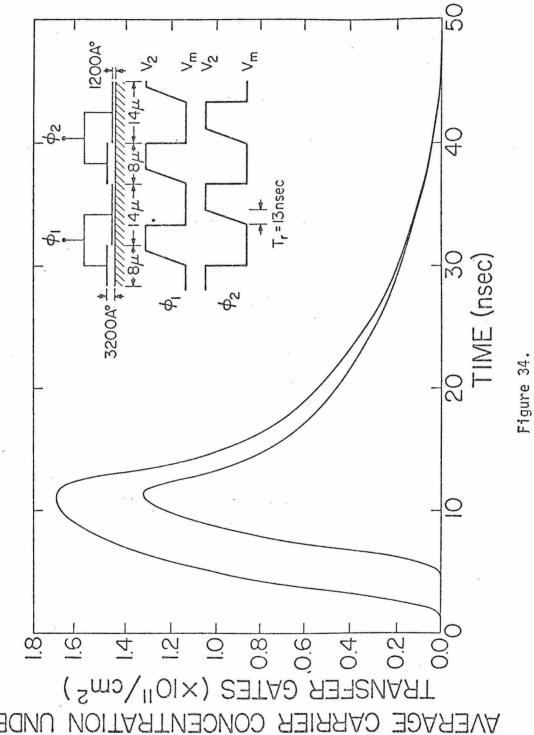

We have simulated numerically the charge transfer characteristics for several devices with various clocking waveforms. In Figs. (13) and (17) we show the transient currents at the beginning and end of the transfer gate, as well as the net current charging the region under the gate. The clock voltages and rise time as well as the oxide thickness under the transfer gates of the device are shown for each case at the top of the figures. Zero time coincides with the instant the clock voltage starts to increase to push the charge and starts the transfer. The currents are zero for the first few nanoseconds until the charge initially confined under the silicon storage gate can flow

to the next gates. This time delay depends on the clock rise time and the initial charge under the storage gate. In Fig. (13) we have plotted the transient currents for a device with 4400  ${\rm \AA}$  oxide under the transfer gate and with a clock rise time equal to 40 nanoseconds and a minimum voltage  $\,V_{_{\rm m}}\,$  equal to -15 volts. The currents at the beginning of the transfer gate starts to increase at about 4.5 nanoseconds reaching a maximum value of about 8 micro amperes, then it drops rapidly to zero at about 40 nanoseconds. The current at the end of the transfer gate has the same waveform but is delayed by 2.5 nanoseconds due to the charge propagation under the gate. From Fig. (13), it is obvious that the transfer gate is charged up rapidly during the first few nanoseconds. After this period, the charge under it remains almost constant. It is discharged at about 40 nanoseconds. In Fig. (14) we have plotted the transient currents for the same device with a similar clocking waveform but the rise time is equal to 50 nanoseconds. In this case the potential of the first phase of the clock  $\phi_1$ , changes from the resting voltage  $V_2$  to the minimum voltage  $\,V_{m}^{}\,$  ending the transfer at about 90 nanoseconds. The currents in this case have almost the same waveform but they drop rapidly to zero at about 49 nanoseconds. The small negative spike at about 90 nanoseconds is due to the flow of the charge in the transfer gate back to the preceding storage gate when the voltage of the first phase of the clock drops to  $\,\,V_{m}^{}\,\,$  ending the transfer.

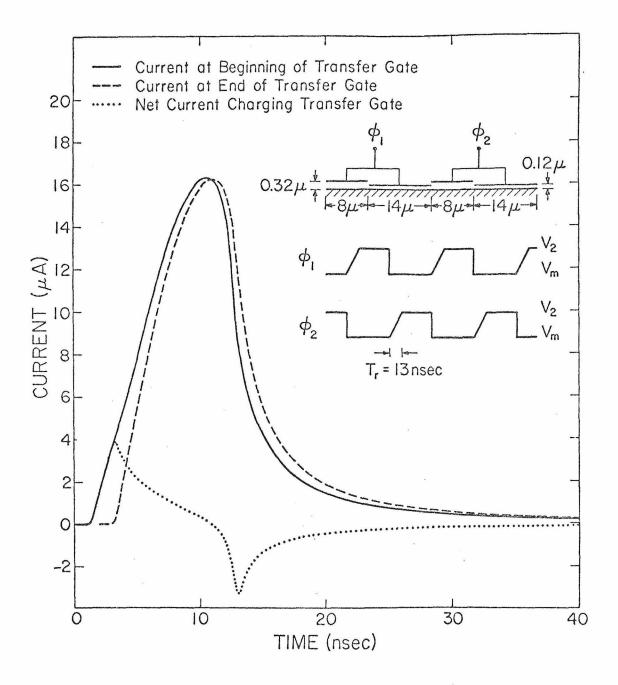

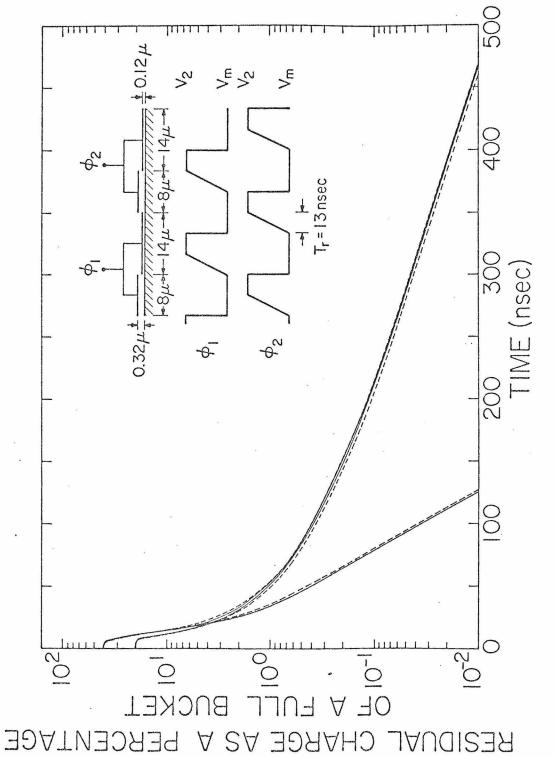

In Figs. (15), (16), and (17) we have plotted the transients current for a device with 3200  $\mathring{A}$  oxide under the transfer gate using a

Figure 13.

Figure 14.

Figure 15.

Figure 16.

Figure 17.

similar clocking waveform but the resting voltage is about -6 volts in the first two cases and -7 volts in the third case and the rise time is 13 nsec, 50 nsec, and 10 nsec, respectively. The current waveforms have essentially the same behavior except that they reach a maximum value of about 16  $\mu$ amp then drop rapidly at 13 nsec in the first case, and in the second case they reach a maximum value of 5.5  $\mu$ amp and drop rapidly at about 42 nsec. In the third case they reach a maximum value of 16  $\mu$ amp and then drop rather slowly at about 10 nsec.

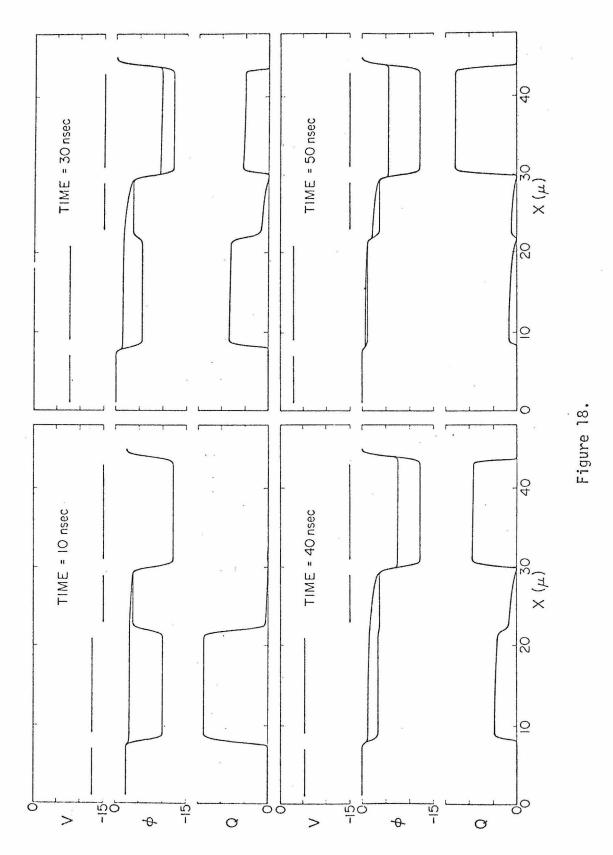

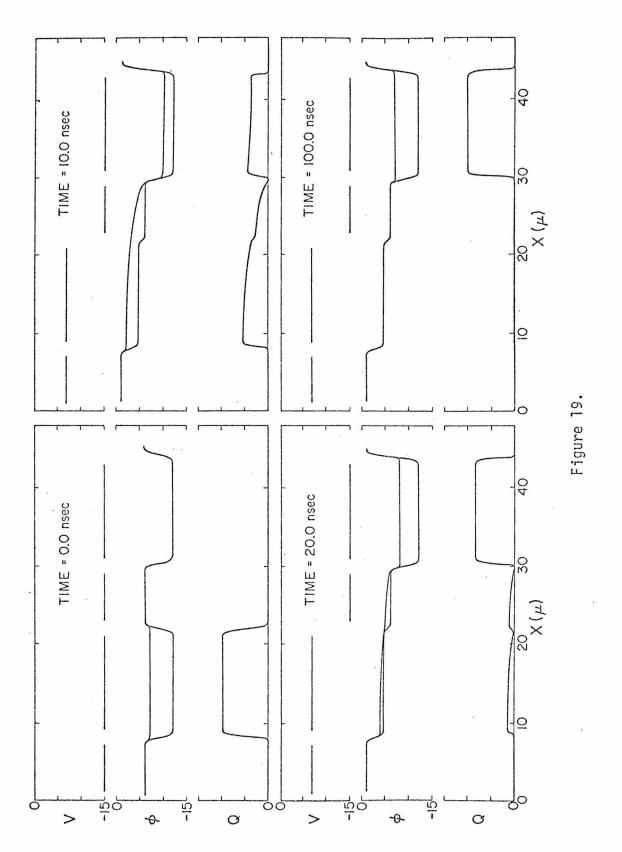

In Figs. (18) and (19), we have plotted a few frames of the surface potential and surface charge density profile for the cases shown in Fig. (14) and (17) respectively. In Fig. (20) and (21) we have plotted the residual charges under the source storage gate versus transfer time.for the cases shown in Fig. (13) and (15) respectively.

From the plots of the transient currents at the end of the transfer gate and the residual charges versus time and the surface charge and surface potential profiles under the gates one can identify several distinct stages of the charge transfer.

(i) In the first stage, the surface potential under the storage gate containing charge increases as the storage gate voltage is increasing, until it becomes equal or less than the surface potential under the next transfer gate by (KT). Then the charge initially confined under the storage gate spreads to charge up the next transfer gate. The time interval of the first part of this stage depends on the amount of initial charge and the clock rise time as given below in Eq. (19).

-41-

-43-

Figure 20.

Figure 21.

(ii) The second stage of the charge transfer is limited by the transport of charge across the transfer gate to the next storage gate. The transfer gate acts as a MOS transistor at pinch off, and the storage gate as its source and drain. For maximum rate of discharge in this stage, the gate voltage should be rising with a rate that keeps the surface potential under the storage gate at a value that does not exceed  $2\phi_F$  to avoid injection of the signal charge into the substrate where  $\phi_F$  is the Fermi potential of the substrate. Since the surface potential under the gate varies almost linearly with the stored charge and the gate voltage, the maximum rate of charge transfer can be achieved by clocking waveforms with ramps of a slope that matches the saturation current of the transfer gate.

According to the lumped circuit model discussed in Appendix V the decay of the residual charge under the storage gate in this stage can be described by the following equations:

$$\frac{d}{dt}(Q_{St} + Q_{Tr}) = - \frac{\mu^{C}Tr^{W}}{2\kappa_{Tr}} \left[ 2\kappa T(\phi_{mT} - \phi_{mTo}) + (\phi_{mT} - \phi_{mTo})^{2} \right] (17a)$$

$$Q_{St} = W \kappa_{St} C_{St}(\phi_{s} - \phi_{so}) , \quad (17b)$$

$$Q_{Tr} = \frac{2}{3} W \epsilon_{Tr} C_{Tr} (\phi_{mT} - \phi_{mTo}) , \quad (17c)$$

$$\phi_{mT} \stackrel{\simeq}{=} \phi_{s}$$

;  $\phi_{mT} \stackrel{\simeq}{=} \phi_{mTo}$ , (17d)

$$\phi_{so} = B_{1s}V + B_{2s}$$

and  $\phi_{mTo} = B_{1T}V_{m} + B_{2T}$ , (17e)

where V and  $V_m$  are the voltages of the first and second phases, driving the source storage gate and transfer gate respectively.  $B_{1s}$ ,  $B_{2s}$ ,  $B_{1T}$ , and  $B_{2T}$  are constants chosen to give the best linear fitting to the relation of the surface potential under the storage and transfer gates to the voltage applied to them. The rest of the notation is similar to that in Eq. (6). For clocking waveforms with ramps or with sufficiently smooth driving functions <sup>12</sup> and for an initial charge  $Q_0$ the residual charge under the storage gate is given by

$$Q = Q'(t) + Q''tanh((t-t_1)/\tau_2)$$

, (18a)

where

$$Q'(t) = We_{St}C_{St}(\phi_{mTo} - \phi_{so}) \qquad , \qquad (18b)$$

$$Q'' = W_{St}C_{St} \sqrt{\frac{2\ell_{Tr}\ell_{St}}{\mu} \frac{C_{St}}{C_{Tr}} \frac{d}{dt} (\phi_{so} - \phi_{mTo})}, \quad (18c)$$

$$\tau_{2} = R \sqrt[4]{\frac{2\ell_{Tr}\ell_{St}}{\mu}} \frac{C_{St}}{C_{Tr}} \frac{1}{\frac{d}{dt}} (\phi_{so} - \phi_{mTo}) , \quad (18d)$$

$$R = 1 + \frac{2}{3} \frac{\ell_{Tr}C_{Tr}}{\ell_{St}C_{St}} . \quad (18e)$$

$t_1$  is the time at which the discharge current I starts to flow. The value of Q'(t) is the minimum initial charge under the source storage gate which causes the discharge current I to start at time t. Hence, for a given initial charge  $Q_0$ ,  $t_1$  is given by

$$Q'(t_1) = Q_0$$

(19)

It follows directly from Eqs.(18) that for a ramp clocking waveform

the minimum rise time  $T_r|_{min}$  of the clocking voltage to prevent injection of the signal charge in the substrate is given by

$$T_{r}|_{min} = \frac{2\ell_{Tr}\ell_{St}}{\mu} \frac{C_{St}}{C_{Tr}} \frac{B_{1s}(V_{2} - V_{m})}{(2\phi_{F} - \phi_{mAo})^{2}} , \quad (20)$$

where  $V_2$  and  $V_m$  are the resting and minimum voltages of the clock. For  $(t-t_1) > \tau_2$  the residual charge under the storage gate decreases according to the waveform of V(t).

The parameters of the device used in the numerical simulation are given below:

$$\begin{array}{ll} l_{\text{St}} = 13.5 \text{ microns}, & l_{\text{Tr}} = 7 \text{ microns}, \\ c_{\text{St}} = 3.14 \times 10^{-8} \text{F/cm}^2, & B_{1s} = 0.9162, \\ v_{\text{m}} = -15 \text{ volts} & \mu = 200 \text{ cm}^2/\text{volt sec}, \end{array} \right\}$$

(21)

If the oxide thickness under the transfer gate is 3200 Å and  $V_2 = -6$  volts and  $T_r = 13$  nsec, then  $C_{Tr} = 1.45 \times 10^{-8} \text{F/cm}^2$ ,  $T_r|_{\text{min}} \cong 5.5$  nsec, and  $\tau_2 \cong 6.5$  nsec. If the oxide thickness under the transfer gate is 4400Å and  $V_2 = -3$  volts and  $T_r = 40$  nsec then  $C_{Tr} = 1.32 \times 10^{-8} \text{F/cm}^2$ ,  $T_r|_{\text{min}} \cong 21$  nsec and  $\tau_2 = 11.5$  nsec.

(iii) In the third stage the clock voltages are nonchanging and the charge transfer is limited by the transport of charge out of the storage gate with an almost perfect sink at its end. The storage gate in this stage is discharged through itself as in the case of the drop clock. The residual charge under the storage gate Q(t) decreases during the first part of this stage hyperbolically with a time constant  $\tau_3$ .

$$Q(t) = \frac{Q_0'}{1 + \frac{t - t_2}{\tau_3}} \qquad t > t_2 \qquad , \quad (22)$$

where  $\tau_3 = \frac{\frac{\ell_S t}{2}}{\alpha \frac{Q_0'}{C_S t^{\ell_S t} W^{\mu}}} \quad and \quad Q_0' \quad is the total charge under the source$

storage gate when the perfect sink at its end is formed at time  $t_2$ .  $t_2$  is approximately <sup>13</sup> equal to  $T_r$  and  $Q_o'$  is obtained from Eq. (18) with  $t = t_2$ .

(iv) In the last stage the residual charge decreases exponentially with a time constant that depends on thermal diffusion and fringing fields under the storage gate as discussed above in Eqs. (13), (14), (15), and (16).

3.2.2 Incomplete Charge Transfer Mode:

In the incomplete (or residual) charge transfer mode, a bias charge is deliberately retained under the storage gates at each transfer. This can be achieved by controlling the resting surface potential under the storage gate relative to that under the next transfer gate at the end of the charge transfer process. In the two phase clocking scheme, for a given substrate doping and minimum voltage  $V_m$  the oxide thickness under the storage and transfer gates should also be properly chosen for optimum device operation in this mode.

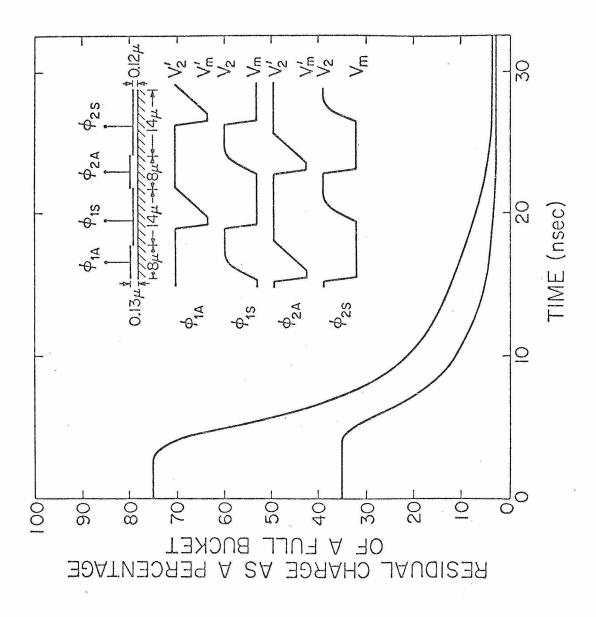

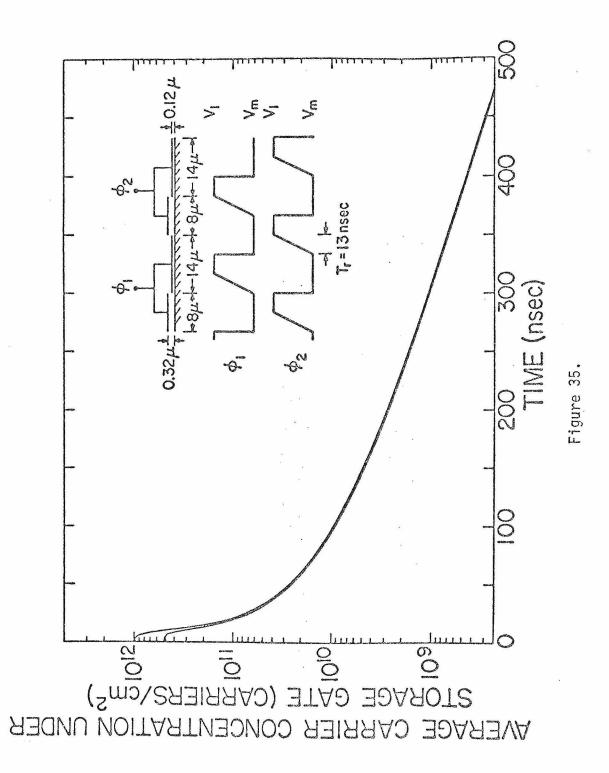

We have simulated numerically the charge transfer for the device shown at the top of Fig. (22) clocked by a two-phase push clock in the incomplete charge transfer mode with a bias charge equivalent to

about one volt. In Fig. (22) we have plotted the transient currents at the beginning and end of the transfer gate and the net current charging the region under the gate. The current at the beginning of the transfer gate starts to increase at about 4.5 nsec reaching a maximum value of about 8 uamp when the clock voltage stops, then the current decreases slowly. The current at the end of the gate has a similar waveform except it is delayed by about 2.5 nsec due to the charge propagation under the gate. We have plotted in Fig. (23) the residual charge under the source storage gate as a fraction of a full bucket versus transfer time for two different initial charges 0.6 and 0.4 of a full bucket. From the plots of the currents at the ends of the gates and the residual charges versus time and the surface charge and surface potential profiles under the gates one can easily identify distinct stages of the charge transfer. The first two stages are similar to the first two stages of the two-phase push clock case described above. The third stage starts when the clock voltage stops at time  $t_2 = T_r$  with a residual charge under the source storage gate equal to Q.'. The charge transfer in the first part of this stage  $\left(\frac{Q(t) - Q'}{W_{LSt}^{C}St} > 2KT\right)$ is similar to the charge transfer in the second stage of the twophase drop clock discussed above in Eqs. (7), (8), and (9). The residual charge is thus given by

$$Q(t) = \frac{Q_0' - Q'}{1 + \frac{(t - t_2)}{\tau_3}} + Q' , \quad (23a)$$

where

Figure 22.

$$\tau_{3} = \frac{2^{\ell} \text{St}^{\ell} \text{Tr}}{\mu} \frac{C_{\text{St}}}{C_{\text{Tr}}} \frac{R}{\frac{Q_{0} - Q^{\dagger}}{WC_{\text{St}}^{\ell} \text{St}}}$$

(23b)

Q' is the bias charge and is equal to  $Wl_{St}C_{St}(\phi_{mTo} - \phi_{1so})$ . This stage ends at time  $t_3$  when

$$Q(t_3) - Q' \simeq WC_{St} t_{St} \cdot 2KT \longrightarrow t_3 = t_2 + \frac{\ell_S t_T r}{D} \frac{C_{St}}{C_T r} \cdot R.$$

(24)

In the last stage of the charge transfer, the surface potential under the storage gate drops below that under the transfer gate. However, the discharge current still continues to flow due to the thermal emission of the carriers under the storage gate over the potential barrier. The mobile charge under the transfer gate also becomes so small that thermal diffusion becomes dominant. Fringing fields under the transfer gate are usually small because the surface potential under the transfer gate and the preceding storage gate are almost equal. The residual charge under the storage gate in this stage decreases logarithmically with time. Using the lumped circuit described in Appendix V the charge transfer in the incomplete charge transfer mode is described by the following equations:

$$\frac{d}{dt} (Q_{St} + Q_{Tr}) = -\frac{\mu C_{Tr} W}{2 \kappa_{Tr}} \left[ 2KT(\phi_{mT} - \phi_{mTo}) + (\phi_{mT} - \phi_{mTo})^{2} \right] (25a)$$

$$Q_{St} = W \kappa_{St} C_{St}(\phi_{1s} - \phi_{1so})$$

$$Q_{Tr} = \frac{2}{3} W \kappa_{Tr} C_{Tr}(\phi_{mT} - \phi_{mTo}) \frac{\left[(\phi_{mT} - \phi_{mTo}) + \frac{3}{2} KT\right]}{\left[(\phi_{mT} - \phi_{mTo}) + 2KT\right]} (25c)$$

$$C_{Tr}(\phi_{mT} - \phi_{mTo}) = C_{St}(\phi_{1s} - \phi_{1so}) \exp -(\phi_{mT} - \phi_{1s})/KT); \phi_{mT}' = \phi_{mTo}$$

(25d)

$$\left[1 + \frac{KT}{\phi_{mT} - \phi_{mTo}}\right] \cdot \frac{d}{dt}(\phi_{mT} - \phi_{mTo}) = \left[1 + \frac{KT}{\phi_{1s} - \phi_{1so}}\right] + \frac{d}{dt}(\phi_{1so} - \phi_{mTo}) + \frac{d}{dt}(\phi_{1so} - \phi_{mTo})$$

(25e)

Assuming a sufficiently large bias charge (Q' >> KT  $W\ell_{St}C_{St}$ ) and taking  $(\phi_{mT} + KT)(\phi_{mT} + 3KT) \cong (\phi_{mT} + 2KT)^2$ , then the above equations reduce to

$$-\frac{\mu C_{Tr}W}{2 Tr} \left[ (\phi_{mT} - \phi_{mTo})^{2} + 2KT(\phi_{mT} - \phi_{mTo}) \right] = \left[ W \ell_{St} C_{St} \left( 1 + \frac{KT}{\phi_{mT} - \phi_{mTo}} \right) + \frac{2}{3} W \ell_{Tr} C_{Tr} \right] \frac{d}{dt} (\phi_{mT} - \phi_{mTo}) .$$

(26)

For  $(\phi_{mT} - \phi_{mTo})$  < KT the residual charge under the source storage gate is given by  $^{14}$

$$Q(t) = Q' - KT We_{St}C_{St} en \left[ 1 + (t-t_3)/\tau_4 \right]$$

(27a)

where

$$\tau_4 = \frac{\ell_{\rm Tr} \ell_{\rm St}}{2D} \frac{C_{\rm St}}{C_{\rm Tr}}$$

(27b)

If

$$t > t_4 = t_3 + \tau_4 \exp(Q'/C_{St} W_{St} KT)$$

, Eq. (25) reduces to

$$Q(t) \sim C_{St} W_{St} KT \exp -((t-t_4)/\tau_5)$$

, (28a)

where

$$\tau_5 = \frac{\ell_{\text{Tr}}\ell_{\text{St}}}{D} \exp\left( \left( \phi_{\text{mTo}} - \phi_{1\text{so}} \right) / \text{KT} \right) \qquad . \quad (28b)$$

However for a bias charge equivalent to one volt  $t_4$  and  $\tau_5$  are larger than the interface storage time<sup>(19)</sup> of the best thermally grown oxide and hence that stage will never be reached practically. If fringing fields under the transfer gate are appreciable for a closer spacing device or a lower substrate doping, then the above relations still hold except  $\frac{D}{\ell_{Tr}}$  is replaced by  $\left(\frac{D}{\ell_{Tr}} + \mu \vec{E}\right)$  where  $\vec{E}$  is the average fringing field under the transfer gate.

When a static two-phase clock is used to operate the device in the incomplete charge transfer, the two first stages of the charge transfer are similar to the two first stages of the static drop clock in the complete charge transfer mode. However in the last stage, the residual charge in the incomplete charge transfer mode decreases logarithmically according to Eq. (27).

## 3.3 Four-Phase Clocking Scheme

In the overlapped gates charge coupled devices, four-phases may be used to control the storage and transfer of charge along the interface. Since each gate electrode is driven by a separate phase, more flexibility in operating the device is expected. With four clocking phases the polysilicon electrodes can be used to store the signal charge and the aluminum electrodes to control the transfer and storage process, or both the polysilicon and aluminum gates can be used as storage sites. The latter method requires four transfers per bit and the aluminum electrode should have the same areas as the polysilicon electrodes, but the former method requires two transfers per bit and the aluminum electrodes can have a smaller area. We will consider the first method as it requires less area per bit and results in less signal degradation due to incomplete free charge transfer.

3.3.1 Complete Charge Transfer Mode:

(A) Drop Clock. With the four-phase drop clock, the minimum and resting voltages ( $V_m$ ' and  $V_2$ ') of the clock phases driving the transfer gates can be independently controlled whatever is the oxide thickness under the transfer electrodes for operation in the complete charge transfer mode. The stages of the charge transfer process are similar to the two-phase drop clocks. So increasing the complexity of the clock from two-phases to four-phases with drop clock does not improve the performance of the device.

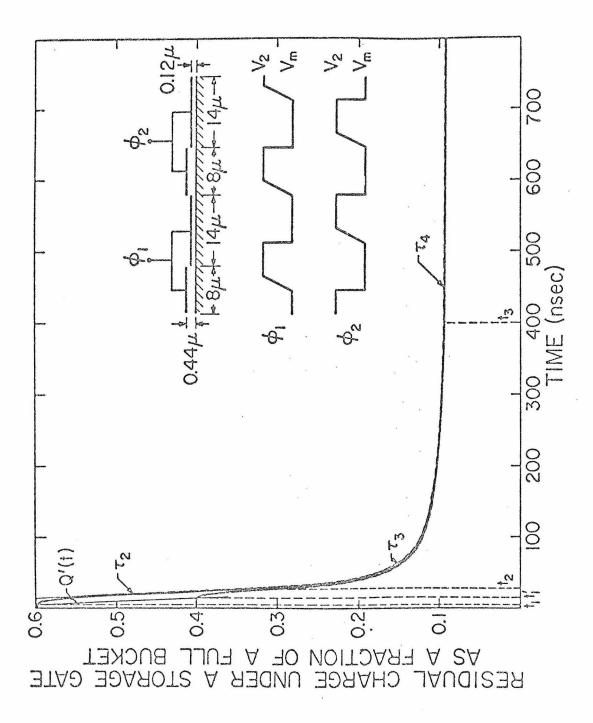

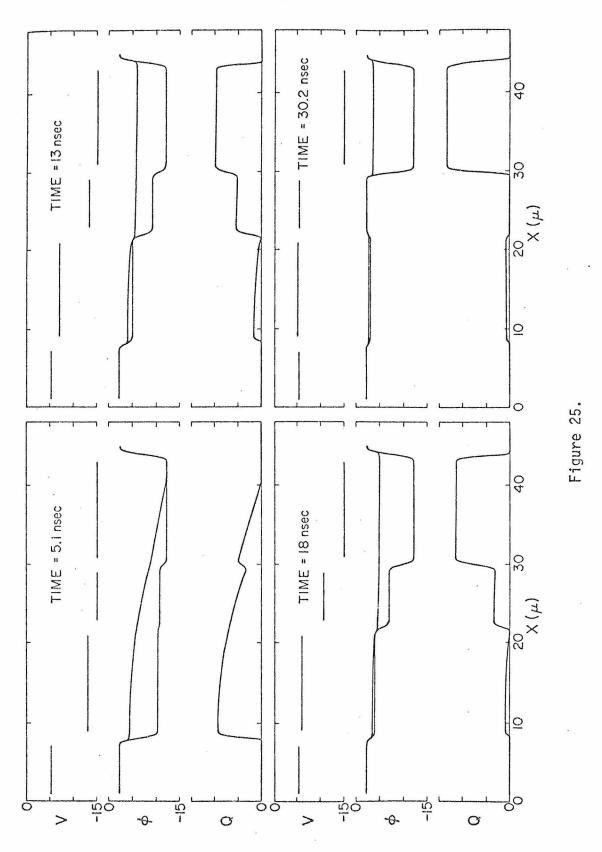

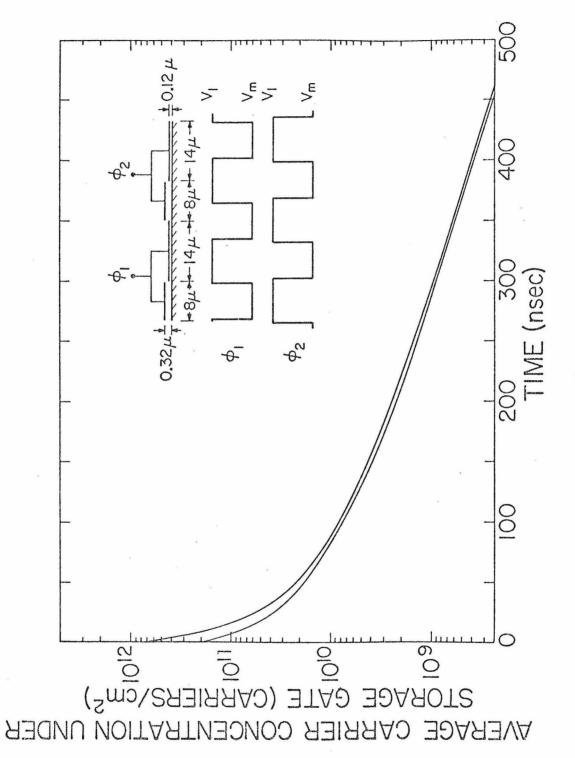

(B) Push Clock. Push clocks take full advantage of the more flexible control of the storage and transfer of charge with the four-phases of the clock. At the top of Fig. (24), we show the device dimensions and the clocking waveforms we have used in our computer simulation of the four-phase push clock. In Fig. (25) we have plotted the surface potential and surface charge density profiles during the charge transfer process.

-56-

Since with four clocking phases the preceding transfer gate can be turned off by the resting voltage  $V_2'$ , the maximum signal charge that can be stored under the storage gate with its voltage equal to  $V_{\rm m}$  can be almost a full bucket. In the two-phase clocking scheme, each set of transfer and storage gates is driven by the same phase of the clock so the preceding transfer gate is turned on when the storage gate is turned Hence the maximum charge that can be stored with four-phase clock on. is larger than with two-phase clock for the same clock voltage amplitude. To transfer the charge for example, from under the first storage gate to the second one,  $\phi_{\text{2A}}$  and  $\phi_{\text{2S}}$  drops to  $V_{\text{m}}$  to turn on heavily the second transfer and storage gates. Then  $\phi_{1S}$  increases to push the charge from under the first storage gate to the adjacent gates. Then  $\phi_{2A}$  increases to push the charge to the next storage gate. As  $\phi_{2A}$ reaches the resting voltage,  $V_2$ ', the charge transfer ends and some of the residual charge under the transfer gate spills back to the preceding storage gate. The rate of rise of  $\phi_{2A}$  should be sufficiently slow so that the amount of charge under the transfer gate which spills back to the preceding storage gate is small. Therefore, the rise time  $T_r$  of the transfer gate clock should increase with the increase of the clock bit time.

In Fig. (24) we have plotted the transient currents at the beginning and end of the transfer gate. The current at the beginning of the transfer gate increases very rapidly with a rate that depends on the fall time of the clock. It reaches a maximum value of about 70  $\mu$ amps, at 5 nsec when the transfer gate is completely on. Then it drops

Figure 24.

-59-

rapidly reversing its sign when some of the residual charge under the transfer gate spills back to the preceding storage gate. The current at the end of the transfer gate has a similar waveform except it is delayed by 1 nsec due to charge propagation across the transfer gate. The second small peak at 10 nsec occurs when the transfer gate voltage starts to increase to push the charge to the next storage gate. In Fig. (26) we have plotted the residual charge under the storage gate for two different initial charges 0.75 and 0.35 of a full bucket. With the four-phase push clock, more charge can be stored and much faster rates of charge transfer in the first stages of the transfer process can be achieved since the transfer gates can be controlled independently. However, in the last stages of the charge transfer process, the residual charge decreases exponentially with a time constant that depends on thermal diffusion and fringing fields as with the two-phase clocks.

3.3.2 Incomplete Charge Transfer Mode:

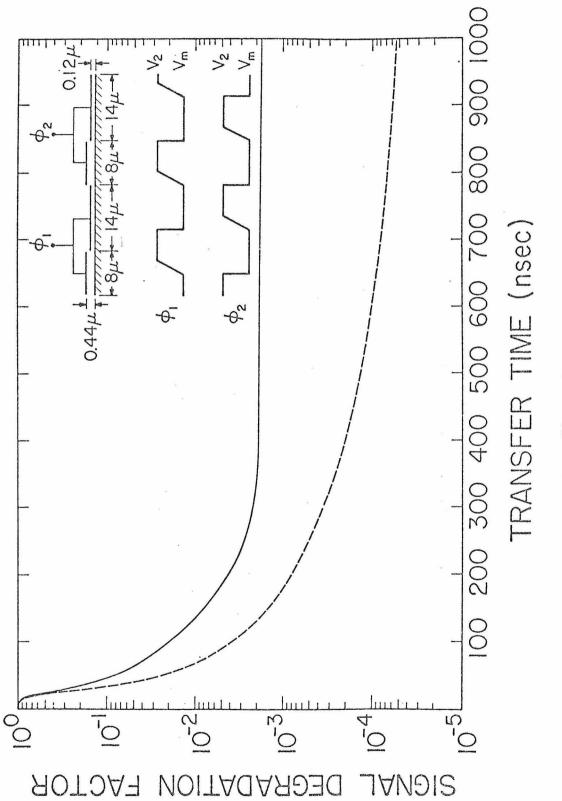

In the incomplete charge transfer mode, a bias charge is left under the storage gate at each transfer. Whether push or drop four-phase clocks are used, the first stages of the charge transfer will be similar to those in the complete charge transfer mode. But in the last stage of the charge transfer, the residual charge under the storage gate does not decrease exponentially as in the complete charge transfer mode, but it decreases logarithmically with a much slower rate.

## 3.4 Signal Degradation

Due to the incomplete transfer of charge from one storage site to

-60-

Figure 26.

-62-

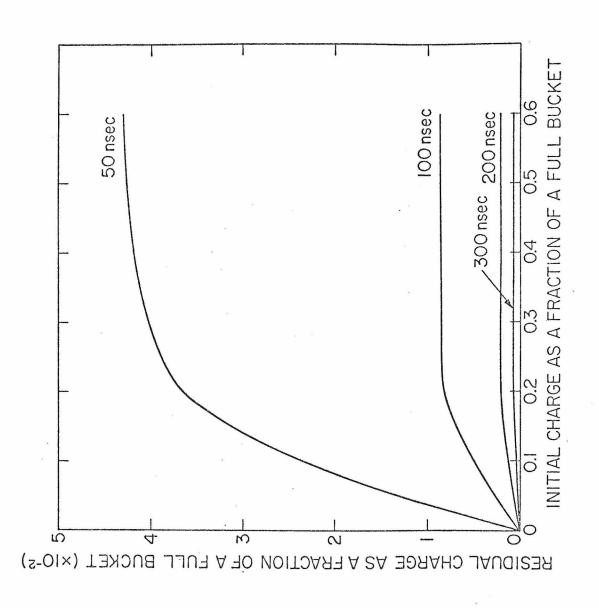

another the signal stored and transferred along the device will be degraded. <sup>15</sup> The charge transfer characteristics presented above show that for any finite transfer time there is a finite residual charge under the original storage gate. In Fig. (27) we have plotted the residual charge Q, due to incomplete free charge transfer versus the initial charge Q; at various transfer times. The saturation characteristics of these plots are due to the strong nonlinearity inherent in the transport dynamics. The plots of the net residual charge due to trapping in interface states versus the initial charge show also the same saturation shape as will be shown in Chapter 4. For larger charge the residual charge tends to be less dependent on the initial charge. This saturation characteristic indicates that the signal degradation due to incomplete free charge transfer and trapping in interface states can be considerably reduced by using a circulating background charge or a "fat zero" to represent the zero signal.

The net charge loss from a charge packet in one transfer event is the difference between the residual charge it lost in the original storage site and the residual charge it gained from the preceding charge packet. From Fig. (27), it is clear that for digital signals the worst bit pattern is when a "one bit" follows a long series of "zero bits" or when a "zero bit" follows a long series of "one bits". Let  $\Delta Q$  be the difference in the residual charge due to a "one bit" and a "zero bit" resulting from incomplete free charge transfer and trapping in the interface states. If  $Q_{in}^{(1)}$  and  $Q_{in}^{(0)}$  are the input charges which represent the one and zero bit, then the worst case output charges

Figure 27.

after n transfer are given approximately by

$$Q_{out}^{(1)} = Q_{in}^{(1)} - n\Delta Q$$

,

$Q_{out}^{(0)} = Q_{in}^{(0)} - n\Delta Q$ , (29)

and the output signal is given by

$$Q_{out}^{(1)} - Q_{out}^{(0)} = Q_{in}^{(1)} - Q_{in}^{(0)} - 2 n\Delta Q$$

(30)

Due to the saturation characteristics in Fig. (27), there exists an optimum fat zero charge  $Q_{in}$  which results in maximum opt output signal and is defined by

$$2n \frac{d}{dQ_{in}}(0) (\Delta Q) + 1 = 0$$

(31)

The shape of the saturation characteristics in Fig. (27) indicates that the optimum fat zero charge  $Q_{in}^{(0)}|_{opt}^{(0)}$  increases by increasing the clock frequency and the number of stages n of the charge coupled register and is independent of the size of the one bit.

The signal degradation due to incomplete charge transfer is best described by the signal degradation factor  $\epsilon$  which is defined by

$$\varepsilon = \frac{\Delta Q_r}{\Delta Q_i} \qquad (32)$$

where  $\Delta Q_r$  is the difference in the residual charge  $Q_r$  due to a difference  $\Delta Q_i$  in the initial charge  $Q_i$ . For small  $\Delta Q_i$ ,  $\epsilon$  tends to its small signal value  $\alpha$ , where

$$\alpha = \frac{dQ_r}{dQ_i}$$

(33)

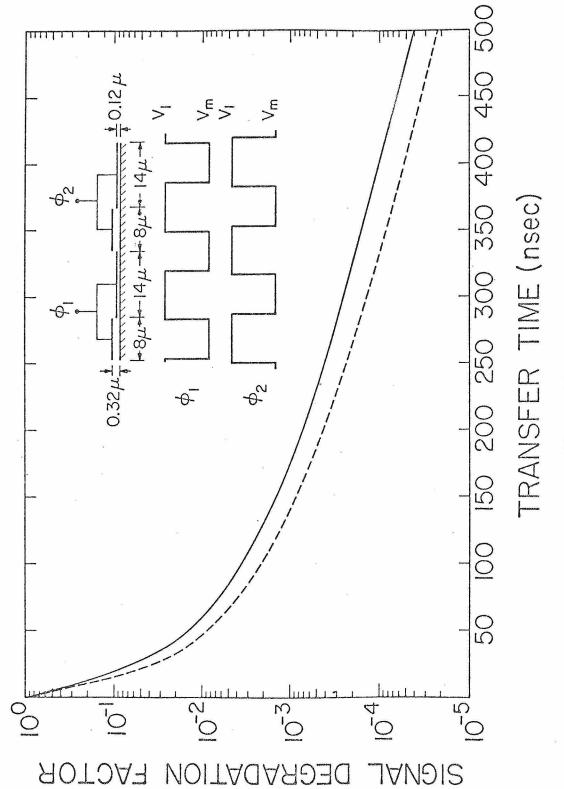

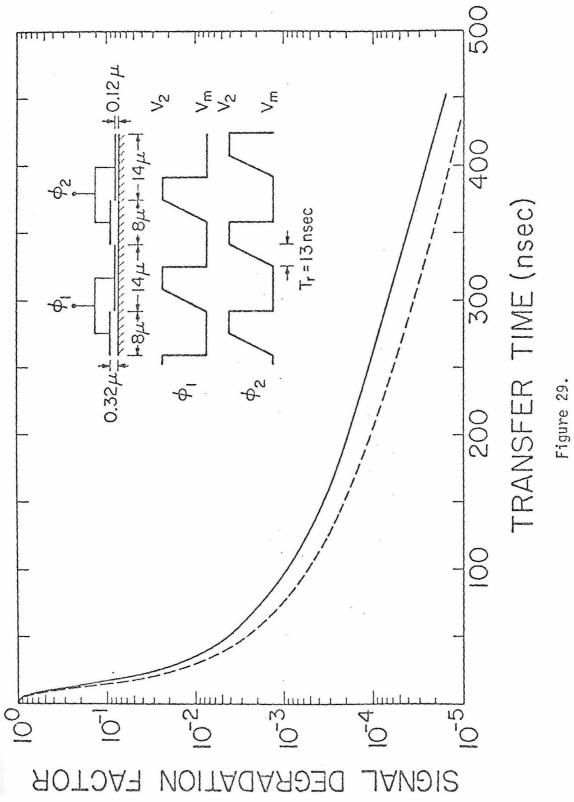

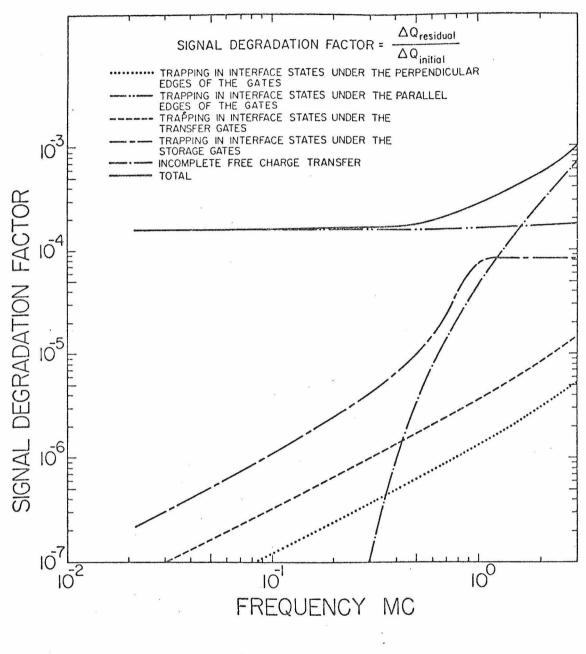

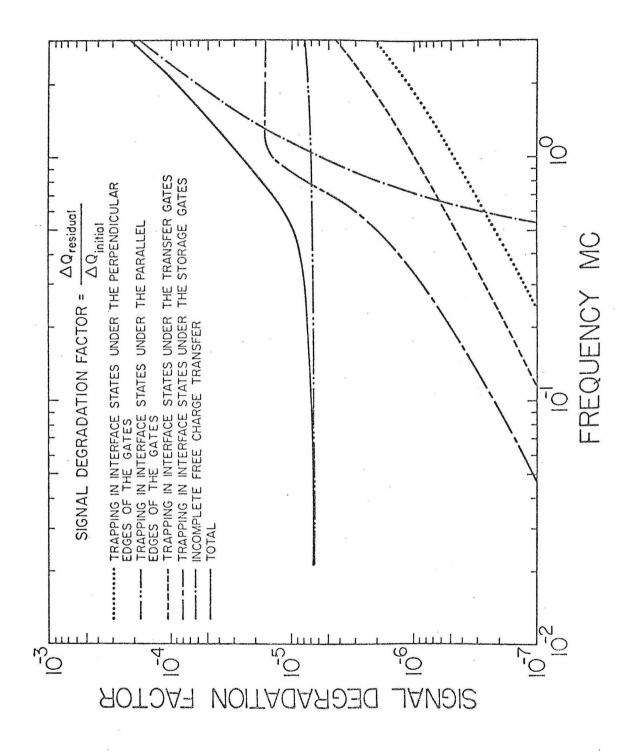

In Figs. (28), (39), and (30) we have plotted the signal degradation factor due to incomplete free charge transfer versus transfer time for the drop and push two-phase clock in the complete charge transfer mode and for the two-phase push clock in the incomplete (or residual) charge transfer mode respectively. The signal degradation of the incomplete free charge transfer is due to an intrinsic transfer rate and due to the modulation of the device parameters by the signal charge being transferred. The intrinsic transfer rate is due to the finite carrier mobility and finite transfer time. The modulation effects are due to the dependence of the effective lengths of the gates, the effective capacitances per unit area and fringing fields under the storage and transfer gates on the signal charge being transferred. In Fig. (28), (29), and (30) the full line curves are the signal degradation due to the intrinsic transfer rate and the device parameters modulations, and the dashed line curves are the signal degradation due to the intrinsic transfer rate only. In the complete charge transfer mode (or CCD mode) the signal degradation due to incomplete free charge transfer decreases exponentially with time. But in the incomplete transfer mode (or bucket brigade mode), the signal degradation tends to a constant value at low clock frequency due to transfer gate length modulation and barrier height modulation (which modulates the residual or bias charge under the storage gates).

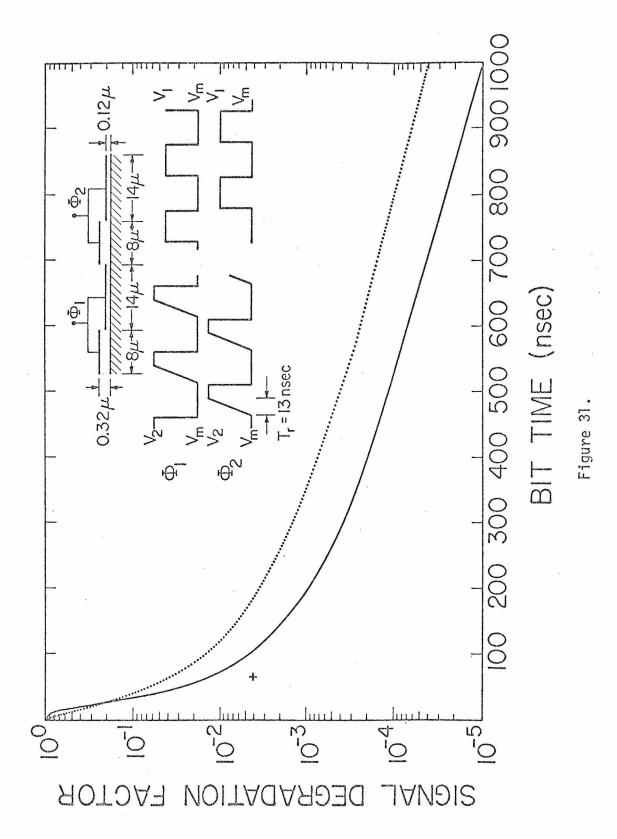

In order to compare the performance of charge coupled devices with Push and drop clocks, we have plotted in Fig. (31) the signal degradation versus bit time for a two-phase push and drop clock. The device

Figure 28.

dimensions and the clocking waveforms are shown at the top of Fig. (31). We have chosen a suitable background charge q\_ to represent a "fat zero" and a larger charge  $q_s$  to represent the signal or one bit, as would be used for example to represent the zero and one bit in a digital serial memory. It is clear that the transfer efficiency is higher for the push clock. The improvement in transfer efficiency is due mainly to an important property of push clocks: The differences in the charge transfer characteristics and the mobile charge profiles under the CCD gates depending on whether a large or small charge is being transferred are minimized with push clocks. With a push clock the transfer of charge does not start until the surface potential under the initial storage gate is larger than that under the next transfer gate. This condition occurs earlier or later in the transfer cycle depending on whether more or less charge was originally stored. Thus provided the zero signal or zero bit is represented by a background charge, the charge profiles under the gates during the remainder of the transfer cycle are almost independent of when the actual movement of charge began: That is they are independent of the initial charge to be transferred. Hence the residual chargesafter each transfer with push clocks are almost independent of the initial charges. Therefore the signal degradation due to incomplete free charge transfer at high frequency is less when the device is operated with push clocks than when it is operated with drop clocks. 16 In Chapter 5, we will show that the signal degradation due to trapping in the interface states, which is dominant at low and moderate clock frequency, is also reduced by using push clocks instead of drop clocks.

In Fig. (31) we show also the signal degradation for the fourphase push described in section (3.3.1 B). It is clear that increasing the clocking scheme complexity from two-phase to four-phase improves the performance of the device at high frequency. This is because increasing the clocking scheme complexity allows a better control of the storage and transfer of the signal charge. This results also in a larger signal dynamic range and larger signal to noise ratio.

#### Chapter 4

## TRAPPING IN THE INTERFACE STATES

The incomplete charge transfer due to trapping in interface states at the semiconductor-oxide interface imposes limitations on the performance of charge coupled devices at moderate and low frequencies, where the incomplete free charge transfer is very small as shown in the previous chapter. In this chapter we use a simple and accurate model to study the incomplete charge transfer due to trapping in interface states and show its dependence on frequency, device parameters, dimensions, and clocking waveforms.

# 4.1 Incomplete Charge Transfer Due to Trapping in Interface States

If a voltage is applied to one of the storage electrodes of the charge couple device, a potential well is created at the interface, where signal charge can be stored. Some of this charge will be trapped in interface states. During the first stages of the transfer of charge to the next storage site, some carriers will also be trapped in interface states under the transfer gates. In the last stages of the transfer process, the relatively large fringing fields under the transfer gates sweep out the mobile carriers very rapidly and the interface states then start to emit the captured carriers. According to the Shockley-Read-Hall rate equations,  $^{(21)}$  the emission time constant  $\tau_e$  of the interface states varies exponentially with their energy level relative to the band edge. If the emission time constant of the

time, then most of the trapped carriers in these states are emitted and can join the main packet. Interface states with an emission time constant equal or larger than the transfer time will emit only a fraction of the trapped carriers. Since the storage gate is longer and has a thinner oxide than the transfer gate, the fringing fields under it are much smaller than under the transfer gate. The residual charge under the storage gate, in the last stages of the charge transfer process, decreases exponentially with a time constant that depends on thermal diffusion and the small fringing fields. Interface states continue to capture carriers from the residual signal charge until the residual charge becomes so small that emission from the traps becomes dominant. The non-emitted trapped carriers under the storage gate and the transfer gate are thus lost from the signal charge and will be emitted in the succeeding packets. If the next signal samples do not contain any charge, the interface states continue to emit the captured carriers until a signal sample containing charge passes. Then the empty interface state fill by capturing carriers from that signal sample. After its transfer, the trapped carriers are emitted and so on.

The charge captured by interface states from a large charge packet passing through the device is larger than the charge emitted into that packet, unless it has been preceded by an equal or larger charge packet. But the charge captured by interface states from a small charge packet passing through the device is smaller than the charge emitted into that packet, unless it has been preceded by an equal or smaller charge packet. Thus the interaction of the signal charge with the interface states results in incomplete transfer of charge from one storage site to another and imposes limitations on the performance of the overlapping gates charge coupled devices.

The signal degradation due to the trapping of carriers in the interface states can be considerably reduced by using the fat zero scheme. In this scheme the zero signal is represented by a small background charge or "fat zero", so that charge packets are always flowing across the device. Hence the interface states under the storage and transfer electrodes are filled every cycle. The net charge trapped from a signal charge packet will then be the difference between the captured charge it lost at each transfer and the charge emitted into that packet, by the interface states under the storage and transfer gates, which was trapped from the preceding charge packets. Since for a sufficiently large fat zero charge the capture time constant of the interface state is very small (as discussed below) the interface states will be almost completely filled during each cycle and similar net trapping occurs during every cycle. The incomplete transfer due to trapping in interface states is consequently reduced by orders of magnitude.

### 4.2 Model and Approximations

The interface states at the semiconductor-oxide interface are characterized by their density  $N_{ss}(E)$  and capture cross-section  $\sigma_h(E)$ . The capture and release of charge from these states is described by the Shockley-Read-Hall equation. <sup>(21)</sup> Assuming a p-channel <sup>17</sup> device and assuming that the interface is always kept under depletion to exclude the majority carrier and suppress any recombination between the trapped holes and electrons, the rate equation describing the occupation of the interface states at an energy E above the valence band is given by

$$\frac{dn_{ss}}{dt} = K_1 (N_{ss} - n_{ss}) p - K_2 n_{ss} \exp(-E/KT)$$

(34a)

$$K_{l} = \sigma_{h} V_{th} / d$$

(34b)

$$K_2 = \sigma_h V_{th} N_v \qquad , \qquad (34c)$$

where  $N_{ss}$  is the interface state density (states/cm<sup>2</sup> - eV),  $n_{ss}$  is the density of filled interface (states/cm<sup>2</sup> - eV), and p is the density per unit area of the mobile holes in the valence band at the interface.  $\sigma_h$  is the trap capture cross-section for holes and  $V_{th}$  is the average thermal velocity of the mobile carriers. d is the average thickness of the inversion layer at the interface,  $N_v$  is the density of states in the valence band, and KT is the electron-volt equivalent of temperature.