## An Ultra-Low-Energy, Variation-Tolerant FPGA Architecture Using Component-Specific Mapping

Thesis by

Nikil Mehta

In Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

California Institute of Technology Pasadena, California

2013 (Defended August 31, 2012)

© 2013 Nikil Mehta All Rights Reserved

## Abstract

As feature sizes scale toward atomic limits, parameter variation continues to increase, leading to increased margins in both delay and energy. Parameter variation both slows down devices and causes devices to fail. For applications that require high performance, the possibility of very slow devices on critical paths forces designers to reduce clock speed in order to meet timing. For an important and emerging class of applications that target energy-minimal operation at the cost of delay, the impact of variation-induced defects at very low voltages mandates the sizing up of transistors and operation at higher voltages to maintain functionality.

With post-fabrication configurability, FPGAs have the opportunity to self-measure the impact of variation, determining the speed and functionality of each individual resource. Given that information, a delay-aware router can use slow devices on non-critical paths, fast devices on critical paths, and avoid known defects. By mapping each component individually and customizing designs to a component's unique physical characteristics, we demonstrate that we can eliminate delay margins and reduce energy margins caused by variation.

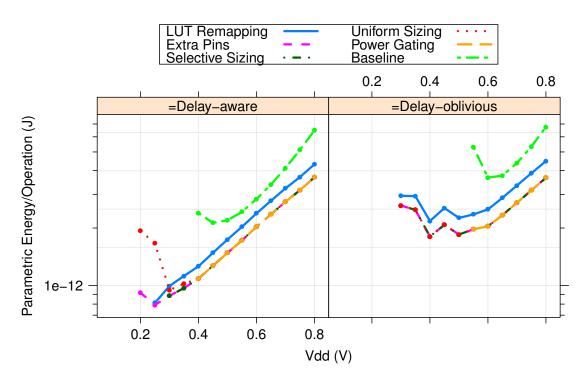

To quantify the potential benefit we might gain from component-specific mapping, we first measure the margins associated with parameter variation, and then focus primarily on the energy benefits of FPGA delay-aware routing over a wide range of predictive technologies (45 nm–12 nm) for the Toronto20 benchmark set. We show that relative to delay-oblivious routing, delay-aware routing without any significant optimizations can reduce minimum energy/operation by  $1.72 \times$  at 22 nm. We demonstrate how to construct an FPGA architecture specifically tailored to further increase the minimum energy savings of component-specific mapping by using the following techniques: power gating, gate sizing, interconnect sparing, and LUT remapping. With all optimizations considered we show a minimum energy/operation savings of  $2.66 \times$  at 22 nm, or  $1.68-2.95 \times$  when considered across 45–12 nm. As there are many challenges to measuring resource delays and mapping per chip, we discuss methods that may make component-specific mapping more practical. We demonstrate that a simpler, defect-aware routing achieves 70% of the energy savings of delay-aware routing. Finally, we show that without variation tolerance, scaling from 16 nm to 12 nm results in a net increase in minimum energy/operation; component-specific mapping, however, can extend minimum energy/operation scaling to 12 nm and possibly beyond.

## Acknowledgements

First, and most importantly, I would like to thank my advisor André DeHon for his guidance on this work. He is a vast resource of insight and technical expertise, and his tireless support made this work possible. It has been a privilege to work with him over the years.

I would also like to thank Alain Martin for his mentorship and for making me a part of his research group, which helped make my last few years at Caltech enjoyable. I would also like to thank the other members of my committee for their support and feedback: Ben Calhoun, Azita Emami, and Ali Hajimiri.

Each student in the IC Lab has helped support this work, but two people deserve special mention. First is Rafi Rubin, for the incredible amount of insight and code he contributed to this project. Second is Ben Gojman, for his ideas and assistance in making this work come together. This thesis represents only the broad strokes of the much larger, more interesting picture of component-specific mapping. Ben and Rafi's dissertations will solve the hard problems that will complete this picture; I am confident that their work will far surpass what I have put forth here.

I would like to specially thank Kevin Cao and Sani Nassif for their collaboration in developing circuit failure models that contributed to this work. I specifically owe Kevin thanks for his support in answering my many questions about the predictive technology models. I also need to thank several people from academia and industry who provided invaluable suggestions: Guy Lemiuex, Tim Tuan, Sinan Kaptanoglu, Sean Keller, Peter Grossman, Peter Jamieson, Jonathan Rose, and Peter Cheung and each of his outstanding students.

I need to thank my family for their support over the many years it took for me to complete this project. I owe both of my parents and my sister so much for their love and support that helped get me through this process.

Finally, I would like to thank my wife Katie Shilton for her constant love, patience, encouragement, and belief in me. She has been a joy to be with even during the parts of this process that transformed me into a fixated, isolated monk. The key for me to finish has been her boundless support and love.

# Contents

| $\mathbf{A}$ | bstra | nct          |                                | iii  |

|--------------|-------|--------------|--------------------------------|------|

| A            | ckno  | wledge       | ments                          | iv   |

| Li           | st of | <b>Table</b> | 3                              | viii |

| Li           | st of | Figur        | es                             | xi   |

| 1            | Inti  | oducti       | on                             | 1    |

|              | 1.1   | Thesis       |                                | 1    |

|              | 1.2   | Motiva       | ation                          | 1    |

|              | 1.3   | Comp         | onent-Specific Mapping         | 2    |

|              | 1.4   | Scope        |                                | 6    |

|              | 1.5   | Contri       | butions                        | 6    |

| <b>2</b>     | Bac   | kgrou        | ıd                             | 9    |

|              | 2.1   | FPGA         | Architecture                   | 9    |

|              | 2.2   | Energ        | y                              | 13   |

|              | 2.3   | Proces       | ss Variation                   | 16   |

|              | 2.4   | Prior        | Work                           | 19   |

|              |       | 2.4.1        | Low-Power Techniques for FPGAs | 19   |

|              |       |              | 2.4.1.1 CAD                    | 19   |

|              |       |              | 2.4.1.2 Architecture           | 21   |

|              |       | 2.4.2        | Variation Tolerance in FPGAs   | 25   |

|              |       | 2.4.3        | Component-Specific Mapping     | 27   |

| 3            | Мо    | deling       |                                | 32   |

|              | 3.1   | Device       | es and Circuits                | 32   |

|              |       | 3.1.1        | Motivation                     | 32   |

|              |       | 3.1.2        | Parameter Extraction           | 33   |

|   |                | 3.1.3 Inverter Circuit                            | 5 |

|---|----------------|---------------------------------------------------|---|

|   |                | 3.1.4 Switch Circuit                              | 8 |

|   |                | 3.1.5 LUT Circuit                                 | 8 |

|   |                | 3.1.6 SRAM Circuit                                | 0 |

|   |                | 3.1.7 Defect Rates                                | 2 |

|   | 3.2            | CAD                                               | 4 |

|   |                | 3.2.1 VPR: Variation and Energy                   | 4 |

|   |                | 3.2.2 Timing-Target Routing 4                     | 5 |

| 4 | $\mathbf{Del}$ | ay-aware Routing 44                               | 3 |

|   | 4.1            | Experimental Setup                                | 8 |

|   | 4.2            | Delay                                             | 1 |

|   | 4.3            | Energy                                            | 2 |

|   | 4.4            | Energy at Target Delay 55                         | 3 |

| 5 | Opt            | imizations 5                                      | 5 |

|   | 5.1            | Power Gating                                      | 5 |

|   | 5.2            | Interconnect Sizing                               | 1 |

|   |                | 5.2.1 Uniform Sizing                              | 2 |

|   |                | 5.2.2 Selective Sizing                            | 5 |

|   | 5.3            | Interconnect Sparing                              | D |

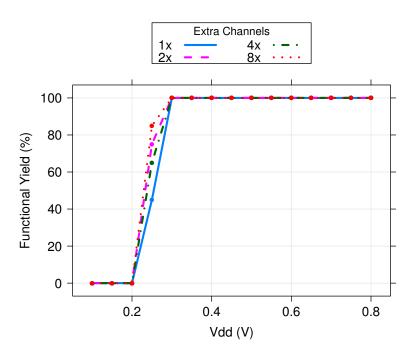

|   |                | 5.3.1 Extra Channels                              | 0 |

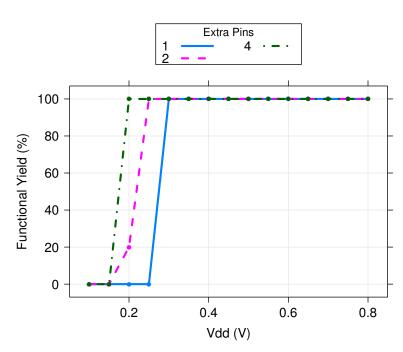

|   |                | 5.3.2 Extra I/O Pins                              | 1 |

|   | 5.4            | LUT Remapping                                     | 3 |

|   | 5.5            | Summary                                           | 9 |

| 6 | Pra            | cticality 8                                       | 1 |

|   | 6.1            | Component-Specific Measurement: Timing Extraction | 1 |

|   | 6.2            | Component-Specific Mapping: CYA Routing           | 5 |

|   | 6.3            | Impact of Delay Precision                         | 7 |

|   |                | 6.3.1 Limited Measurement Precision Mapping 88    | 8 |

|   |                | 6.3.2 Limited Storage Precision Mapping           | 0 |

| 7 | $\mathbf{Sen}$ | sitivity 93                                       | 3 |

|   | 7.1            | Pipeline Depth                                    | 3 |

|   | 7.2            | Circuit Size                                      | 9 |

|   | 7.3            | $V_{th}$ Variation                                | 0 |

|   | 7.4            | Feature Size                                      | 2 |

| 8  | Future Work | 105 |

|----|-------------|-----|

| 9  | Conclusions | 109 |

| Bi | bliography  | 111 |

## List of Tables

| 1.1 | Component-specific mapping energy savings per optimization                     | 8   |

|-----|--------------------------------------------------------------------------------|-----|

| 2.1 | Roundup of low-power FPGA techniques                                           | 24  |

| 2.2 | Roundup of FPGA techniques for variation tolerance                             | 27  |

| 3.1 | Predictive technology model parameters                                         | 35  |

| 4.1 | Toronto20 benchmark characteristics                                            | 50  |

| 7.1 | Multiplier benchmark characteristics                                           | 99  |

| 7.2 | ITRS predicted $V_{th}$ variation (Tables PIDS2 and DESN9 in [3])              | 102 |

| 7.3 | Minimum energy/operation variation-induced margins and component-specific map- |     |

|     | ping benefits                                                                  | 104 |

| 8.1 | FPGA/ASIC gap [59]                                                             | 107 |

# List of Figures

| 1.1  | Component-specific mapping example                                                                    | 4  |

|------|-------------------------------------------------------------------------------------------------------|----|

| 1.2  | Delay as a function of $V_{dd}$ and $\sigma_{V_{th}}$ for a 22 nm FPGA switch driver                  | 4  |

| 1.3  | Defect-aware routing example                                                                          | 5  |

| 2.1  | FPGA architecture                                                                                     | 10 |

| 2.2  | FPGA CLB and LUT circuits                                                                             | 11 |

| 2.3  | FPGA switchbox and switch circuits                                                                    | 12 |

| 2.4  | Measured power breakdown for 90 nm Xilinx Spartan-3 [115] $\ldots$                                    | 13 |

| 2.5  | Minimum energy/operation for a 16-bit FPGA multiplier (22 nm HP) $\hdots$                             | 16 |

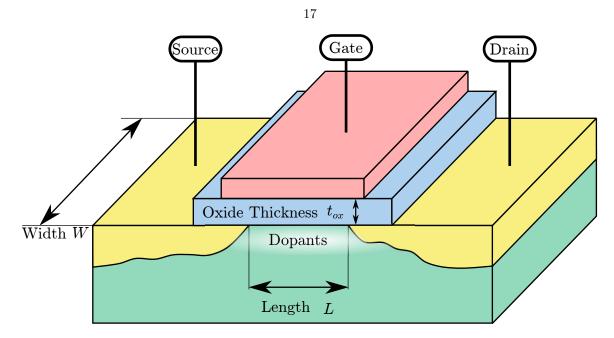

| 2.6  | Transistor layout                                                                                     | 17 |

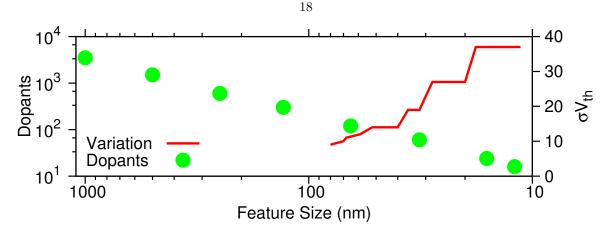

| 2.7  | Decreasing dopants and increasing $V_{th}$ variation from ITRS 2010 [3]                               | 18 |

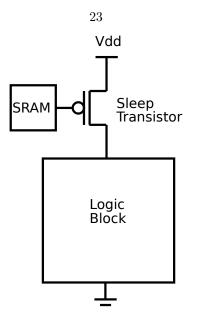

| 2.8  | Power gating circuit                                                                                  | 23 |

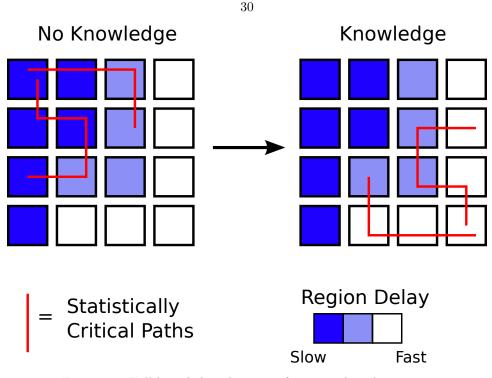

| 2.9  | Full knowledge placement for region-based variation                                                   | 30 |

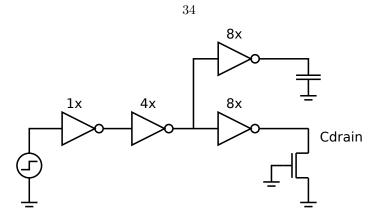

| 3.1  | Drain capacitance extraction circuit                                                                  | 34 |

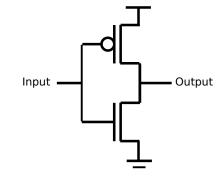

| 3.2  | CMOS inverter                                                                                         | 35 |

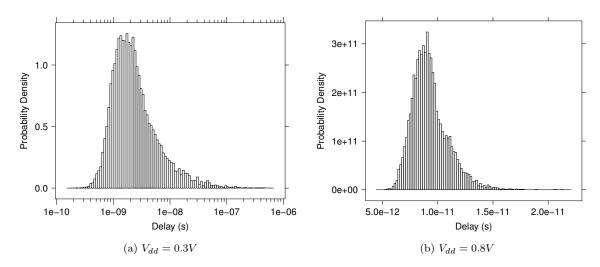

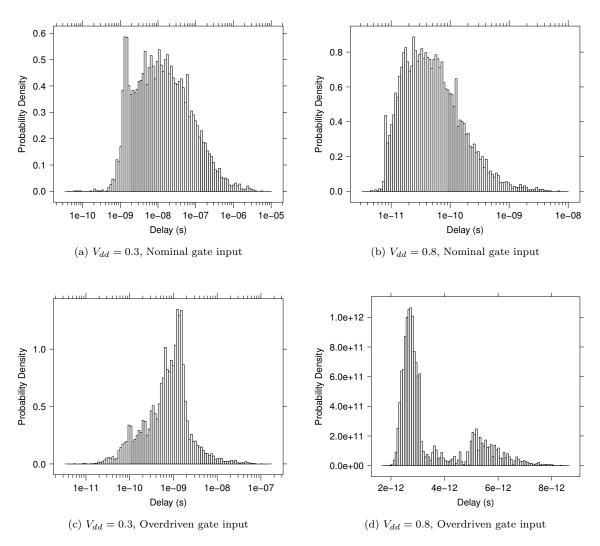

| 3.3  | Inverter delay distribution (22 nm LP, 10,000 samples)                                                | 37 |

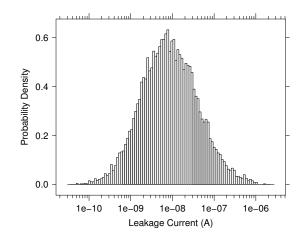

| 3.4  | Inverter leakage distribution (22 nm LP, $V_{dd} = 0.8V$ , 10,000 samples)                            | 37 |

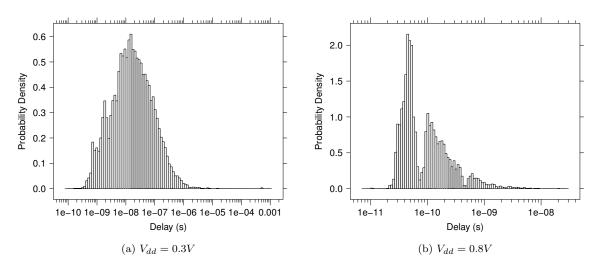

| 3.5  | NMOS pass gate delay distribution (22 nm LP, 10,000 samples) $\ldots \ldots \ldots \ldots$            | 39 |

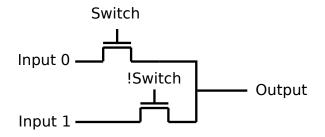

| 3.6  | 2-to-1 multiplexer                                                                                    | 39 |

| 3.7  | 2-input LUT with buffering                                                                            | 40 |

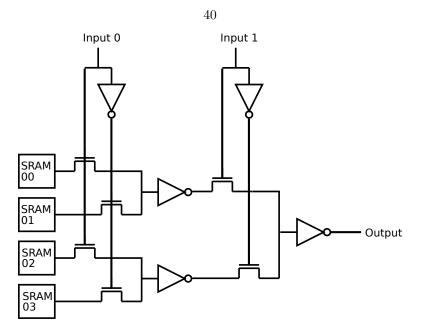

| 3.8  | 2-to-1 mux delay distribution (22 nm LP, 10,000 samples)                                              | 41 |

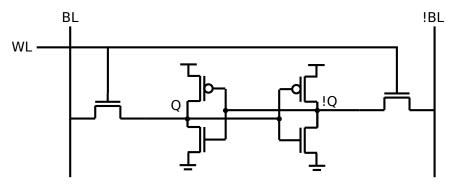

| 3.9  | 6T SRAM cell                                                                                          | 41 |

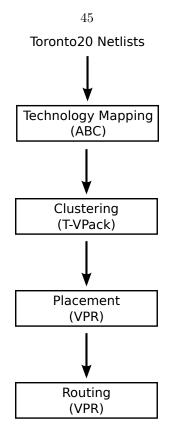

| 3.10 | SRAM leakage distribution (22 nm LP, 10,000 samples)                                                  | 42 |

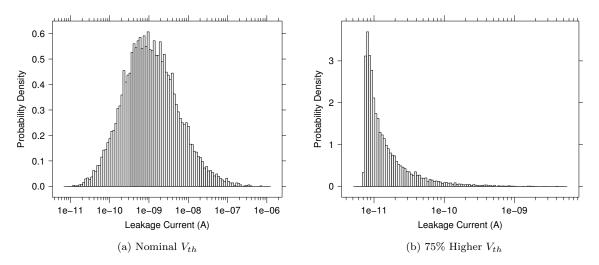

| 3.11 | Primitive circuit failure rates (22 nm LP, 10,000 samples)                                            | 44 |

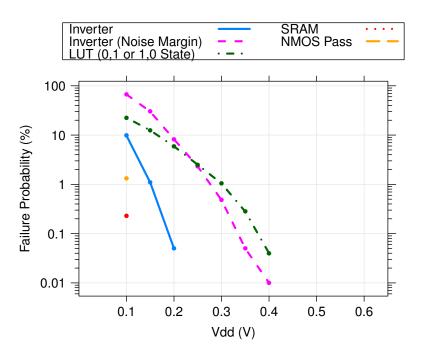

| 3.12 | Standard FPGA mapping CAD flow                                                                        | 45 |

| 3.13 | Percent delay improvement for faster-wire architecture over uniform architecture for                  |    |

|      | the Toronto20 benchmarks [99] $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 46 |

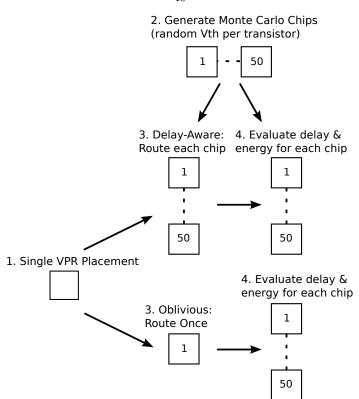

| 4.1  | Experimental CAD flow                                                                                 | 49 |

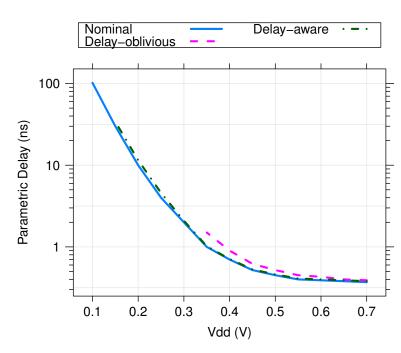

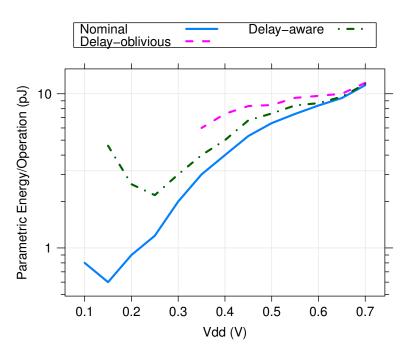

| 4.2  | Delay vs $V_{dd}$ (alu4, 22 nm LP)                                                          | 51 |

|------|---------------------------------------------------------------------------------------------|----|

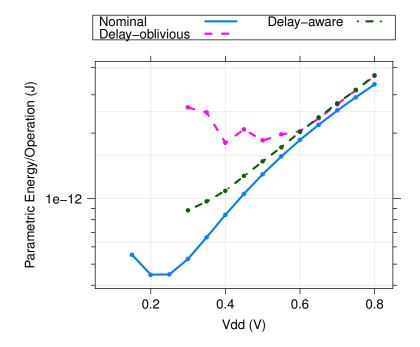

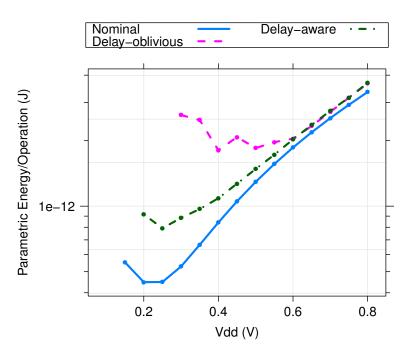

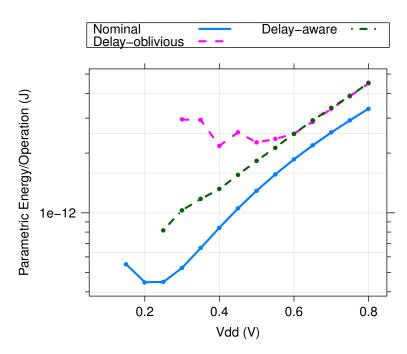

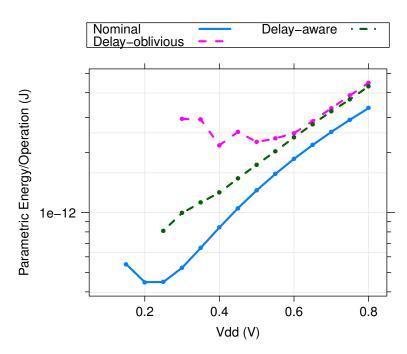

| 4.3  | Energy/operation vs $V_{dd}$ (alu4, 22 nm LP)                                               | 53 |

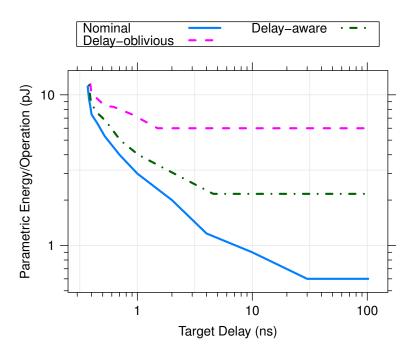

| 4.4  | Energy/operation vs delay target (alu4, 22 nm LP)                                           | 54 |

| 5.1  | Energy/operation vs $V_{dd}$ without power gating (des, 22 nm LP, minimum sizes, no         |    |

|      | variation)                                                                                  | 56 |

| 5.2  | Power gated 3-input switch                                                                  | 57 |

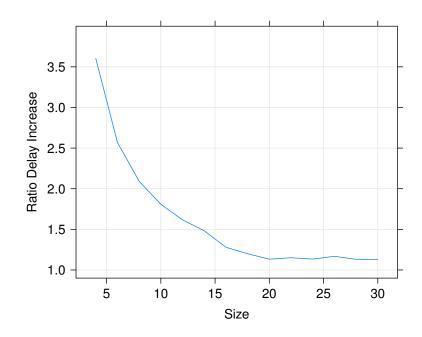

| 5.3  | Sleep transistor delay as a function of size (22 nm LP, 16-input switch circuit) $\ .$      | 58 |

| 5.4  | Energy/operation vs $V_{dd}$ with power gating (des, 22 nm LP, minimum sizes, no variation) | 59 |

| 5.5  | Energy/operation vs $V_{dd}$ without power gating (des, 22 nm LP, minimum sizes)            | 60 |

| 5.6  | Energy/operation vs $V_{dd}$ with power gating (des, 22 nm LP, minimum sizes)               | 60 |

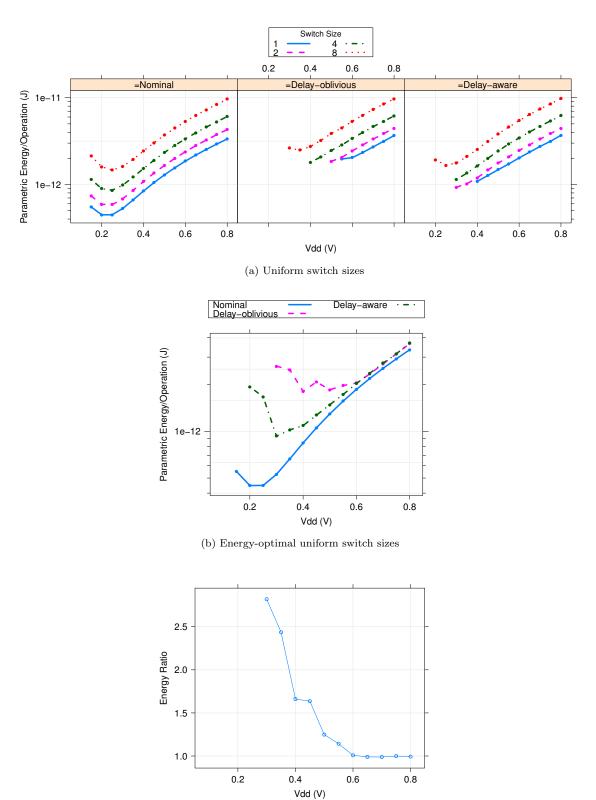

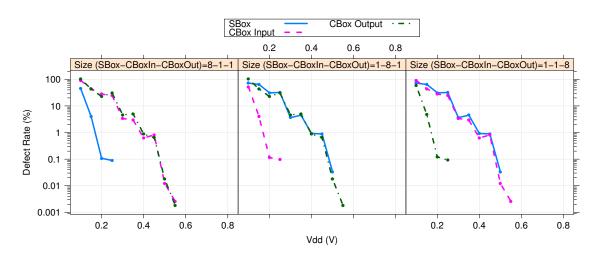

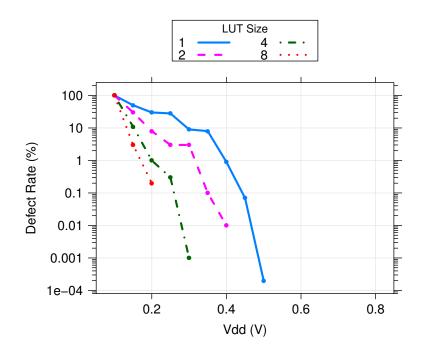

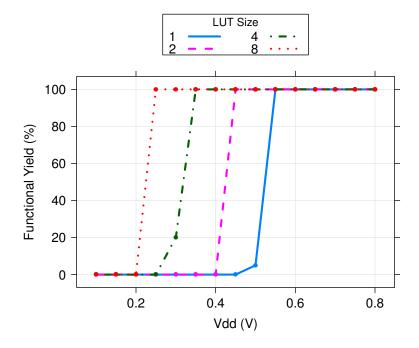

| 5.7  | Defect rates vs $V_{dd}$ for uniform sizing (des, 22 nm LP)                                 | 62 |

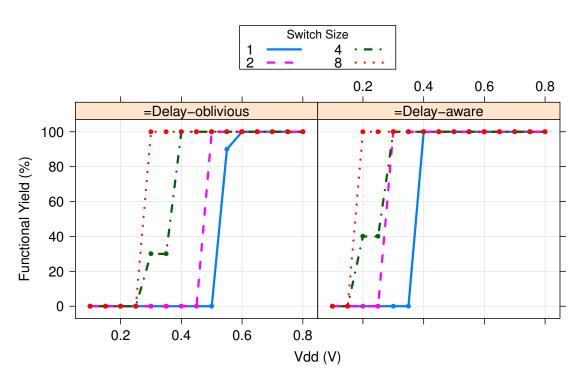

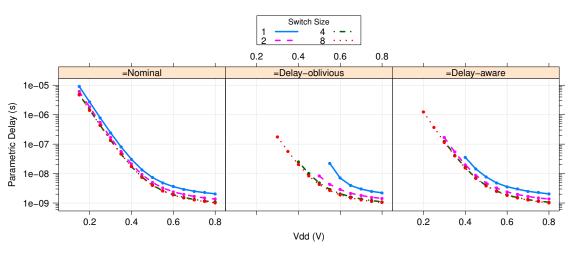

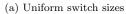

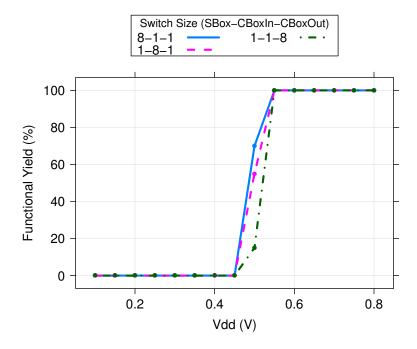

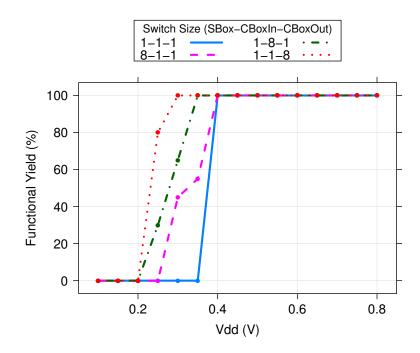

| 5.8  | Functional yield vs $V_{dd}$ for uniform sizing (des, 22 nm LP)                             | 63 |

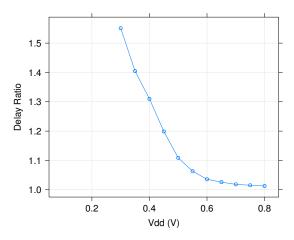

| 5.9  | Delay vs $V_{dd}$ for uniform sizing (des, 22 nm LP)                                        | 64 |

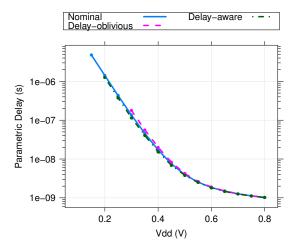

| 5.10 | Energy/operation vs $V_{dd}$ for uniform sizing (des, 22 nm LP)                             | 66 |

| 5.11 | Defect rates vs $V_{dd}$ for selective sizing (des, 22 nm LP)                               | 68 |

| 5.12 | Delay-oblivious functional yield vs $V_{dd}$ for selective sizing (des, 22 nm LP)           | 68 |

| 5.13 | Delay-aware functional yield vs $V_{dd}$ for selective sizing (des, 22 nm LP)               | 69 |

| 5.14 | Energy/operation vs $V_{dd}$ for energy-optimal selective sizing (1-2-2) (des, 22 nm LP) .  | 69 |

| 5.15 | Delay-aware functional yield vs $V_{dd}$ for extra channels (des, 22 nm LP)                 | 71 |

| 5.16 | Delay-aware functional yield vs $V_{dd}$ for extra pins (des, 22 nm LP)                     | 72 |

| 5.17 | Energy/operation vs $V_{dd}$ for energy-optimal sizing (2-2-2) and 4 extra pins (des, 22    |    |

|      | nm LP)                                                                                      | 73 |

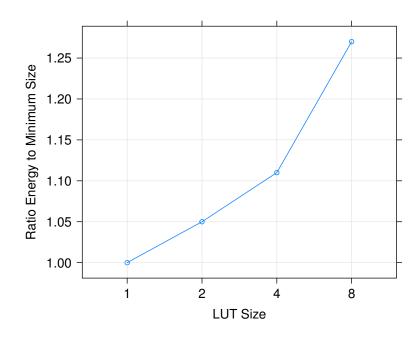

| 5.18 | Energy ratio of sized LUT to minimum as a function of LUT size                              | 74 |

| 5.19 | Defect rates vs $V_{dd}$ for LUT sizes (des, 22 nm LP)                                      | 75 |

| 5.20 | Functional yield vs $V_{dd}$ for LUT sizes (des, 22 nm LP)                                  | 75 |

| 5.21 | Energy/operation vs $V_{dd}$ for LUT sizes (des, 22 nm LP)                                  | 76 |

| 5.22 | Defective LUT configuration under variation                                                 | 77 |

| 5.23 | Valid, remapped LUT configuration under variation                                           | 77 |

| 5.24 | Energy/operation vs $V_{dd}$ for LUT sizes (des, 22 nm LP)                                  | 78 |

| 5.25 | Energy/operation vs $V_{dd}$ for each optimization technique (des, 22 nm LP)                | 79 |

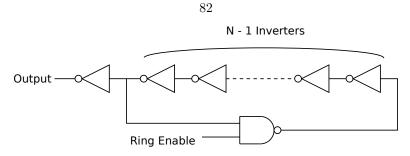

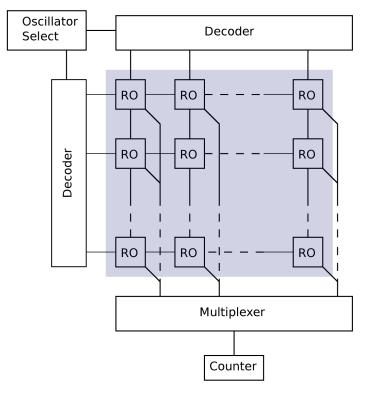

| 6.1  | Ring oscillator                                                                             | 82 |

| 6.2  | Measurement array of ring oscillators [104]                                                 | 83 |

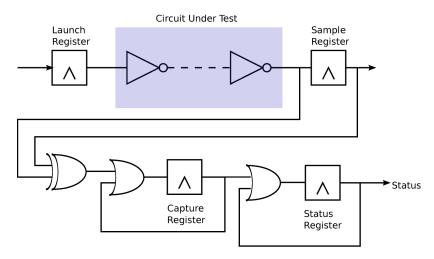

| 6.3  | Path delay measurement circuit [124]                                                        | 83 |

| 6.4  | CLB with 4-LUT, register, and local interconnect                                            | 84 |

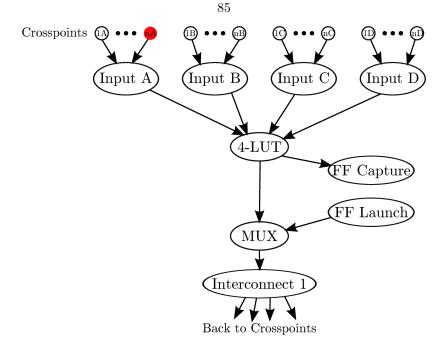

| 6.5  | Graph of logical components (LCs) for CLB                                                   | 85 |

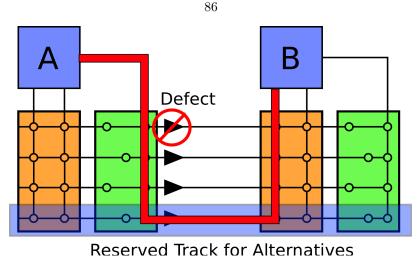

| 6.6  | CYA example                                                                                  | 86  |

|------|----------------------------------------------------------------------------------------------|-----|

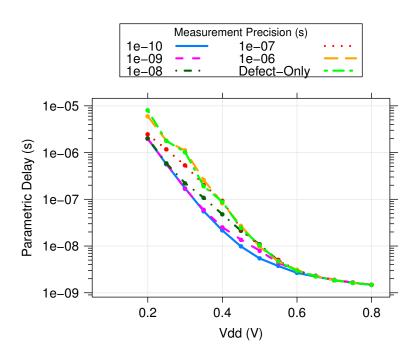

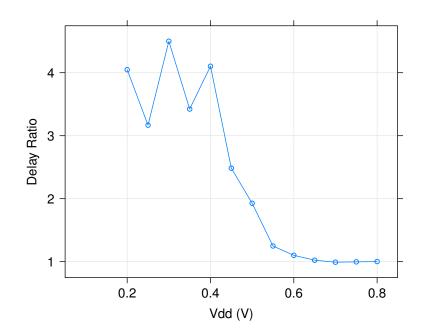

| 6.7  | Delay vs $V_{dd}$ of delay-aware router for different measurement precisions (des, 22 nm LP) | 88  |

| 6.8  | Delay ratio of defect-only to full precision to routing vs $V_{dd}$ (des, 22 nm LP)          | 89  |

| 6.9  | Energy/operation vs $V_{dd}$ of delay-aware router for different measurement precisions      |     |

|      | (des, 22 nm LP)                                                                              | 89  |

| 6.10 | Delay vs $V_{dd}$ of delay-aware router for different storage precisions (des, 22 nm LP)     | 91  |

| 6.11 | Energy/operation vs $V_{dd}$ of delay-aware router for different storage precisions (des, 22 |     |

|      | nm LP)                                                                                       | 92  |

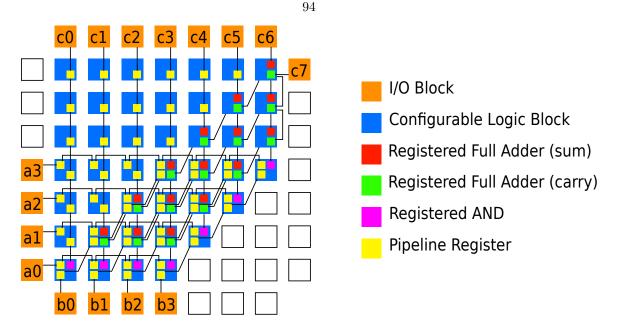

| 7.1  | Fully pipelined $4 \times$ FPGA multiplier                                                   | 94  |

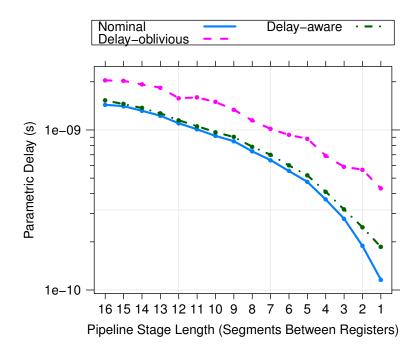

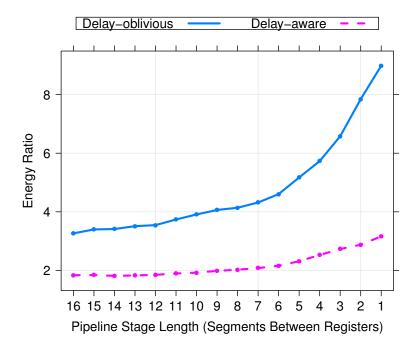

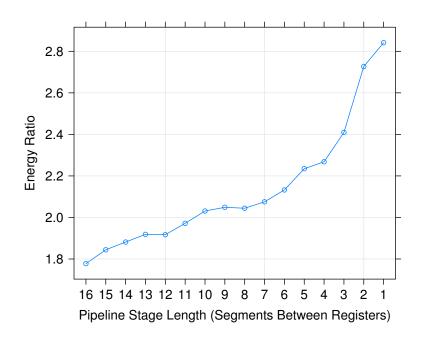

| 7.2  | Delay vs pipeline stage length (mult16, 22 nm LP, $V_{dd} = 600 \text{mV}$ )                 | 95  |

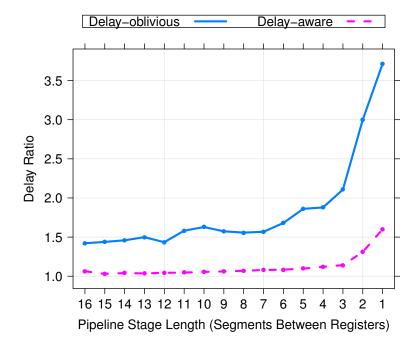

| 7.3  | Delay ratio to nominal vs pipeline stage length (mult16, 22 nm LP, $V_{dd}=600{\rm mV})$     | 95  |

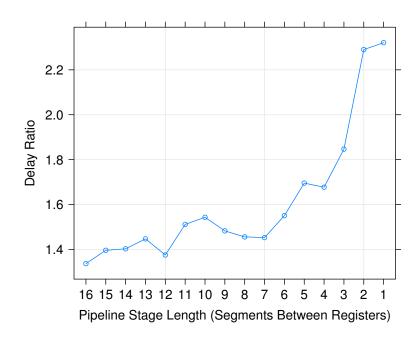

| 7.4  | Delay ratio of delay-oblivious/delay-aware routing vs pipeline stage length (mult16, 22      |     |

|      | nm LP, $V_{dd} = 600$ mV)                                                                    | 96  |

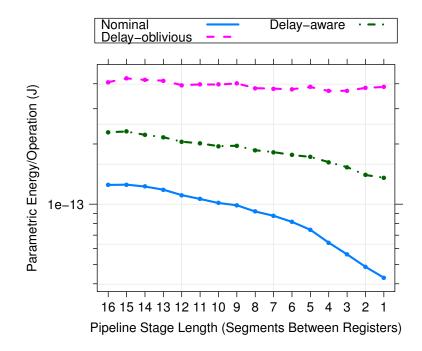

| 7.5  | Minimum energy/operation vs pipeline stage length (mult16, 22 nm LP) $\ldots \ldots$         | 97  |

| 7.6  | Minimum energy/operation ratio to nominal vs pipeline stage length (mult16, 22 nm $$         |     |

|      | LP)                                                                                          | 97  |

| 7.7  | Minimum energy/operation ratio of energy-oblivious/energy-aware routing vs pipeline          |     |

|      | stage length (mult16, 22 nm LP)                                                              | 98  |

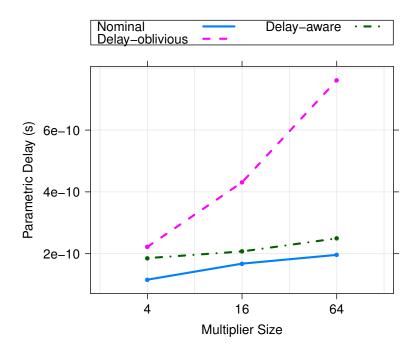

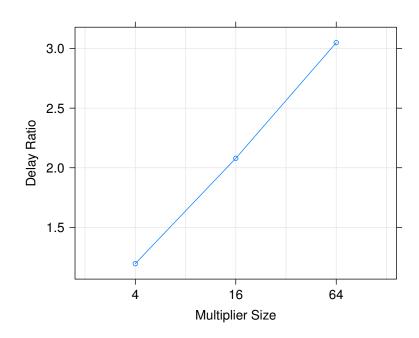

| 7.8  | Delay vs multiplier size (22 nm LP, $V_{dd} = 600 \text{mV}$ )                               | 99  |

| 7.9  | Delay ratio of delay-oblivious/delay-aware routing vs multiplier size (22 nm LP, $V_{dd} =$  |     |

|      |                                                                                              | 100 |

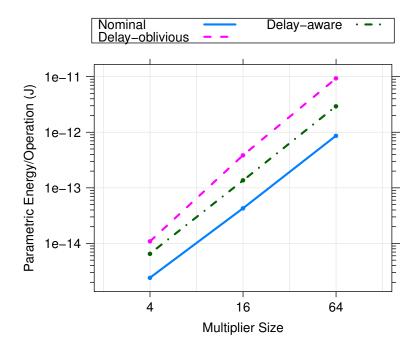

| 7.10 | Minimum energy/operation vs multiplier size (22 nm LP)                                       | 101 |

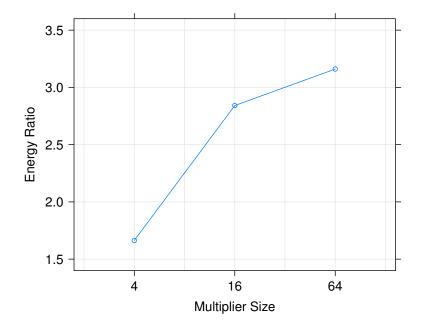

| 7.11 | Minimum energy/operation ratio of energy-oblivious/energy-aware routing vs multi-            |     |

|      | plier size (22 nm LP)                                                                        | 101 |

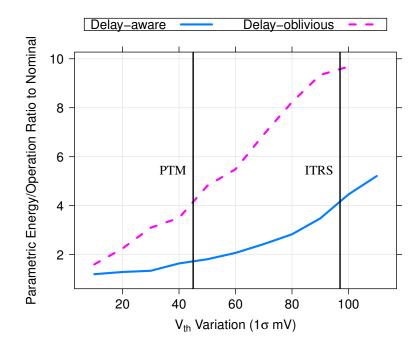

| 7.12 |                                                                                              | 103 |

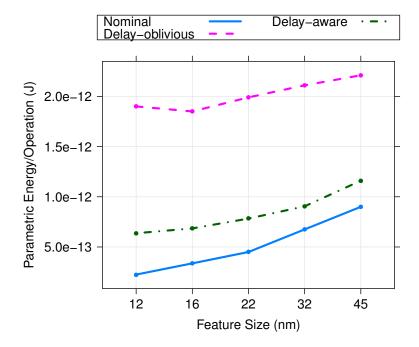

| 7.13 | Minimum energy/operation vs feature size $(des)$                                             | 103 |

# Chapter 1 Introduction

#### 1.1 Thesis

An FPGA using post-fabrication component-specific mapping and an optimized architecture can reduce minimum energy/operation in future technology nodes by  $1.68-2.95\times$ , and can extend minimum-energy scaling by at least one additional technology generation.

#### 1.2 Motivation

The scaling down of transistor feature sizes during the last several decades has led to unparalleled growth in the computational capability of integrated circuits. As individual transistors get smaller they get faster, and more transistors can fit in a fixed area. Historically, designers have considered performance and density to be the most important metrics driving the design of integrated circuits. Early circuits were so limited in density and performance that almost every design choice revolved around utilizing the large, slow transistors as efficiently as possible. For example, the Intel 4004 (the first widely available commercial microprocessor) contained a mere 2,300 transistors operating at 740 kHz. Forty years of scaling has led to processors with billions of transistors operating at clock frequencies of several GHz, enabling designers to have much more freedom in allocating transistors.

While density and performance are still important in modern integrated circuits, in the last decade two new metrics have emerged as primary design constraints: energy and reliability. In a keynote speech in 2005, Intel Fellow Shekhar Borkar described how energy/power and reliability will be the two biggest challenges facing the integrated circuit industry [21].

Energy and power have already become primary design constraints of current circuits: no longer is it possible to deliver performance at any cost, as designs must fall within a power density or energy budget [40]. Smaller feature sizes mean more transistors in a fixed area, but because voltages have largely remained constant [3], this increased density translates to more power dissipated per unit area. Increased power density leads to substantial heat generation, which may be too high to cool easily. The absence of voltage scaling has also limited the scaling down of energy/operation, which limits the amount of time (i.e., number of operations) that a circuit can compute using a fixed supply of battery energy. An emerging and important class of applications such as micro-sensor networks [92] and biomedical sensors [103] have extreme battery and cost limitations; for these applications, minimal energy/operation is absolutely essential.

Reliability is starting to become a primary design constraint, and will likely become the dominant constraint for future technologies: Borkar estimated that 100 billion transistor designs in 2016 will be subject to substantially higher failure rates due to 20% fabrication-time defects [22]. With transistors currently sized at  $\approx 50$  silicon atoms long (22 nm), it becomes impossible to perfectly control their physical structure and atomic composition, leading to defects or variations in how an individual transistor will operate. Designing a functioning integrated circuit with billions of unique transistors with shapes and sizes that cannot be known a priori because of these process variations is an enormous challenge, and can lead to a significant percentage of non-functioning chips. With every new generation of yet smaller transistors, these reliability problems will only get worse.

Unfortunately, reliable operation and low-energy computation are largely competing goals. Most techniques that attempt to increase system reliability also increase energy (e.g., gate sizing, voltage margining, redundancy). Consequently, current techniques and methodologies that simultaneously lower energy/power and increase reliability are extremely scarce. Because reliable operation is of paramount importance, designers are more often than not willing to accept higher-energy operation in exchange for functional devices.

The motivation behind this report is to demonstrate one core technique, component-specific mapping (and its many possible optimizations), that will enable a device to both operate at very low energy and maintain reliable operation in future technologies. In the next section we will illustrate the idea behind component-specific mapping with a simple example, and then describe the scope and contributions of this report.

## **1.3** Component-Specific Mapping

The core of the reliability challenge in dealing with fabricating small transistors is that their exact electrical characteristics cannot be known prior to fabrication. Fabricated circuits may contain transistors that are either defective or too slow; additionally, a transistor that may be acceptable at nominal voltage may slow down or fail at a low voltage. The key idea behind component-specific mapping is to somehow measure the electrical characteristics of every transistor after a chip is fabricated, and to use that knowledge to customize the circuit in a way that avoids bad transistors and utilizes good ones at low voltages.

In order to do this, we require an integrated circuit that can be customized at the hardware

level after fabrication. The majority of chips today are fabricated as application-specific integrated circuits (ASICs), meaning that they are designed for a single fixed use; transistors and wires cannot be chosen or avoided after manufacturing. However, field-programmable gate arrays (FPGAs) are reconfigurable devices that can be programmed after fabrication to implement any digital logic (Section 2.1). In FPGAs blocks of configurable logic are connected via programmable interconnect, which are simply switches controlled by memory cells. By assigning appropriate values to those memory cells (i.e., the device configuration), any set of logical functions and connectivity between those functions can be mapped or re-mapped to the component.

The flexibility of making connections configurable (e.g., replacing a directly connected wire with a switch and memory cell) typically comes at a cost in performance, area, and energy. However, configurability means that instead of relying on external testers, one can configure in situ circuits to self-test and measure transistor characteristics in a device post-fabrication. Then, using that information, designs can be mapped to each fabricated FPGA in a component-specific manner. These per chip customized designs attempt to exploit the fact that every transistor is unique, and specifically target low energy, reliable operation.

The first step in component-specific mapping is to perform a series of measurements per chip to extract delays for every resource. Once that information is obtained, it can be used by FPGA mapping algorithms to minimize energy under variation. To illustrate the basic idea and potential energy and delay benefits of post-fabrication component-specific mapping, we start with a simple, illustrative example. The goal will be to reduce the overall energy consumed by carefully selecting the assignment of FPGA routes to resources based on the component characteristics.

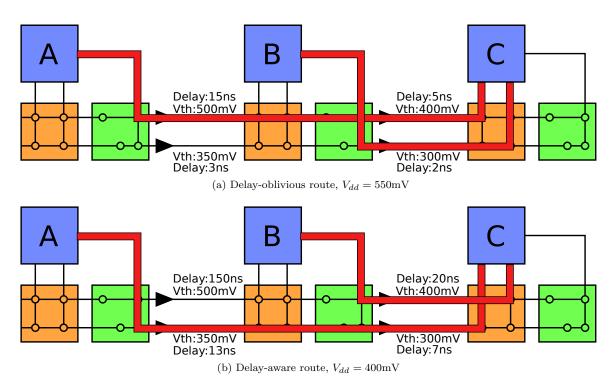

Figure 1.1 shows a cartoon version of simplified, 1D FPGA organization with three logic blocks (blue) computing functions A B C, connection boxes (orange) connecting wire segments to the inputs of the logic blocks, and switch boxes (green) connecting wire segments to each other and the output of the logic blocks. Programmable circular switches can be configured to connect wires and blocks together. The wires are driven by buffers at the start of the segment; each driver has a threshold voltage  $V_{th}$  which can be used to calculate the delay of the driver. The expected nominal threshold voltage is 400 mV. However, due to process variation, only one out of the four segments has its nominal value.

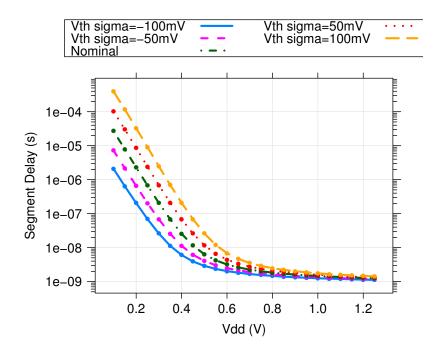

Assume our goal is to compute C = A + B within 20 ns. The outputs of function blocks A and B must be connected to the input of function block C; there are two such possible configurations (Figures 1.1a and 1.1b). Ignoring logic delays, to meet our timing target the maximum delay of either path  $A \to C$  or  $B \to C$  through the interconnect must take at most 20 ns. Figure 1.2 shows the delay of a wire segment as a function of supply voltage  $V_{dd}$  and threshold voltage variation  $\sigma_{V_{th}}$ . We see that raising  $V_{th}$  makes the segment slower, while raising  $V_{dd}$  makes the segment faster. Because  $V_{th}$  is fixed at fabrication time, in order to tune segment delays we must change  $V_{dd}$ .

Figure 1.1: Component-specific mapping example

Figure 1.2: Delay as a function of  $V_{dd}$  and  $\sigma_{V_{th}}$  for a 22 nm FPGA switch driver

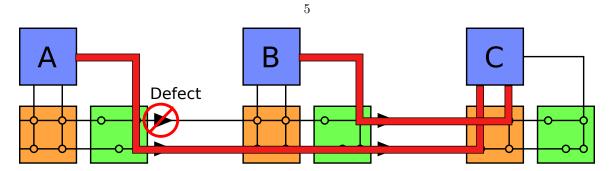

Figure 1.3: Defect-aware routing example

For a router that is oblivious to the variation present in the FPGA, all segments have drivers with  $V_{th} = 400$ mV, and both possible configurations are identical. Thus, the router may produce the results shown in Figure 1.1a, which use the two slowest, highest  $V_{th}$  drivers on the critical path  $A \to C$ . Using Figure 1.2 to determine delays, we see that to meet our interconnect timing requirement of 20 ns for this particular route configuration, we must set our supply voltage to at least  $V_{dd} = 550$ mV. This yields a path delay  $A \to C = 20ns$  (with the parallel path  $B \to C = 2ns$ ).

If we instead give a delay-aware router the delays of each segment as a function of  $V_{dd}$ , it can find the route shown in Figure 1.1b. Here, path  $A \to C$  is still the slowest path, but using the full knowledge of component characteristics, the router assigns this long connection to fast, low  $V_{th}$ segments, avoiding the slowest driver with  $V_{th} = 500mV$ . Since the parallel path  $B \to C$  is less delay critical, the router can afford to assign it to a higher  $V_{th}$ , slower segment while still meeting timing. At  $V_{dd} = 400mV$ , both paths  $A \to C$  and  $B \to C$  have a delay of 20 ns. In this example, using knowledge of the underlying characteristics of the FPGA can reduce the voltage and active energy consumption by a factor of  $\left(\frac{550}{400}\right)^2 = 1.9$  compared to the delay-oblivious route. Delay-aware routing can be tuned to either improve delay at a fixed  $V_{dd}$ , or achieve identical delay but at a lower  $V_{dd}$ .

Delay-aware routing can also avoid defects, as defects can be easily detected in the delay measurement process. We will see that defects are not uncommon at very low  $V_{dd}$  and large amounts of  $V_{th}$  variation. Figure 1.3 shows the same example where the high  $V_{th}$  driver is actually defective at low enough  $V_{dd}$ ; delay-aware routing can detect this defect and route around it. Avoiding these variation induced defects is critical to being able to safely lower  $V_{dd}$  to minimize energy.

While these simplified cases illustrate the use of routing to navigate interconnect resources and reduce energy consumption, it should be clear that the general idea can be applied much more broadly. Instead of just customizing configurations for interconnect, we can perform similar substitution or assignment for all resources (e.g., logic, memory). Furthermore, mapping based on post-fabrication resource knowledge can be exploited in not just routing, but in placement, memory assignment, clustering, and function binding.

#### 1.4 Scope

Component-specific mapping is a large, challenging problem with many pieces and possible optimizations. This report does not represent a complete solution, as the scope and effort required for a working solution is worthy of several dissertations.

The most significant portion of component-specific mapping that is not addressed in depth is the problem of measurement. While Chapter 6 does illustrate the basic strategy for performing measurements, this work assumes that component-specific delay measurements are attainable and available for use in mapping.

The second major problem not addressed in this work is the cost of actually mapping every chip individually. This breaks the typical FPGA model of one-mapping-fits-all, and requires a CAD algorithm to be run for every chip. Chapter 6 also describes this problem in more detail with some existing, partial solutions that allow one CAD run to be customized per chip. However, these techniques are not explored in depth here.

Additionally, this work does not attempt to address all possible sources of unreliability. Effects such as transient errors (e.g., soft errors, shot noise, thermal noise), environmental effects (e.g., temperature variation,  $V_{dd}$  fluctuation), and lifetime failures (e.g., NBTI, HCI, TDDB, electromigration) are left for future work. Instead, we focus on the phenomena that is predicted to have one of the most important impacts on transistor reliability in near future technologies: random  $V_{th}$ variation [16, 47].

Finally, the scope of this work is to focus specifically on the metrics of minimum energy/operation and fabrication-time parametric yield. Minimum energy/operation is the critical metric for several important applications [92, 103], and also represents an important, fundamental limit on the energy efficiency of technologies. We will quantify aspects of performance and area; however, they will primarily be optimized in so far as they can help reduce energy. Additionally, this work will not focus on reducing power density, although low energy operation typically goes hand-in-hand with low-power operation.

#### 1.5 Contributions

In the following chapters, we will explore the answers to the following questions involving componentspecific mapping and make the following contributions:

• Modeling: How can we efficiently and accurately model key characteristics (performance, energy) of FPGAs in future technologies? Chapter 3 illustrates our techniques for performing HSPICE simulations and curve fitting to build an accurate model for FPGA circuit delay and energy. We also document our modifications to the academic CAD mapping tool VPR [95]

which allows us to explore a wide range of FPGA architectures.

Contributions:

- Construction of an HSPICE based device model for computing delay and energy, accurate to within 10% across a wide range of technologies, circuits, voltages and parameter variation.

- Enhancements to VPR which stabilize routing results under variation and allow for the exploration of more detailed architectures.

- Benefits: What are the benefits of component-specific mapping? Chapter 4 details our experimental methodology and builds an intuition for the expected benefits using experimental results without extensive optimizations.

Contributions:

- Quantification of delay and energy margins of delay-oblivious routing due to random  $V_{th}$  variation in interconnect.

- Demonstration of the potential energy savings of component-specific routing.

- Optimizations: What optimizations can we perform to increase those benefits? Chapter 5 explores the energy and reliability tradeoff between adjusting gate sizes and the number of spare resources. We show that delay-aware routing is able to use smaller, less reliable gates to save energy, and that adding extra resources for more mapping flexibility results in even more energy savings. We also show that fine-grained power gating is necessary to achieve these benefits. Finally, we demonstrate techniques for LUT remapping to deal with variation in LUTs, further saving energy.

Contributions:

- Quantification of the impact of switch-level power gating on energy.

- Quantification of the impact of interconnect buffer sizing on energy.

- Quantification of the impact of interconnect sparing (extra channels, extra pins) on energy.

- Quantification of the impact of LUT variation and subsequent LUT sizing and remapping on energy.

- Design space exploration across all sizing and sparing variables.

- Summary of energy savings of all optimizations combined.

- **Practicality:** Given the large cost in measuring every transistor in every chip and performing component-specific customization, what are the benefits of component-specific mapping without perfect measurement? Chapter 6 demonstrates that with imprecise delay information (100

| ۵ | - | 2  |  |

|---|---|----|--|

| 2 |   | ٤. |  |

|   |   | ,  |  |

|   |   |    |  |

| Technique                                    | Energy Savings       |

|----------------------------------------------|----------------------|

| Component-Specific Mapping (Baseline, 22 nm) | 1.72×                |

| Power Gating                                 | +5%                  |

| Uniform Interconnect Buffer Sizing           | +6%                  |

| Selective Interconnect Buffer Sizing         | +8%                  |

| Interconnect Channel Sparing                 | +0%                  |

| CLB I/O Sparing                              | +12%                 |

| LUT Remapping                                | +17%                 |

| Overall (22 nm)                              | $2.66 \times$        |

| Overall (45 nm–12 nm)                        | $1.68 - 2.95 \times$ |

Table 1.1: Component-specific mapping energy savings per optimization

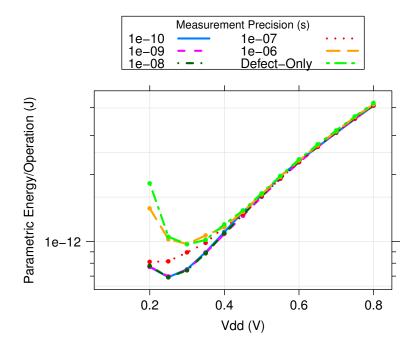

ps measurement precision or 8-bit storage precision) we can obtain the same energy savings achieved with full precision delay information. In fact, using only defect maps instead of full delay measurements, we can achieve 70% of the energy savings obtained by full delay-aware mapping.

Contributions:

- Quantification of energy savings of only defect-aware mapping.

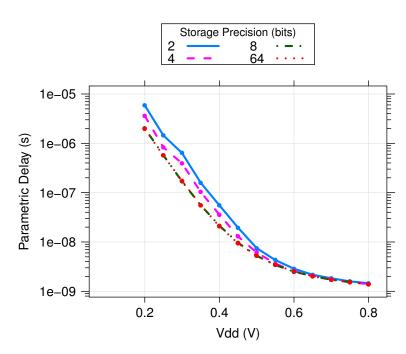

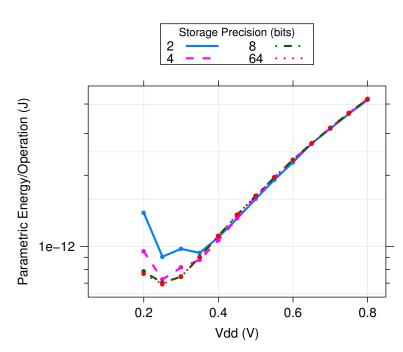

- Exploration of the impact of delay measurement precision on component-specific mapping.

- Exploration of the impact of delay measurement storage on component-specific mapping.

- Sensitivity: How sensitive are these results to changes in technological or design assumptions? Chapter 7 shows that as we increase the pipelining of benchmark circuits, the size of circuits, and the magnitude of variation, the energy savings of component-specific mapping increase. We also show how our results scale from 45 nm to 12 nm feature sizes and demonstrate that energy savings increase with scaling. We further show that delay-oblivious mapping results in a minimum energy/operation *increase* at 12 nm due to variation, while delay-aware routing is able to extend minimum energy scaling.

Contributions:

- Sensitivity analysis of component-specific mapping to pipeline depth of the mapped circuit.

- Sensitivity analysis of component-specific mapping to size of the mapped circuit.

- Sensitivity analysis of component-specific mapping to magnitude of  $V_{th}$  variation.

- Quantification of energy savings of component-specific mapping for 45 nm, 32 nm, 22 nm, 16 nm, and 12 nm technology nodes.

Table 1.1 quantifies the energy savings achievable by each of the optimizations and situations examined in this work. In the next several chapters we will examine these in depth.

# Chapter 2 Background

To provide a baseline for understanding the optimizations performed in this work, in this chapter we will summarize important, basic concepts in FPGAs, energy, and variation. We will also describe prior work in low-power techniques for FPGAs, variation tolerance techniques for FPGAs, and component-specific mapping in order to ground our contributions.

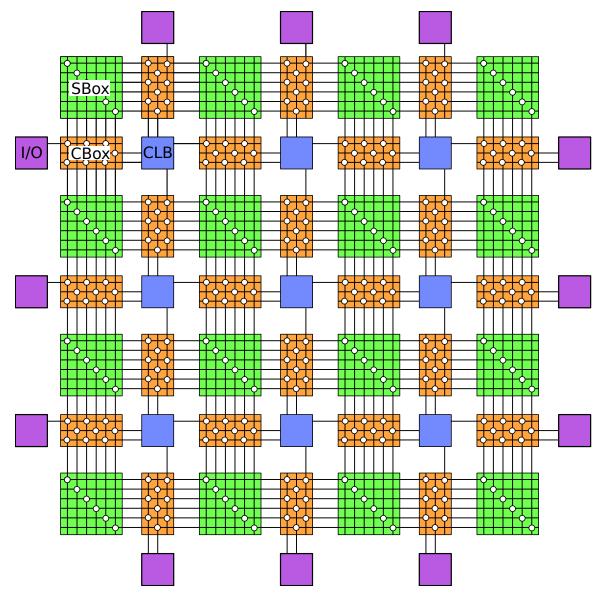

## 2.1 FPGA Architecture

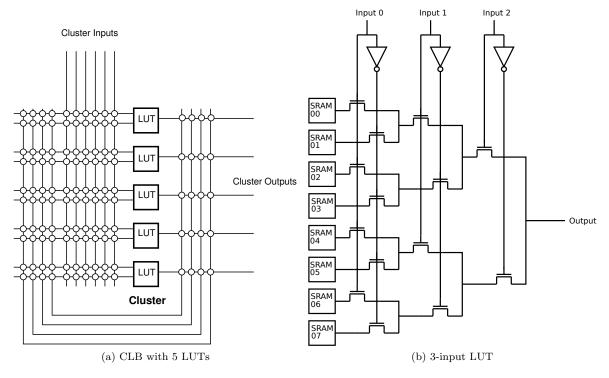

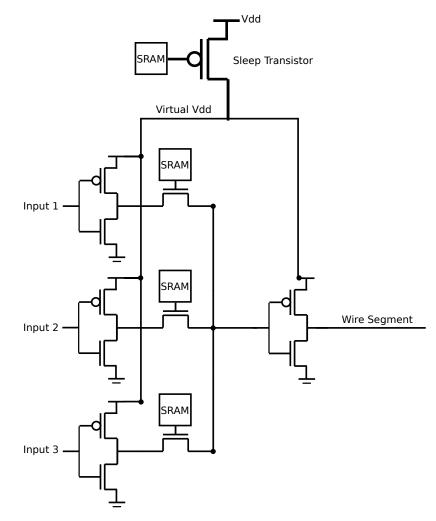

To understand delay-aware routing and its potential energy benefits, it first helps to understand the architecture of an FPGA. A conventional, island-style FPGA can be viewed as an array of configurable logic blocks (CLBs) connected by programmable interconnect (switchboxes and connection boxes, or SBoxes and CBoxes for short, respectively) (Figure 2.1). Inside the CLB (Figure 2.2a), N programmable lookup tables (LUTs) are connected together using internal interconnect. The LUT is simply a circuit that selects the output of an SRAM cell based on the LUT's k inputs: by programming appropriate values in the SRAM cells the LUT can implement any k-input function (Figure 2.2b).

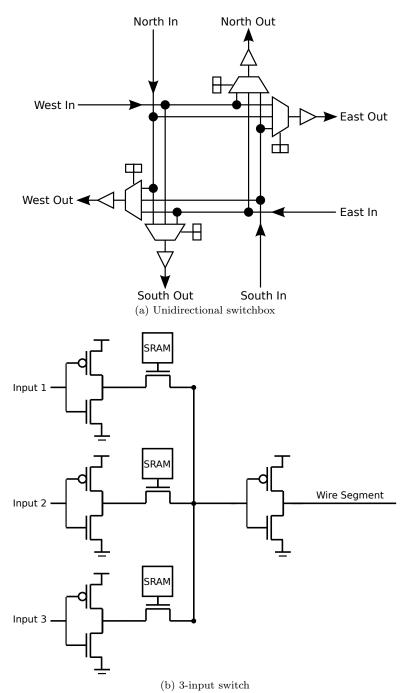

All programmable interconnect is implemented using the simple, unidirectional switch that takes several inputs and selects one output (Figure 2.3b). The circuit consists of input stub buffers for each input that serve to isolate the switch, a multiplexer, and an output buffer that drives a long wire segment. Each of the input and output buffers can be built using a single or multiple staged inverters. Figure 2.3a shows how to assemble these switches into a switchbox.

With an FPGA any circuit can be realized; however, to support this programmability the FPGA must provision significantly more resources (buffers, wires, memory cells) than those required by a custom designed and fabricated implementation. This resource overhead costs area, performance, and energy (typical overheads are described later in Table 8.1).

The main sources of energy utilization in an FPGA are the logic, interconnect, clock network, and configuration memory. Modern FPGAs also consume non-negligible energy in embedded blocks

Figure 2.1: FPGA architecture

Figure 2.2: FPGA CLB and LUT circuits

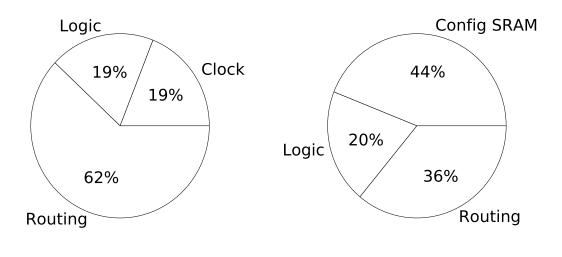

(memories, multipliers, etc.) and in I/O drivers. Several studies have estimated the power dissipated in each of these elements to provide a breakdown of both static and dynamic power dissipation [60, 106,115]. Each study arrives at similar breakdowns for power dissipation; Figure 2.4 shows the most recently published results for a 90 nm Xilinx Spartan-3 [115]. Dynamic and static power charts are shown; in this particular device dynamic power is typically an order of magnitude larger than static power. In Figure 2.4a we see that interconnect dominates dynamic power, contributing 62%. Clock and logic power are the next two largest contributors and are roughly equivalent at 19%. For static power (Figure 2.4b) configuration bits contribute the largest amount of leakage at 44%, as every *n*-input switch requires *n* configuration bits and every *k*-input LUT requires  $2^k$  configuration bits. Routing and logic transistors also leak significantly. If we assign the static power of configuration bits to their sources (either interconnect or logic), interconnect static power will dominate. Hence, interconnect is the primary source of both dynamic and static energy dissipation.

In order to configure a design onto an FPGA, several CAD operations are performed. A user typically starts with a design specified in a hardware description language (HDL), such as Verilog or VHDL. The design is then synthesized into gates and mapped into a netlist of LUTs via technology mapping. The LUTs are then grouped into clusters using a clustering algorithm, and then those clusters are assigned to physical CLBs via a placement algorithm. Finally, the routing algorithm specifies all the necessary routing tracks and configurations of switches needed to connect all the

Figure 2.3: FPGA switchbox and switch circuits

Figure 2.4: Measured power breakdown for 90 nm Xilinx Spartan-3 [115]

(b) Static Power

CLBs together.

(a) Dynamic Power

Because interconnect is the dominant source of energy and delay in FPGAs, the assignment of nets to routing resources is critical. Further, as future technologies will be dominated by random  $V_{th}$ variation which operates at the scale of individual transistors, any successful variation mitigation scheme must have fine-grained control over which transistors to select. For example, placement only serves to relocate CLBs in the FPGA fabric, which will only have a very coarse-grained impact on which routing transistors are selected for configured paths. Routing, however, allows for finegrained selection of routing transistors, and is the best opportunity for mitigating the delay and energy margins induced by variation.

Hence, in this work we focus largely on delay-aware routing as our primary variation mitigation technique. However, as LUTs still experience variation and can have an impact on total energy if ignored, we perform a level of component-specific LUT mapping using delay information (Section 5.4).

## 2.2 Energy

Power is a significant design challenge in modern integrated circuits, particularly in microprocessors. Using conventional air cooling technology (i.e., thermal paste, heatsinks and fans), the practical limit of power density that can be cooled is approximately 100 watts/ $cm^2$  [101]. Total chip power can be

expressed as:

$$P_{dynamic} = \alpha \times C \times V_{dd}^2 \times f \tag{2.1}$$

$$P_{static} = I_{leak} \times V_{dd} \tag{2.2}$$

$$P_{transistor} = P_{dynamic} + P_{static} \tag{2.3}$$

$$P_{chip} = \sum_{i=0}^{N_{transistor}} P_{transistor}.$$

(2.4)

We see that the power of a single transistor can be expressed as the sum of dynamic and static power. Dynamic power depends on the switching probability  $\alpha$  (0–1), the switched capacitance C, the supply voltage  $V_{dd}$ , and the clock frequency f.  $P_{static}$  is typically several orders of magnitude lower than the 100 watts/ $cm^2$  limit, so  $P_{dynamic}$  is usually the dominant factor. We can immediately see that one simple way to reduce power, and hence power density, is to just reduce the clock frequency f. By accepting lower performance, a given chip can always operate within a power envelope of 100 watts/ $cm^2$ . For many modern systems that are cooling limited, this is an acceptable tradeoff.

A more fundamental challenge is reducing energy/operation. Energy/operation is the primary design constraint for many low-power, embedded systems. While power is the key metric for describing how efficiently an integrated circuit can be cooled, energy is the key metric for circuits that operate using batteries. To perform each operation, a circuit must draw some number of joules from its battery; hence the joules/operation of a circuit expresses how many operations it can perform and thus how long it can operate with a given battery capacity. Energy/operation can be derived by the fact that power is simply energy per unit time:

$$E_{dynamic} = \alpha \times C \times V_{dd}^2 \tag{2.5}$$

$$E_{static} = I_{leak} \times V_{dd} \times \frac{1}{f}$$

(2.6)

$$E_{transistor} = E_{dynamic} + E_{static} \tag{2.7}$$

$$E_{chip} = \sum_{i=0}^{N_{transistor}} E_{transistor}.$$

(2.8)

Unlike power, reducing energy/operation is not simply a function of accepting slower operation by reducing clock frequency, which almost any design could accomplish. Here, we must reduce physical parameters such as capacitance and supply voltage.

Both C and  $V_{dd}$  can be reduced by accepting reduced transistor performance. The current and

delay of a transistor can be expressed as [119]:

$$I_{sat} = W \times v_{sat} \times C_{ox} \times \left( V_{gs} - V_{th} - \frac{V_{d,sat}}{2} \right)^{\gamma}$$

(2.9)

$$I_{sub} = \frac{W}{L} \times \mu C_{ox} \times (n-1) \times (v_T)^2 e^{\frac{V_{gs} - V_{th}}{n \times v_T}} \times \left(1 - e^{\frac{-V_{ds}}{v_T}}\right)$$

(2.10)

$$I_{on} = \begin{cases} I_{sat} \quad for \quad V_{ds} = V_{dd} \ge V_{th} \\ I_{sub} \quad for \quad V_{ds} = V_{dd} < V_{th} \end{cases}$$

(2.11)

$$\tau_p = \frac{CV_{dd}}{I_{cn}} \tag{2.12}$$

where W and L are the channel width and length,  $C_{ox}$  is the oxide capacitance,  $\mu$  is mobility,  $v_{sat}$ is saturation velocity, n is the subthreshold slope,  $v_T$  is the thermal voltage, and  $V_{gs}$ ,  $V_{ds}$ ,  $V_{th}$  are the gate-source, drain-source, and threshold voltages respectively. The constant  $\gamma$  is between 1–2 and depends on the degree of velocity saturation.

Because  $C \propto WL$ , we can reduce dynamic energy linearly by sizing down transistors (until the fundamental technology limit of W = L = 1), at the cost of reducing drive strength  $I_{on}$  and thus increasing delay  $\tau_p$ . Alternatively, we can drop  $V_{dd}$ , which will reduce  $E_{dynamic}$  quadratically, again with a delay cost. Voltage scaling is a preferred technique for achieving low energy/operation because of its quadratic effect.

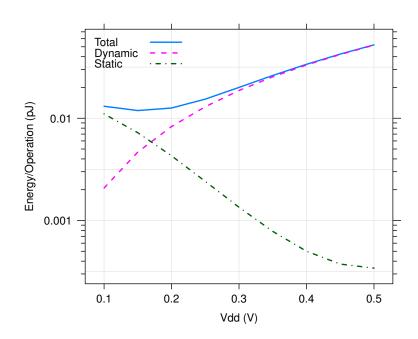

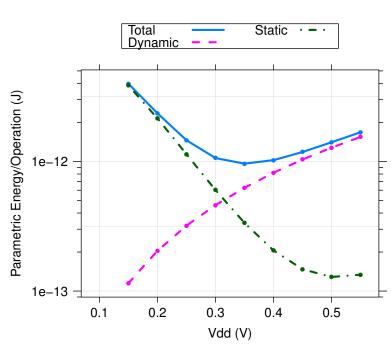

Many circuits may need to simply minimize energy/operation at the cost of delay. For these circuits, reducing  $V_{dd}$  to near zero may appear to be the optimal energy point; however, there exists a  $V_{dd} > 0$  where energy/operation is minimized [24]. With  $V_{dd} > V_{th}$  the delay of a transistor depends on  $I_{sat}$  and is super linear; however, when  $V_{dd} < V_{th}$  delay depends on  $I_{sub}$  making it exponential in both  $V_{dd}$  and  $V_{th}$ . The exponential dependence in  $V_{dd}$  means that operations become significantly longer at lower voltages. As static energy/operation is expressed as leakage power times the length of an operation (Eq. 2.6), at low  $V_{dd}$  static energy will increase dramatically and eventually become the dominant source of energy dissipation.

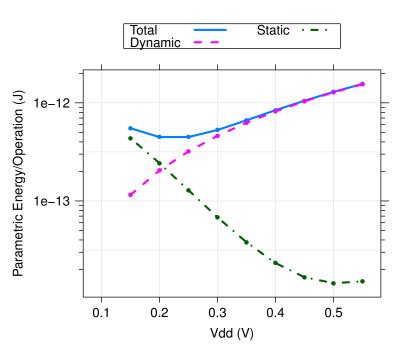

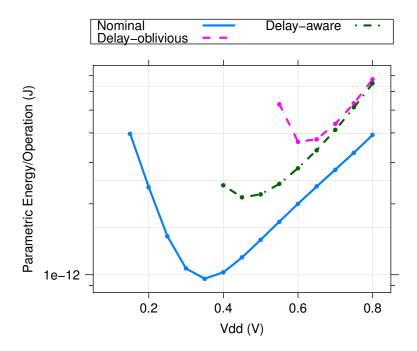

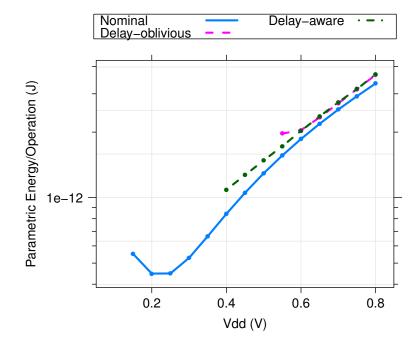

Figure 2.5 shows the energy/operation of a 16-bit multiplier mapped to a 22 nm FPGA. We see that there exists a  $V_{dd}$  at which energy is minimized. This gives a well-defined target point of operation—we should operate at the energy-optimal  $V_{dd}$  when minimizing energy/operation. Furthermore, note that the minimum-energy point occurs below the threshold voltage in this example  $(V_{th} = 300 \text{ mV})$ , as it does for most designs. These types of circuits where  $V_{dd} < V_{th}$  are termed subthreshold circuits.

Minimal energy/operation is an important target for many designs, and represents fundamental limits on energy efficiency for CMOS technologies. As we scale to future technologies, we want the minimum-energy point to continue to reduce. However, parameter variation has a significant impact

Figure 2.5: Minimum energy/operation for a 16-bit FPGA multiplier (22 nm HP)

on this minimum-energy point, and unmitigated it can increase energy/operation significantly; even to the point where it is no longer beneficial to scale to a new technology [20]. One of the goals of our work is to extend this range of beneficial, minimum-energy scaling through component-specific mapping.

#### 2.3 Process Variation

While there are numerous, varied effects that can reduce the reliability of a device over its lifetime (NBTI, HCI, TDDB, electromigration [7,8,97,111]), during operation (temperature variation,  $V_{dd}$  fluctuation [23]), or instantaneously (soft-errors, shot noise, thermal noise [15,102]), a substantial source of unreliability in modern technologies is process variation. Traditionally, circuits have been designed using the assumption that all transistors have identical electrical characteristics. However, because fabrication is an imperfect process, it is impossible to have the physical control necessary to ensure uniform transistors. Process variations describe deviations of transistor electrical characteristics at fabrication time.

Slight process variations have always been present since the birth of CMOS processing; however, it is only recently with submicron-sized device that they have begun to significantly alter the characteristics of designs. Because of law of large numbers effects [33], variations on the scale of 10–100s of atoms (2–22 nm) in a transistor were not readily apparent for micron sized devices; however, for sub-100 nm-sized devices these variations are significant.

Figure 2.6: Transistor layout

Process variations can be classified based on the scale in which the variability of parameters manifest: lot-to-lot, wafer-to-wafer, die-to-die and within die (WID) variations. Historically, large scale variations such as wafer-to-water and die-to-die variations dominated smaller scale variations. However, with submicron processes die-to-die variations have become more significant, and with nanometer designs WID variations contribute the most to parameter variability [88].

Each type of variation can be further categorized based on predictability into systematic and stochastic. Systematic variations are changes in transistor characteristics that are typically layout dependent, and given enough pre-processing effort, can generally be predicted and corrected for [48]. Sources include mask errors, chemical mechanical polishing (CMP), optical proximity effects (OPE) and other tool optics [48, 127]. Variations that are either too difficult to predict based on layout or inherently unpredictable are classified as stochastic variations. Stochastic variations that can be modeled as distance dependent or regional (e.g., lens aberrations, oxide thickness variation [12]) are termed spatially correlated; variations that are at the scale of individual transistors are characterized as random.

Random WID  $V_{th}$  variation is caused by effects like random dopant fluctuation (RDF), channel length variance, and line-edge roughness [11,13]. RDF is the dominant source of random variation [3, 16], and arises from the injection of dopant atoms into a transistors channel (Figure 2.6). Because the injection process is not perfectly precise, the exact number and placement of dopant atoms will vary from transistor to transistor. This variation in dopant atoms results in threshold voltage variation, where  $V_{th}$  can be accurately modeled as a Gaussian random variable. Random variation, due to its inherently stochastic nature, cannot be predicted prior to fabrication unlike systematic or

Figure 2.7: Decreasing dopants and increasing  $V_{th}$  variation from ITRS 2010 [3]

spatially correlated variation.

Further, as transistor volumes shrink with scaling, the magnitude of this variation will increase, as the standard deviation of  $V_{th}$  is inversely proportional to the transistor's cross-sectional area (assuming constant height):

$$\sigma_{V_{th}} \propto \frac{1}{\sqrt{WL}} \tag{2.13}$$

Random variation is expected to dominate future sources of variation [3, 16]. Figure 2.7 shows how  $V_{th}$  variation increases due to decreases in dopant count as a function of feature size. The impact of this random variation is three-fold:

**Increased Delay:** The first impact of  $V_{th}$  variation is that gates will exhibit a large spread in delays, reducing the speed of designs as the delay of a circuit is set by its slowest path. From Equation 2.12, we see that the delay  $\tau_p$  is dependent on  $V_{th}$ ; larger  $V_{th}$  reduces drive strength and increases gate delay.

**Increased Energy:** The second impact of  $V_{th}$  variation is that it raises energy per operation. For a circuit operating at a target delay, to compensate for slower gates, designers are often forced to raise  $V_{dd}$  to increase transistor drive strength ( $I_{sat}$ , Eq. 2.9), increasing energy/operation.

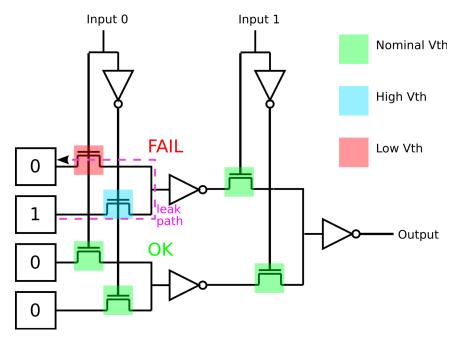

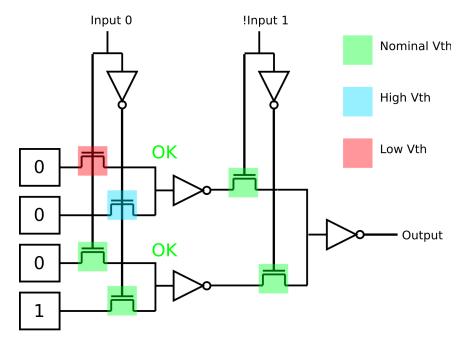

**Increased Failures:** The third impact of parameter variations is the increase in functional failures due to  $V_{th}$  mismatch [89]. SRAMs are commonly the first circuits to fail due to  $V_{th}$  variation which causes read upsets, write upsets, hold failures, and access time failures. Static logic, however, can also fail due to  $V_{th}$  variation. We can define a CMOS inverter to be defective due to variation when

leakage current overpowers on current:

$$I_{PMOS,off} > I_{NMOS,on}$$

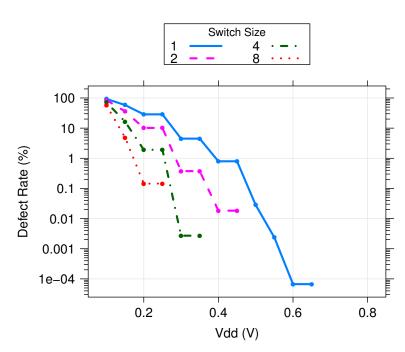

or  $I_{PMOS,on} < I_{NMOS,off}$  (2.14)

Under these conditions the inverter can never switch; this can only happen when  $V_{th}$  variation is large enough such that a very high  $V_{th}$  device is paired with a very low  $V_{th}$  device. Furthermore, as  $V_{dd}$  decreases, the probability of a defect increases as  $I_{on}$  degrades for both PMOS and NMOS transistors (Eq. 2.9) [61]. Consequently, this effect is particularly acute for subthreshold operation, preventing operation near the minimum-energy point [26].

In general, to avoid the negative effects of random  $V_{th}$  variation, designers typically opt to either increase  $V_{dd}$  or increase the size of transistors, both of which cost energy. Here, we can see how energy and reliability are competing goals. Conventional design techniques create energy margins, potentially wasting energy; this underscores the need for other techniques such as component-specific mapping to improve reliability without inducing significant energy margins.

#### 2.4 Prior Work

In this section we summarize prior work in reducing FPGA power dissipation and improving FPGA variation tolerance. A large design space of CAD, architecture, and circuit optimizations have been previously explored. We will see that a some of these techniques are complimentary to component-specific mapping, while others are necessary to maximizing its benefit. Those techniques that are necessary (e.g., power gating, dual  $V_{th}$  design) will be explored in more depth in future sections.

Finally, we will summarize the energy savings achieved by each technique. We will see that this work attempts to dramatically reduce energy under variation by integer factors, in comparison to most prior work which achieves typically modest energy savings.

#### 2.4.1 Low-Power Techniques for FPGAs

Optimizations for low-power operation in FPGAs have been explored at all levels of design: CAD, architecture, and circuits. CAD level optimizations typically operate by adapting the core CAD algorithm's cost function to target low-power operation. Architectural optimizations examine how FPGA power scales as a function of standard architectural parameters (e.g., number of LUTs per CLB, segment length).

#### 2.4.1.1 CAD

**Technology Mapping:** The goal of low-power technology mapping is to reduce dynamic power (Equation 2.5) by either minimizing the switching activity of connections between LUTs ( $\alpha$ ) or by

reducing the total number of these connections and therefore the overall capacitance (C). Previous work has reduced interconnect switching activity by identifying the highest activity connections between gates and mapping in such a way that these nodes are internal to a LUT [39,62,71]. Other work has reduced the total number of interconnect segments by limiting duplication [9], a common technique used in technology mapping. In general, low-power technology mapping has been shown to yield approximately 7.6–17% power savings using both switching activity reduction and limited duplication [62,71].

**Clustering:** Low-power clustering operates on a similar principle as low-power technology mapping. Instead of covering high activity gate to gate connections within the same LUT, in low-power clustering, the goal is to place high activity LUT to LUT connections within the same CLB, utilizing the more energy efficient local interconnect. Lamoureux et al. demonstrated that for a cluster size of 4, an average energy reduction of 12.6% is achievable. [62] Alternatively, depopulation (removing LUTs from fully occupied CLBs and placing them elsewhere) has been shown to reduce routing resource demand, decreasing both average wirelength and switch utilization [32]. Approximately 13% total power can be saved through depopulation-based clustering [107].

**Placement:** Low-power placement algorithms attempt to place CLBs with high activity connections between them close together. Several works have implemented simulated annealing [55] placers with cost functions modified to reflect switching activity [46,62,116]. Each of these placers calculate the cost of a swap by adding a power term to the existing wirelength and delay terms; which includes the switching activity of the nets involved in the swap along with their capacitance. However, because net capacitance is not known prior to routing it must be estimated. On average, placers without accurate capacitance estimation reduce total power by 3.0% with 4% delay cost; placers with accurate capacitance estimation can achieve reductions of 8.6-13% with delay cost of 1-3% [46,116].

**Routing:** PathFinder [81], the standard FPGA routing algorithm, can be modified for low-power routing by adjusting the cost function to account for net activity and capacitance [46,62]. The cost of a resource is modified to include the activity of the net being routed and the capacitance of the candidate routing resource. In modern FPGA architectures, routing resources are not identical and have differing capacitances; hence, lower capacitance paths can be selected. Ideally, high activity nets should be mapped to low capacitance routes. However, as in placement, power-aware routers must be careful to balance delay and power minimization; low activity routes may end up being critical. In fact, power-aware routers have been shown to reduce total power by 2.6% but with a delay increase of 3.8%.

**Glitch Reduction:** A glitch is a switching event in a combinational circuit that does not contribute to the computation of that circuit's final value. Glitches occur when inputs to a gate arrive at different times, causing the gate to switch multiple times prematurely. Wilton et al. proposed pipelining circuits to reduces glitches [120]. A highly pipelined design has fewer glitches because it limits the number of logic levels between registers. Pipelining can reduce energy per operation substantially (40–90%) for circuits with significant glitching at a cost of latency. Glitches can also be minimized during CAD steps in either technology mapping [28] or routing [36]; glitch-aware CAD has been shown to reduce dynamic power by 11–18.7%.

**Summary:** We see that CAD optimizations to reduce FPGA power typically attempt to reduce switched capacitance and switching activity. Each of these techniques yields savings that would benefit both delay-aware mapping and delay-oblivious mapping under variation, and would not significantly change our results.

#### 2.4.1.2 Architecture

Logic Block Architecture: Several researchers have attempted to determine energy favorable values of k (number of LUT inputs) and N (number of LUTs per CLB) when designing an FPGA logic block [67,72,91]. Changing k can have the following tradeoffs in terms of power: first, if k is increased, CLBs require more local routing to connect all LUT input pins (Figure 2.2a), increasing the dynamic energy of the interconnect local to the CLB. However, larger LUTs can implement more complex functions, reducing the total number of LUTs and CLBs. Fewer CLBs mean less demand for global routing resources, saving dynamic interconnect energy. The tradeoff in selecting N is similar: large values of N increase CLB capacity and functionality, which increases local interconnect energy but reduces global interconnect energy. k and N impact leakage energy solely by changing the total area of a design—larger area mean more devices leaking. It has been shown that k = 4 minimizes area [6] and therefore leakage energy [72]. Lin et al. examined total FPGA energy as a function of k and N [72], finding that a LUT input size of k = 4 and smaller cluster sizes (N = 6-10) typically use the least energy.

For this work we re-examined these results and found very similar architectural parameters that we used for this study (k = 4, N = 4) (Section 4.1).

**Interconnect Architecture:** Poon et al. [91] studied the impact of segment length  $L_{seg}$  and switchbox configurations on FPGA energy. A longer wire segment connects to more switches, increasing its capacitance; however, longer segments should lead to fewer total switches. They found the shortest segments  $L_{seg} = 1$  are the most energy efficient.

Jamieson et al. [51] studied the effect of directional versus bi-directional switches on interconnect

energy. In the past, FPGAs were manufactured with bi-directional switches. These switches suffer from the inefficiency that, once configured, an FPGA only uses a switch in one direction; hence, only 50% of drivers are ever utilized. Directional switches drive segments in a single direction, ensuring that all drivers could be utilized. While directional drivers would seem to require more wiring because wires can only be utilized in one direction, in practice they use the same number of wires as the bi-directional case, saving area and improving delay [65] and energy [51].

For this work we also found directional drivers with  $L_{seg} = 1$  to be energy optimal (Section 4.1).

**Dynamic Voltage Scaling:** Dynamic voltage scaling (DVS) reduces  $V_{dd}$ , saving both dynamic and static energy, but at the expense of increasing delay. DVS is useful in scenarios where a design needs to operate at a target frequency. In these cases,  $V_{dd}$  can be lowered to the point where the target is still achieved, minimizing the energy wasted on margins. The exact value of  $V_{dd}$  can be different between chips due to variation and can change over time due to environmental variation; hence, an on-chip control circuit with delay feedback is typically used to adjust  $V_{dd}$ . DVS in FPGAs was examined by [30]. They use a design-specific measurement circuit that tracks the delay of a design's critical path to provide feedback to the voltage controller. Through this technique energy savings of 4–54% can be observed.

DVS is one of the most effective ways to reduce energy/operation because of its quadratic effect. For this work, our main goal is to reduce  $V_{dd}$  but to tolerate variation. Our delay-oblivious router effectively represents a DVS case where the minimum  $V_{dd}$  is found given a set of yield and delay constraints. The delay-aware router attempts to further scale  $V_{dd}$  through component-specific mapping.

**Power Gating:** Leakage power is a significant source of FPGA power dissipation, and is expected to increase as technology scales [114]. FPGAs have significant area overhead due to programmability—hence, large portions of an FPGA are often unused. Instead of leaving these unused portions to sit idle and leak, it is possible to use power gating (Figure 2.8). In power gating a large, high  $V_{th}$  sleep transistor is inserted between the power supply and the block to be gated. The high threshold ensures that leakage through the sleep transistor will be negligible. The gate of the sleep transistor is to a control bit that can either be set at configuration time (i.e., static power gating) or during runtime (i.e., dynamic power gating).

Many researchers have explored different points in the design space for power gating granularity in FPGAs. Calhoun et al. [25] perform power gating at the gate level; Gayasen et al. [42] use larger power gating blocks, choosing to gate off regions of 4 CLBs at a time. They show 20% leakage power savings and that coarse-grained power gating with improved placement achieves the same results as fine-grained power gating. Rahman et al. [93] suggest that a combination of fine and coarse-grained

Figure 2.8: Power gating circuit

power gating provides the best results.

In this work we found power gating to be essential to minimizing energy/operation. We used a simple, fined-grained, switch-level power gating scheme to reduce energy (Section 5.1).

**Dual**  $V_{dd}$ : Instead of simply using sleep transistors to disable or enable blocks of logic, they can be used to select from different supply voltages  $(V_{dd})$  to power the block. Because not all paths in a circuit are critical, only elements on critical paths need to be placed in high  $V_{dd}$  regions to ensure fast operation; all other block can be on a low  $V_{dd}$  region to save power. Dual  $V_{dd}$  design has been studied extensively in the FPGA literature [10, 41, 50, 68, 69, 73], typically achieving  $\approx 50\%$  leakage power savings.

**Dual**  $V_{th}$  and **Body Biasing:** Dual  $V_{th}$  FPGAs define low and high  $V_{th}$  regions at fabrication time. High  $V_{th}$  regions reduce leakage at the cost of increased delay. Body biased FPGAs are very similar, using embedded circuitry to change the body the source voltage for regions at configuration time, which effectively changes  $V_{th}$ .

Much work has also been done in dual  $V_{th}$  design for FPGAs [49, 54, 70, 115] with body biasing being integrated into commercial FPGAs [66]. Similar tradeoffs exist when mapping circuits to either dual  $V_{th}$ /body biased architectures or dual  $V_{dd}$  architectures. Critical paths must be placed on low  $V_{th}$  blocks to ensure minimal delay reduction, and timing slack must be available to save leakage energy on non-critical paths. Block granularity is important [49] and selection of appropriate body bias voltages is important [54].

While the previous discussion of  $V_{th}$  and  $V_{dd}$  selection applies at the level of the mapped design, it is also profitable to use different  $V_{th}$  devices for circuits that play different roles in the FPGA

| Technique                   | Level        | Reduces     | Benefit Type  | Benefit    |

|-----------------------------|--------------|-------------|---------------|------------|

| Technology Mapping          | CAD          | $C, \alpha$ | $P_{total}$   | 7.6 - 17%  |

| Clustering                  | CAD          | $C, \alpha$ | $P_{total}$   | 13%        |

| LUT Input Transformation    | CAD          | $I_{leak}$  | $P_{static}$  | 50%        |

| Placement                   | CAD          | $C, \alpha$ | $P_{total}$   | 3.0–13%    |

| Routing                     | CAD          | $C, \alpha$ | $P_{total}$   | 3%         |

| Glitch Routing/Placement    | CAD          | $\alpha$    | $P_{dynamic}$ | 1119%      |

| Logic Block Architecture    | Architecture | C           | $P_{total}$   | 48%        |

| Interconnect Architecture   | Architecture | C           | $P_{total}$   | 12%        |

| Dynamic Voltage Scaling     | Architecture | $V_{dd}$    | $P_{total}$   | 4–54%      |

| Power Gating                | Architecture | $I_{leak}$  | $P_{static}$  | 20%        |

| Dual $V_{dd}$               | Architecture | $V_{dd}$    | $P_{total}$   | 50%        |

| Dual $V_{th}$ /Body Biasing | Architecture | $I_{leak}$  | $P_{static}$  | 43%        |

| Low Swing Interconnect      | Architecture | $V_{dd}$    | $P_{total}$   | 50%        |

| Subthreshold Operation      | Architecture | $V_{dd}$    | $P_{total}$   | $22\times$ |

Table 2.1: Roundup of low-power FPGA techniques

architecture. Notably, high  $V_{th}$  devices can significantly reduce the configuration SRAM bit leakage reduced without impacting area or delay [115]. Configuration bits are a prime candidate for high  $V_{th}$  transistors because they constitute a significant fraction of FPGA area and are always on and leaking. Fortunately, configuration bits are set only at configuration time and do not contribute any delay or switching energy to mapped circuits. Increasing configuration SRAM  $V_{th}$  has been shown to reduce leakage energy by 43% for a particular implementation [115]. Today's commercial FPGAs are fabricated with three different effective threshold voltages to reduce leakage [56].

In this work we found multiple  $V_{th}$  voltages to be very beneficial in controlling SRAM energy. We utilize high  $V_{th}$  transistors for SRAM cells to substantially reduce their leakage energy (Section 3.1.6).

Low Swing Interconnect: A low swing interconnect segment consists of a driver and receiver operating at nominal voltages, with the wire between them operating at reduced voltage. The driver converts a full swing input into a low swing interconnect signal and the receiver converts it back. With this technique the amount of dynamic energy dissipated in interconnect segments can be reduced significantly; for an FPGA, interconnect energy can be reduced by a factor of 2 [43].

Subthreshold Design: We have seen that minimal energy/operation is achieved when  $V_{dd}$  is set below the threshold voltage (Section 2.2). Ryan et al. fabricated an FPGA designed for subthreshold operation, demonstrating a very significant 22× energy reduction relative to a conventional FPGA at full  $V_{dd}$  [100]. The design used dual  $V_{dd}$ , low swing interconnect to reduce energy and improve delay. Our work builds on this idea, similarly constructing an FPGA architecture targeted for minimum energy, subthreshold operation. We explore the impact of variation on a subthreshold FPGA, and demonstrate the benefits of component-specific mapping and architectural design space exploration. **Summary:** Table 2.1 summarizes low-power FPGA techniques, the level at which they operate, the terms in the power equations they attempt to reduce, the type of power reduction, and the demonstrated benefit. It is important to note that the experimental parameters for each technique explored in prior work is very different, so the savings achieved per technique may not be directly comparable.

This work uses many low-power concepts explored in prior work. Most importantly, we build upon the idea of operating an FPGA in subthreshold, which yields tremendous energy savings. In terms of CAD we focus primarily on routing for variation tolerance; we do not alter the routing cost function to target low power. Similar to prior work, we found the energy savings to be negligible considering the delay cost.

We leverage the work done in architectural exploration, selecting our minimum-energy architectural parameters  $(k, N, L_{seg})$  according to those found in prior work. Additionally, we examine the energy impact of several architectural optimizations not explored before: CLB I/O sparing, extra channels, and buffer sizing. We also re-examine the impact of power gating at different granularities in detail in Chapter 5 for the purposes of on component-specific routing.

Finally, we demonstrate energy savings of  $1.68-2.95\times$ , larger than the savings shown by most prior work in FPGA power reduction.

#### 2.4.2 Variation Tolerance in FPGAs

To tolerate FPGA parameter variation, researchers have employed many of the same techniques used for ASICs and CPUs. Typically these optimizations fall under statistical CAD techniques or architectural parameter selection. To describe the impact of variation and the benefits of variation tolerance on FPGA designs, metrics like timing yield and power yield are often used.

**SSTA:** A heavily researched method for dealing with variation during the technology mapping, place and route stages of an ASIC design is the use of statistical static timing analysis (SSTA). SSTA attempts to model variability directly in CAD algorithms to help produce circuits that inherently account for variation. Traditional CAD algorithms do not aggressively minimize near-critical paths since their reduction would not reduce the delay of the circuit. However, near critical paths are important under variation because there is a probability that they will become critical. SSTA is a methodology that identifies statistically critical paths and enables CAD algorithms to optimize those paths. Integrating SSTA into clustering, placement and routing algorithms of the FPGA CAD flow simply involves replacing the nominal STA routine with an SSTA routine.

FPGA CAD algorithms modified for SSTA have been studied for placement [78] and routing [58, 109]. Lin et al. studied a full SSTA CAD flow with clustering, placement, and routing and characterized the interaction between each stage [75]. For a 65 nm predictive technology with  $3\sigma_{L_{eff}}/\mu_{L_{eff}}$  and  $3\sigma_{V_{th}}/\mu_{V_{th}}$  of 10%, 10%, and 6% for D2D, WID spatially correlated, and WID random variation, they observed that SSTA based clustering alone can improve  $\mu_{\tau}$  and  $\sigma_{\tau}$  by 5.0% and 6.4% respectively, and improve timing yield by 9.9%. Placement improves  $\mu_{\tau}$ ,  $\sigma_{\tau}$  and timing yield by 4.0%, 6.1%, and 8.0%; routing achieves 1.4%, 0.7%, and 2.2% improvement. All three SSTA algorithms combined yield 6.2%, 7.5%, and 12.6% improvement.

A critical distinction between this work and SSTA is that SSTA is used for one-sized-fits-all mapping, not component-specific mapping. SSTA attempts to make predictions for a single mapping that will be statistically beneficial for many different mappings. The advantage of component-specific mapping is that it is able to customize mappings per chip, rather than estimating optimized mappings prior to fabrication.

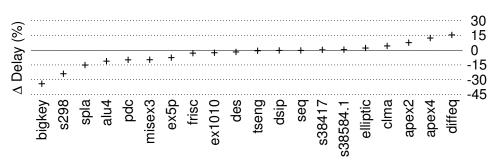

Architecture Optimization: Similar to finding architectural values of N and k that reduce energy, one can attempt to find the values of architectural parameters that improve timing and leakage yield.